Patents

Literature

225 results about "Transistor–transistor logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Transistor–transistor logic (TTL) is a logic family built from bipolar junction transistors. Its name signifies that transistors perform both the logic function (the first "transistor") and the amplifying function (the second "transistor"); it is the same naming convention used in resistor–transistor logic (RTL) and diode–transistor logic (DTL).

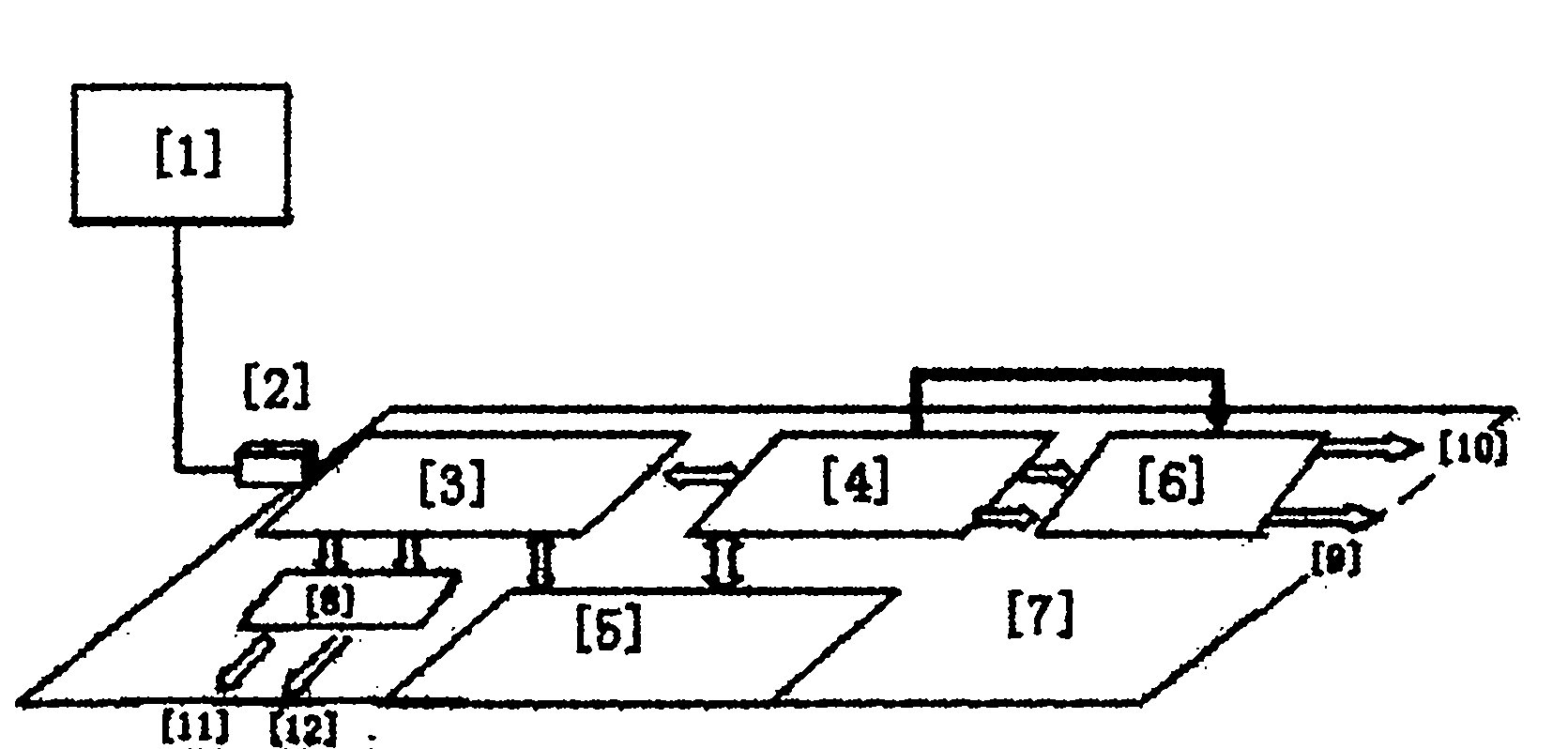

Magnetic navigation system suitable for automatic guided vehicle (AGV) and navigation method

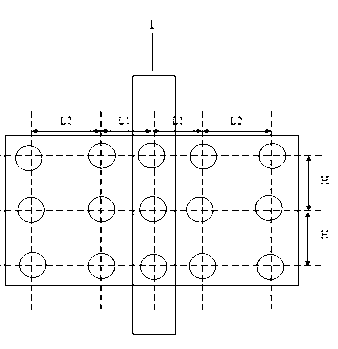

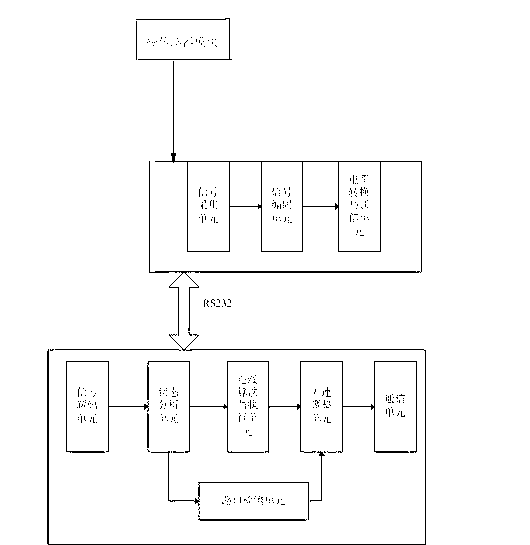

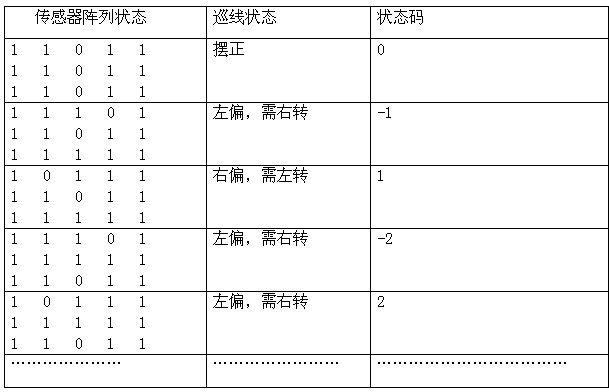

ActiveCN103292806AControl the trajectoryImprove navigation speedNavigation instrumentsSensor arrayTransistor–transistor logic

The invention discloses a magnetic navigation system suitable for an automatic guided vehicle (AGV) and a navigation method. The system comprises a sensor module, a magnetic sensor signal acquisition module and a line patrol main board module, wherein a sensor array of the magnetic sensor signal acquisition module is arranged in a three-row five-column form; the magnetic sensor signal acquisition module acquires a transistor transistor logic (TTL) level signal of each sensor and encodes the level signal into a specified 16-scale protocol form; the level signal is converted into a 232 level signal and is transmitted to the line patrol main board module for analysis, and the current line patrol state of the AGV is obtained, the AGV left and right wheel differential adjustment is performed according to the line patrol state, and the AGV line patrol state and the intersection detection result are reported to an upper computer. The system is high in navigation speed and small in swing amplitude, can well control the motion track of the AGV and can be applied to various types of intersections.

Owner:CHENGDU SIWI HIGH TECH IND GARDEN

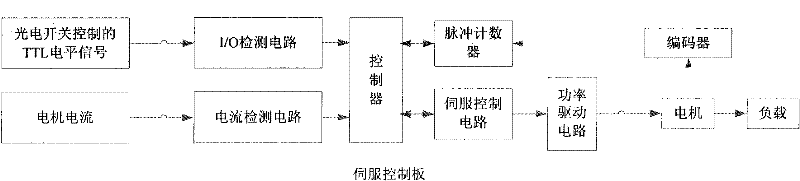

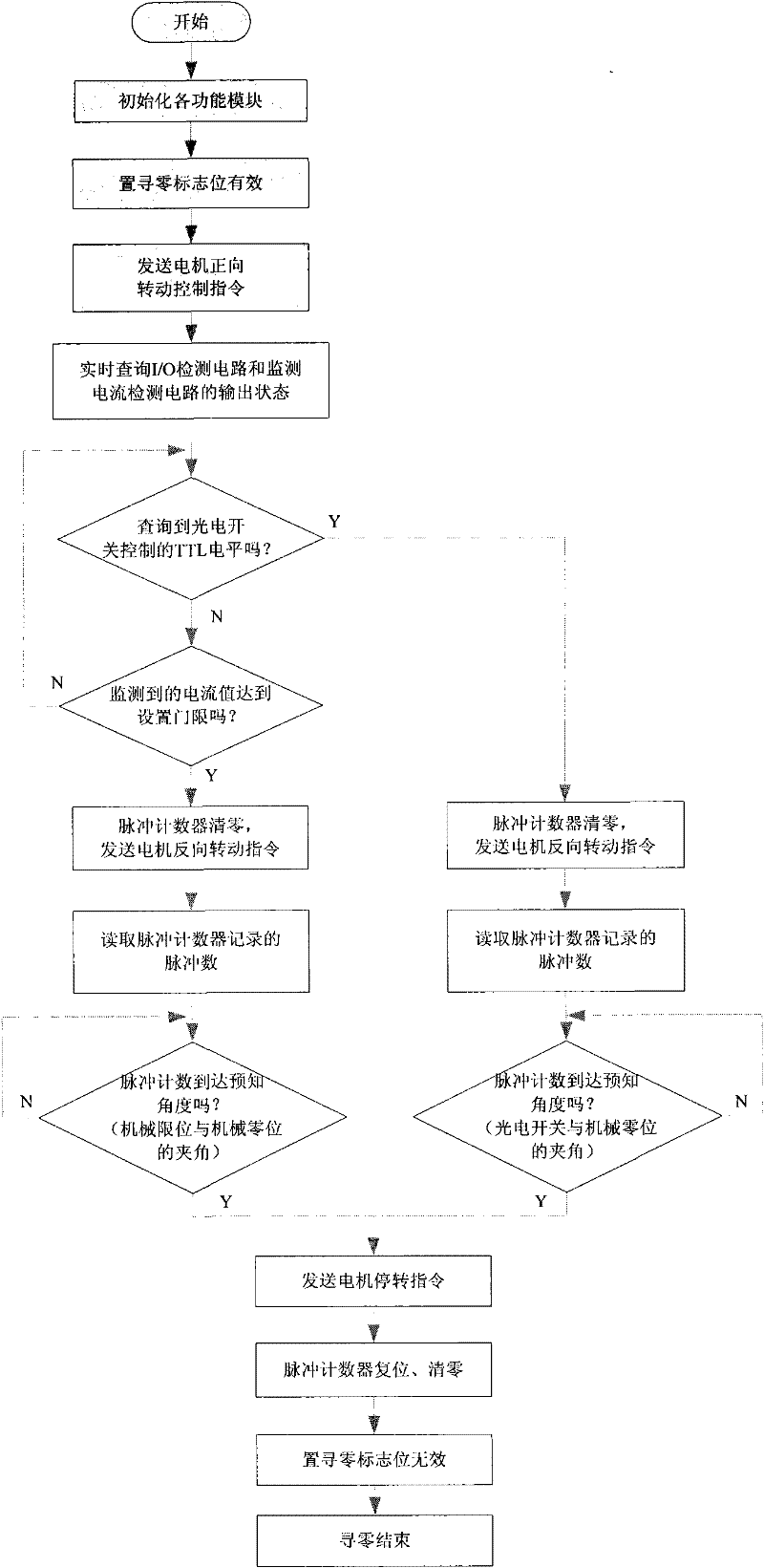

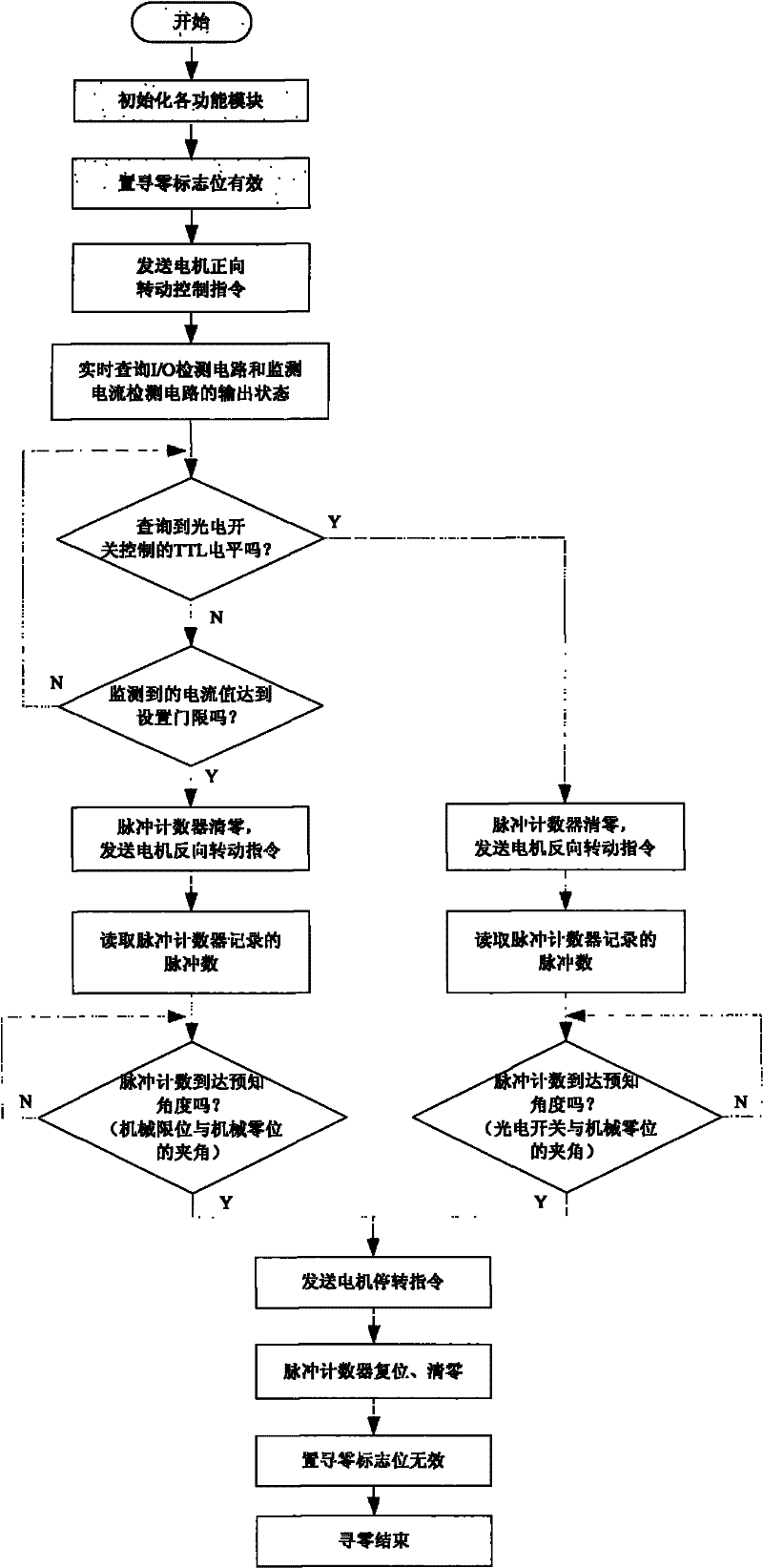

Zero position-searching method for limited angle servo turntable

ActiveCN102183916AHigh working reliabilityLow costConverting sensor output opticallyNumerical controlTurn angleTransistor–transistor logic

The invention discloses a zero position-searching method for a limited angle servo turntable and belongs to the technical field of servo control. In the method, an optoelectronic switch is installed between a mechanical zero position and a positive limit of the servo turntable; the position of the optoelectronic switch and the positive mechanical limit are respectively taken as a first reference point and an auxiliary reference point of the method; a motor rotates positively when the servo turntable turns on; and the motor can be controlled to reversely rotate at a corresponding known angle when a transistor-transistor logic (TTL) level signal controlled by the optoelectronic switch is searched or a current value of the motor is monitored to reach a set threshold value, and then the accurate mechanical zero position can be found out. According to the method, the zero position searching is performed by preferably using the first reference point and is carried out through the auxiliary reference point when the optoelectronic switch is out of work. Moreover, the zero position-searching reliability and the working stability of the servo turntable are improved by the method on the basis of not increasing any cost.

Owner:CHINA NORTH IND NO 205 RES INST

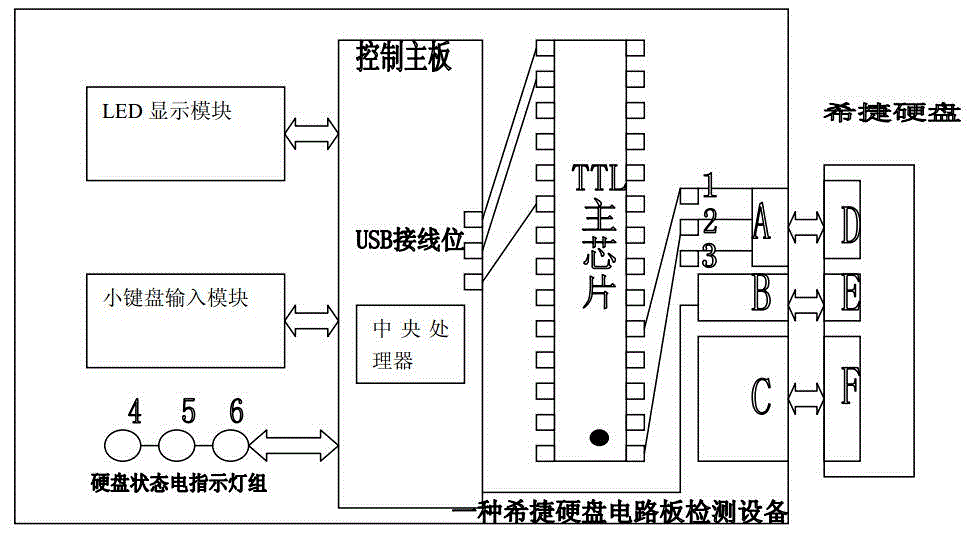

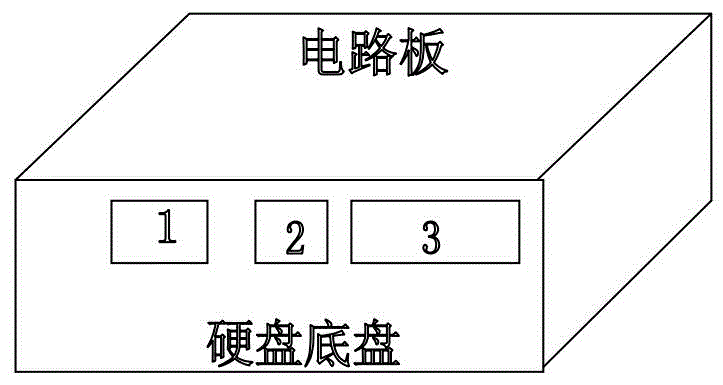

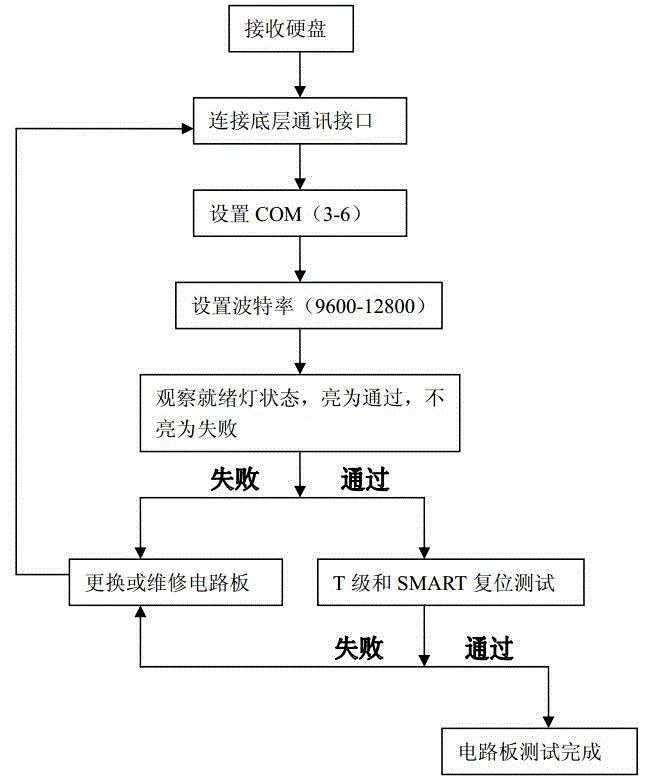

Seagate hard disk circuit board detection equipment and detection method

The invention discloses Seagate hard disk circuit board detection equipment, which comprises an enclosure, a detection control mainboard, a TTL (transistor-transistor logic) main chip circuit board, one row of four-core hole type interface, a power supply module, an LED display module, a keypad input module and a hard disk state electric indicating lamp group, wherein the detection control mainboard is provided with a central processing unit; the control mainboard is connected with the TTL main chip circuit board by a USB wiring position; the TTL main chip circuit board is connected with one row of four-core hole type interface; the control mainboard is connected with a target Seagate hard disk by an ATA signal interface wire; the power supply module supplies power to the Seagate hard disk circuit board detection equipment and the target Seagate hard disk; the row of four-core hole type interface is connected with the power supply module and the target Seagate hard disk; and the keypad input module, the LED display module and the hard disk state electric indicating lamp group are each connected with the control mainboard. The invention also discloses a Seagate hard disk circuit board detection method which can be used for precisely judging the state of the Seagate hard disk circuit board so as to confirm whether deep maintenance can be carried out to the target Seagate hard disk.

Owner:蔡敏灵

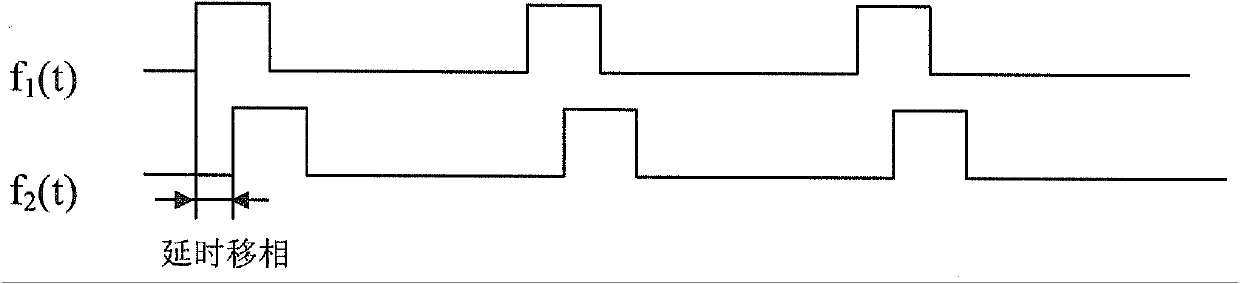

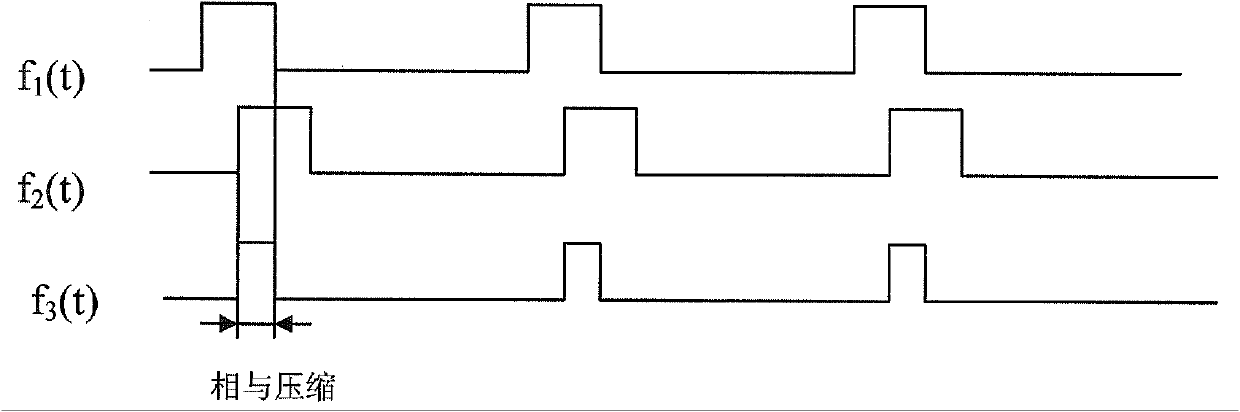

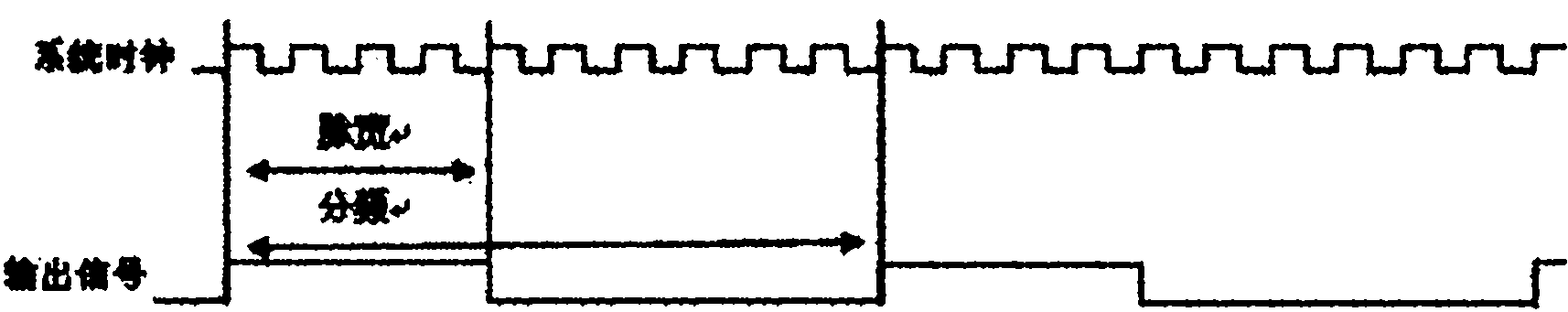

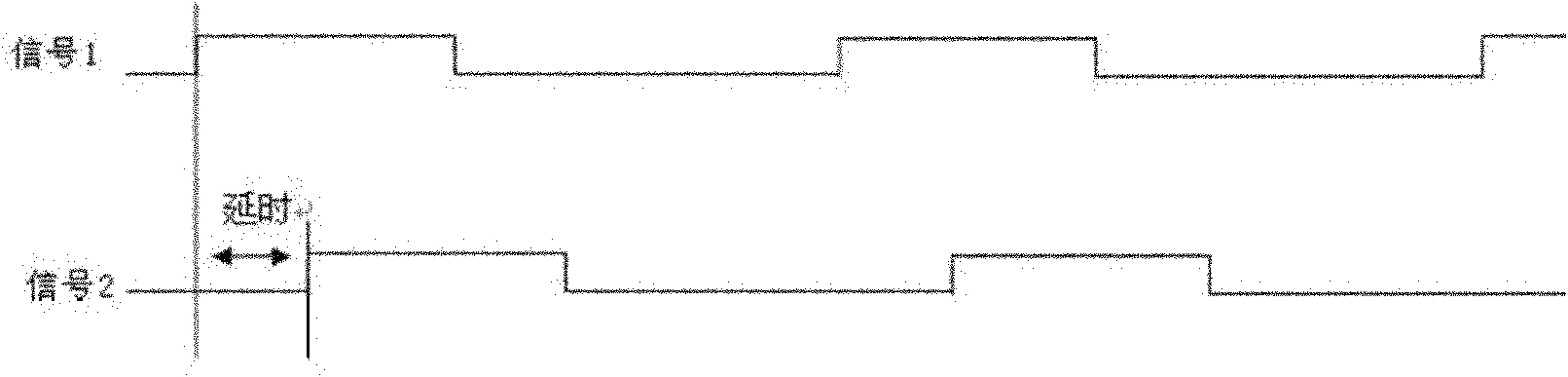

Picosecond-accuracy narrow-pulse width transistor-transistor logic (TTL) signal acquisition method based on phase shift AND operation

InactiveCN102170277AMeet Timing RequirementsImproved Pulse Width Regulation AccuracyElectric pulse generator circuitsPicosecondRange gate

The invention relates to the technical field of range gated imaging, and discloses a picosecond-accuracy narrow-pulse width transistor-transistor logic (TTL) signal acquisition method based on phase shift AND operation. The method comprises the following steps of: dividing each path of TTL pulse triggering signals comprising pulse laser triggering signals and intensified charge coupled device (ICCD) triggering signals in range gating into two paths of time sequence signals with completely identical phase and amplitude by using a multipath generator; delaying one of the divided two paths of signals by adopting a picosecond-accuracy delay line technology to produce a phase shift between the two paths of signals; and then causing the two paths of signals to pass through a logic AND gate for a logic AND operation, thereby compressing a pulse width. By the method, the phase shift between the two paths of signals is accurately controlled to obtain high-accuracy pulse width signals and higher pulse width compression accuracy, and the compressed pulse width can be close to the limit of the TTL signal, namely the order of magnitude of 1ns; and the method is applied in the field of gating application such as range gated three-dimensional imaging, underwater imaging and the like with high-accuracy time sequence requirements.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

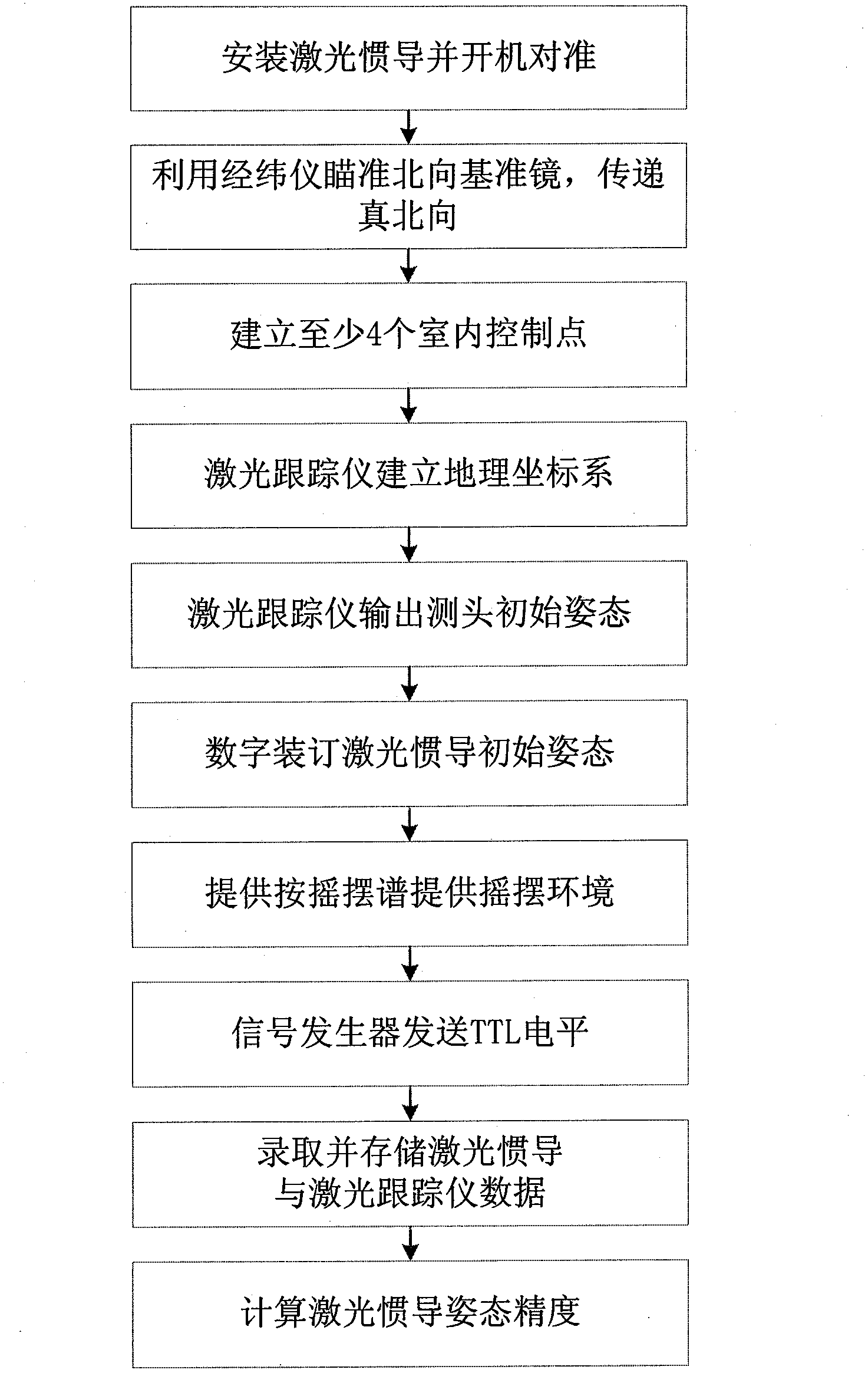

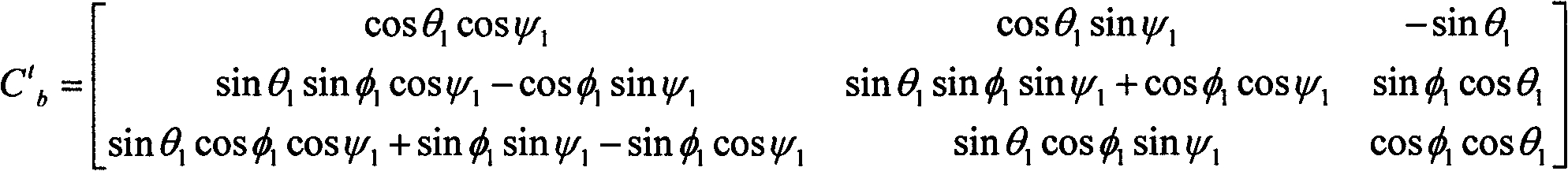

Attitude precision estimation method of multiple high-accuracy inertial navigations system

InactiveCN102706361AReduce measurement uncertaintyGuaranteed uptimeMeasurement devicesTransistor–transistor logicEstimation methods

The invention provides an attitude precision estimation method of multiple high-accuracy inertial navigation systems. According to the method, a set of laser tracker, an attitude measuring head, a signal generator, a swing table or turntable, and a data recording device are used to realize the attitude precision estimation of multiple high-accuracy inertial navigation systems at the same time through initial alignment calibration and synchronous data acquisition, wherein the swing table or turntable is used for providing a dynamic swing environment and can realize pitching, horizontal rolling and longitudinal swing according to a given period and amplitude value, the laser tracker and components matched with the laser tracker can measure three attitude angles of the swing table under a geographical system in real time, the signal generator sends TTL (transistor-transistor-logic) synchronizing level to the laser tracker and the laser inertial navigation systems so as to trigger data output, and the data recording device is used for receiving attitude data sent by the laser tracker and the inertial navigation systems in real time and storing the attitude data into lines. The method is quite suitable for the attitude precision estimation of the laser inertial navigation systems and can be used for estimating the attitude precision of multiple high-accuracy laser inertial navigation systems at the same time by using simplest equipment components.

Owner:中国人民解放军92537部队

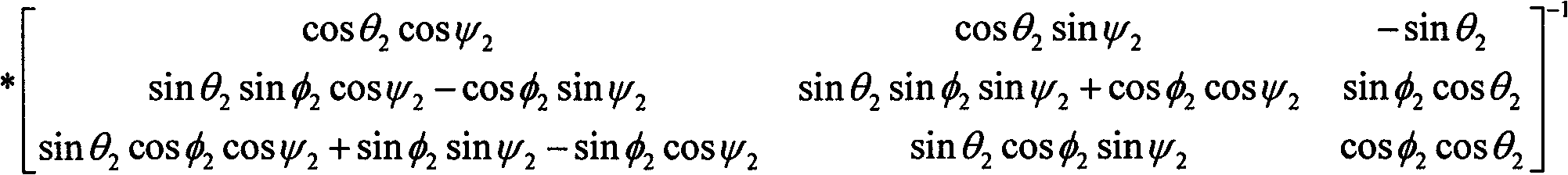

Image processing device and method as well as system

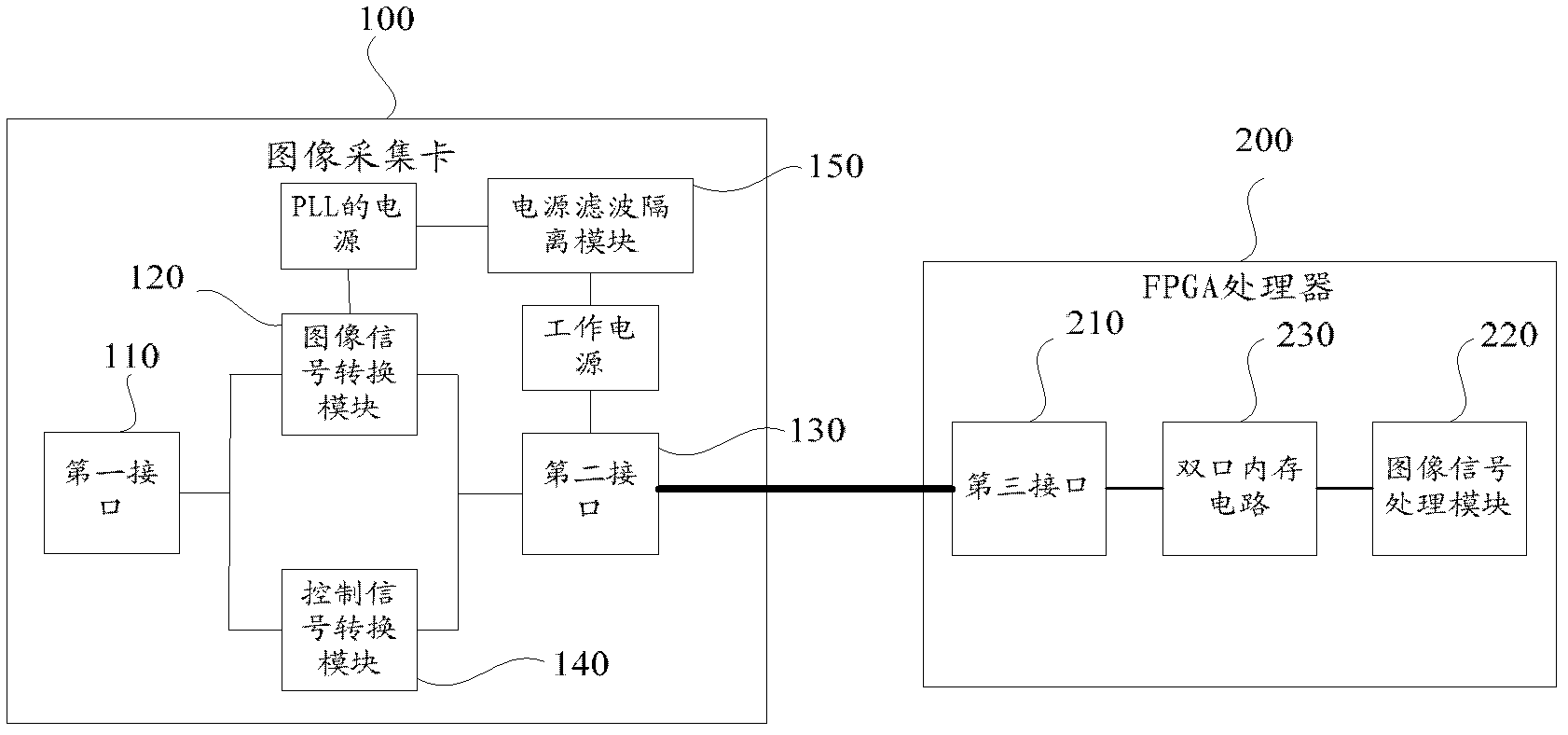

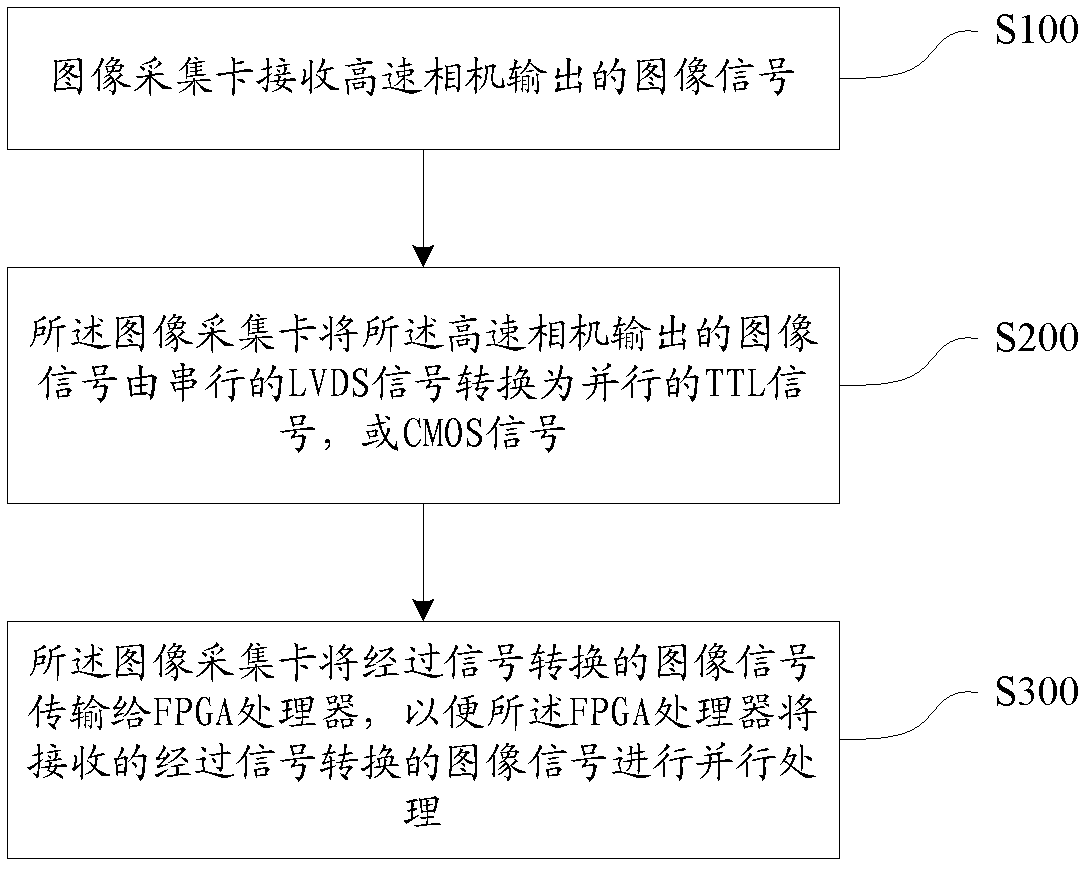

InactiveCN102629968ARealize processingGuaranteed reliabilityTelevision system detailsColor television detailsLow voltageField-programmable gate array

The embodiment of the invention provides an image processing device and method as well as system. The image processing device comprises an image acquisition card and a FPGA (Field Programmable Gate Array) processor; the image acquisition card comprises a first interface, an image signal conversion module and a second interface, wherein the first interface is used for receiving image signals output by a high-speed camera, the image signal conversion module is used for converting the image signals into parallel TTL (Transistor-Transistor Logic) signals or CMOS (Complementary Metal Oxide Semiconductor) signals from serial LVDS (Low Voltage Differential Signals), and the second interface is used for transmitting the image signals subjected to the signal conversion to the FPGA processor; and the FPGA processor comprises a third interface and an image signal processing module, wherein the third module is used for receiving the image signals which are transmitted by the second interface and are subjected to the signal conversion, and the image signal processing module is used for carrying out parallel processing on the received image signals. The image processing device solves the problem that the prior art is high in cost as multiple devices are adopted for processing the image signals, and simultaneously the image signals are processed in a hardware manner, thereby the reliability of the image signal processing is ensured.

Owner:HUNAN RAMON SCI & TECH

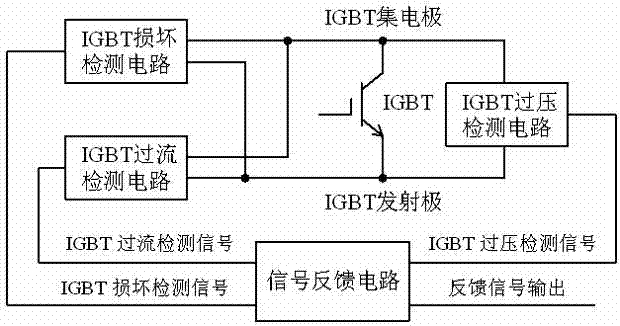

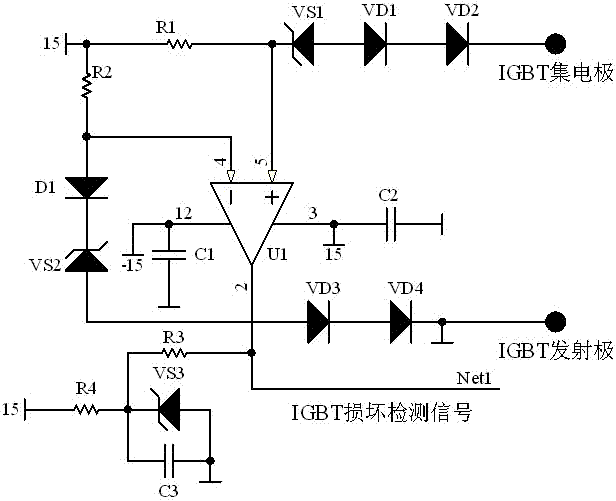

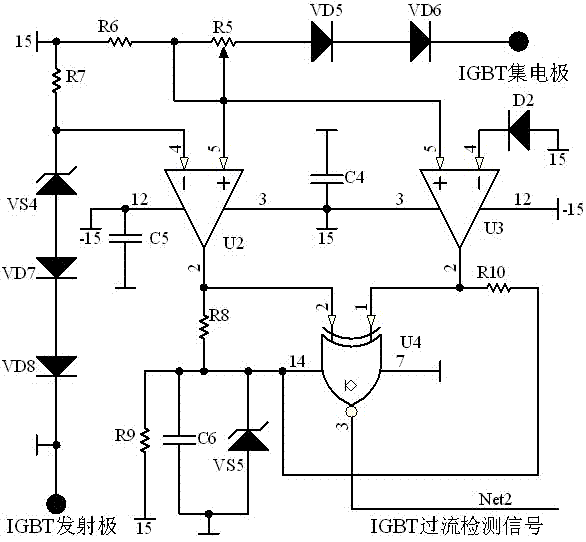

Insulated gate bipolar transistor (IGBT) fault detection circuit

InactiveCN103033732AFast outputCurrent/voltage measurementIndividual semiconductor device testingOvervoltageTransistor–transistor logic

The invention discloses an insulated gate bipolar transistor (IGBT) fault detection circuit which comprises an IGBT damage detection circuit, an IGBT over-current detection circuit, an IGBT overvoltage detection circuit and a signal feedback circuit. Three detection circuits can detect voltage of an IGBT collector electrode - emitting electrode through high flexibility voltage comparers, the voltage is compared with reference voltage set by the voltage comparers, and detection results of all detection circuit can be input into the signal feedback circuit in a transistor-transistor logic (TTL) electrical level mode. When any fault of damage, over current and overvoltage of the IGBT happens, optical fiber light emitting heads in the feedback circuit can all be triggered. The achieved fault feedback signals can be separated and transmitted by optical fibers to be output by a high speed optocoupler. The IGBT fault detection circuit can detect whether the IGBT is damaged in real time, can detect whether over current of the IGBT happens in real time, can detect whether overvoltage of the IGBT happens, and can quickly output fault feedback signals when any fault happens.

Owner:ZHEJIANG UNIV

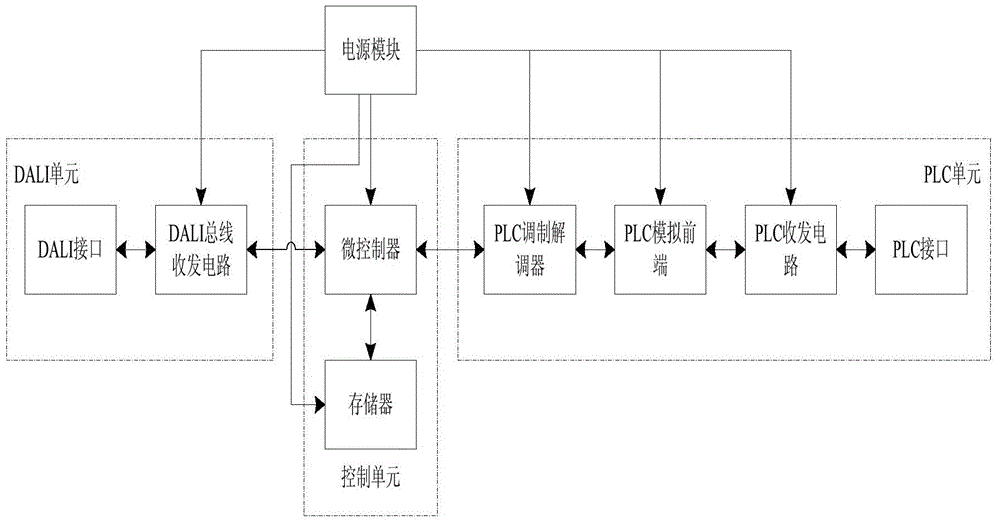

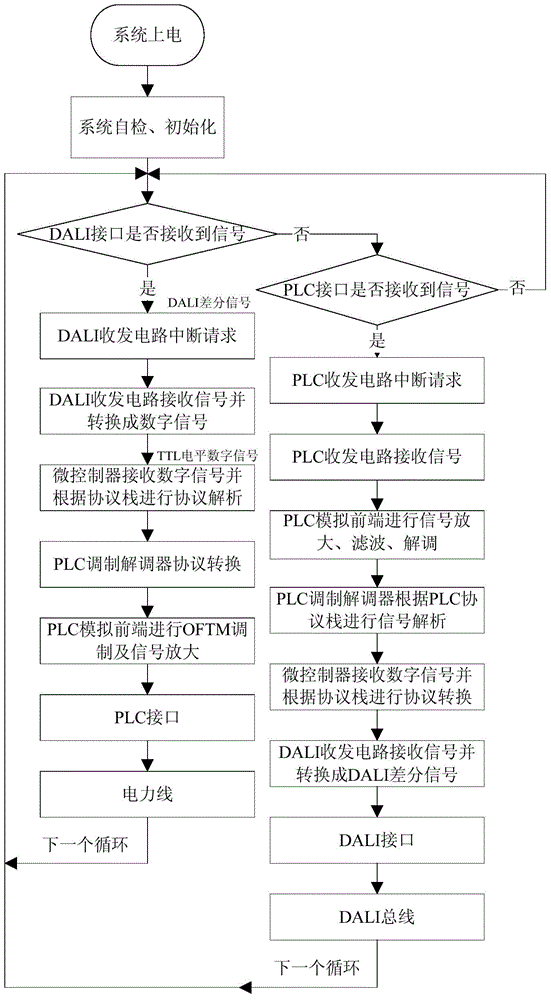

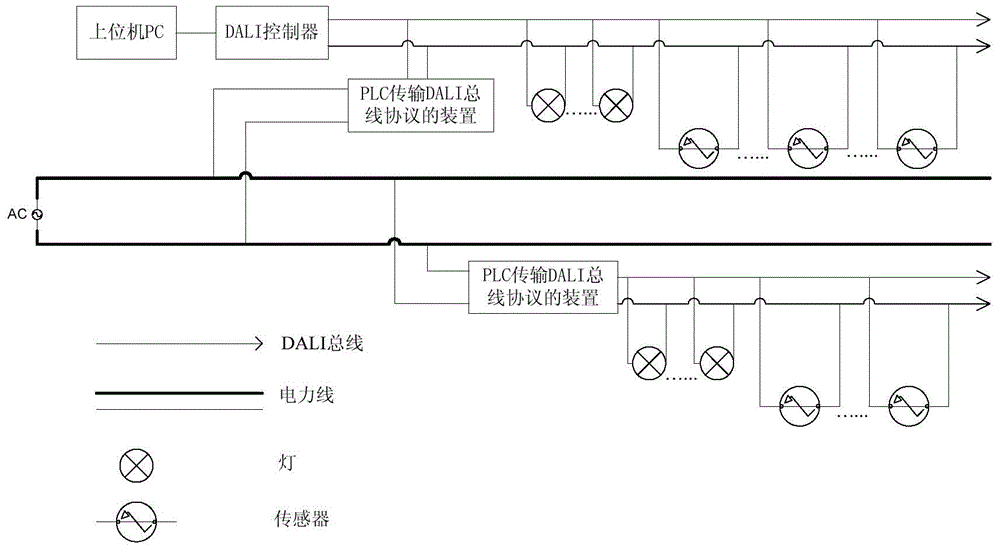

Device and method for converting DALI (digital addressable lighting interface) protocol data and lighting control system

ActiveCN104797046AMeet high scalability needsFlexible operationElectric light circuit arrangementEnergy saving control techniquesIntelligent lightingDifferential signaling

The invention discloses a device and a method for converting DALI (digital addressable lighting interface) protocol data and a lighting control system. The device comprises a DALI unit, a PLC (programmable logic control) unit and a control unit. DALI bus differential signals and first TTL (transistor-transistor logic) intermediate level signals can be converted by the DALI unit; PLC signals carried on electric power lines and second TTL intermediate level signals can be converted by the PLC unit; the first TTL intermediate level signals and the second TTL intermediate level signals can be converted by the control unit on the basis of DALI protocol stacks. The device can work in two working states. The device and the lighting system have PLC receiving and transmitting functions, the DALI bus differential signals can be transmitted via the electric power lines, DALI terminals can be addressed and controlled on the basis of DALI bus protocols, large-scale and high-expansibility requirements of the intelligent lighting control system can be met, and the device, the method and the lighting control system have the advantages of energy conservation, high efficiency and flexibility in operation.

Owner:四川九洲投资控股集团有限公司

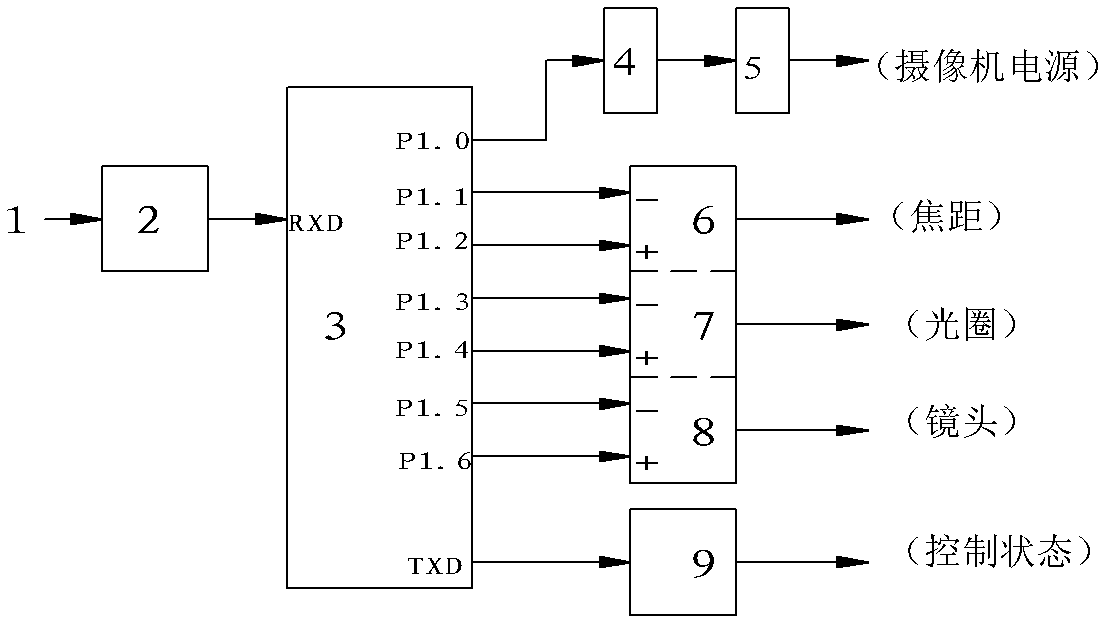

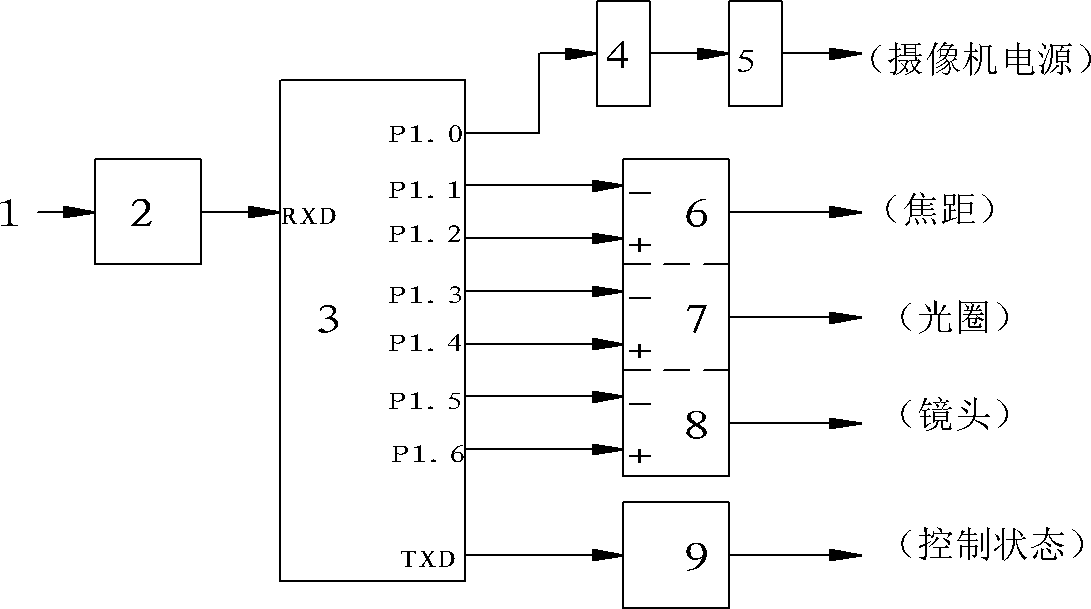

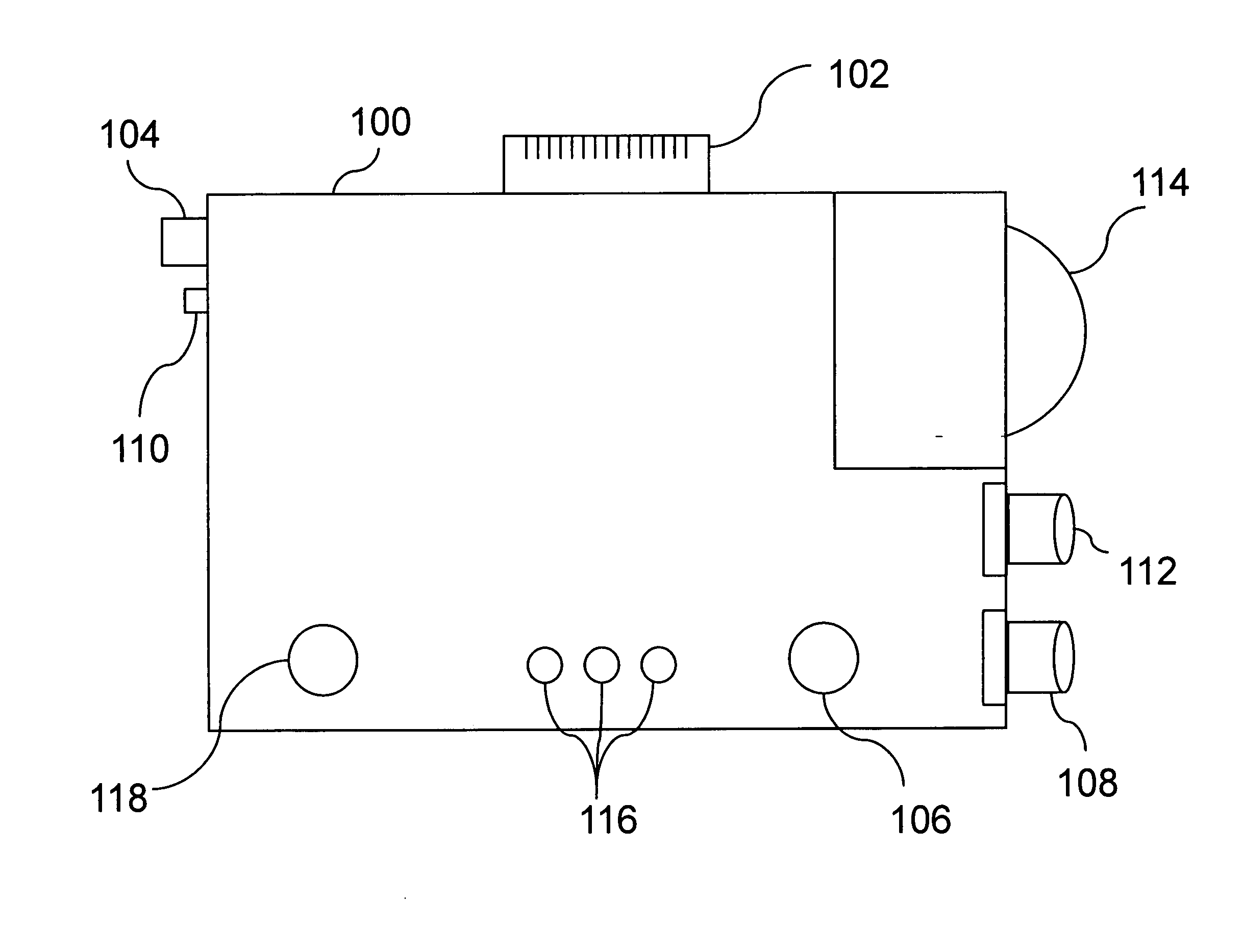

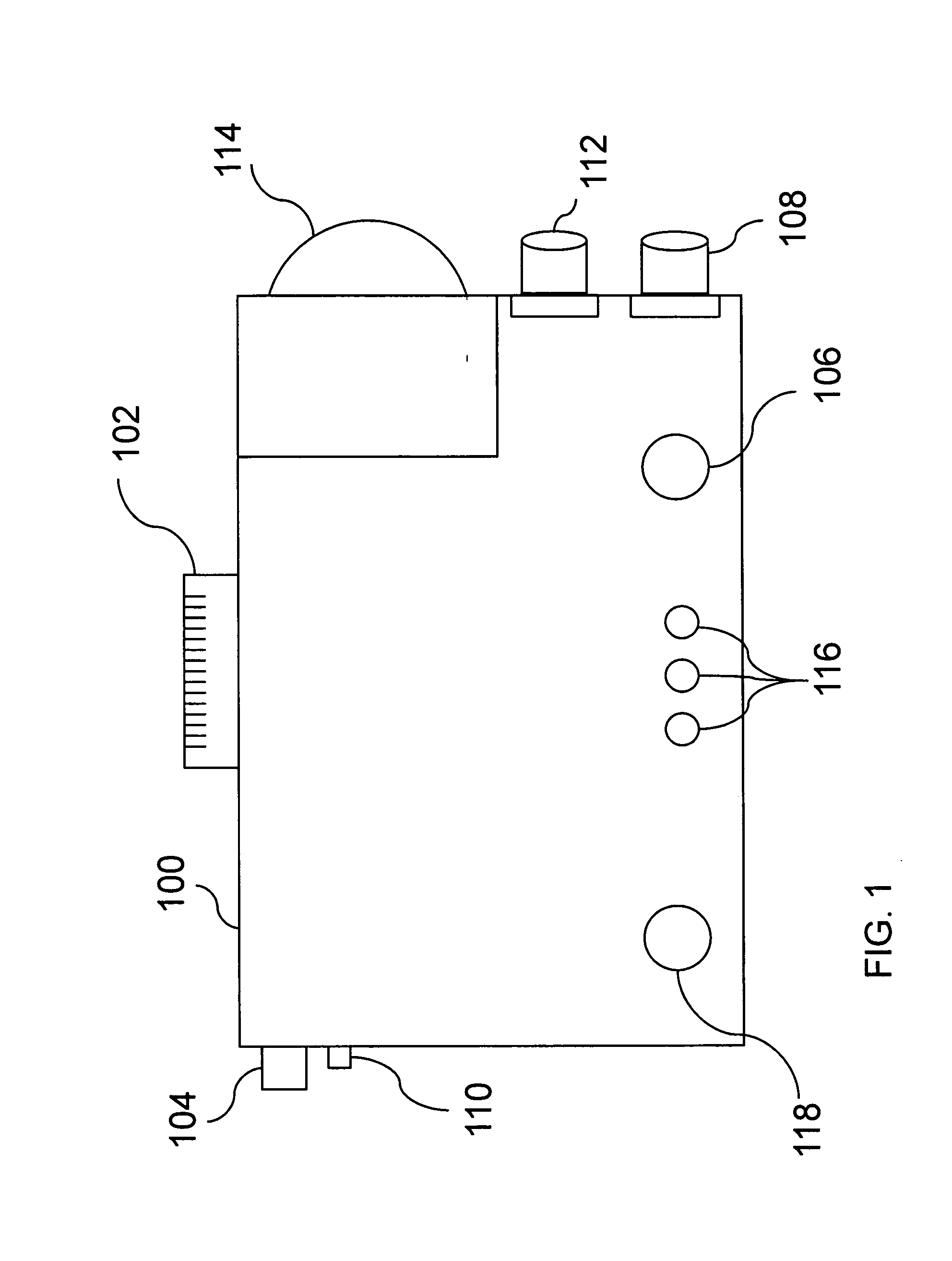

Small-sized airborne camera controller

InactiveCN102629987AImplement bilateral level controlOvercome remote controlTelevision system detailsElectric signal transmission systemsMicrocomputerMicrocontroller

The invention discloses a small-sized airborne camera controller. The small-sized airborne camera controller is characterized in that a control instruction enters an instruction decoding circuit through an instruction receiving circuit, the instruction decoding circuit recognizes different control functional codes, then corresponding TTL (Transistor-Transistor Logic) level is written into data I / O (Input / Output) ports of the instruction decoding circuit, wherein one path enters a power source switch driving circuit which completes the on-off control on a camera power source, any two of the other six paths form a group which respectively enters inverse and same-phase input ends of a bilateral level driving circuit to complete the focal length control on a camera; and simultaneously, the TTL level is coded according to a stated frame formal and enters the input end of a control state transmission circuit through an asynchronous serious data transmitting end of a single-chip microcomputer to realize the real time monitoring on the control state of the camera. The small-sized airborne camera controller has the advantages that the circuits are simplified, the volume is reduced, the control state of the camera can be collected in real time, and the remote control and monitoring on the camera is realized.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

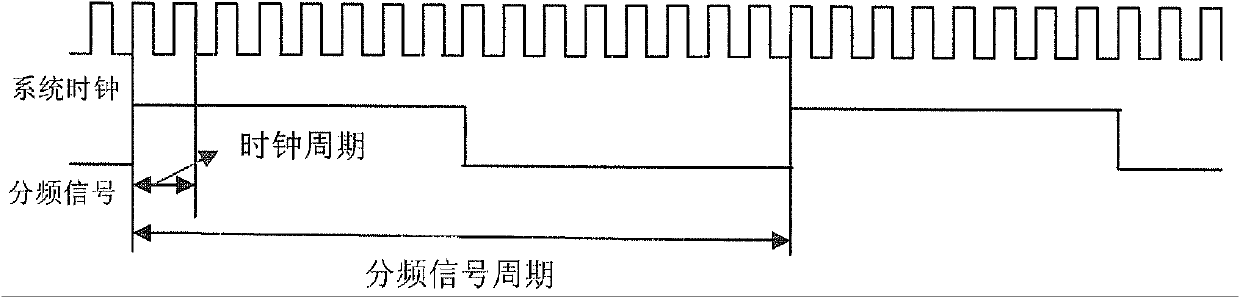

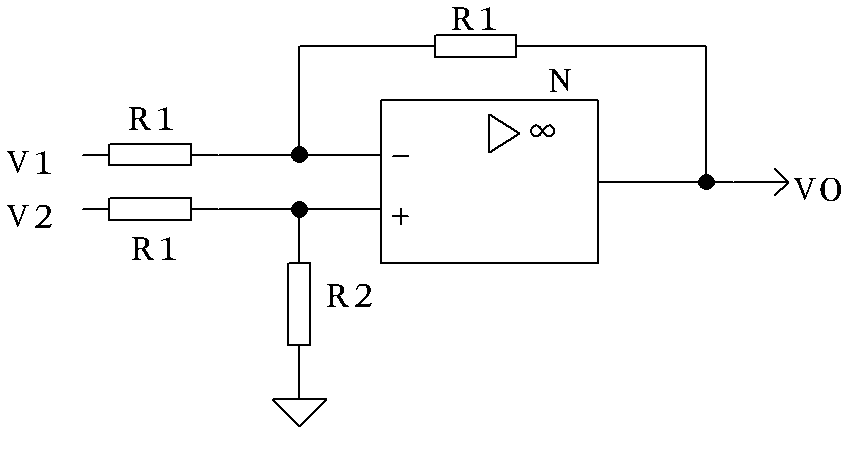

Range gating based laser imaging synchronous control system

ActiveCN102096388ADelay real-time adjustmentConvenient delay compensationProgramme control in sequence/logic controllersTime delaysRange gate

The invention discloses a range gating based laser imaging synchronous control system. The system comprises a computer software interface, a USB interface, a micro controller, an FPGA (field programmable gate array), a peripheral circuit, a time delay fine tuning circuit, a PCB (printed circuit board) and an operational amplifier, wherein the data sent out from the computer software interface aretransmitted to the micro controller by virtue of the USB interface; the micro controller transmits the frequencies, pulse width parameters of triggering signals of a pulse laser and an ICCD (intensified charge coupled device) and control parameters of delays and mutual delay of the two triggering signals to the FPGA; the FPGA generates two TTL (transistor-transistor logic) signals which are used for triggering the pulse laser and the ICCD and are adjustable (coarse tuning) in frequency, pulse width, delay and interactive delay after receiving the control parameters, the two signals are used for realizing fine tuning on the delays and the interactive delay by virtue of the time delay fine tuning circuit, and finally the pulse laser and the ICCD are triggered. By applying the system in the invention, the aim of flexibly setting imaging parameters can be achieved; and meanwhile, the structure is compact, and the system is convenient to carry and use and has good stability.

Owner:北京中科盛视科技有限责任公司

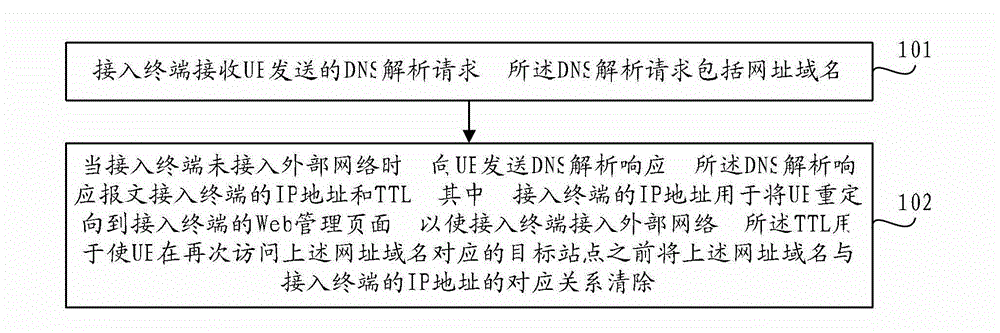

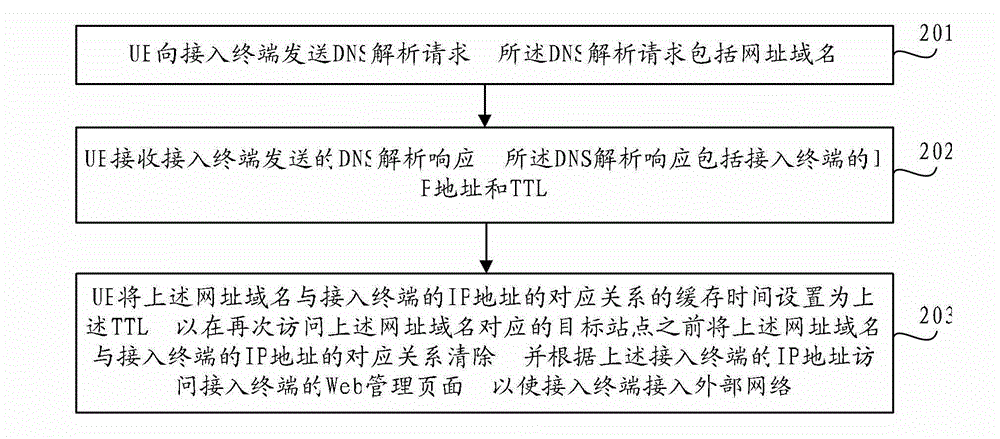

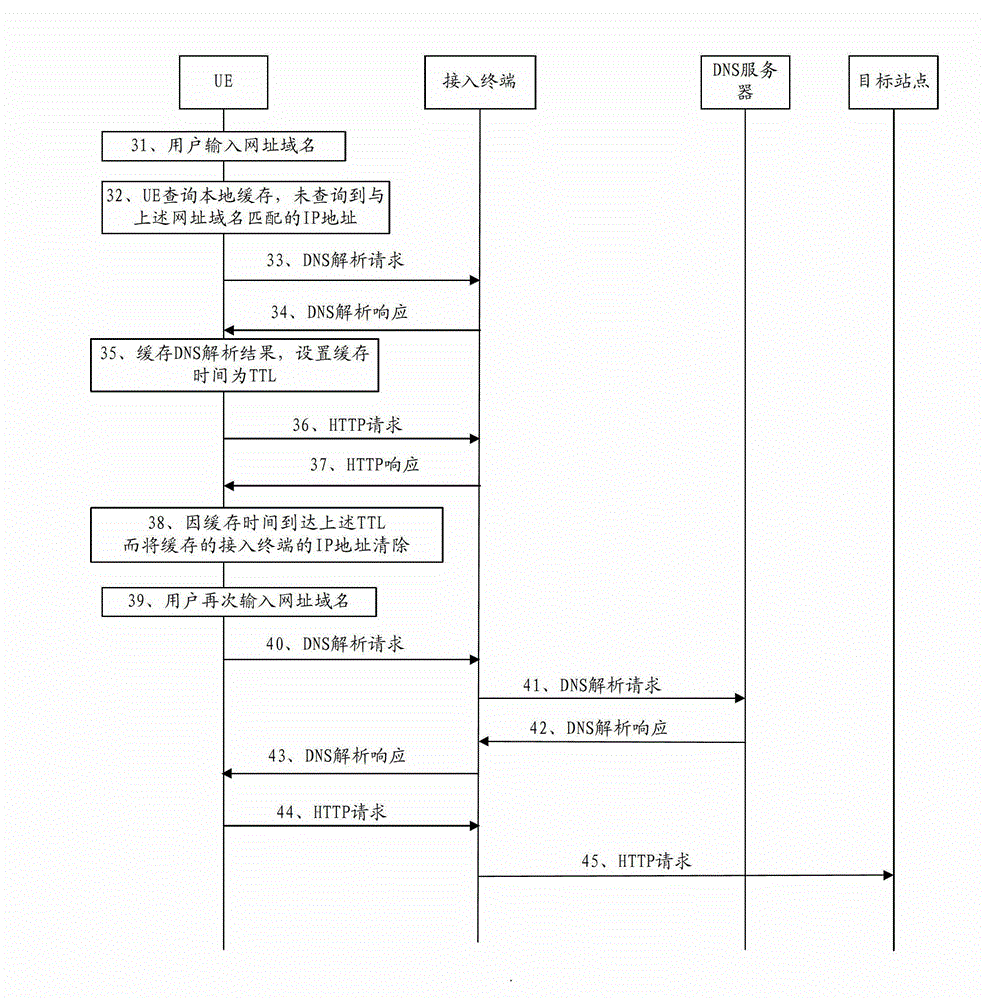

Redirection method and device

InactiveCN102752411ASolve the problem of not being able to access the target siteTransmissionWeb siteTransistor–transistor logic

The embodiment of the invention provides a redirection method and a redirection device. The redirection method comprises the steps as follows: an access terminal receives a DNS (domain name server) analysis request transmitted by UE (user equipment); the DNS analysis request comprises a web site domain name; the access terminal transmits the DNS analysis response to the UE when not being accessed into an external network; and the DNS analysis response comprises an IP (internet protocol) address and a TTL (transistor-transistor logic) of the access terminal, wherein the IP address of the access terminal is used for directing the UE to a Web management page of the access terminal, so the access terminal is accessed into the external network, and the TTL is used for clearing the corresponding relation between the web site domain name and the IP address of the access terminal before the UE accesses a destination website corresponding to the web site domain name again. According to the technical scheme disclosed by the invention, the problem that a user cannot access the destination website is solved.

Owner:HUAWEI DEVICE CO LTD

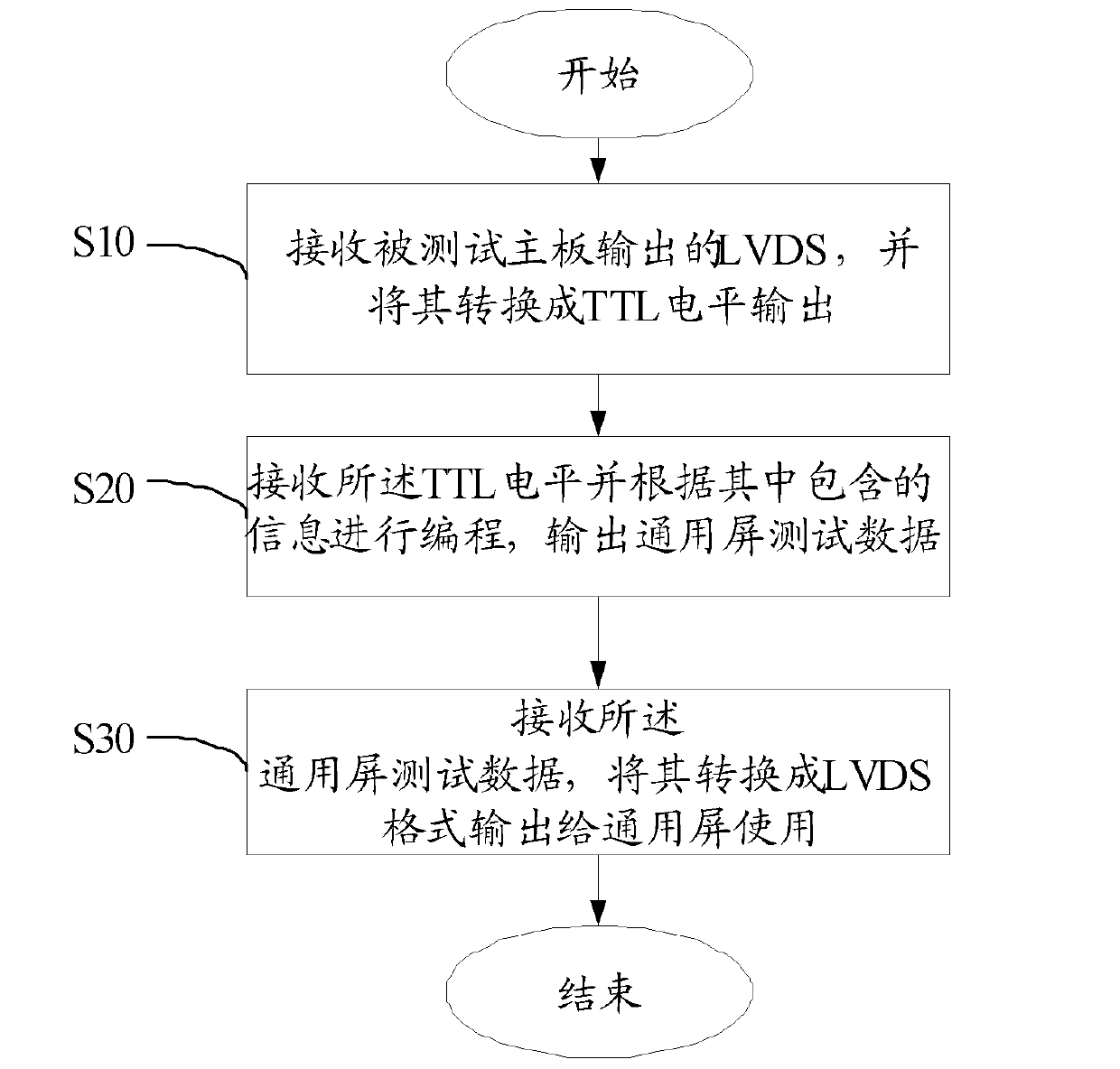

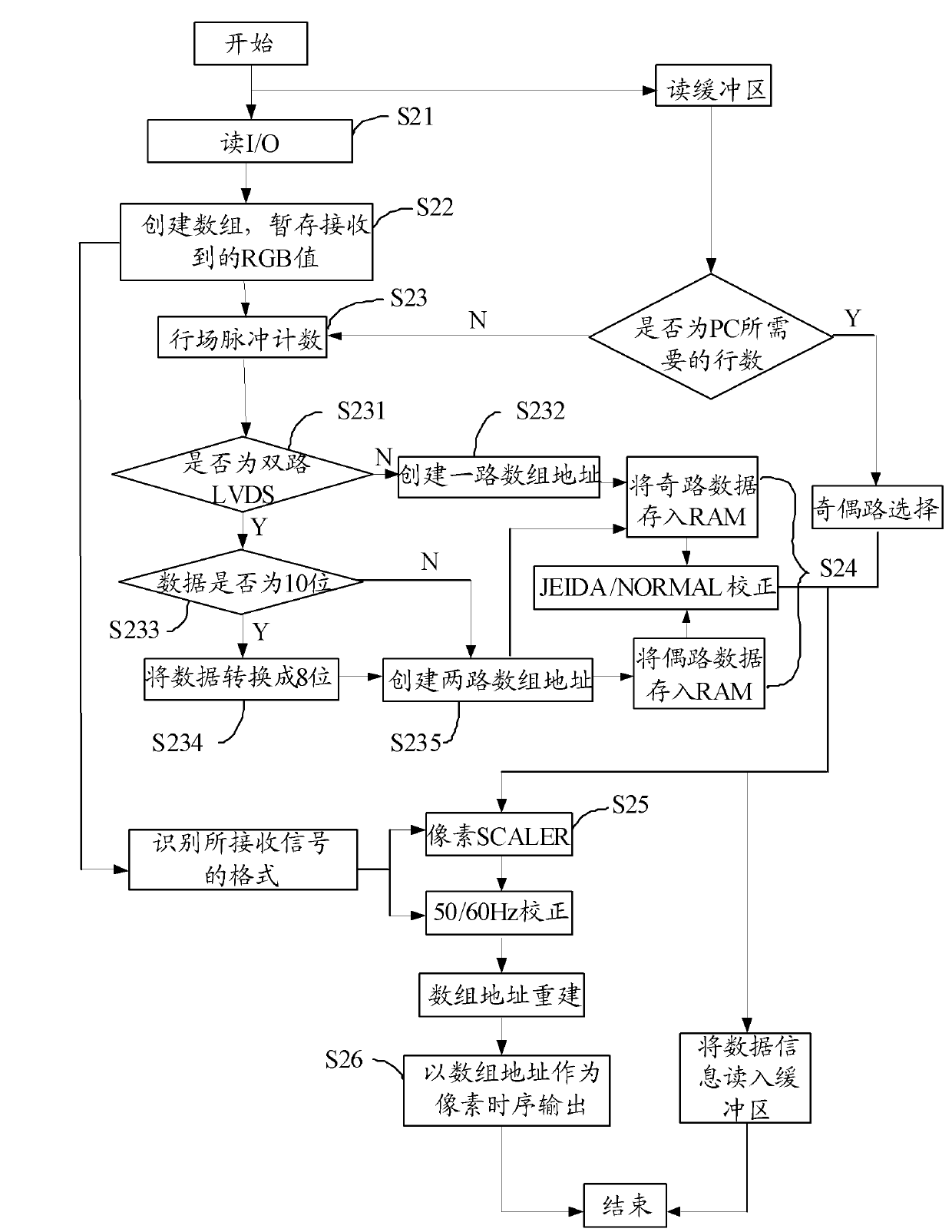

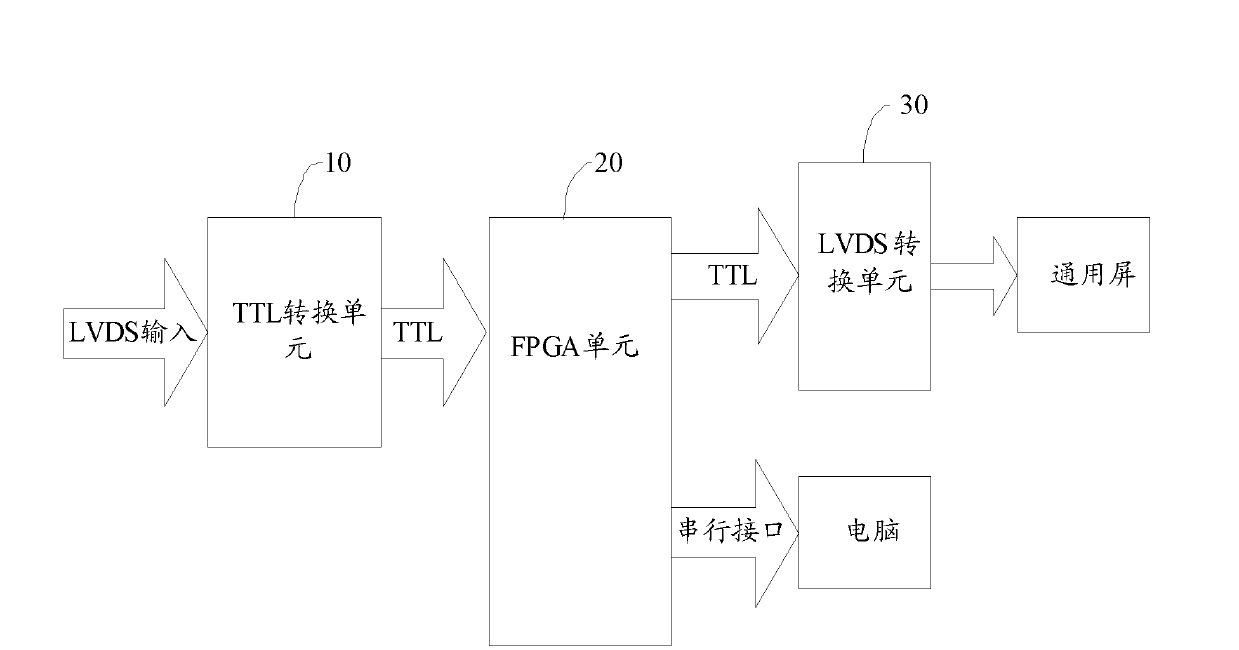

Television testing method, device and system

ActiveCN102170580ASave the screenRealize fully automatic testingTelevision systemsTest efficiencyTransistor–transistor logic

The invention provides a television testing method, device and system. The method comprises the following steps: receiving an LVDS (low-voltage differential signal) output by a mainboard to be tested, and converting the LVDS into TTL (Transistor-transistor logic) level to be output; receiving the TTL level, programming according to the information contained in the TTL level, and outputting test data of a general screen; and receiving the test data of the general screen, and converting the test data of the general screen into an LVDS format to be output to the general screen to be used. The invention also provides the television testing device and the television testing system. The television testing method and the television testing device or the television testing system provided by the invention, can reduce the testing cost and improve the testing efficiency.

Owner:SHENZHEN TCL NEW-TECH CO LTD

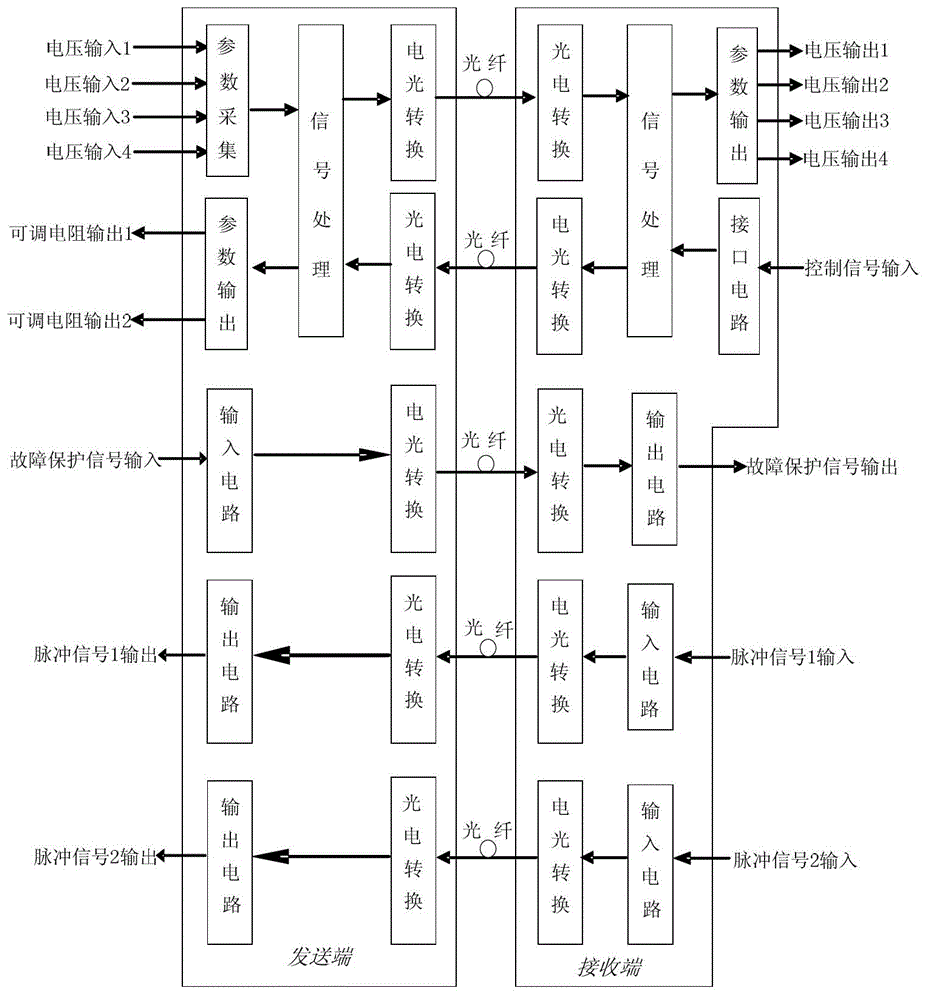

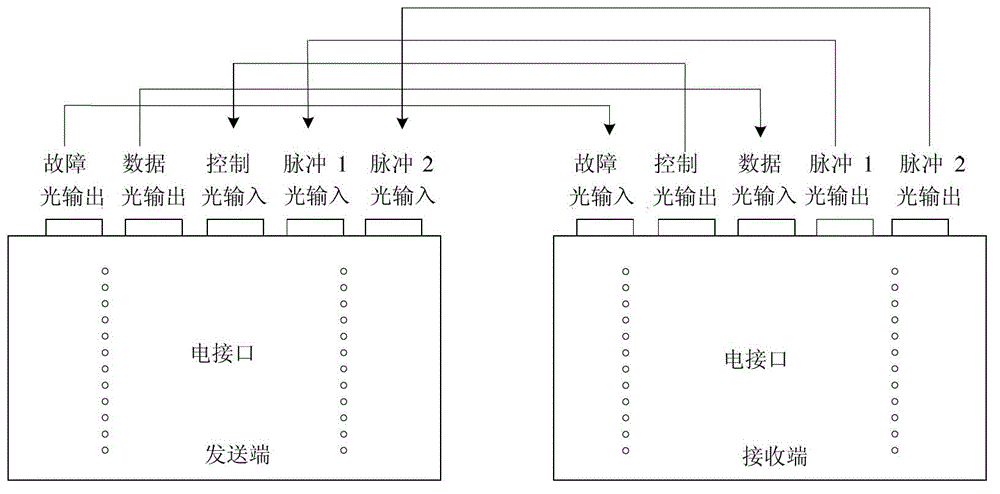

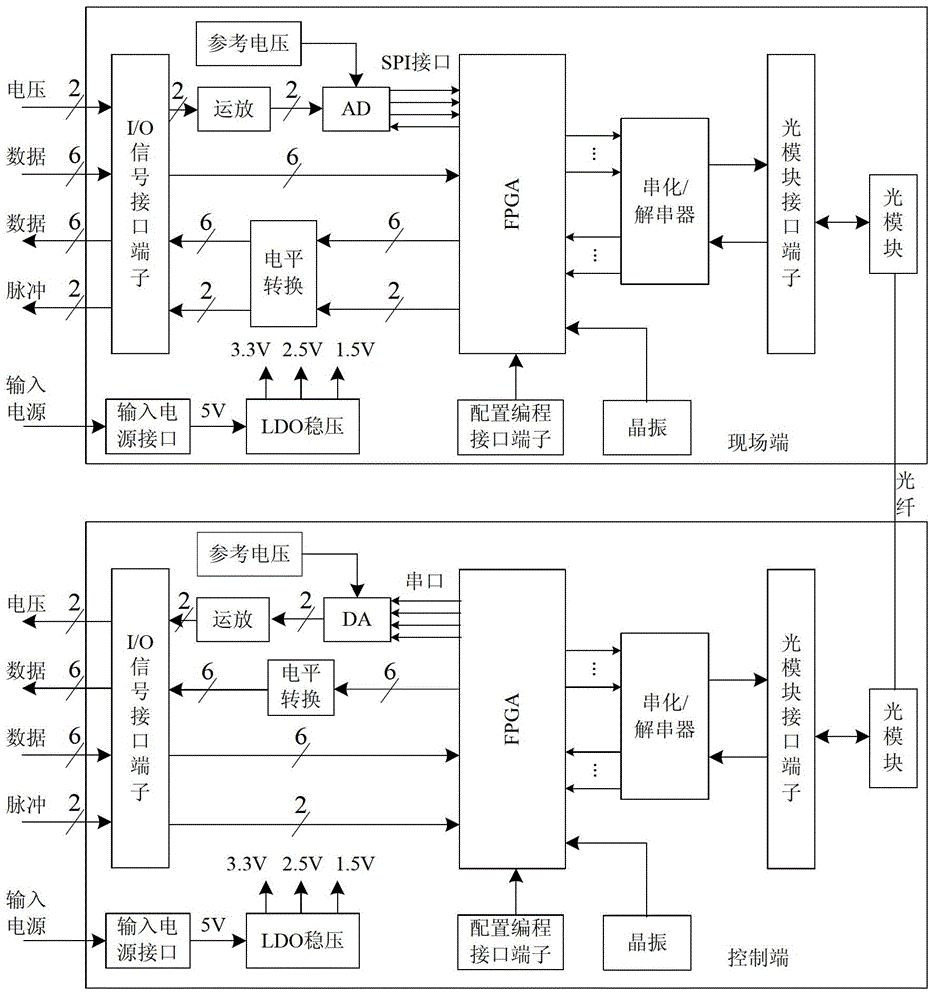

Miniaturized multi-path two-way signal optical fiber transmission component

ActiveCN102882604AReduce volumeSuitable for data transmission applicationsFibre transmissionTransistor–transistor logicAnti jamming

The invention discloses a miniaturized multi-path two-way signal optical fiber transmission component. The miniaturized multi-path two-way signal optical fiber transmission component comprises a field end and a control end which have multi-chip stack encapsulation structures; the field end is connected with the control end through a transmission optical fiber; the control end can input a plurality of voltage signals and a plurality of data signals, convert a plurality of voltage signals and a plurality of data signals into a positive emitter coupled logic (PECL) signal and transmit the PECL signal to the control end through an optical module and a transmission optical cable; the control end reduces the received PECL signal into a plurality of voltage signals and a plurality of data signals and outputs a plurality of voltage signals and a plurality of data signals; the control end also can input a plurality of transistor-transistor logic (TTL) pulse signals and a plurality of data signals, convert a plurality of TTL pulse signals and a plurality of data signals into the PECL signal, and transmit the PECL signal to the field end through the optical module and the transmission optical cable; the field end reduces the received PECL signal into a plurality of data signals and a plurality of TTL pulse signals and outputs a plurality of data signals and a plurality of TTL pulse signals, so that a plurality of two-way signals are transmitted by an optical fiber, and the anti-jamming capacity is high; and therefore, the miniaturized multi-path two-way signal optical fiber transmission component is particularly suitable for the data transmission of a modern airborne and ship-borne radar system.

Owner:8TH RES INST OF CETC

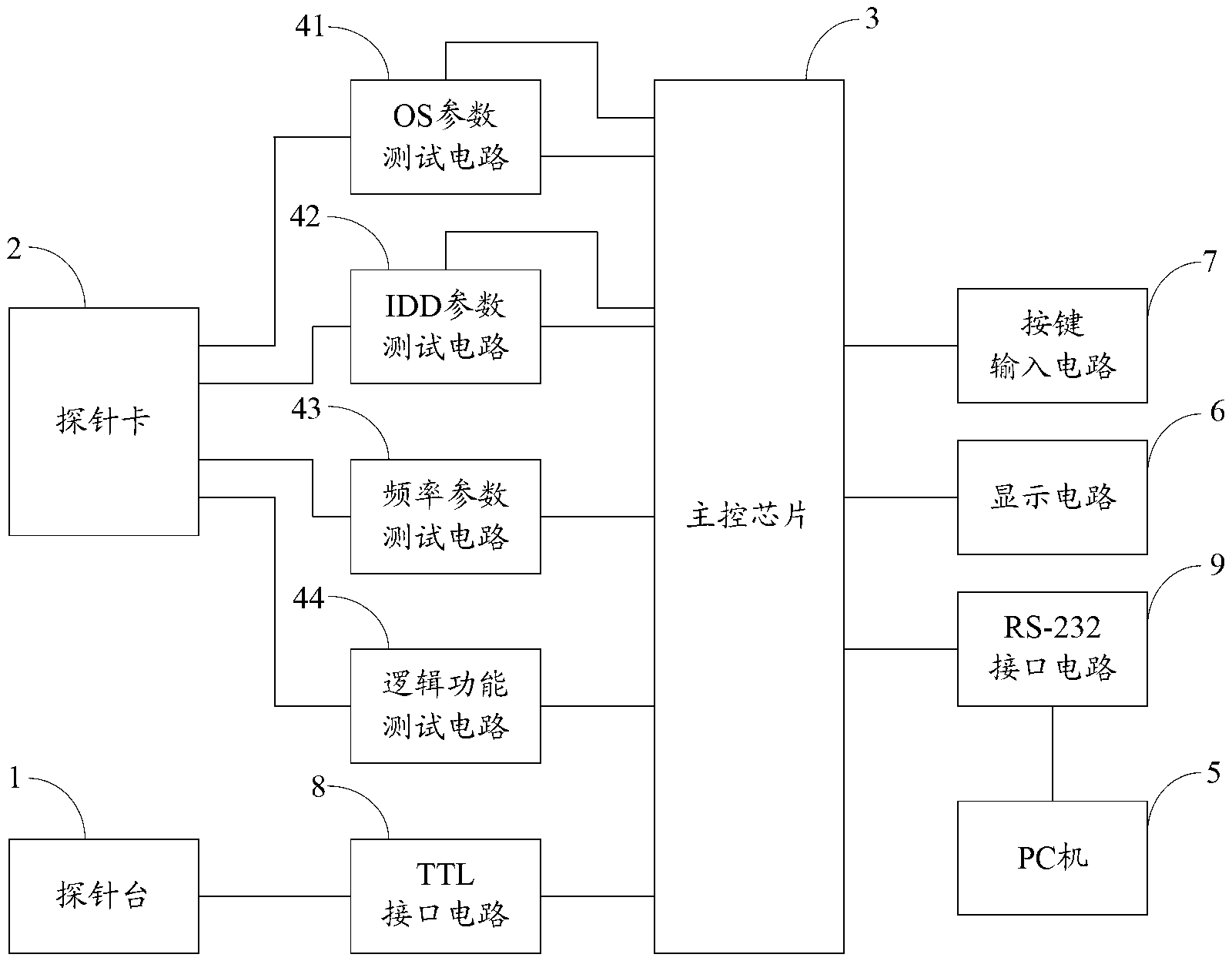

Chip detector for digital electronic watches

ActiveCN103064012AReduce testing costsReduce manufacturing costDigital circuit testingTransistor–transistor logicElectricity

The invention relates to the chip detecting field and in particular to a chip detector for digital electronic watches. The chip detector for the digital electronic watches comprises a probe station, a probe card, a main control chip, a parameter testing circuit, an international direct dial (IDD) parameter testing circuit, a frequency parameter testing circuit and a logical function testing circuit. The parameter testing circuit can be used for testing whether a protection diode on a base pin of a wafer chip is sound. The IDD parameter testing circuit is used for testing the power consumption of the wafer chip which works under the conditions of being provided with a power-on and a clock. The frequency parameter testing circuit is used for testing the work frequency of the wafer chip. The logical function testing circuit is used for testing the logical function of the wafer chip. The control signal of the main control chip can be transmitted to a transistor-transistor logic (TTL) interface circuit of the probe station. The chip detector for digital electronic watches is simple in circuit structure and provided with testing functions which are essential for digital electronic watch chips of an operating system (OS) parameter test, an IDD parameter test, a frequency parameter test, logical function test and the like. At the same time of guaranteeing testing requests, the testing cost and the production cost of the digital electronic watch chips can be reduced.

Owner:深圳米飞泰克科技股份有限公司

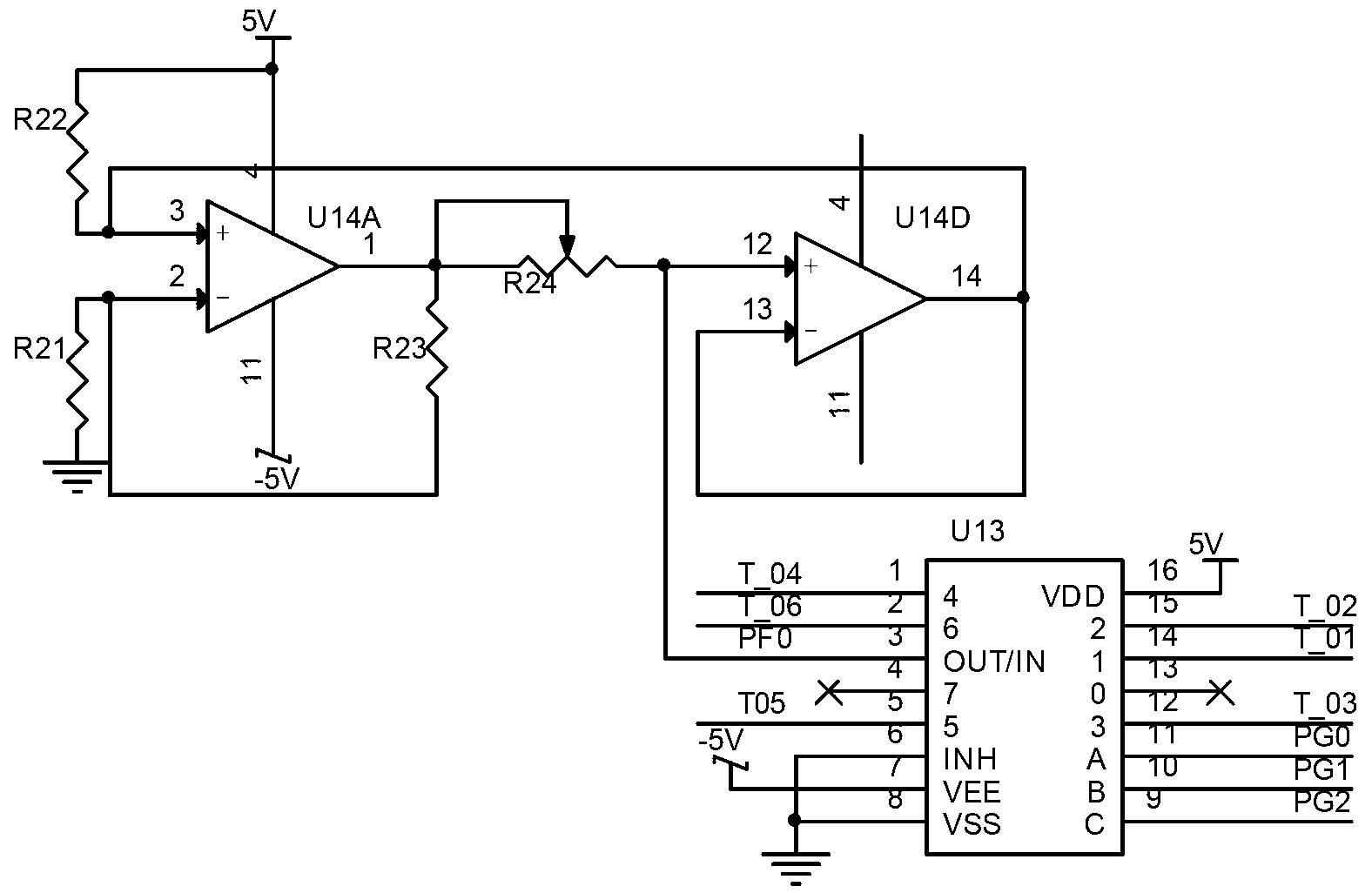

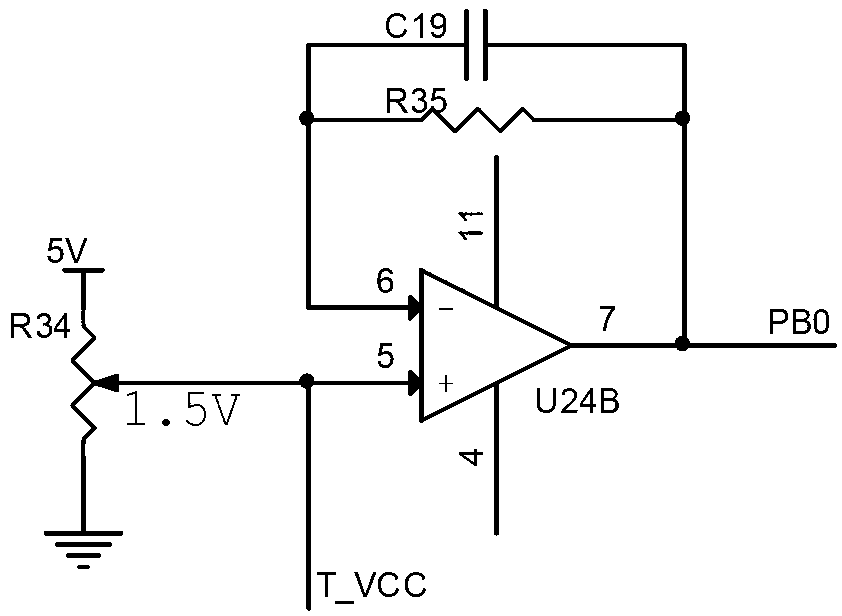

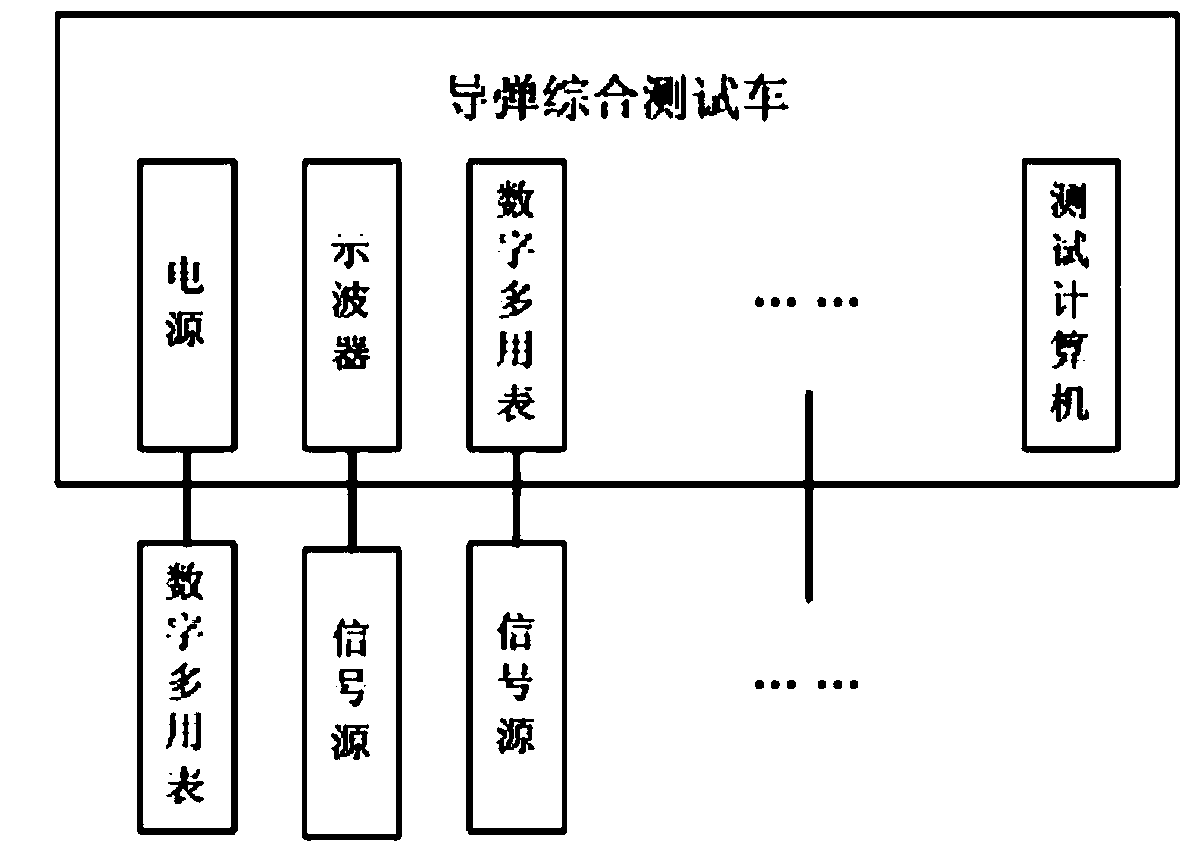

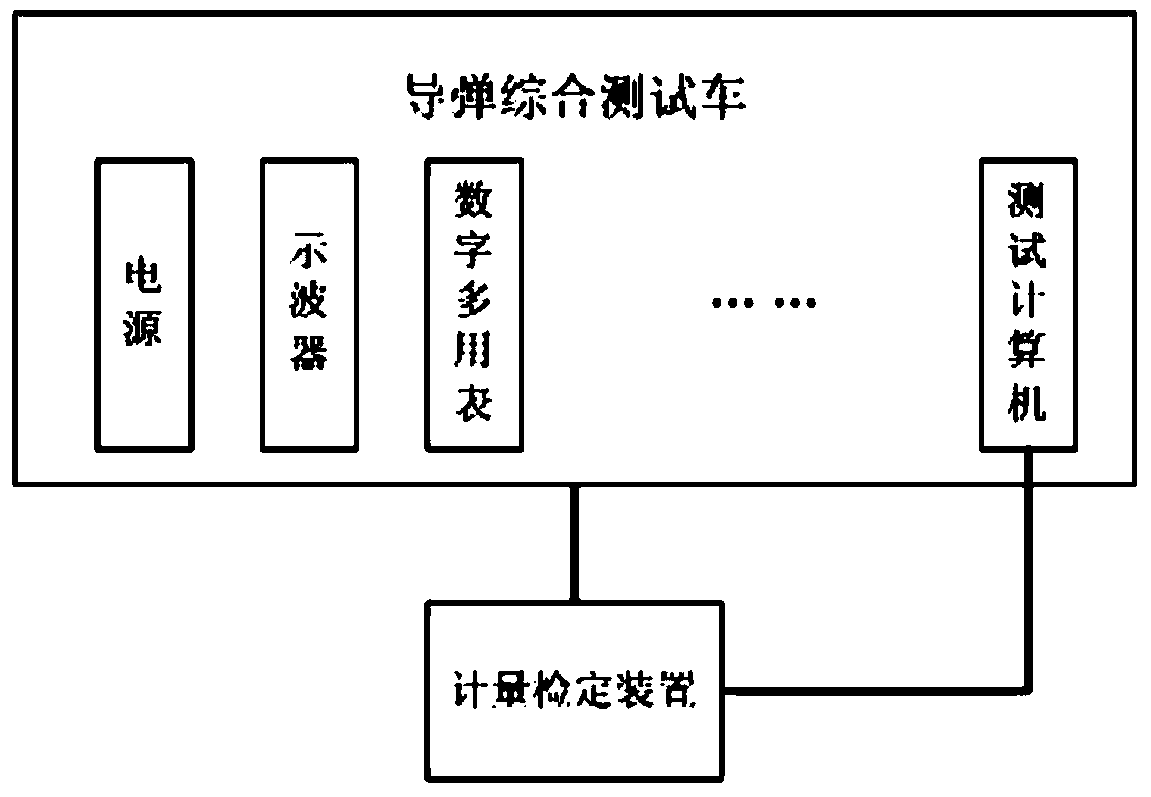

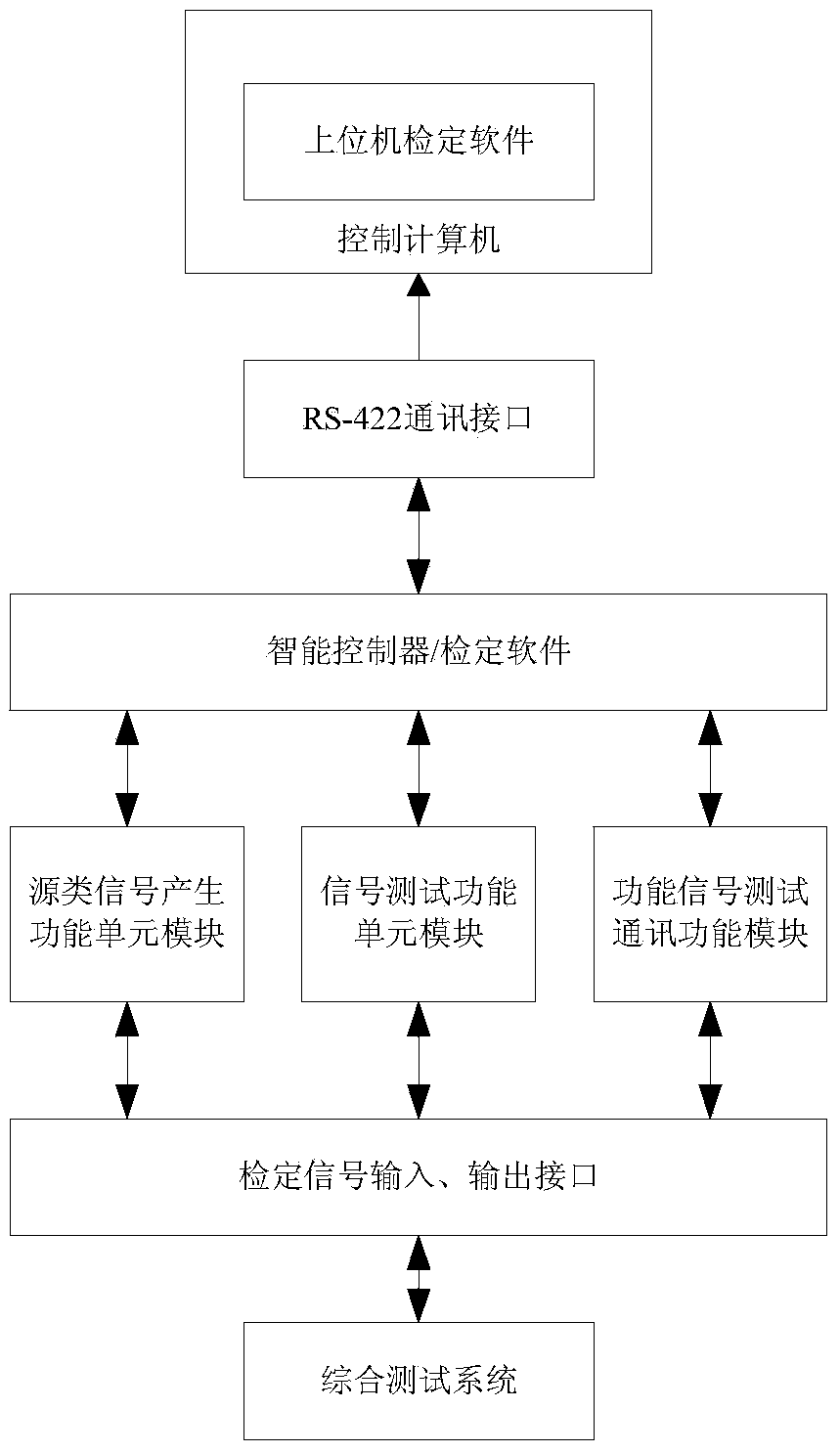

Portable type automatic metering calibrating device and method for guided missile comprehensive test vehicle

ActiveCN103471473AAvoid complexitySimplify complexityAmmunition testingElectrical resistance and conductanceTransistor–transistor logic

The invention relates to a portable type automatic metering calibrating device and method for a guided missile comprehensive test vehicle. The calibrating device comprises a functional signal testing unit, a source signal generation unit and a signal testing function unit, wherein the functional signal testing unit is used for realizing communication between a shot ground and a missile board machine in a testing system and is used for testing a resetting signal and a resetting responding signal of the missile board machine; the source signal generation unit is used for generating a test signal source needed by a test; the signal testing function unit is used for acquiring and testing time intervals of direct-current voltage, alternating-current voltage, standard resistance, a pulse signal and a TTL (Transistor-Transistor Logic) level signal which are generated by the source signal generation unit. According to the calibrating device, the complexity of metering and calibration, previously carried out by manual operation, is solved and the universality and the expandability of the metering calibration of the guided missile comprehensive test vehicle are guaranteed.

Owner:BEIJING INST OF ELECTRONICS SYST ENG

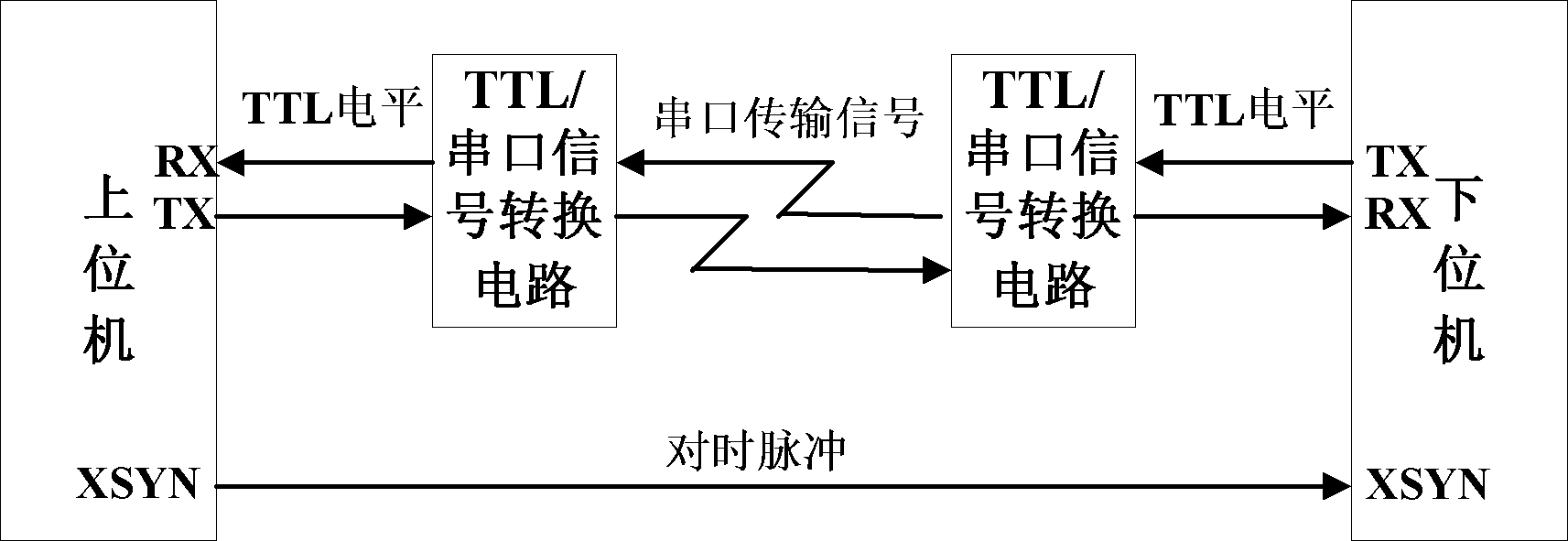

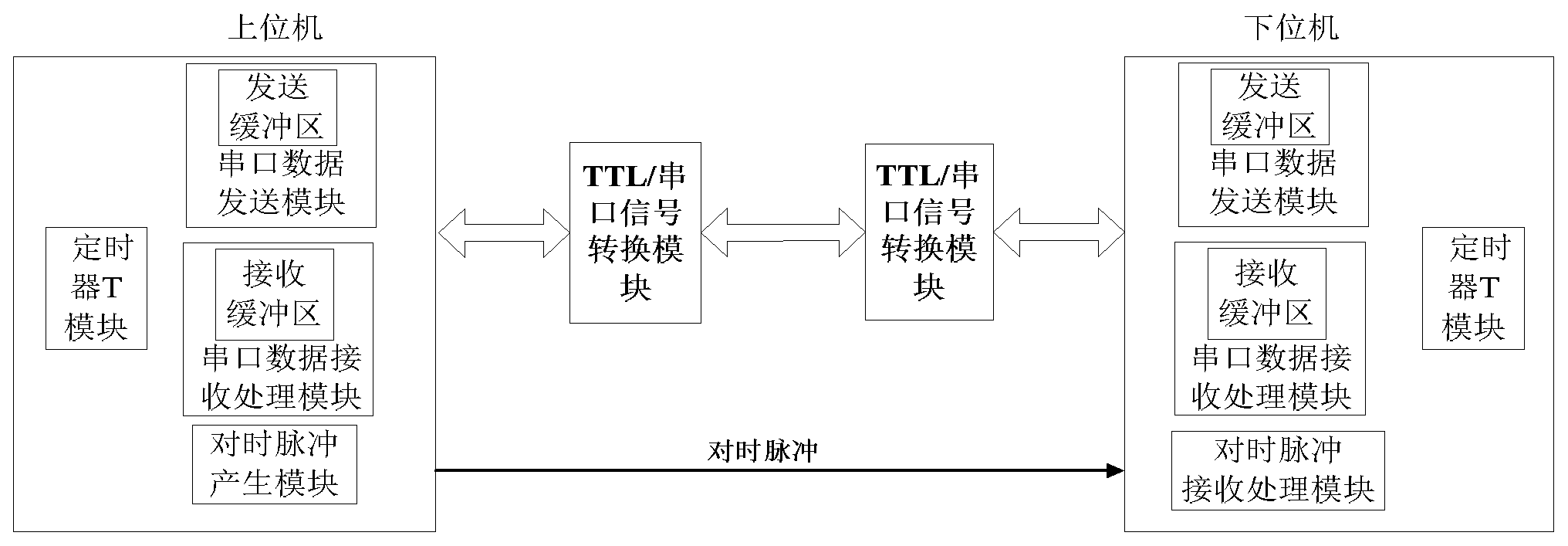

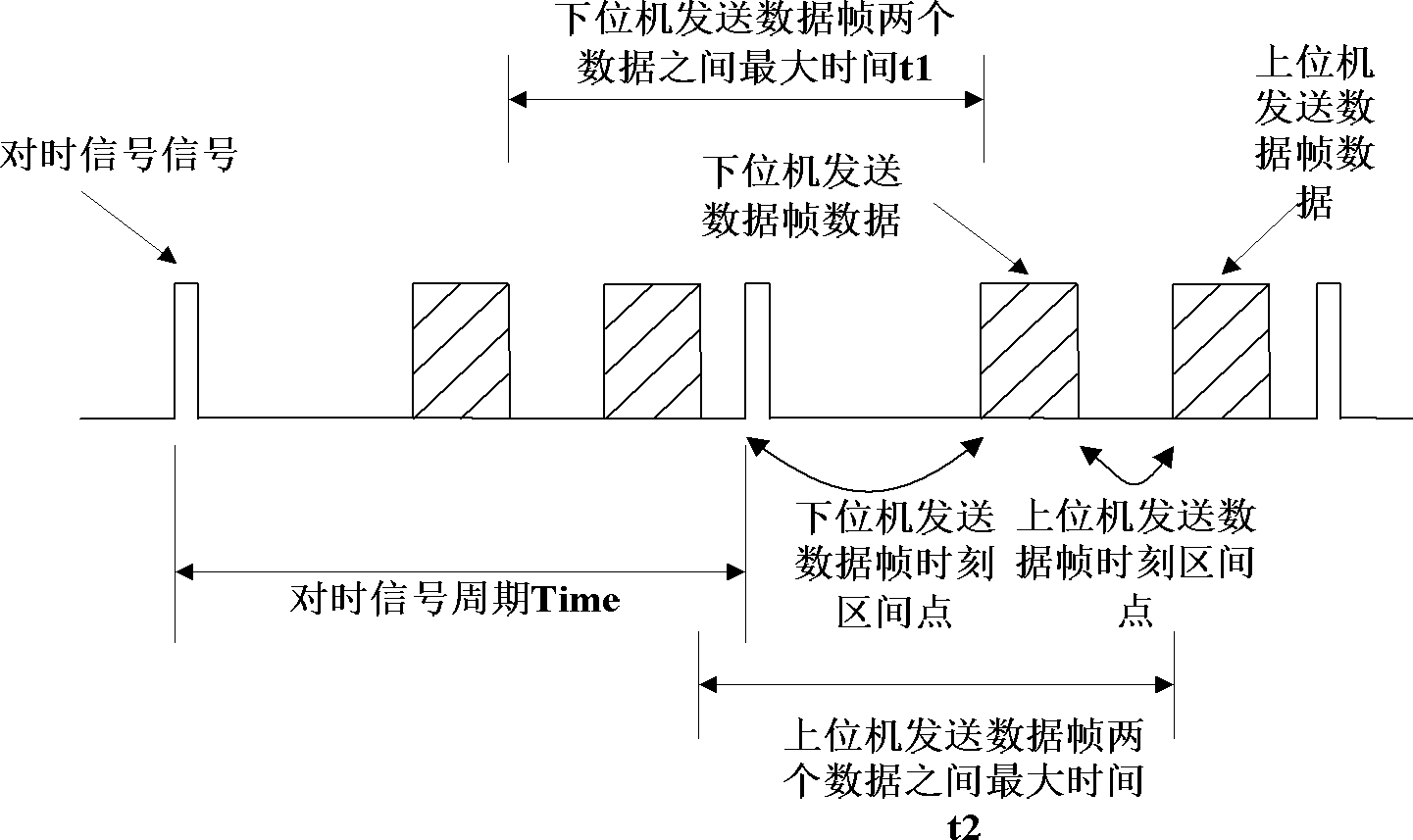

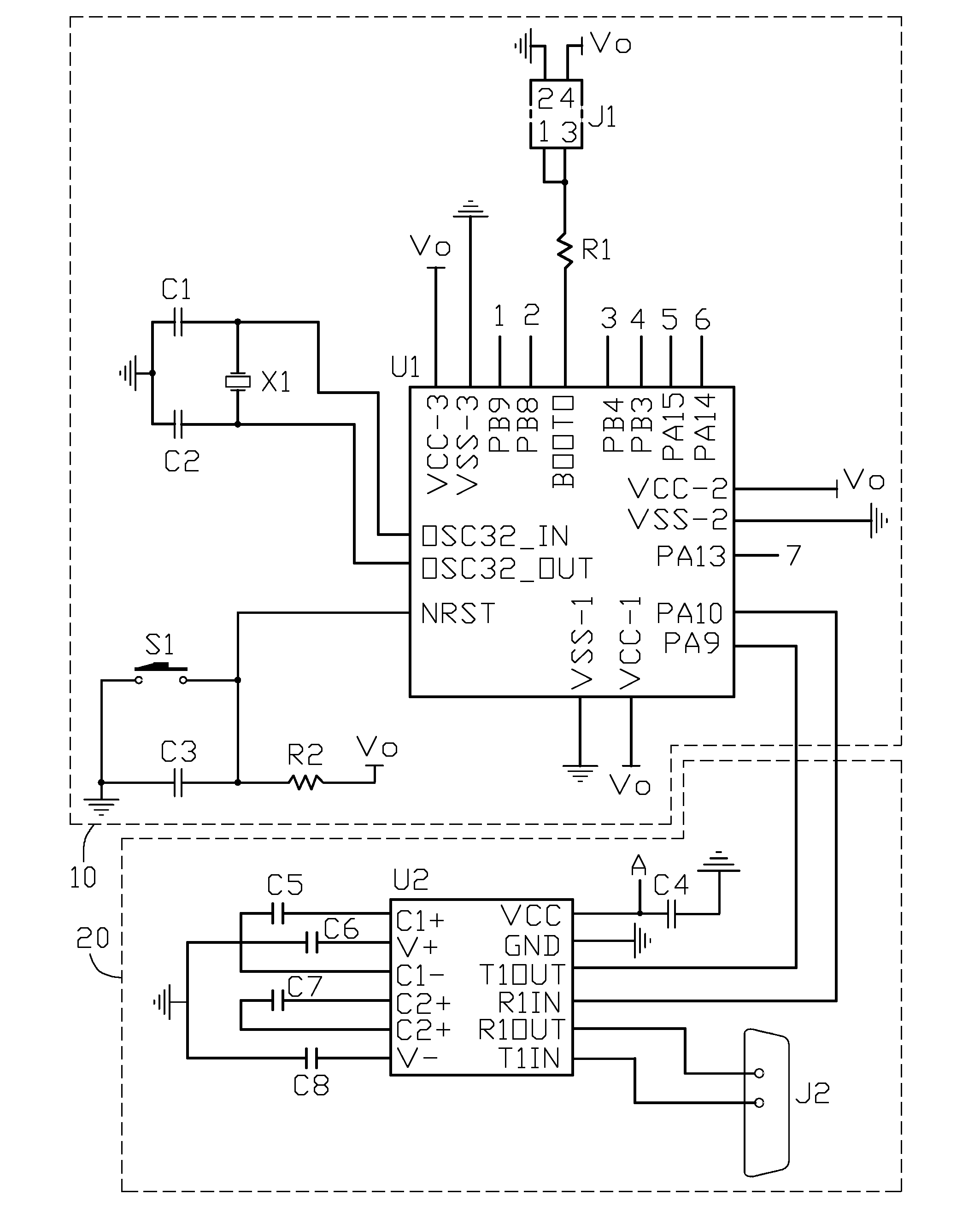

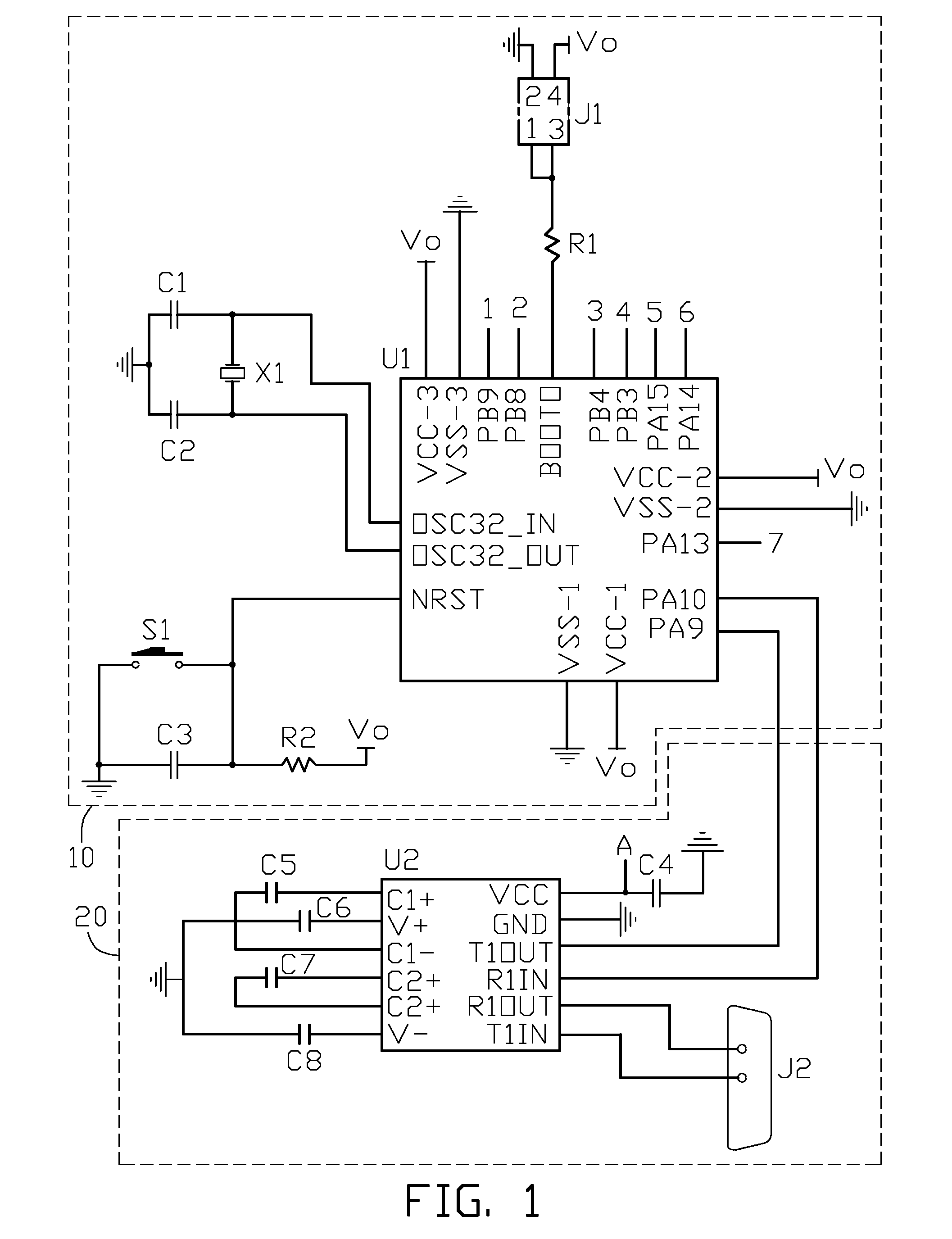

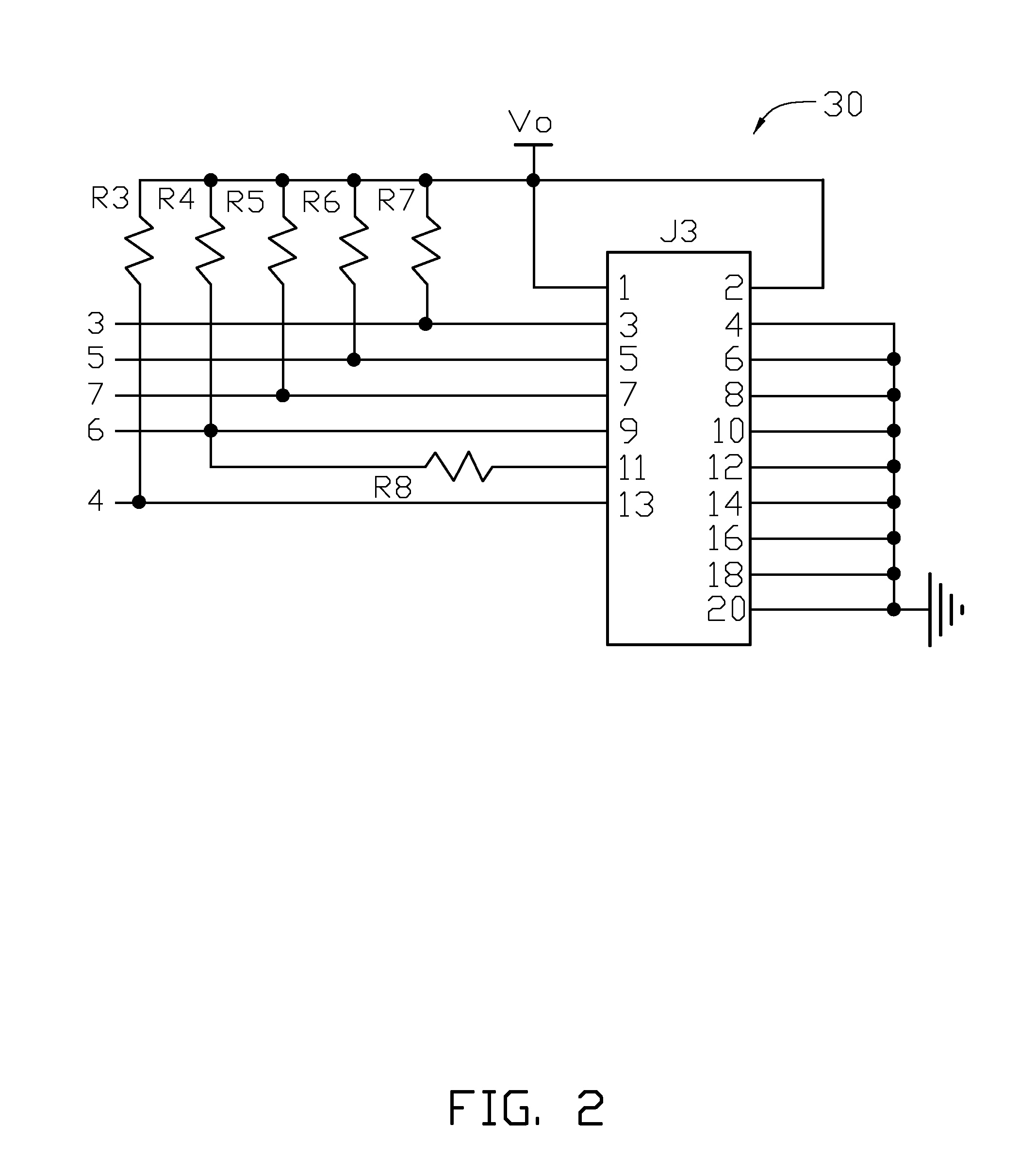

Serial asynchronous communication data transmission method

InactiveCN104239254AIntuitive and simple structure modeShort design processElectric digital data processingTransistor–transistor logicAsynchronous serial communication

The invention discloses a serial asynchronous communication data transmission method, and aims to provide a method which is intuitive and simple in structural model, short in design flow, distinct in procedure level and high in reliability, and can ensure the instantaneity of communication transmission data on communication time series and data frame formats. The serial asynchronous communication data transmission method is implemented through the following technical scheme and comprises the steps of adopting an upper computer micro-control chip as an upper computer for asynchronous serial communication, adopting a lower computer micro-control chip as a lower computer for asynchronous serial communication, and connecting the upper computer and the lower computer through a TTL (Transistor-Transistor Logic) / serial signal conversion circuit to form a serial asynchronous communication data transmission device; arranging serial asynchronous communication data transmission program software formed by a serial data receiving processing module, a serial data transmission module and a timer T module in the upper computer micro-control chip and the lower computer micro-control chip; transmitting serial data frame information to transmit buffers of the upper computer and the lower computer in a time-division way; assigning the real data frame to a buffer array Ai through a receive buffer; storing an array word string consistent to a communication frame protocol into a buffer array Bi.

Owner:SOUTH WEST INST OF TECHN PHYSICS

Test equipment and test method of test equipment

InactiveCN102944852AImprove reliabilityImprove accuracyLamps testingTest efficiencyTransistor–transistor logic

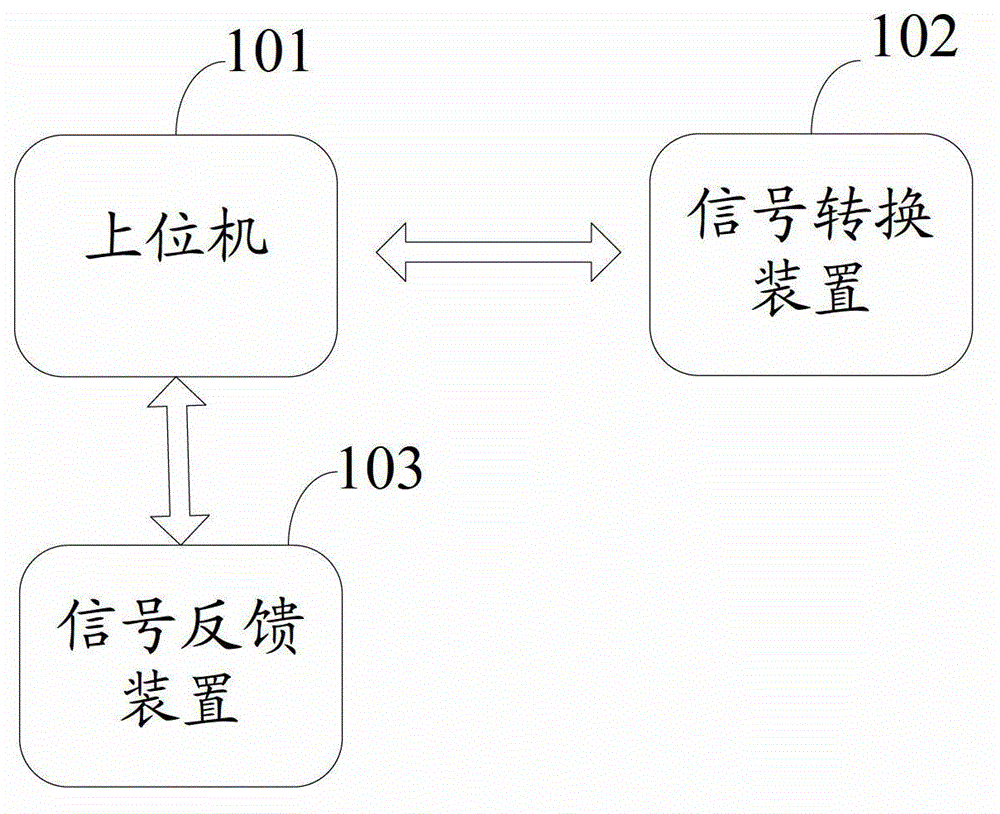

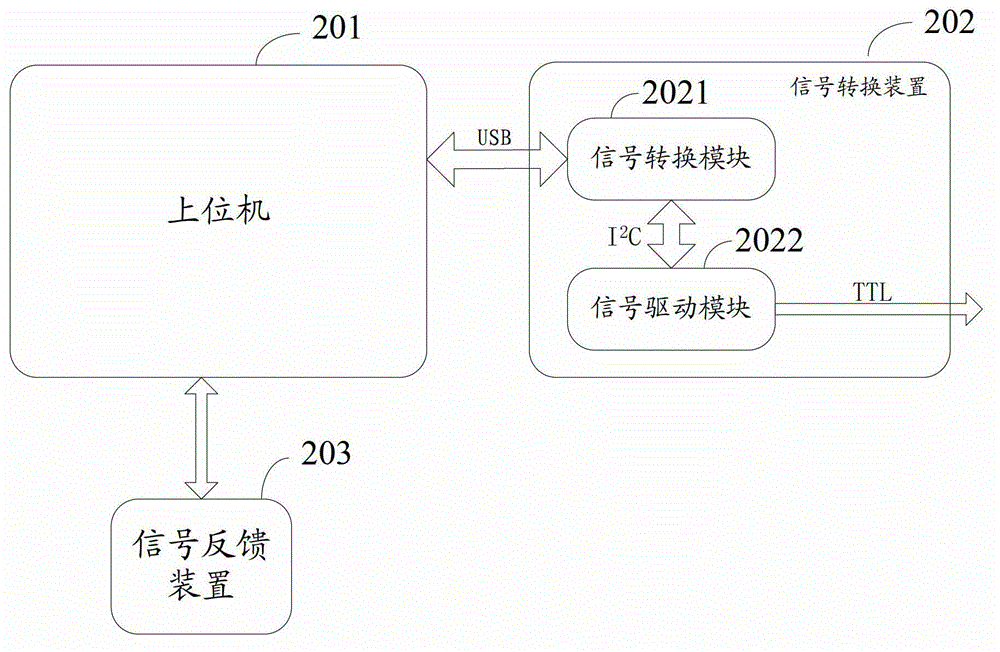

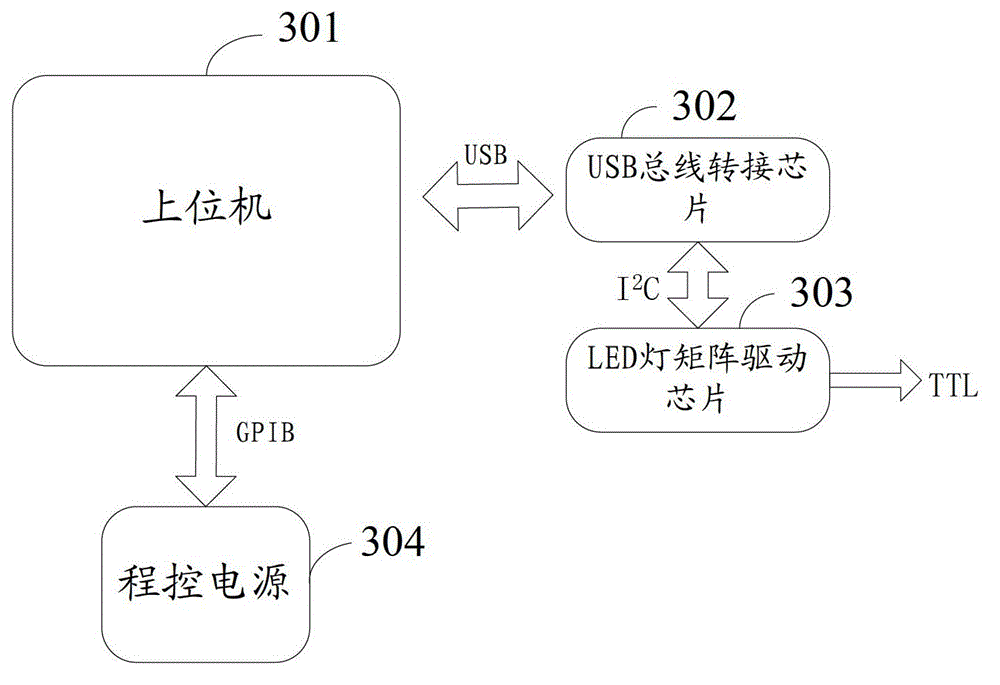

The invention discloses test equipment, which is used for testing LED (light emitting diode) lamp matrixes. The test equipment comprises a upper computer, a signal conversion device and a signal feedback device, wherein the upper computer is used for generating system control signals, the signal conversion device is connected with the upper computer and is used for receiving the signal control signals from the upper computer and outputting multipath TTL (transistor-transistor logic) level signals according to the system control signals, the multipath TTL level signals are used for testing the LED lamp matrixes, the signal feedback device is connected with the upper computer, and is used for measuring the current value in the LED lamp matrixes and feeding back measuring results to the upper computer, and the upper computer judges whether the LED lamp matrix test is passed or not according the measuring results. The invention also discloses a test method of the test equipment. Through adopting the mode, the test equipment and the test method of the test equipment have the advantages that the test reliability and the accuracy can be improved, and the test efficiency is improved.

Owner:HUIZHOU TCL MOBILE COMM CO LTD

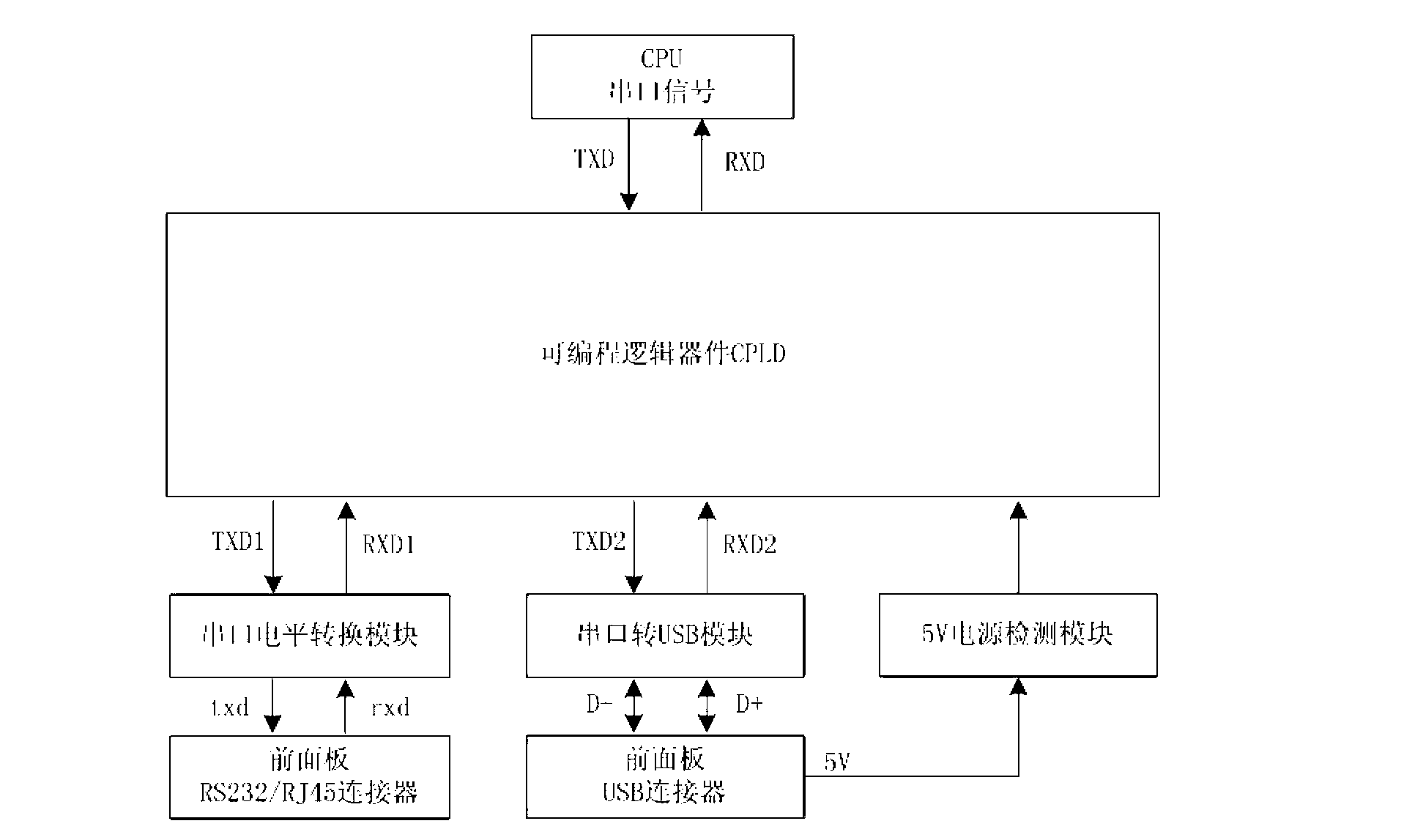

Device for switching universal serial bus (USB) interface and standard serial port

InactiveCN103077151AFlexible switchingFunction increaseElectric digital data processingTransistor–transistor logicProgrammable logic device

The invention discloses a device for switching a universal serial bus (USB) interface and a standard serial port, which belongs to an interface switching device, and the device comprises a main control panel, a programmable logic device, a serial port transform USB module, a front panel USB connector and a power supply detection module; the serial port transform USB module is respectively connected with the front panel USB connector and the programmable logic device; the power supply detection module is respectively connected with the programmable logic device and the front panel USB connector; the programmable logic device is connected with a central processing unit (CPU) module of the main control panel; the device is connected with an external USB interface through the front panel USB connector; the conversion of a transistor-transistor logic (TTL) signal and a USB signal can be realized through the serial port transform USB module; and the programmable logic device detects whether the front panel USB connector is connected with the external USB interface or not through the power supply detection module. The device has the beneficial effects that flexibility for switching the USB interface and the serial port can be realized, the function of a traditional device such as Ethernet passive optical network (EPON) rack equipment can be expanded, and the equipment can be convenient to operate and maintain.

Owner:PHICOMM (SHANGHAI) CO LTD

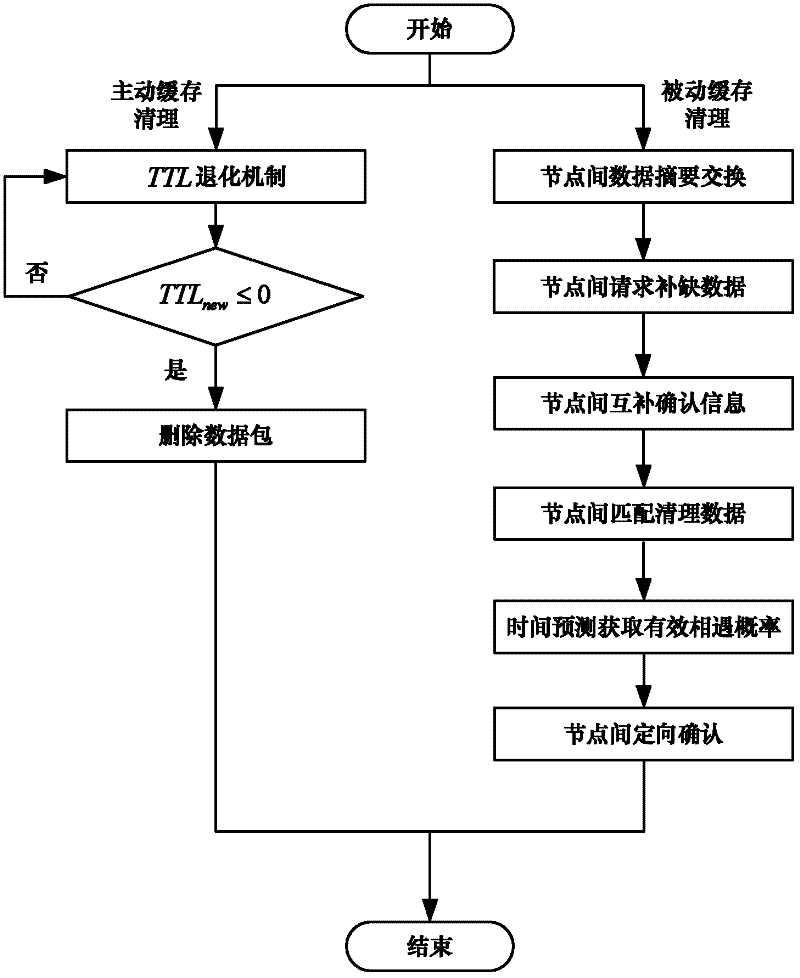

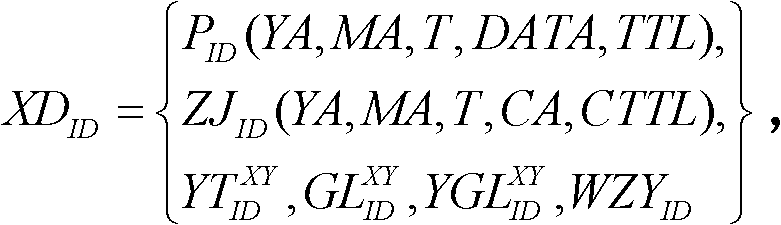

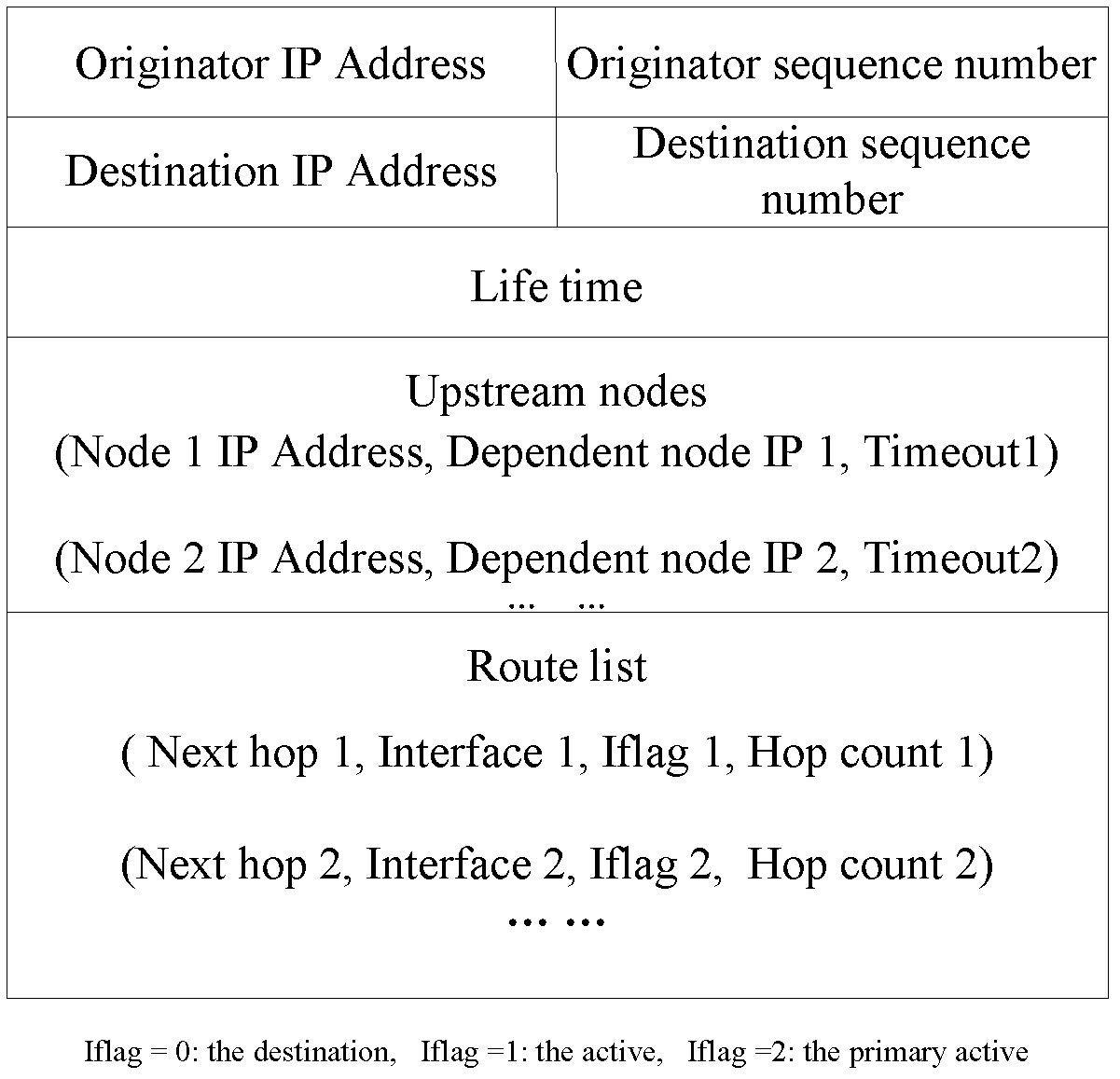

A Delay Tolerant Network Cache Clearing Method Based on Time Prediction and Direction Acknowledgment

InactiveCN102271089AIncrease available cache spaceQuick clean upData switching networksQuality of serviceTransistor–transistor logic

The invention discloses a cache cleaning method based on time prediction and directional acknowledgement for a delay tolerant network. By fusing an active cache cleaning strategy with a passive cache cleaning strategy, the method realizes the efficient cache cleaning of a redundant copy of a data packet in the delay tolerant network. Active cache cleaning cancels an invalid copy by using a TTL (transistor-transistor logic) degradation mechanism. In passive cache cleaning, through leading in a transmission control mechanism based on the time prediction and the directional acknowledgement, the validity of the cache cleaning is improved, the time delay of the cache cleaning is decreased, the consumption of a bandwidth and a storage space caused by the multi-copy transmission of acknowledgement information is reduced, and the quick and efficient cache cleaning is realized. When different delay tolerant network models have different requirements on the service quality of the cache cleaning, the method can obtain better network performance through adjusting a transmission scheme in a directional acknowledging mechanism. The method has high practicality and a wide application range, and promotes the utilization rate of the limited cache in the delay tolerant network.

Owner:BEIHANG UNIV

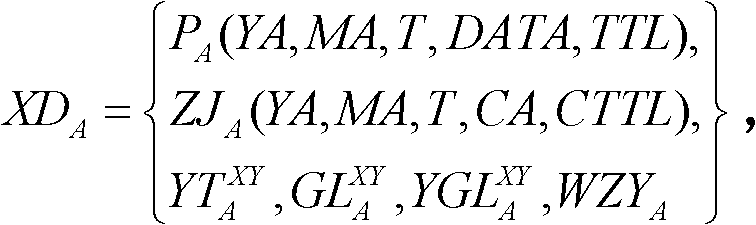

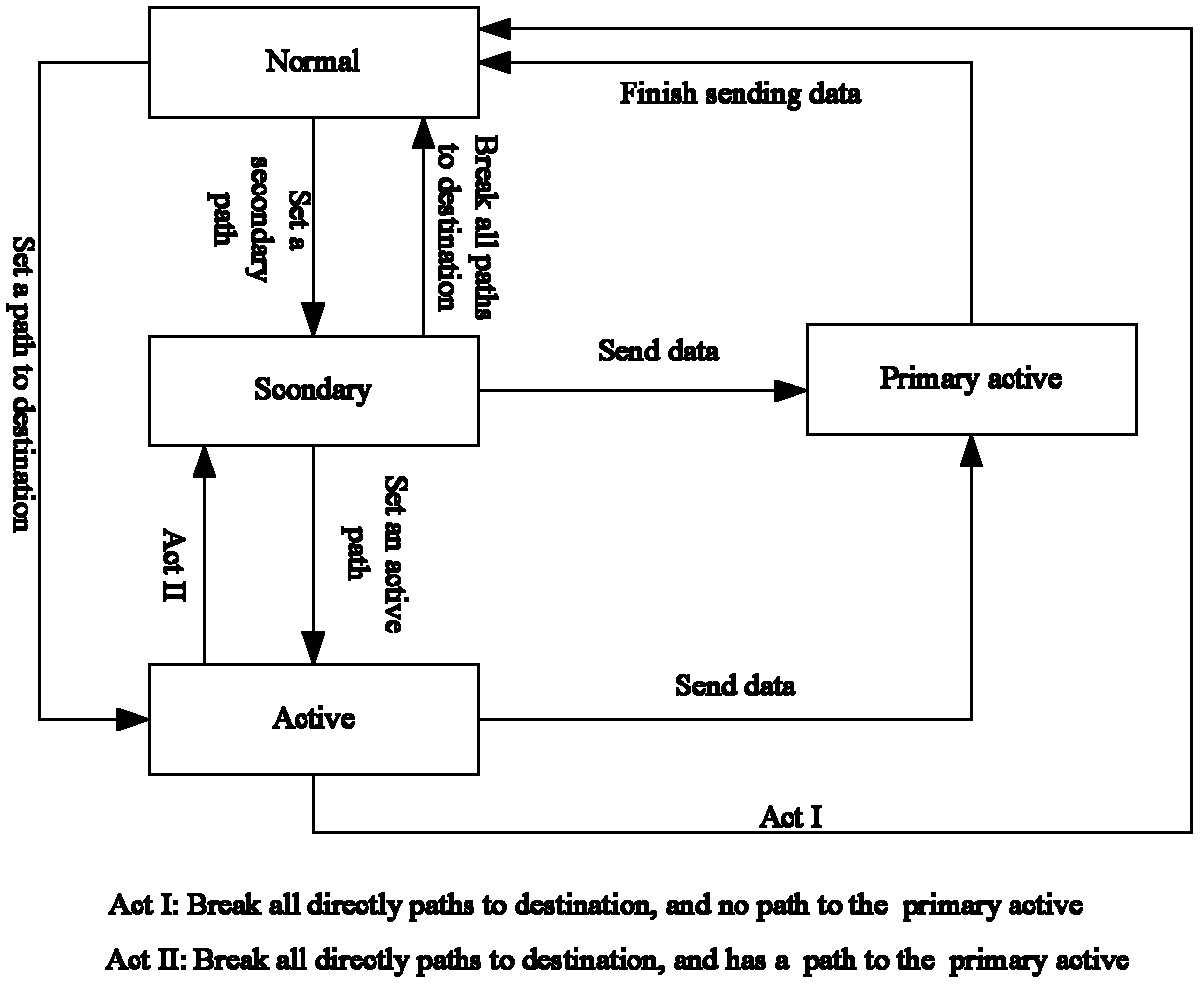

Wireless self-organizing network fusing routing generation method based on node characteristics

InactiveCN102572994AReduce complexityUninterrupted transmissionWireless communicationTransistor–transistor logicSelf-organizing network

A wireless self-organizing network fusing routing generation method based on node characteristics comprises the steps that first a source node sends out a communication request to a target node, and communication is directly started if routing information to the target node exists; otherwise, the source node generates a main routing detecting bag and broadcasts the main routing detecting bag to an adjacent node; and a node receiving the main routing detecting bag responds to a detecting message, the target node replies to the message, multiple path information which is not intersected from the source node to the target node is searched, then a main movable node detects and backups the next node, and therefore, the fusing protection routing from the source node to the target node is generated. Compared with the existing routing generation, the generation method achieves the structure of the back-up of the next node and for transmitting the data on the basis of inheriting advantages of the distributed routing algorithm, can ensure that the data can be transmitted continuously under the condition that a linkage or the nodes lose efficacy, avoids flood of control bags in a whole network by introducing a dynamic transistor-transistor logic (TTL) and clock control mechanism, and has the advantages of being simple and convenient to implement and low in algorithm complexity.

Owner:TSINGHUA UNIV

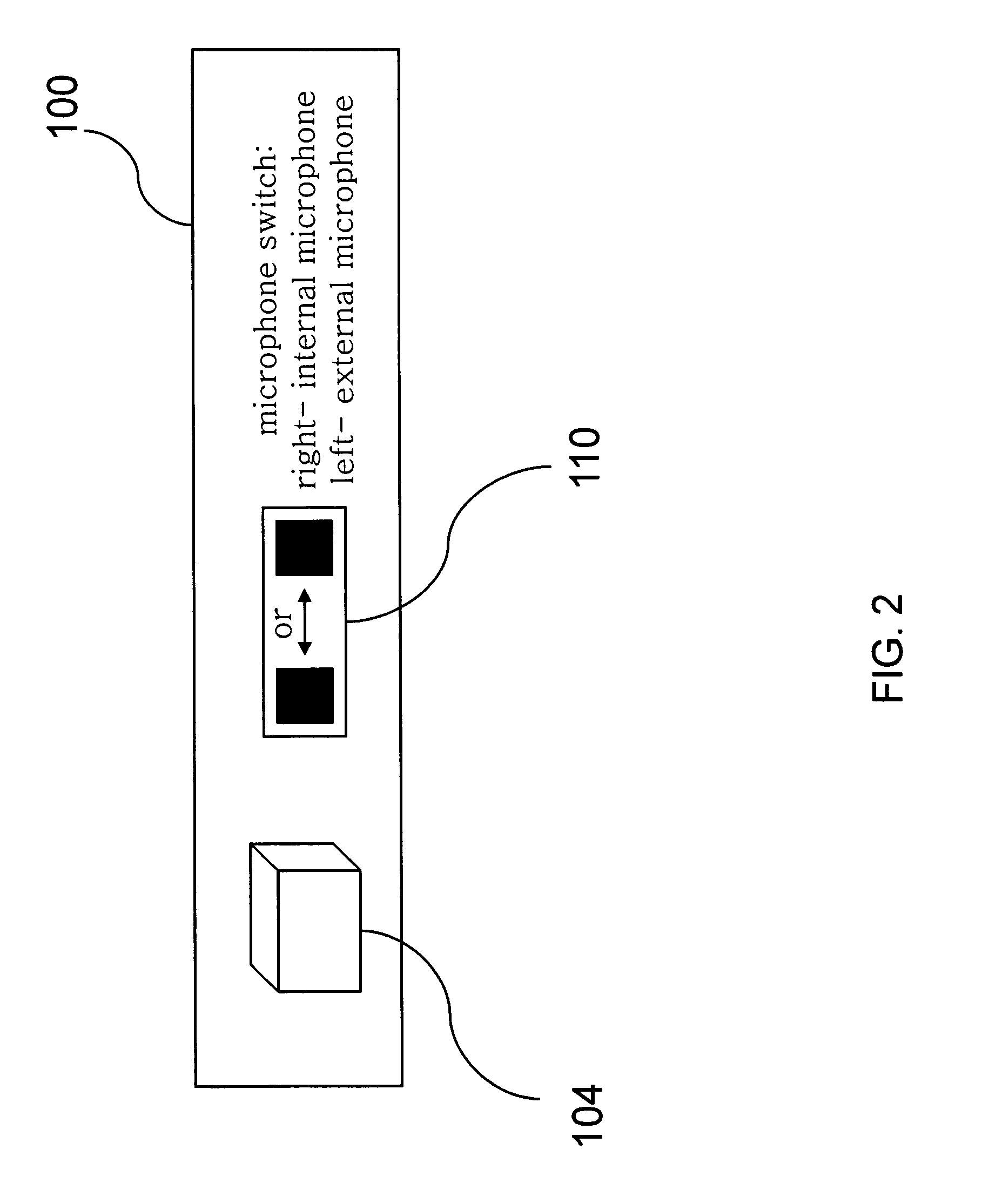

Portable device and associated software to enable voice-controlled navigation of a digital audio player

InactiveUS20080243281A1Easy to carryRecord information storageCarrier indicating arrangementsMicrocontrollerOn board

Methods are disclosed to describe a portable device that enables the user to navigate the menus of a digital audio player using a set of simple voice commands. The system is comprised of a microcontroller, serial flash memory device, on-board microphone, volume controller, a connector for headphones or external audio amplifier and a connector for an external microphone. Power is supplied by the digital audio device via a connector. The device is loaded with necessary software to interface with the digital audio player using Transistor-Transistor-Logic-level serial commands. The loaded software allows for a search for playlists, artists, albums, genres, or songs, which is accomplished via an extremely low memory ASCII character comparison with sublinear performance functionality.

Owner:KADABA NEENA SUJATA +1

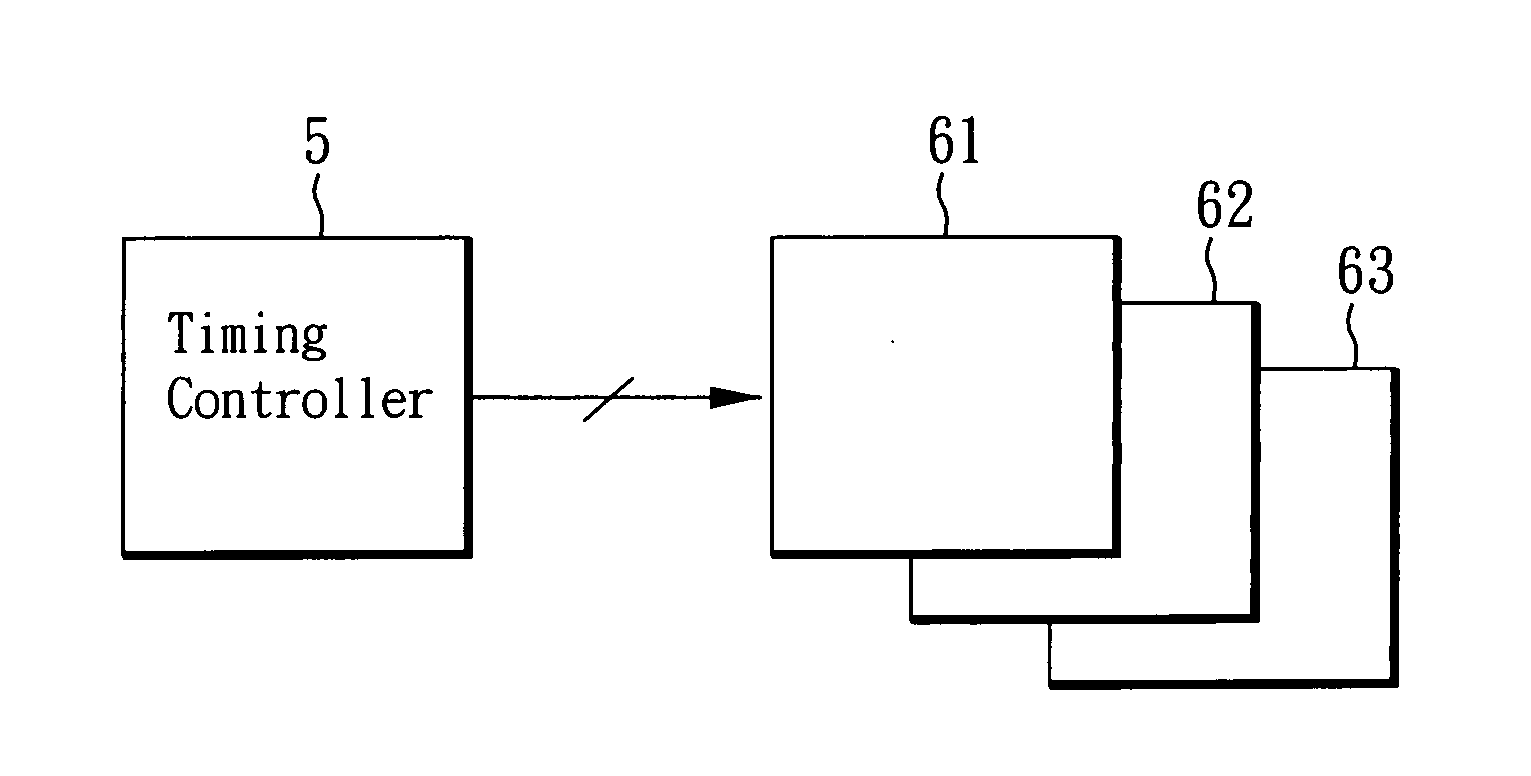

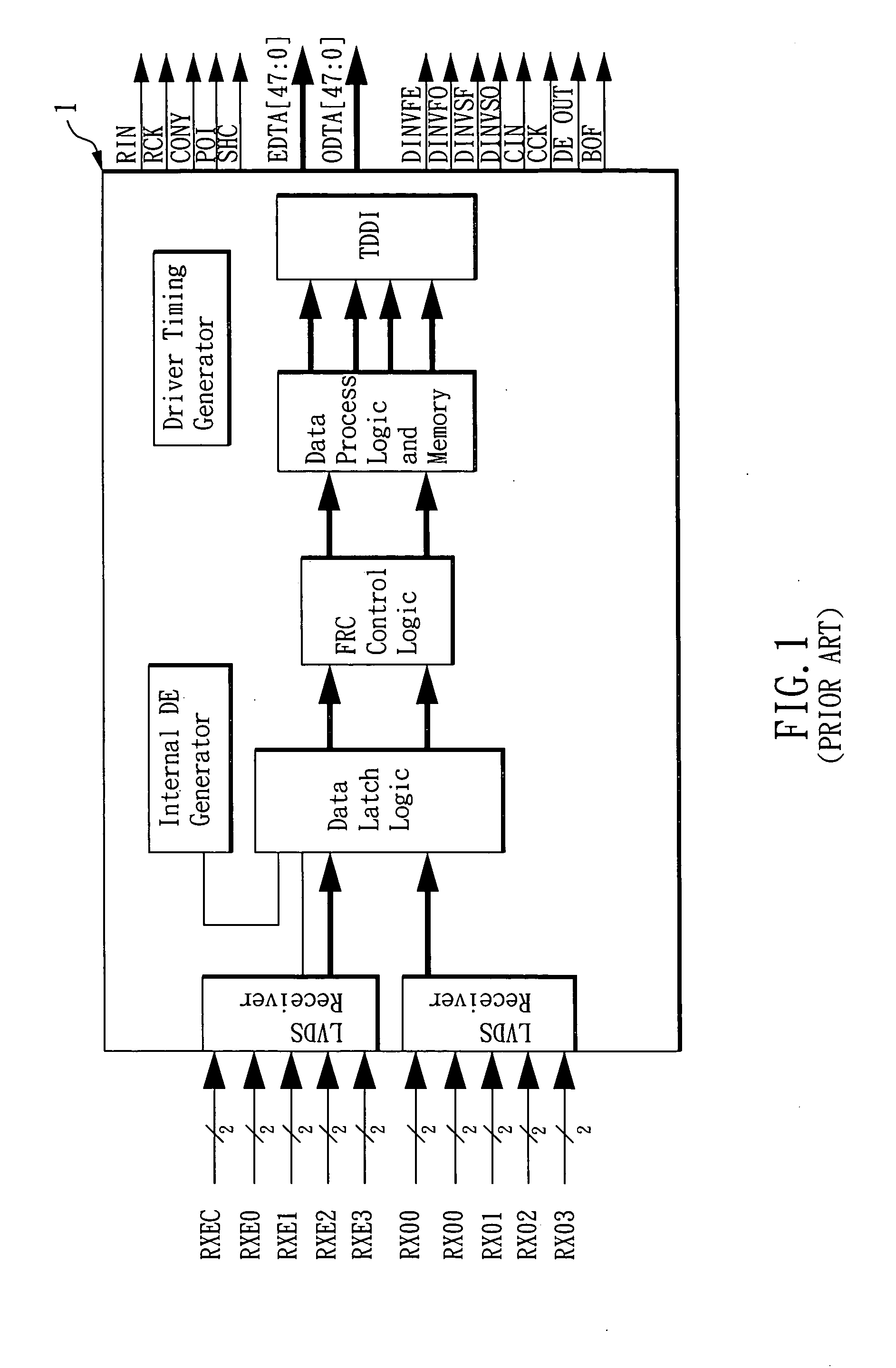

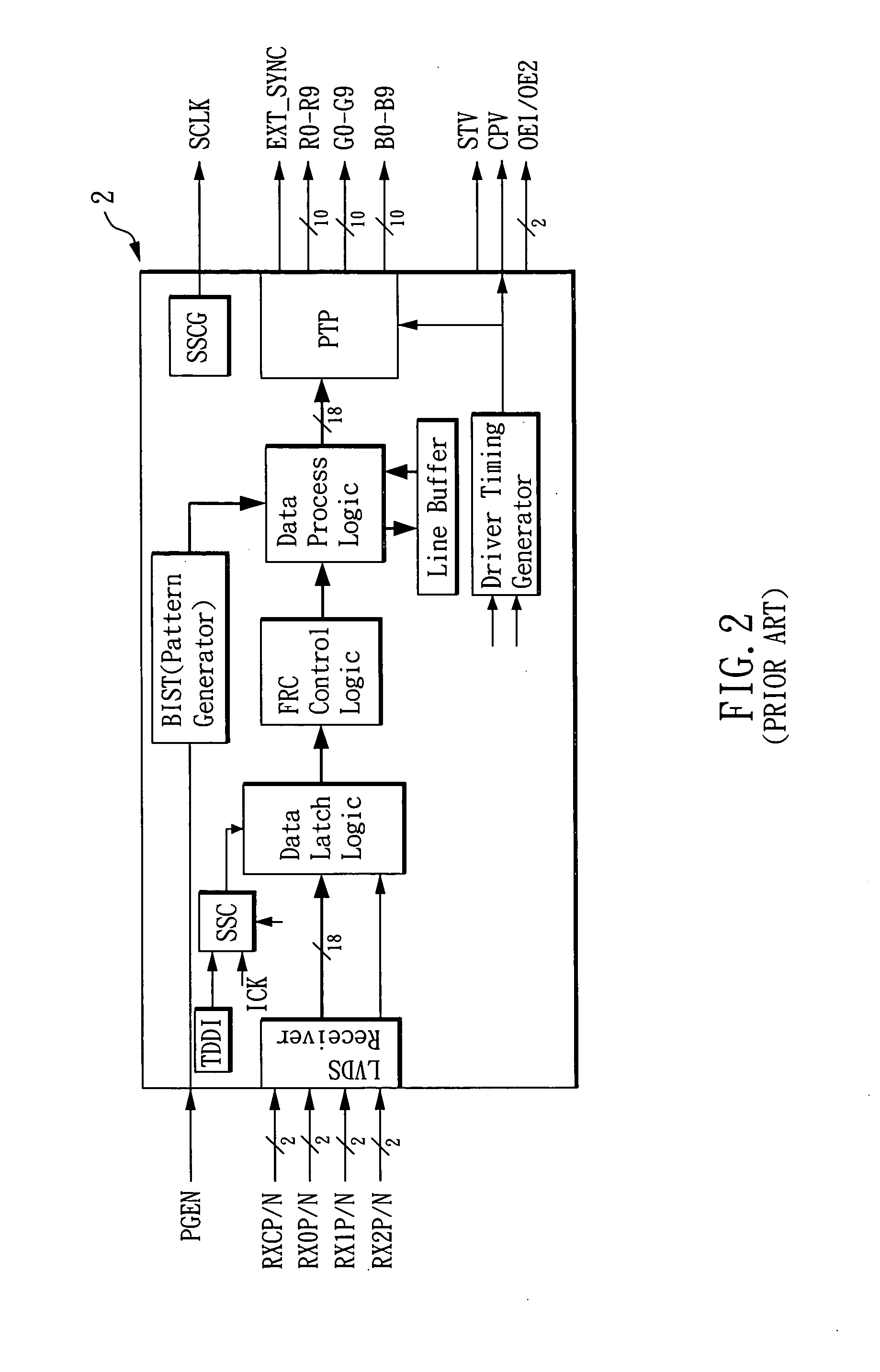

Method for improving the EMI performance of an LCD device

ActiveUS20080252623A1Improve EMI performanceImprove electric power consumptionCathode-ray tube indicatorsInput/output processes for data processingTransistor–transistor logicImaging data

A method for improving the EMI performance of an LCD device is disclosed, adapting for a point-to-point transistor transistor logic interface of the LCD device. The disclosed method comprises the following steps: receiving a plurality of image data based on a fifth CLK signal; providing a first CLK signal and a second CLK signal to a plurality of source drivers by a timing controller, wherein the frequencies of the first CLK signal and the second CLK signal are smaller than the frequency of the fifth CLK signal, the phase of the first CLK signal is different from the phase of the second CLK signal; and the timing controller transmitting a plurality of first image data to the plurality of source drivers based on the first CLK signal, and the timing controller transmitting a plurality of second image data to the plurality of source drivers based on the second CLK signal.

Owner:AU OPTRONICS CORP

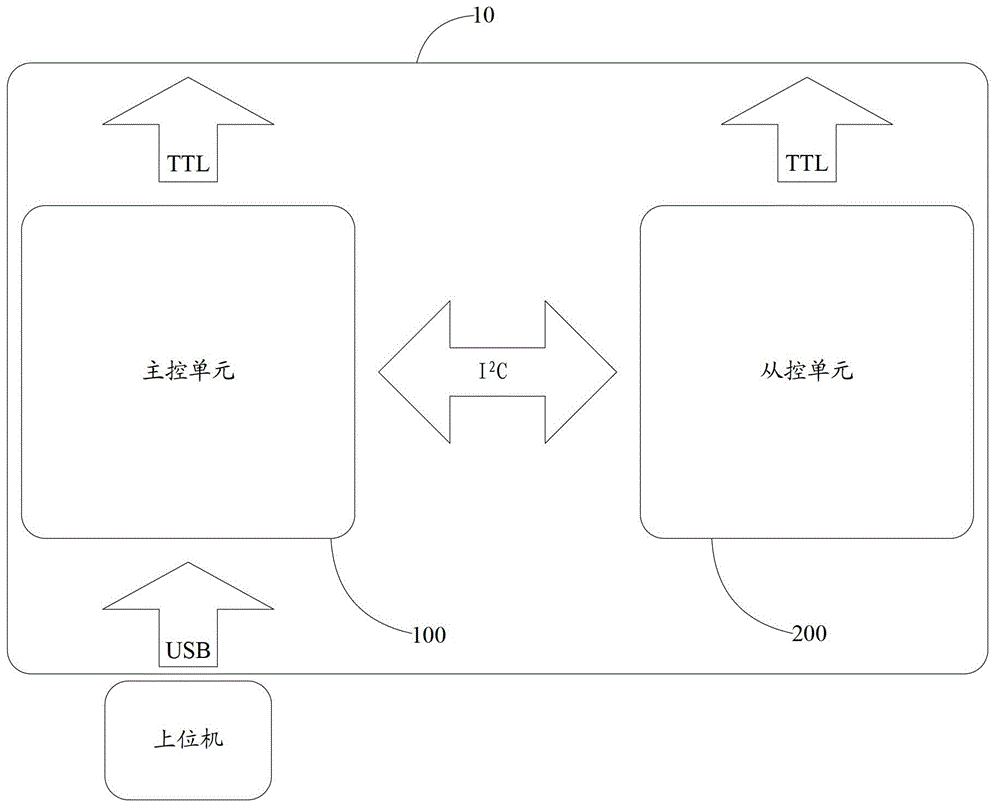

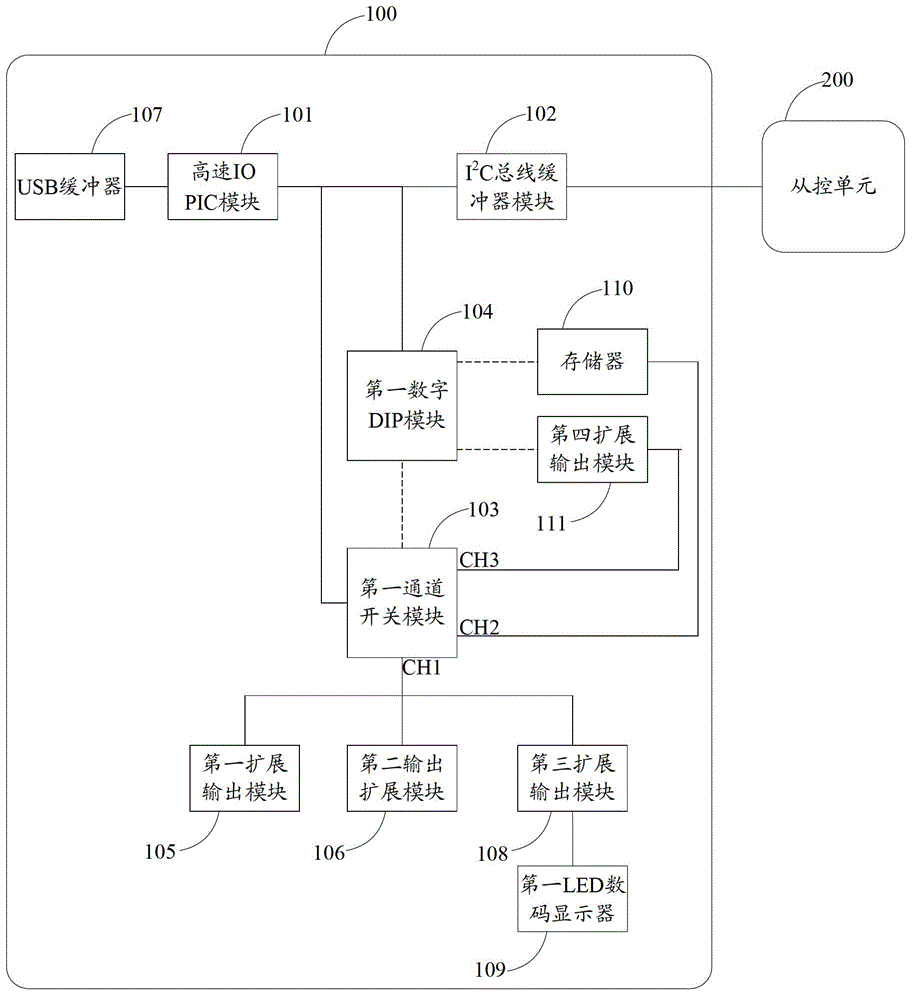

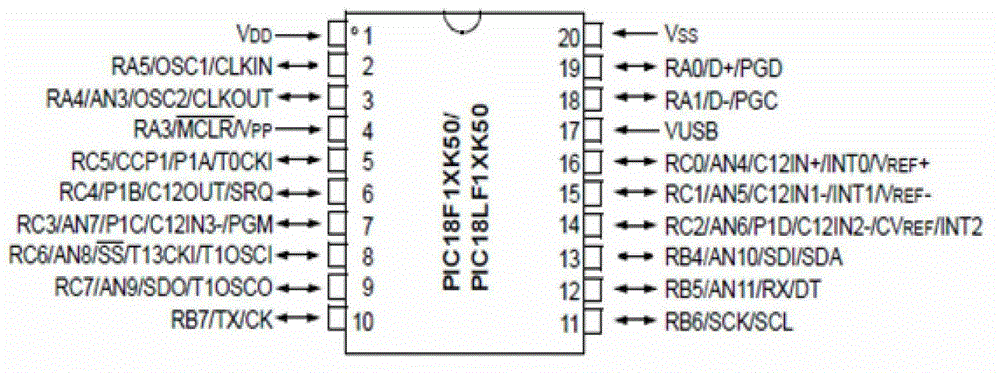

Signal conversion device and automatic testing system

ActiveCN102866683AFlexible collocationRealize automatic controlTotal factory controlProgramme total factory controlTransistor–transistor logicTransport system

The invention discloses a signal conversion device, which is used for receiving system control information from an upper computer and converting the system control information into a plurality of TTL (Transistor-Transistor Logic) level signals to be output. The signal conversion device comprises a master control unit, wherein the master control unit is used for receiving the system control information from the upper computer through a USB (Universal Serial Bus) communication protocol and converting the system control information into an I2C (Inter-Integrated Circuit) communication protocol data format; the system control information is transmitted outwards and external return information is received through an I2C bus; and the master control unit is also used for outputting the TTL level signals according to the system control information. The invention also discloses an automatic testing system using the signal conversion device. In such a mode, a drive is not required to be mounted, and the required TTL level signals can be flexibly output; and the signal conversion device and the automatic testing system are suitable for controlling complex conditions.

Owner:ANHUI TATFOOK M&E TECH

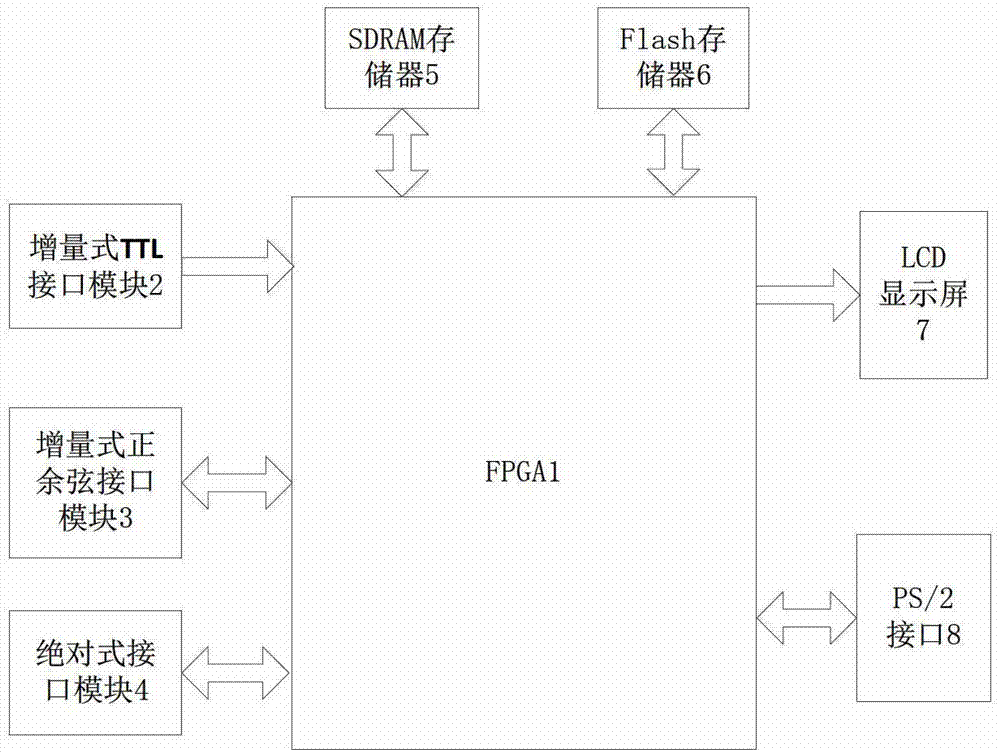

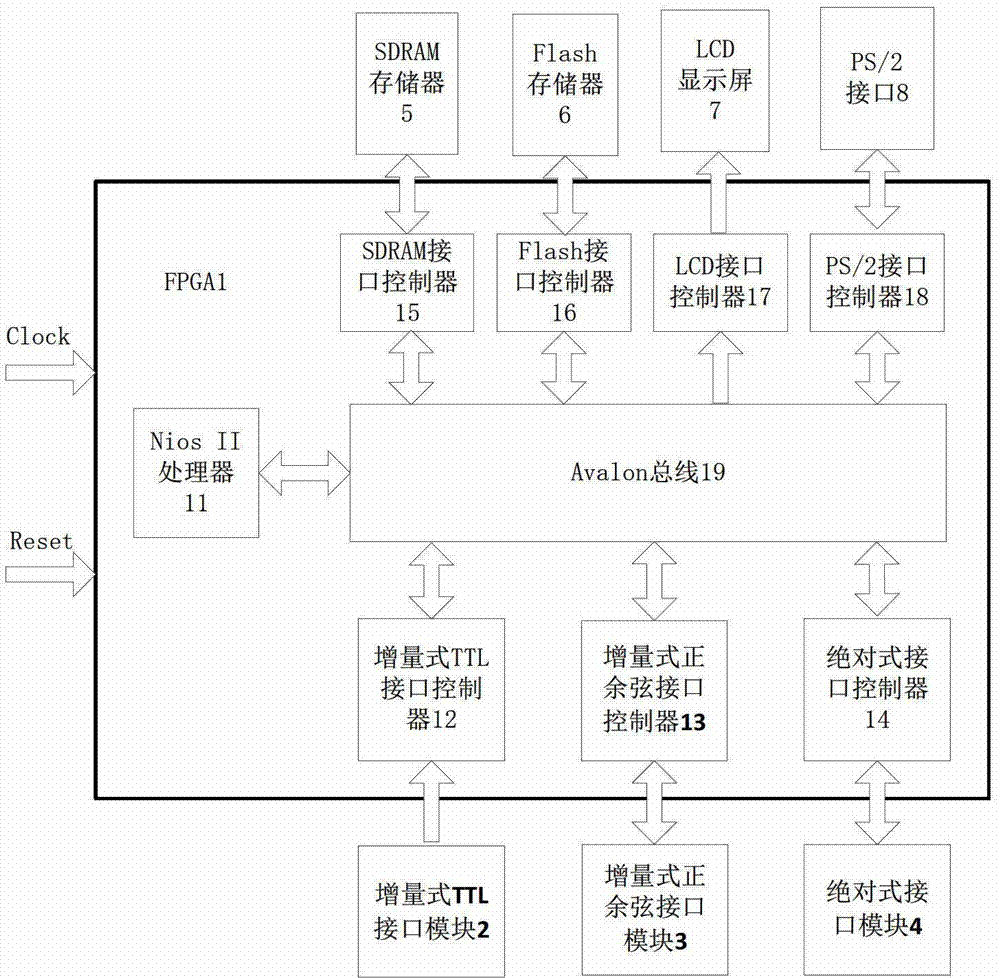

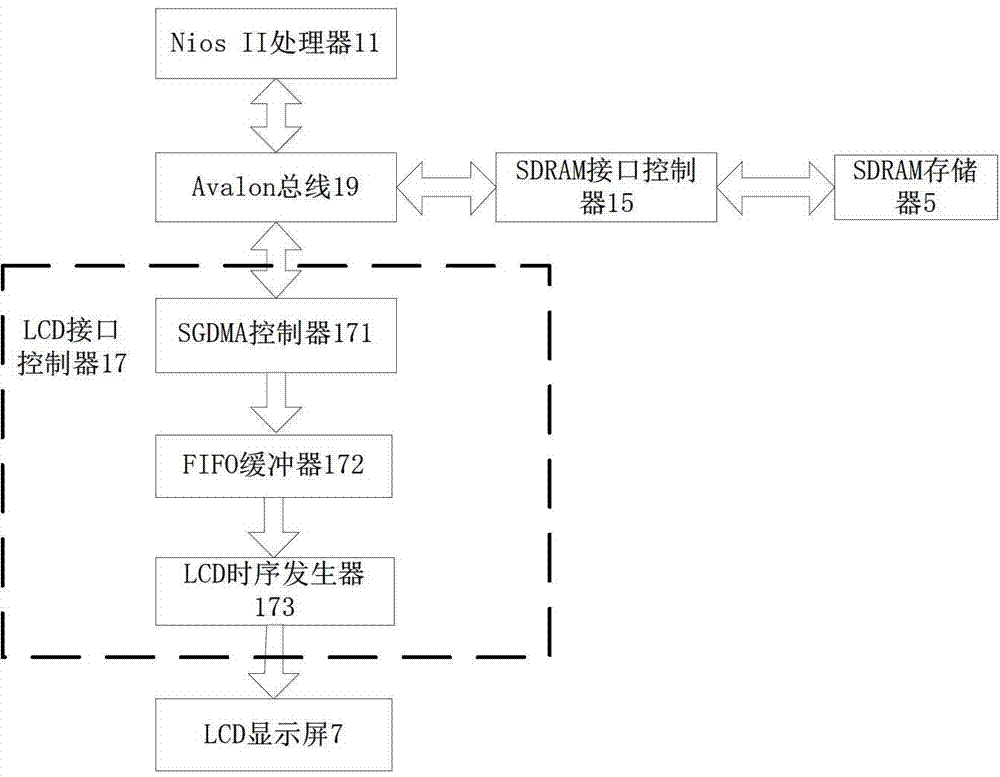

Coder interface testing device based on Nios II processor

InactiveCN102967326AHighly integratedReduce volumeInstrumentsTransistor–transistor logicDifferential signaling

The invention discloses a coder interface testing device based on a Nios II processor. The device comprises an FPGA (Field Programmable Gate Array) chip, an incremental TTL (Transistor Transistor Logic) interface module, an incremental sine and cosine interface module, an absolute interface module, a display screen and a PS (Poly Styrene) / 2 interface device, wherein the incremental TTL interface module, an incremental sine and cosine interface module, an absolute interface module, a display screen and a PS / 2 (Purple Green) interface device are connected with the FPGA chip; the incremental TTL interface module is used for being connected with the coder of an incremental TTL interface type, the incremental sine and cosine interface module is used for being connected with the coder of an incremental sine and cosine interface type, the absolute interface module is used for being connected with an absolute coder so that a serial digital signal output by the absolute interface module is transformed between a differential signal and a single-end signal, and the FPGA chip comprises a Nios II processor embedded in a chip, and the Nios II processor is used for processing an input signal and realizing the testing of coder interfaces. The Nios II processor-based coder interface testing device can be used for solving the problems that the coder interfaces in the existing coder testing platform can not be mutually compatible and are inconveniently carried, and has the characteristics of low cost, strong function, small volume, compact structure and high integration.

Owner:SUZHOU TIANCHENMA INTELLIGENT EQUIP +1

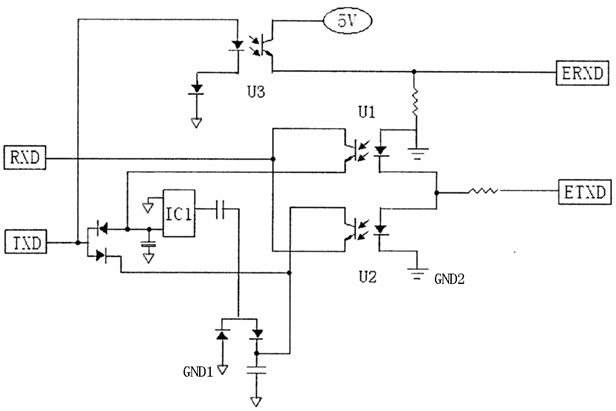

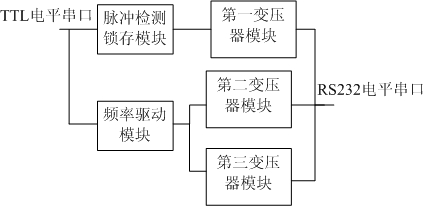

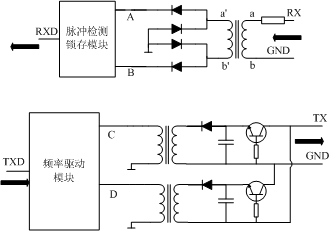

Method for realizing serial port isolation and serial port isolating circuit

InactiveCN102064821ASimple structureAvoid damageLogic circuits using opto-electronic devicesTransmission line coupling arrangementsTransistor–transistor logicTransformer

The invention provides a method for realizing serial port isolation and a serial port isolating circuit. The method comprises the following steps: converting RS232 level signals output by an RS232 level serial port into impulse signals by a first transformer module, converting the impulse signals into transistor-transistor logic (TTL) level signals, and then outputting the TTL level signals to a TTL level serial port; according to the received TTL level signals output by the TTL level serial port, selecting to output high-frequency signals to a second transformer module or third transformer module; converting the received high-frequency signals into RS232 negative level signals by the second transformer module, converting the received high-frequency signals into RS232 positive level signals by the third transformer module, and then outputting the RS232 positive level signals to the RS232 level serial port. The invention can effectively inhibit static electricity and surge, and preventan earth loop and surge from damaging a device serial port or interfering the normal operation of the device.

Owner:ZTE CORP

Serial port remote control circuit

InactiveUS20120246366A1Programme controlElectric digital data processingTransistor–transistor logicRemote control

A serial port remote control circuit includes a first interface circuit, a control circuit, an output circuit, and a power circuit. The first interface circuit converts recommended standard 232 (RS232) level signals to transistor-transistor logic (TTL) level signals or vice versa. The control circuit is connected to the first interface circuit, to convert the TTL level signals to physical bus signal or vice versa. The output circuit is connected to the control circuit, to convert the received physical bus signals from the control circuit to network bus signals or vice versa. The power circuit outputs a first voltage and a second voltage converted from the first voltage to the control circuit, the first interface circuit, and the output circuit.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

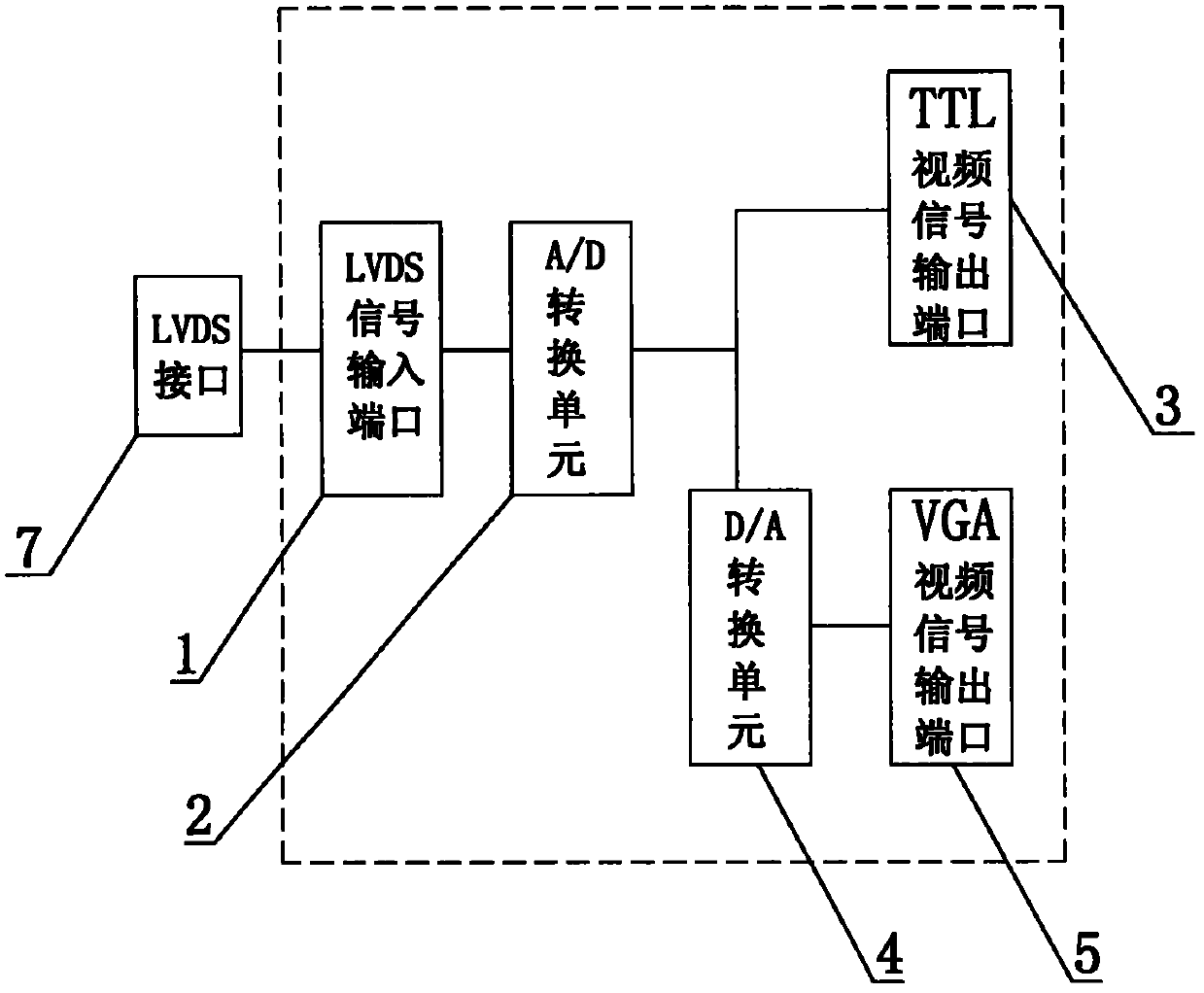

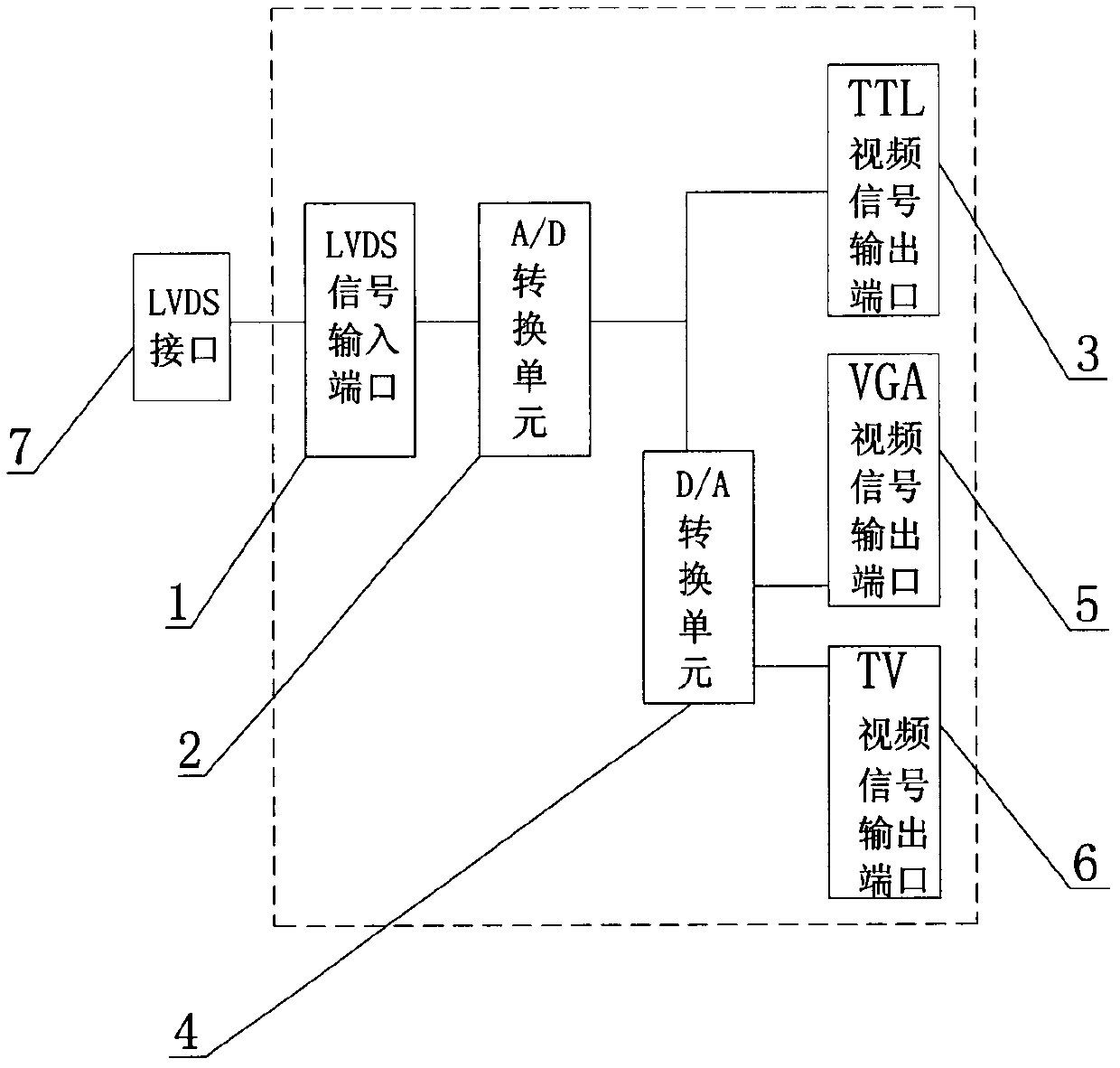

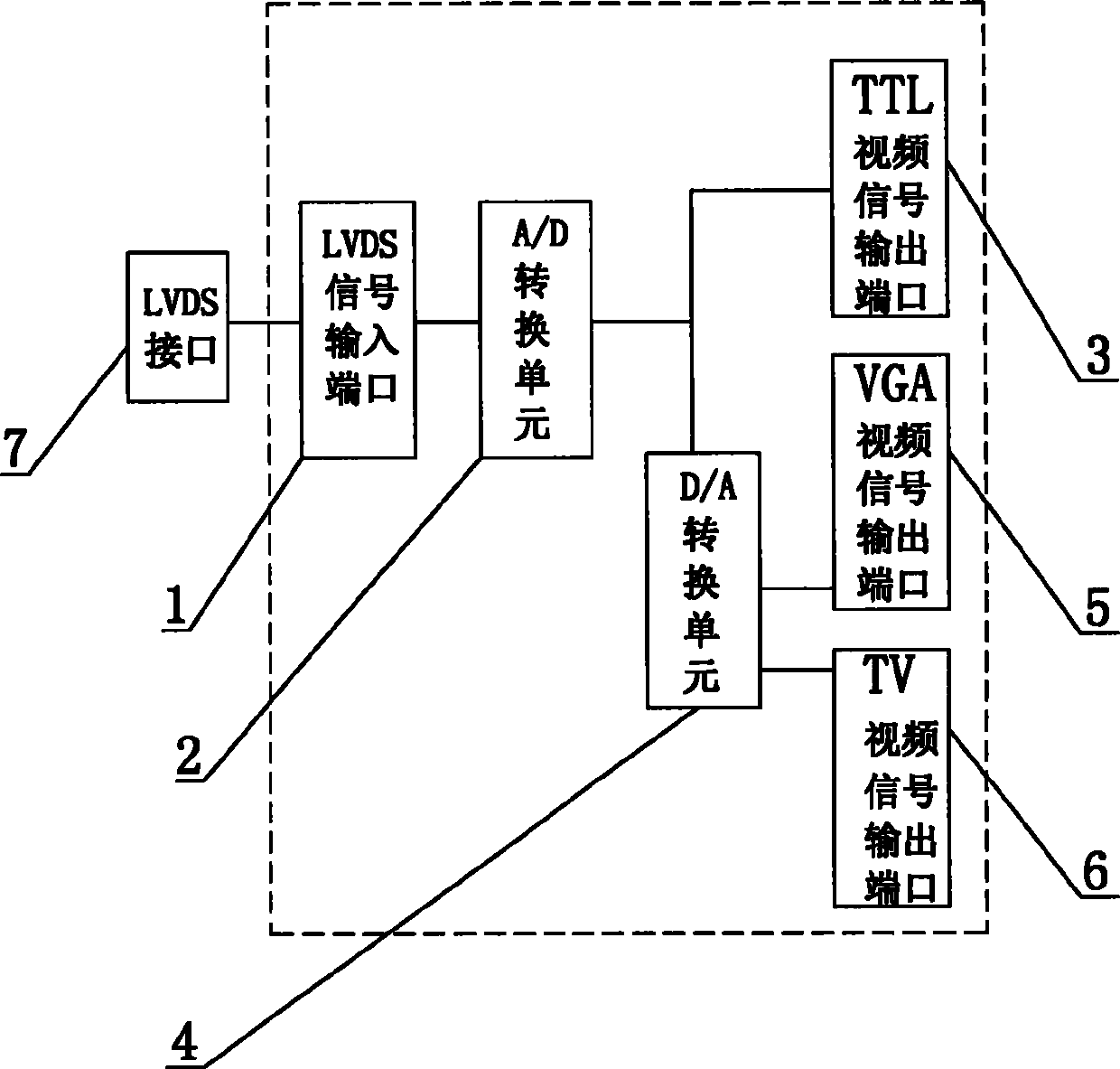

Video conversion device

InactiveCN102572213ARealize dual-screen displayTelevision system detailsColor television detailsDigital videoCRTS

The invention relates to a video signal conversion technology, and particularly discloses a video conversion device which is used for converting LVDS (Low Voltage Differential Signaling) into video signals of various other types. The video conversion device comprises an A / D (analog-to-digital) conversion unit and a D / A (digital-to-analog) conversion unit. According to the invention, through the A / D conversion unit, the LVDS video signals output by the LVDS video interface of a Menlow platform are converted into transistor-transistor logic level digital signals required by an LCD, and then converted into simulating signals supporting VGA (Video Graphics Array) display through the D / A conversion unit. Through the Menlow platform added in the invention, the double-screen display is flexibly realized; and more than nine display combinations are realized, such as LVDS display, CRT (Cathode Ray Tube) display and TV display which are converted based on LVDS interface of the Menlow platform, as well as VGA display, HDMI (High-Definition Multimedia Interface) display, and TV display which are converted based on SDVO (Serial Digital Video Output).

Owner:深圳市英康仕电子有限公司

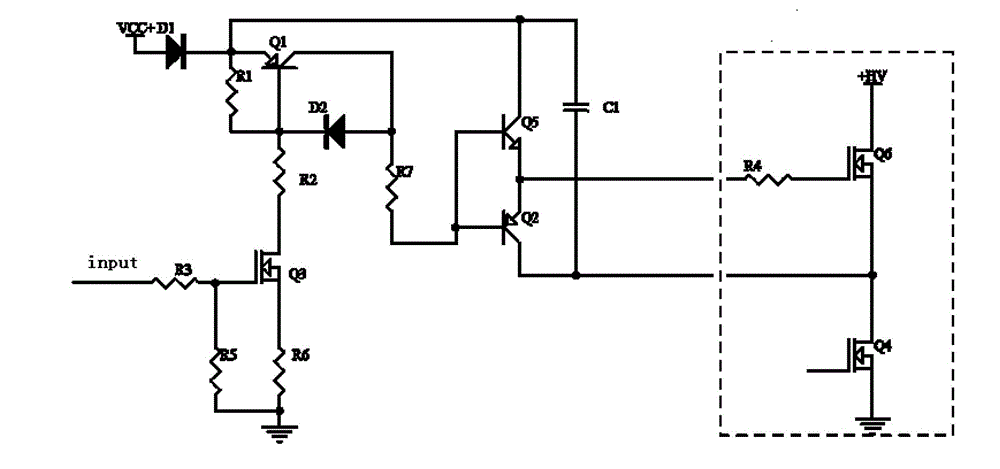

Bootstrap driving circuit

InactiveCN102751977AComply with suspension drive MOS tubeMeet the requirementsLogic circuits coupling/interface using field-effect transistorsMicrocontrollerTransistor–transistor logic

The invention provides a bootstrap driving circuit. The bootstrap driving circuit comprises a totem pole output circuit, and further comprises a low-pressure-controlled high-pressure MOS (metal oxide semiconductor) pipe circuit and a switching signal circuit which are connected, wherein the low-pressure-controlled high pressure MOS pipe circuit is arranged on the input end of the bootstrap driving circuit, and the switching signal circuit is connected with the totem pole output circuit. The bootstrap driving circuit provided by the invention fully utilizes the conventional discrete element to reduce the circuit cost, input-output interfaces of the circuit are relatively easy to be connected with a MCU (microprogrammed control unit) of a singlechip, a TTL (transistor-transistor logic) device, and the cost is low.

Owner:HUIZHOU SANHUA IND

Signal conversion device and method

ActiveCN105635619AHighly integratedEasy to operateTelevision system detailsStatic indicating devicesTransistor–transistor logicComputer module

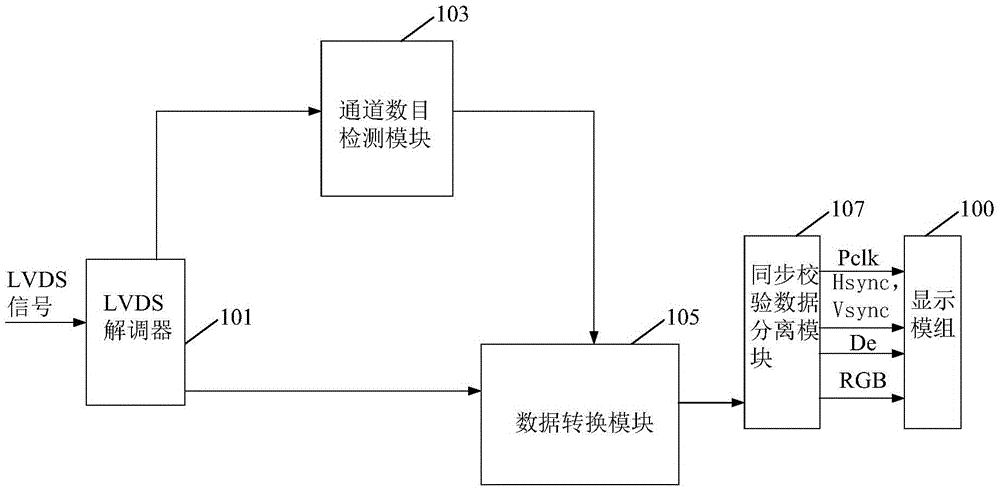

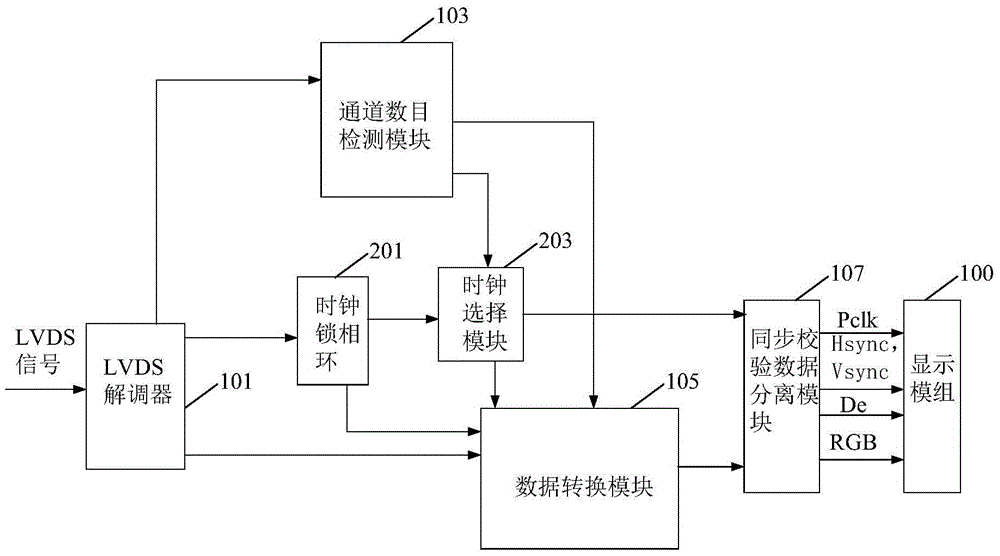

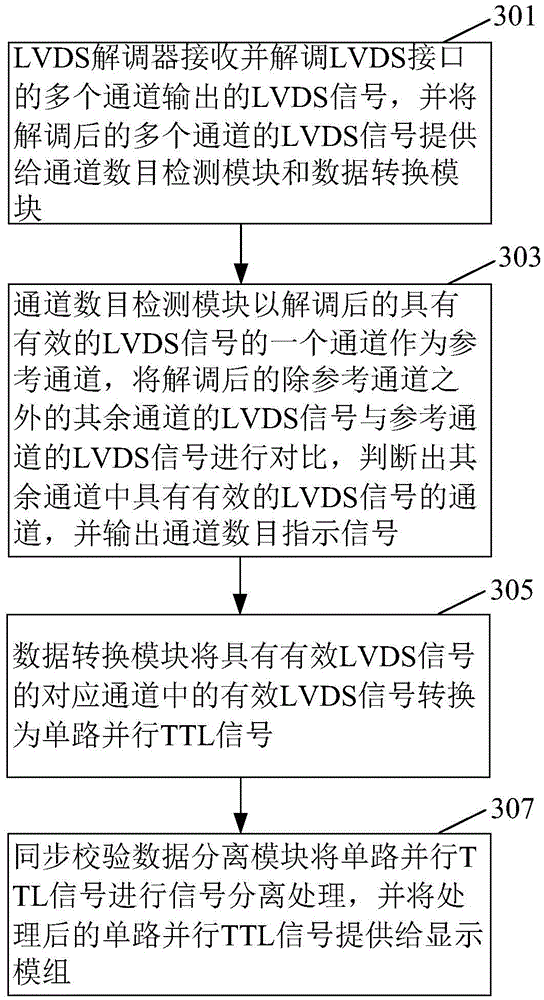

Embodiments of the invention disclose a signal conversion device and method. The signal conversion device comprises an LVDS (Low Voltage Differential Signaling) demodulator, a channel number detection module, a data conversion module and a synchronous check data separation module, wherein the LVDS demodulator is used for receiving and demodulating LVDS signals output by a plurality of channels of an LVDS interface; the channel number detection module is used for taking one channel provided with an effective LVDS signal after demodulation as the reference channel, carrying out comparison on the LVDS signals of the remaining channels except for a reference channel after demodulation and the LVDS signal of the reference channel, judging the channels provided with the effective LVDS signals in the remaining channels, and outputting a channel number indication signal; the data conversion module is used for converting the effective LVDS signals in the corresponding channels provided with effective LVDS signals into one way of parallel TTL (Transistor-Transistor Logic) signals; and the synchronous check data separation module is used for carrying out signal separation processing on one way of parallel TTL signals. According to the signal conversion device and method, the number of the LVDS channels can be automatically recognized, and the device and the method have the advantages of simplicity in operation, high efficiency and low cost.

Owner:KUSN INFOVISION OPTOELECTRONICS

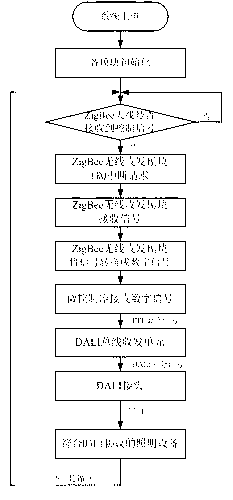

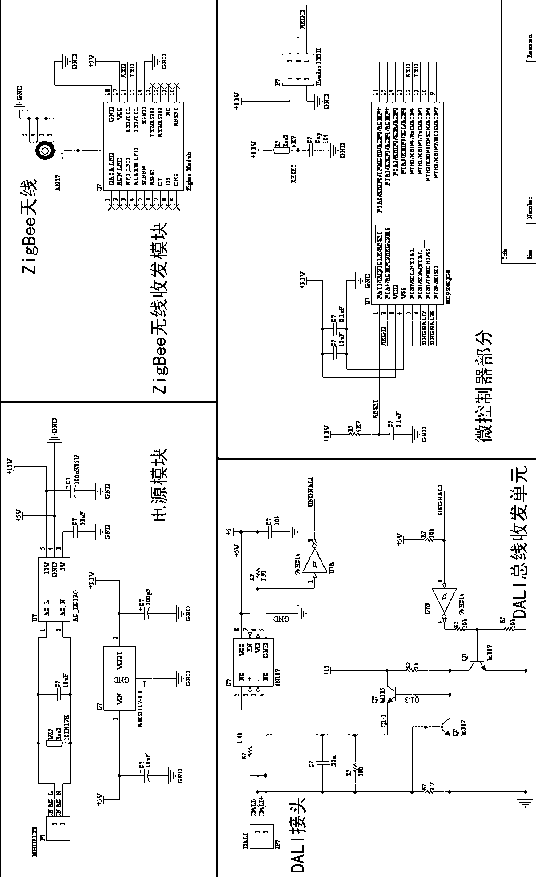

Lighting control device for realizing transmission of DALI (digital addressable lighting interface) bus protocol through ZigBee

ActiveCN102802316ALarge scaleMeet needsNetwork topologiesElectric light circuit arrangementMicrocontrollerIntelligent lighting

The invention discloses a lighting control device for realizing the transmission of a DALI (digital addressable lighting interface) bus protocol through ZigBee, which comprises a DALI joint, a DALI bus transceiver unit, a FLASH-containing microcontroller, a ZigBee wireless transceiver module, a 2.4 G antenna and a power module, wherein the DALI joint is used for outputting DALI bus control signals, the DALI bus transceiver unit is used for carrying out mutual conversion on a TTL (transistor-transistor logic) level and a DALI difference level, the ZigBee wireless transceiver module is used for carrying out ZigBee wireless data transmission, the DALI joint, the DALI bus transceiver unit, the microcontroller, the ZigBee wireless transceiver module and the 2.4 G antenna are sequentially connected, and the power module is simultaneously connected with the DALI bus transceiver unit, the microcontroller and the ZigBee wireless transceiver module. The lighting control device disclosed by the invention not only has a wireless ZigBee receiving function, but also can carry out addressing on lighting equipment according to the DALI bus protocol, and control the lighting state of the lighting equipment, therefore, the lighting control device can effectively meet the large-scale, high-scalability requirements of intelligent lighting control systems.

Owner:JIANGSU PROVINCIAL COMM PLANNING & DESIGN INST