Signal conversion device and method

A signal conversion device and signal technology, applied in the direction of standard conversion, film film standard conversion, image communication, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

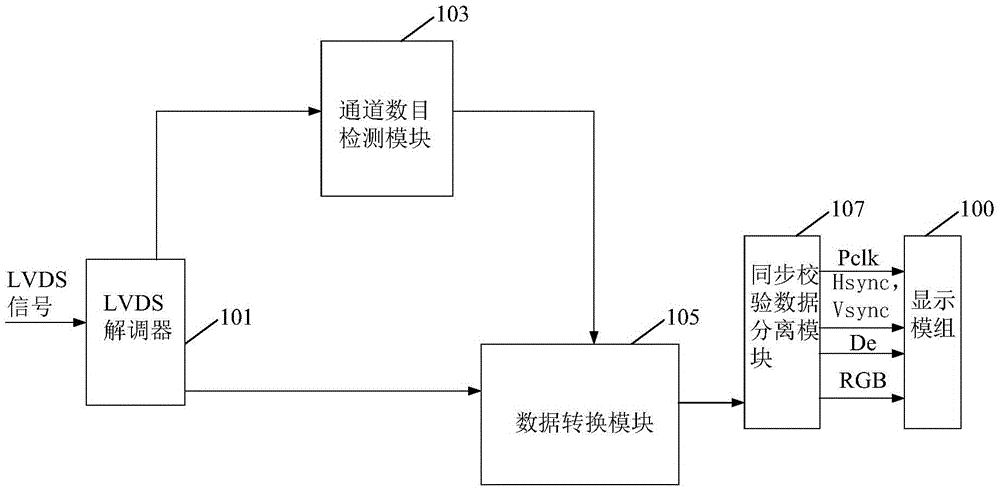

[0021] figure 1 is a structural block diagram of the signal conversion device provided by the first embodiment of the present invention. The signal conversion device is used to convert the LVDS signal output by the LVDS interface into a TTL signal and provide it to the display module. Please refer to figure 1 , the signal conversion device includes an LVDS demodulator 101, a channel number detection module 103, a data conversion module 105, and a synchronization verification data separation module 107. Wherein, the signal conversion device may be integrated into an FPGA (Field-Programmable Gate Array, ie Field-Programmable Gate Array) chip.

[0022] Specifically, the LVDS demodulator 101 is connected to the channel number detection module 103 and the data conversion module 105, and is used to receive and demodulate the LVDS signals output by multiple channels of the LVDS interface, and convert the demodulated LVDS signals of multiple channels The signal is provided to the c...

no. 2 example

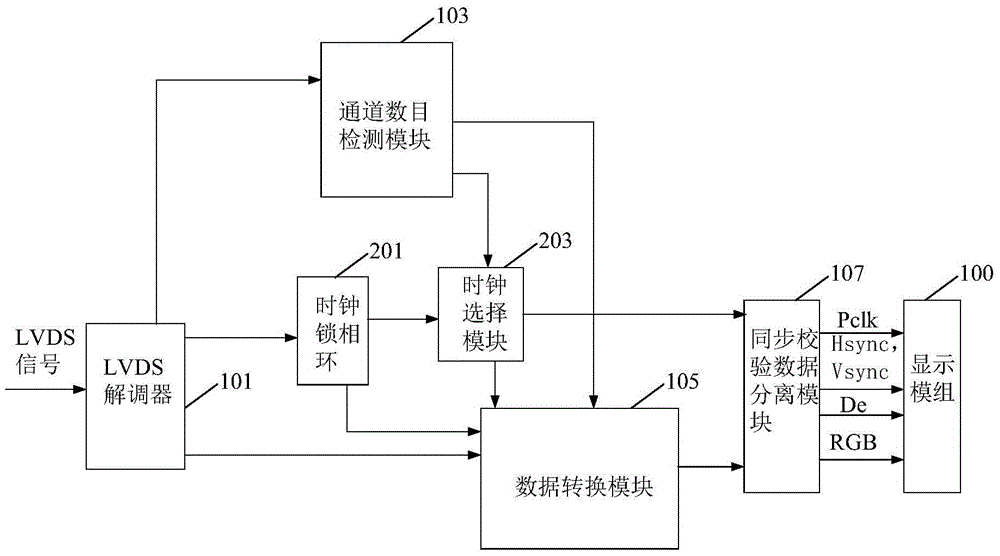

[0034] figure 2 is a structural block diagram of the signal conversion device provided by the second embodiment of the present invention. figure 2 is in figure 1 improved on the basis of figure 2 and figure 1 The difference is that figure 2 The signal conversion device may further include: a clock phase-locked loop 201 and a clock selection module 203 .

[0035] The clock phase-locked loop 201 is connected with the LVDS demodulator 101, the clock selection module 203, and the data conversion module 105, and is used for latching and multiplying the pixel clock signal in the LVDS signal of the demodulated first channel to generate Multiple pixel clock signals are generated, and the generated multiple pixel clock signals are provided to the clock selection module 203 and the data conversion module 105 . For example, the clock phase-locked loop 201 can generate a single-channel pixel clock signal, such as a double-frequency pixel clock signal, or a dual-channel pixel cloc...

no. 3 example

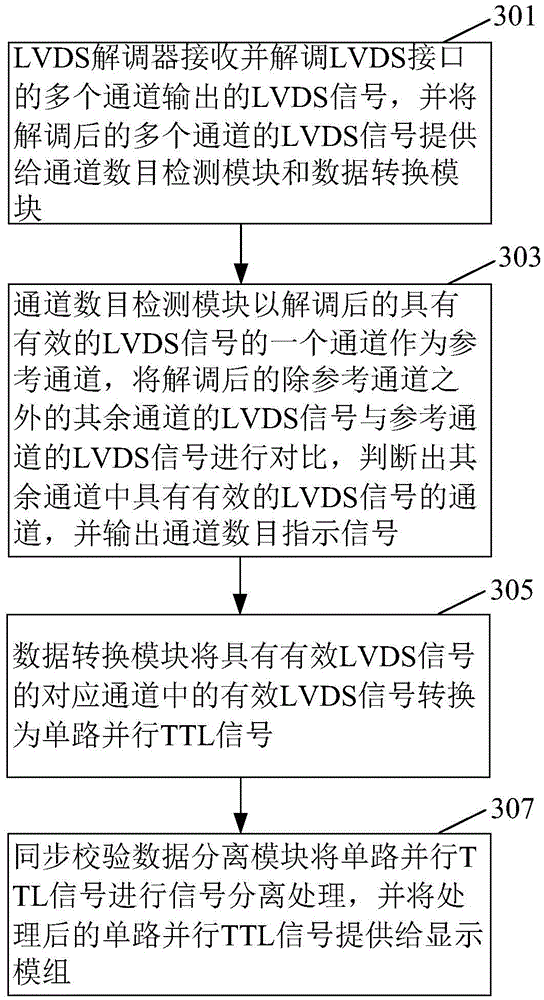

[0041] image 3 It is a flow chart of the steps of the signal conversion method provided by the third embodiment of the present invention. The method is applied to the above-mentioned signal conversion device, please refer to image 3 , the signal conversion method of this embodiment includes the following steps 301-307.

[0042] In step 301, the LVDS demodulator receives and demodulates LVDS signals output by multiple channels of the LVDS interface, and provides the demodulated LVDS signals of multiple channels to the channel number detection module and the data conversion module, and the multiple channels include the first One to the nth channel, where n is an integer greater than 0;

[0043] Step 303, the channel number detection module uses a channel with an effective LVDS signal after demodulation as a reference channel, compares the LVDS signals of other channels except the reference channel after demodulation with the LVDS signal of the reference channel, and judges ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More