Patents

Literature

82results about How to "Improve reverse withstand voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

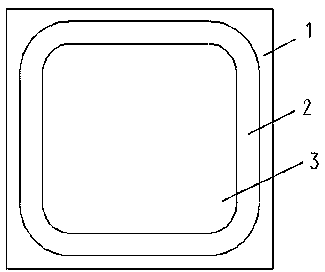

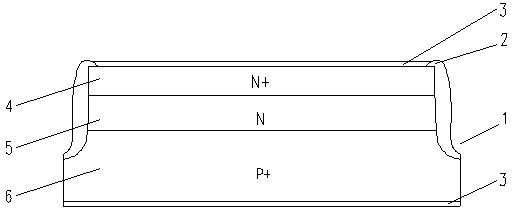

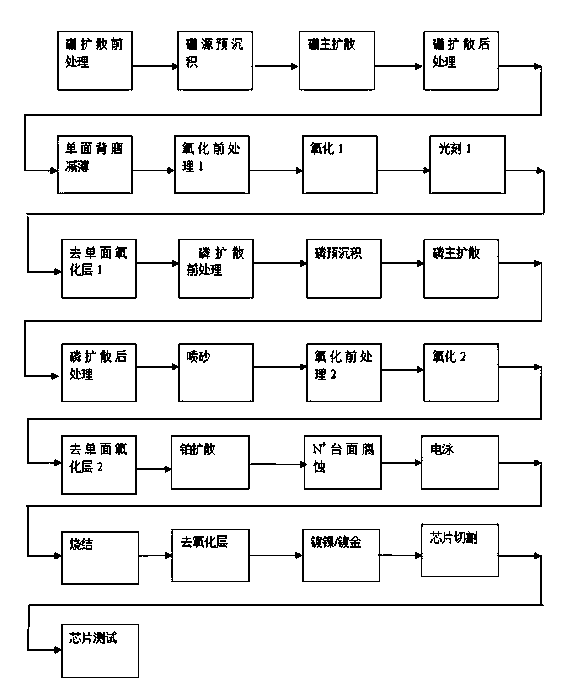

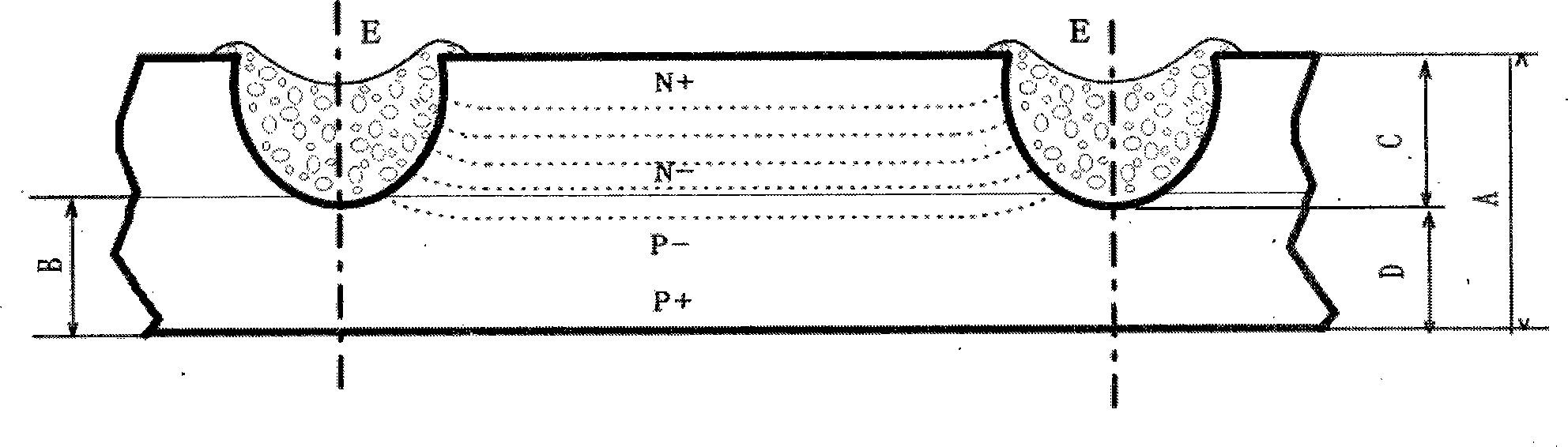

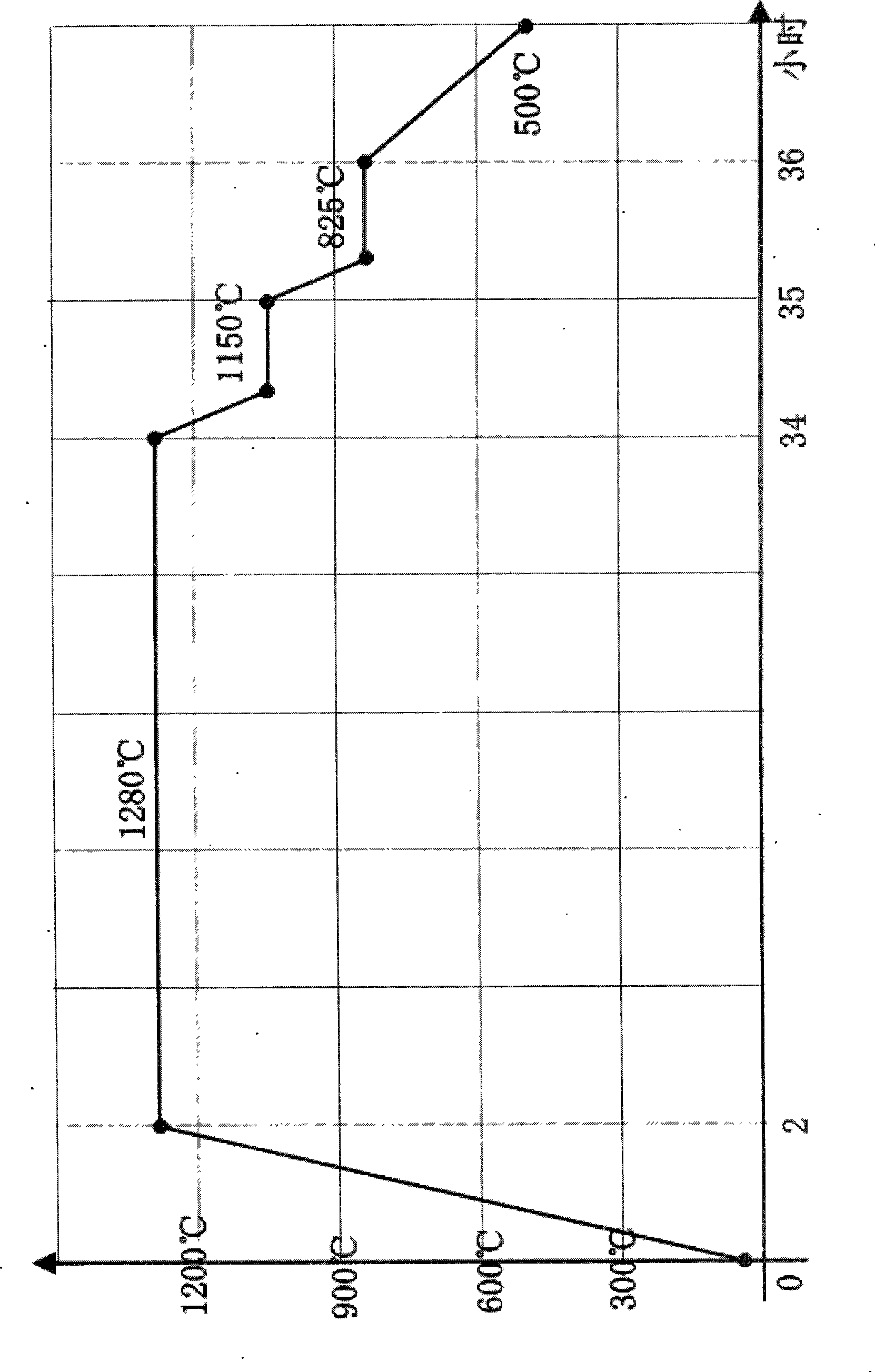

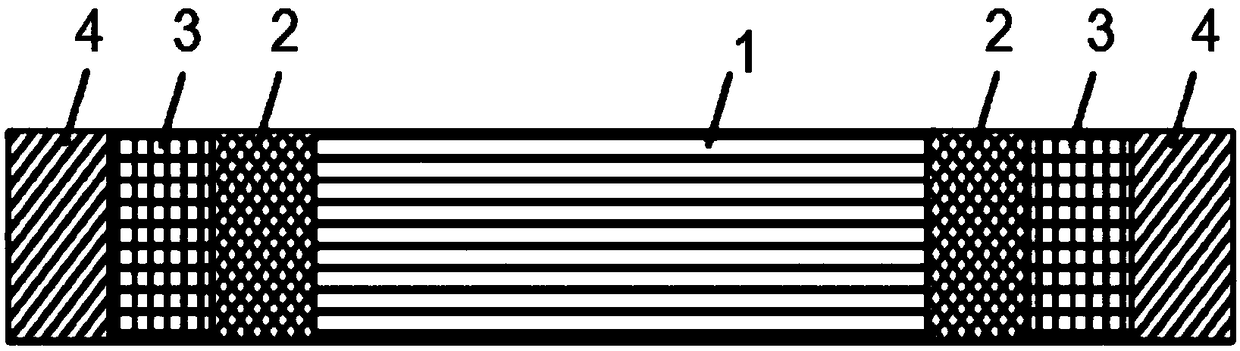

Fast recovery diode FRD chip and production process for same

ActiveCN104201102AImprove anti-surge performanceImprove flatnessSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingLayer removal

The invention relates to a fast recovery diode FRD chip and a production process for the same. The process comprises the following steps of: diffusion pre-treatment, boron source pre-deposition, boron source main diffusion, diffusion after-treatment, single-surface back grinding thinning, oxidation pre-treatment, oxidation, photoetching, single-surface oxide layer removal, phosphorus source pre-deposition, phosphorus diffusion, sand blasting, platinum diffusion, N + surface mesa etching, electrophoresis, sintering, oxide layer removal, nickel plating, gold plating and chip cutting, wherein the structure of the obtained chip is P+-N-N+ type. According to the process, the uniformity of the reverse recovery time of the fast recovery diode is improved and controllability is improved, meanwhile, voltage drop is reduced, leakage current is reduced, and voltage-proof stability is improved; the contradiction of mutual condition among the reverse voltage, the positive voltage, the reverse recovery time and the leakage current of the fast recovery diode is solved to enable the various parameters to achieve the optimal matching, thus improving the reliability and switching characteristic of the diode, and reducing power consumption. The fast recovery diode disclosed by the invention breaks through the technical bottleneck of the traditional fast recovery diodes.

Owner:SUZHOU QILAN POWER ELECTRONICS

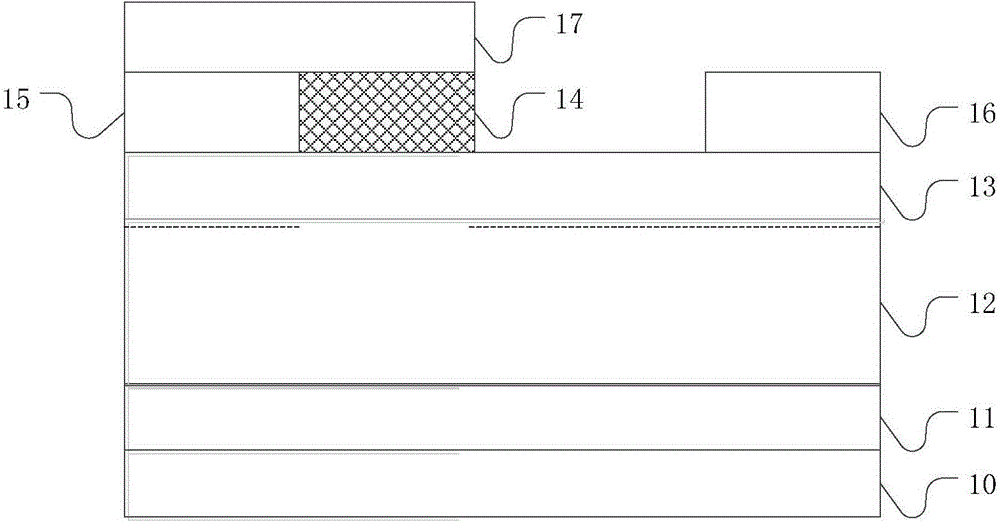

GaN hetero-junction diode device and method for manufacturing same

ActiveCN104362181AAchieve rectification characteristicsLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionPower flow

The invention discloses a GaN hetero-junction diode device and a method for manufacturing the same. The GaN hetero-junction diode device comprises a substrate, a buffer layer, a channel layer, a potential barrier layer, a cap layer, a first Ohm anode, an Ohm cathode and a second Ohm anode. The buffer layer is positioned on the substrate; the channel layer is positioned on the buffer layer; the potential barrier layer is positioned on the channel layer, the potential barrier layer and the channel layer form a hetero-structure, and a two-dimensional electric channel is formed at a hetero-junction interface; the cap layer is positioned on the potential barrier layer; the first Ohm anode and the Ohm cathode are positioned on the upper side of the potential barrier layer and are arranged on two sides of the cap layer, and the first Ohm anode is in contact with the cap layer; the second Ohm anode is positioned on the first Ohm anode and the cap layer and is in Ohm metal contact with the cap layer. The GaN hetero-junction diode device and the method have the advantages that the problem of conflict between forward start voltage control and reverse electric leakage in the prior art can be solved, and a diode has characteristics of low start voltages and turn-on resistance and high reverse withstand voltages and forward turn-on currents.

Owner:GPOWER SEMICON

Schottky diode and manufacturing method for Schottky diode

InactiveCN104134704AIncrease widthReduce concentration effectSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierSchottky diode

The invention provides a Schottky diode and a manufacturing method of the Schottky diode. The Schottky diode has the advantages that due to the fact that a groove structure with the wide upper portion and the narrow lower portion is mainly formed in a semiconductor layer, the concentration of two-dimensional electron gas below the Schottky metal inclined groove face can be effectively modulated, the Schottky barrier width and the Schottky barrier height can be increased, and therefore reverse electric leakage can be reduced; meanwhile, the concentration effect of an electric field at the edge of a groove can be further effectively improved, and the breakdown voltage of a device can be increased.

Owner:GPOWER SEMICON

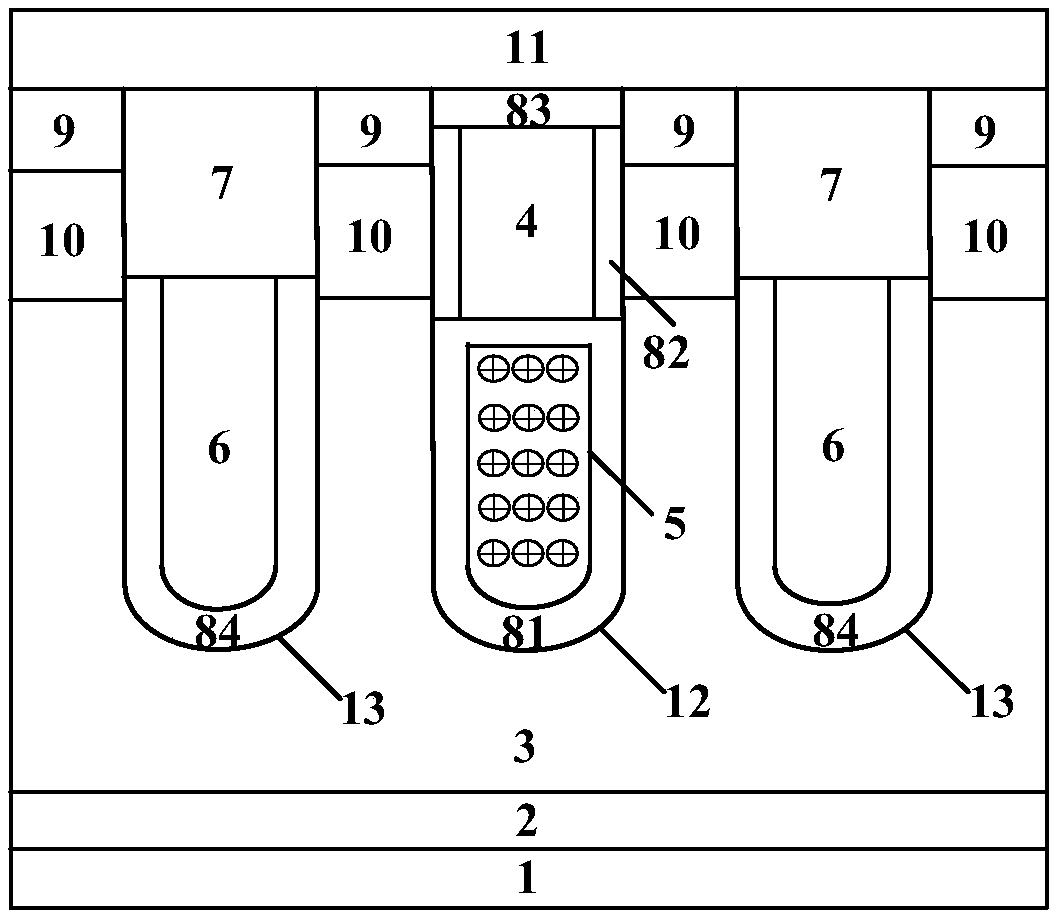

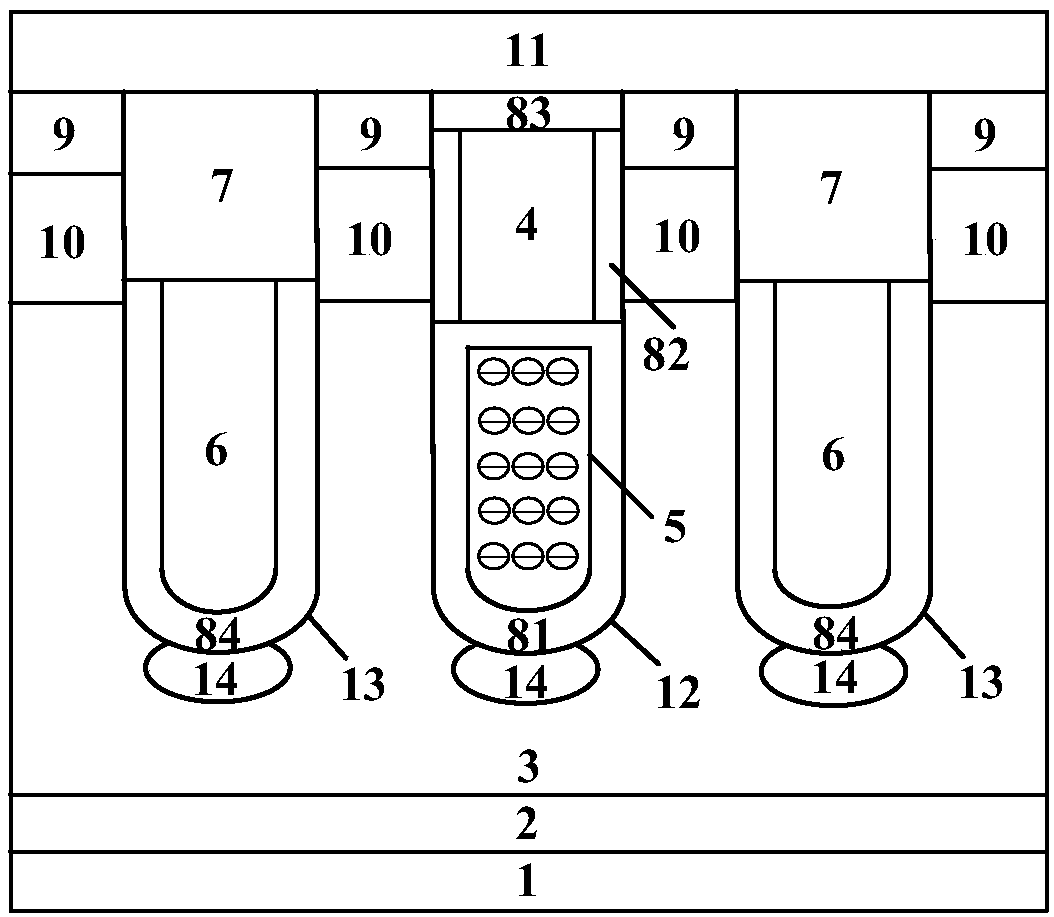

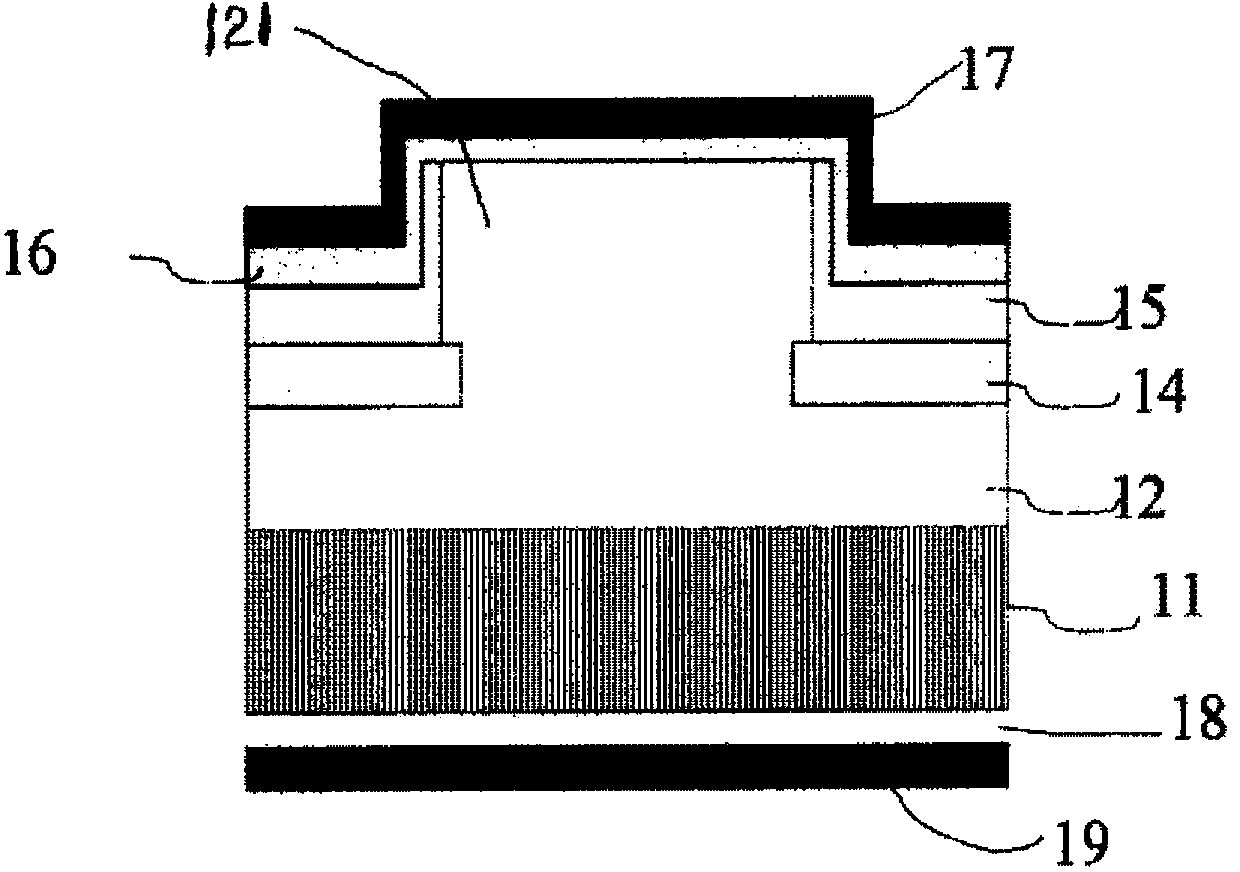

Silicon carbide diode with low turn-on voltage and low on resistance and manufacturing method

ActiveCN111312802ALower turn-on voltageLower on-resistanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate dielectric

The invention provides a silicon carbide diode with low turn-on voltage and low on resistance and a manufacturing method thereof. The silicon carbide diode comprises a cathode metal electrode, an N +substrate above the cathode metal electrode and an N-drift region above the N + substrate, a P-type shielding buried layer arranged above the N-drift region; a P + ohmic contact region arranged in theP-type shielding buried layer, an anode metal electrode arranged above the P + ohmic contact region, a trench gate dielectric layer arranged above the P-type shielding buried layer, a polysilicon trench gate arranged in the trench gate dielectric layer, an N+ source regions arranged between the trench gate dielectric layers, a plane gate dielectric layer arranged above the N + source regions, anda polysilicon plane gate arranged in the plane gate dielectric layer. The anode metal electrode covers the trench gate dielectric layer, the polysilicon trench gate, the N+ source region, the plane gate dielectric layer and the polysilicon plane gate. According to the invention, the three-channel accumulation type channel MOSFET and the JFET are connected in series to form the super-barrier diode, and the silicon carbide diode has the characteristics of low turn-on voltage, small on-resistance, high reverse withstand voltage, small leakage current and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

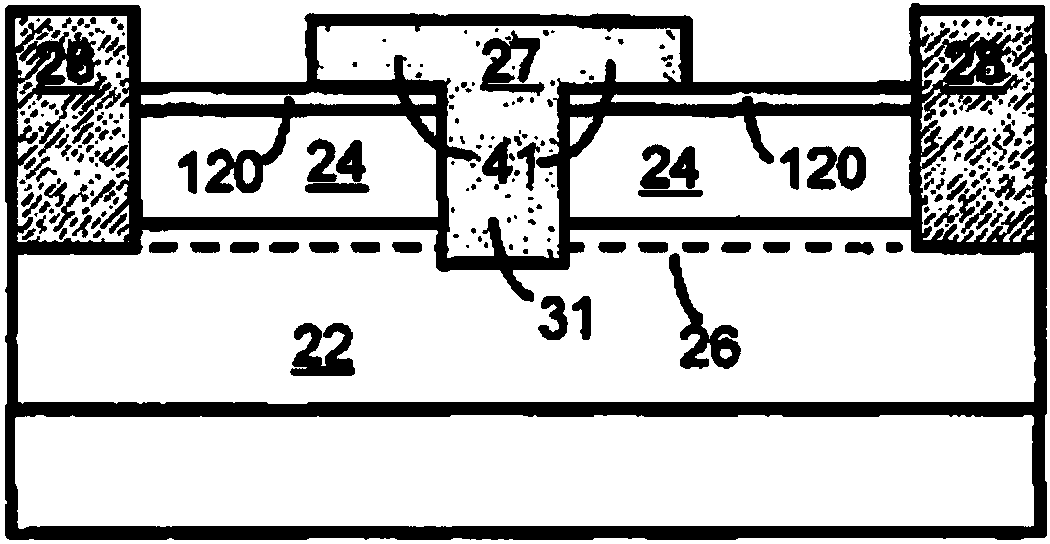

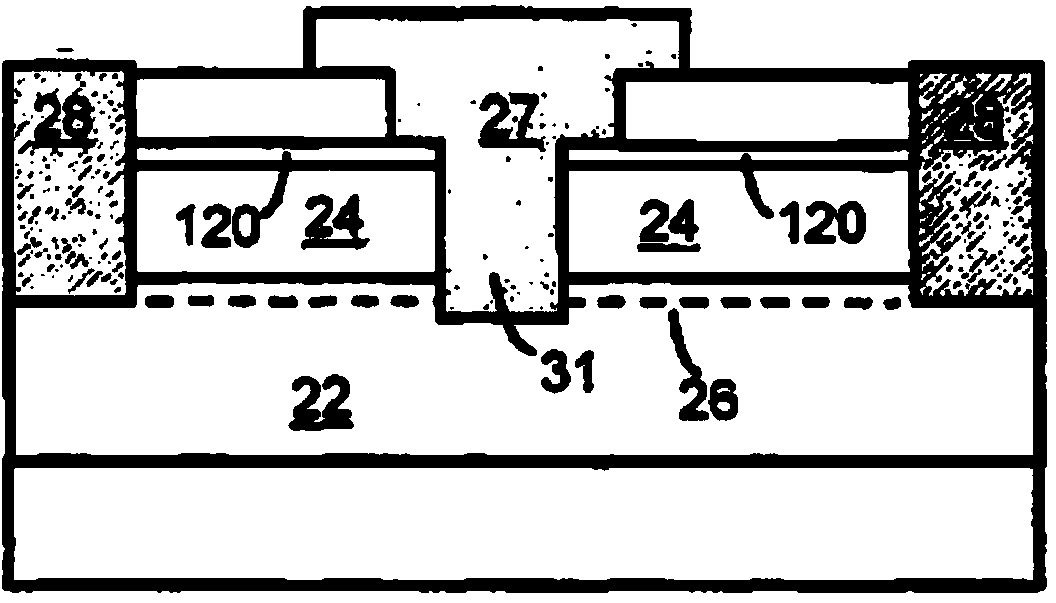

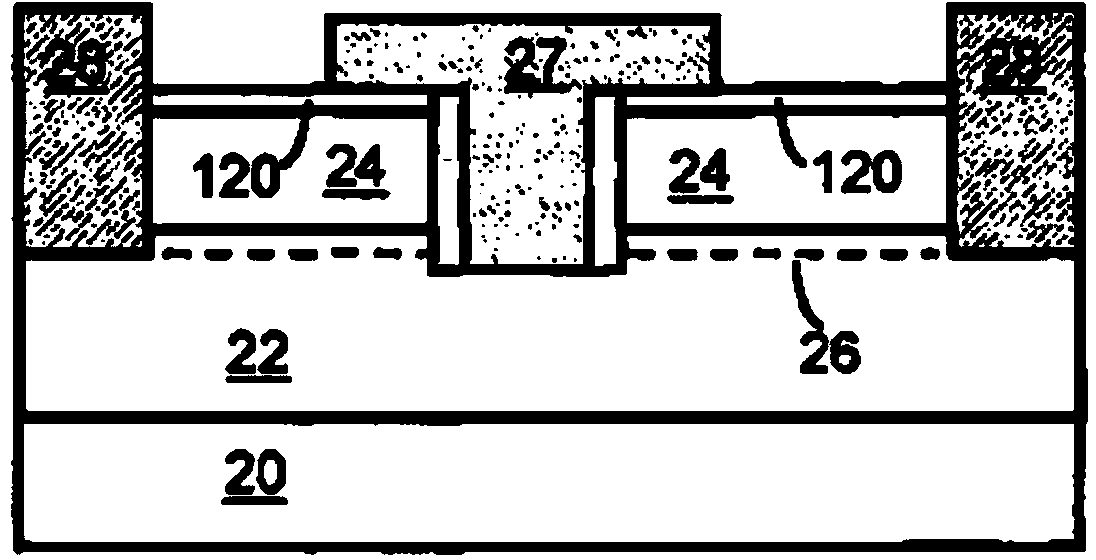

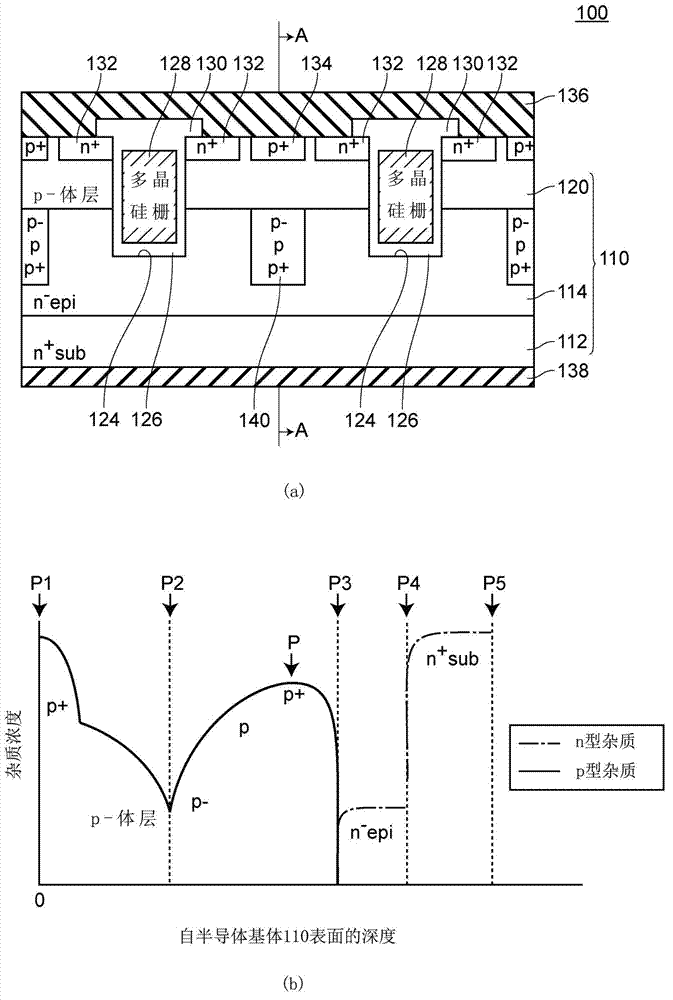

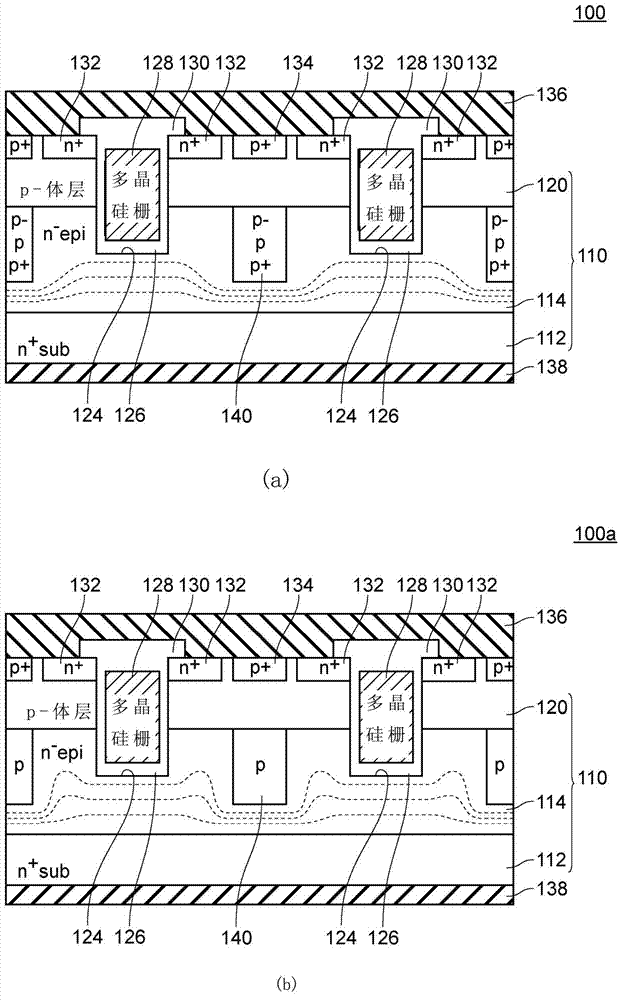

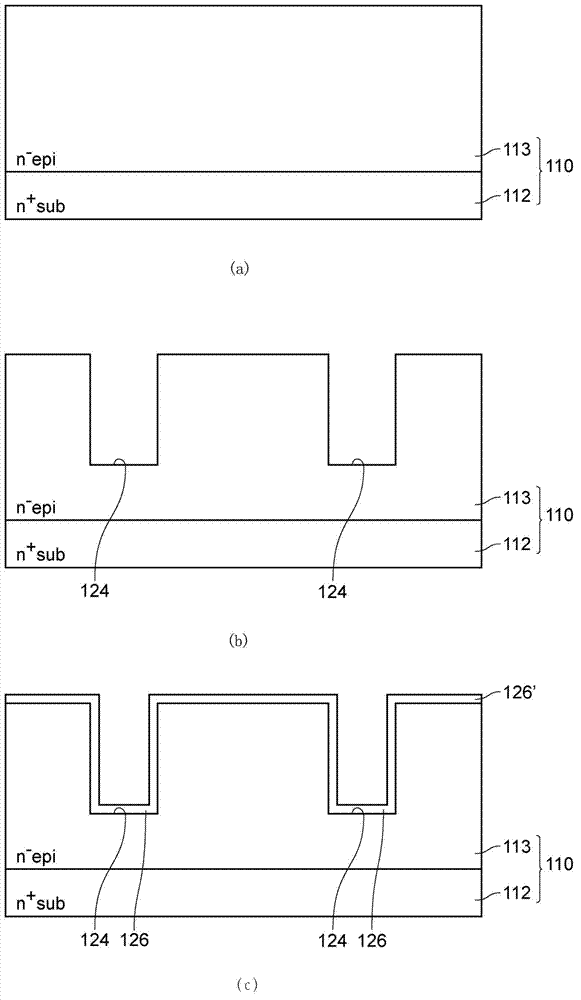

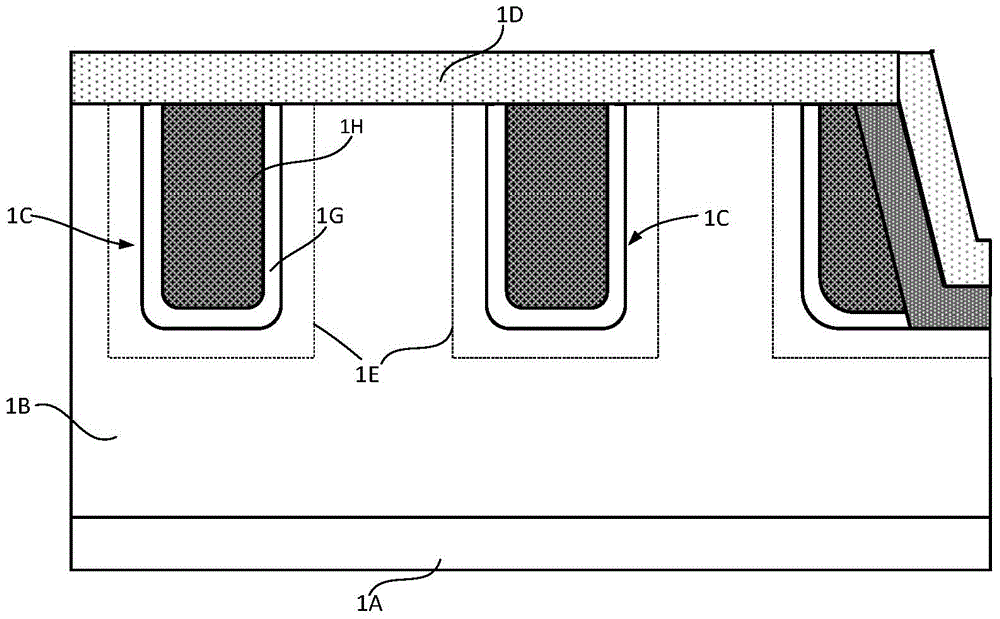

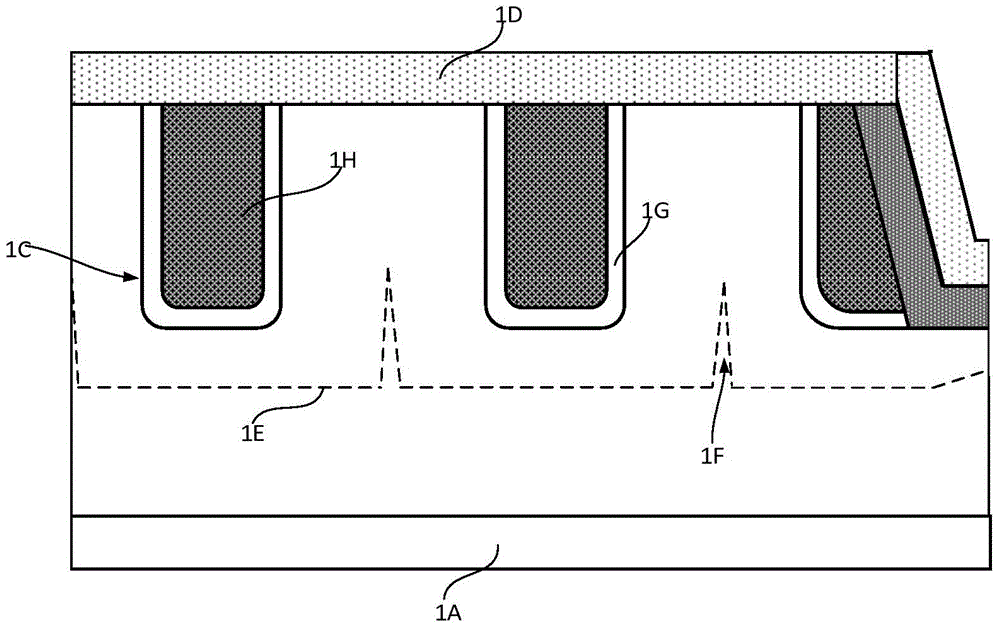

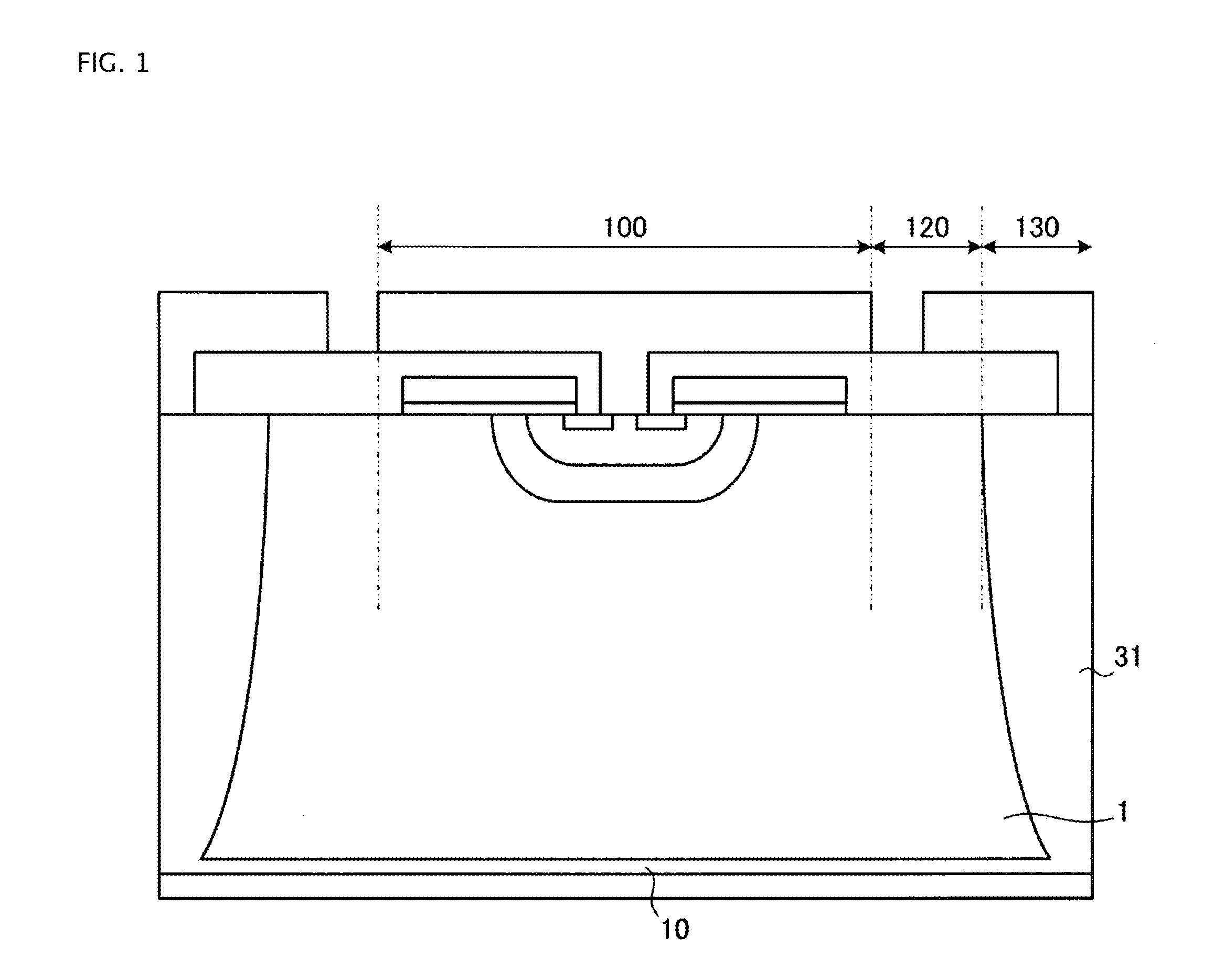

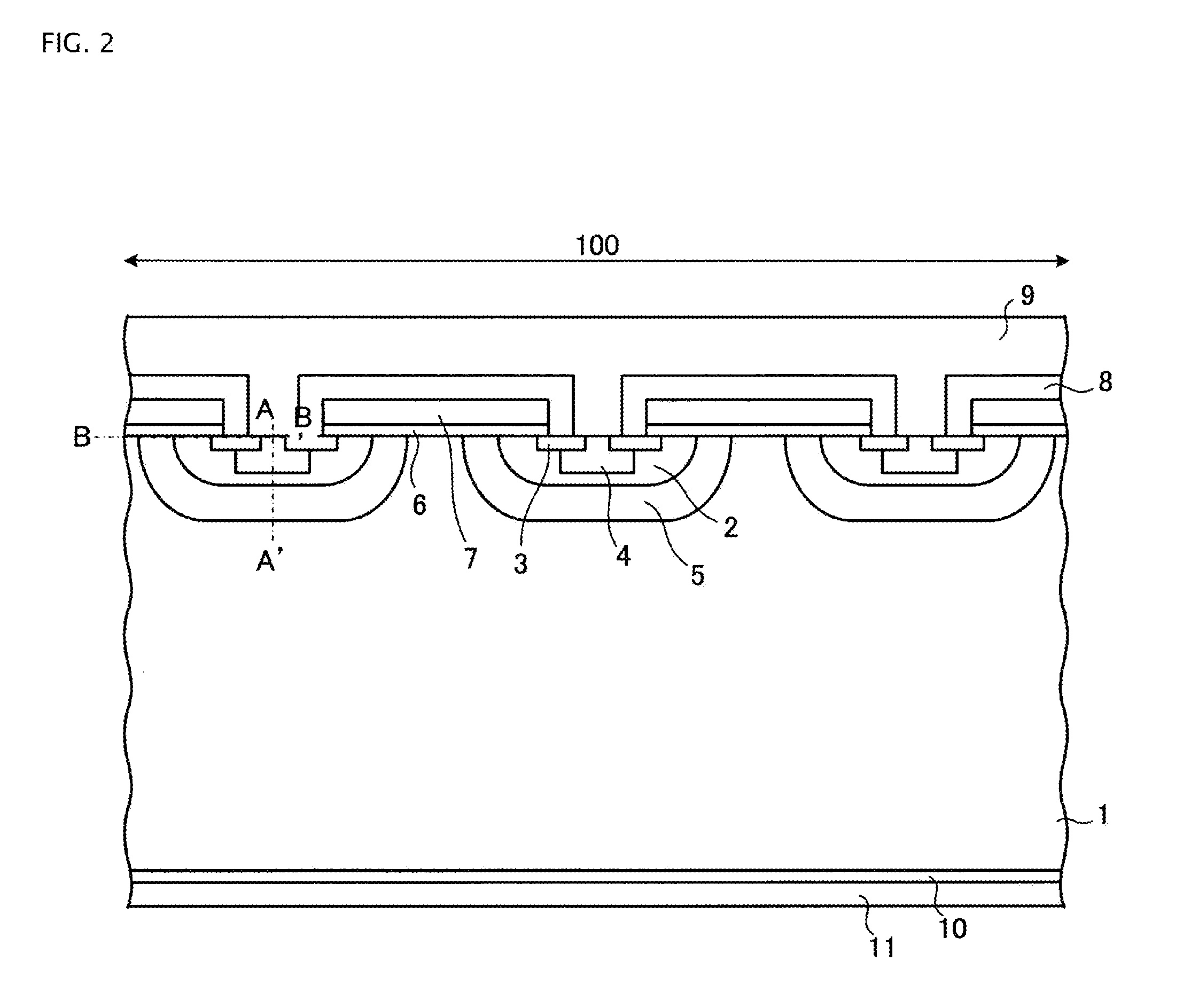

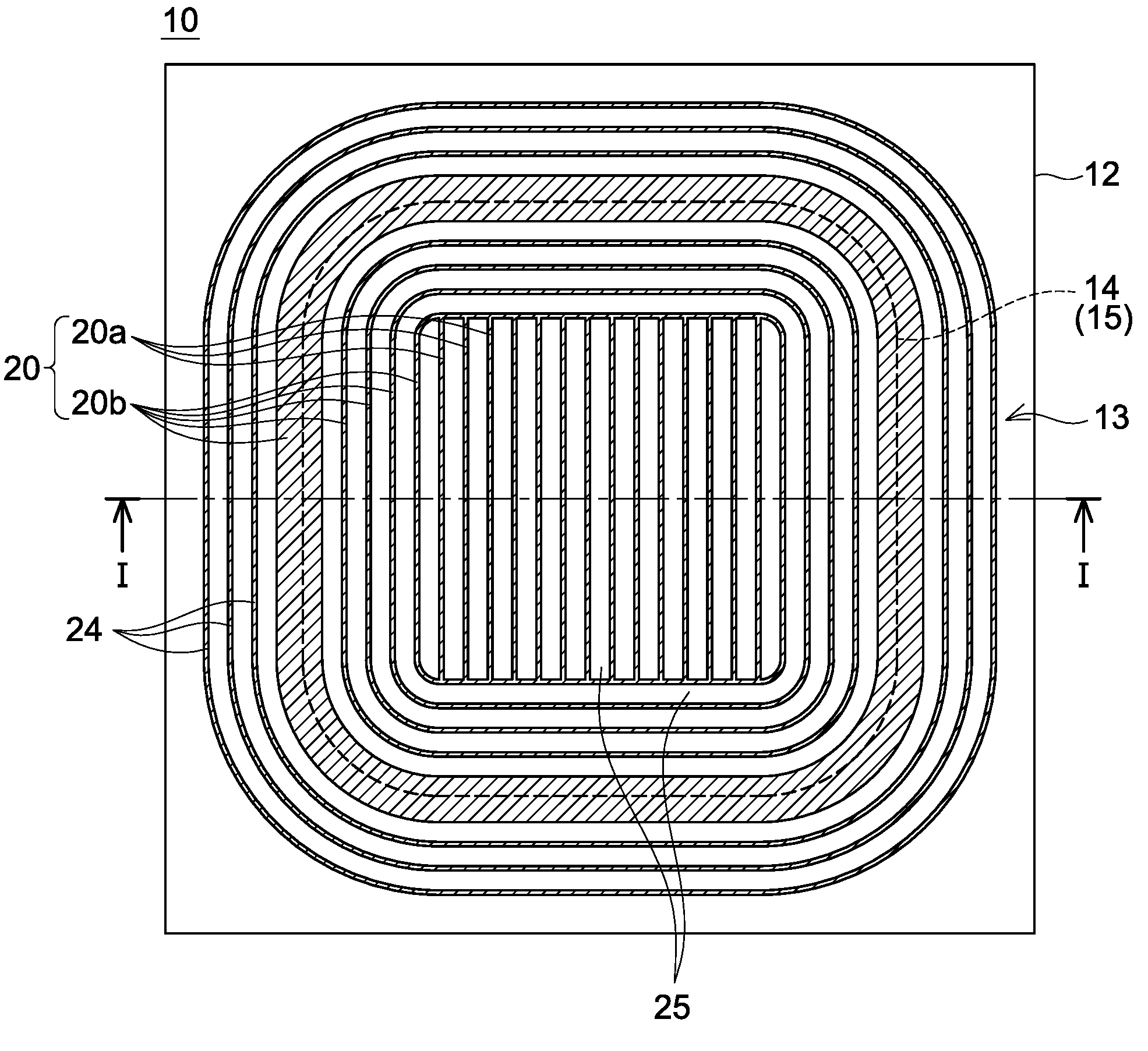

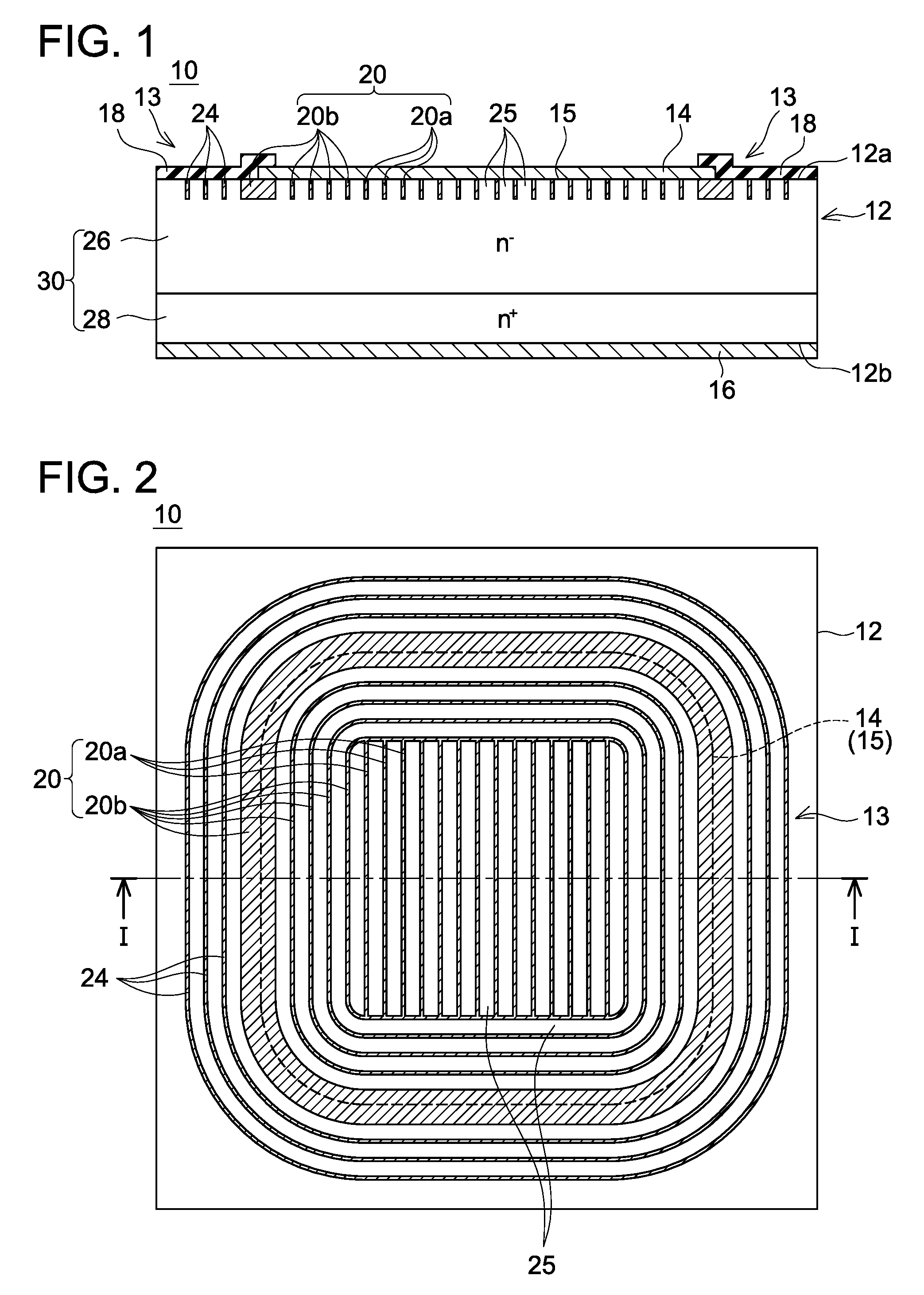

Trench gate power semiconductor device and method for manufacturing same

ActiveCN103250254AImprove reverse withstand voltageIncrease impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceEngineering

A trench gate power semiconductor device (100) of the present invention is provided with: an n--type drift layer (114); a p-type body layer (120); a groove (124); an n+-type source region (132); a gate insulating film (126) that is formed on the inner peripheral surface of the groove (124); a gate electrode film (128) that is formed on the inner peripheral surface of the gate insulating film (126); and a source electrode layer (136) that is formed to be in contact with the source region (132), while being insulated from the gate electrode film (128). In the drift layer (114), a region sandwiched between two adjacent grooves (124) is provided with a p-type buried region (140) that is in contact with the body layer (120) and extends deeper than the grooves (124). In the buried region (140), the depth position at which the p-type impurity concentration is maximum is located deeper than the midway between the bottom surface (P2) of the body layer (120) and the bottom surface (P3) of the buried region (140). This trench gate power semiconductor device (100) has high reverse breakdown voltage and further lower on-resistance.

Owner:SHINDENGEN ELECTRIC MFG CO LTD

High-voltage LDMOS (landscape diffusion metal oxide semiconductor) device

InactiveCN102157560ALower forward conduction resistanceImprove reverse withstand voltageSemiconductor devicesElectrical resistance and conductanceLDMOS

The invention relates to a high-voltage LDMOS (landscape diffusion metal oxide semiconductor) device which comprises a substrate, an epitaxial layer, a drift region, a drain region, a source region and at least one pair of n-type semiconductor regions and p-type semiconductor regions, wherein the epitaxial layer is positioned above the substrate; the drift region is positioned on one side, close to the drain region, of the epitaxial layer, and the lower surface of the drift region is coincided with the lower surface of the epitaxial layer; the drain region and the source region are positioned at two ends of the LDMOS device; at least one pair of the n-type semiconductor regions and the p-type semiconductor regions are arrayed alternatively, pass through the lower surface of the epitaxial layer on the border surface of the substrate and the epitaxial layer; the border surface of the n-type semiconductor regions and the p-type semiconductor regions is in parallel with the surface voltage drop direction of a power device in working; and the n-type semiconductor regions and the p-type semiconductor regions are arrayed closely, thus a PN junction is formed. The invention has the beneficial effects that the n-type semiconductor regions and the p-type semiconductor regions provided by the invention are named a bulk reduced surface field layer, and the contradiction of improving the reverse withstand voltage and reducing the positive conduction resistance of the existing LDMOS device is solved effectively by the LDMOS device with the bulk reduced surface field layer.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

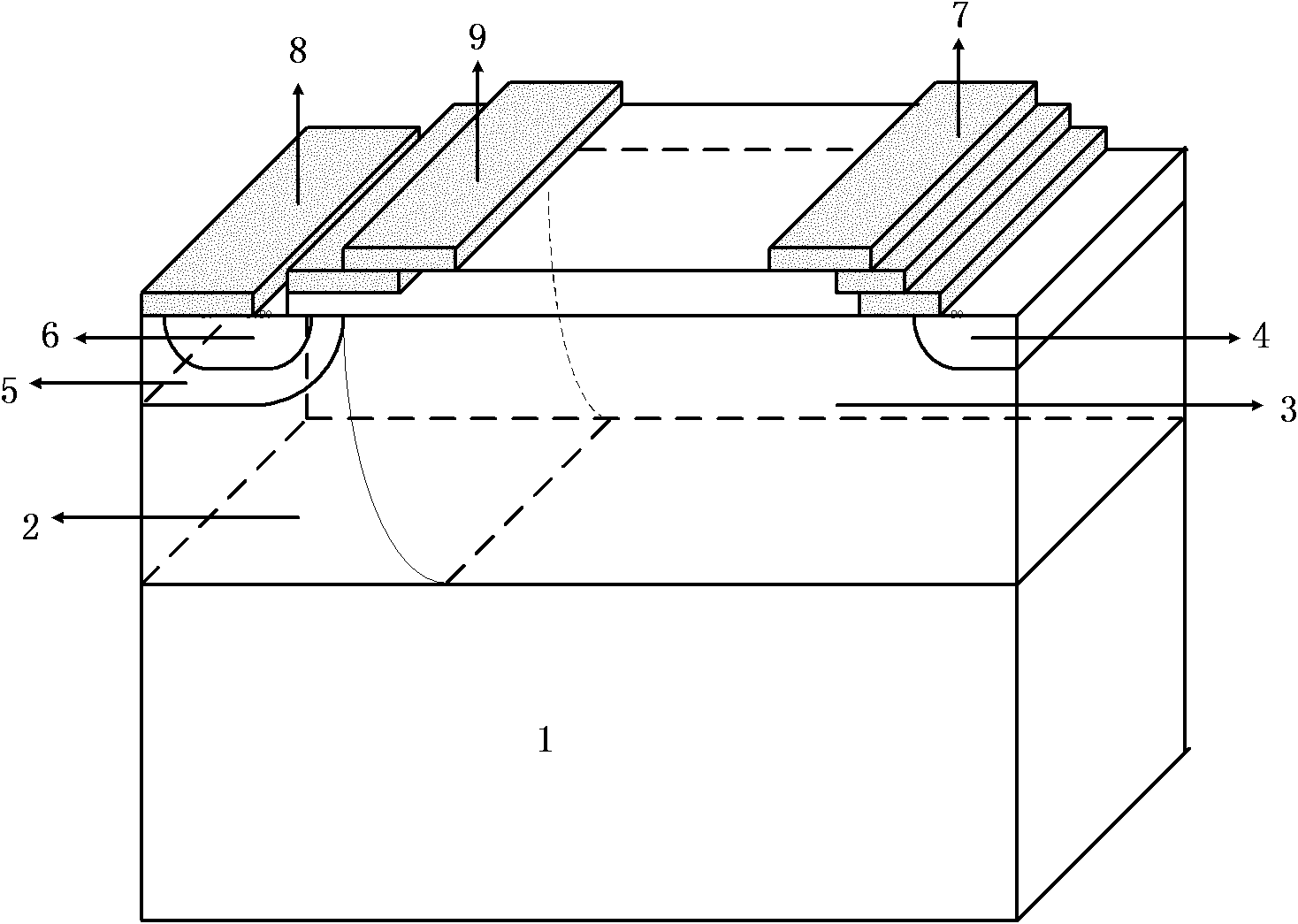

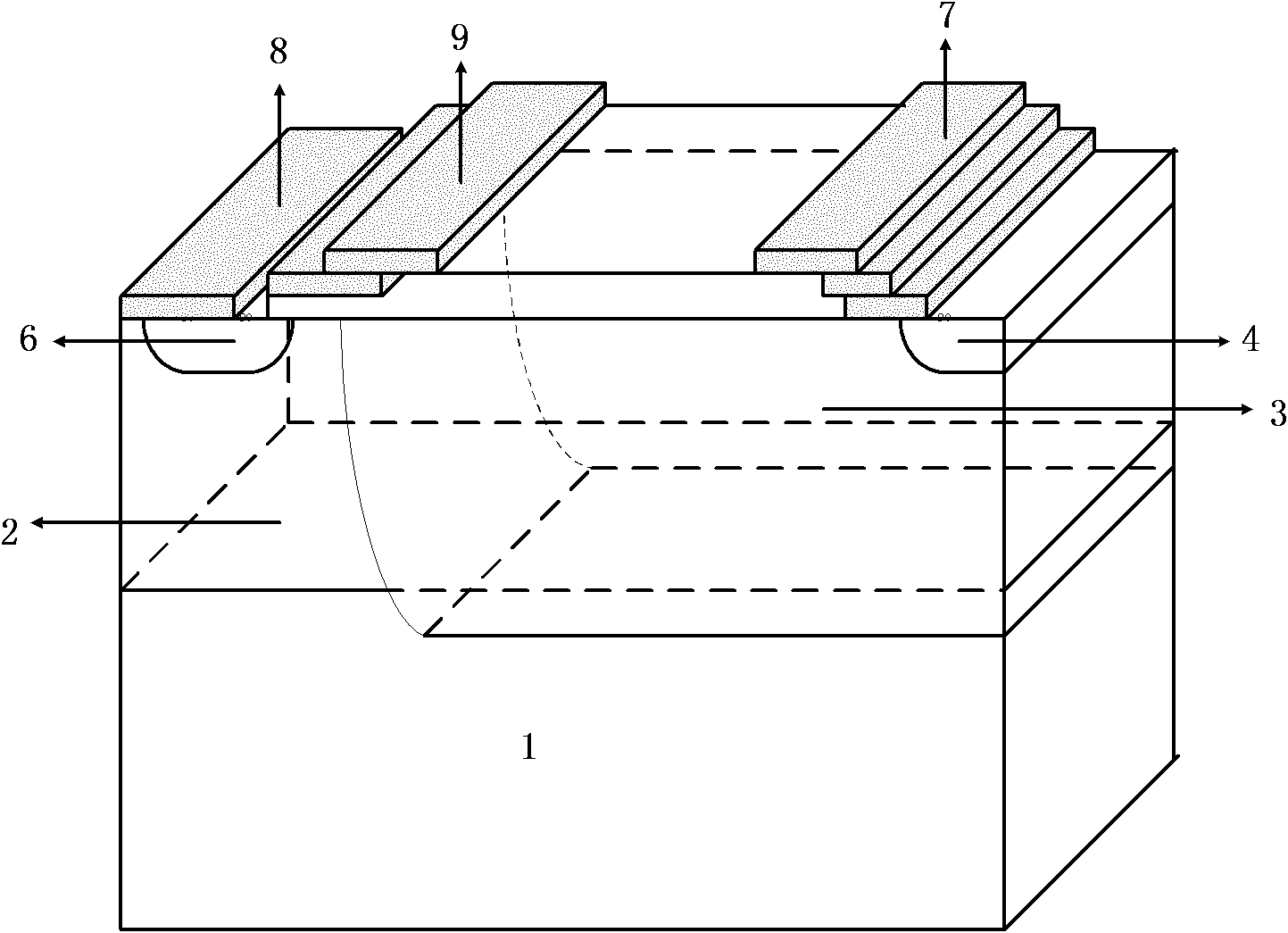

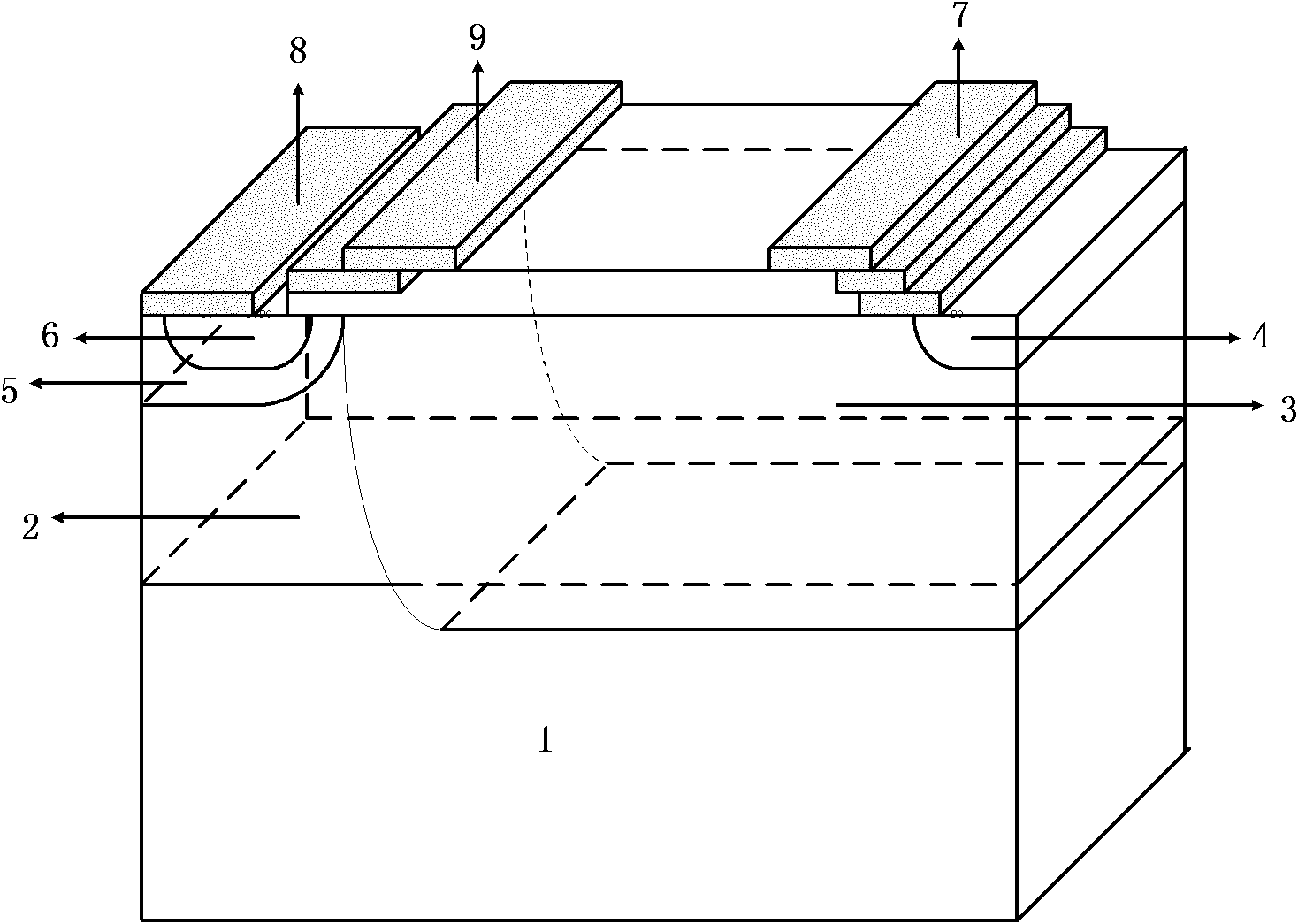

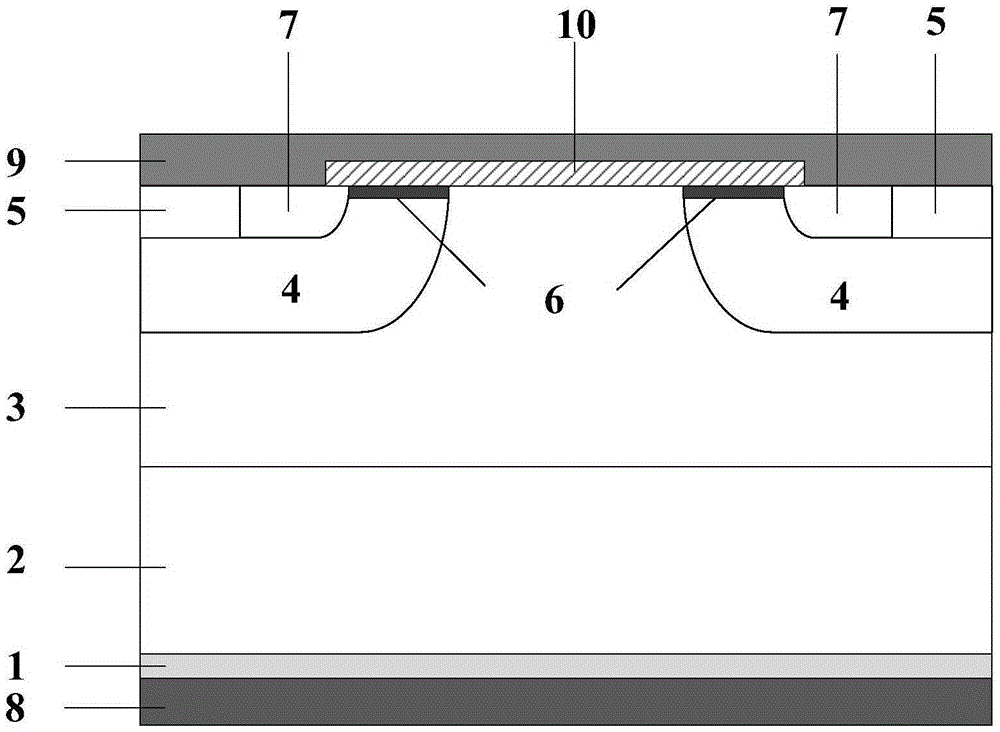

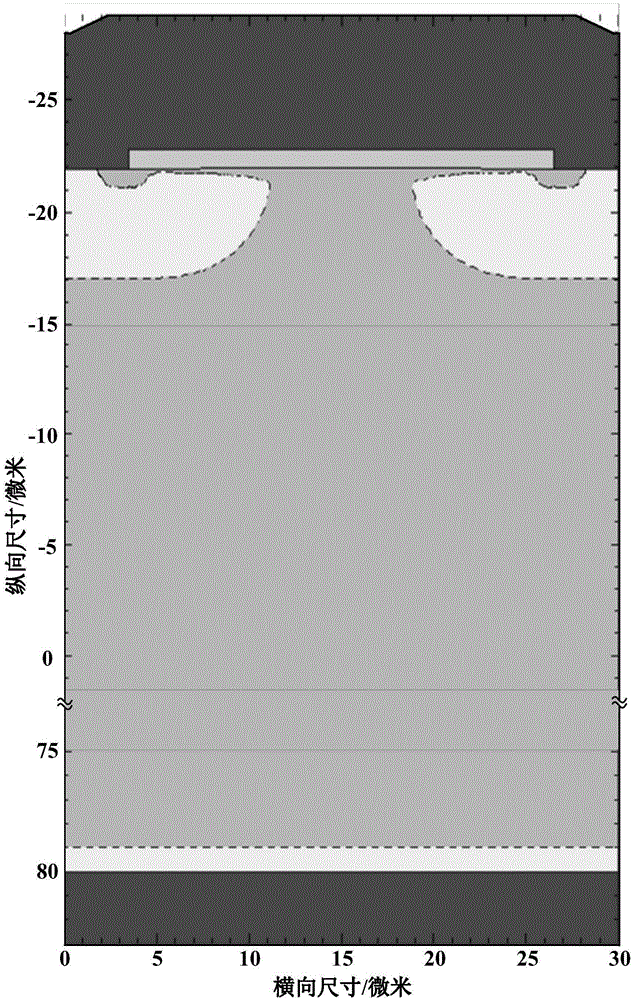

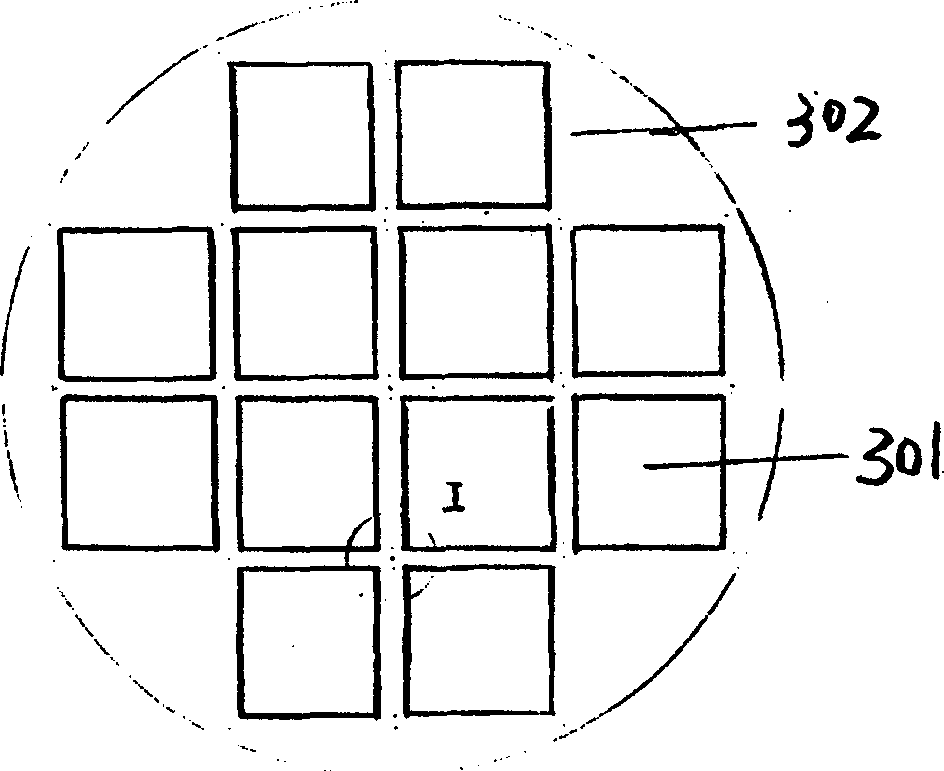

Semiconductor device and manufacturing method thereof

InactiveCN105405873AIncrease current densityImprove reverse withstand voltageTransistorElectron currentSemiconductor materials

The invention discloses a semiconductor device and a manufacturing method thereof, and belongs to the technical field of semiconductors. The semiconductor device comprises a plurality of cells which are the same in structure and are sequentially connected with one another, wherein each cell comprises an N-type doped substrate, an N-type lightly doped epitaxial layer, a diffused P-type well region, a first P-type heavily dope region, an N-type heavily dope region, an oxidation layer, a metal cathode, a second P-type heavily doped region and a metal anode; the N-type lightly doped epitaxial layer is located on the N-type doped substrate; the diffused P-type well region is located in the N-type lightly doped epitaxial layer; the first P-type heavily dope region and the N-type heavily dope region are located in the diffused P-type well region; the oxidation layer is located on the upper surfaces of the N-type lightly doped epitaxial layer and the diffused P-type well region; the metal cathode covers the overall cells; and the second P-type heavily doped region and the metal anode are located on the lower surface of the N-type doped substrate. According to the semiconductor device disclosed by the invention, a semiconductor material which is opposite to the substrate in the doping type is injected into the back surface of the substrate, so that, on one hand, holes are injected into the N-type substrate and the N-type lightly doped epitaxial layer through P-type heavily doped back injection, the semiconductor device has two carrier currents, namely a hole current and an electron current, and the current density of the device is increased; and on the other hand, the reverse withstand voltage of the device can be improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

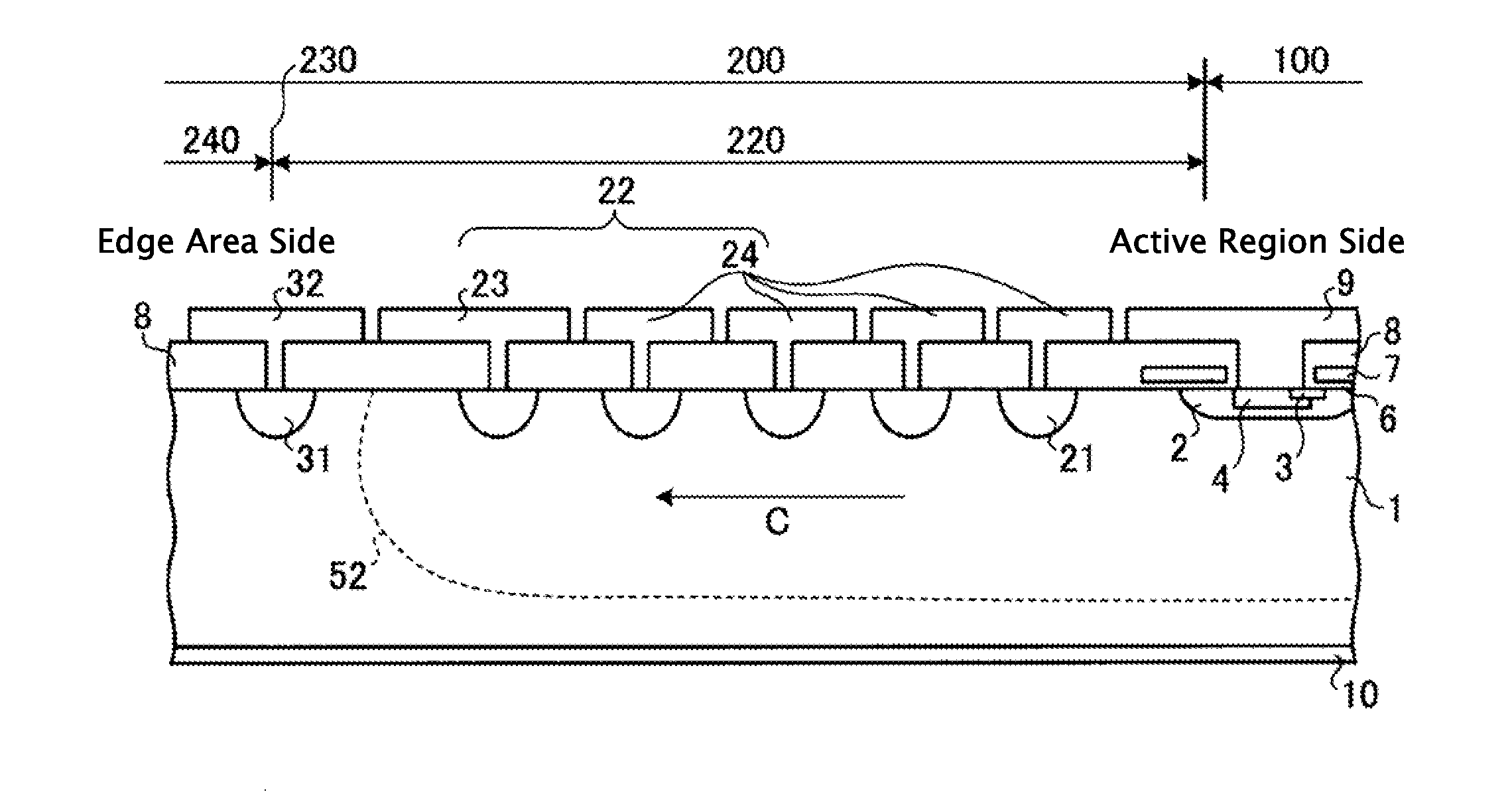

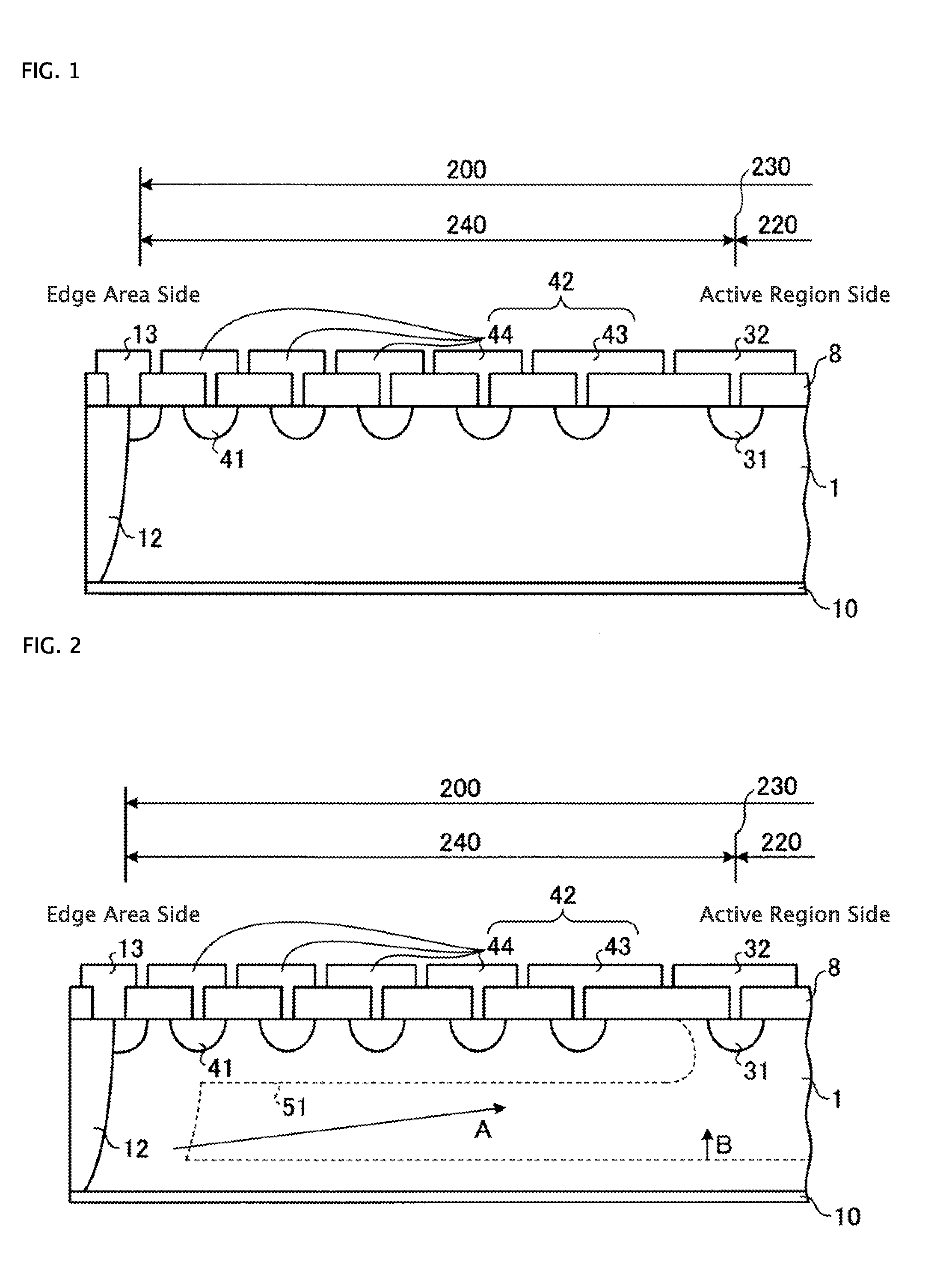

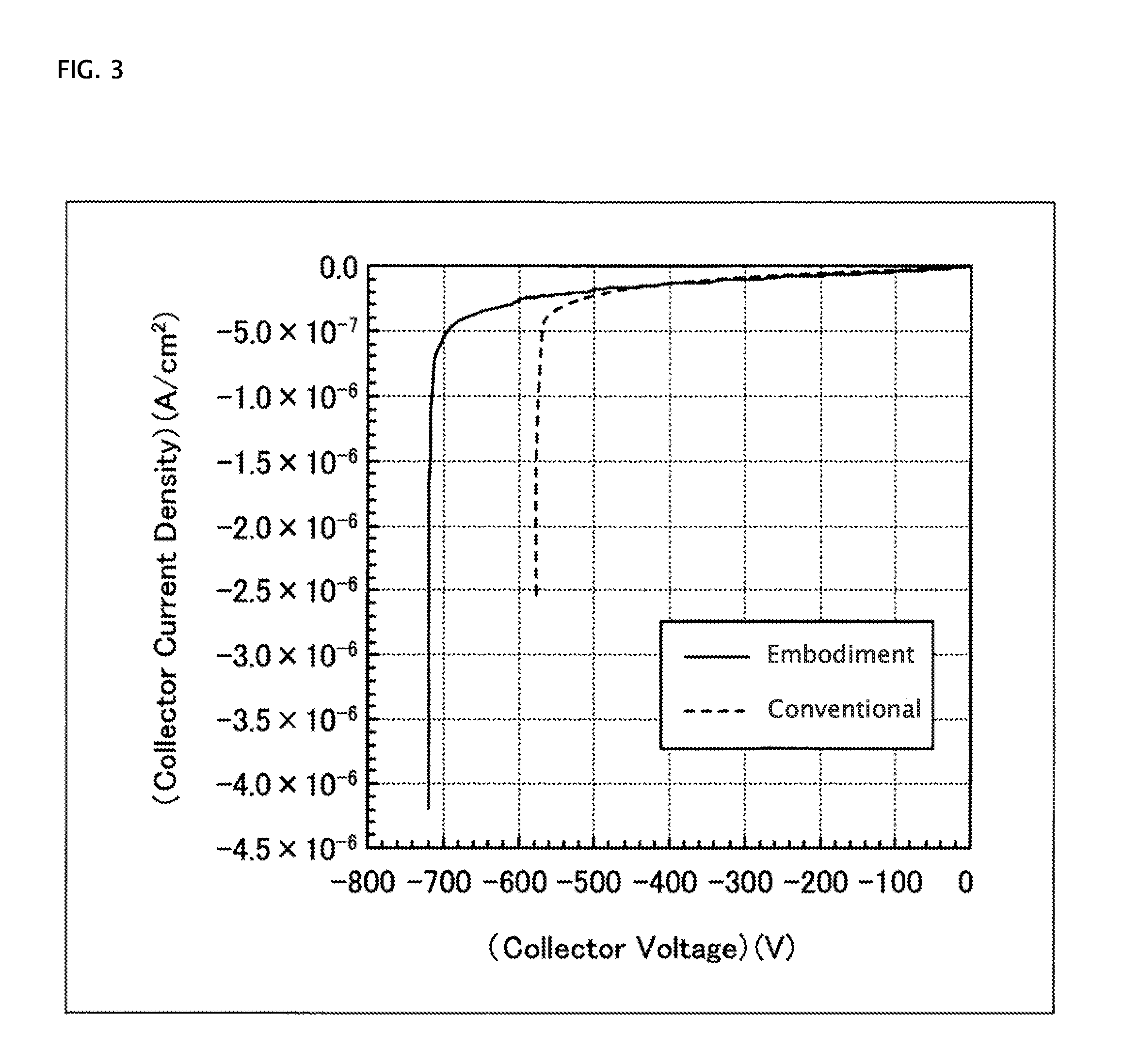

Semiconductor device

Owner:FUJI ELECTRIC CO LTD

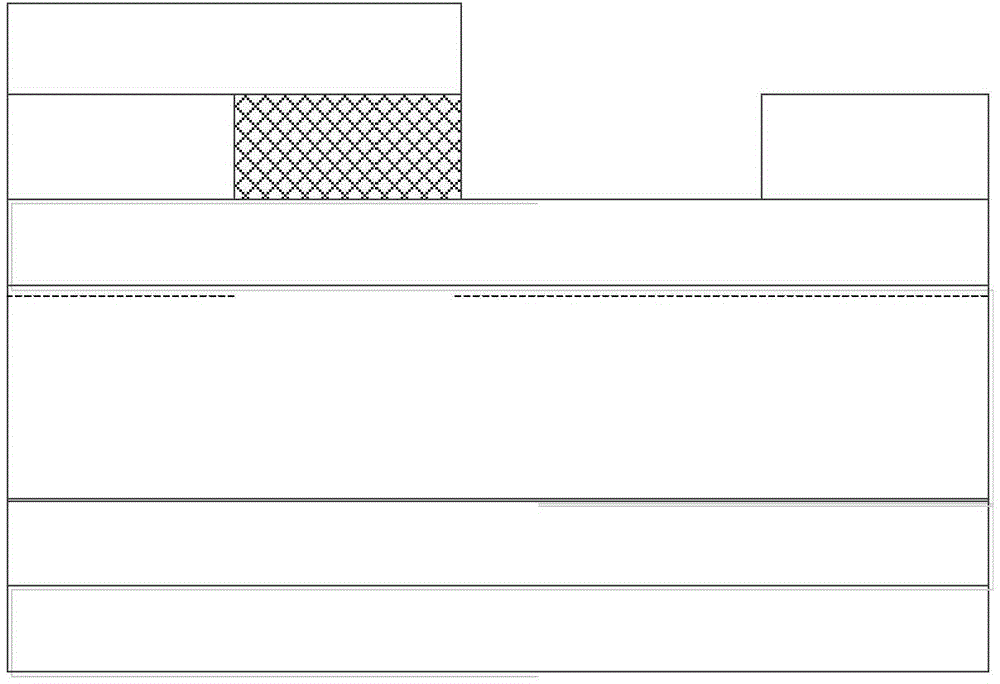

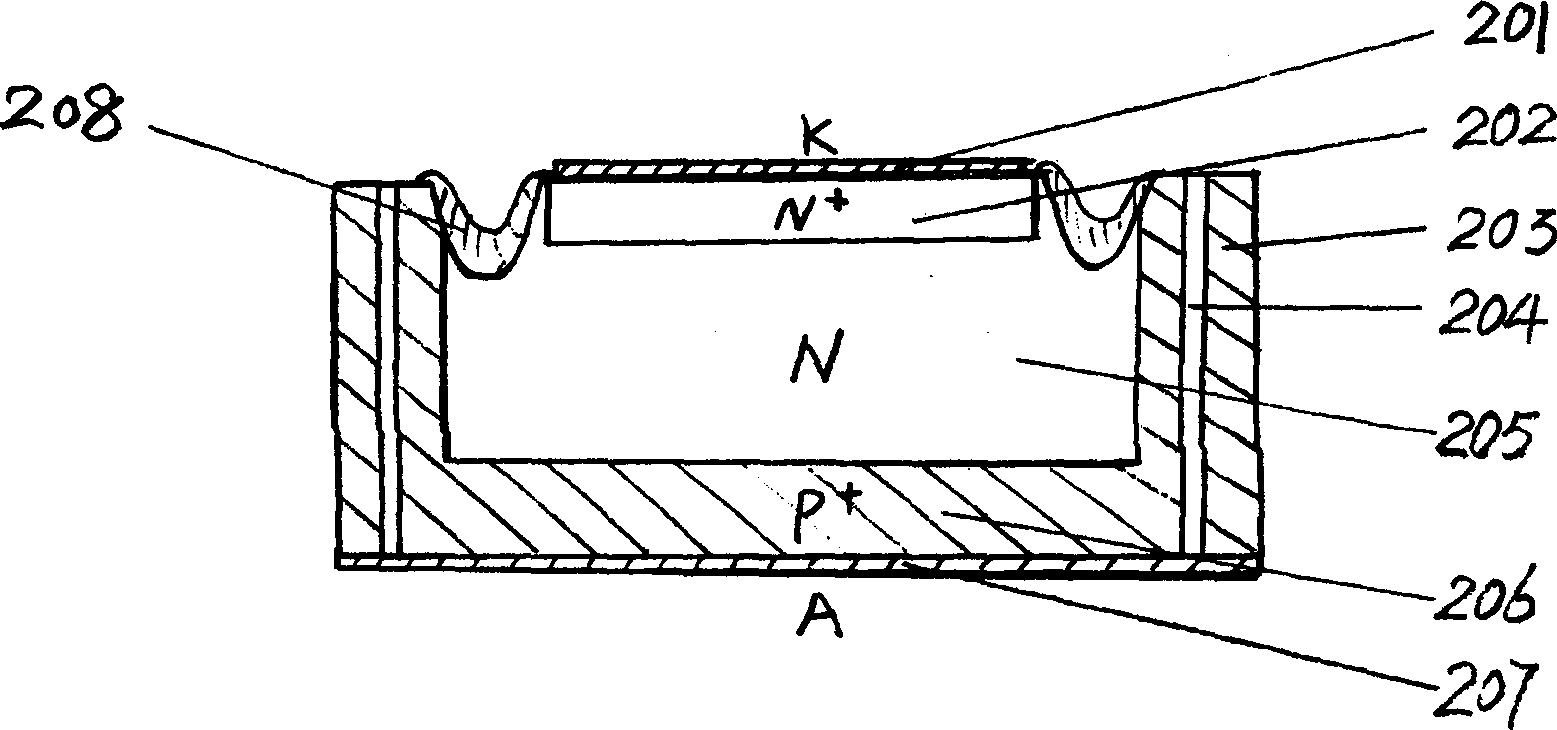

GPP rectification chip based on reverse grooving technology

InactiveCN104269398AWidening of the pressure-resistant area on the surfaceImprove reverse withstand voltageSemiconductor/solid-state device detailsSolid-state devicesVoltEngineering

The invention provides a new product of a GPP rectification chip based on the reverse grooving technology. The electric polarity of the GPP rectification chip is opposite to that of a conventional GPP rectification chip, the face, with a smaller area, in the up direction of the chip is the N type and the negative pole of the new product, and the face, with a larger area, in the down direction of the chip is the P type and the positive pole of the new product. The electric heating property of the new product is better than that of the conventional product, and the reveres withstand voltage is higher than 2000 volts. The production cost of the new product is not higher than that of the conventional product, so the new product can be produced through on-line equipment, instruments and materials of the conventional product, and requirements of customers for different polarities of rectification chip products can be met.

Owner:HUANGSHAN GUIDING ELECTRONICS

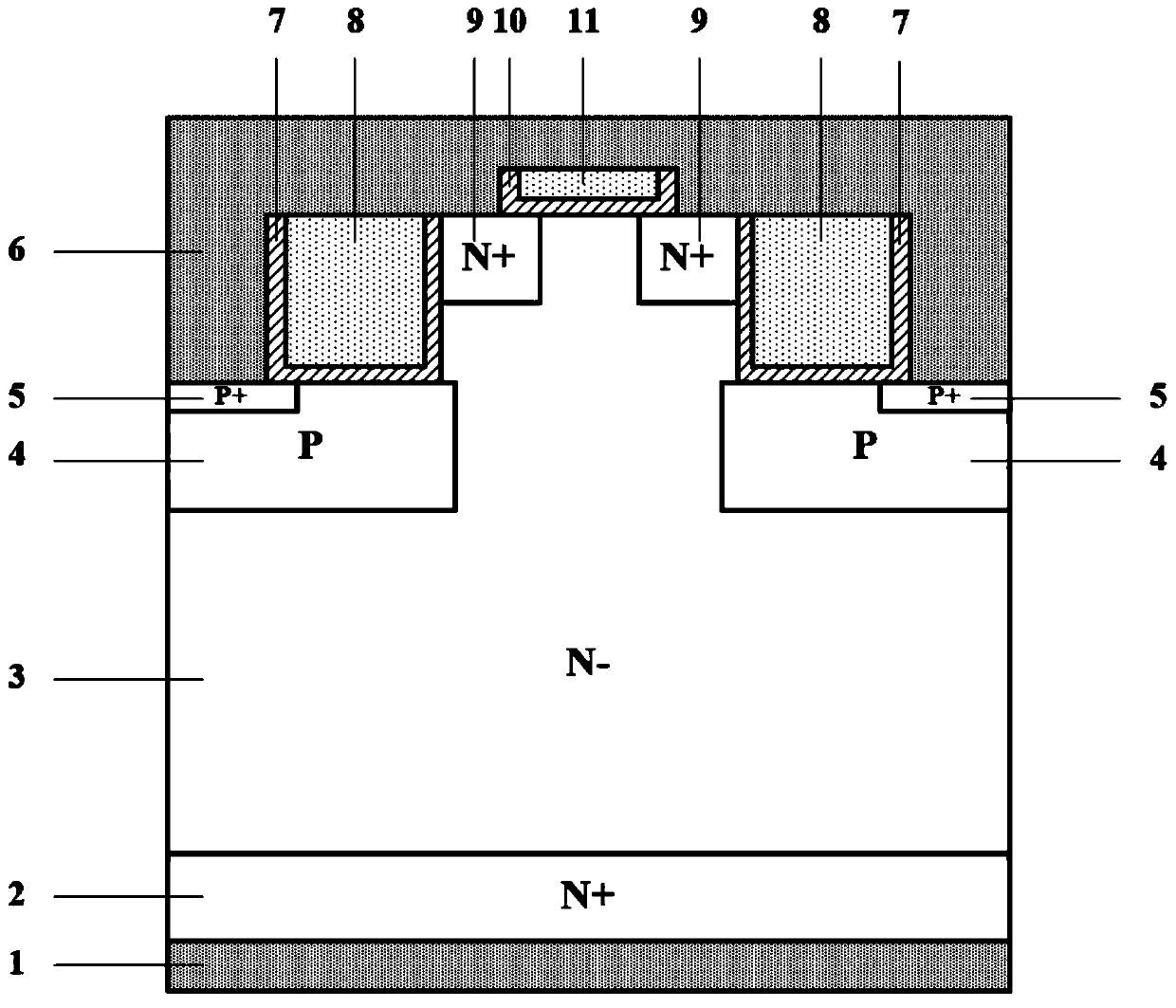

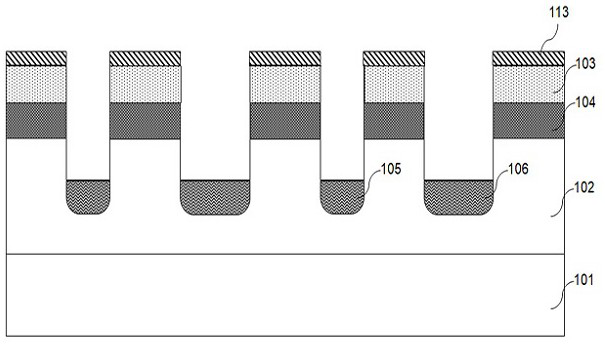

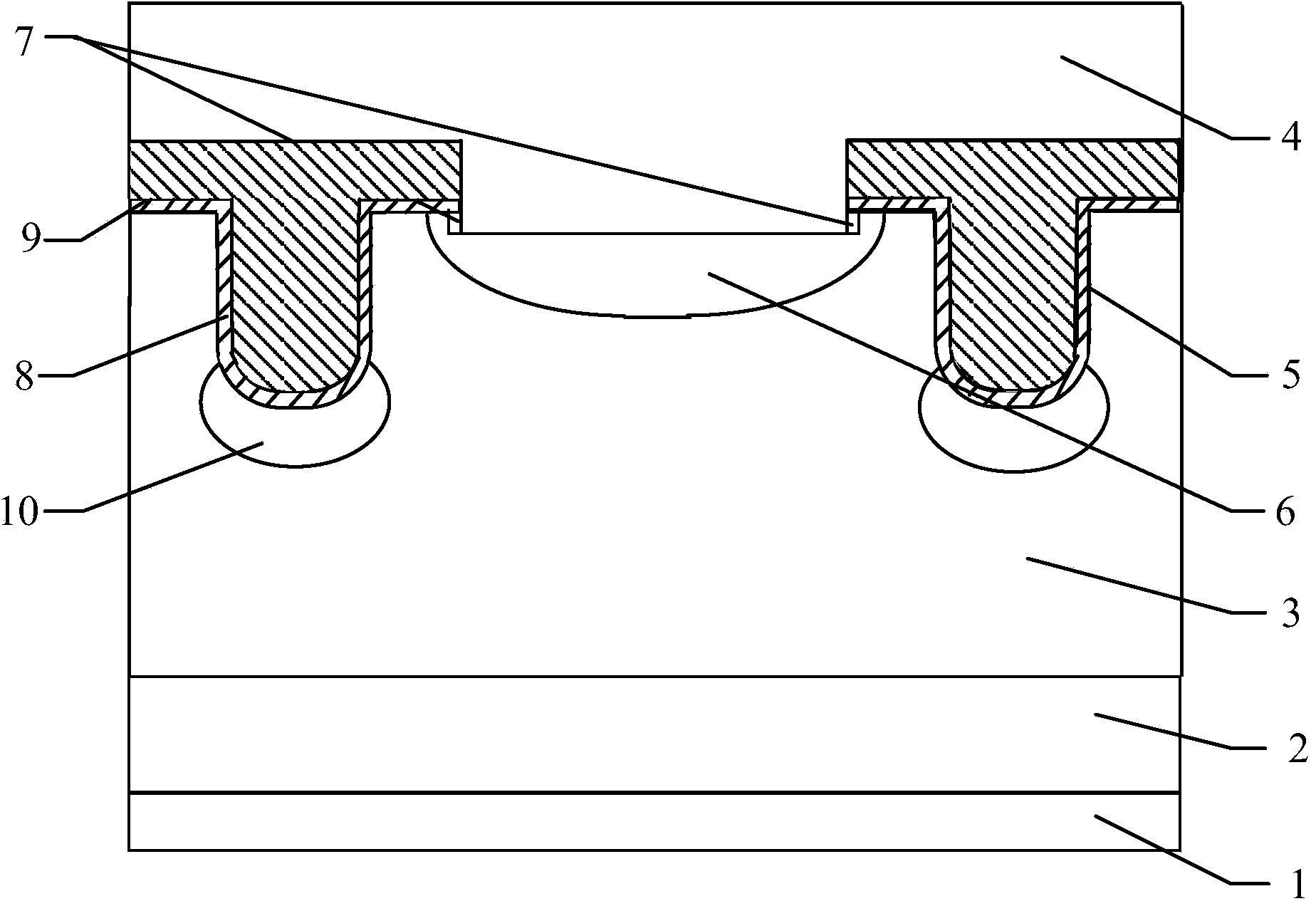

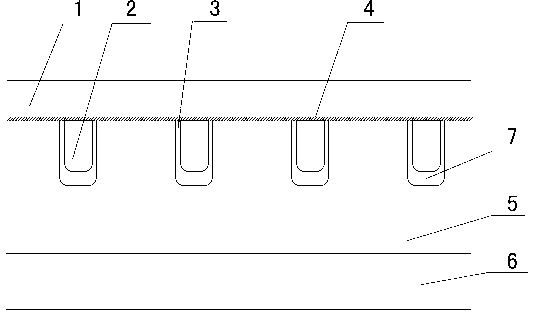

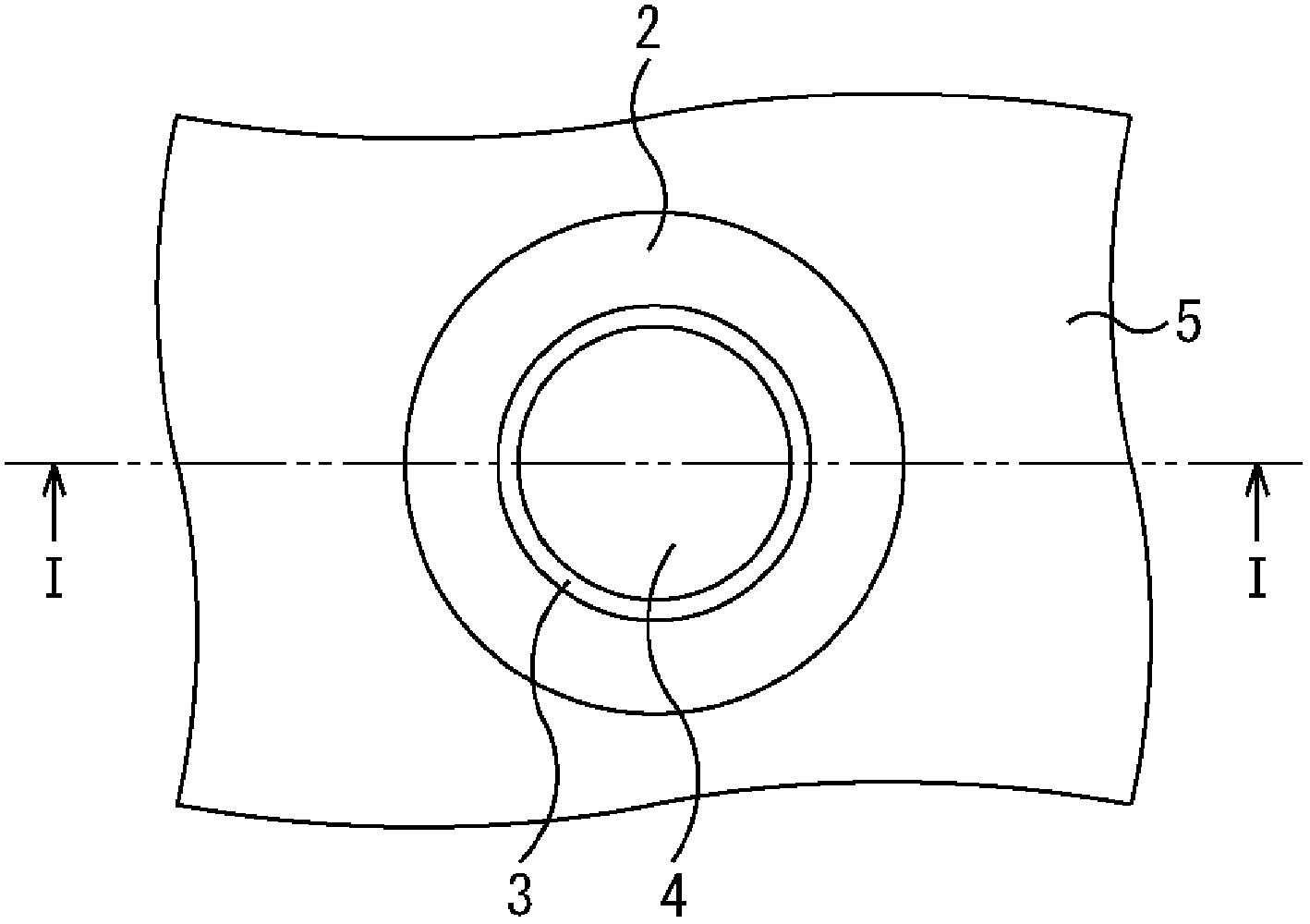

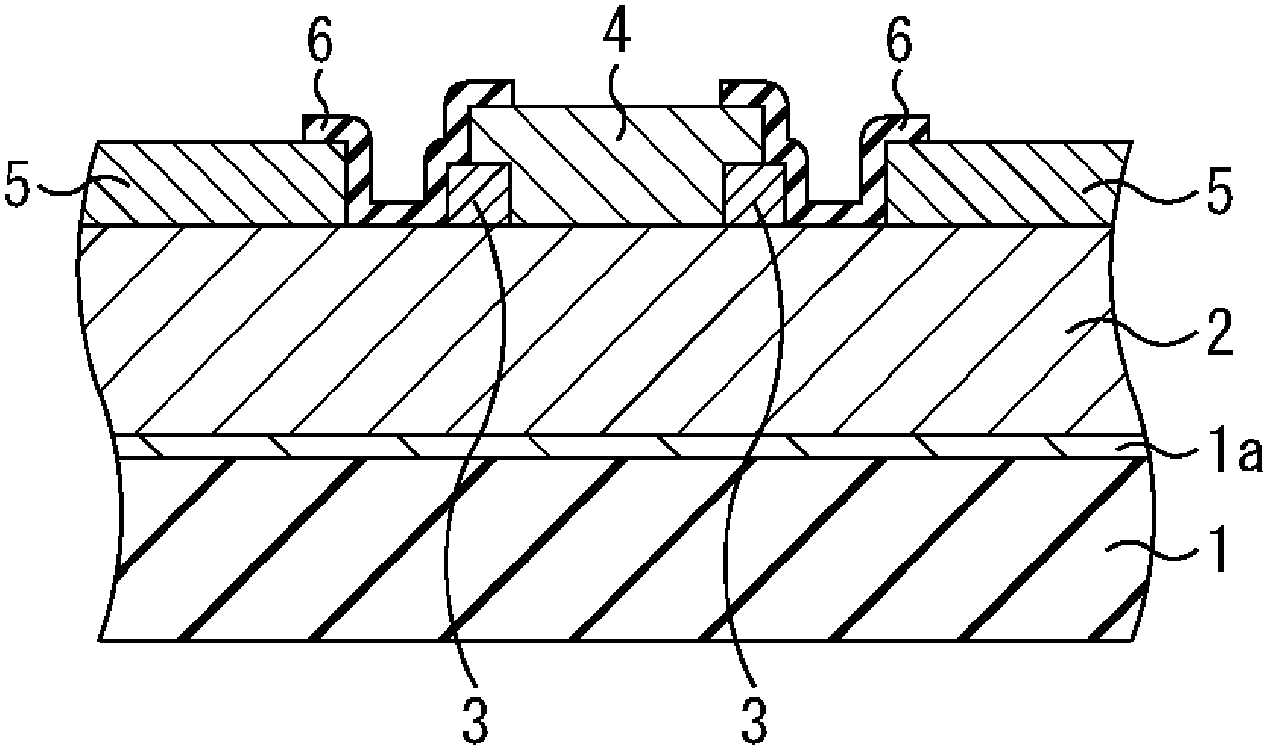

MOS super barrier rectifier device and manufacturing method thereof

InactiveCN103325839AGuaranteed depthLow costSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringImpurity

The invention discloses an MOS super barrier rectifier device which is provided with a groove, a second conduction type injection region wraps the groove, the structure can replace a protecting ring structure, a primary photomask is removed compared with the prior art, the depth of the second conduction type injection region is guaranteed, and good pressure proof functions are performed. In addition, the invention further discloses a manufacturing method. According to the method, after the groove is formed, the second conduction type injection region is injected and formed by carrying out heat treatment on activator impurities, the photomask needed when a protecting ring is formed and the processes of long-time trap pushing are removed, cost is saved, the damage, caused by injection by using macro-energy, to the surfaces of devices is avoided, transverse diffusion distance of micro-energy injection region is small, and the control over the length of a channel region and the distance between adjacent second conduction type injection regions is better.

Owner:ZHANGJIAGANG CASS SEMICON

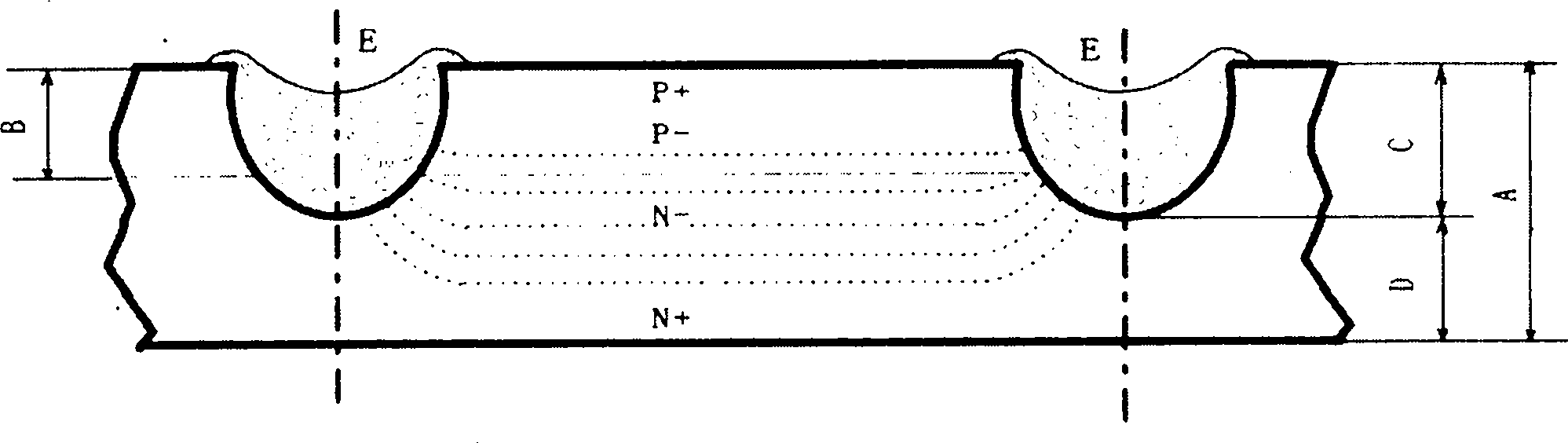

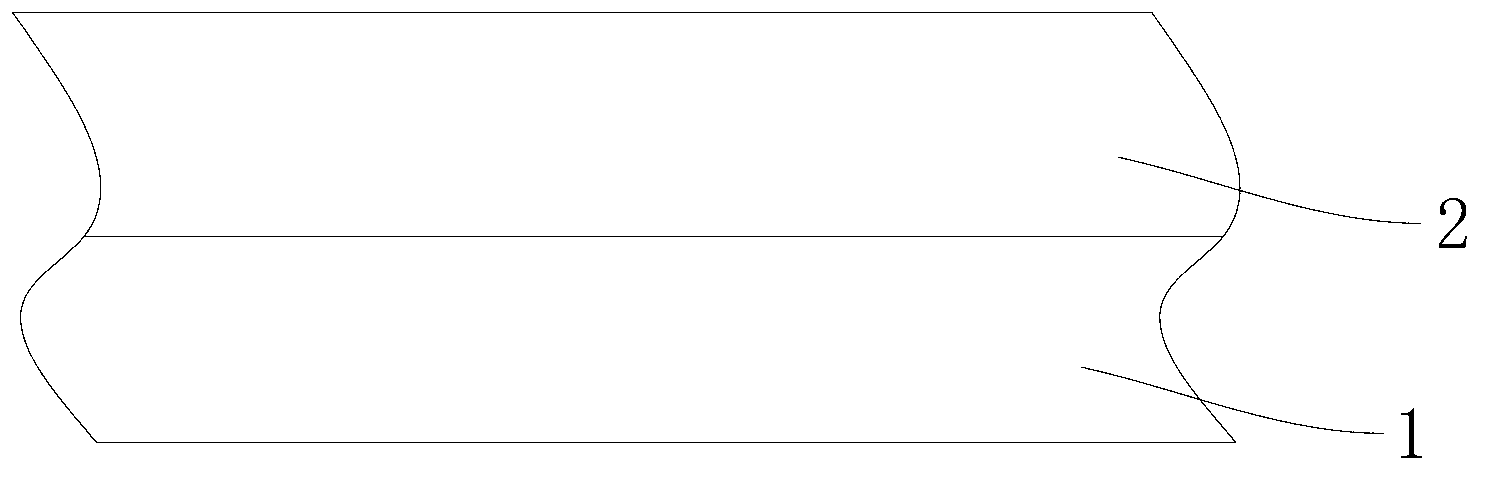

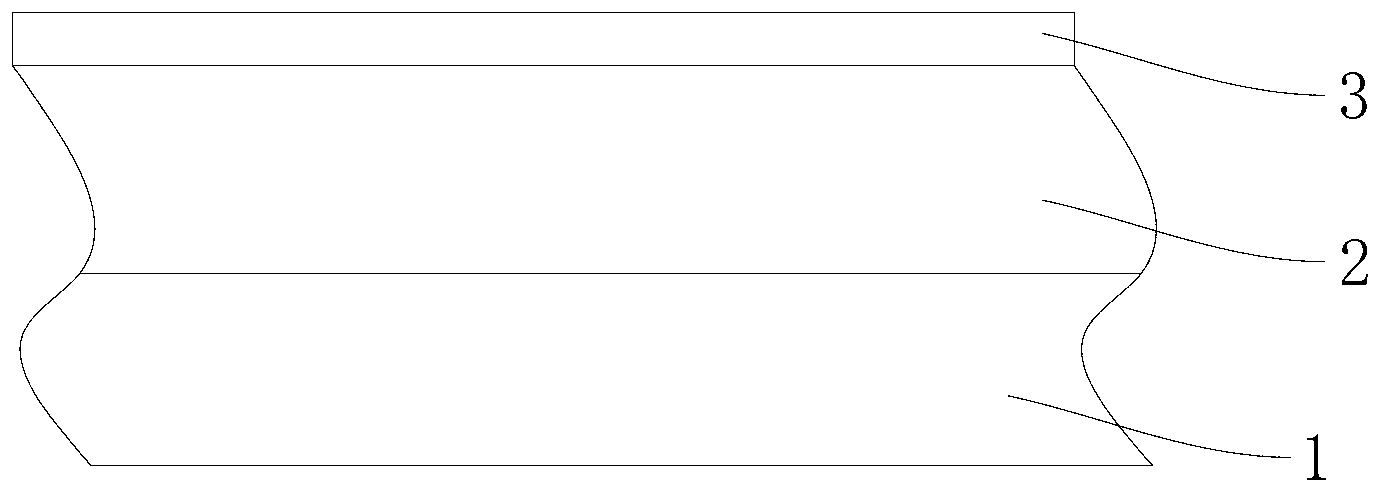

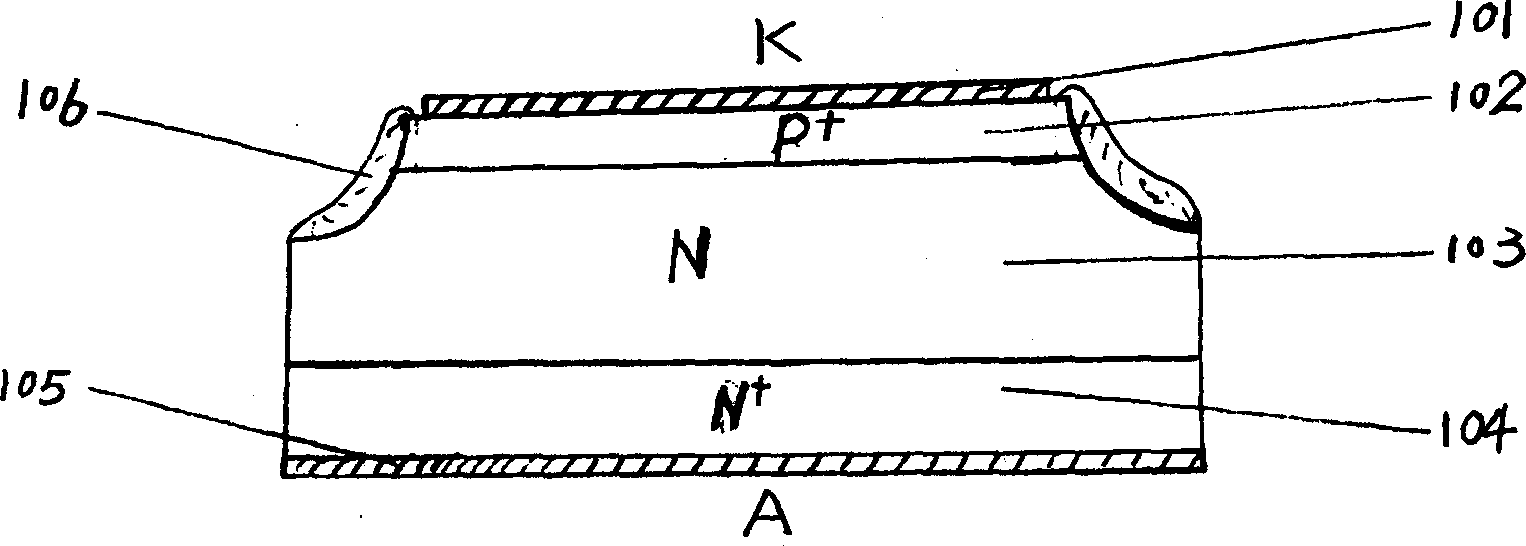

Rectifier diode, chip special for producing rectifier diode and producing method

ActiveCN1783516AAccelerateNot easy to short circuitSemiconductor/solid-state device manufacturingSemiconductor devicesBoron diffusionRectifier diodes

This invention discloses a commutation diode, chips especially for manufacturing the diodes and the manufacturing method, in which, said commutation diode is composed of a shell, a chip and a lead out wire, in which, the chip includes a long base region N, a phosphor diffusion region N area, a heavy boron diffusion region P area and a groove passive mesa, the long base region is in the middle of the chip, cathode K is on the phosphor diffusion region, anode A is on the heavy boron diffusion region, the upper part is the P diffusion region, the lower part is the B diffusion region, isolation walls are surrounding the chip with vertical through laser holes in the diameter smaller than 200mum and the inter-distance of 40-400mum and the mesa is between the isolation wall and the cathode K.

Owner:ANHUI PROVINCE QIMEN COUNTY HUANGSHAN ELECTRIC APPLIANCE

Schottky rectifier and making method thereof

ActiveCN104795452AImprove reverse withstand voltageFaster pinch offSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierDepth direction

The invention discloses a Schottky rectifier and a making method thereof. The Schottky rectifier comprises a first conductivity type substrate, a first conductivity type conductive layer formed on the surface of the first conductivity type substrate, at least one trench formed in the first conductivity type conductive layer, side wall oxide layers and bottom oxide layers formed in the trenches, polycrystalline silicon deposited in the trenches and doped with a second conductivity type impurity, and a metal layer formed on the surface of the first conductivity type conductive layer, wherein the doping concentration of the second conductive type impurity changes from high to low from the top to the bottom of the trenches in the depth direction of the trenches. According to the invention, a reverse electric field originally acting on a Schottky barrier quickly leaves a Schottky barrier region and is borne by a depletion layer, so that electric leakage due to original action of the electric field on the Schottky barrier is avoided, and the overall reverse withstand voltage of the device is greatly improved.

Owner:WILL SEMICON (SHANGHAI) CO LTD

Semiconductor device

ActiveUS20110156210A1Improve reverse withstand voltageOscillation suppressionTransistorSolid-state devicesDevice materialBody region

A semiconductor device according to embodiments of the invention includes an n−-type drift region; a p-type base region formed selectively in the surface portion of the drift region; an n+-type emitter region and a p+-type body region, both formed selectively in the surface portion of base region; and an n-type shell region between the drift region and the base region, a shell region surrounding the entire region below base region. The shell region is doped more heavily than the drift region. The shell region contains an n-type impurity at an effective impurity amount of 8.0×1011 cm−2 or smaller. A drift region exhibits a resistivity low enough to prevent the depletion layer expanding from collector region, formed on the back surface of the drift region, toward a shell region from reaching the shell region.

Owner:FUJI ELECTRIC CO LTD

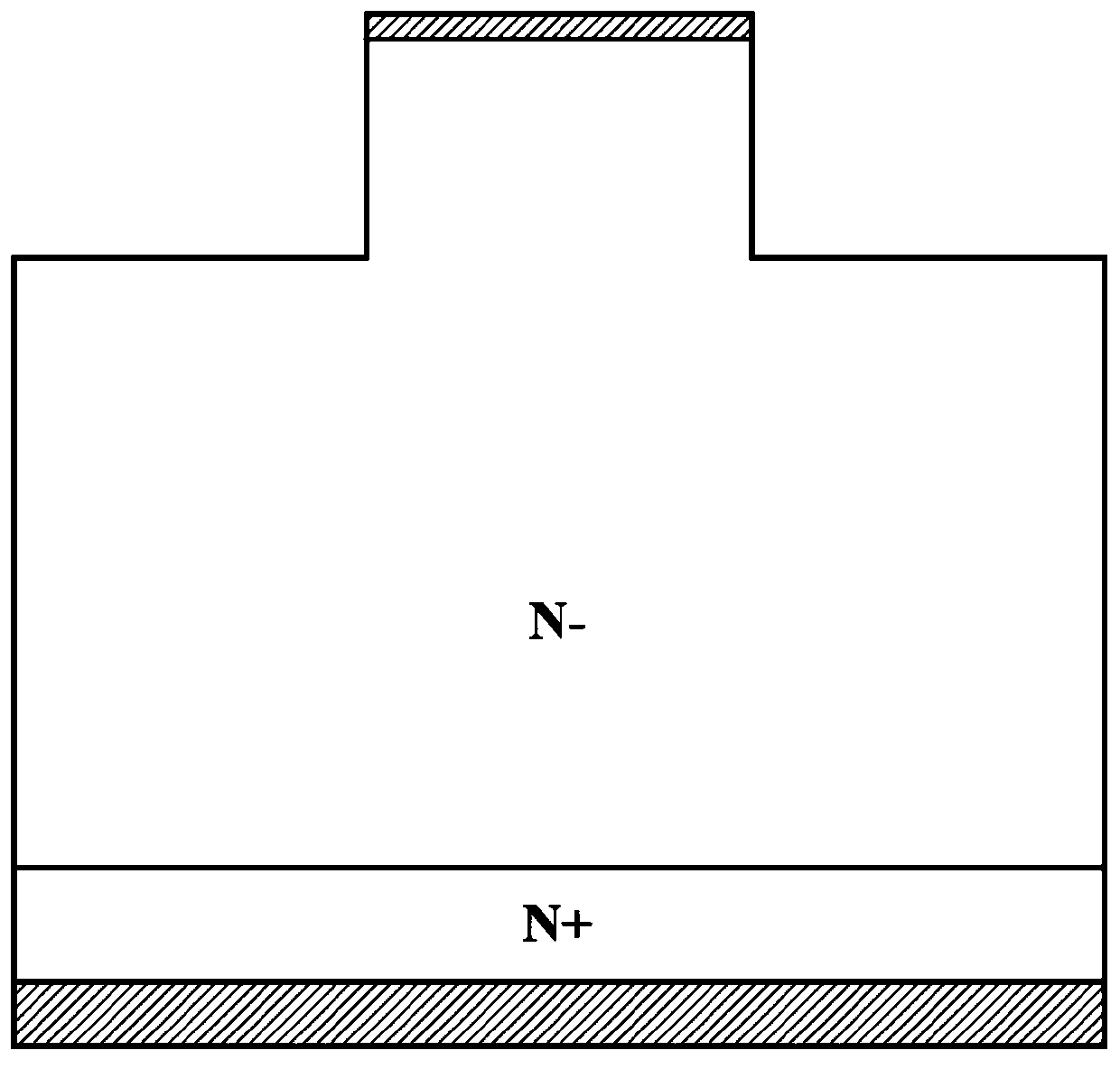

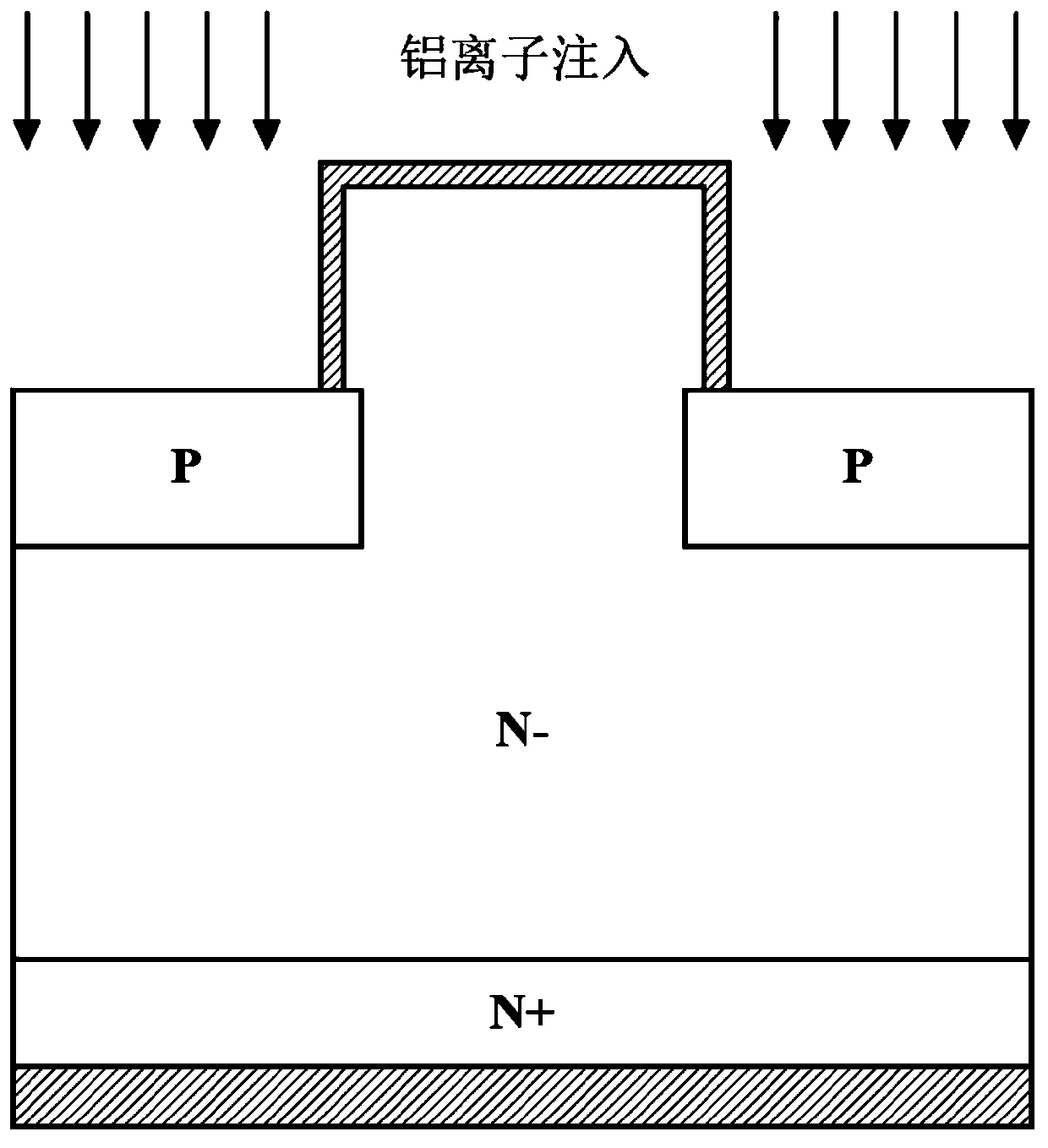

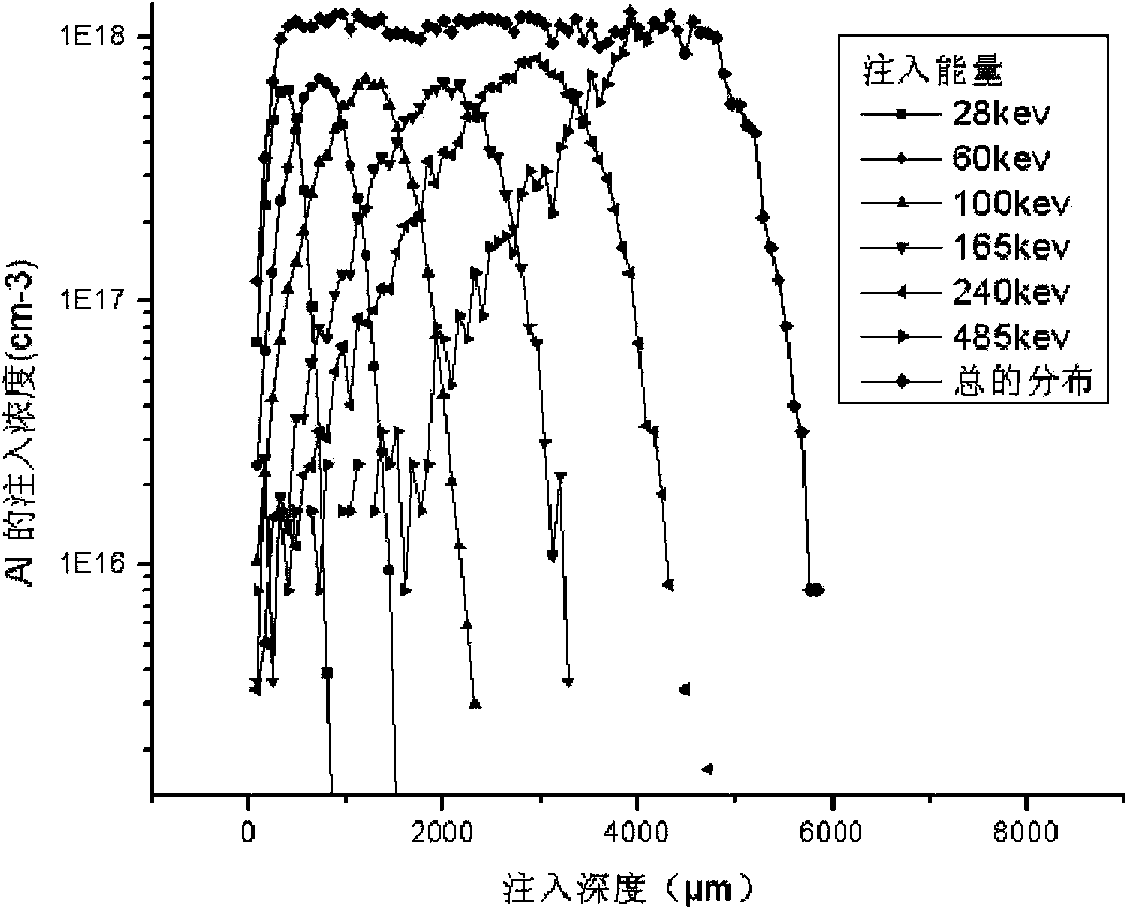

High-voltage-resistant silicon carbide device and preparation method thereof

ActiveCN114420761AImprove reverse withstand voltageLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconMetal electrodes

The invention discloses a high-voltage-resistant silicon carbide device and a preparation method thereof, the high-voltage-resistant silicon carbide device comprises a silicon carbide substrate, a silicon carbide epitaxial layer arranged on the silicon carbide substrate and a drain metal electrode arranged on the back surface of the silicon carbide substrate, and a blocking injection region and a source injection region are sequentially arranged on the silicon carbide epitaxial layer; a plurality of first grooves and second grooves are etched in the silicon carbide epitaxial layer; a gate protection region is arranged at the bottom of the first groove, an oxide layer grows on the surface of the first groove, a gate polycrystalline silicon electrode is arranged on the oxide layer, and an insulating layer covers the gate polycrystalline silicon electrode; the bottom of the second groove is provided with a voltage-withstanding injection region, and the second groove is provided with a polycrystalline silicon filler. And the source electrode injection region and the insulating layer are covered with a source electrode metal electrode, so that the problems of low reverse voltage and complex process in the prior art are solved.

Owner:成都功成半导体有限公司

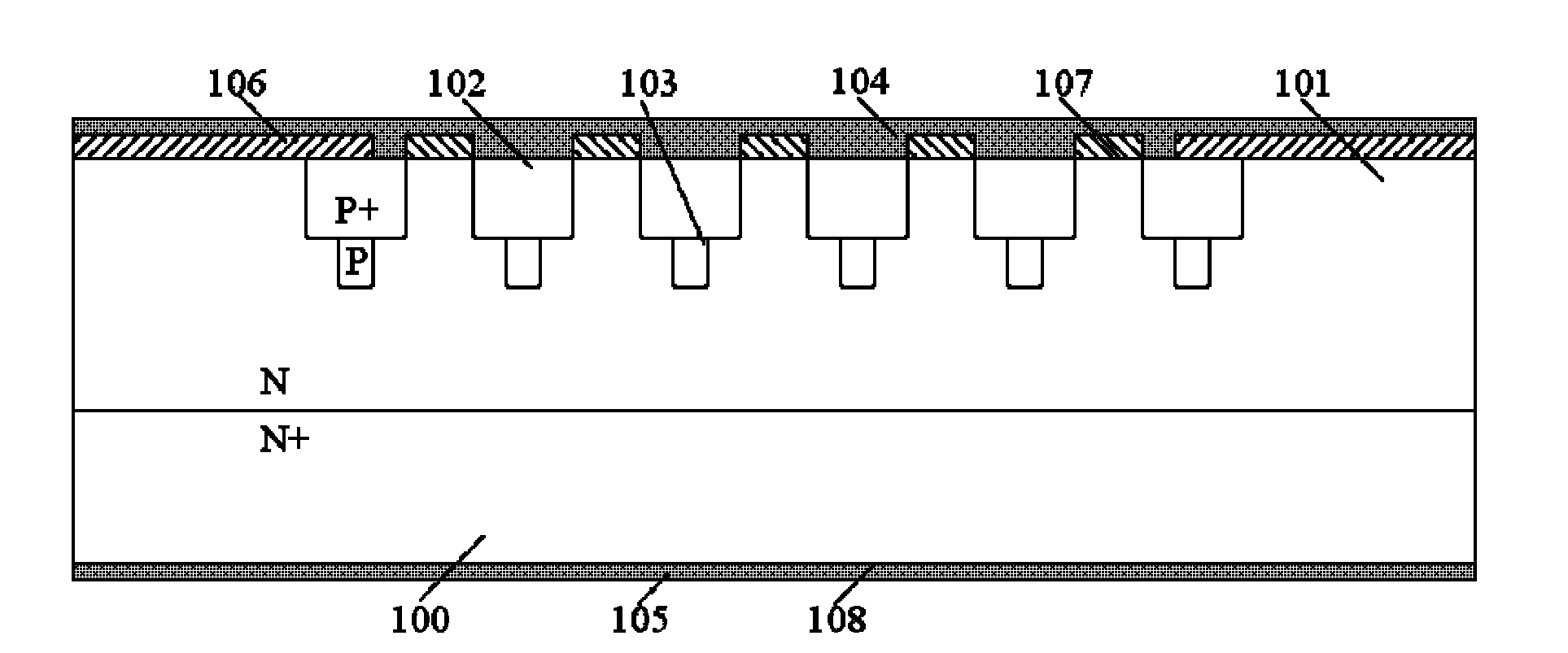

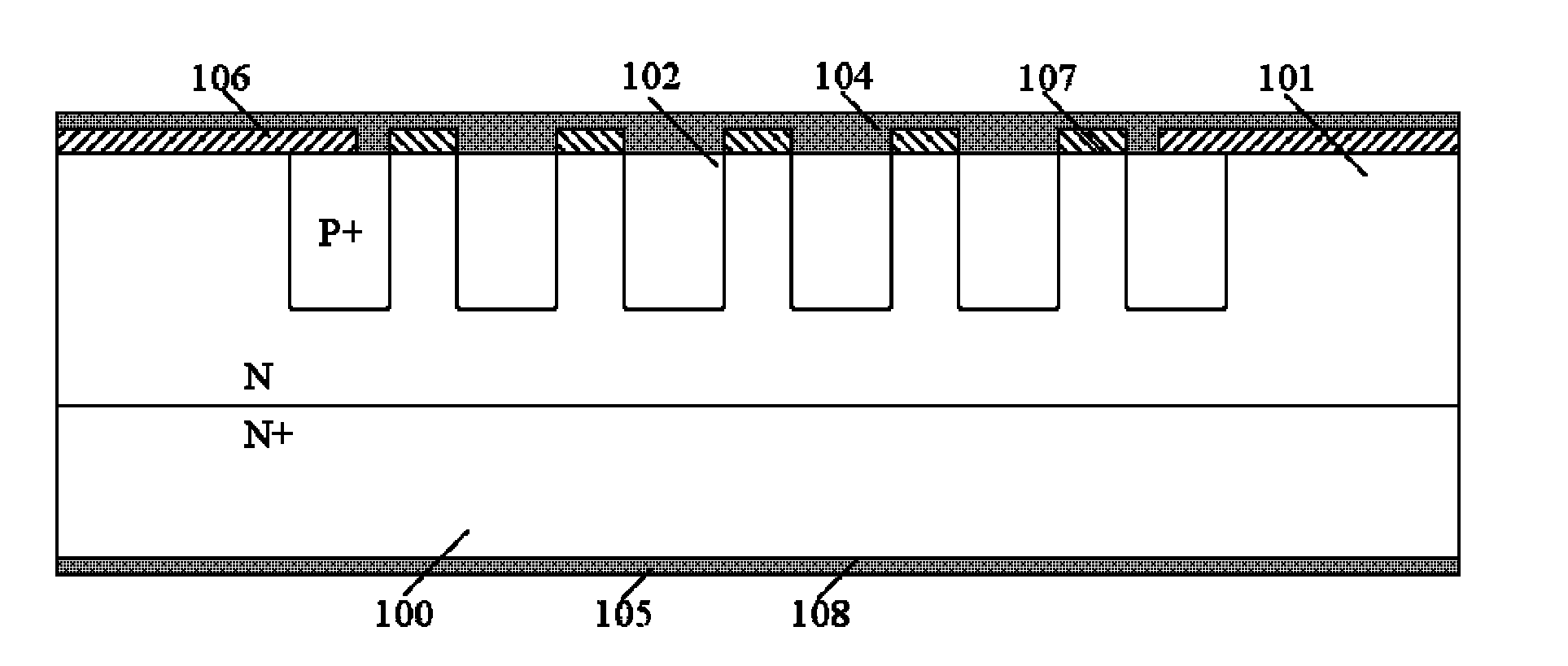

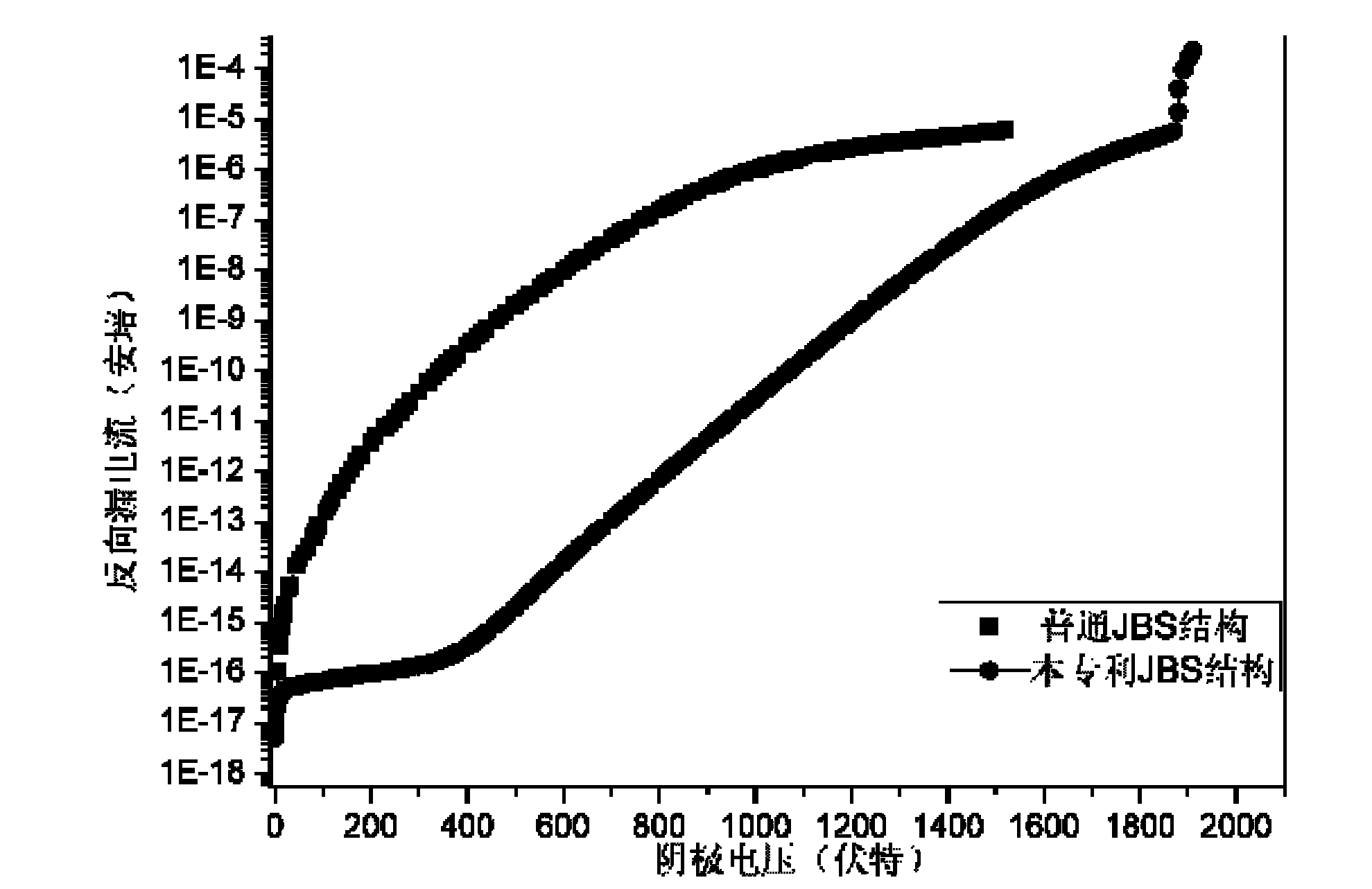

Schottky diode controlled by junction barrier having superposed P<+>-P structure

InactiveCN102208456AEasy to meet application requirementsImprove reverse withstand voltageSemiconductor devicesCapacitanceElectronic systems

The invention provides a schottky diode controlled by a junction barrier having a superposed P<+>-P structure. The schottky diode comprises an N<+> type substrate zone (100), an N type drift region (101), P<+> portions of the superposed P<+>-P structure (102), an anodic electrode (104), a cathodic electrode (105), a silicon dioxide layer (106), a schottky contact (107), and an ohmic contact (108). Besides, the schottky diode also includes P portions of the superposed P<+>-P structure (103), wherein the P<+> window portions of the superposed P<+>-P structure (102) is on the P window portions of the superposed P<+>-P structure (103). According to the invention, before the P<+> portions of the superposed P<+>-P structure in an area are formed, the P portions of the superposed P<+>-P structure in an area are formed, wherein the P portions are separated from each other and the structure of P portions is similar to the netted structure of a junction barrier schottky (JBS). Therefore, reverse withstand voltage of the JBS diode device can be improved and the output capacitance can be reduced, on the condition that the forward conduction characteristic of the device is not sacrificed. The process of the invention has the strong feasibility of implementation, and the application requirement of the power electronic system can be satisfied easily according to the invention.

Owner:HARBIN ENG UNIV

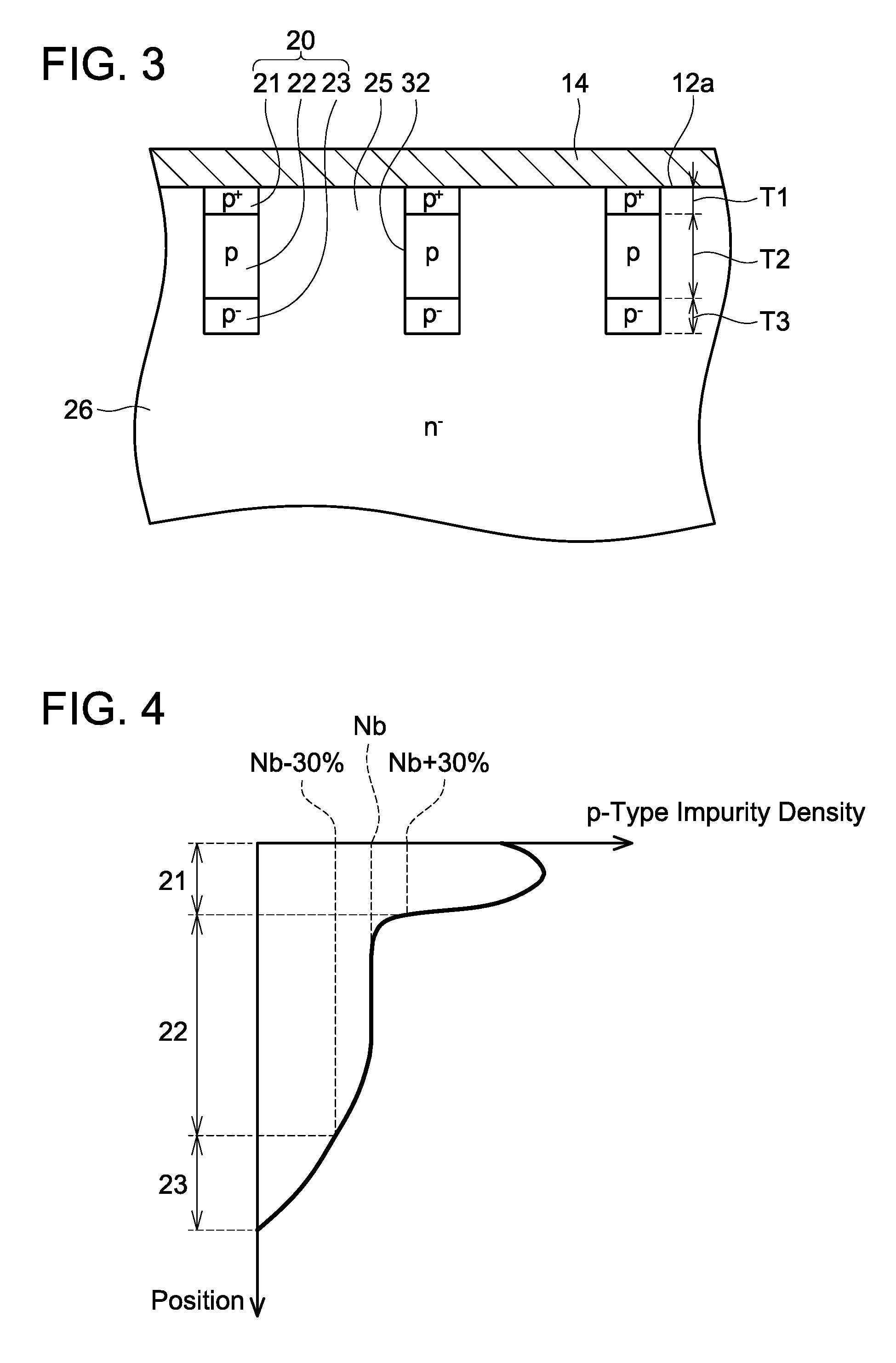

Diode and method of manufacturing diode

InactiveUS20160300960A1Improve response speedSuppresses electric field concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesImpuritySemiconductor

A diode is provided with a semiconductor substrate; an anode electrode located on a front surface of the semiconductor substrate; and a cathode electrode located on a rear surface of the semiconductor substrate. Each of the p-type contact regions includes: a first region being in contact with the anode electrode; a second region located on the rear surface side of the first region, having a p-type impurity density lower than a p-type impurity density in the first region; and a third region located on the rear surface side of the second region and having a p-type impurity density lower than the p-type impurity density in the second region. A thickness of the second region is thicker than a thickness of the first region.

Owner:TOYOTA JIDOSHA KK +1

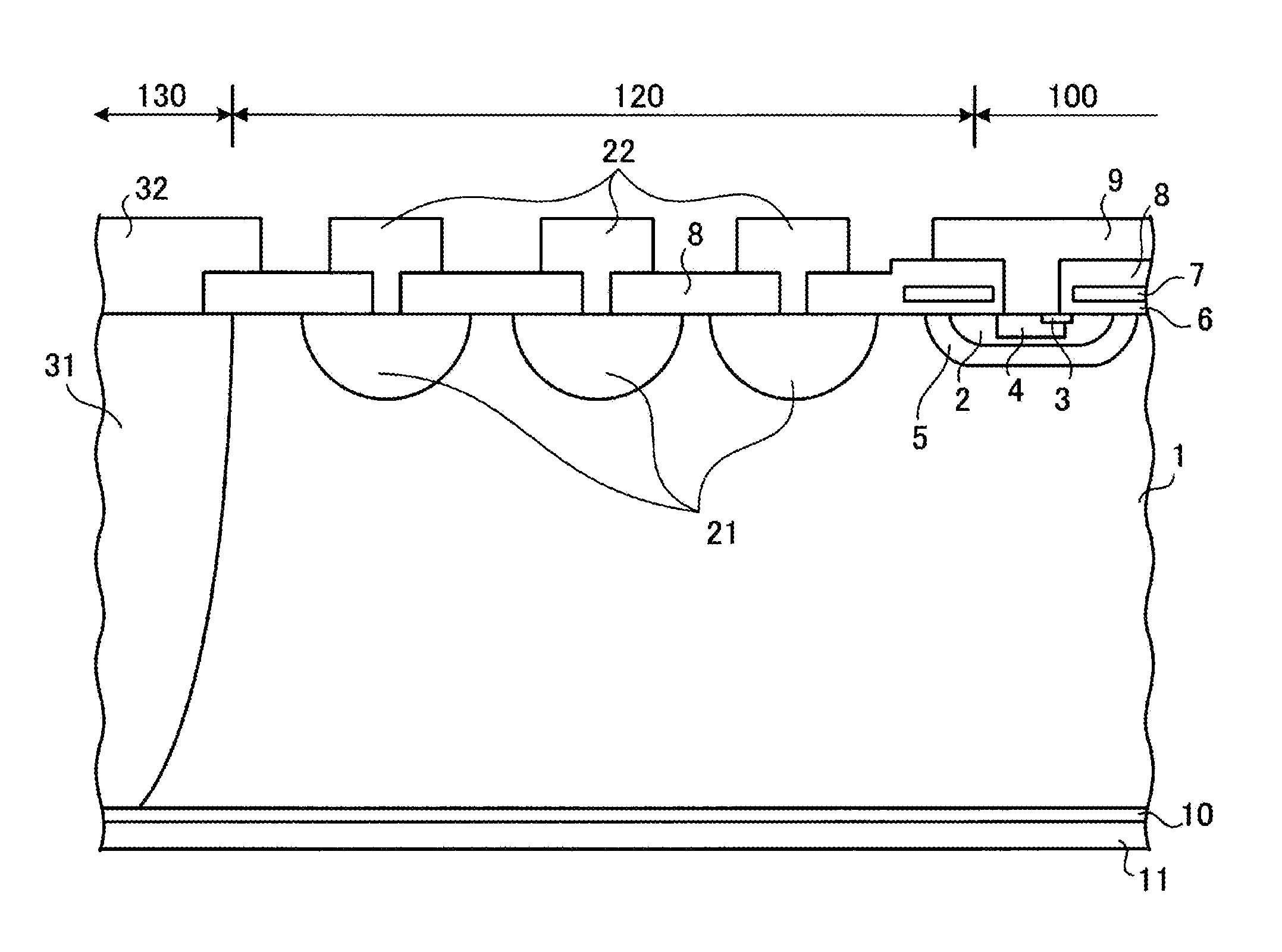

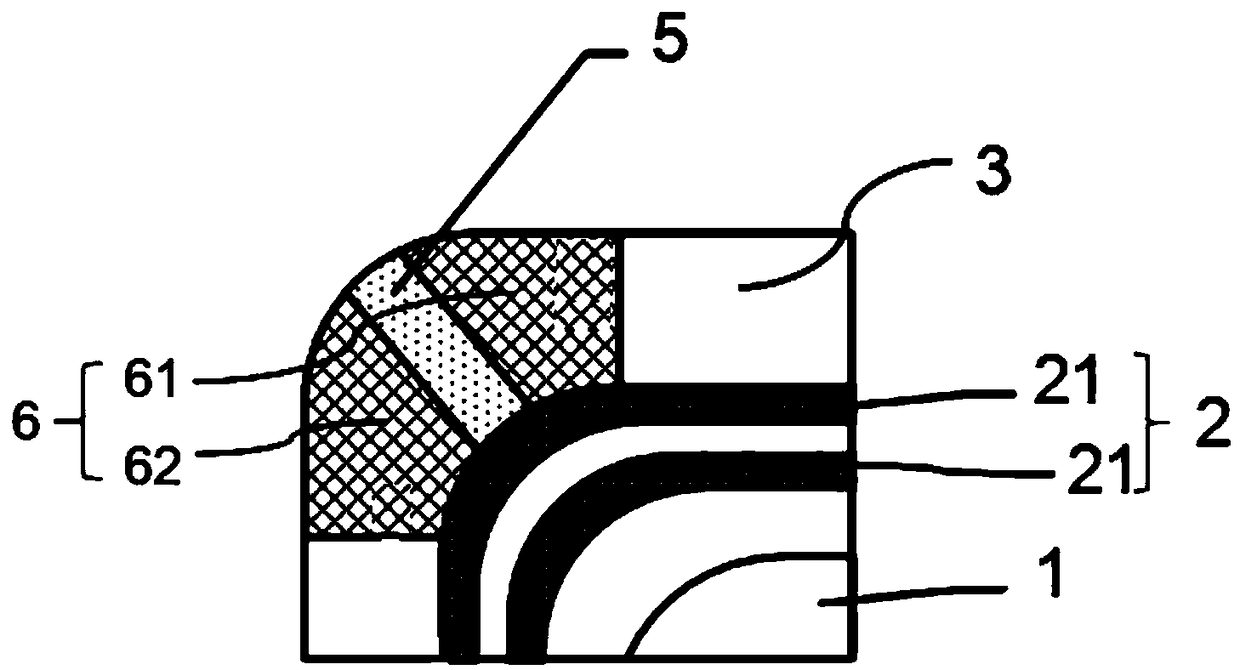

Power diode and method for manufacturing power diode

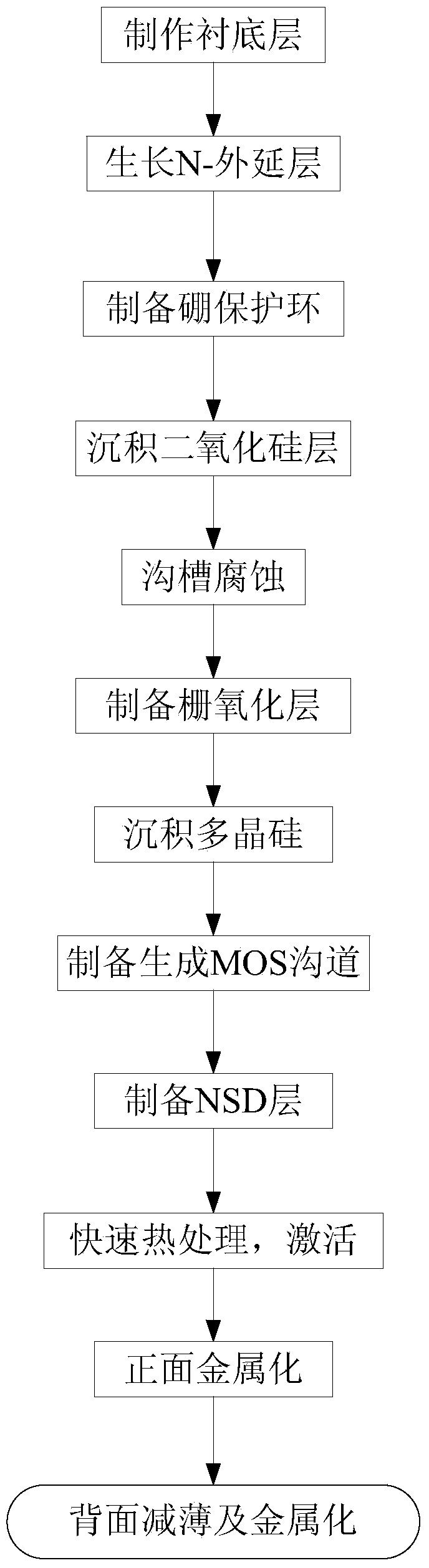

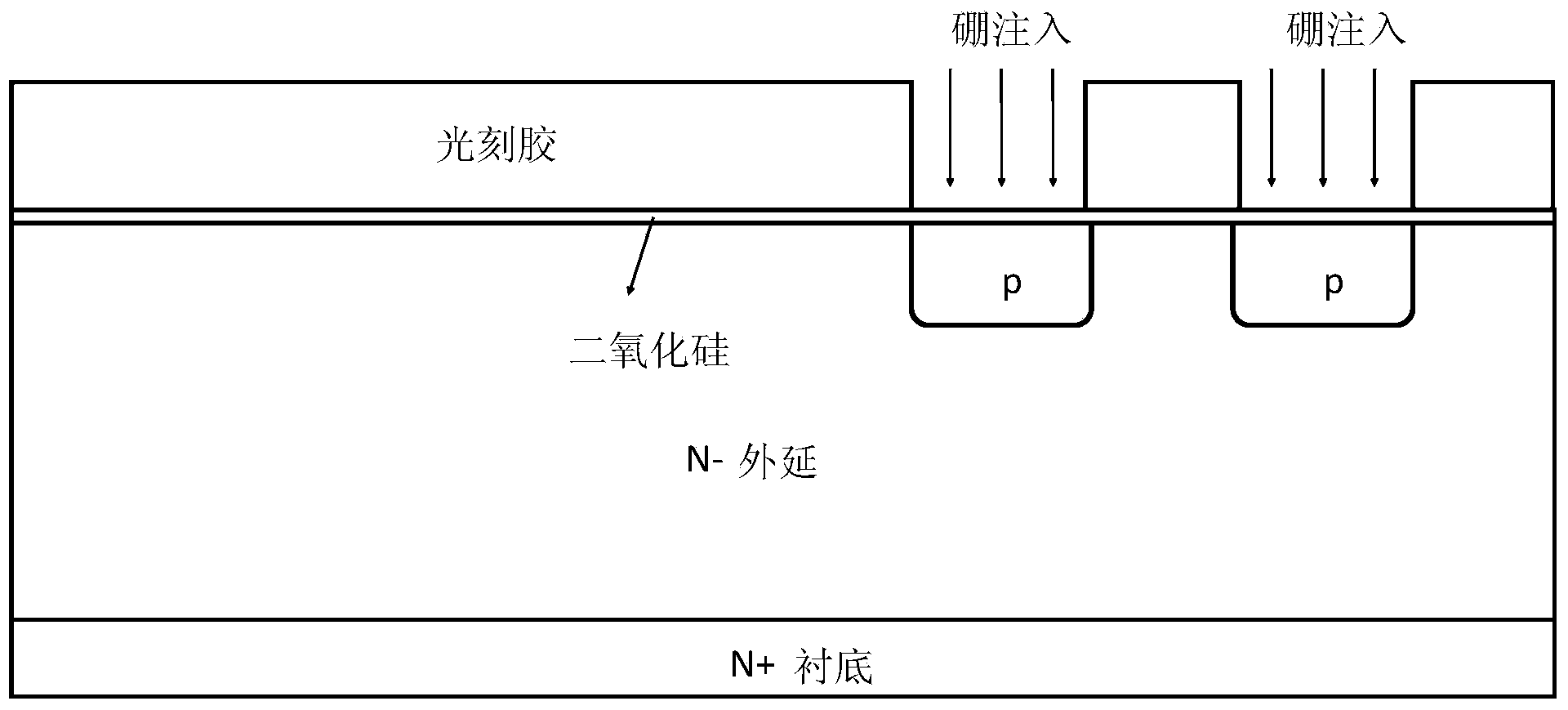

ActiveCN104051546AImprove reverse withstand voltage capabilityImprove reverse withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETElectricity

The invention relates to a power diode and a method for manufacturing the power diode. The power diode comprises a bottom electrode, a substrate layer, an N- type epitaxial layer and a top electrode, wherein the top electrode serves as the positive electrode of the power diode, the bottom electrode serves as the negative electrode of the power diode, at least two grooves are transversely formed in the upper portion of the N- type epitaxial layer in a spaced mode, and an MOS channel is formed in the portion, between every two adjacent grooves, of the N- type epitaxial layer. The power diode is made of silicon materials and can be obtained through an existing silicon semiconductor integrated circuit; special metal materials are not needed, and the method for manufacturing the power diode is compatible with an existing semiconductor production technology; the backward voltage resistance of the device is improved through p+ regions injected into the grooves; when backward voltage is applied to the device, the p+ exhaustion regions in the grooves expand and are connected, a backward current channel is cut off, and the voltage resistance of the device is improved; when the power diode operates in the forward direction, electricity is conducted through parasitic mosfet, and the forward starting voltage of the device is reduced.

Owner:无锡橙芯微电子科技有限公司

Current-limiting diode

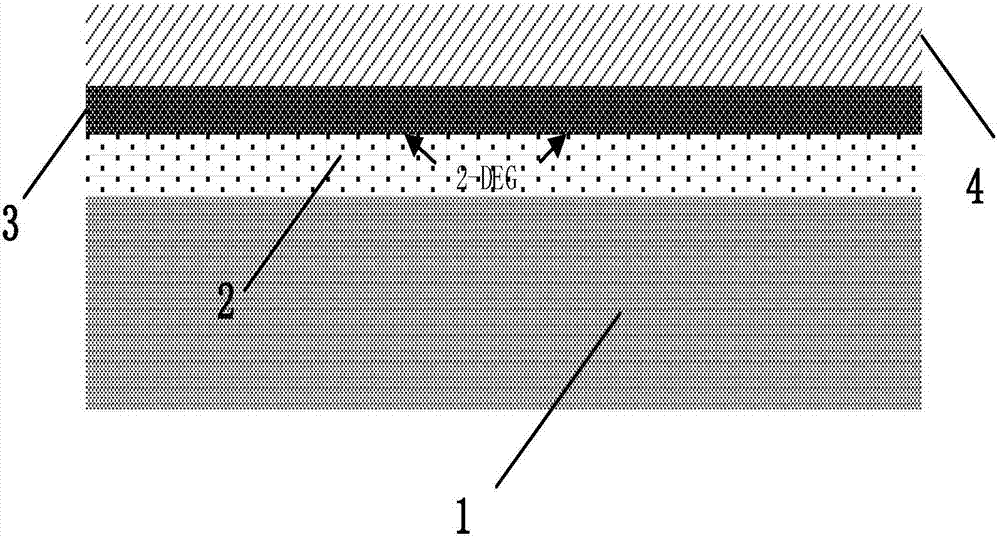

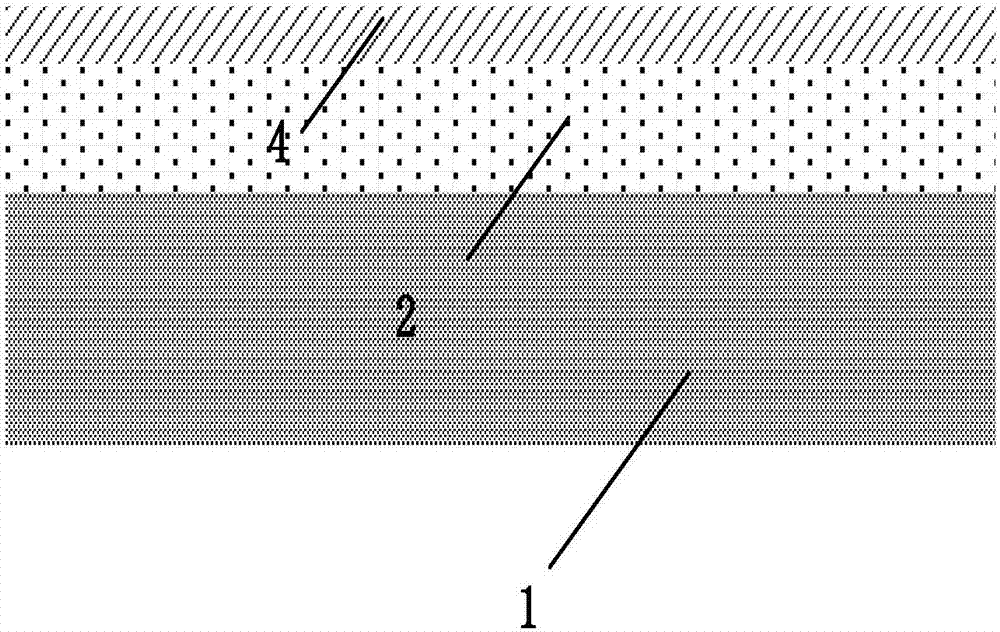

The invention belongs to the technical field of semiconductors, and relates to a current-limiting diode. The invention proposes the novel current-limiting diode, and the diode employs the technology of growing a charge restoration layer on a thin carrier AlGaN / GaN heterojunction to modulate two-dimensional electron gas. The structural advantages of the diode lie in that fluorine-based gas used for etching of the charge restoration layer can hardly cause any etching impact on a barrier layer below the charge restoration layer under the conditions that a device is enhanced and the diode has a lower start voltage and a large reverse withstand voltage, and finally can achieve the self-terminating at an AlGaN interface, so as to achieve the precise control of the barrier layer. The diode avoids the etching of the AlGaN layer, and cannot cause damages to the AlGaN layer, so the device is large in current density, is higher in electron mobility and is lower in conduction resistance.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

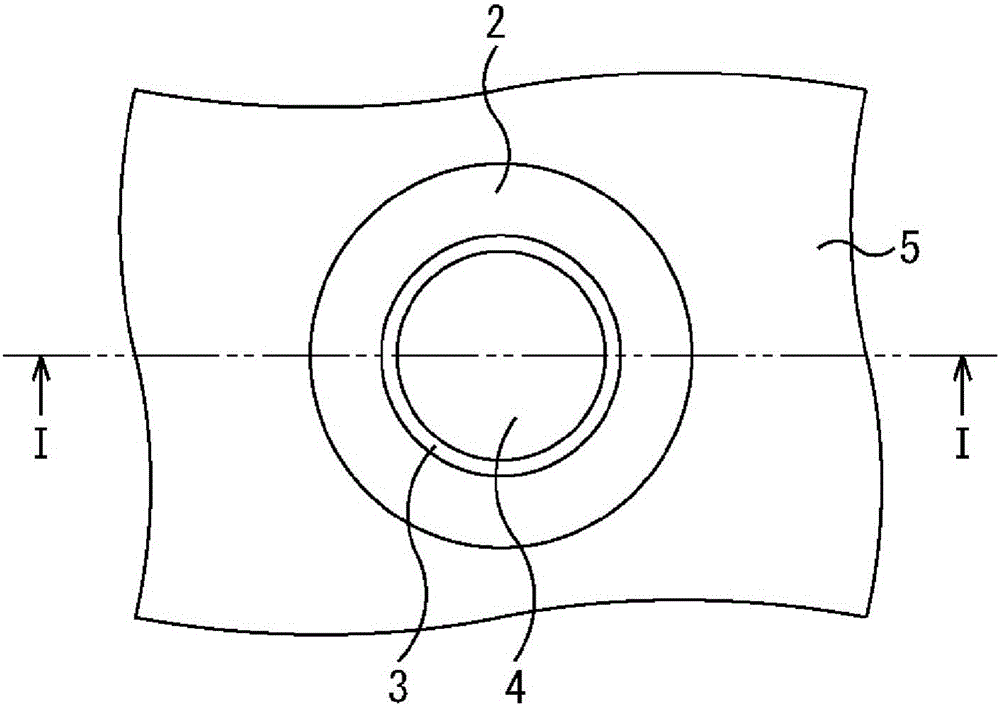

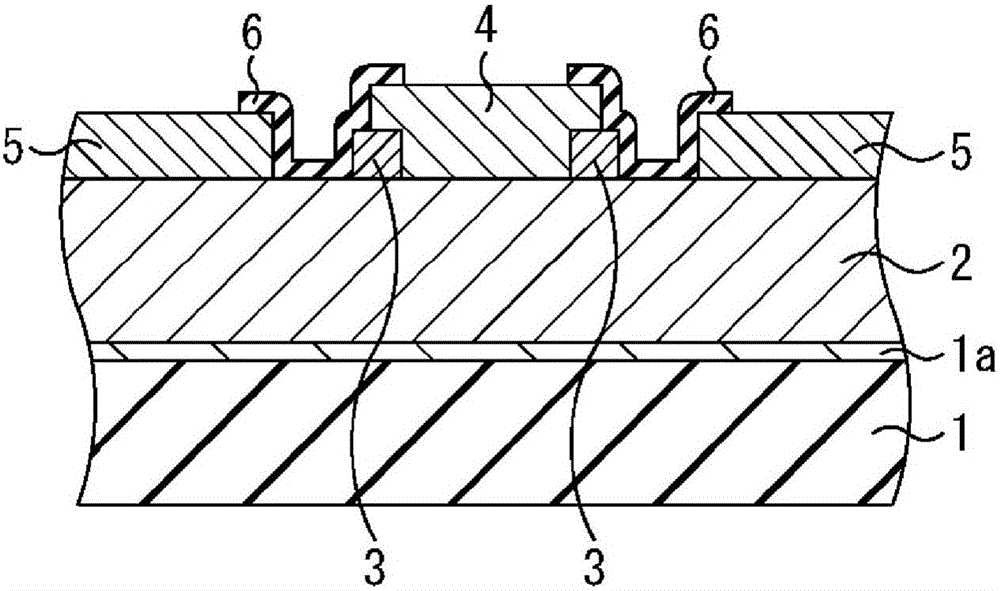

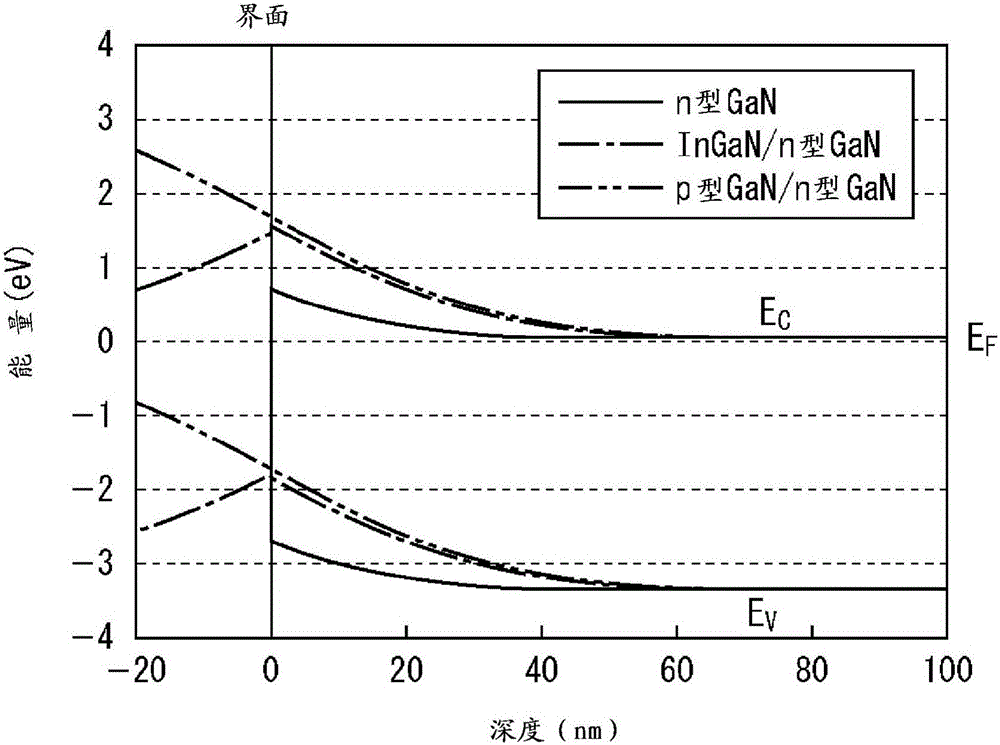

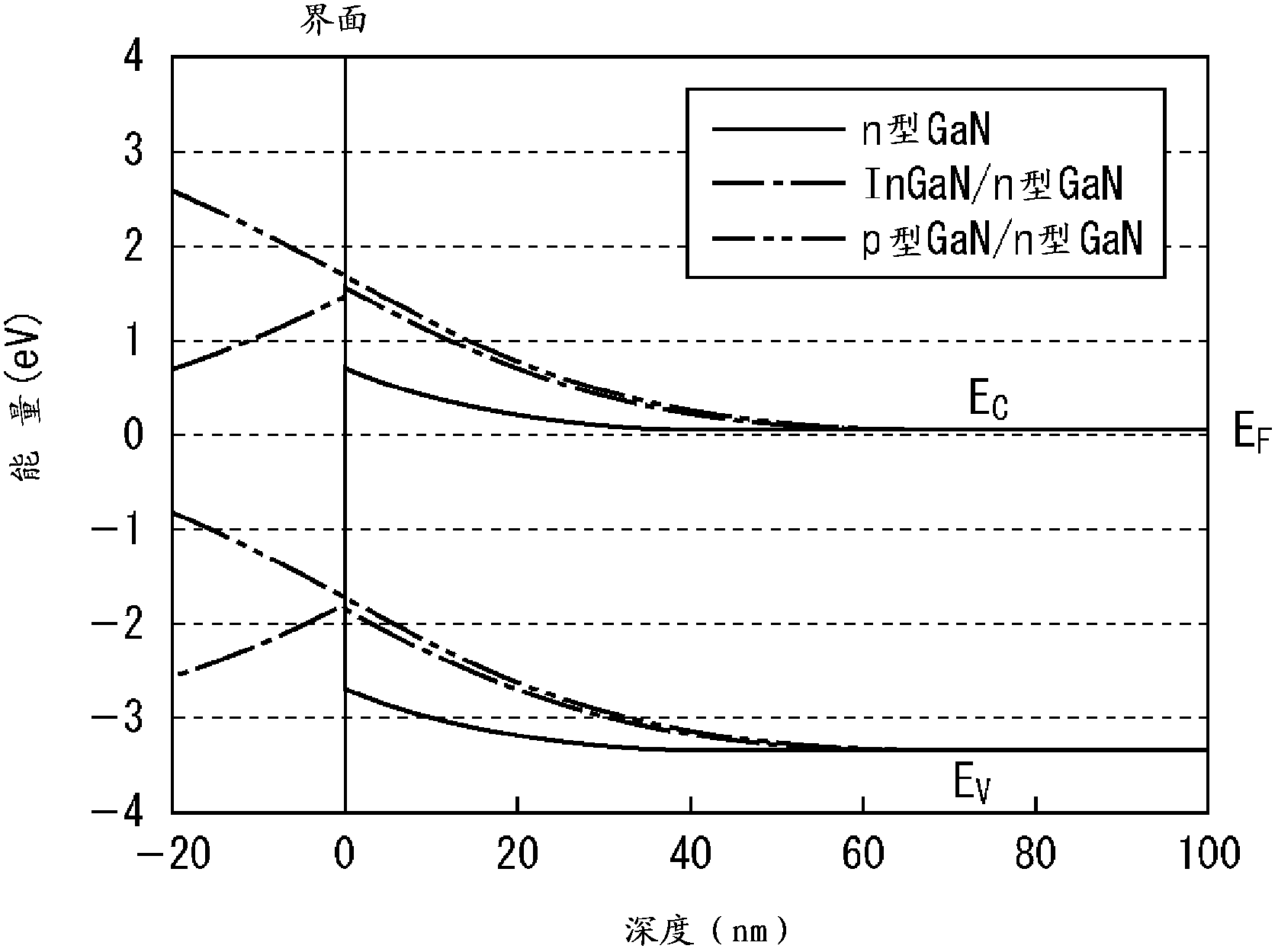

Semiconductor device and manufacturing method thereof

ActiveCN105977209AImprove reverse withstand voltageSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorSemiconductor device

The invention discloses a semiconductor device, comprising a GaN layer (2), an anode electrode (4) in Schottky connection with the Ga surface of the GaN layer (2) and an InGaN layer (3) between at least a part of the anode electrode (4) and the GaN layer (2).

Owner:FUJITSU LTD

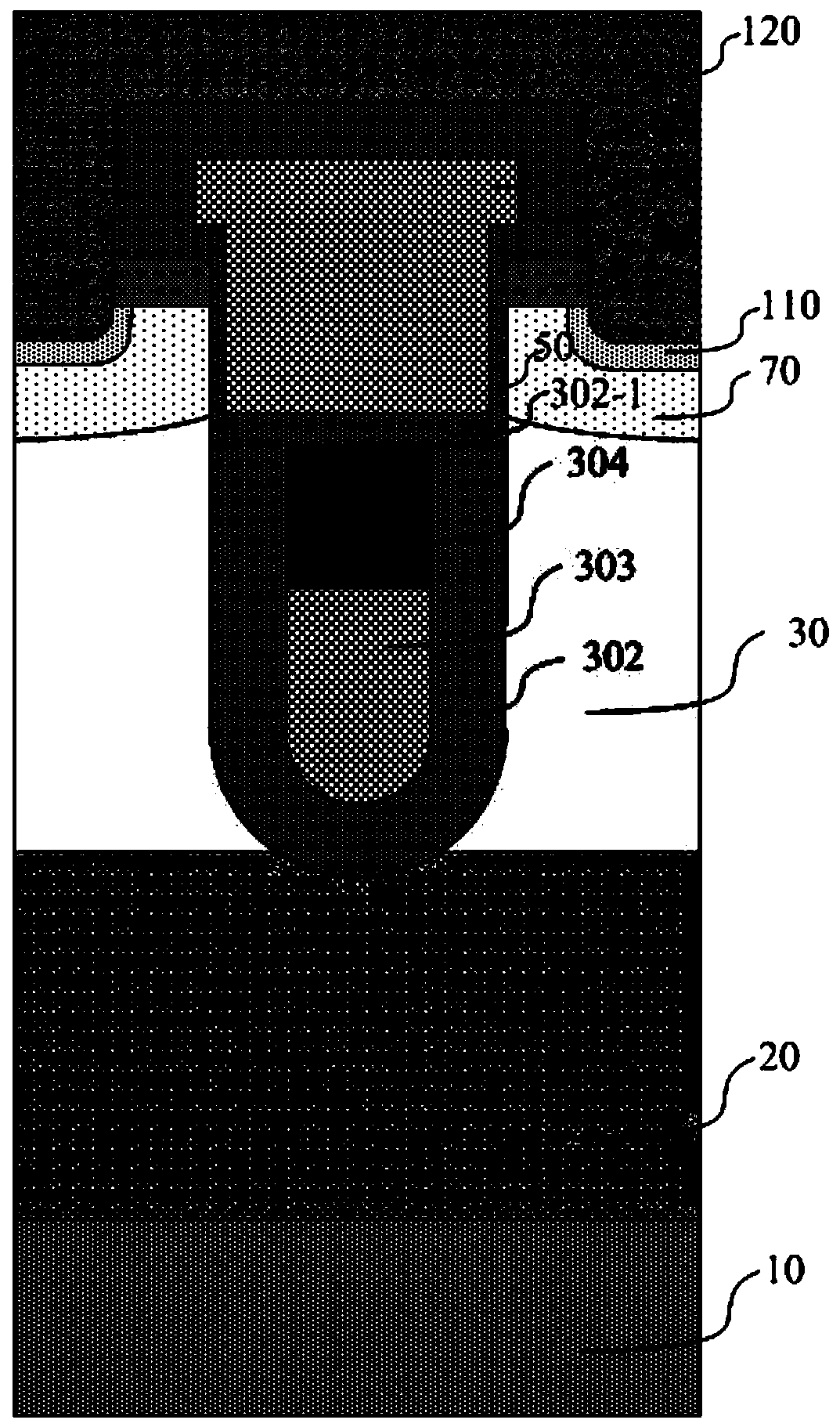

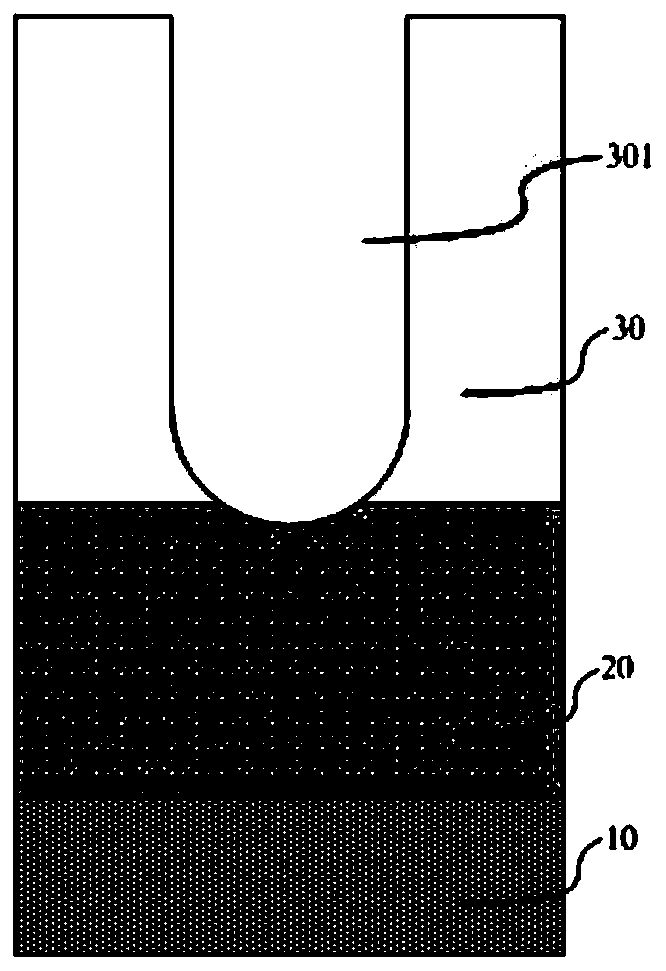

A preparation method of a shielded gate power device

InactiveCN109037071AReduce static power lossReduce capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceHigh resistance

An object of the present invention is to provide a preparation method of a shielded gate power device. A double-layer different resistivity epitaxy is adopted, the lower layer is low resistance epitaxy, which has smaller on-state resistance than the homogeneous high resistance epitaxial layer under the same withstand voltage to reduce the static power loss of the device, the gate oxide longitudinally extends to the drain, and the transverse electric field distribution of the upper layer high resistance layer is optimized by a Resurf technology, so as to improve the reverse withstand voltage ofthe device. As the shield gate is PN-doped polysilicon, the capacitance between the shield gate and the drain can be reduced so as to reduce the switch power loss of the shielded gate power MOSFET.

Owner:厦门芯一代集成电路有限公司

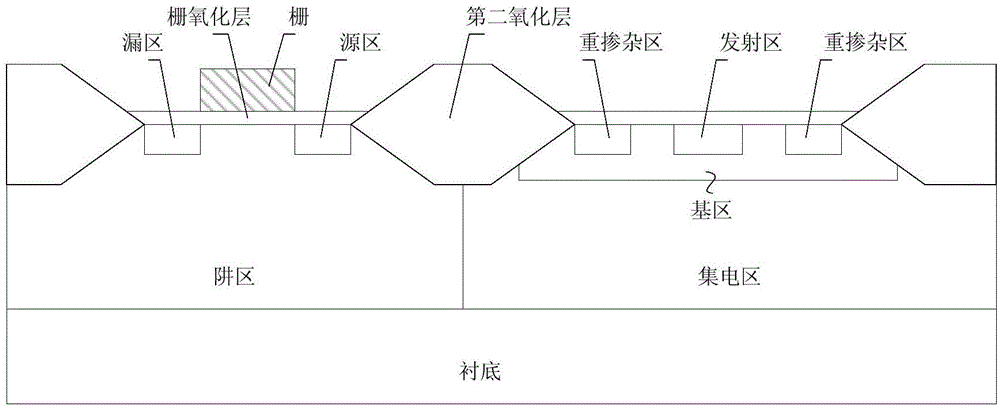

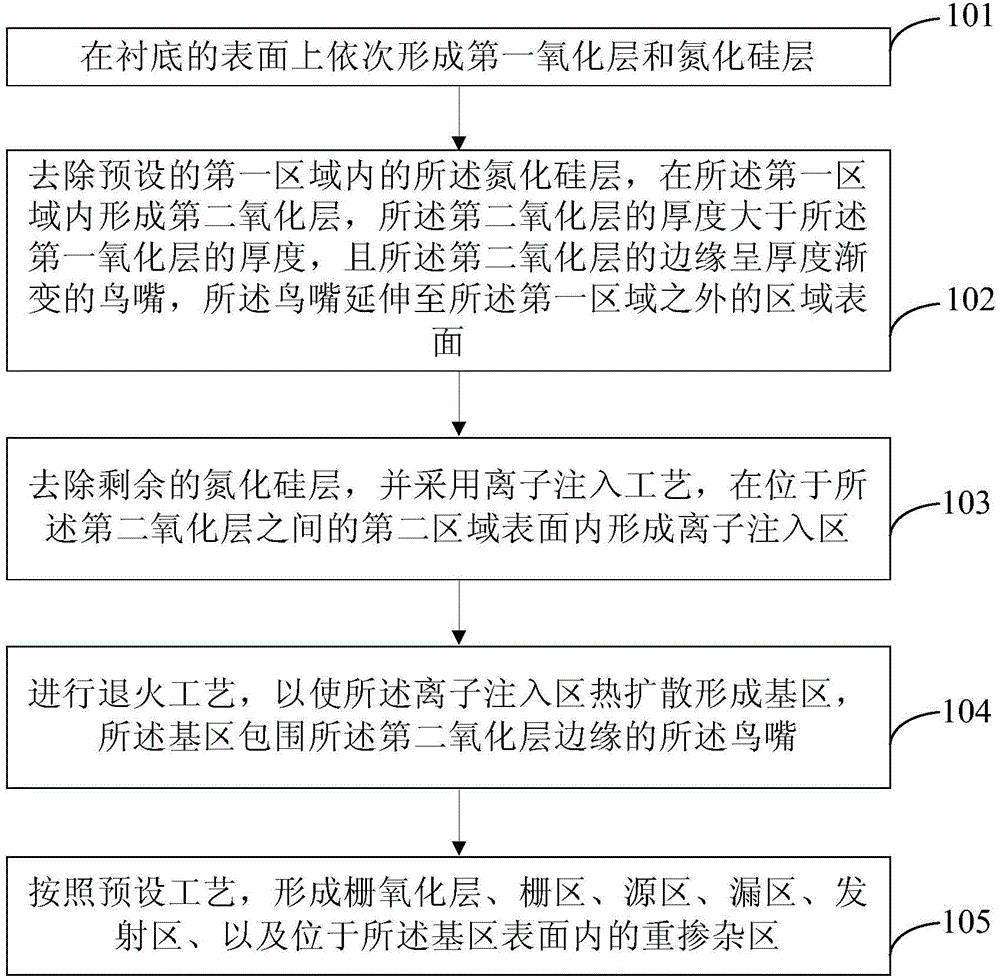

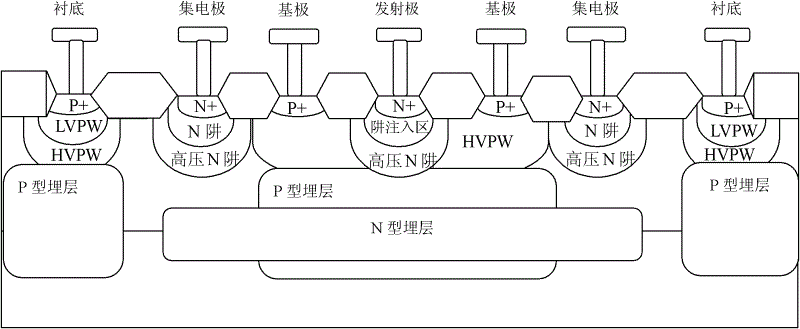

Manufacturing method of BiCMOS integrated circuit

InactiveCN105990254AImprove reverse withstand voltageIncrease working voltageSemiconductor/solid-state device manufacturingSemiconductor devicesBicmos integrated circuitsEngineering

The present invention provides a manufacturing method of a BiCMOS integrated circuit. The method comprises a step of orderly forming a first oxide layer and the silicon nitride layer on the surface of a substrate, a step of removing the silicon nitride layer in a preset first area, forming second oxide layers in the first area, wherein the edges of the second oxide layers are in the shape of a beak with increasing thickness, and the beak extends to the area surface outside the first area, a step of removing the remaining silicon nitride layer and forming ion implanting area in the second area surface between the second oxide layers, a step of carrying out annealing process such that the ion implanting area is allowed to be in thermal diffusion to form a base area which surrounds the beaks of the edges of the second oxide layers. Through the scheme provided by the invention, the base area can laterally spread to an area under the beaks and surrounds the beaks, when a transistor is under high voltage, a wide depletion layer can be realized in the base area, thus the reverse voltage withstanding of the BiCMOS integrated circuit is improved, the highest working voltage of the transistor is raised, and the requirement of a high voltage device is satisfied.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

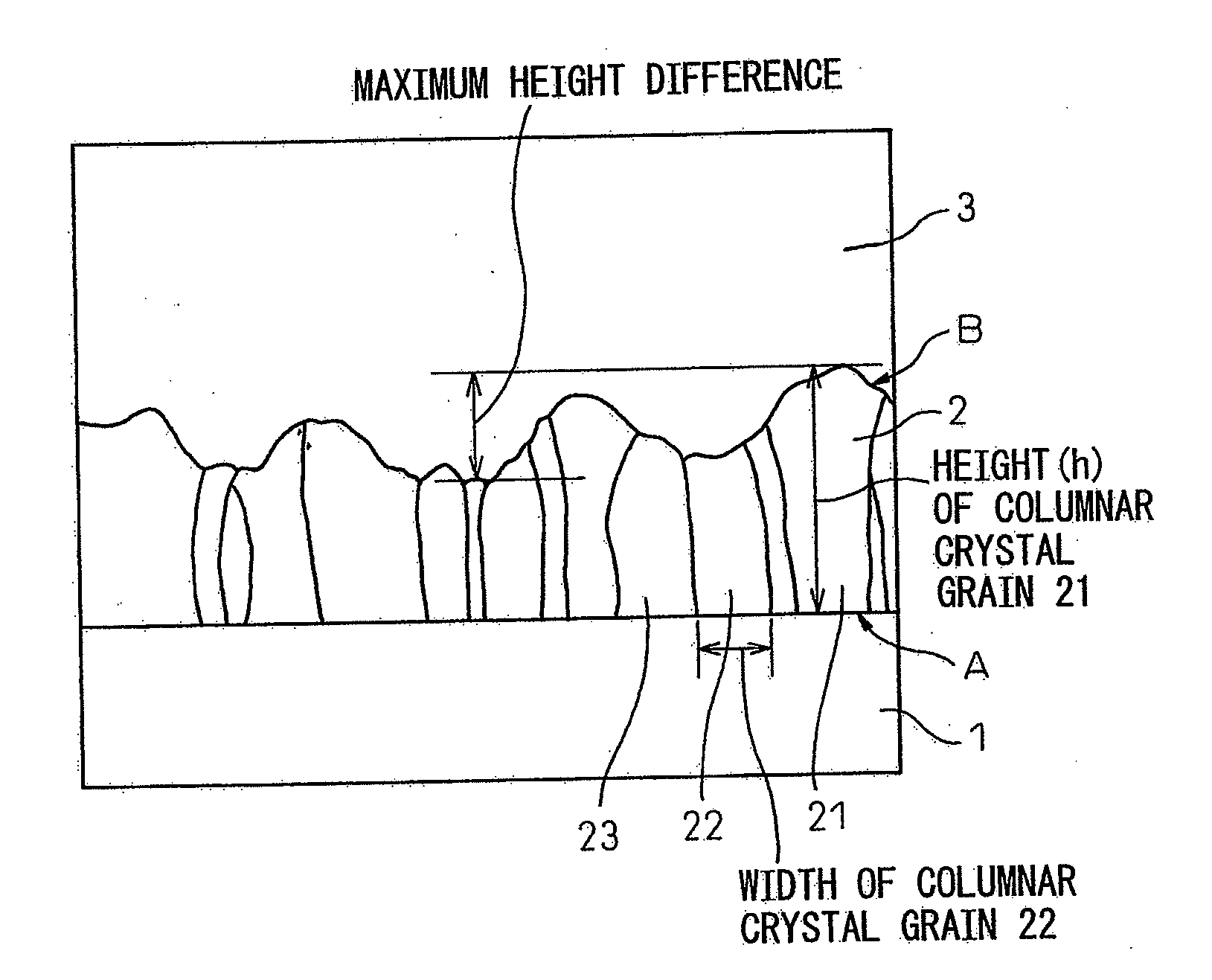

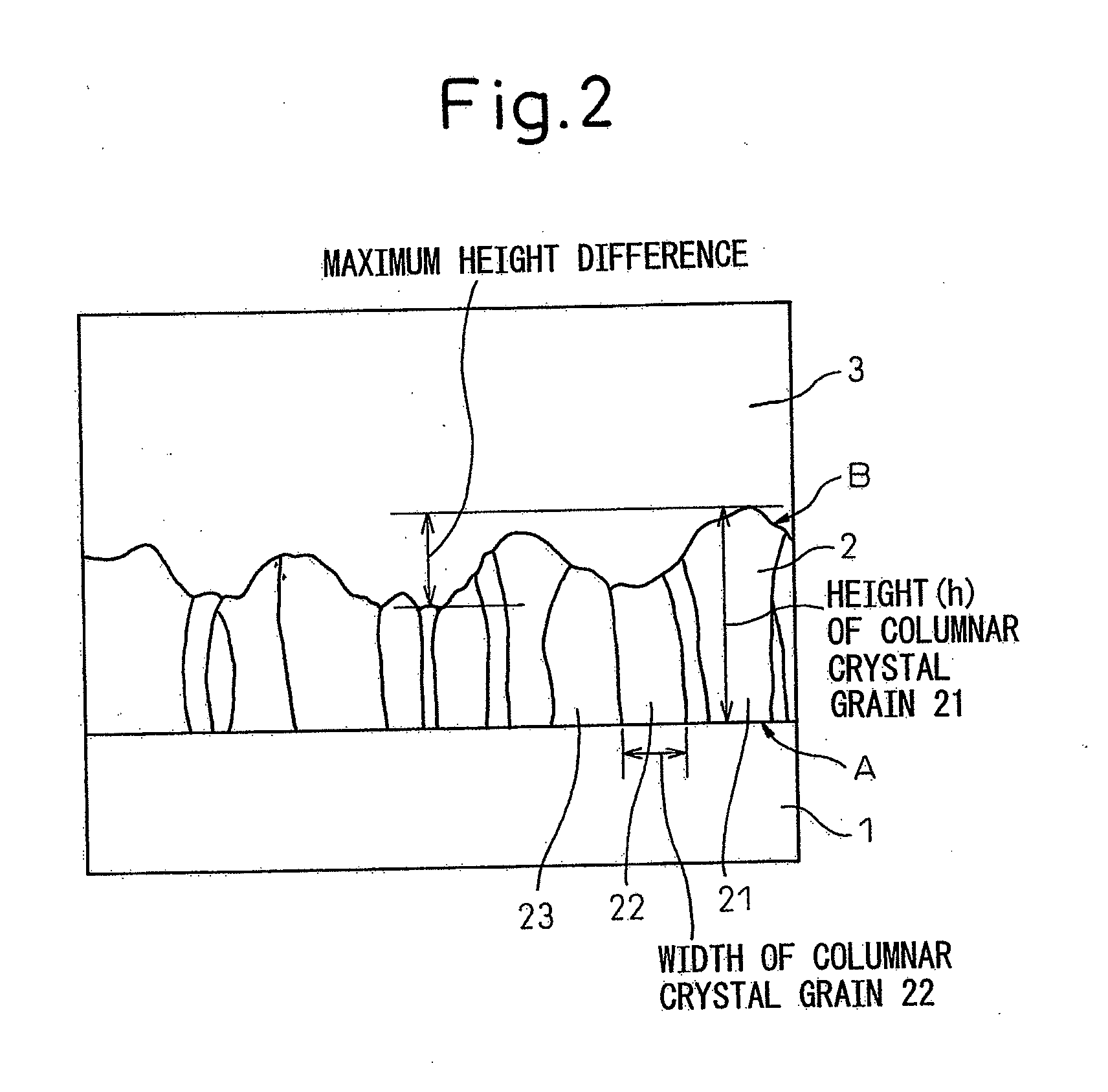

Group iii nitride semiconductor device and light-emitting device using the same

InactiveUS20100267221A1High crystallinityImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesSingle crystalMetal particle

A Group III nitride semiconductor device and method for producing the same. The device includes a substrate, and a plurality of Group III nitride semiconductor layers provided on the substrate. A first layer which is in contact with the substrate is composed of AlxGa1-x N (0≦x≦1), and the difference in height between a protrusion and a depression which are present at the interface between the first layer and a second layer provided thereon is 10 nm or more and is equal to, or less than, 99% the thickness of the first layer. The method includes a first step of depositing on a substrate, a layer containing fine Group III metal particles containing silicon; a second step of nitridizing the fine particles in an atmosphere containing a nitrogen source; and a third step of growing a Group III nitride semiconductor single crystal on the thus-nitridized fine particles.

Owner:RESONAC HOLDINGS CORPORATION

An accumulation type DMOS device

The invention provides an accumulation type DMOS device, comprising a metallized drain electrode, an N + substrate, an N-drift region and a metallized source which are successively stacked from bottom to top. The upper layer of the N-drift region has an N-type light doped region, and an N + heavily doped region is located directly above the N-type light doped region. The N-drift region is also provided with a first trench and a second trench inside, wherein the first trench is provided with a polysilicon gate electrode and a positive charge region, the polysilicon gate electrode and the metallization source electrode are isolated by a second dielectric layer, and the positive charge region is positioned directly below the polysilicon gate electrode. The depth of the lower surface of the N-type light doped region is smaller than that of the lower surface of the polycrystalline silicon gate electrode. The invention solves the problem that the conventional accumulated power DMOS is a normally-on device. The invention is not only a normally-off device, but also has the advantages of low threshold voltage, small on resistance, high reverse withstand voltage, good reverse recovery characteristic of the body diode and no parasitic transistor.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

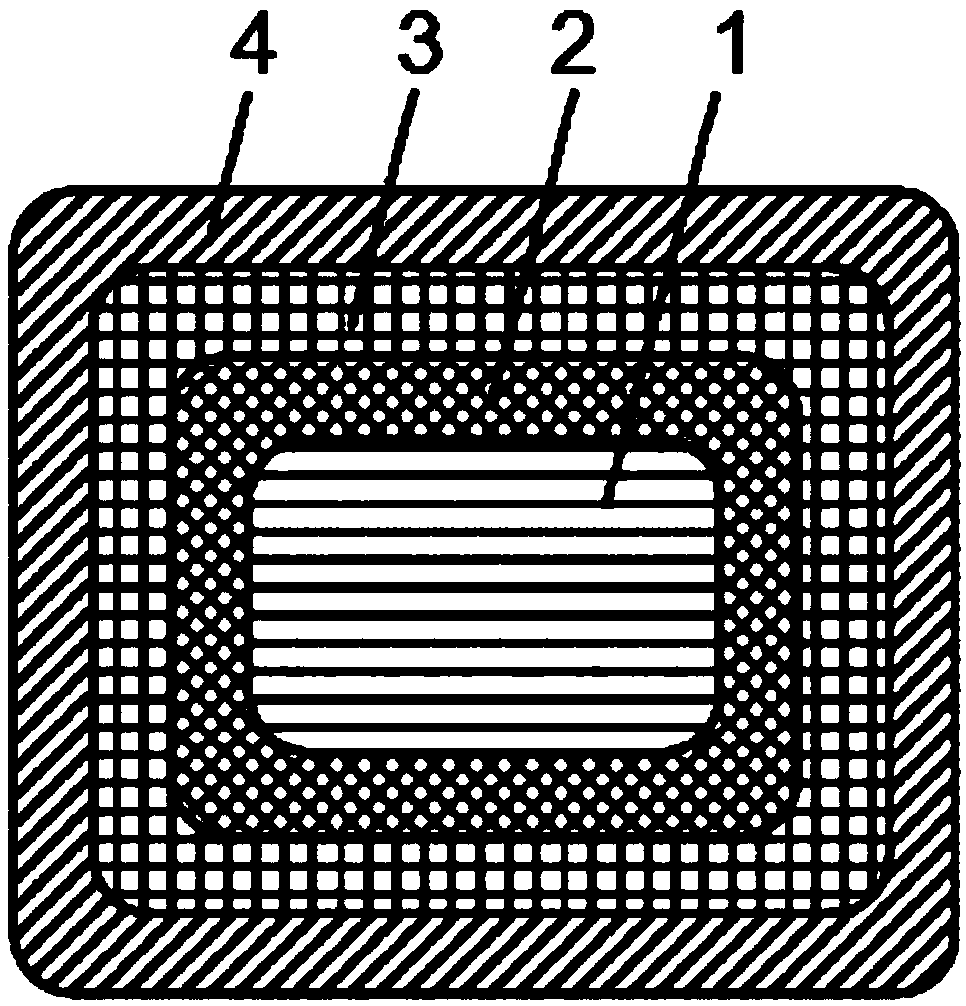

A power device

ActiveCN108987459ASmall radius of curvatureImprove reverse withstand voltageSemiconductor devicesVoltage

The invention relates to apower device including the active area, a voltage sharing region and a cut-off ring region, the voltage sharing region comprising at least one voltage sharing ring of a firstconductivity type, A cut-off re region is arranged at that periphery of the voltage sharing ring, the voltage sharing ring having at least one corner, the cut-off ring region having at least one outer corner corresponding one-to-one to a corner of the voltage sharing ring, A super junction structure is for in that cut-off ring region, the super junction structure includes a first injection regionof a first conductivity type and a second injection region of a second conductivity type, the first injection region extends from a peripheral corner of the voltage sharing ring to a corresponding corner of the cut-off ring region, The second injection region includes a first portion formed on both sides of the first injection region and connected to the first injection region, and a second portion formed on both sides of the first injection region. One end of the first injection region and the second injection region jointly cover a corner region of the first voltage sharing ring.

Owner:郯城县新区建设发展有限公司

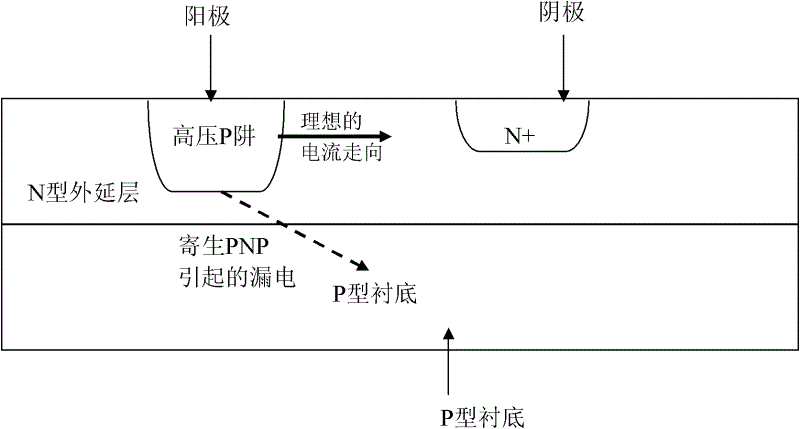

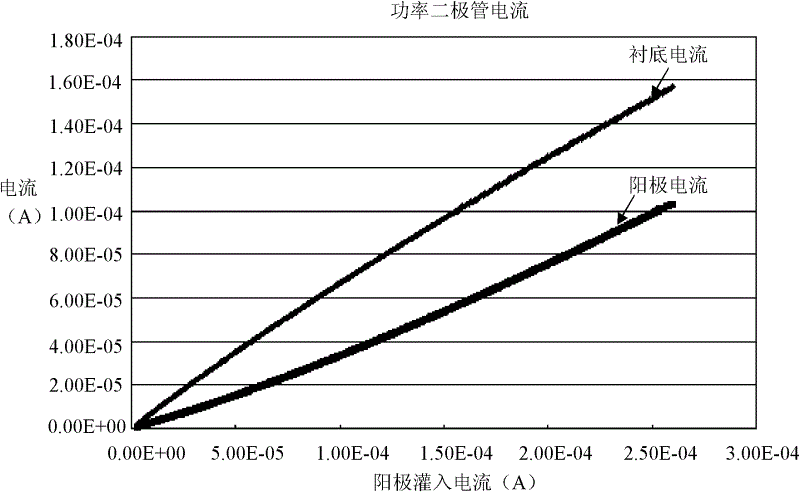

Power diode

ActiveCN102623511AReduced substrate leakageImprove reverse withstand voltageSemiconductor devicesPower diodeImpurity

The invention discloses a power diode. A NPN structure is employed by the power diode. A base electrode and a collector electrode of the NPN structure are connected and work as an anode of the power diode, and an emitter electrode of the NPN structure works as a cathode of the power diode. A well implantation region is provided under an emission area of an emitter electrode end. The well implantation region has a same conduction type with the emission area, and has a lower impurity concentration than the emission area. A buried layer is provided in the substrate under the base electrode. The buried layer has a same conduction type with the base electrode area, and has a higher impurity concentration than the base electrode area. The power diode of the invention has low substrate electric leakage and high reverse breakdown voltage.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

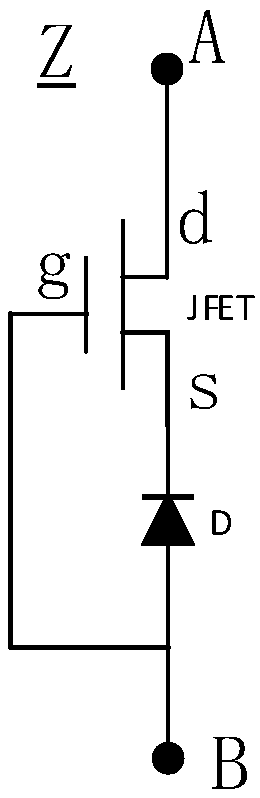

Combined switch

InactiveCN107707235AImprove reverse withstand voltageLower forward voltageDiodeReverse recoveryTunneling field effect transistor

The invention discloses a combined switch. The combined switch comprises a junction field effect transistor and a diode. The junction field effect transistor comprises a gate electrode, a source electrode and a drain electrode; the diode comprises an anode and a cathode; the drain electrode of the junction field effect transistor is a first terminal of the combined switch; the source electrode ofthe junction field effect transistor is connected with the cathode of the diode; the gate electrode of the junction field effect transistor is connected with the anode of the diode; and the anode of the diode is a second terminal of the combined switch. Compared to a single diode, the combined switch disclosed by the invention has a higher reverse withstand voltage, and has zero reverse recovery characteristic and a lower forward turn-on voltage.

Owner:FSP POWERLAND TECH

Trench MOS barrier Schottky diode and manufacturing method

InactiveCN103441152AReduce power consumptionImprove reverse withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricOhmic contact

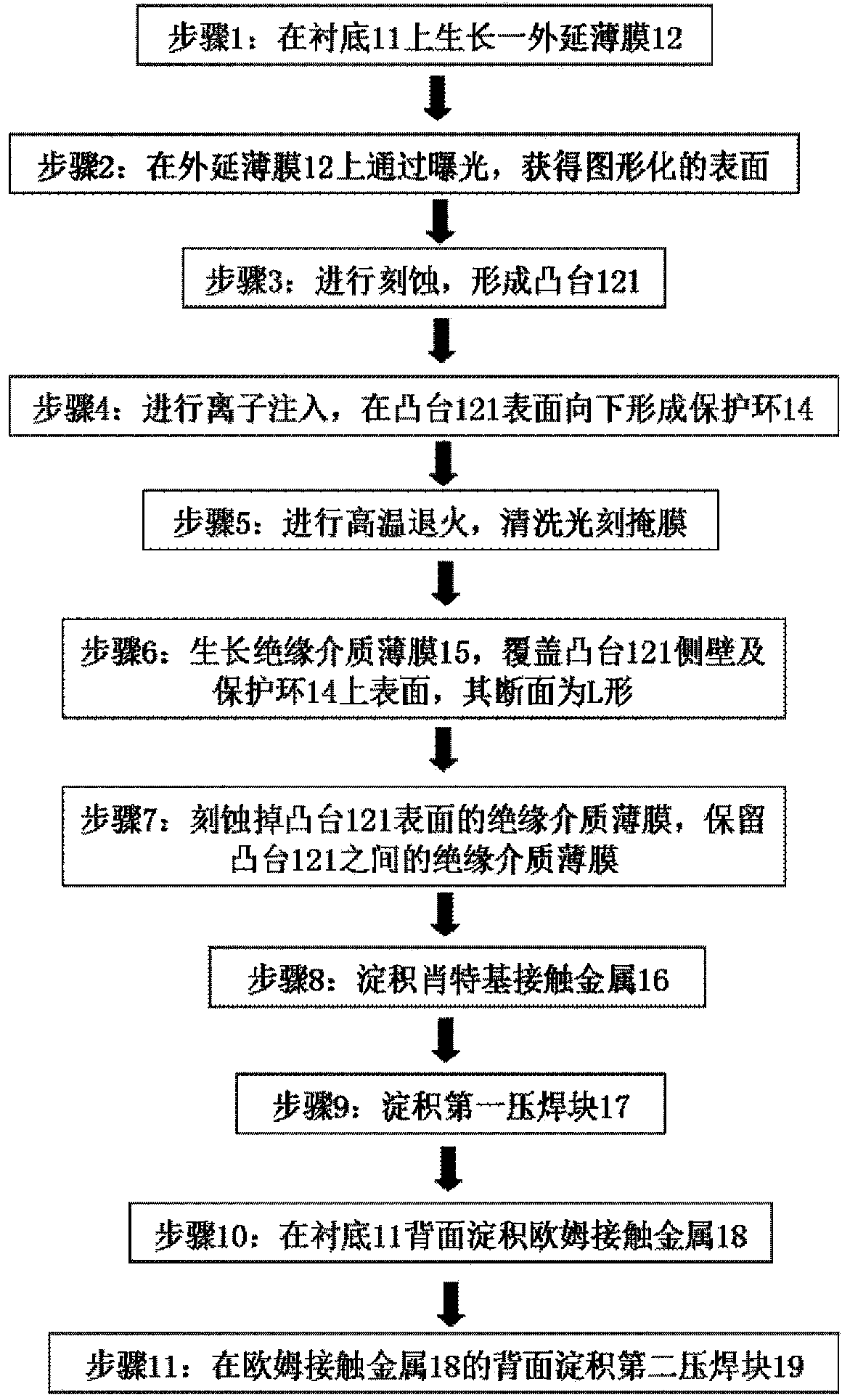

Provided are a trench MOS barrier Schottky diode and a manufacturing method. The trench MOS barrier Schottky diode comprises a substrate, an epitaxial thin film manufactured on the substrate, a protective ring, an insulation dielectric film, Schottky contact metal, a first bonding block, ohmic contact metal and a second bonding block. A boss is arranged in the middle of the epitaxial thin film, and the side wall of the boss is a plane. The protective ring is manufactured on the periphery of the boss of the epitaxial thin film and is located below the plane on the periphery of the boss. The insulation dielectric film is manufactured on the side wall of the periphery of the boss of the epitaxial thin film, the height of the insulation dielectric film is flush with that of the boss of the epitaxial thin film, the insulation dielectric film is located on the protective ring, the height of the part, on the protective ring, of the insulation dielectric film is smaller than that of the surface of the boss, and the section of the insulation dielectric film is an L shape. The Schottky contact metal is manufactured on the surface of the insulation dielectric film and covers the surface of the boss of the epitaxial thin film. The first bonding block covers the surface of the Schottky contact metal. The ohmic contact metal is manufactured on the back face of the substrate. The second bonding block is manufactured on the back face of the ohmic contact metal and can further lower the power consumption of a carborundum power electronic device.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

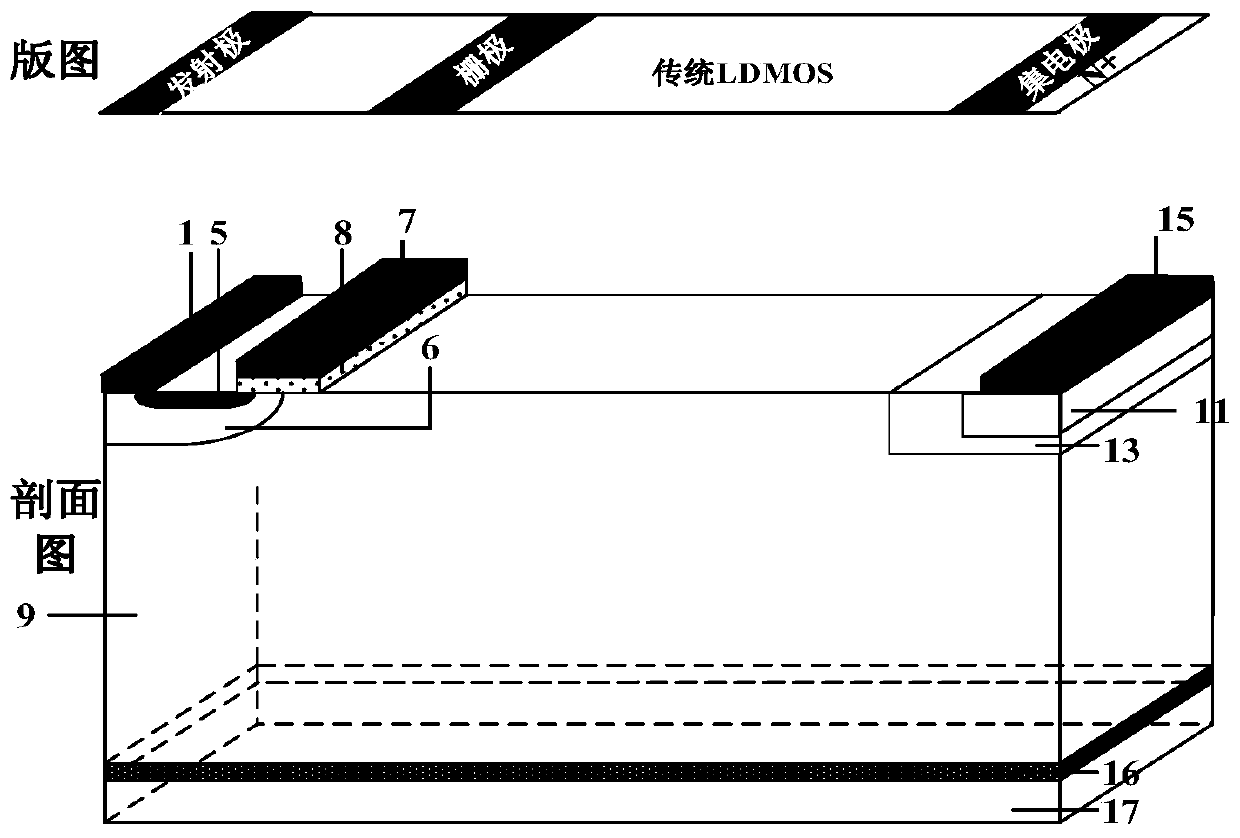

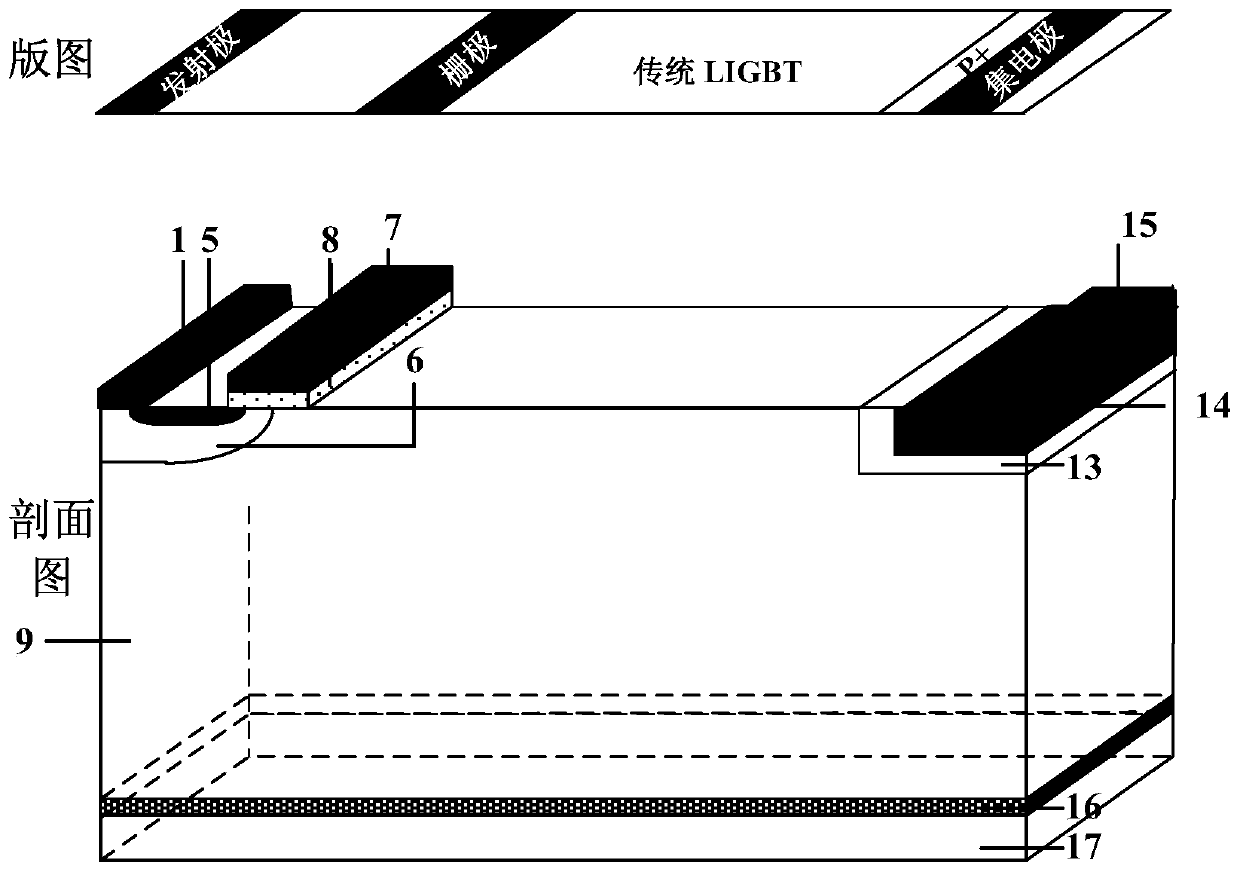

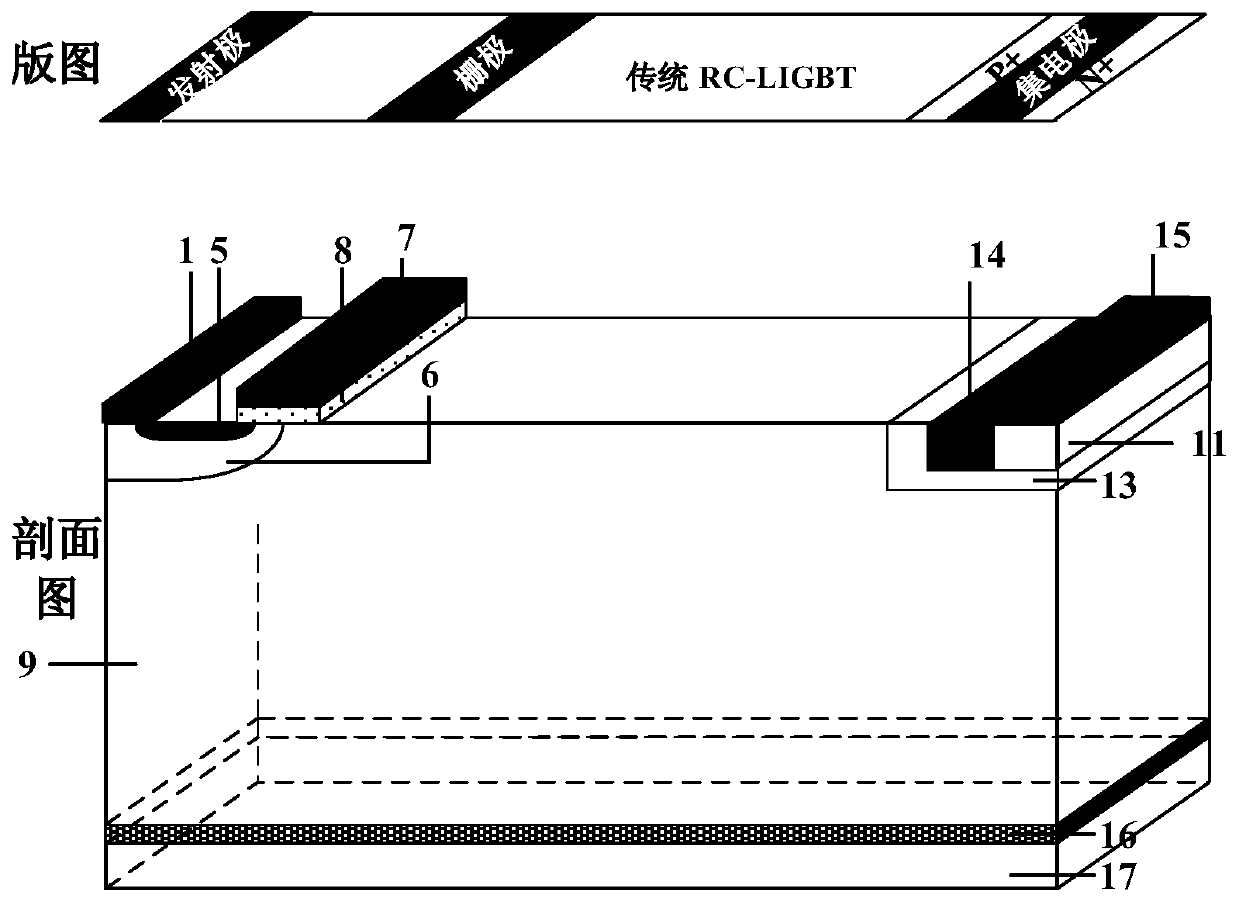

Composite RC-LIGBT (Reverse-Conducting Lateral Insulated Gate Bipolar Transistor) device integrated with LDMOS (Laterally Diffused Metal Oxide Semiconductor) and LIGBT (Lateral Insulated Gate Bipolar Transistor)

ActiveCN109742090AAvoid the snapback effectImprove reverse withstand voltageSolid-state devicesSemiconductor devicesLDMOSBlock effect

The invention discloses a composite RC-LIGBT (Reverse-Conducting Lateral Insulated Gate Bipolar Transistor) device integrated with an LDMOS (Laterally Diffused Metal Oxide Semiconductor) and an LIGBT(Lateral Insulated Gate Bipolar Transistor). The composite RC-LIGBT device comprises an LDMOS active area and an LIGBT active area which form a left and right symmetrical structure and share the sameemitter. A channel of the LDMOS active area is controlled by a gate I. The channel of the LIGBT active area is controlled by a gate II. A metal collector I is connected with a metal collector II. Thecomposite RC-LIGBT device has the following advantages that when forward switch-on is carried out, snapback effect is eliminated; due to existence of a collector N-Collector in the LDMOS area, when backward switch-on is carried out, the RC-LIGBT composite is enabled to have backward switch-on capability; and blocking effect of a collector P-Collector to a current does not exist, so the backward switch-on capability of the composite RC-LIGBT is superior to that of a conventional RC-LIGBT. The composite RC-LIGBT technology provided by the invention is compatible with a conventional RC-LIGBT technology, only layout design is required, and an additional technology is avoided.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

Highly voltage-withstanding schottky chip

InactiveCN103000668AIncrease the doping concentrationImprove efficiencySemiconductor devicesSilicon oxideSemiconductor

The invention discloses a highly voltage-withstanding schottky chip and belongs to the technical field of semiconductor device production. The chip comprises a top metal layer (1), a schottky interface (4) under the top metal layer (1), polysilicon (2) closely attached to the underside of the schottky interface (4), a silicon oxide layer outside the polysilicon (2), an N-type epitaxial layer N-EPI (5) and an N-type substrate N+Substrate (6) on the lower portion. The chip is characterized in that the thickness of a bottom silicon oxide layer (7) of the silicon oxide layer outside the polysilicon (2) is larger than that of a side silicon oxide layer (3). Due to the fact that the bottom thickness of the silicon oxide is larger than that in the prior art, the reverse voltage of an electric field at a bending position at the bottom of a groove is untwined, so that the reverse voltage withstanding of a product can be improved by 15%-30%.

Owner:淄博美林电子有限公司

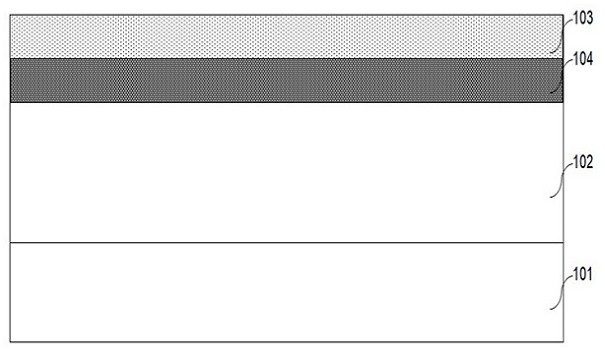

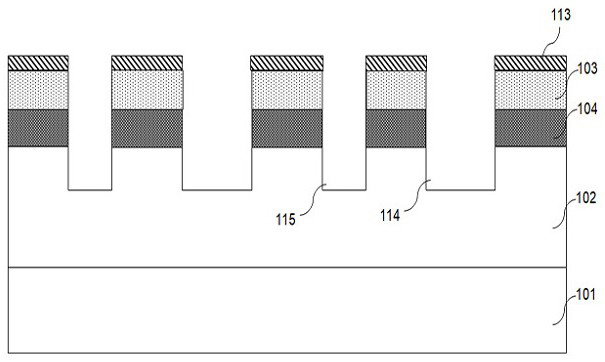

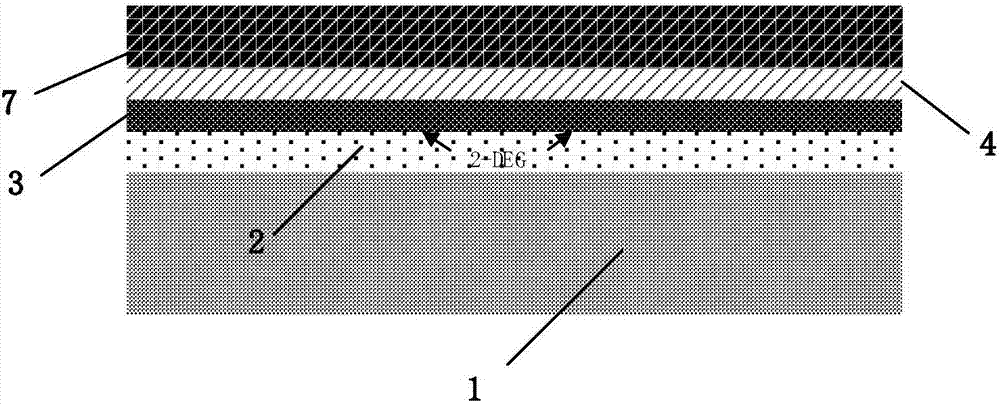

Semiconductor device and method for manufacturing same

ActiveCN103168362AImprove reverse withstand voltageSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorSemiconductor device

Disclosed is a semiconductor device which is provided with a GaN layer (2), an anode electrode (4) formed by a Schottky junction on the Ga surface of the GaN layer (2), and an InGaN layer (3), which is positioned between at least a part of the anode electrode (4) and the GaN layer (2).

Owner:FUJITSU LTD