Highly voltage-withstanding schottky chip

A high withstand voltage, chip technology, applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problems of low reverse withstand voltage of Schottky chips, cannot meet high withstand voltage or reduce forward voltage drop, etc., to achieve improved efficiency effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

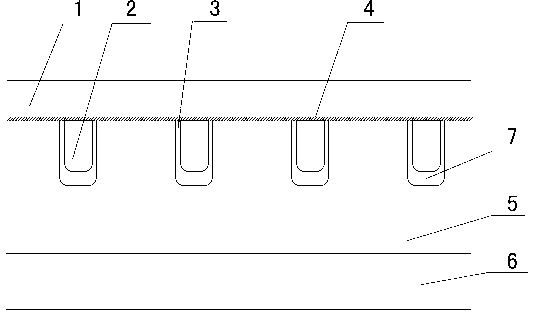

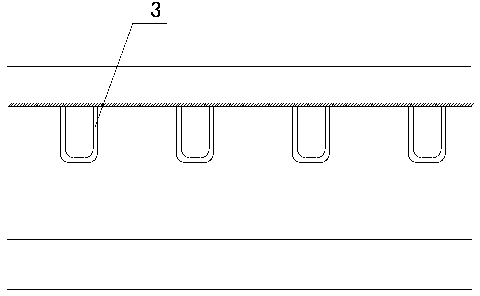

[0012] figure 1 It is the best embodiment of the present invention. Attached below figure 1 A high withstand voltage Schottky chip of the present invention is further described.

[0013] This high withstand voltage Schottky chip consists of top metal layer 1, polysilicon 2, side silicon oxide layer 3, Schottky interface 4, N-type epitaxial layer N-EPI5, N-type substrate N + Substrate6 and bottom silicon oxide layer 7. N type substrate N + Substrate6 is heavily doped N-type substrate. From bottom to top: N-type substrate N + Substrate6, N-type epitaxial layer N-EPI 5 , bottom silicon oxide layer 7, polysilicon 2, side silicon oxide layer 3, Schottky interface 4 and top metal layer 1, silicon oxide layer outside polysilicon 2 bottom silicon oxide layer 7 The thickness is greater than the thickness of the silicon oxide layer 3 at the edge. The thickness of the bottom silicon oxide layer 7 is 2-5 times of the thickness of the side silicon oxide layer 3 .

[0014] For ex...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More