High-dielectric-constant gate dielectric composite channel field effect transistor and preparing method thereof

A technology with high dielectric constant and gate dielectric, applied in transistors, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of high device power consumption, low ZnO channel mobility, and high operating voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

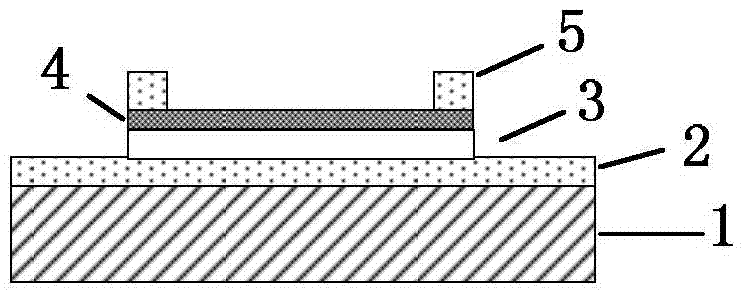

[0043] Graphene / MoS of the above-mentioned high dielectric constant gate dielectric proposed by the present invention 2 The preparation method of the composite channel field effect transistor device, as shown in Figure 2, mainly includes the following steps:

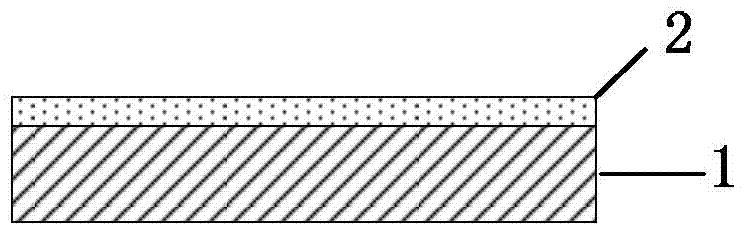

[0044] 1. Clean Si substrate 1: Boil Si substrate 1 with a mixture of hydrogen peroxide and concentrated sulfuric acid at a ratio of 1:4 at 80-85°C for 10-15 minutes to remove surface stains, and then rinse with deionized water for 10-10 minutes. 15min, dry for later use.

[0045] 2. Atomic layer deposition (ALD) is adopted on a Si substrate 1 with a thickness of 300 μm±0.05 μm, the temperature of the heat source (Hf source or Al source) is 80°C, the temperature of the cavity is 200°C, and the growth rate is 0.1nm per Prepared in a cyclic environment, the back gate high-k dielectric uses HfO 2 or Al 2 o 3 , thickness 10 ~ 25nm.

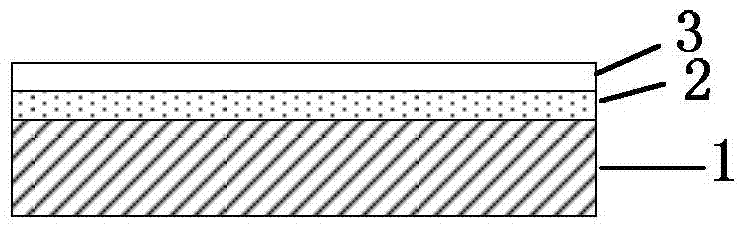

[0046] 3. Transfer the single-layer graphene 3 grown by CVD to the grown HfO with a thi...

Embodiment 1

[0052] Graphene / MoS of high dielectric constant gate dielectric in this embodiment 2 Composite channel field effect transistor devices include sequentially stacked substrates, high dielectric constant (high k) gate dielectrics, patterned graphene conductive channels, patterned MoS 2 A thin film conduction channel, and a metal source electrode and a metal drain electrode on the compound conduction channel. Among them, the substrate is an N-type phosphorus-doped single-throw silicon substrate with a (100) crystal orientation, a resistivity of 0.006-0.009Ω·cm, and a thickness of 300μm±0.05μm; a high dielectric constant (high k) gate dielectric Using HfO 2 ; The thickness of single-layer graphene is 0.4nm ~ 0.6nm; MoS 2 Film thickness is 1.5~2nm

[0053] The source-drain electrodes 5 and 6 adopt a chromium (Cr) / gold (Au) stack structure with a thickness of 10-20nm / 50-60nm;

[0054] Its preparation method of the present embodiment, concrete technological process is as follows: ...

Embodiment 2

[0062] In this embodiment, graphene / MoS based on high dielectric constant gate dielectric is produced 2 Composite channel field effect transistor device and its preparation method are similar to embodiment one, the difference is that the back gate dielectric HfO with a thickness of 20nm is grown on the substrate Si1 2 2;

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More