Ferro-electric field effect transistor based on structured carbon nano tube striped array and manufacturing method thereof

A carbon nanotube and electric field effect technology, applied in the field of memory, can solve the problems of cumbersome and complicated operations, small open current of ferroelectric field effect transistors, and easy mutual conduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

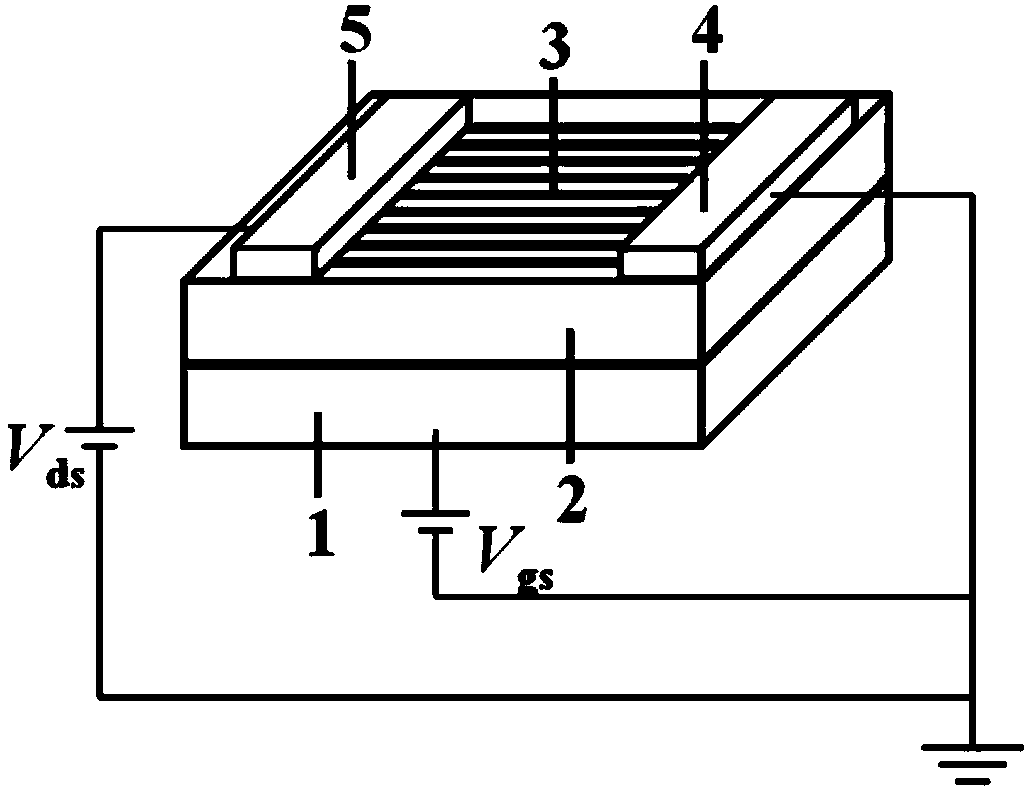

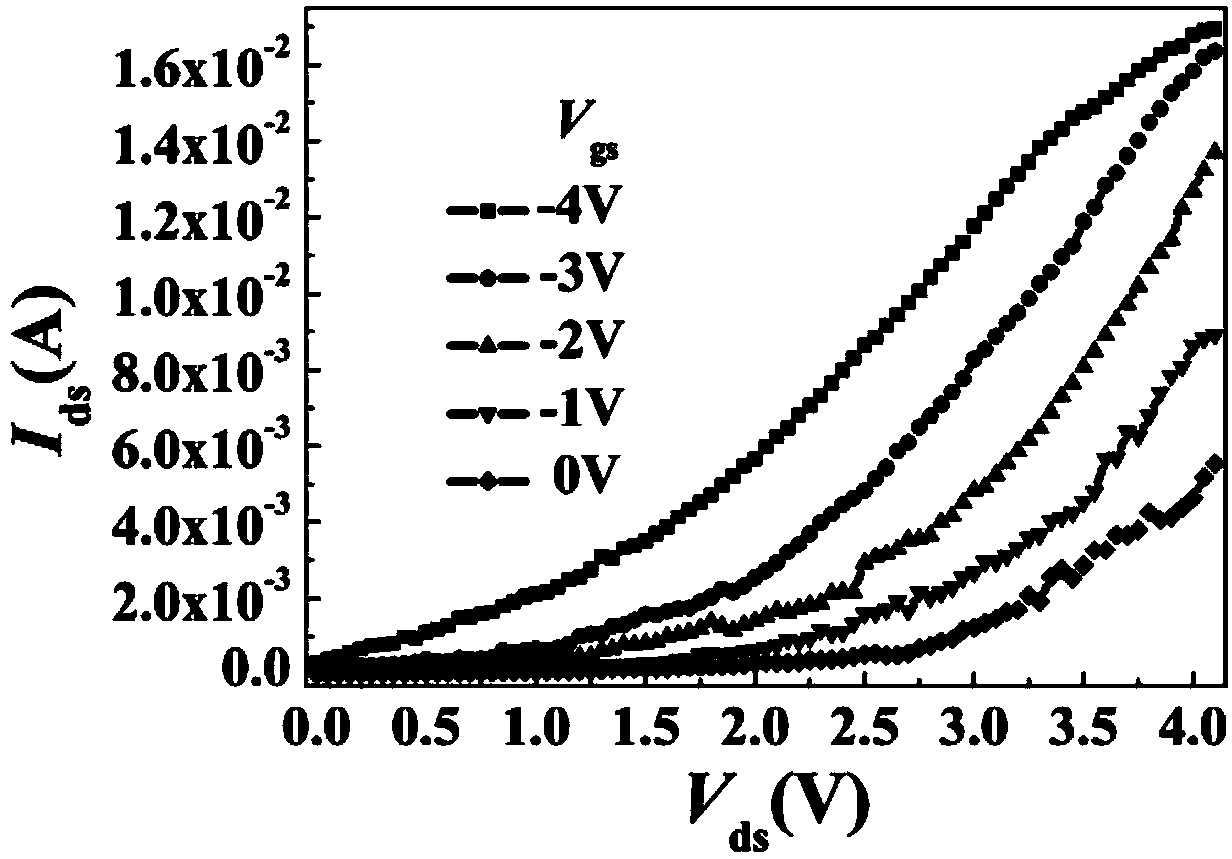

[0029] In this embodiment, Pt is used as the bottom electrode material, Bi 3.15 Nd 0.85 Ti 3 o 12 (BNT for short) is a ferroelectric field-effect transistor with a ferroelectric thin film insulating gate material, a regular MWCNT stripe array as a channel material, and Pt as a source and drain material. The specific steps are as follows:

[0030] (1) Growth of Pt bottom electrode

[0031]Clean the single crystal Si wafer, place the Pt target on the target frame, and deposit the Pt metal bottom electrode by the vacuum evaporation coating method. In order to improve the adhesion between Pt and the substrate Si, a growth Ti and SiO 2 .

[0032] (2) Growth of BNT ferroelectric thin film

[0033] Using the sol-gel method. First, prepare the BNT precursor solution. The process is: weigh 1.69785 g of bismuth nitrate crystals and 0.386495 g of neodymium nitrate powder, add them to 3 mL of glacial acetic acid until they are completely dissolved; then add 0.5 mL of acetylacetone ...

Embodiment 2

[0054] This embodiment is a ferroelectric field effect transistor with heavily doped n-type Si as the substrate and bottom electrode, BNT as the ferroelectric thin film insulating gate material, regular BWCNT stripe array as the channel material, and Pt as the source and drain materials. ,Specific steps are as follows:

[0055] (1) Growth bottom electrode

[0056] The heavily doped n-type Si is used as the substrate and bottom electrode of the ferroelectric field effect transistor.

[0057] (2) Growth of BNT ferroelectric thin film

[0058] Using the sol-gel method. The configuration process of the BNT precursor solution is the same as in Example 1, and the heat treatment process of the BNT thin film is as follows: ① 180° C., 5 minutes; ② 400° C., 5 minutes; ③ 800° C., 20 minutes. Take out the sample and continue to spin-coat the BNT film, repeat the above process 5 times, and obtain a BNT film with a uniform thickness of 340nm.

[0059] (3) Growth regular BWCNT stripe arr...

Embodiment 3

[0065] This example is to prepare a ferroelectric field effect transistor with Au as the bottom electrode material, BNT as the ferroelectric thin film insulating gate material, a regular SWCNT stripe array as the channel material, and Pt as the source and drain materials on a single crystal Si substrate. ,Specific steps are as follows:

[0066] (1) Growth of Au bottom electrode

[0067] Clean the single crystal Si wafer, place the Au target on the target frame, and deposit the Au metal bottom electrode by vacuum evaporation coating method.

[0068] (2) Growth of BNT ferroelectric thin film

[0069] Using the sol-gel method. The configuration and preparation process of the BNT precursor solution are the same as in Example 1. The heat treatment process of the BNT thin film is: ① 180°C, 5min; ② 400°C, 5min; ③ 700°C, 10min. Take out the sample and continue to spin-coat the BNT film, repeat the above process 7 times, and obtain a BNT film with a uniform thickness of 380nm.

[0...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More