Method for manufacturing thin film transistor array panel for display device

a technology of thin film transistor array panel and manufacturing method, which is applied in the direction of optics, instruments, electrical equipment, etc., can solve the problems of deterioration of adhesiveness between the organic insulating layer and the ito film, and achieve the effect of minimizing contact resistance and good adhesiveness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0042] First, a transflective type LCD according to the present invention will be described in detail with reference to FIGS. 1 and 2.

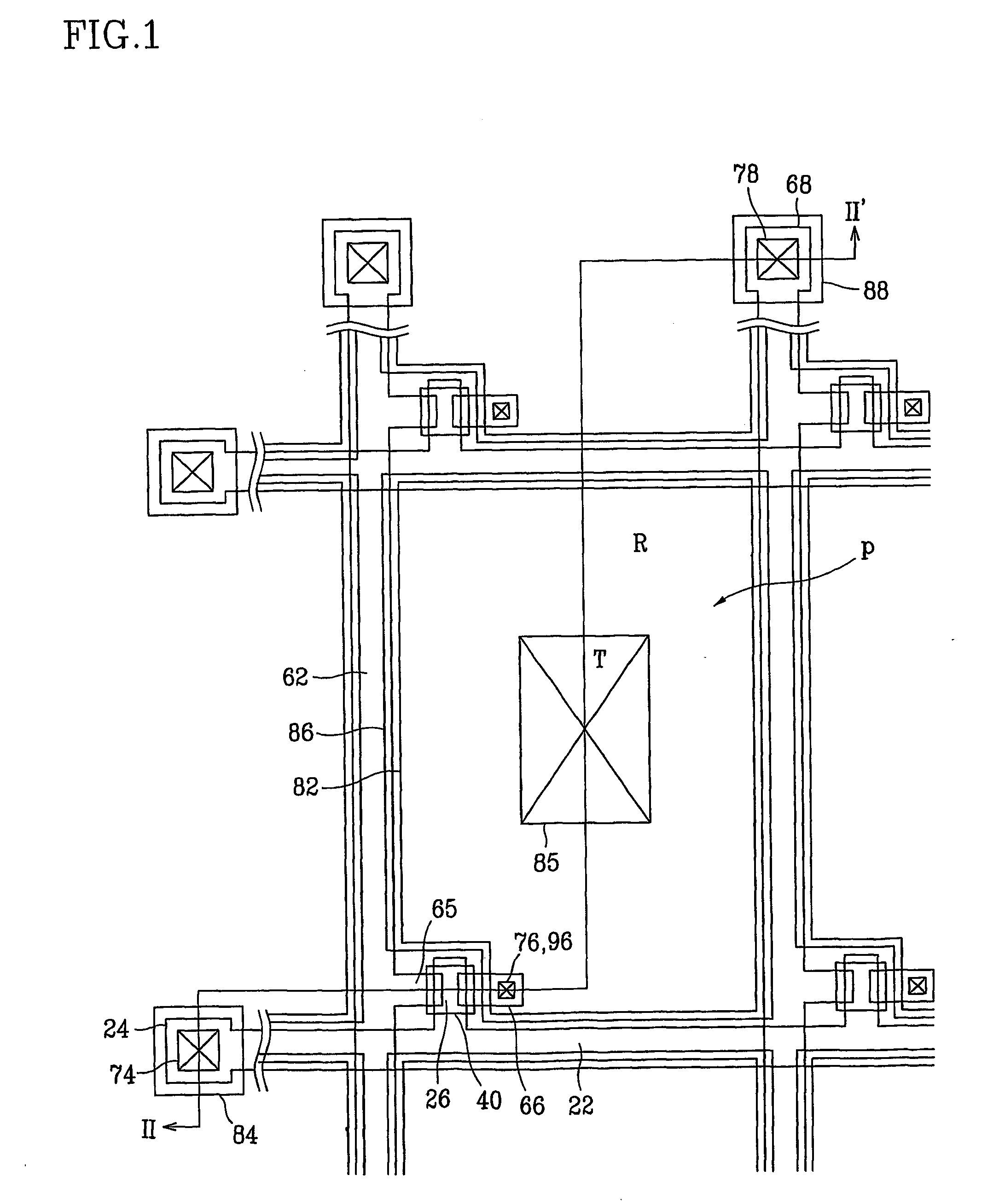

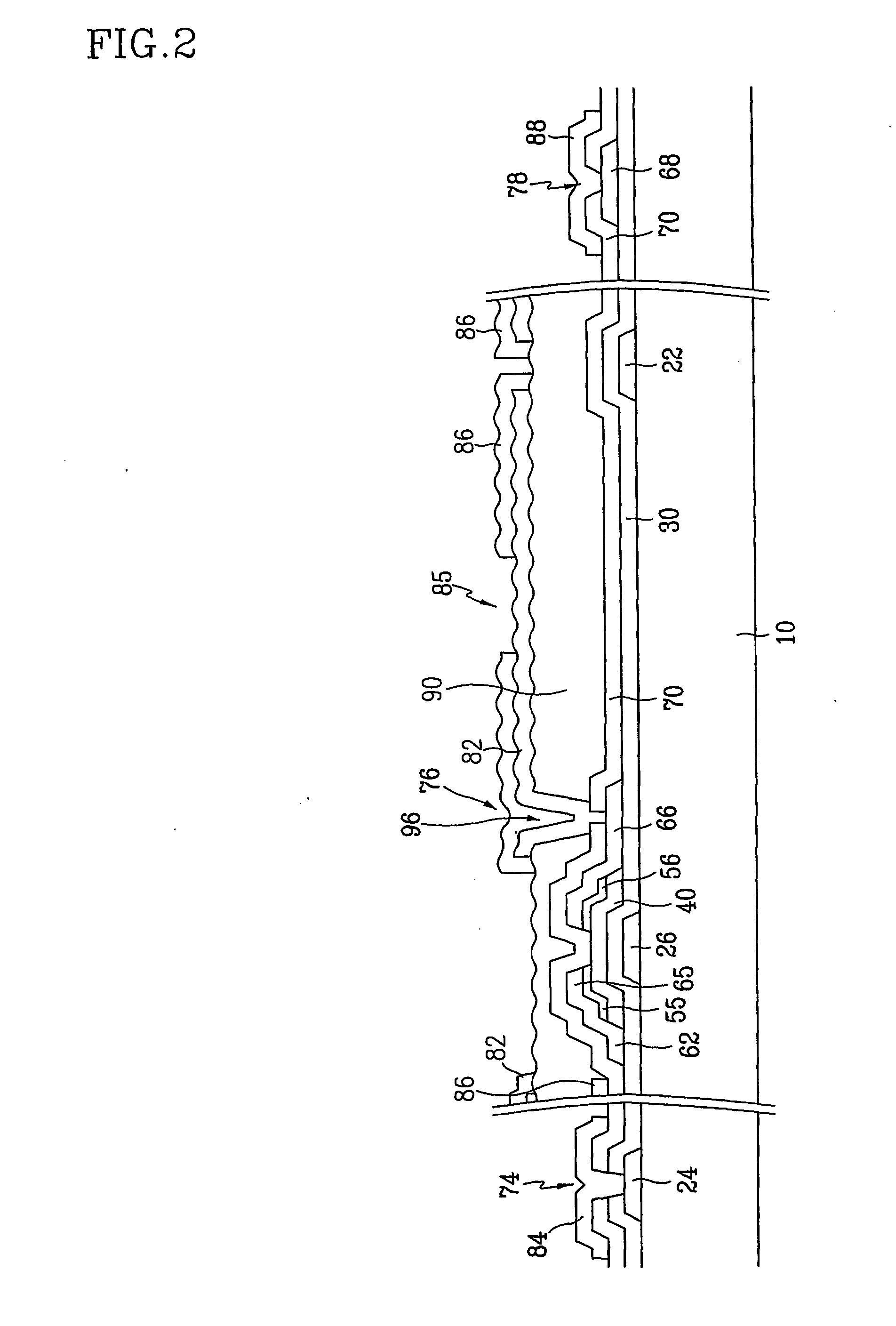

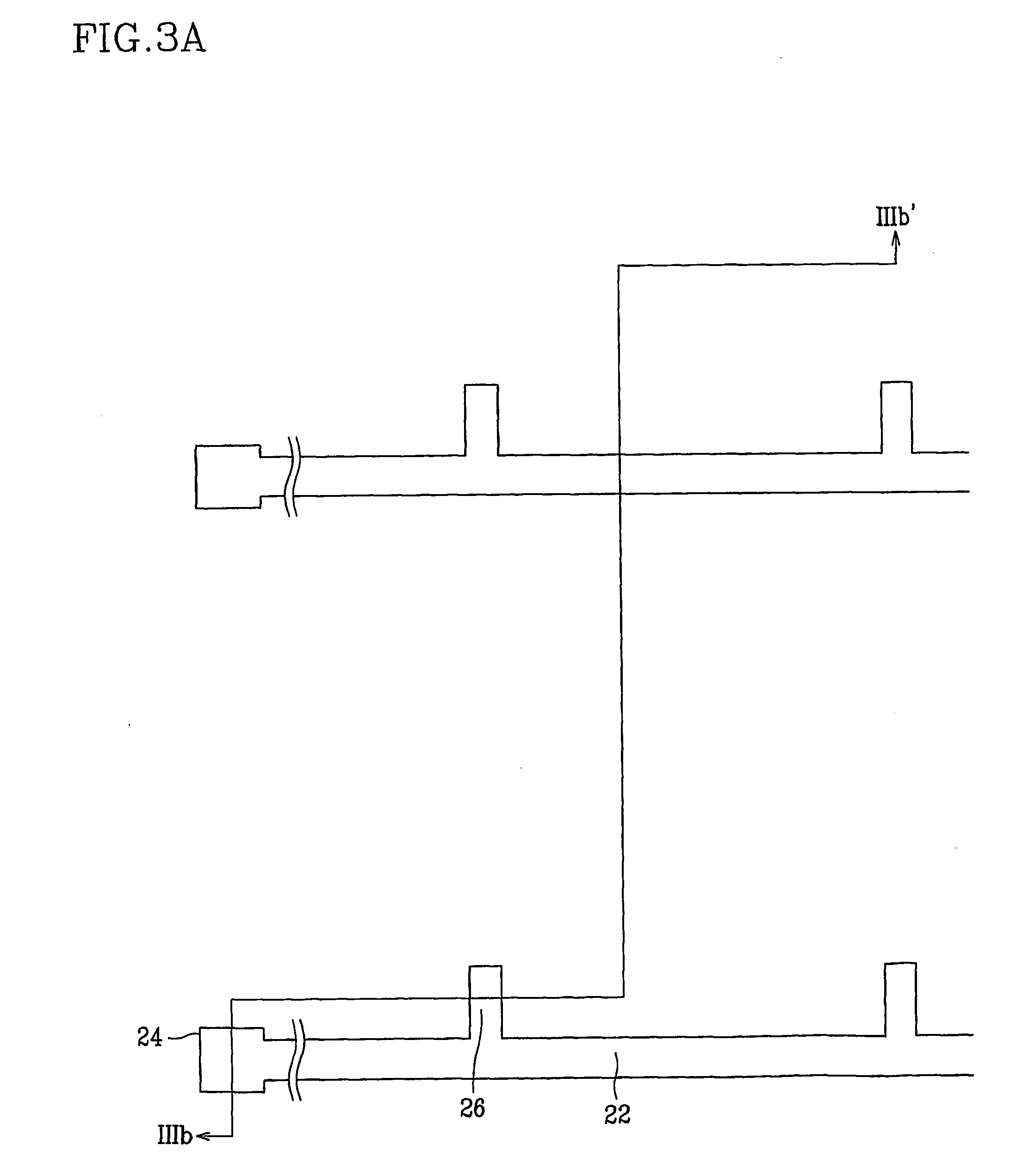

[0043]FIG. 1 is a layout view of a TFT array panel for a transflective type LCD according to a first embodiment of the present invention, and FIG. 2 is a sectional view of the TFT array panel shown in FIG. 1 taken along the line II-II′.

[0044] A gate wire is formed on an insulating substrate 10. The gate wire includes either a single layer preferably made of Ag, Ag alloy, Al and Al alloy having low resistivity, or multiple layers including the single layer. The gate wire includes a plurality of gate lines 22 extending substantially in a transverse direction, a plurality of gate pads 24 connected to one ends of the gate lines 22 for receiving gate signals from external devices and transmitting the gate signals to the gate lines 22, and a plurality of gate electrodes 26 of TFTs connected to the gate lines 22. The gate wire may overlap pixel electrodes 8...

second embodiment

[0067] A TFT array panel for a reflective type LCD according to the present invention will be described in detail with reference to FIGS. 10 and 11.

[0068] As shown in FIGS. 10 and 11, the structure is almost the same as the structure according to the first embodiment.

[0069] However, different from the first embodiment, a plurality of reflecting films 86 are located directly on an organic insulating layer 90 and in direct electrical connection with a plurality of drain electrodes 66 through a plurality of contact holes 76 and 96. In addition, the reflecting film 86 occupies the entire pixel area.

[0070] Moreover, a plurality of gate wire 22, 24 and 26 and a plurality of data wire 62, 65 and 66 overlap relevant pixel electrodes 82 via the organic insulating layer 90 with low dielectric constant to give maximum aperture ratio.

[0071] Furthermore, a data wire 62, 65, 66 and 68 includes a conductor pattern 64 for storage capacitors overlapping the gate lines 22, and the pixel electrodes...

fourth embodiment

[0076]FIG. 12 is a layout view of a TFT array panel for an LCD according to the present invention, and FIGS. 13 and 14 are sectional views of the TFT array panel shown in FIG. 12 taken along the line XIII-XIII′ and the line XIV-XIV′ of FIG. 12, respectively.

[0077] As in the second embodiment, a gate wire is formed on an insulating substrate 10. The gate wire is preferably made of a material with low resistivity such as Ag, Ag alloy, Al and Al alloy. The gate wire includes a plurality of gate lines 22, a plurality of gate pads 24, and a plurality of gate electrodes 26. The gate wire further includes a plurality of storage electrodes 28 formed on the substrate, which are substantially parallel to the gate lines 22 and applied with a predetermined voltage such as a common voltage from an external source, which is also applied to a common electrode of an upper panel. The storage electrodes 28 overlap a storage capacitor conductor pattern connected to pixel electrodes 82, which will be d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More