VDMOS transistor and preparation method thereof

A technology of transistors and polysilicon layers, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as poor reliability, VDMOS performance degradation, and increased gate leakage current, achieving small leakage current, Good reliability and less number of steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

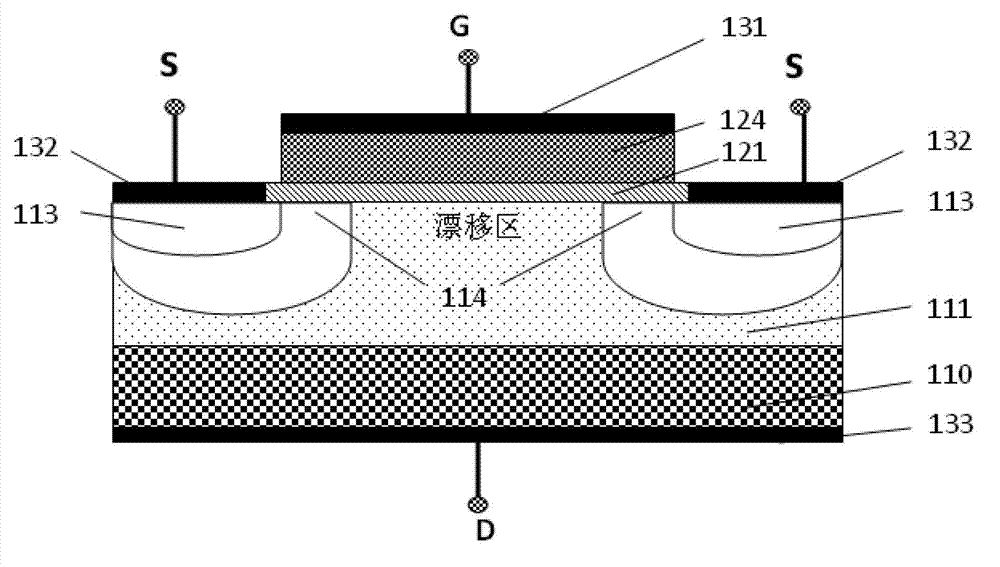

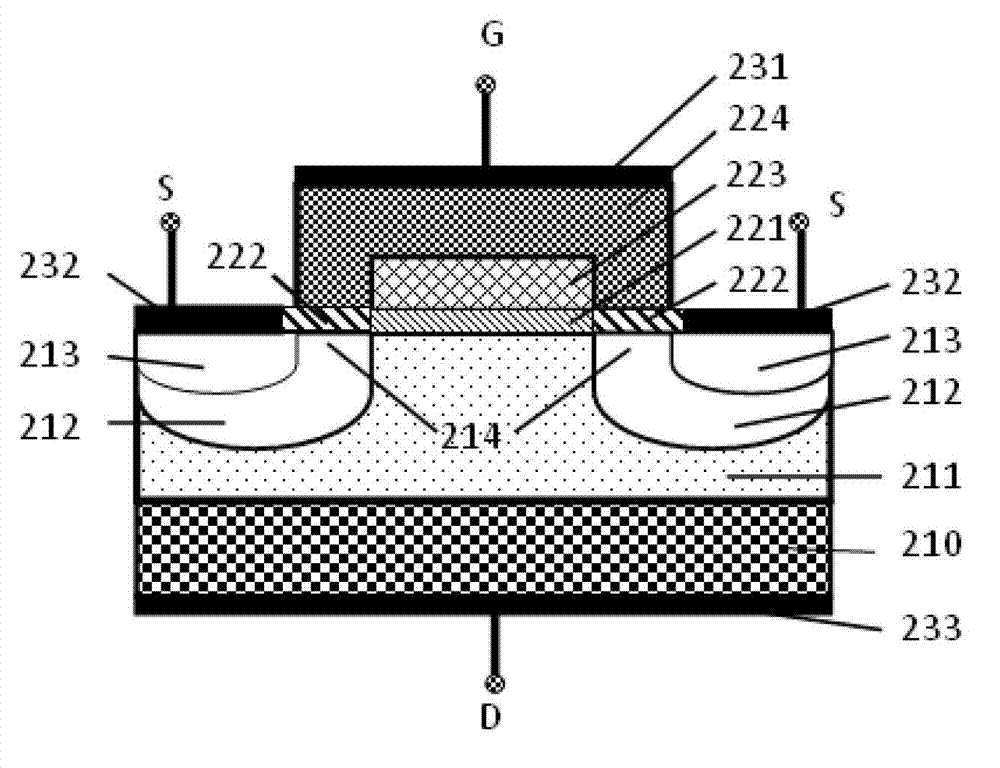

[0075] The first conductivity type is N-type, the second conductivity type is P-type, the prepared transistor is an N-channel MOS transistor, and the provided substrate is a silicon substrate.

[0076] A kind of preparation method of VDMOS transistor, comprises, in N + Fabrication of N over silicon substrates - epitaxial layer, the N - A gate structure is fabricated over the epitaxial layer.

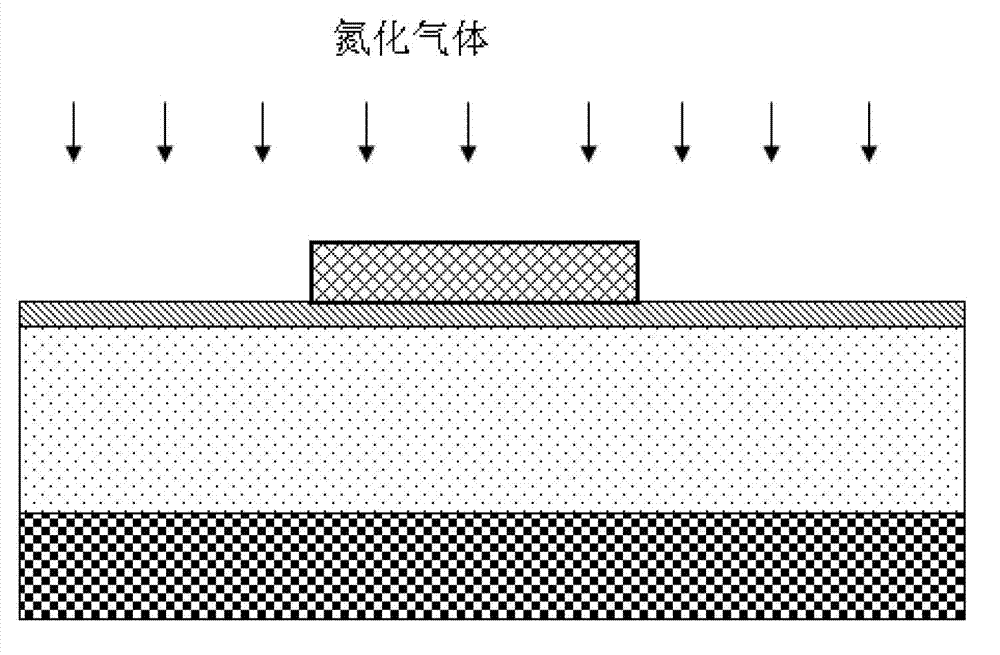

[0077] The preparation method of the gate structure specifically includes the following steps:

[0078] (1) A thermal oxidation method is used to form a thickness of the silicon dioxide layer;

[0079] (2) On the surface of the silicon dioxide layer, a semi-insulating polysilicon SIPOS layer is formed by a low-pressure chemical vapor deposition method, and a silane SiH 4 and laughing gas N 2 O is used as the reaction gas, and by controlling the flow ratio of the reaction gas and other process conditions, the thickness of the semi-insulating polysilicon SIPOS is about Resistivity...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More