Patents

Literature

48results about How to "Small dielectric coefficient" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

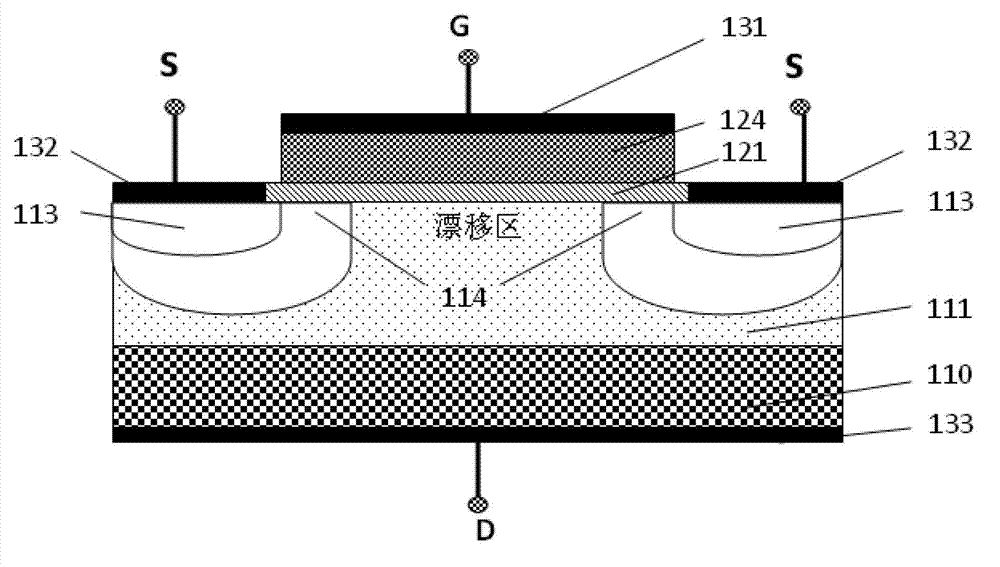

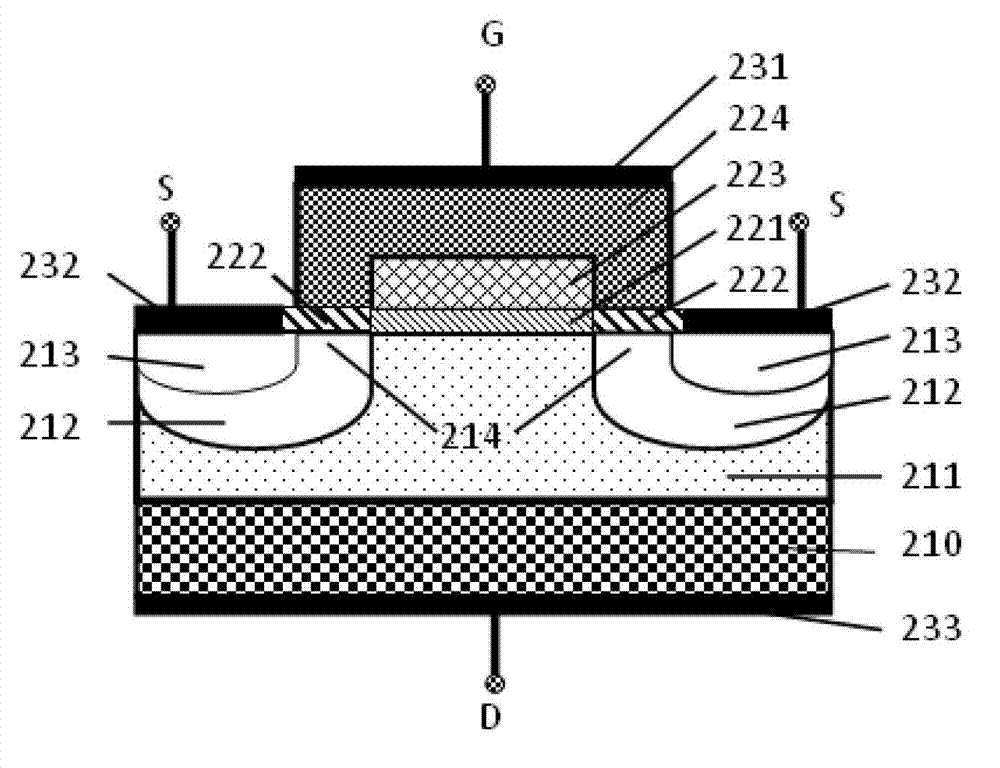

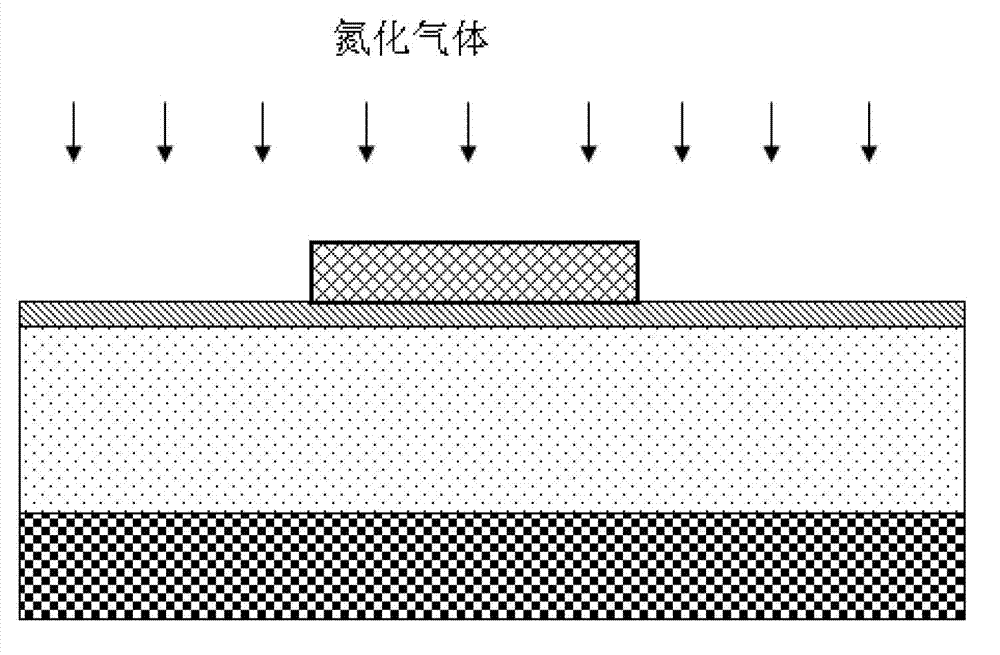

VDMOS transistor and preparation method thereof

InactiveCN103035732AIncreasing the thicknessReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceSilicon dioxide

The invention discloses a VDMOS transistor and a preparation method thereof and belongs to the field of semiconductors. The VDMOS transistor comprises a first conduction type substrate, a first conduction type epitaxial layer, a second conduction type injection region, a first conduction type highly doped source region and a grid structure, the second conduction type injection region and the first conduction type highly doped source region are arranged in the epitaxial layer, and the grid structure comprises a grid insulating layer, a semi-insulating polycrystalline silicon layer, a silicon oxynitride layer and a polycrystalline silicon layer. The grid insulating layer is arranged above a drift region of the epitaxial layer, the semi-insulating polycrystalline silicon layer is arranged above the grid insulating layer, the silicon oxynitride layer is arranged above a channel region, and the polycrystalline silicon layer is covered on the semi-insulating polycrystalline silicon layer and the silicon oxynitride layer. A heat nitriding silicon oxynitride layer is introduced into the preparation method, a traditional silica layer which is used as a gate medium layer on a channel is replaced, and the semi-insulating polycrystalline silicon layer is added on an oxide layer which is arranged above the drift region of the epitaxial layer. The VDMOS transistor and the preparation method thereof can obviously reduce grid-drain capacitance and achieve overcoming the defects that insulating performance of the grid insulating layer is poor, current leaking of a grid electrode is increased, and degeneration of the VDMOS performance is unreliable.

Owner:SOUTH CHINA UNIV OF TECH

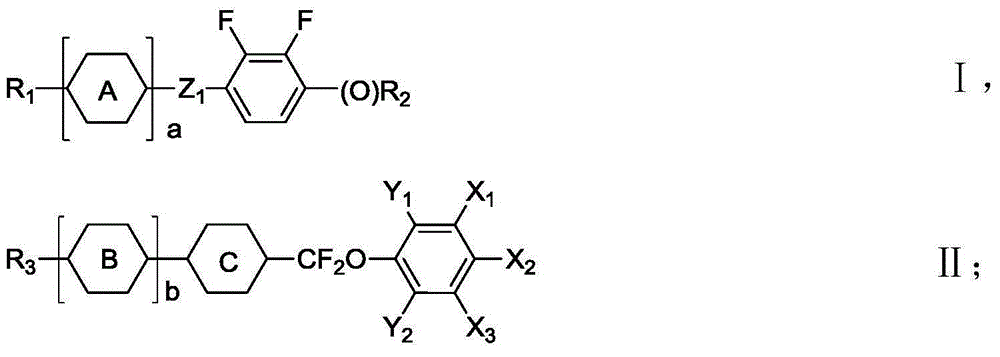

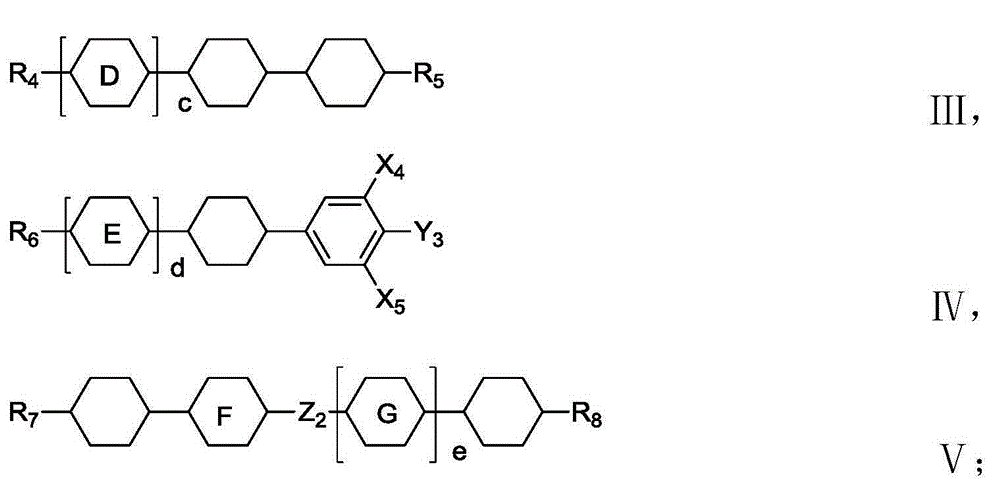

Positive-negative-mixed liquid crystal composition

ActiveCN105131975AImprove transmittanceLow rotational viscosityLiquid crystal compositionsNon-linear opticsCrystallographyCharge retention

The invention discloses a positive-negative-mixed liquid crystal composition. The positive-negative-mixed liquid crystal composition is characterized by comprising a component A composed of at least one kind of negative compounds shown in the first general formula (please see the specification for the first general formula) and a component B composed of one or more kinds of positive compounds shown in the second general formula (please see the specification for the second general formula). The liquid crystal composition has the advantages of being positively dielectric, high in charge retention rate, low in rotary viscosity, short in response time and particularly high in transmittance; the positive-negative-mixed liquid crystal composition is suitable for manufacturing a high-transmittance and rapid-responding TFT-LCD.

Owner:SHIJIAZHUANG CHENGZHI YONGHUA DISPLAY MATERIALS CO LTD

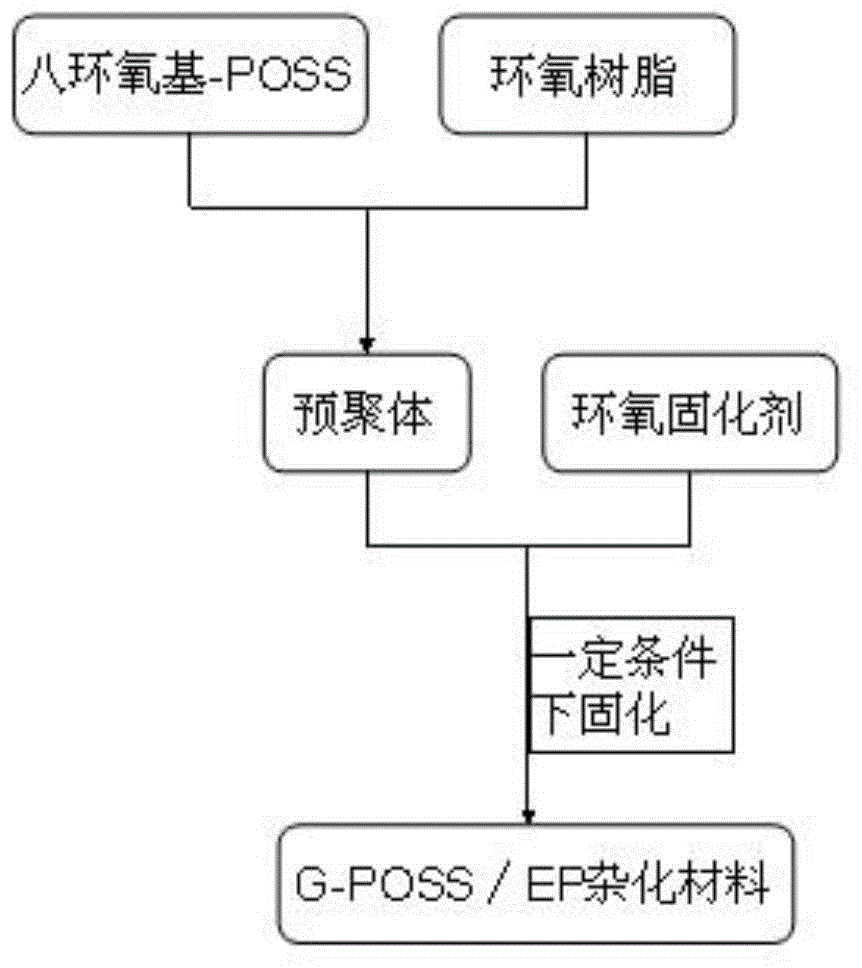

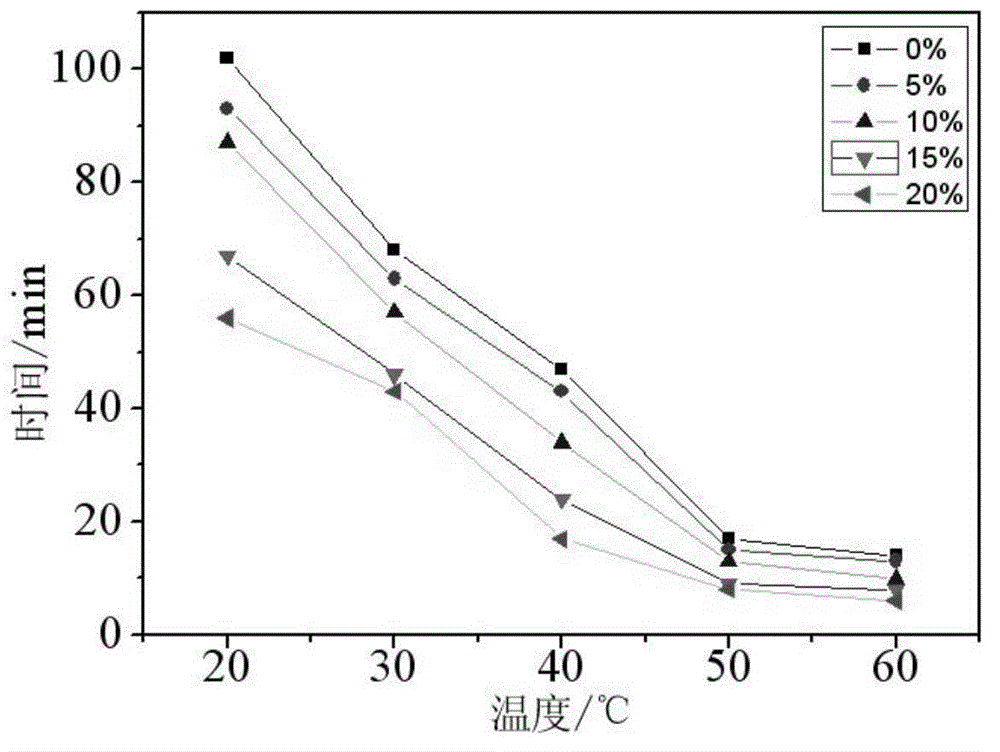

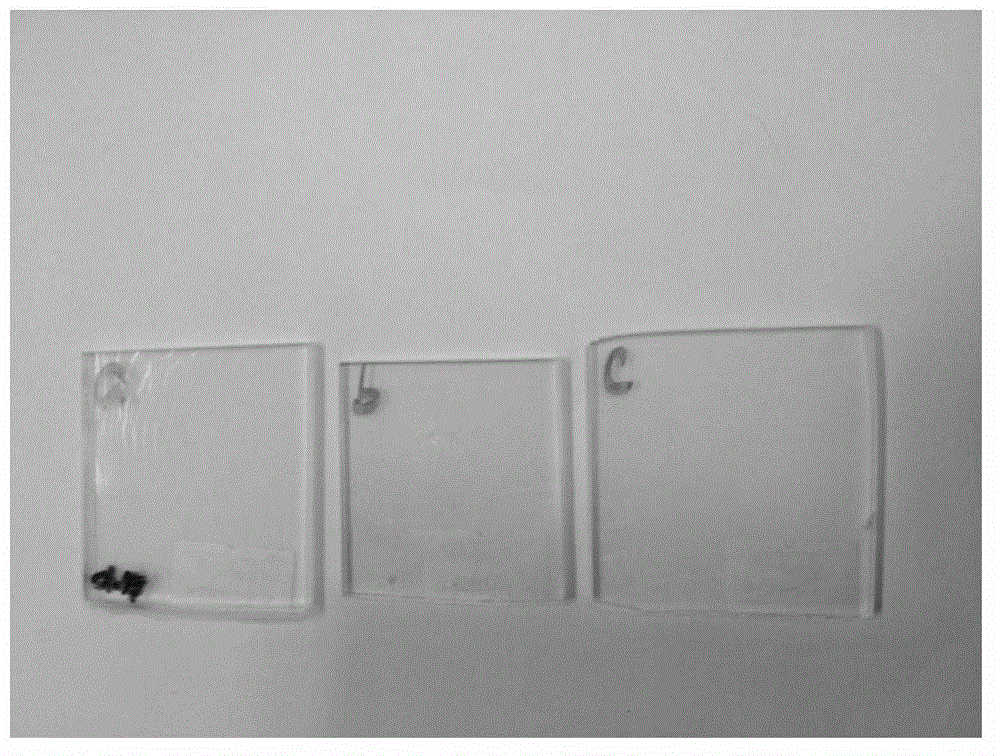

Low dielectric constant polyhedral oligomeric silsesquioxane (POSS)/ epoxy resin hybrid material and preparation method

The invention relates to a low dielectric constant polyhedral oligomeric silsesquioxane (POSS) / epoxy resin hybrid material and a preparation method. Epoxy resin and eight epoxy group polyhedral oligomeric silsesquioxane (G-POSS) are evenly mixed in a 80 DEG C breaker according to a certain proportion, an equivalent amount of curing agent triethylene tetramine (TETA) (an amino group in the TETA and an epoxy group in the G-POSS, epoxy resin (EP) are measured according to a 1:1 molar rate) is added and fully stirred, after vacuum defoamation is conducted for 20-30 minutes, the mixture is slowly poured into a preheating mold, conducted solidification in a stove 50 DEG C / 2 hours, 70 DEG C / 3 hours and 80DEG C / 1 hour, cooled to room temperature along with the stove and processed for 4-6 hours after demolding. The low dielectric constant POSS / epoxy resin hybrid material is small in average grain size and excellent in transparent performance, mechanical property and dielectric property.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

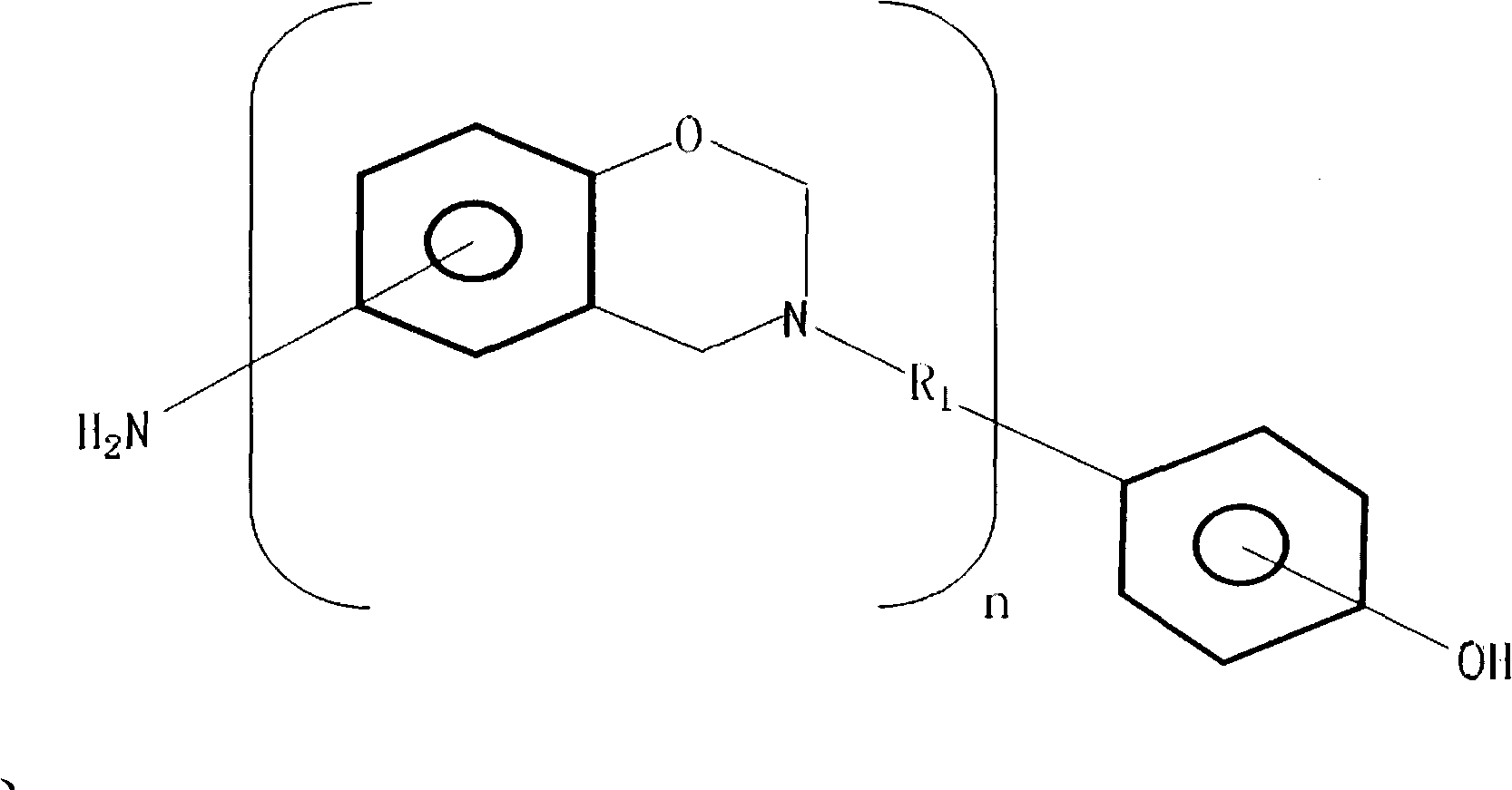

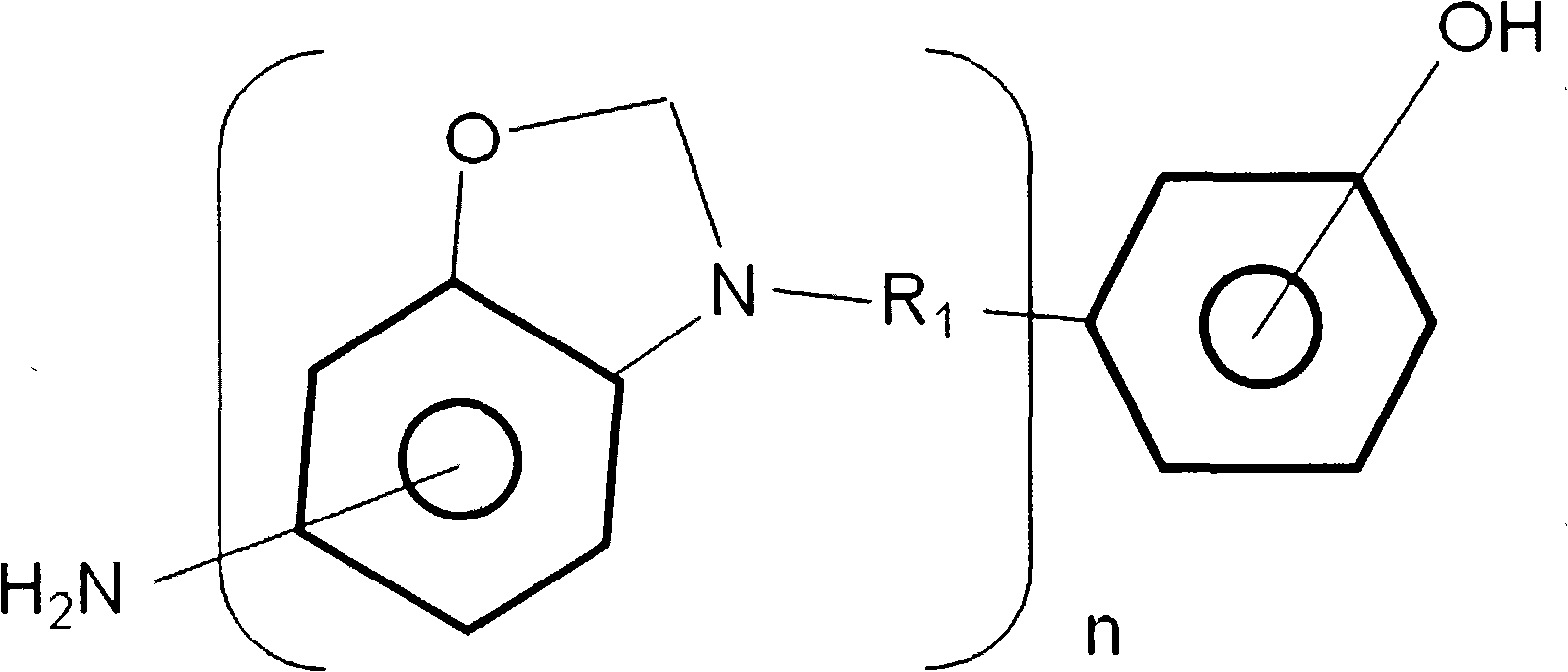

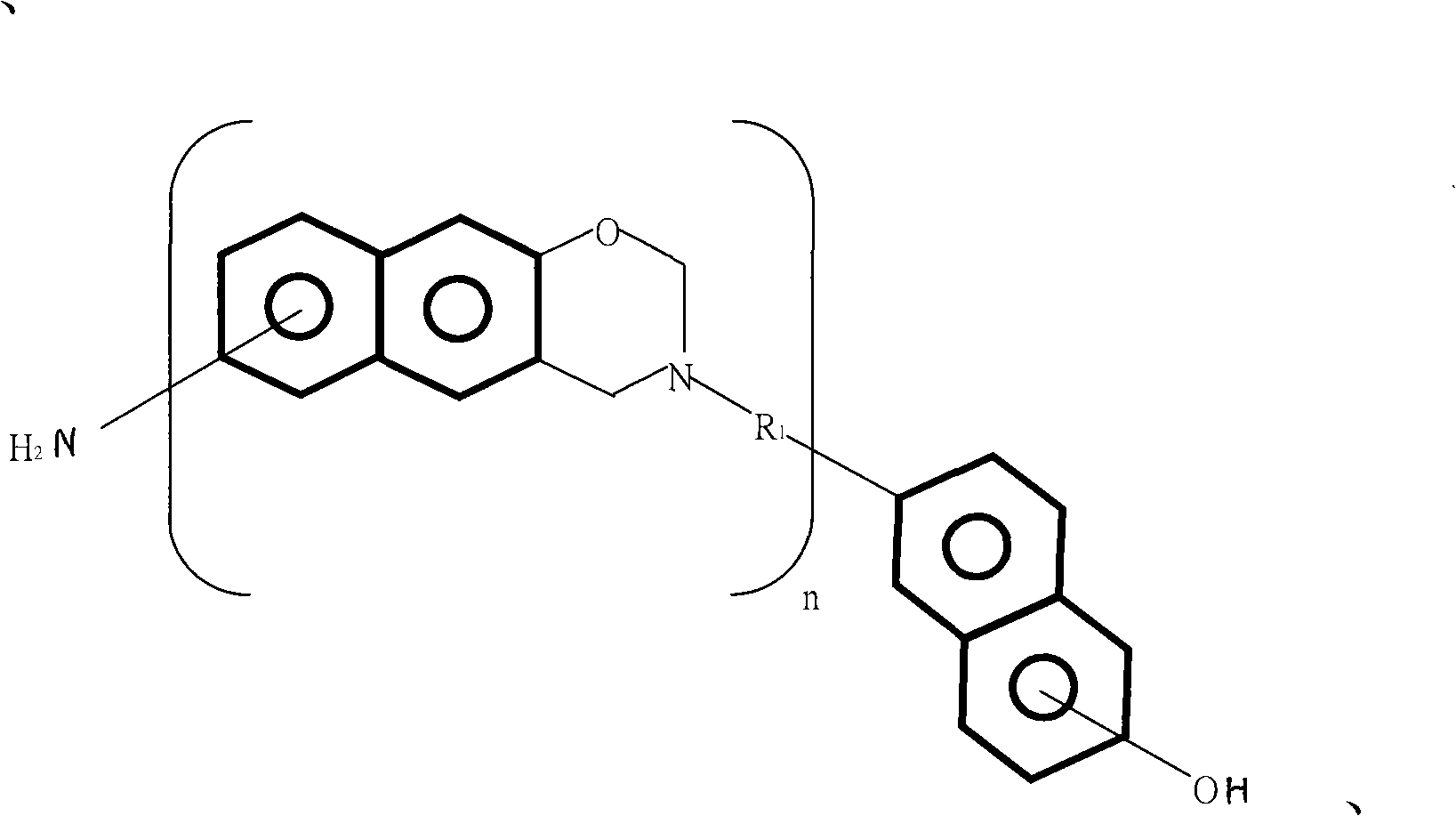

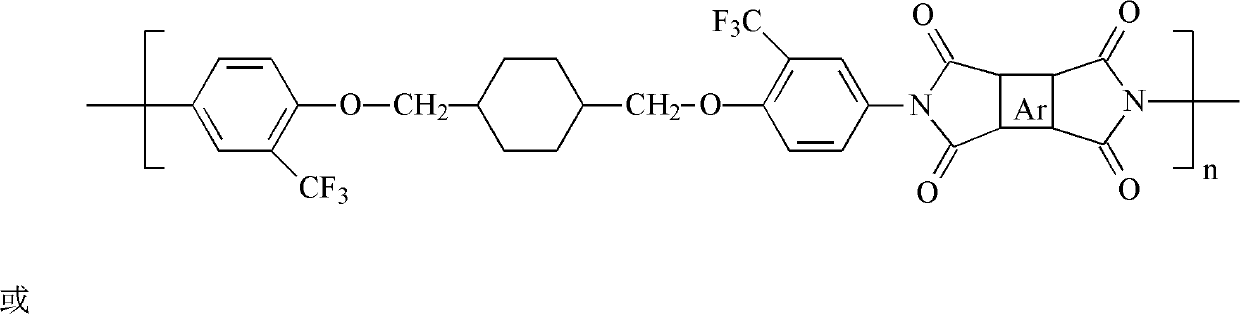

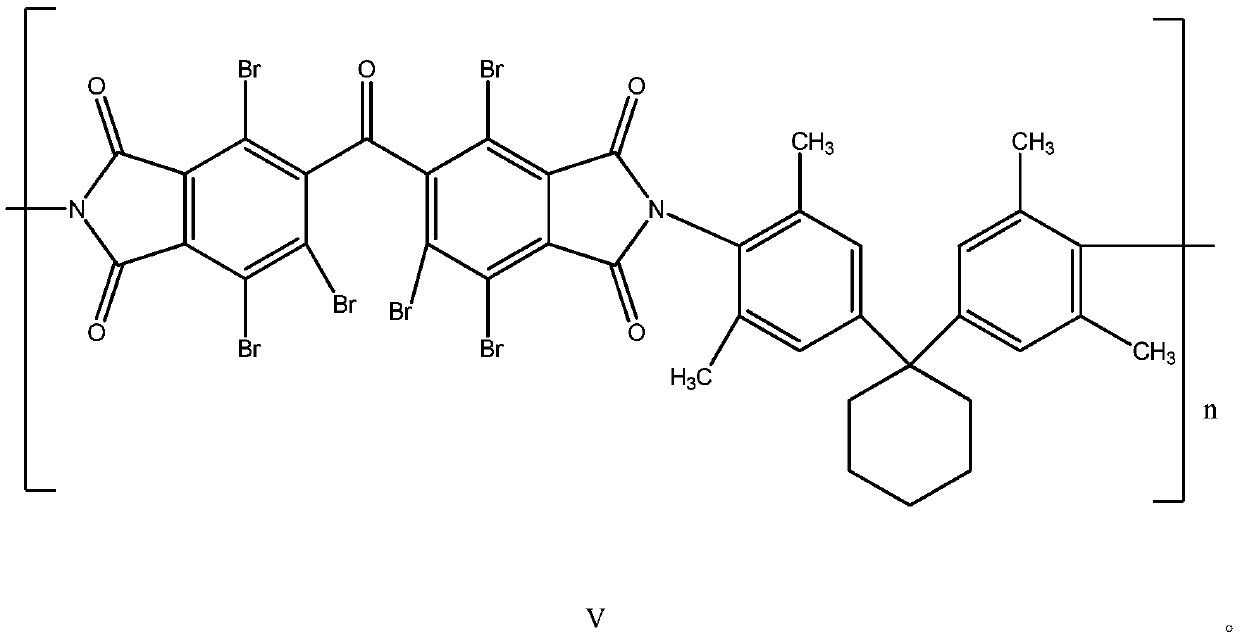

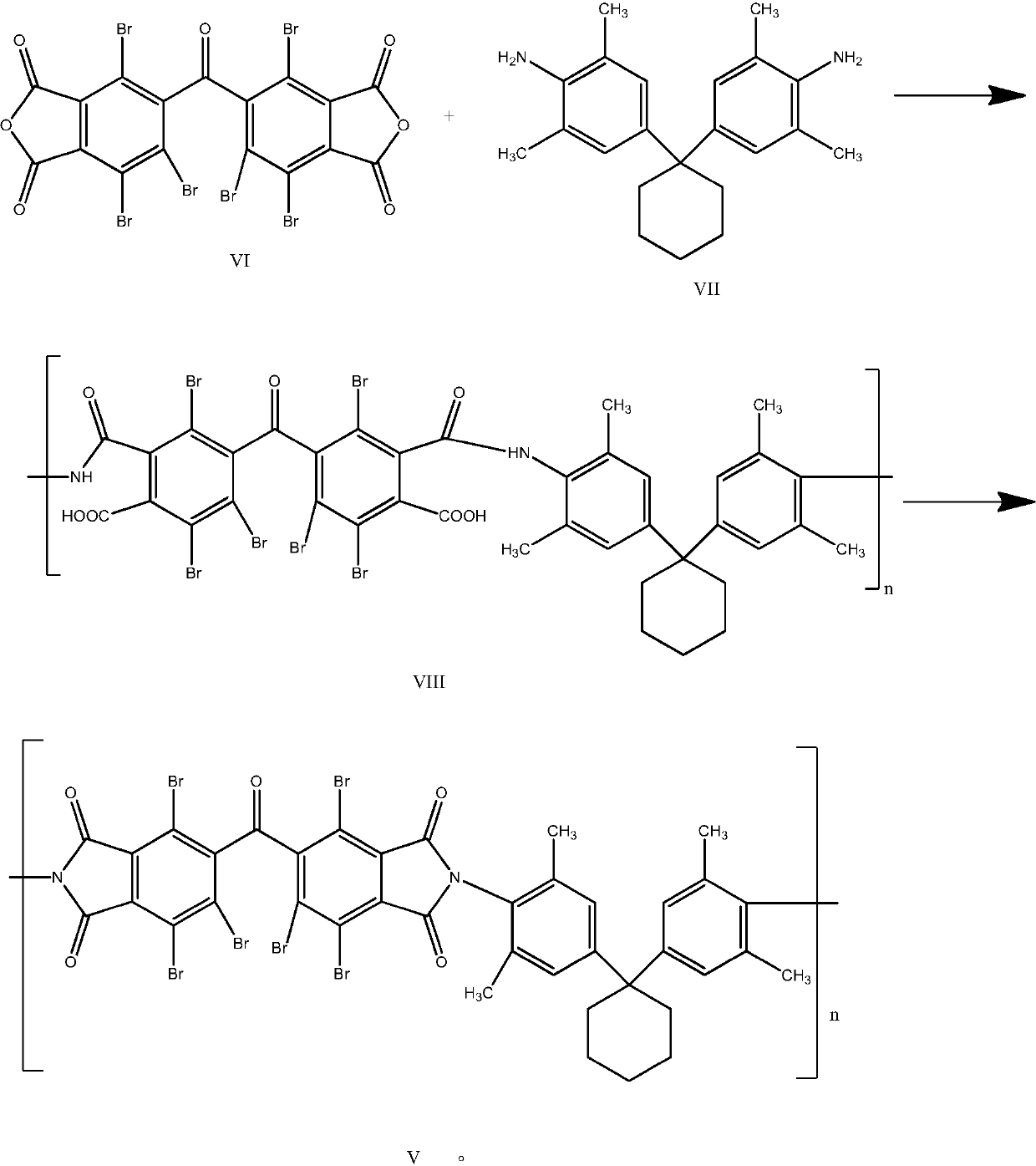

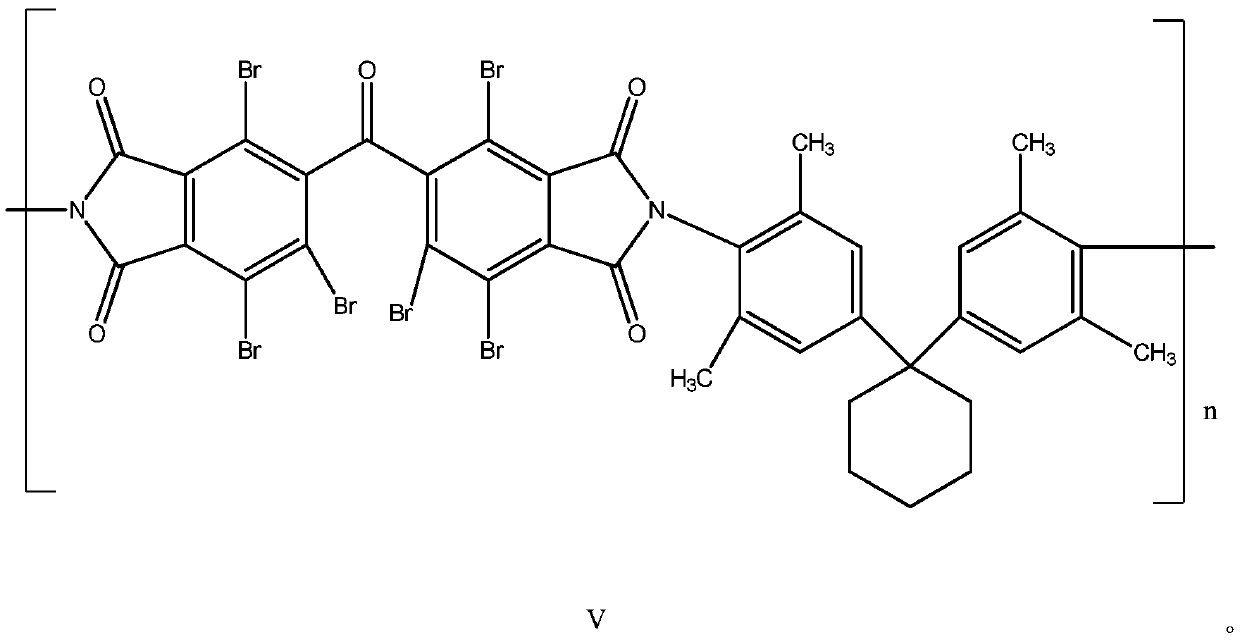

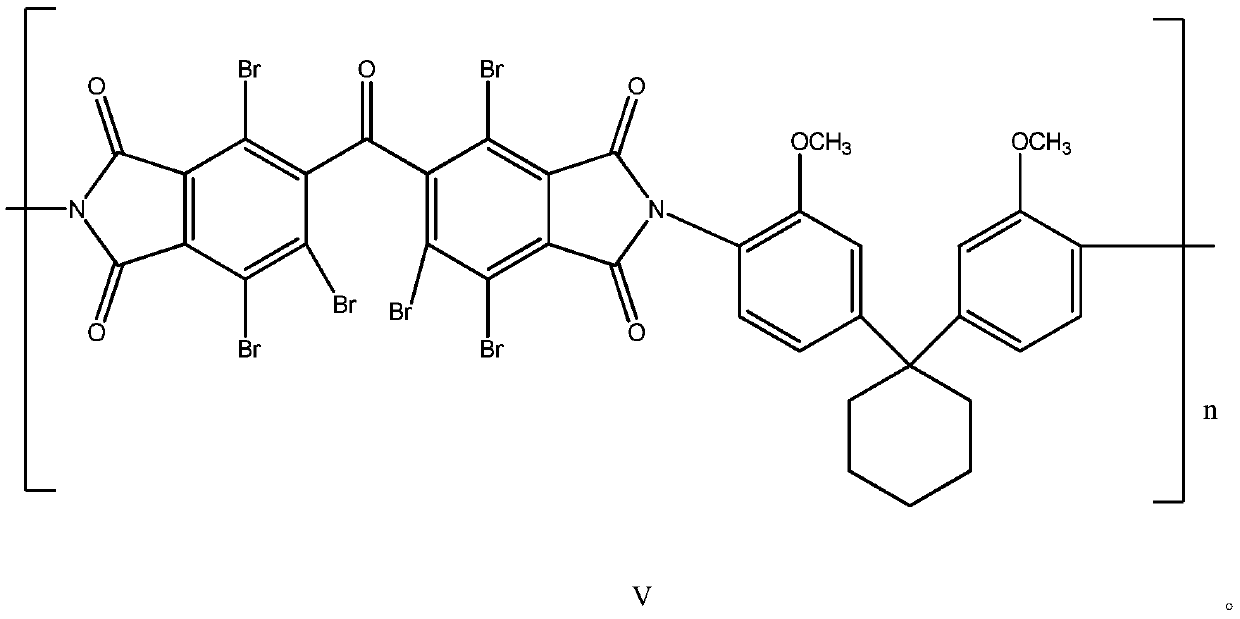

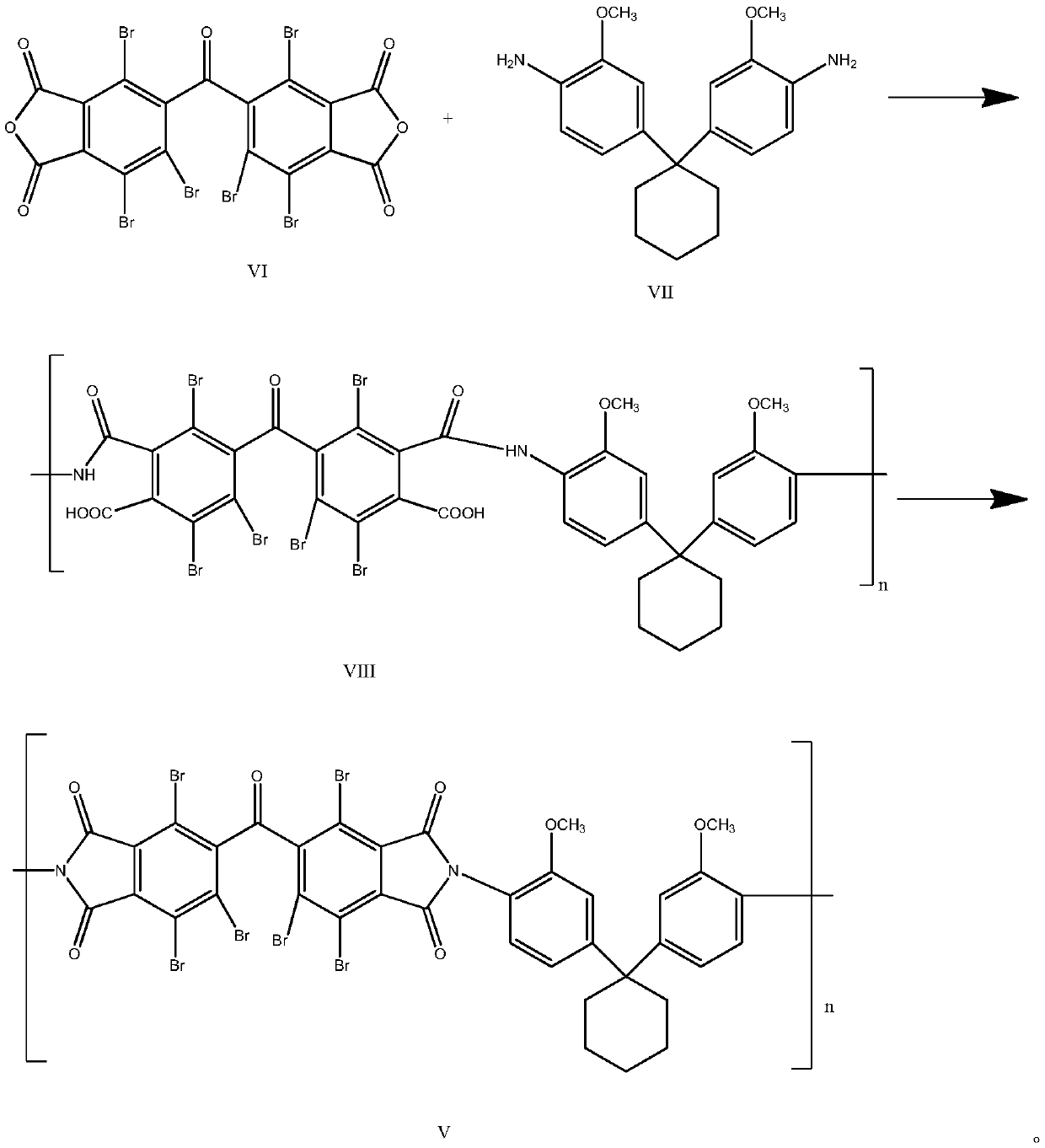

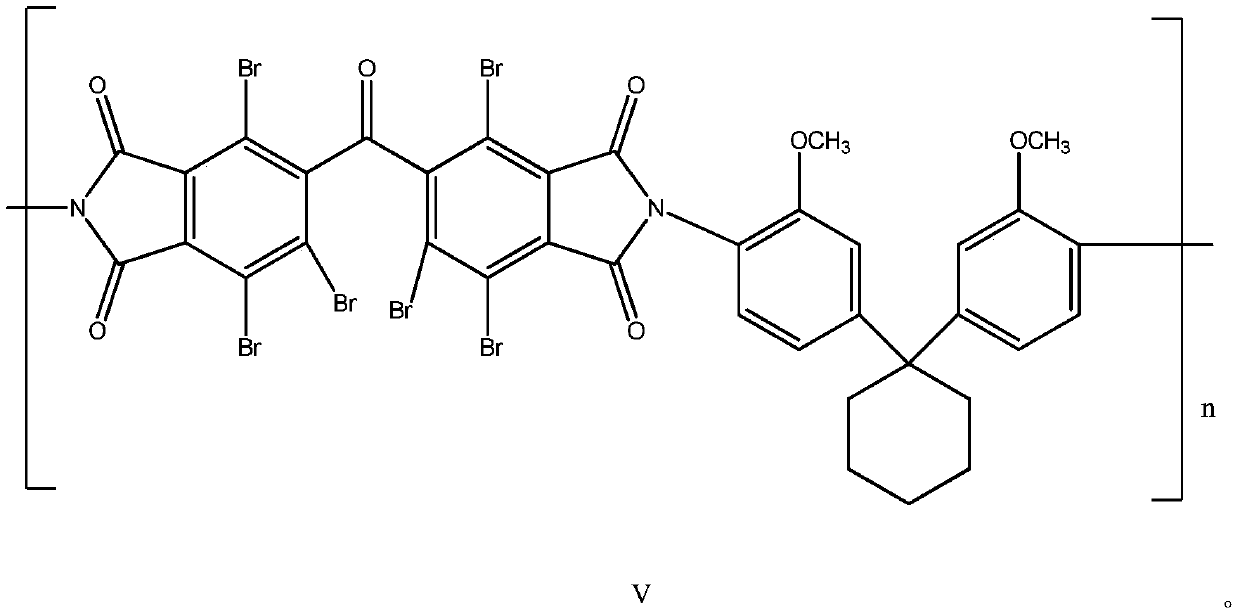

Polymer material and application thereof

InactiveCN102108068ABondingSmall dielectric coefficientOrganic chemistryCircuit susbtrate materialsPolymer scienceOxygen

The invention relates to a polymer material. The polymer material is a long-chain nitrogen-oxygen heterocyclic benzo compound and comprises a plurality of nitrogen-oxygen heterocyclic benzo structures, wherein, the plurality of nitrogen-oxygen heterocyclic benzo structures are connected with each other through at least one structure among covalent bonds, methylene and isopropylidene. The invention further relates to the application of the polymer material.

Owner:ELITE MATERIAL

High heat conductivity insulation composite and preparation method thereof

ActiveCN103187131AImprove thermal conductivityHigh thermal conductivitySemiconductor/solid-state device detailsSolid-state devicesFiberComposite film

The invention relates to a high heat conductivity insulation composite and a preparation method thereof, and belongs to the technical field of electronic packaging. The composite consists of a high heat conductivity composite and an insulation layer plated on the high heat conductivity composite, wherein the high heat conductivity composite is a composite of reinforced particles or fibers and a matrix; the matrix is copper, aluminum or silver; and the insulation layer is a diamond, aluminum nitride or boron nitride ceramic film or a composite film of diamond and aluminum nitride or boron nitride. The composite is prepared by depositing the insulation film on the surface of the high heat conductivity composite by a chemical vapor deposition technology. The high heat conductivity insulation composite achieves high heat conductivity and insulation under applications with specific insulating property requirements, and is applicable to integrated circuit systems, high-power or high power density devices and the like.

Owner:GRIMAT ENG INST CO LTD

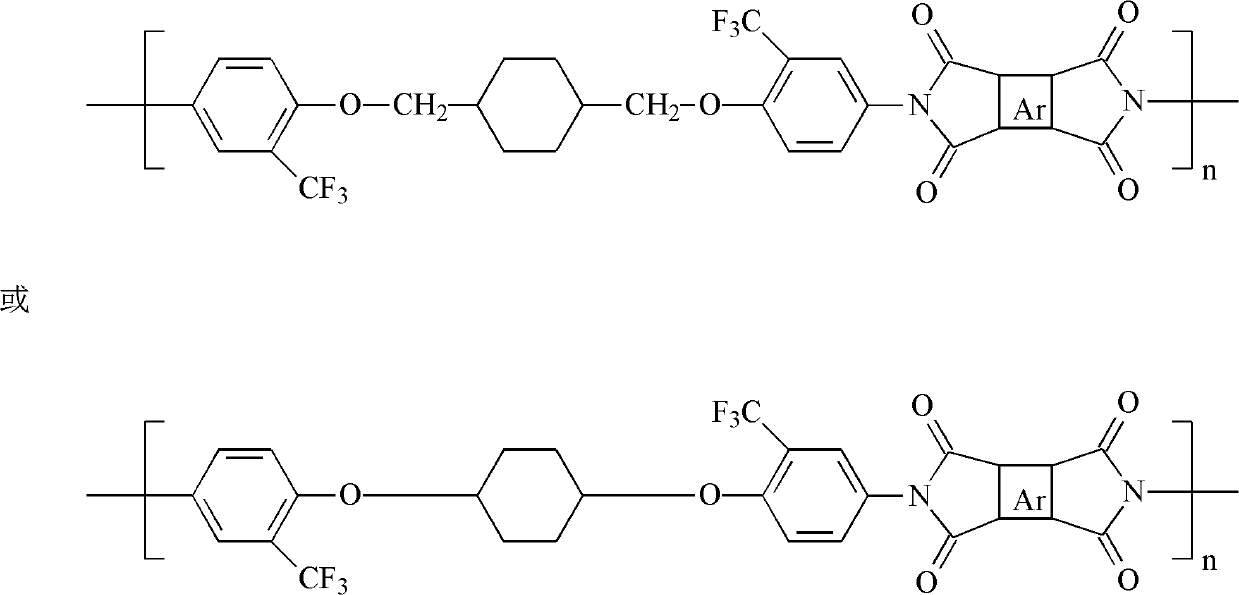

Polyimide and preparation method thereof

InactiveCN102250354ASolve solubilitySolve shortcomings such as optical transparencySolubilityOptical transparency

The invention relates to polyimide prepared from a trifluoromethyl-substituted aromatic diamine monomer containing a cyclohexane structure and a preparation method thereof. The molecular structural formula of polyimide is shown as the specification. The preparation method comprises the following steps: dissolving a trifluoromethyl-substituted aromatic diamine monomer containing the cyclohexane structure and an aromatic dianhydride monomer in an organic solvent in a molar ratio of 1:1 under the protection of nitrogen, adding isoquinoline to be used as the catalyst, performing a condensation reaction at 90-120 DEG C for 2-6 hours, performing an imidization reaction at 190-210 DEG C for 10-24 hours, performing a one-step polymerization reaction, pouring the reaction product in methanol or ethanol, collecting the separated precipitate, and drying to obtain fibrous polyimide. The method modifies the one-step preparation method of polyimide; and the prepared polyimide can be used to solve the defects of the traditional polyimide film on dissolubility, optical transparency and the like, and correct the problems such as high cost required by the manufacturing process and poor electric properties.

Owner:DONGHUA UNIV

Silica microparticle, composition forming polyimide aerogel, polyimide aerogel and manufacturing method thereof, and composite material

The invention provides a silica microparticle, a composition forming a polyimide aerogel, the polyimide aerogel and a manufacturing method thereof, and a composite material. The silica microparticle containing an amino group is prepared by subjecting alkoxy silane as shown in a formula (I) and alkoxy silane as shown in a formula (II) to hydrolytic condensation in the presence of a catalyst, wherein the formula (I) is Si(OR<1>)<4>, and the formula (II) is (NH<2>-Y)<m>-Si(OR<2>)<4-m>; in the formula (I), R<1> is an alkyl group with a carbon number of 1 to 10; and in the formula (II), Y is an alkyl group with a carbon number of 1 to 10 or an alkyl group with a carbon number of 2 to 10, R<2> is an alkyl group with a carbon number of 1 to 10, and m is an integer in a range of 1 to 3. According to the invention, the polyimide aerogel has the characteristics of high porosity, good thermal insulation properties, good flexural strength, flame resistance, resistance to UV light and chemicals, low dielectric coefficient and the like, does not need low-surface-energy solvents like hexane and pentane and a carbon dioxide supercutical fluid in the process of preparation, and is applicable to the composite material.

Owner:TAIWAN TEXTILE RESEARCH INSTITUTE

Antioxidation anticorrosion transformer oil containing multiple nanoparticles and preparation method thereof

ActiveCN104130829AImprove insulation performanceSmall dielectric coefficientAdditivesButylated hydroxytolueneOxidation resistant

Disclosed antioxidation anticorrosion transformer oil containing multiple nanoparticles is characterized by being prepared from the following raw materials in parts by weight: 1000-1500 parts of cycloalkyl base oil, 2-4 parts of aluminium nitride, 0.2-0.5 parts of molybdenum disulfide, 0.3-0.5 parts of polyisobutylene, 0.5-1.0 parts of active alumina micro powder, 0.2-0.5 parts of resorcinol, 0.2-0.5 parts of nanometer tantalum carbide powder, 0.2-0.5 parts of butylated hydroxytoluene, 2-4 parts of boron phosphide, and 0.5-1.0 parts of an auxiliary agent. The nanoparticles are prepared by utilizing an absolute-ethanol ball milling method, and employed equipment is simple and easy to operate. The added multiple nanoparticles help the transformer oil to improve insulating property and heat conduction property and enable the dielectric coefficient to be small. The added auxiliary agent improves the anti-oxidation, anti-corrosion and insulating properties of the transformer oil. The problems that transformer oil is easy to oxidize and corrode, is not long in service life and the like are effectively solved, and the safety coefficient of the transformer oil is substantially improved.

Owner:桐乡市华宇电力设备股份有限公司

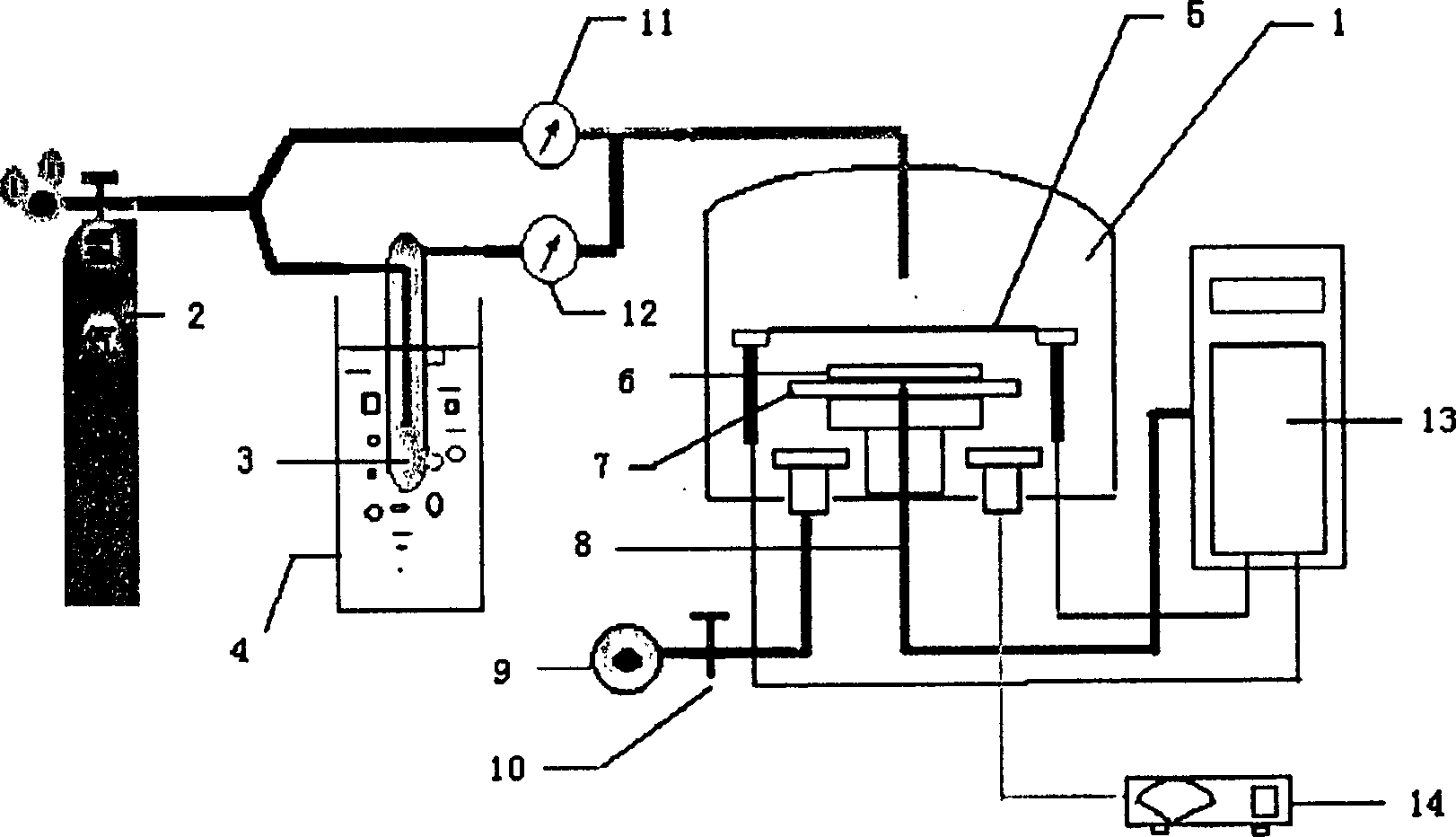

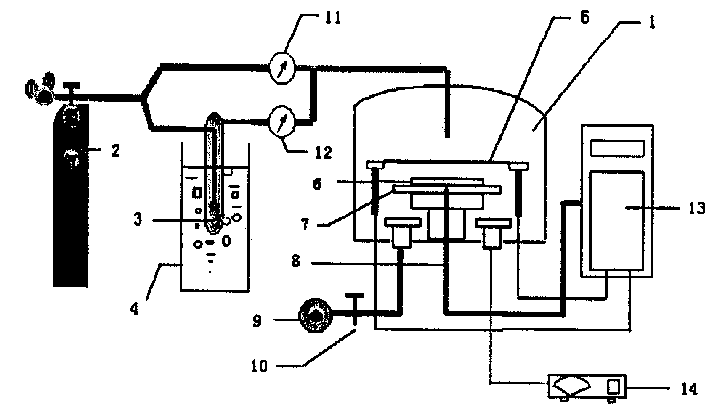

Method for producing material of base plate for encapsulating integrated circuit

InactiveCN1415781ASmall dielectric coefficientHigh thermal conductivitySemiconductor/solid-state device detailsSolid-state devicesAlcoholHydrogen

A substrate material for IC package features that the diamond film is deposited on the alumina ceramics by hot-wire chemical gas-phase deposition method, that is, the diamond film is deposited on the alumina ceramics in the reaction chamber under vacuum condition. In this process, W wire is used as heat source and ethyl alcohol and hydrogen gas are used as reactants.

Owner:SHANGHAI UNIV

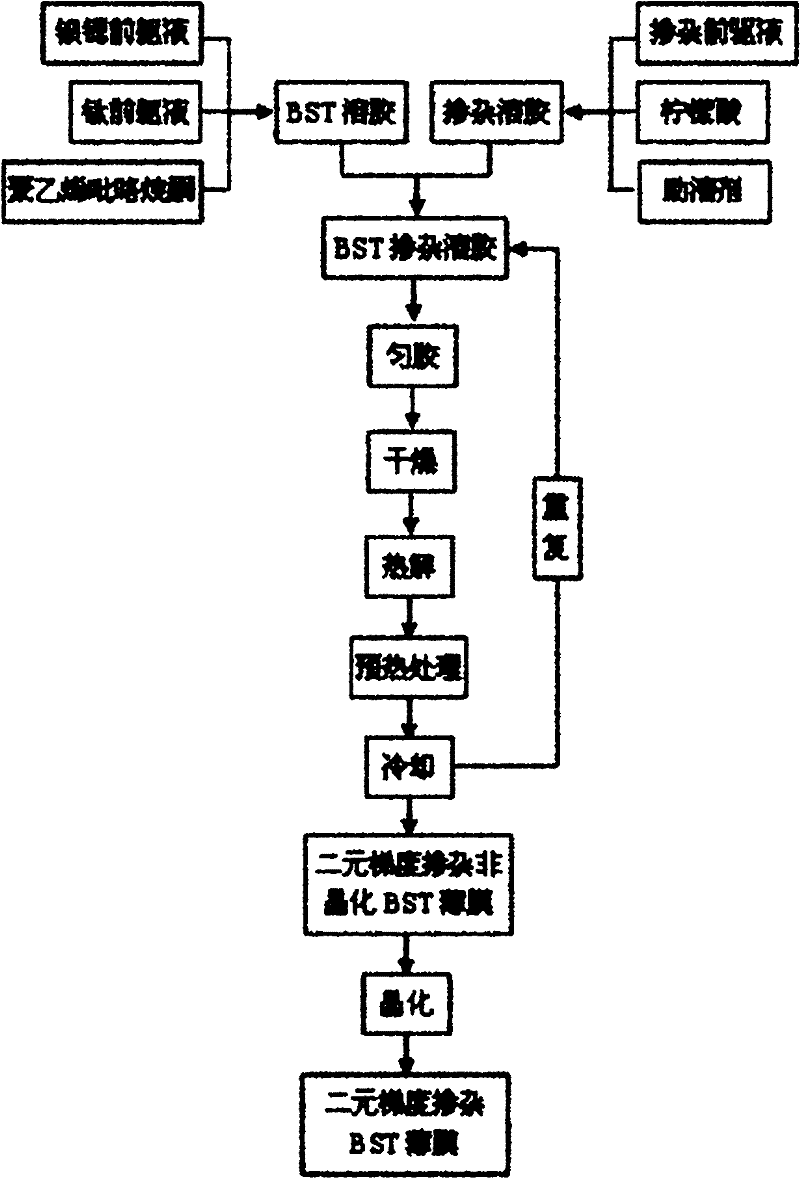

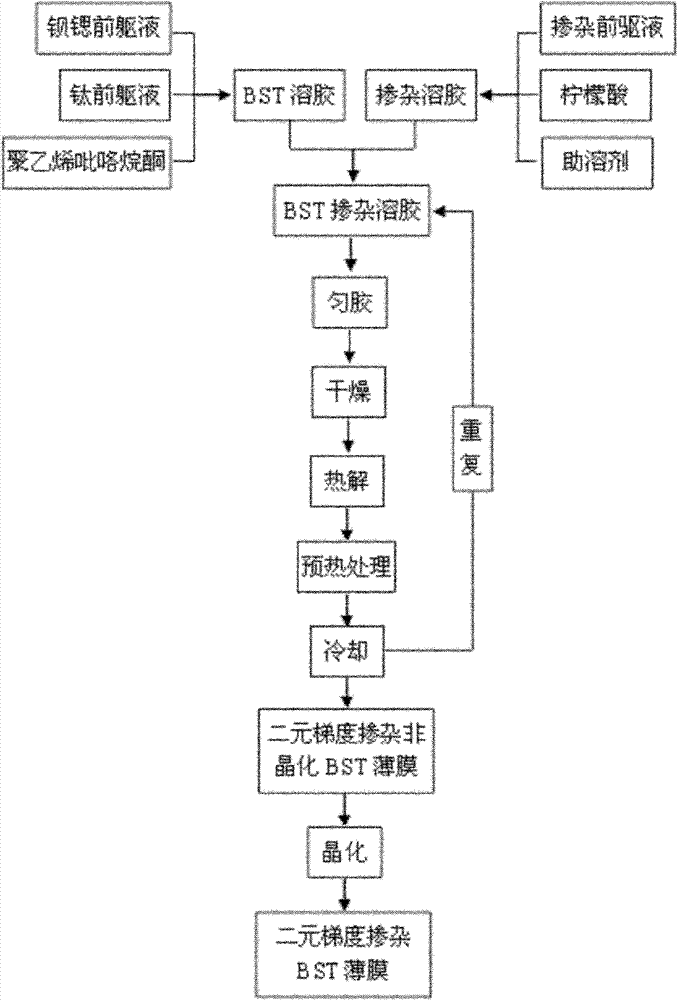

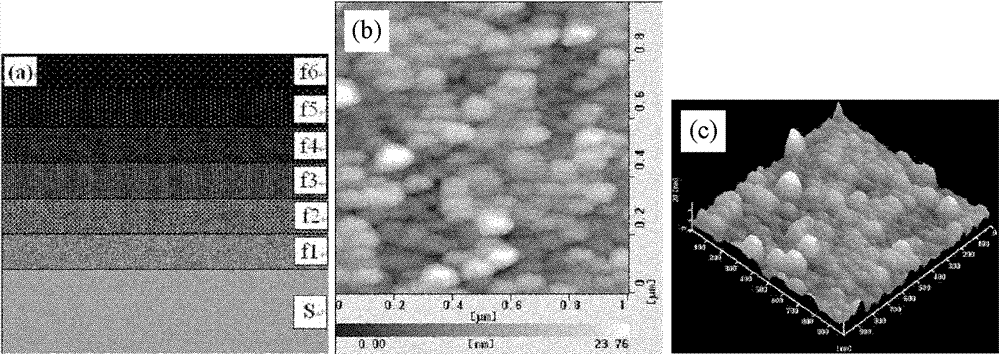

Preparation method of binary gradiently doped barium strontium titanate (BST) film

InactiveCN102173783AExcellent dielectric propertiesSuitable ferroelectric phaseStrontium titanateMicrowave

The invention provides a preparation method of a binary gradiently doped barium strontium titanate (BST) film, aiming at the technical problem that the comprehensive dielectric property of the BST film is difficult to increase owning to the ferroelectric phase or paraelectric phase single-phase structure caused by the narrow Curie temperature (Tc) range of the conventional BST film, and belonging to the technical field of functional materials. By controlling the molar ratio of Ba and Sr to Ti, the doping element, the concentration, the gradient, the direction and the film design and the preheating treatment and the film thickness (or layer number), the binary gradiently doped BST film with a wider Tc range, a ferroelectric phase and paraelectric phase composite structure and excellent comprehensive performance can be prepared, wherein the dielectric constant is less than 240, the tuning rate is more than 25%, the dielectric loss is less than 0.63% and the permittivity-temperature coefficient is less than 0.0024 / K. The method is convenient, fast, cheap and efficient; and the prepared binary gradiently doped BST film can be used in microwave tuning elements.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

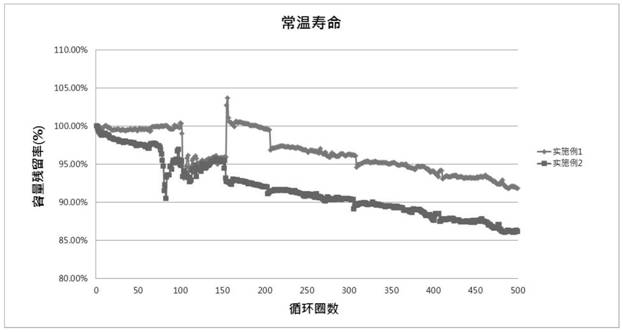

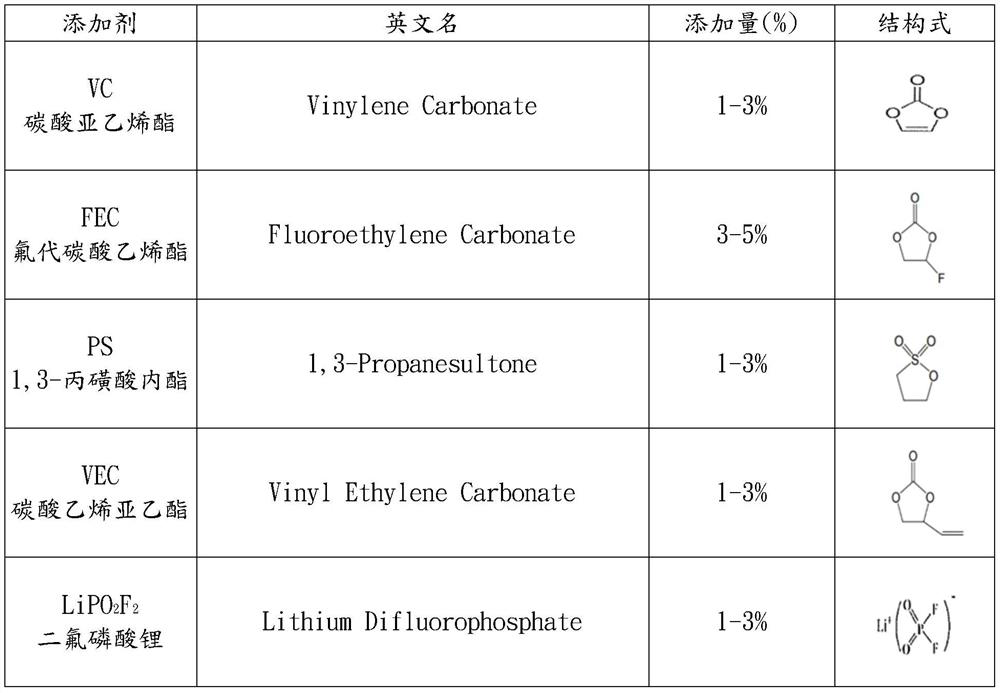

Non-aqueous electrolyte for lithium ion battery with ternary positive electrode material and negative silicon-oxygen-carbon composite negative electrode material

PendingCN113299996AReduce viscosityLow melting point propertiesSecondary cells servicing/maintenanceOrganic electrolytesElectrolytic agentCarbon composites

The invention belongs to the field of lithium ion batteries, and discloses a non-aqueous electrolyte for a lithium ion battery with a ternary positive electrode material and a negative silicon-oxygen-carbon composite negative electrode material, which comprises a non-aqueous organic solvent, an electrolyte lithium salt and an electrolyte additive; the non-aqueous organic solvent comprises ethylene carbonate and methyl ethyl carbonate; and the electrolyte additives comprise vinylene carbonate, fluoroethylene carbonate, 1, 3-propane sultone, vinylethylene carbonate and lithium difluorophosphate. The non-aqueous electrolyte contains cyclic carbonate, a negative electrode film-forming agent, a positive electrode film-forming agent and three lithium salts. The lithium ion non-aqueous electrolyte can be applied to improvement of high-temperature and normal-temperature cycle performance.

Owner:KUNSHAN SYNERGY SCIENTECH CO LTD

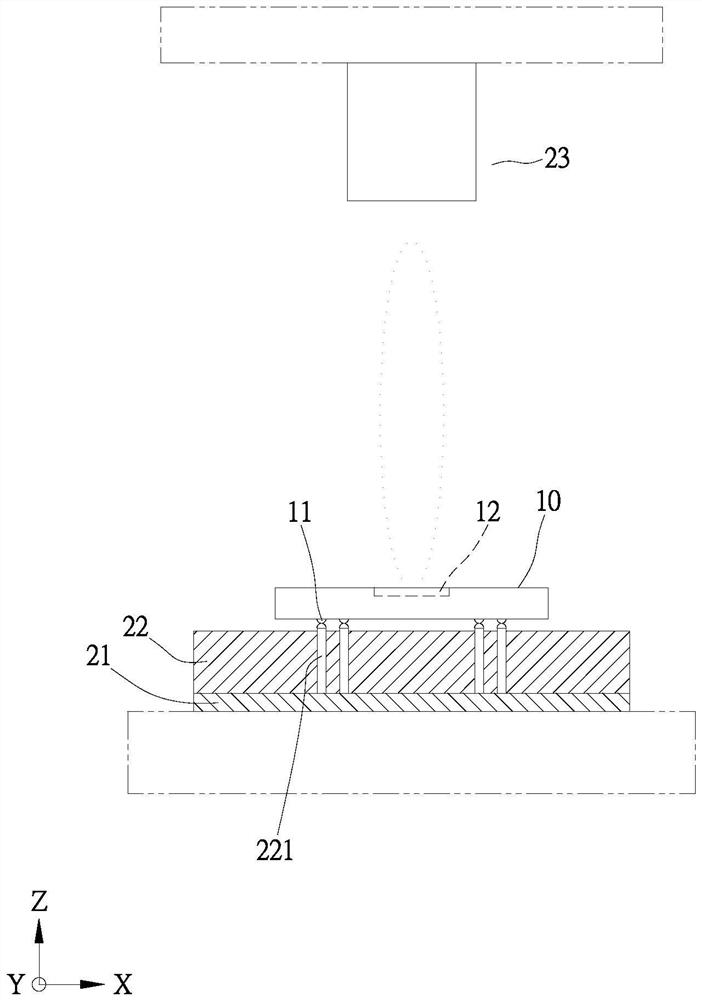

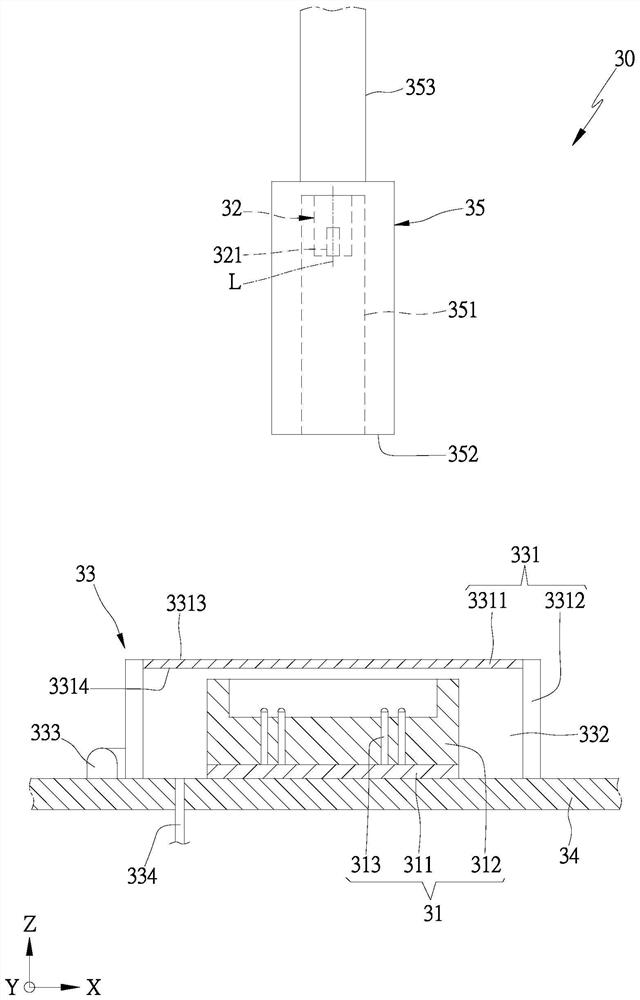

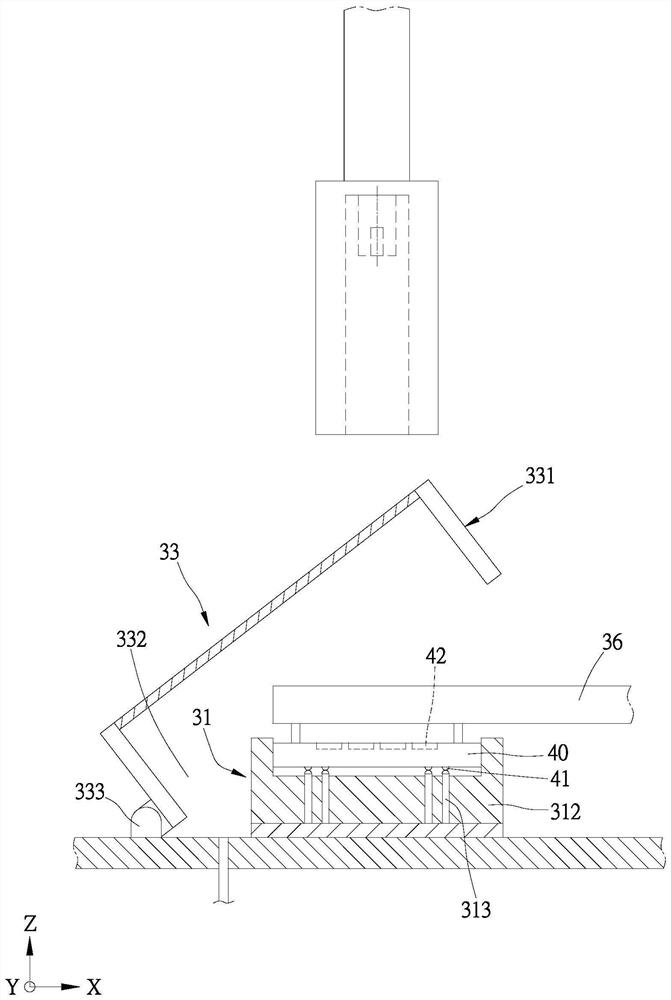

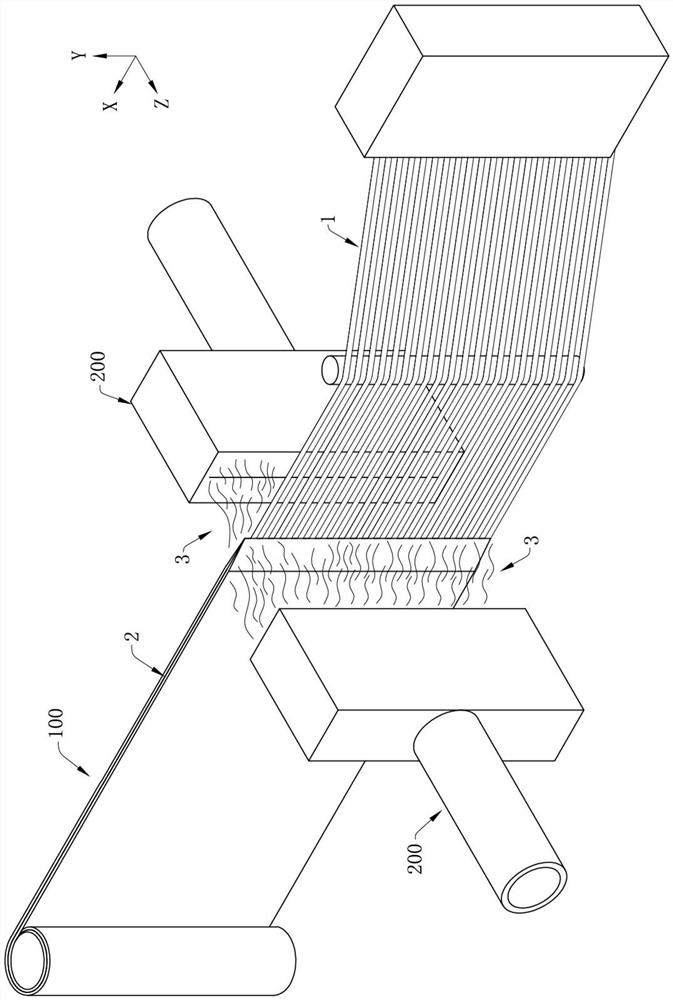

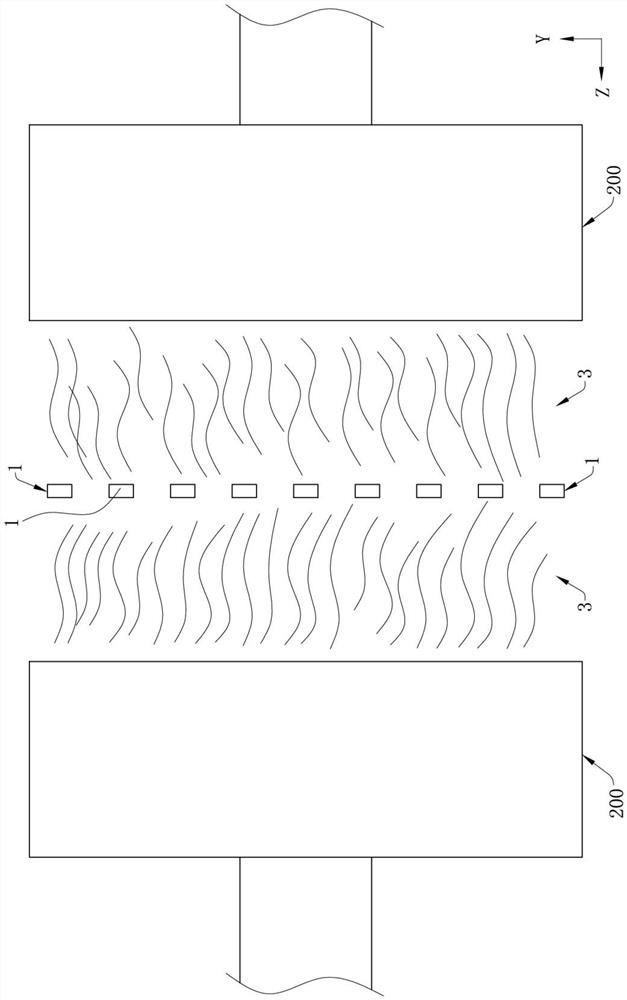

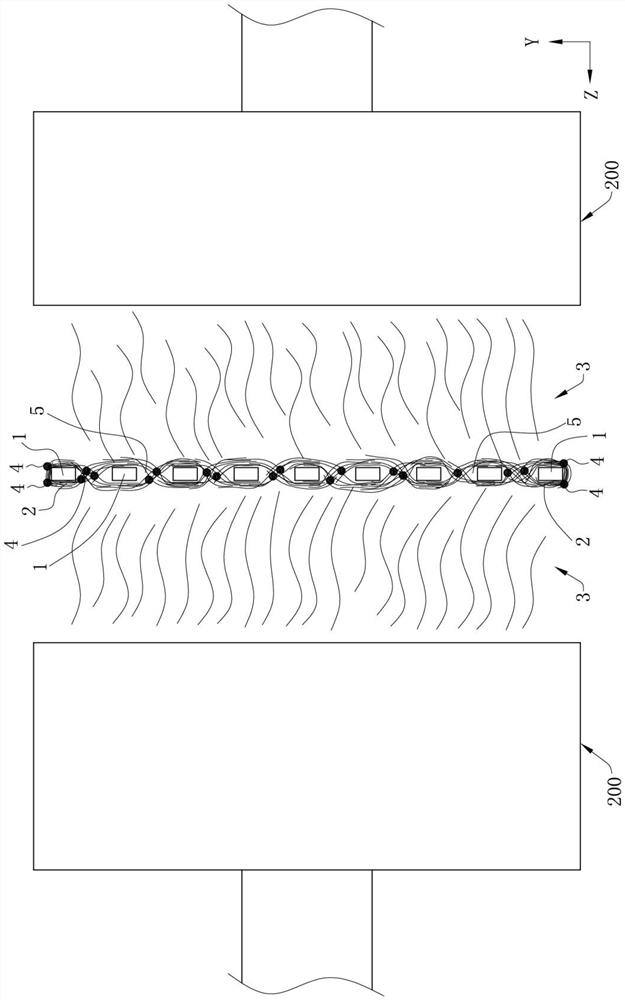

Radio frequency electronic component testing device and testing equipment applying same

PendingCN113945777ASmall dielectric coefficientImprove test qualityInstrument screening arrangementsElectrical testingTest roomElectrical testing

The invention provides a radio frequency electronic component testing device which comprises an electrical tester, an antenna tester and a testing chamber, wherein the testing chamber is provided with a cover body with a first anti-interference component, the first anti-interference component is made of shielding-proof materials and has a low dielectric coefficient so that wireless signals can pass through, the cover body closes a first bearing tool to form a testing space, and the testing space is used for accommodating an electrical tester with a radio frequency electronic component; the testing chamber is located between the electrical tester and the antenna tester, so that the radio frequency electronic component can execute electrical testing operation in the electrical tester in the testing chamber, and can also execute wireless signal testing operation with the external antenna tester through the first anti-interference component in the testing chamber, thereby improving the testing quality. The invention further provides testing equipment applying the radio frequency electronic component testing device. The testing equipment comprises a machine table, a feeding device, a material receiving device, a radio frequency electronic component testing device, a conveying device, and a central control device.

Owner:HON PRECISION INC

Hollow glass fiber production method

The invention relates to a process method for hollow glass fiber, which comprises: arranging special discharge spouts on Pt discharge plate for glass to pass, putting one Pt air-blowing pipe with Pt / Rh=90 / 10 on midst of every spout with lower end to form column gap with spout and top end connected to compress-air device; blowing air as proper quantity by pipe into spout, driving fusing glass to cross the gap and generate hollow when translating into fiber. Wherein, the air in glass fiber can lead to reduction of dielectric coefficient.

Owner:泰安佳成机电科技有限公司

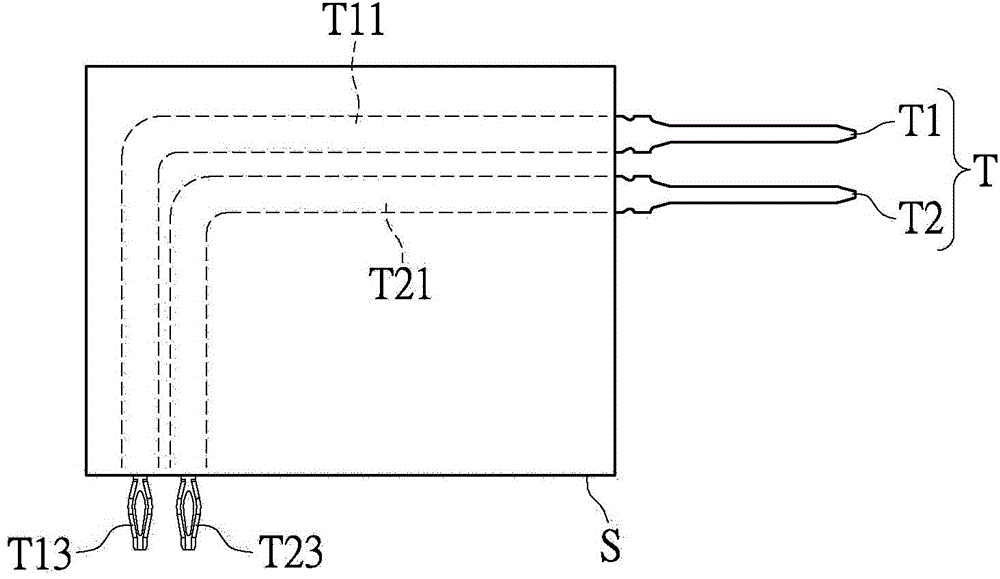

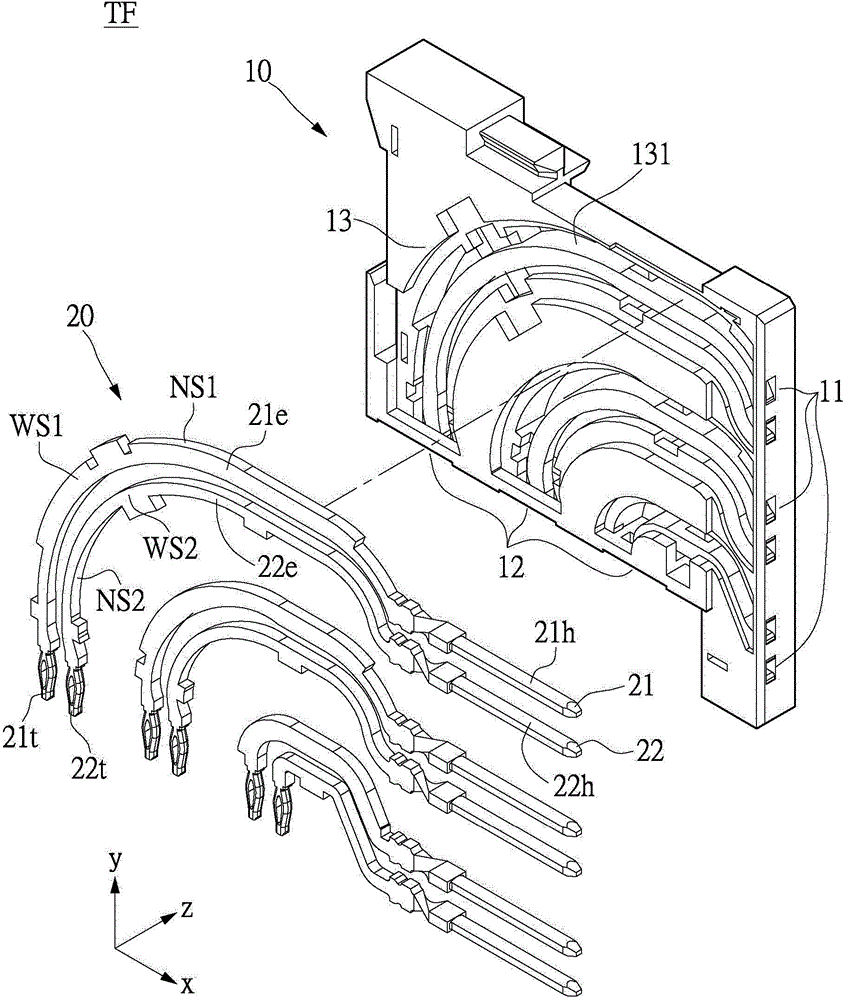

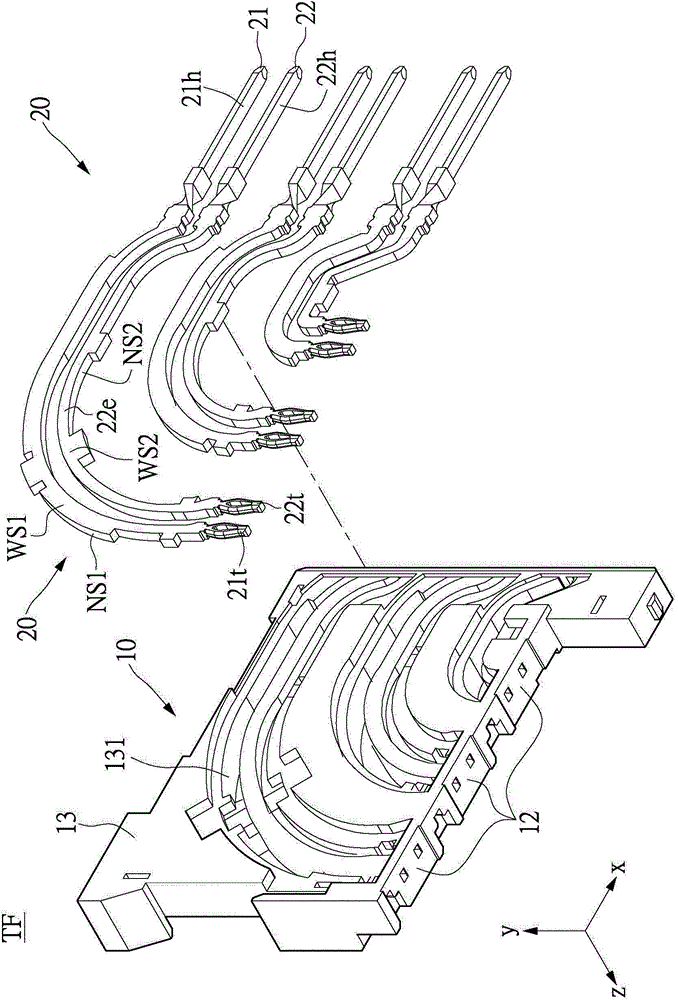

Communication connector and terminal frame thereof

ActiveCN104466492ASmall dielectric coefficientSecuring/insulating coupling contact membersCoupling contact membersTransmission qualityElectrical and Electronics engineering

Provided are a communication connector and a terminal frame thereof. The terminal frame comprises an insulating frame and a plurality of pairs of terminal pairs in the insulating frame. The insulating frame is a first medium and at least comprises a side surface. The terminal pair comprises a first terminal and a second terminal. The first terminal comprises a first extending portion which extends along a first path in the insulating frame. The second terminal comprises a second extending portion which extends along a second path in the insulating frame. The first path is longer than the second path. The first extending portion contacts with a second medium, so that the first extending portion has first contact area relative to the contact second medium, and the second extending portion has second contact area relative to the contact second medium, and the first contact area is larger than the second contact area. Thus, transmission quality of the terminal pairs is improved.

Owner:STARCONN ELECTRONICS SU ZHOU CO LTD

Preparation method of high-performance polyimide flexible copper-clad plate

ActiveCN111300950ASmall size changeLow moisture absorptionNon-macromolecular adhesive additivesLaminationImidePolymer science

The invention provides a preparation method of a polyimide flexible copper-clad plate. The method comprises the following steps: adding polyimide and a heat-conducting filler into dimethylformamide, and stirring to uniformly mix so as to obtain a polyimide glue solution; selecting rolled copper foil, and coating the rough surface of one piece of copper foil with the polyimide glue solution under the protection of inert gas; carrying out imidization in a nitrogen protection oven; covering the polyimide glue solution with another copper foil with the same size to obtain a semi-finished product,and heating and laminating the semi-finished product; and putting the semi-finished product glue-free copper-clad plate into a muffle furnace, and treating under the protection of heating inert gas toobtain the polyimide flexible copper-clad plate. The two-layer flexible copper-clad plate provided by the invention is small in size change and stable, the formed polyimide layer and the copper foilare good in cohesiveness, and the polyimide layer is low in moisture absorption rate, low in dielectric coefficient and excellent in performance.

Owner:NANJING ZHONGHONG RUNNING ADVANCED MATERIAL TECH CO LTD

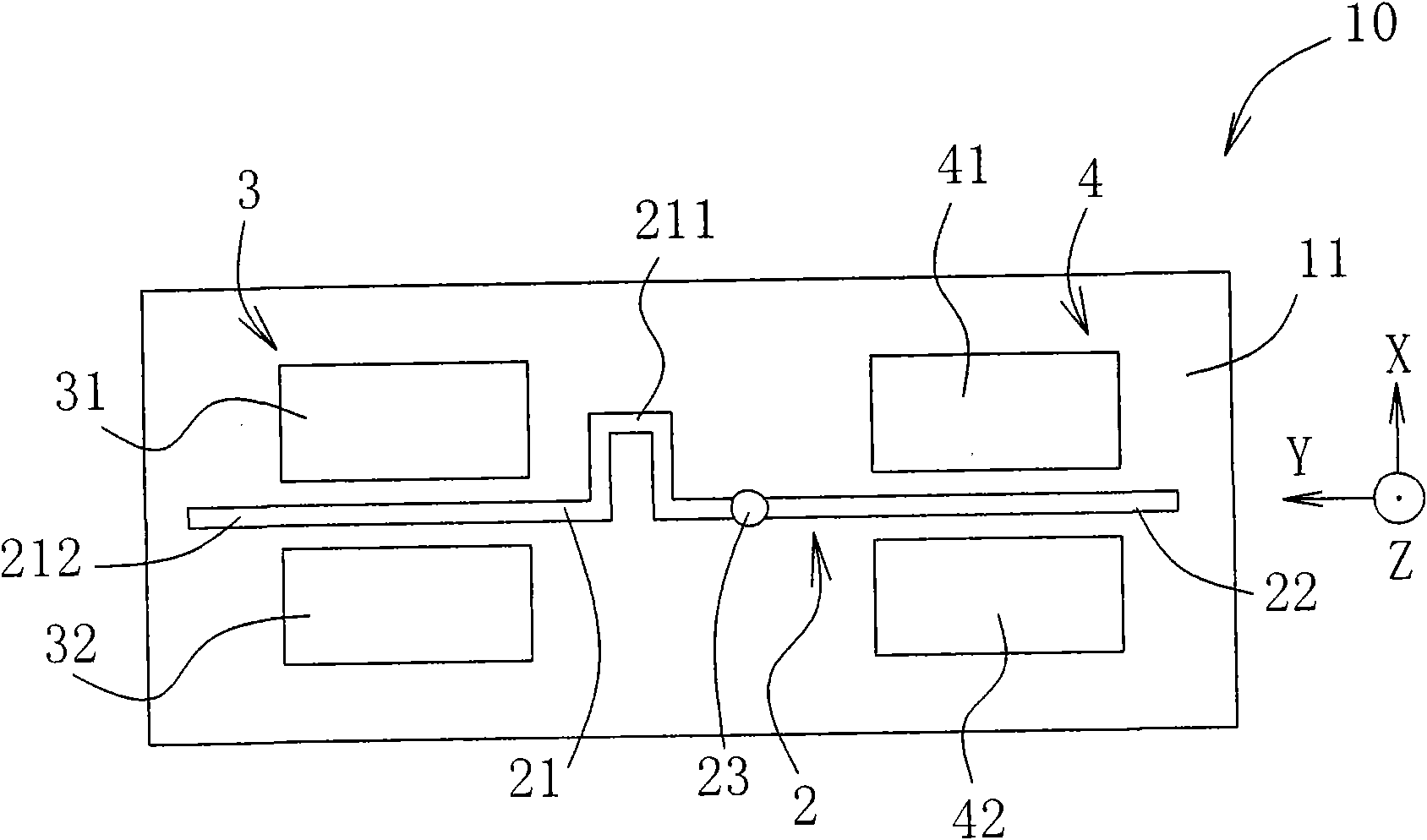

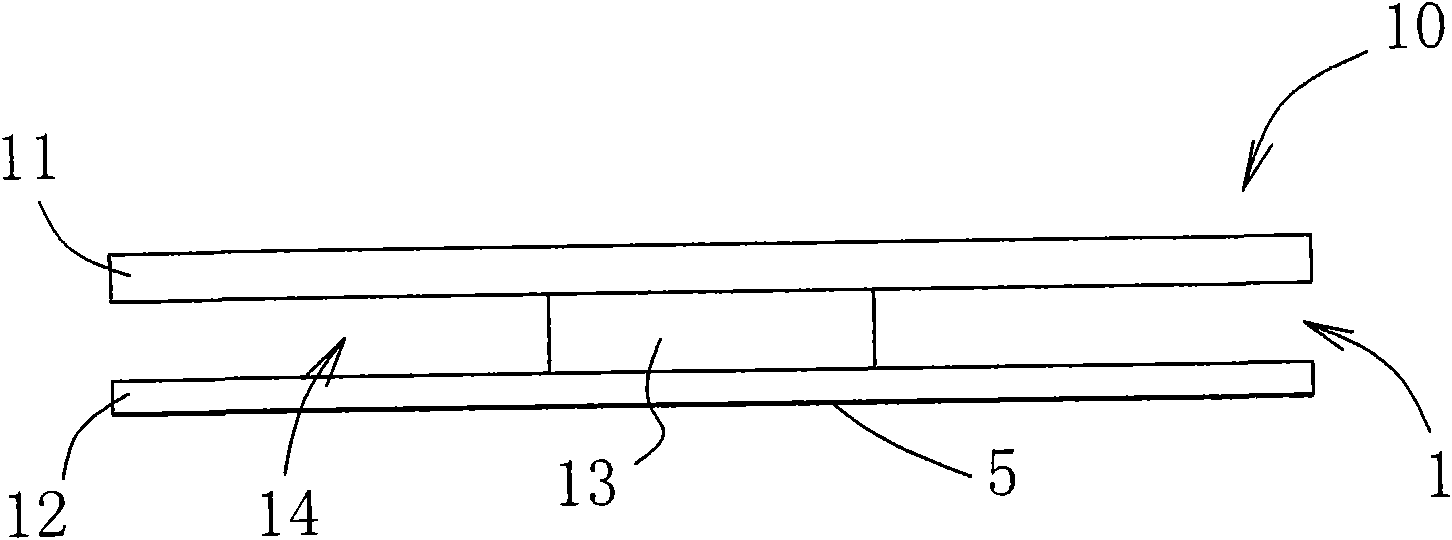

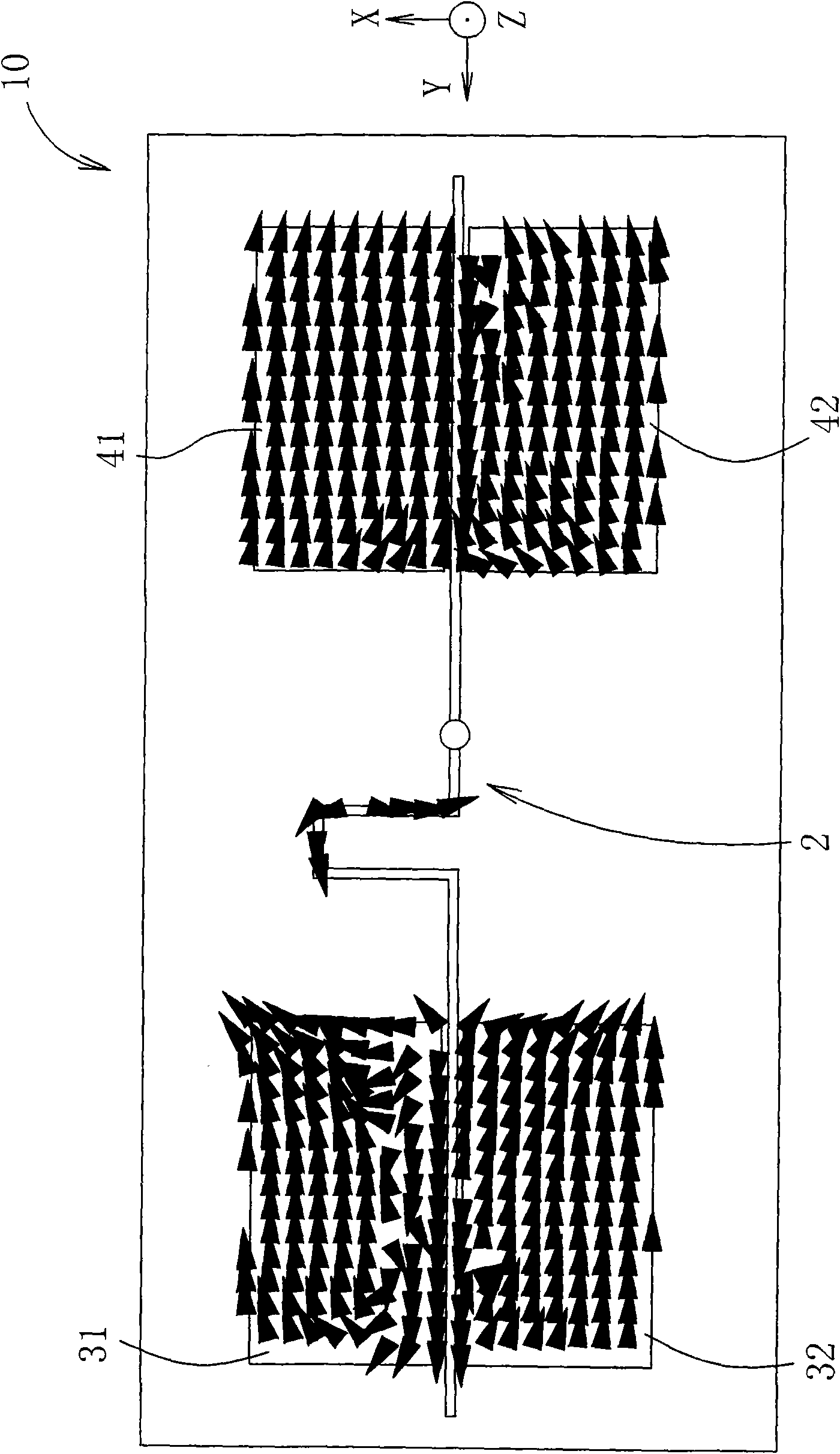

Plane antenna

InactiveCN101685904ASmall dielectric coefficientHigh gainRadiating elements structural formsResonant antennasPhysicsFeed line

The invention relates to a plane antenna which comprises a base plate, a feed line, a first radiating unit, a second radiating unit and a grounding unit, wherein the base plate is provided with an upper surface and a lower surface in parallel; the feed line is arranged on the upper surface; and the grounding unit is arranged on the lower surface and used for grounding. The plane antenna is characterized in that the feed line is divided into a long first feed section and a short second feed section by a feed point for feeding a signal, and the first feed section is longer than the second feed section by a half wavelength of the operation frequency of the plane antenna; and the first radiating unit and the second radiating unit are respectively two radiating metal sheets adjacent to the first feed section and the second feed section.

Owner:ADVANCED CONNECTION TECH

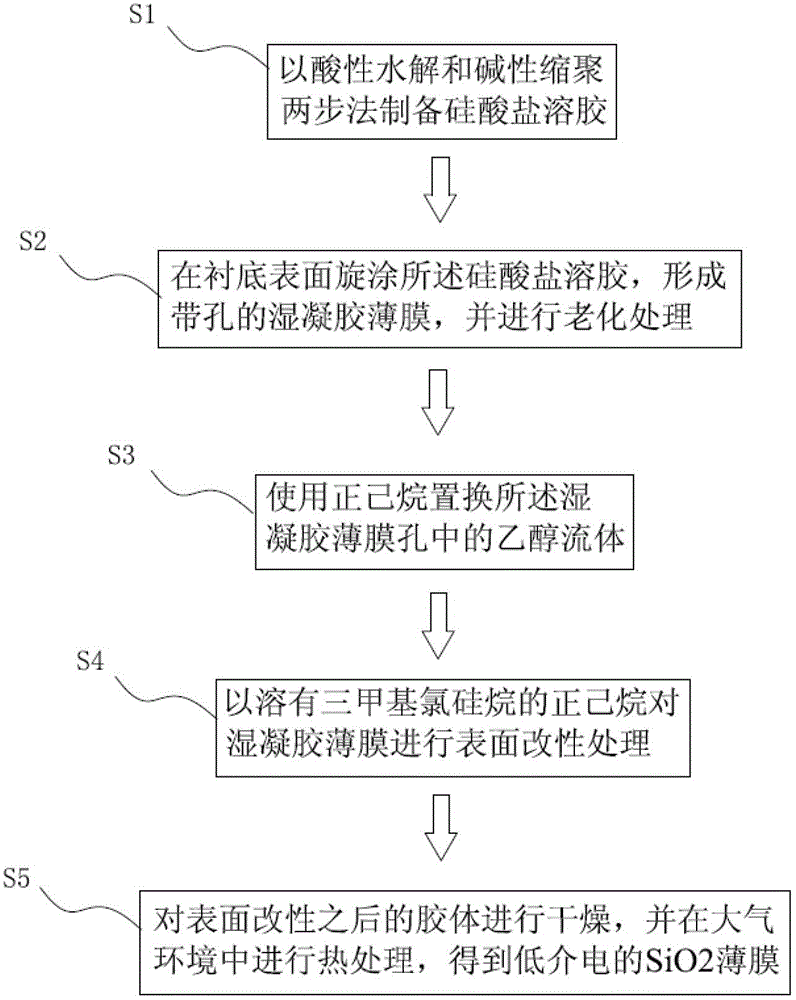

Surface modification process for low-dielectric material

InactiveCN102718226ASmall dielectric coefficientSmall water absorptionSilicon compoundsPorositySolvent

The invention discloses a surface modification process for a low-dielectric material. According to the surface modification process, a silicon dioxide wet gel thin film obtained by using a spin coating method is soaked in a modification solution for surface modification, and then is subjected to thermal treatment in an atmospheric environment, so that the silicon dioxide thin film material with a low dielectric constant is prepared. A method for reducing the dielectric coefficient of the material through using two simple and convenient techniques of soaking with a solvent and performing the thermal treatment is used in the process, so that the porosity of the material still maintains at a relatively low level, and the mechanical strength can keep a relatively high level.

Owner:SUZHOU UNIV

High thermal conductive insulation layered composite material and preparation method thereof

ActiveCN103895281AImprove corrosion resistanceImprove thermal conductivityLamination ancillary operationsLaminationInsulation layerConductive materials

The invention belongs to the technical field of electronics, and in particular relates to a high thermal conductive insulation layered composite material and a preparation method thereof. The high thermal conductive insulation layered composite material provided by the invention is welded from a high thermal conductive material and a dielectric material. In addition to excellent performances of low density, high strength, wear resistance and corrosion resistance, the composite material has high thermal conductivity of a high thermal conductive material to quickly emit heat in electronic devices, and has good electrical insulation and low dielectric coefficient of a dielectric material. According to the invention, a welding method is employed to connect the high thermal conductive material with the dielectric material, so that the high thermal conductive insulation layered composite material can be applied to occasions simultaneously requiring high thermal conductivity, low dielectric constant and electrical insulation.

Owner:GRIMAT ENG INST CO LTD

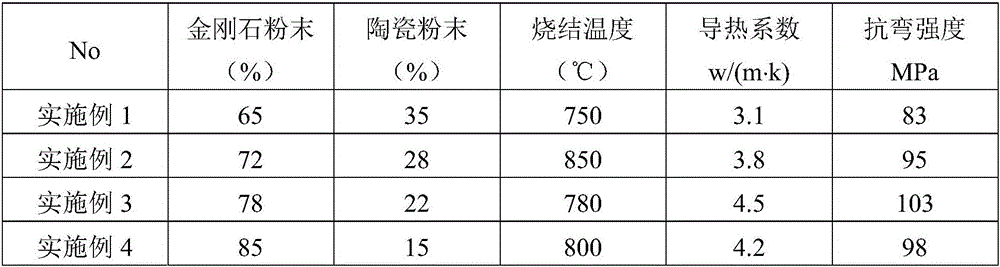

Rare earth doped ceramic-based diamond substrate material and preparation method thereof

InactiveCN105924172ASmall dielectric coefficientCoefficient of thermal expansion matchingRare earthThermal expansion

The invention discloses a rare earth doped ceramic-based diamond substrate material. The rare earth doped ceramic-based diamond substrate material comprises the following raw materials in percentages by mass: 65 to 85% of diamond powder and 15 to 35% of ceramic powder, wherein the ceramic powder comprises the following raw materials in percentages by mass: 40 to 62% of SiO2, 21 to 33% of B2O3, 5 to 13% of Li2O, 3 to 7% of Al2O3, 2 to 6% of Na2O, 2 to 5% of CaO and 1 to 10% of CeO2. The material is prepared through the following steps: preparing the ceramic powder, then carrying out batching and molding, and carrying out sintering at 750 to 800 DEG C. The rare earth doped ceramic-based diamond substrate material provided by the invention is prepared at low temperature and normal pressure, has highest thermal conductivity and flexure strength respectively reaching to 4.5 w / (m-k) and 103 Mpa, has the advantages of low dielectric coefficient and thermal expansion coefficient matching with a Si electronic component, and is a substrate material applicable to electronic packaging.

Owner:TIANJIN UNIV

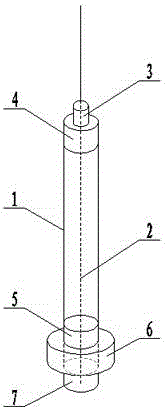

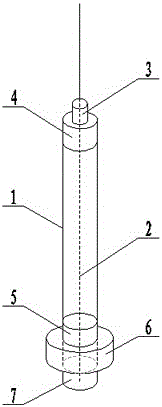

Air coaxial center-fed antenna

ActiveCN104134847AReduce lossSmall dielectric coefficientAntenna supports/mountingsElectrical conductorEngineering

The invention relates to an air coaxial center-fed antenna which comprises an outer conductor and an inner conductor, wherein the inner conductor is coaxially arranged in the outer conductor in a penetrating manner; one end of the inner conductor is connected with an antenna feed port formed at one end of the outer conductor; the outer conductor is hollow; and the other end of the inner conductor is connected with a tightener arranged at the other end of the outer conductor. The inner conductor is coaxially arranged in the hollow outer conductor in a penetrating manner by utilizing the characteristics of low air transmission loss and dielectric coefficient, no insulating material is filled in the outer conductor, the inner conductor and the outer conductor are tightened by the tightener to be coaxial, and the diameter of the inner conductor can be increased, so that the transmission loss is reduced, and the efficiency of the antenna is improved.

Owner:TAIXING DONGSHENG ELECTRONICS EQUIP FACTORY

A kind of high thermal conductivity insulating composite material and preparation method thereof

ActiveCN103187131BImprove thermal conductivityHigh thermal conductivitySemiconductor/solid-state device detailsSolid-state devicesFiberComposite film

The invention relates to a high heat conductivity insulation composite and a preparation method thereof, and belongs to the technical field of electronic packaging. The composite consists of a high heat conductivity composite and an insulation layer plated on the high heat conductivity composite, wherein the high heat conductivity composite is a composite of reinforced particles or fibers and a matrix; the matrix is copper, aluminum or silver; and the insulation layer is a diamond, aluminum nitride or boron nitride ceramic film or a composite film of diamond and aluminum nitride or boron nitride. The composite is prepared by depositing the insulation film on the surface of the high heat conductivity composite by a chemical vapor deposition technology. The high heat conductivity insulation composite achieves high heat conductivity and insulation under applications with specific insulating property requirements, and is applicable to integrated circuit systems, high-power or high power density devices and the like.

Owner:GRIMAT ENG INST CO LTD

Polyimide flexible copper-clad plate

ActiveCN111300922ASmall size changeLow moisture absorptionNon-macromolecular adhesive additivesMetal layered productsImidePolymer science

The invention provides a preparation method of a polyimide flexible copper-clad plate. The method comprises the following steps: adding polyimide and a heat-conducting filler into dimethylformamide, and stirring to uniformly mix so as to obtain a polyimide glue solution; selecting rolled copper foil, and coating the rough surface of one piece of copper foil with the polyimide glue solution under the protection of inert gas; carrying out imidization in a nitrogen protection oven; covering the polyimide glue solution with another copper foil with the same size to obtain a semi-finished product,and heating and laminating the semi-finished product; and putting the semi-finished product glue-free copper-clad plate into a muffle furnace, and treating under the protection of heating inert gas toobtain the polyimide flexible copper-clad plate. The two-layer flexible copper-clad plate provided by the invention is small in size change and stable, the formed polyimide layer and the copper foilare good in cohesiveness, and the polyimide layer is low in moisture absorption rate, low in dielectric coefficient and excellent in performance.

Owner:NANJING ZHONGHONG RUNNING ADVANCED MATERIAL TECH CO LTD

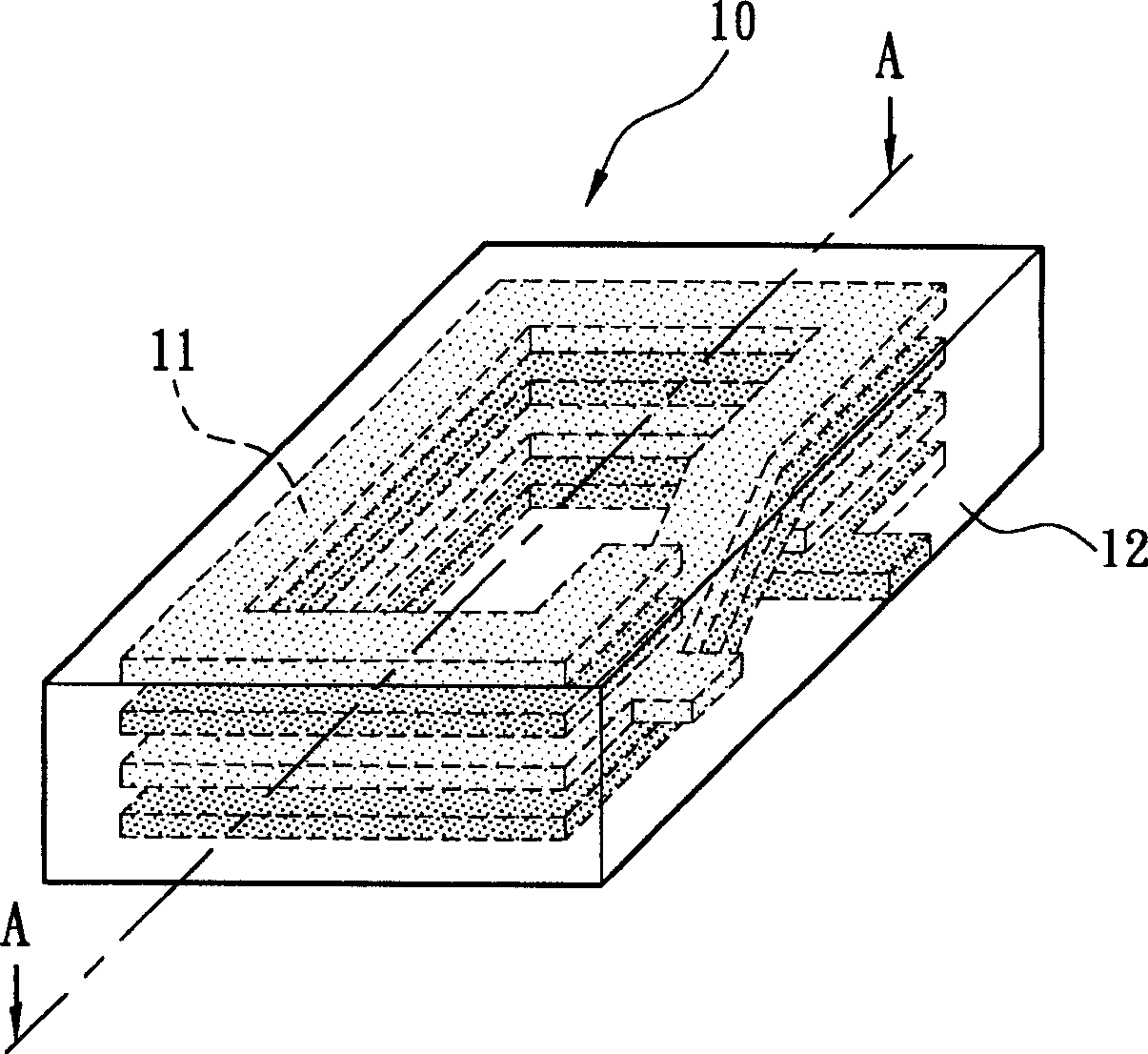

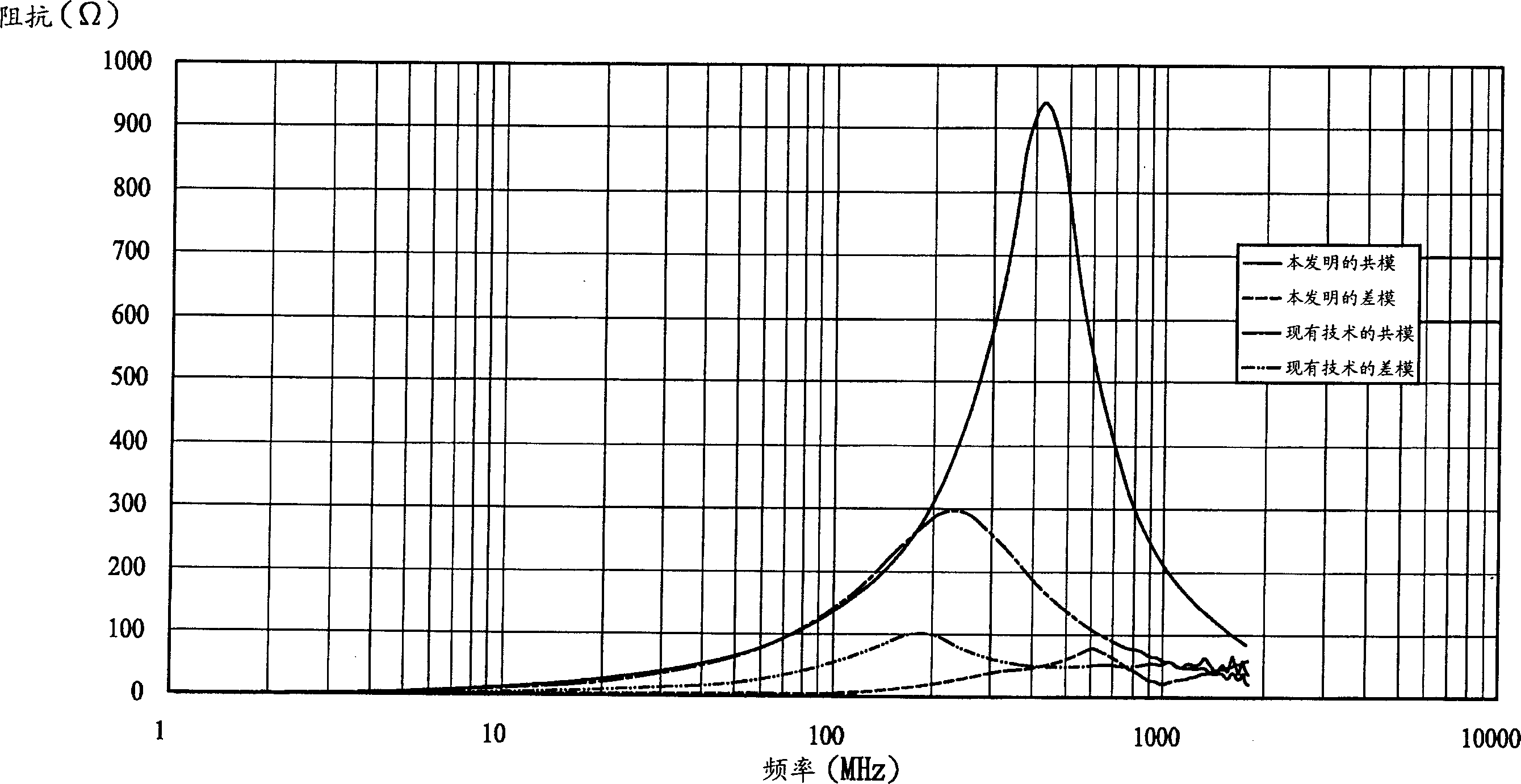

Ceramic co-fired type common mode filter and its making method

InactiveCN1763870ALow magnetic permeabilitySmall dielectric coefficientImpedence networksWaveguide type devicesCeramic

The invention discloses a ceramic co-sinter co-mode filter to overcome the defect of laminated or winding filter. Wherein, selecting proper materials of different electrical property according to different demand of parts of element, adjusting proper operation by material powder character to integrate together, then completing the element main body with special sintering curve and co-sinter method, finally, obtaining the objective filter.

Owner:INPAQ TECH

Preparation method of binary gradiently doped barium strontium titanate (BST) film

InactiveCN102173783BExcellent dielectric propertiesMeet application needsStrontium titanateMicrowave

The invention provides a preparation method of a binary gradiently doped barium strontium titanate (BST) film, aiming at the technical problem that the comprehensive dielectric property of the BST film is difficult to increase owning to the ferroelectric phase or paraelectric phase single-phase structure caused by the narrow Curie temperature (Tc) range of the conventional BST film, and belongingto the technical field of functional materials. By controlling the molar ratio of Ba and Sr to Ti, the doping element, the concentration, the gradient, the direction and the film design and the preheating treatment and the film thickness (or layer number), the binary gradiently doped BST film with a wider Tc range, a ferroelectric phase and paraelectric phase composite structure and excellent comprehensive performance can be prepared, wherein the dielectric constant is less than 240, the tuning rate is more than 25%, the dielectric loss is less than 0.63% and the permittivity-temperature coefficient is less than 0.0024 / K. The method is convenient, fast, cheap and efficient; and the prepared binary gradiently doped BST film can be used in microwave tuning elements.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

A kind of anti-oxidation and corrosion transformer oil containing multiple nanoparticles and preparation method thereof

ActiveCN104130829BImprove insulation performanceSmall dielectric coefficientAdditivesOxidation resistantResorcinol

The invention discloses an anti-oxidation and corrosion transformer oil containing various nanoparticles, which is characterized in that it is made of the following raw materials in parts by weight: naphthenic base oil 1000-1500, aluminum nitride 2-4, Molybdenum 0.2‑0.5, polyisobutylene 0.3‑0.5, activated alumina micropowder 0.5‑1.0, resorcinol 0.2‑0.5, nanometer tantalum carbide powder 0.2‑0.5, dibutylhydroxytoluene 0.2‑0.5, boron phosphide 2‑4 , additives 0.5‑1.0; using absolute ethanol ball milling method to prepare nano powder, the equipment used is simple and easy to operate; various nanoparticles added increase the functions of transformer oil insulation, thermal conductivity and small dielectric coefficient; added additives The anti-oxidation, anti-corrosion and insulating functions of the transformer oil are added, and the invention effectively solves the problems of easy oxidation, corrosion and short service life of the transformer oil, which greatly improves the safety factor of the transformer oil.

Owner:桐乡市华宇电力设备股份有限公司

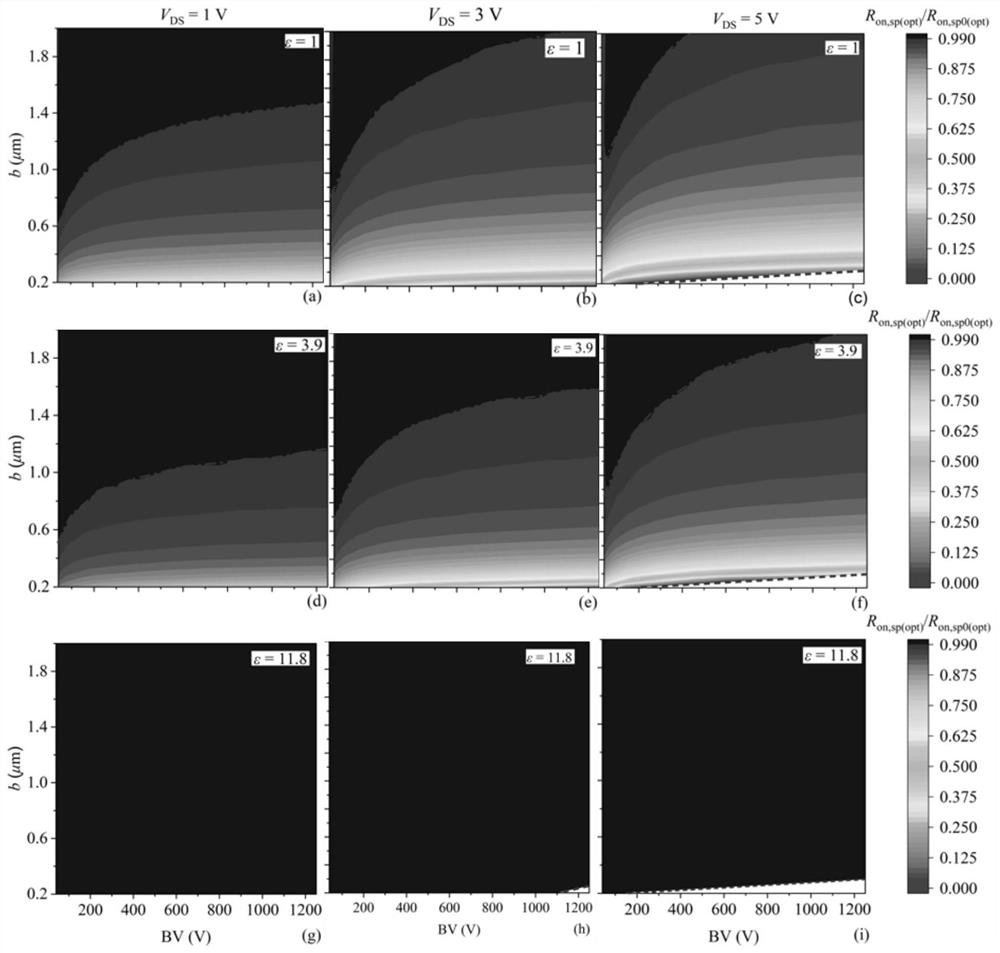

Optimization method of isolation column super junction structure

ActiveCN114781309ASmall dielectric coefficientProve superiorityDesign optimisation/simulationConstraint-based CADElectrical resistance and conductanceEngineering

The optimization method of the isolation column super-junction structure is suitable for the super-junction structure of any application condition, the influence of temperature is comprehensively considered, all optimized design parameters are obtained through one objective function and two constraint conditions, and the optimization method is suitable for the super-junction structure of any application condition. Results with different error precisions can be obtained by performing iteration of different times through the same optimization process. Compared with a traditional super-junction structure, the isolation column super-junction structure obtained through the optimization method has a lower specific on-resistance design parameter value range, and the superiority of the low-dielectric-coefficient dielectric isolation column super-junction structure is proved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

An air coaxial mid-fed antenna

ActiveCN104134847BReduce lossSmall dielectric coefficientAntenna supports/mountingsElectrical conductorEngineering

The invention relates to an air coaxial center-fed antenna which comprises an outer conductor and an inner conductor, wherein the inner conductor is coaxially arranged in the outer conductor in a penetrating manner; one end of the inner conductor is connected with an antenna feed port formed at one end of the outer conductor; the outer conductor is hollow; and the other end of the inner conductor is connected with a tightener arranged at the other end of the outer conductor. The inner conductor is coaxially arranged in the hollow outer conductor in a penetrating manner by utilizing the characteristics of low air transmission loss and dielectric coefficient, no insulating material is filled in the outer conductor, the inner conductor and the outer conductor are tightened by the tightener to be coaxial, and the diameter of the inner conductor can be increased, so that the transmission loss is reduced, and the efficiency of the antenna is improved.

Owner:TAIXING DONGSHENG ELECTRONICS EQUIP FACTORY

Hollow glass fiber production method

The invention relates to a process method for hollow glass fiber, which comprises: arranging special discharge spouts on Pt discharge plate for glass to pass, putting one Pt air-blowing pipe with Pt / Rh=90 / 10 on midst of every spout with lower end to form column gap with spout and top end connected to compress-air device; blowing air as proper quantity by pipe into spout, driving fusing glass to cross the gap and generate hollow when translating into fiber. Wherein, the air in glass fiber can lead to reduction of dielectric coefficient.

Owner:泰安佳成机电科技有限公司

Conductive substrate and manufacturing method thereof

ActiveCN112133476BSmall dielectric coefficientReduce lossFlat/ribbon cablesFlexible cablesFiberElectrically conductive

Owner:DEYI PRECISION ELECTRONIC IND CO LTD PANYU

A cross-linked moisture barrier rubber adhesive, a double-sided adhesive tape using the adhesive and a preparation method thereof

ActiveCN108865021BHigh moisture barrierHigh bonding strengthNon-macromolecular adhesive additivesMacromolecular adhesive additivesPolymer scienceHigh humidity

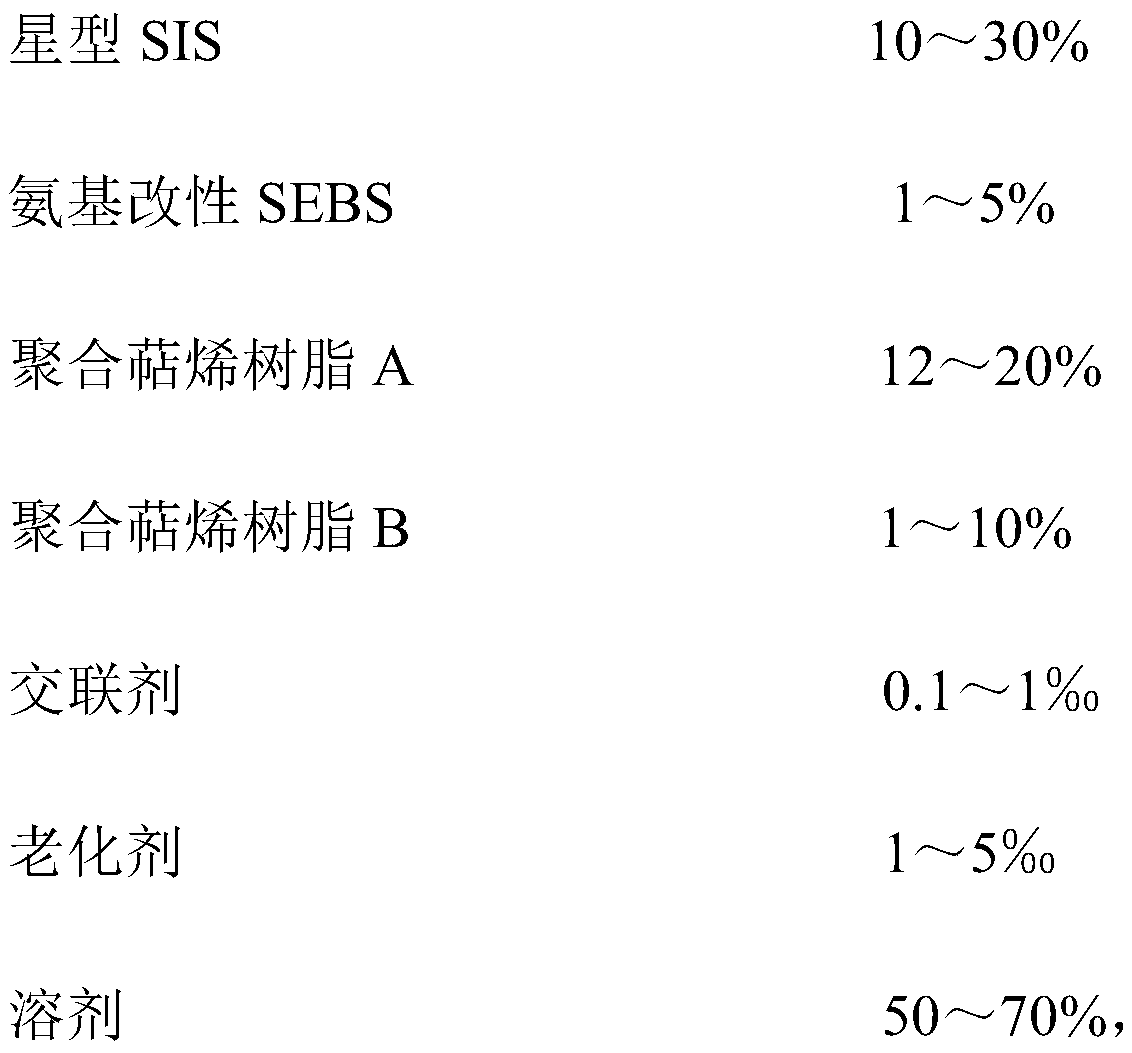

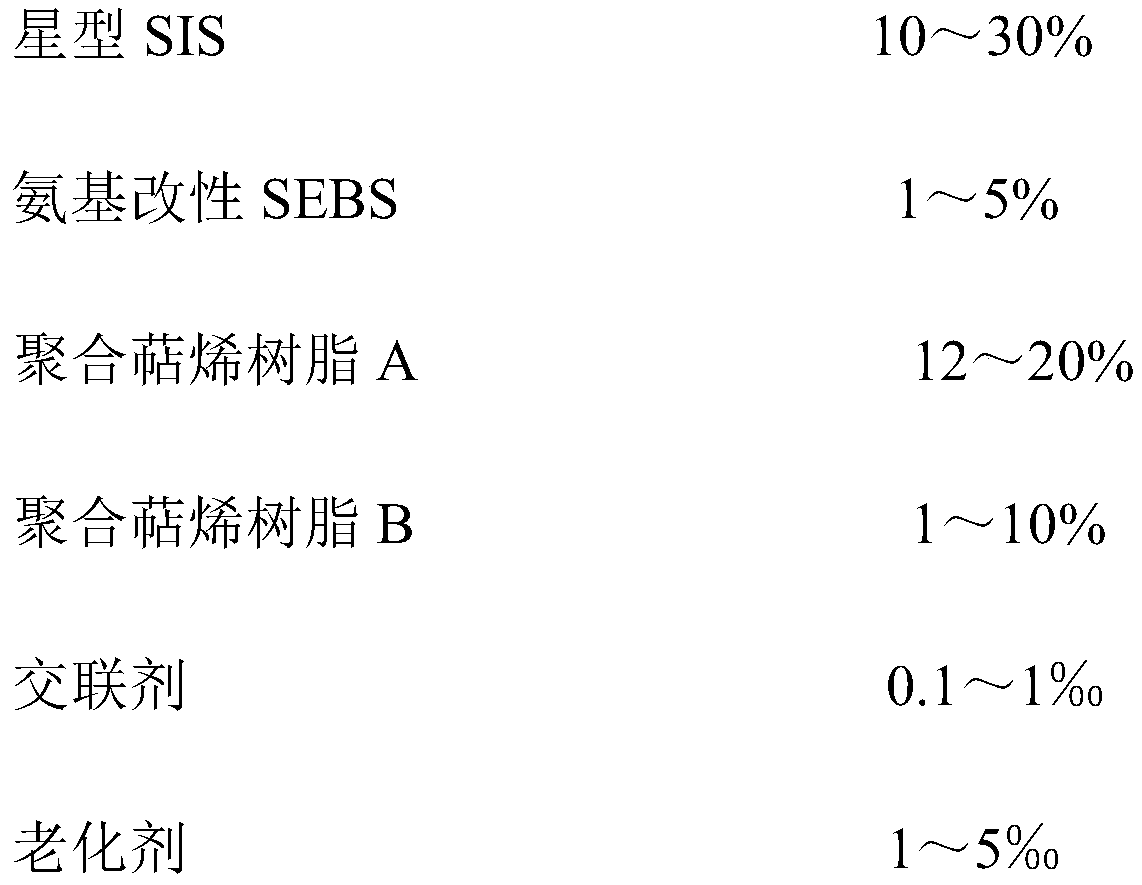

The invention discloses crosslinked moisture barrier type rubber adhesive, which is prepared from the following components by mass percent: 10-30% of star-shaped SIS, 1-5% of amino-modified SEBS, 12-20% of polymerized terpene A, 1-10% of polymerized terpene B, 0.01-0.1% of a cross-linking agent, 0.1-0.5% of an aging agent and 50-70% of a solvent. The crosslinked moisture barrier type rubber adhesive has the characteristics of being high in bonding strength and moisture barrier property, low in dielectric coefficient, free from acidity or weak in acidity, and the like; furthermore, the crosslinked moisture barrier type rubber adhesive can resist a certain high temperature (85 DEG C), is excellent in high temperature and high humidity properties, and is good in subsequent die cutting processing performance.

Owner:新纶电子材料(常州)有限公司