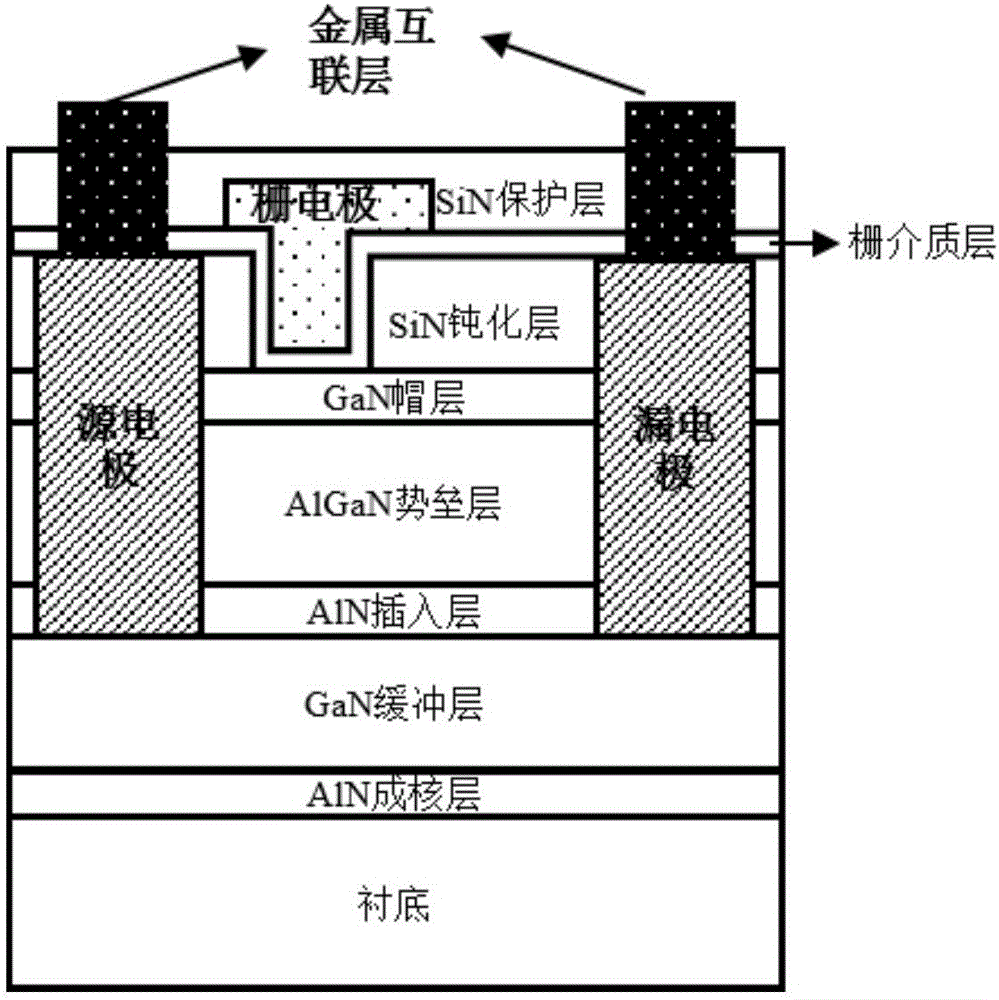

Fabrication method for transistor with composite gate dielectric GaN-based insulating gate and high electron mobility

A technology with high electron mobility and composite gate dielectric, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as unstable oxygen substitution nitrogen, unstable threshold voltage, device performance degradation, etc., to achieve improved Effects of activity, reduction of interface charge, and improvement of compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

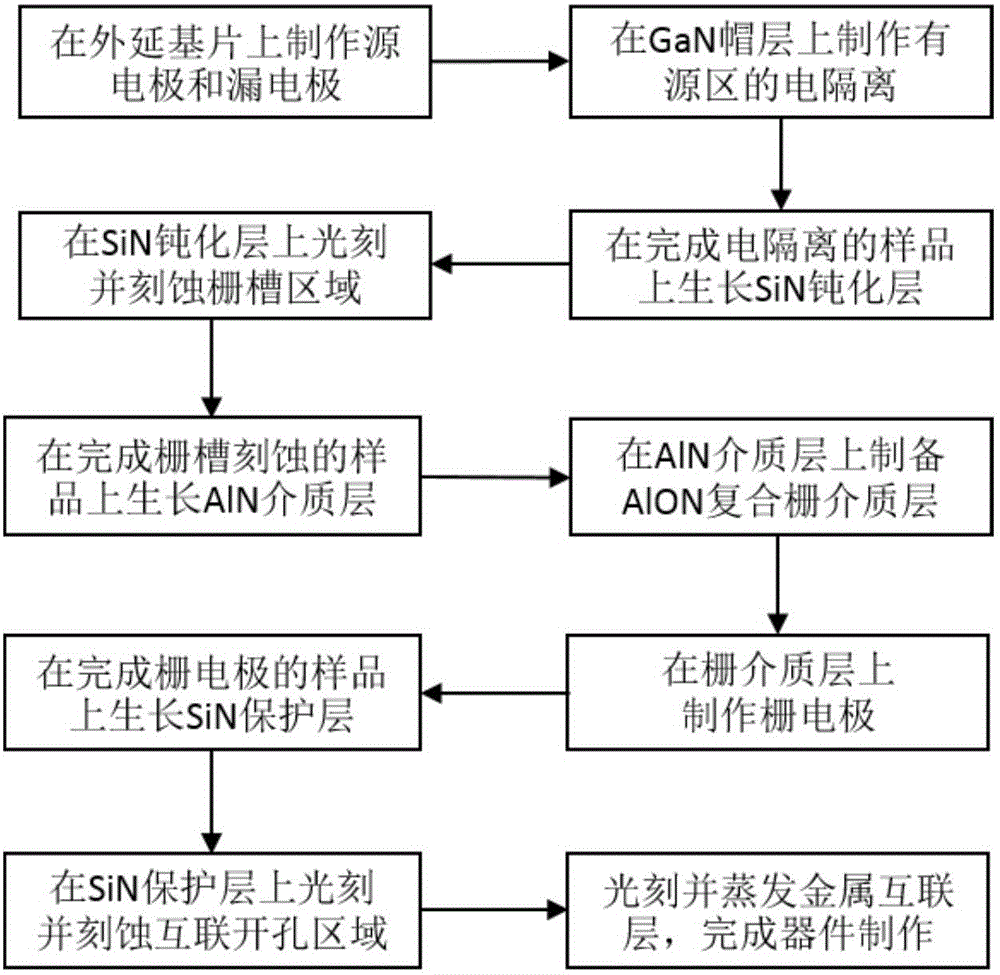

[0052] Embodiment 1, a GaN-based insulated gate high electron mobility transistor with an AlON composite gate dielectric layer thickness of 10 nm is fabricated on a sapphire substrate by thermal oxidation process.

[0053] Step 1, making source electrodes and drain electrodes on the GaN buffer layer of the epitaxial substrate.

[0054] 1a) Photoetching the source electrode region and the drain electrode region on the GaN cap layer:

[0055] First, bake the epitaxial substrate on a hot plate at 200°C for 5 minutes;

[0056] Then, apply and spin the peeling glue on the GaN cap layer, the thickness of the peeling glue is 0.35 μm, and bake the sample on a hot plate at 200 ° C for 5 minutes;

[0057] Next, apply and spin the photoresist on the stripping adhesive, the thickness of the coating is 0.77 μm, and bake the sample on a hot plate at 90°C for 1 min;

[0058] After that, put the sample that has been glued and glued into a photolithography machine to expose the photoresist i...

Embodiment 2

[0142] Embodiment 2, a GaN-based insulated gate high electron mobility transistor with an AlON compound gate dielectric layer thickness of 5 nm is fabricated on a SiC substrate by using a plasma-assisted oxidation process.

[0143] Step 1, making a source electrode and a drain electrode on the GaN buffer layer of the epitaxial substrate.

[0144] 1.1) Photoetching the source electrode region and the drain electrode region on the GaN cap layer:

[0145] The concrete realization of this step is identical with the step 1a) among the embodiment one;

[0146] 1.2) Evaporate the source and drain electrodes on the GaN cap layer within the source and drain electrode regions and on the photoresist outside the source and drain electrode regions:

[0147] The concrete realization of this step is identical with the step 1b) among the embodiment one;

[0148] 1.3) Put the ohmic metal evaporated and stripped sample into a rapid thermal annealing furnace for annealing treatment, so that th...

Embodiment 3

[0175] Embodiment 3, a GaN-based insulated gate high electron mobility transistor with an AlON compound gate dielectric layer thickness of 8 nm is fabricated on a Si substrate by using a plasma-assisted oxidation process.

[0176] Step A, making source electrodes and drain electrodes on the GaN buffer layer of the epitaxial substrate.

[0177] The specific implementation of this step is the same as step 1 in the first embodiment.

[0178] In step B, the electrical isolation area of the active area is photolithographically etched on the GaN cap layer, and the electrical isolation of the active area of the device is fabricated by using an ion implantation process.

[0179] The specific implementation of this step is the same as step 2 in the second embodiment.

[0180] In step C, a SiN passivation layer is grown on the GaN cap layer of the source electrode, the drain electrode and the active region by PECVD process.

[0181] The specific implementation of this step is the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More