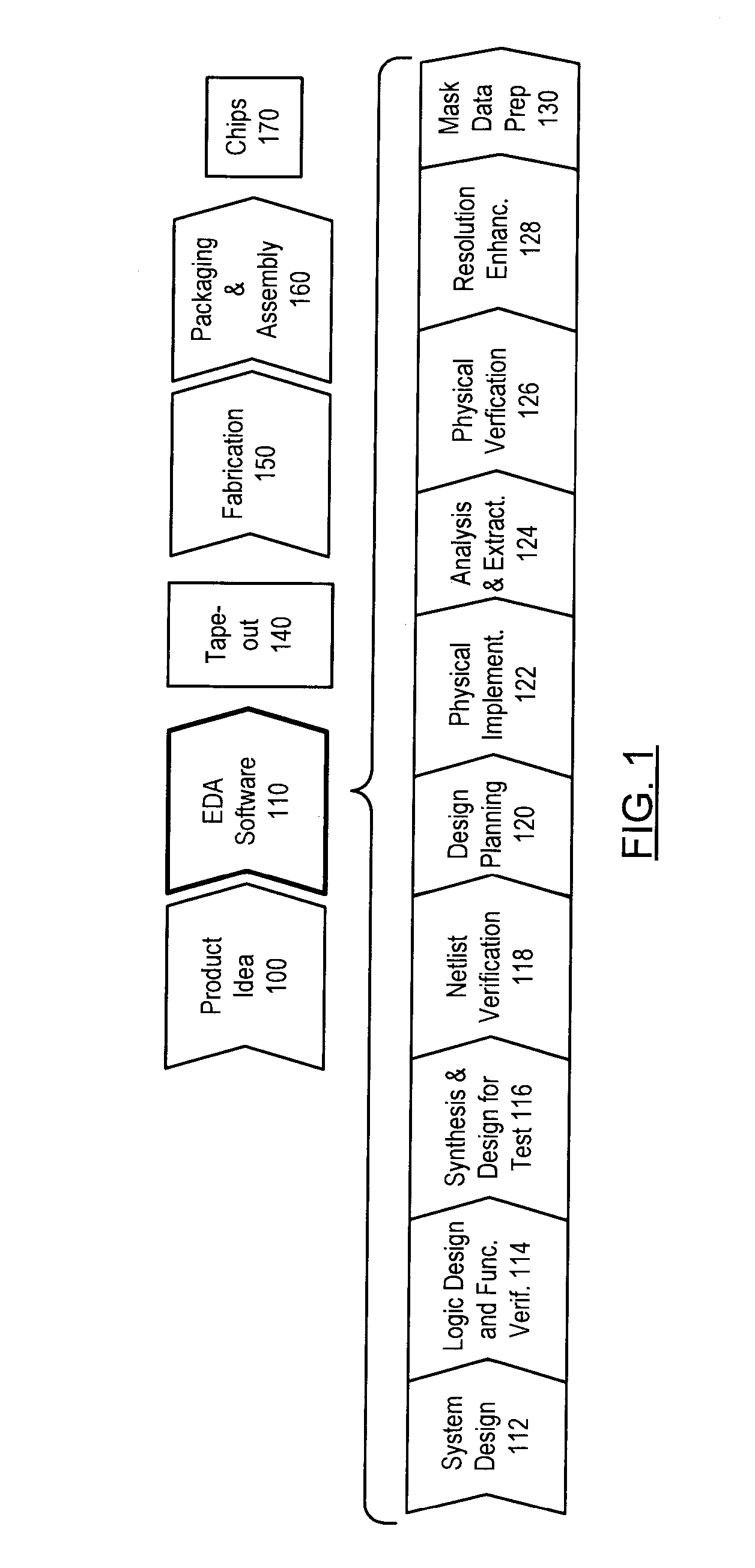

Patents

Literature

475 results about "Stress effects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Common effects of stress on the body include muscle tension and pain as a result of the body's muscles tightening. Stress can also result in chest pain and a rapid heartbeat, headaches, fatigue and low energy, nausea, and stomach pain or an upset stomach including diarrhoea and constipation.

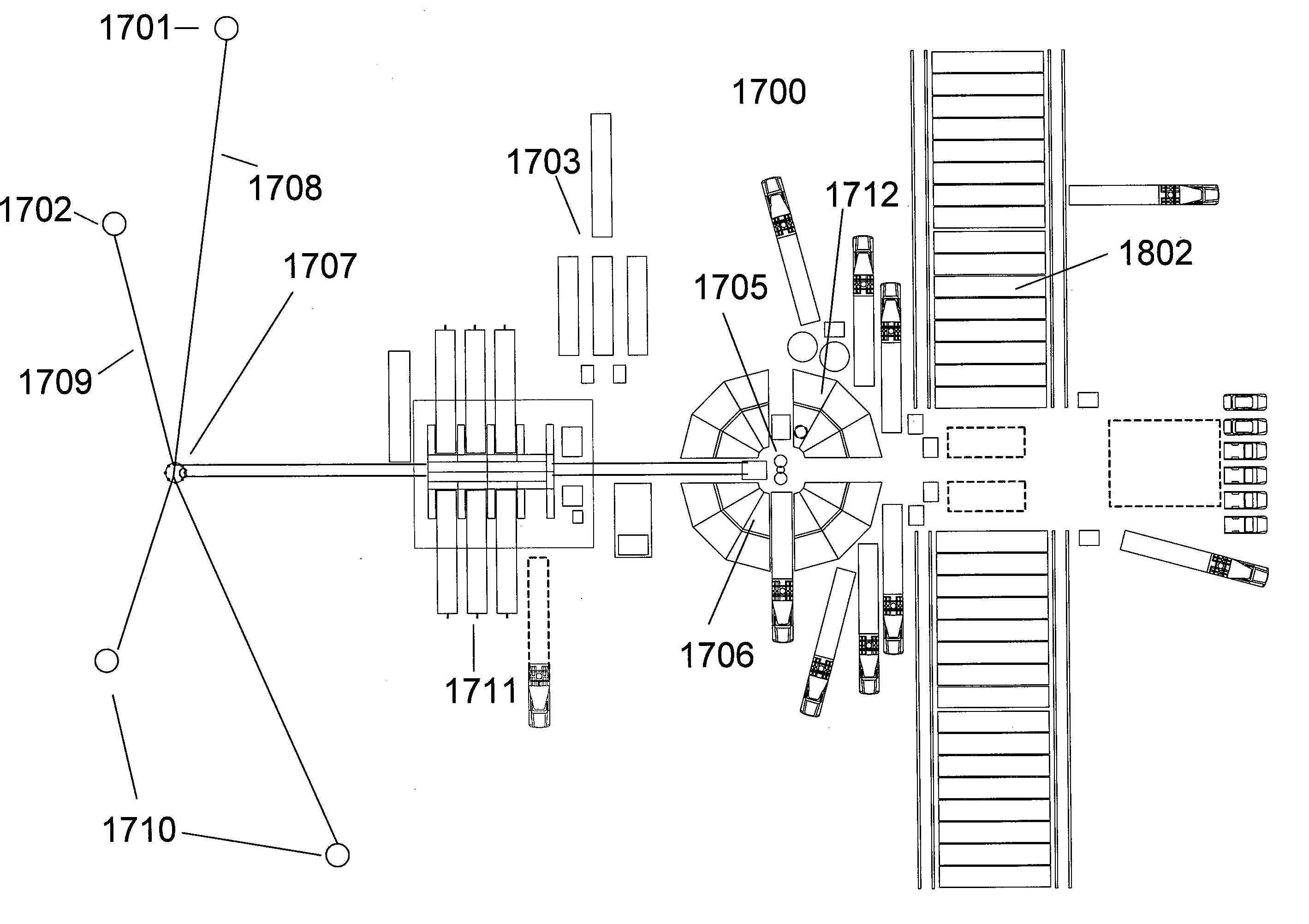

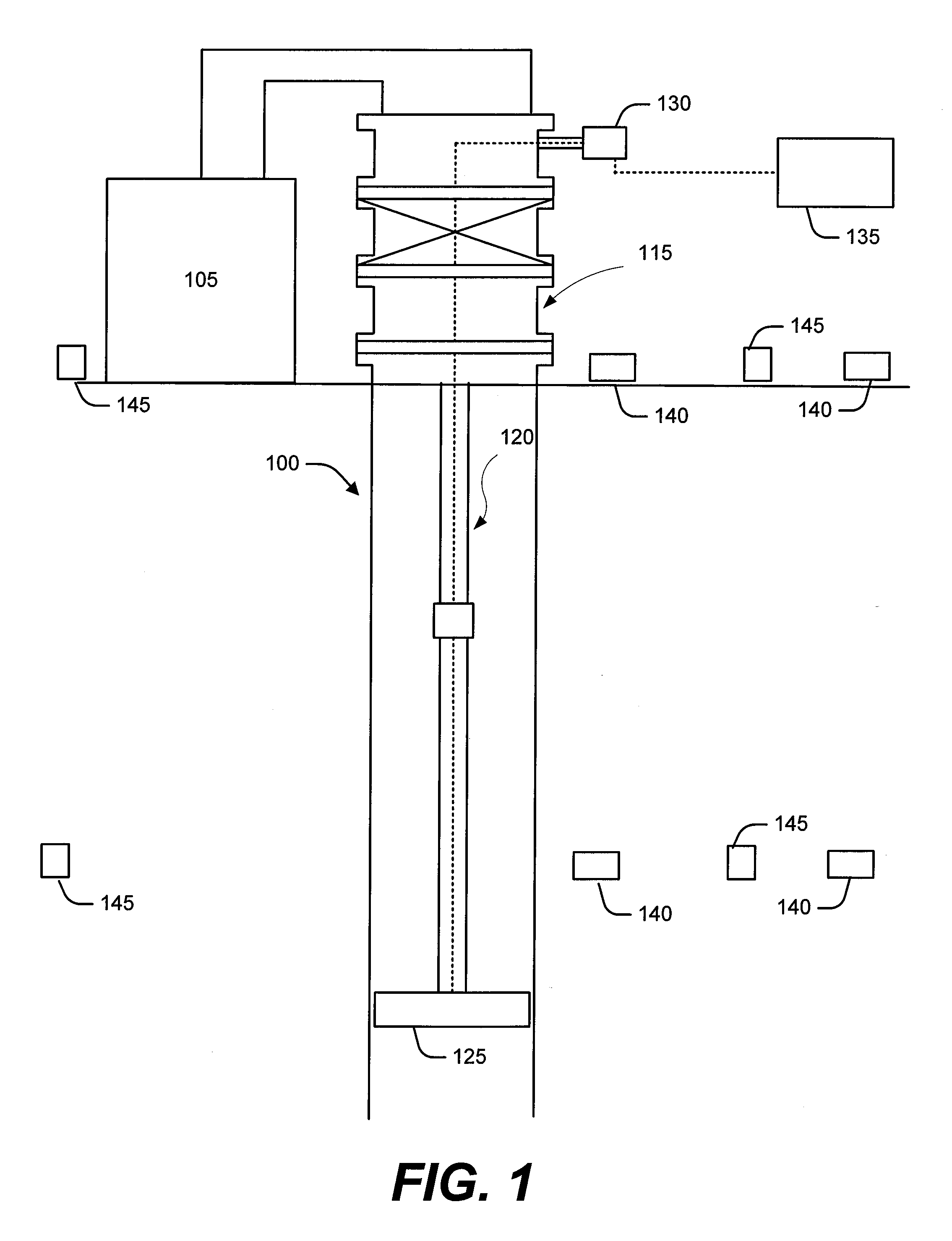

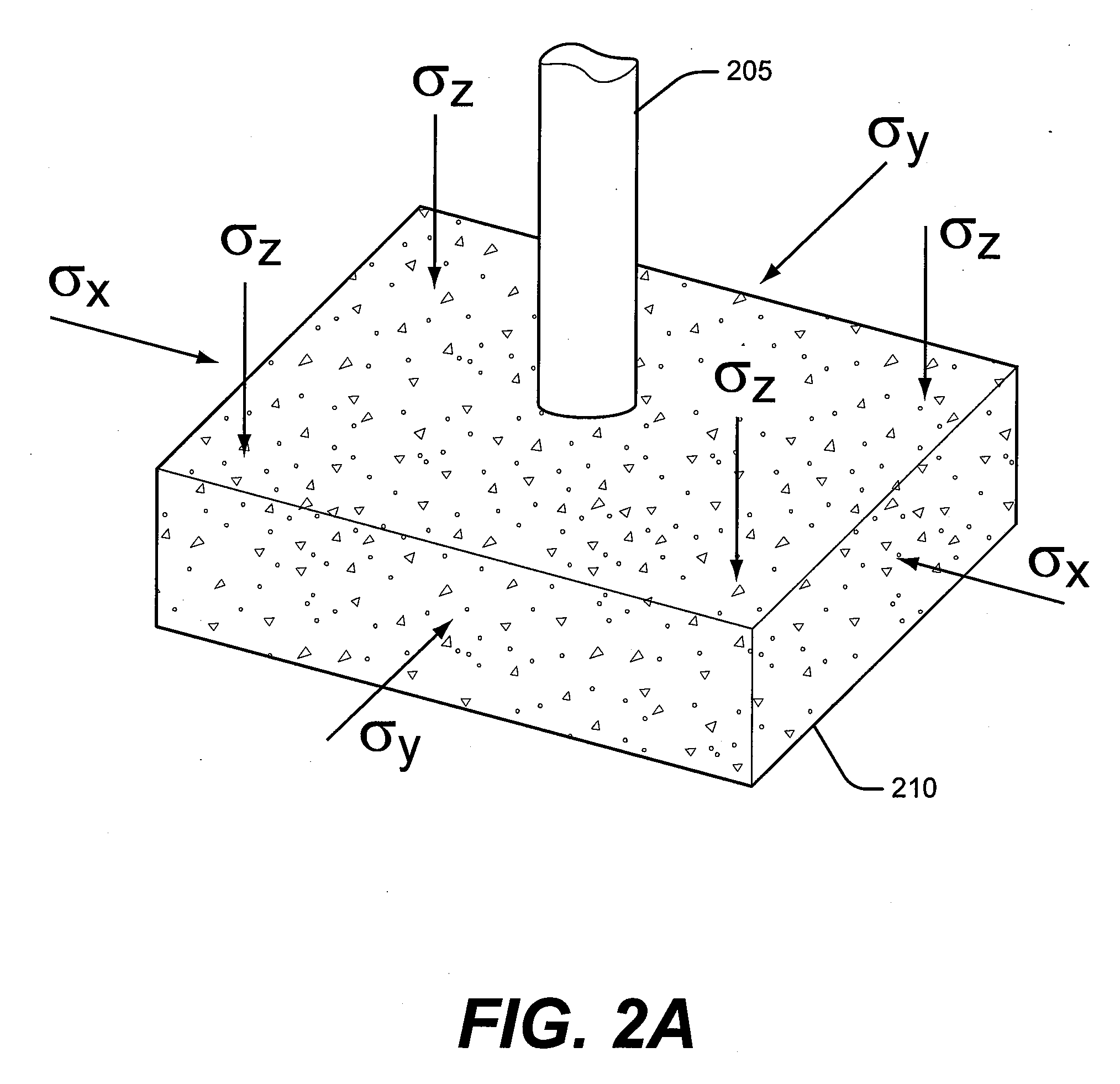

Method and Apparatus for Orchestration of Fracture Placement From a Centralized Well Fluid Treatment Center

A method and apparatus for orchestrating multiple fractures at multiple well locations in a region by flowing well treatment fluid from a centralized well treatment fluid center is disclosed that includes the steps of configuring a well treatment fluid center for fracturing multiple wells, inducing a fracture at a first well location, measuring effects of stress fields from the first fracture, determining a time delay based in part upon the measured stress effects, inducing a second fracture after the time delay at a second location based upon the measured effects, and measuring the stress effects of stress fields from the second fracture. Sensors disposed about the region are adapted to output effects of the stress fields. Location and orientation of subsequent fractures is based on the combined stress effects of the stress fields as a result of the prior fractures which provides for optimal region development.

Owner:HALLIBURTON ENERGY SERVICES INC

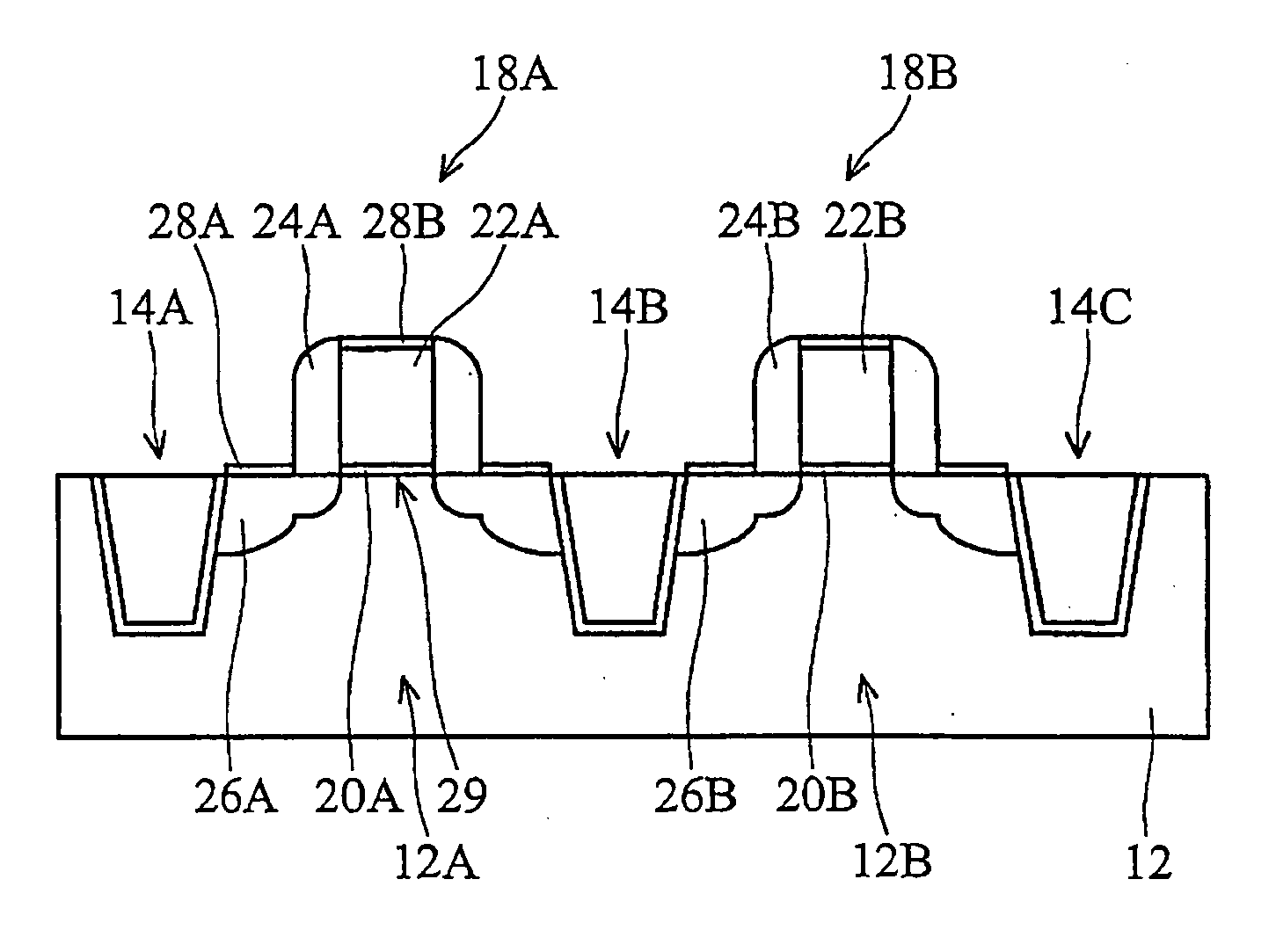

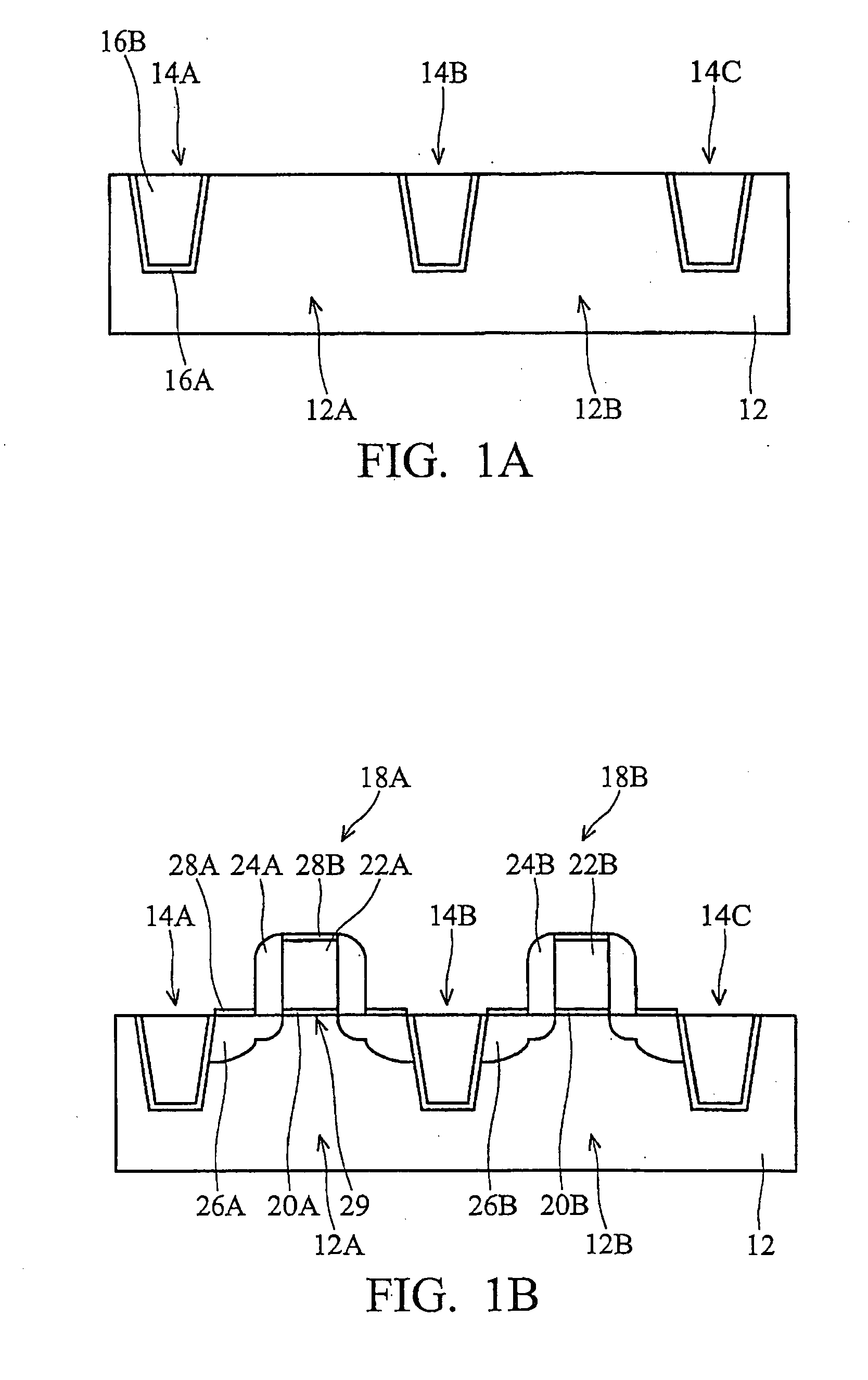

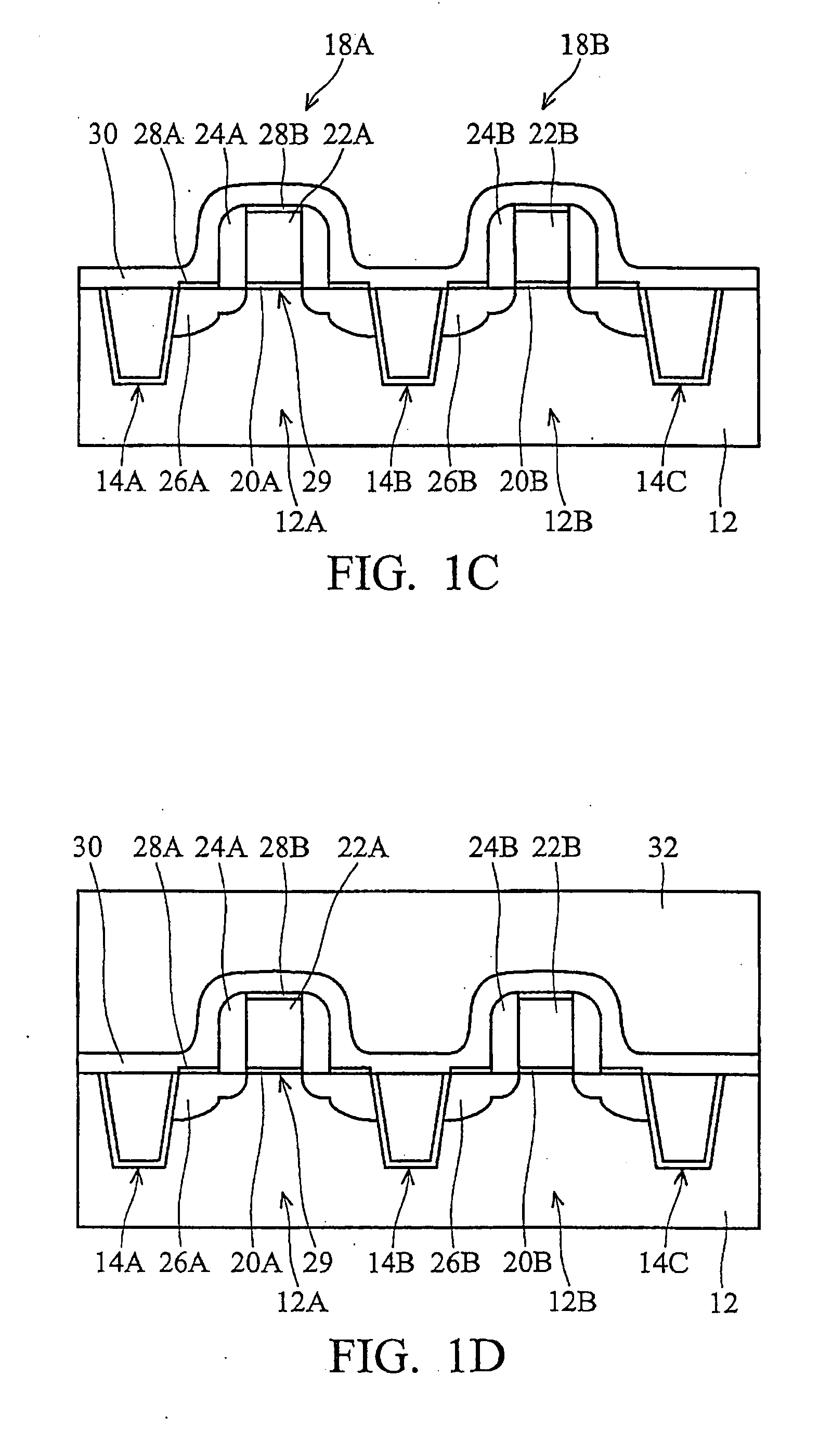

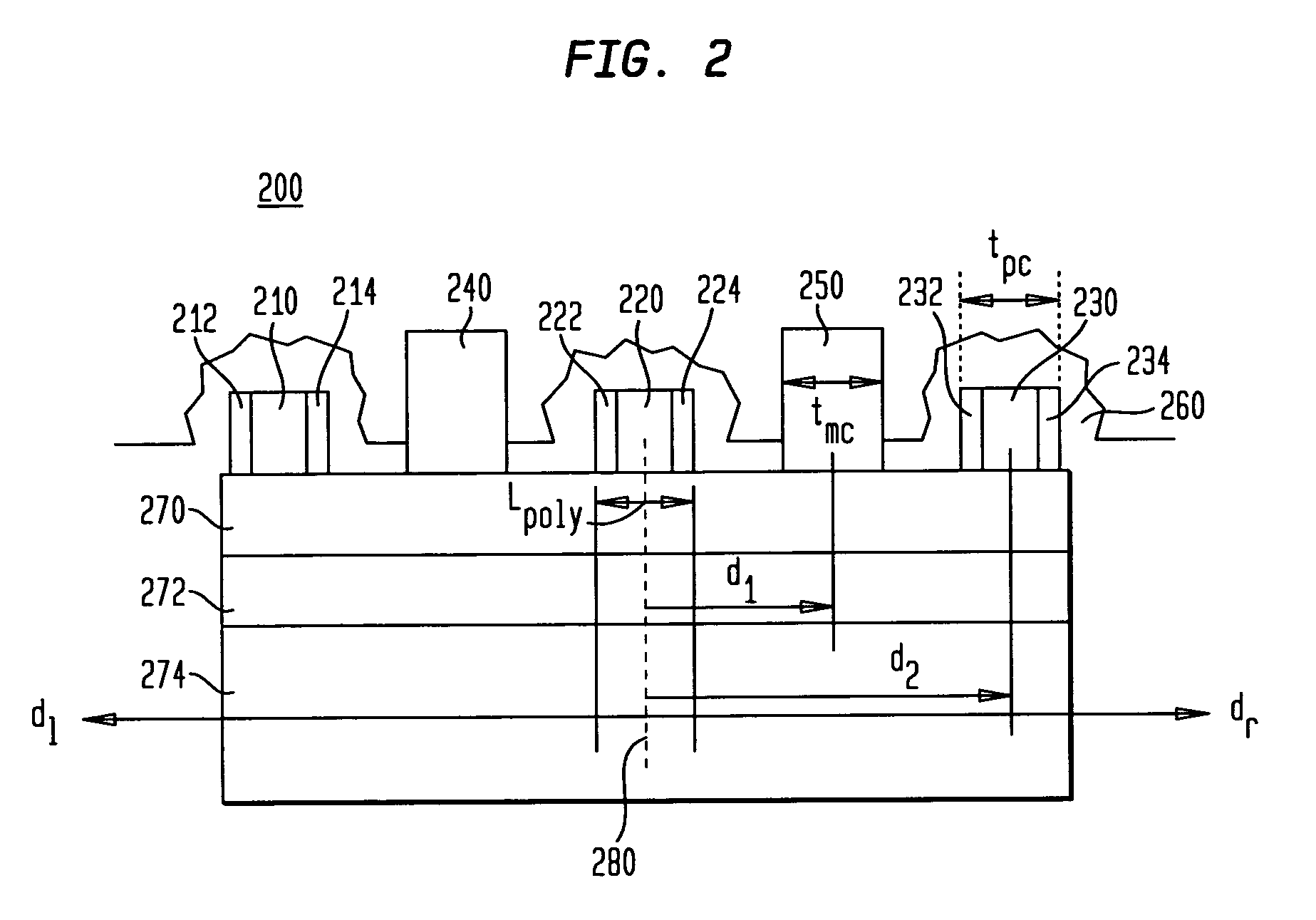

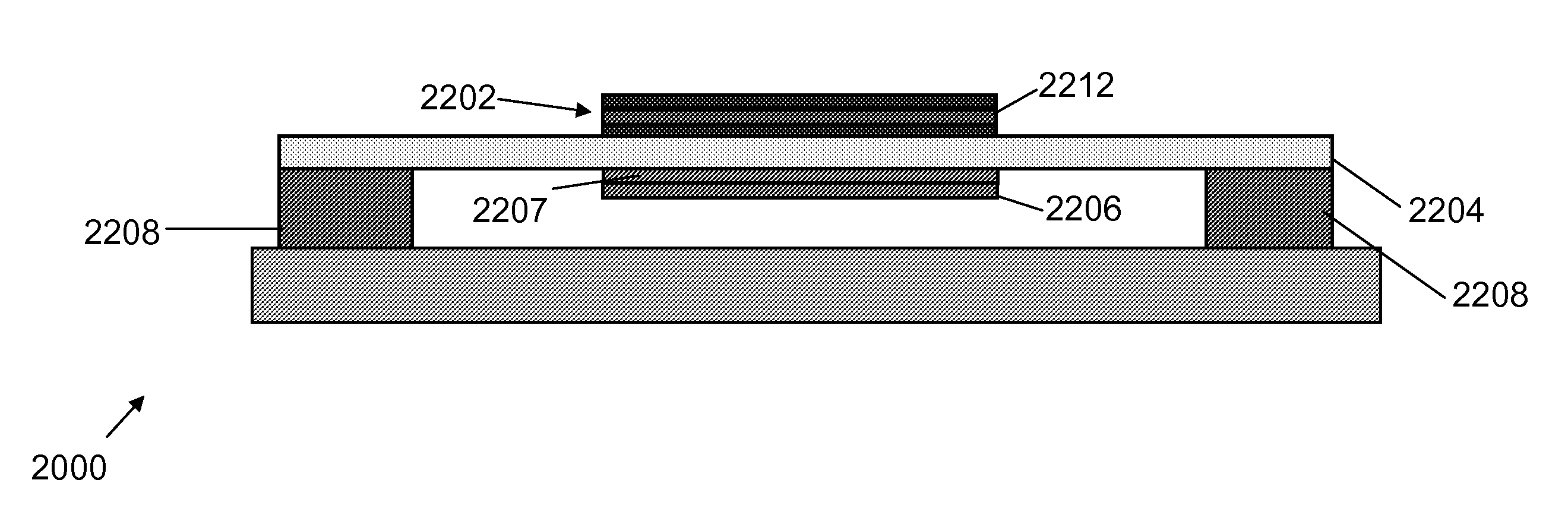

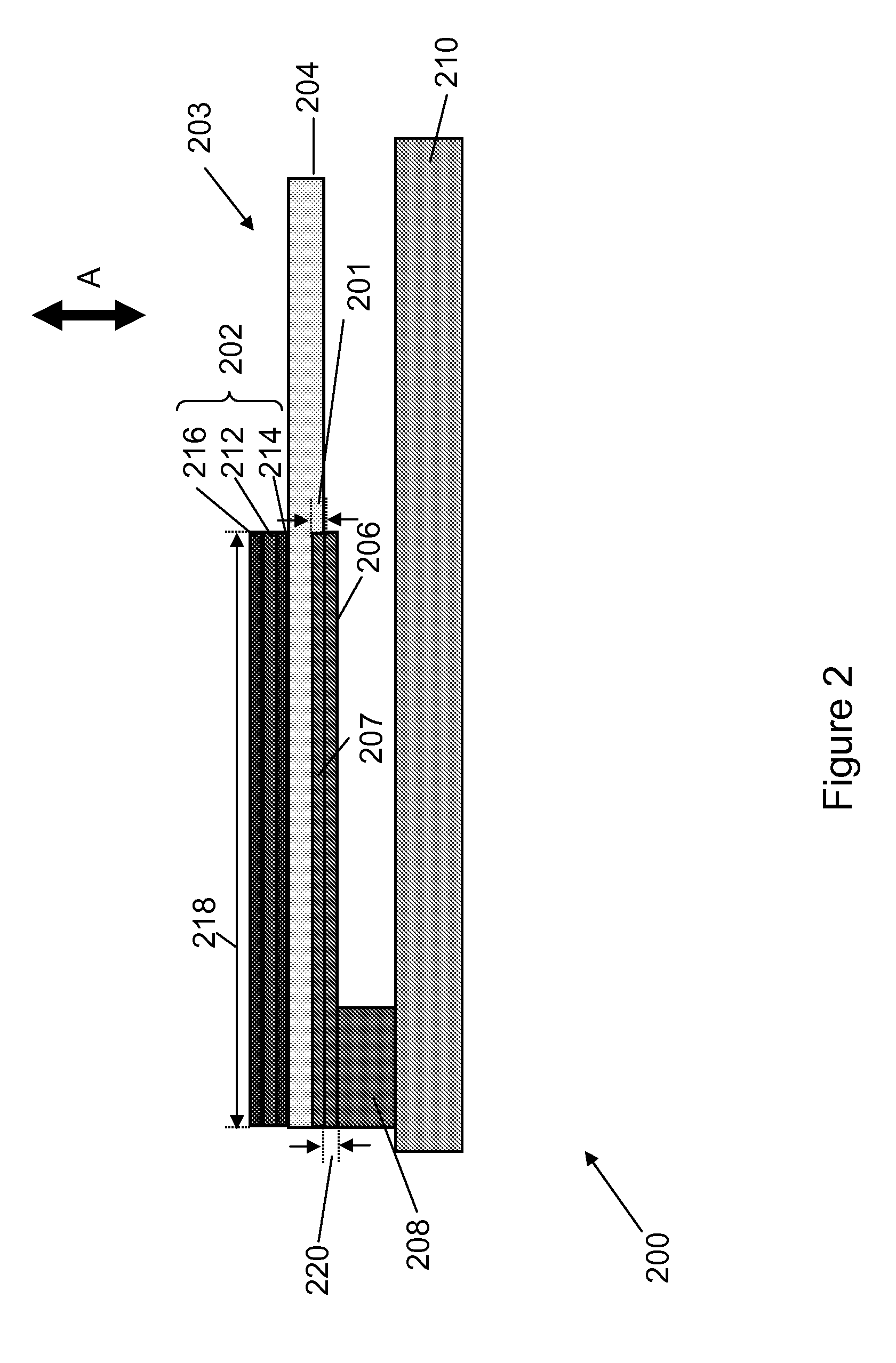

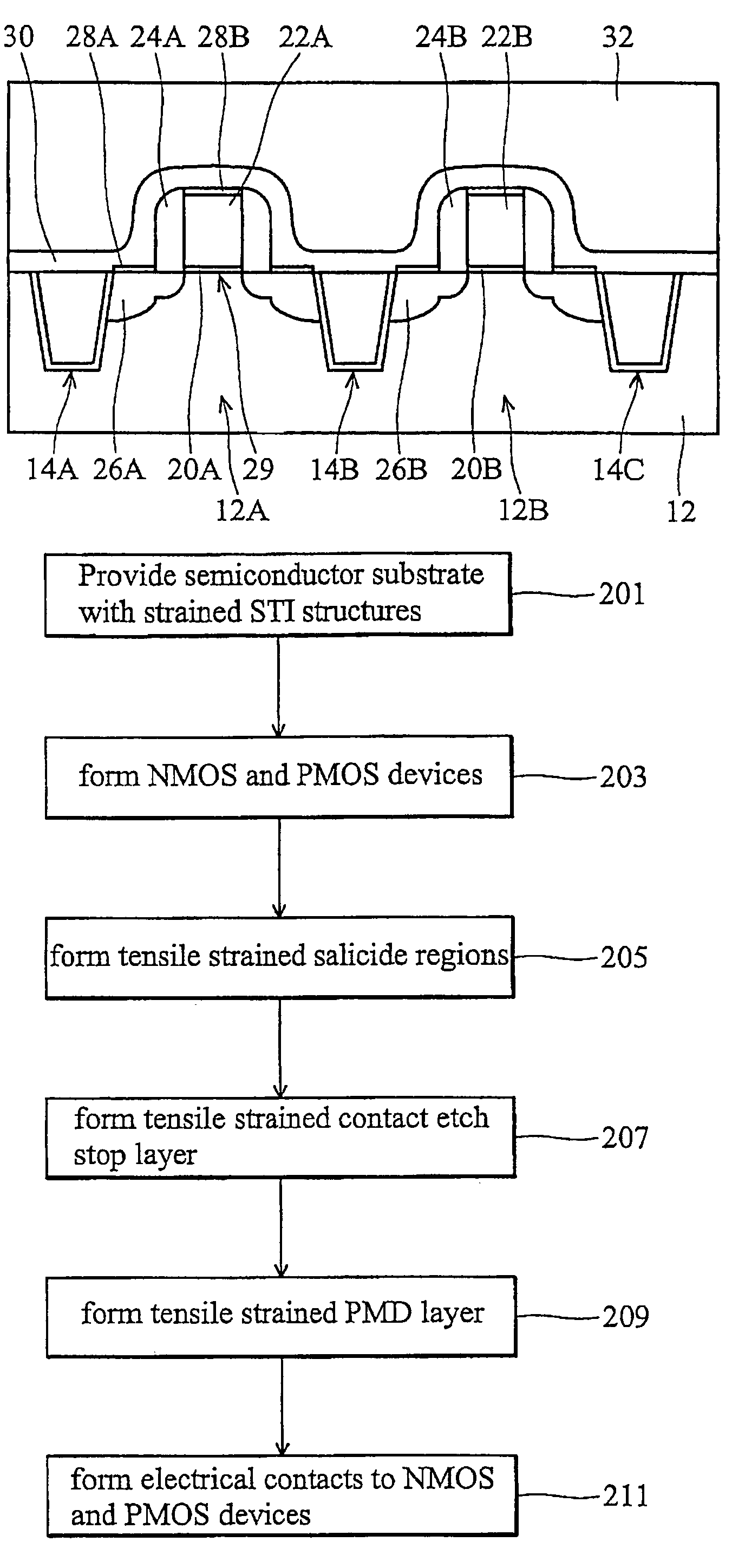

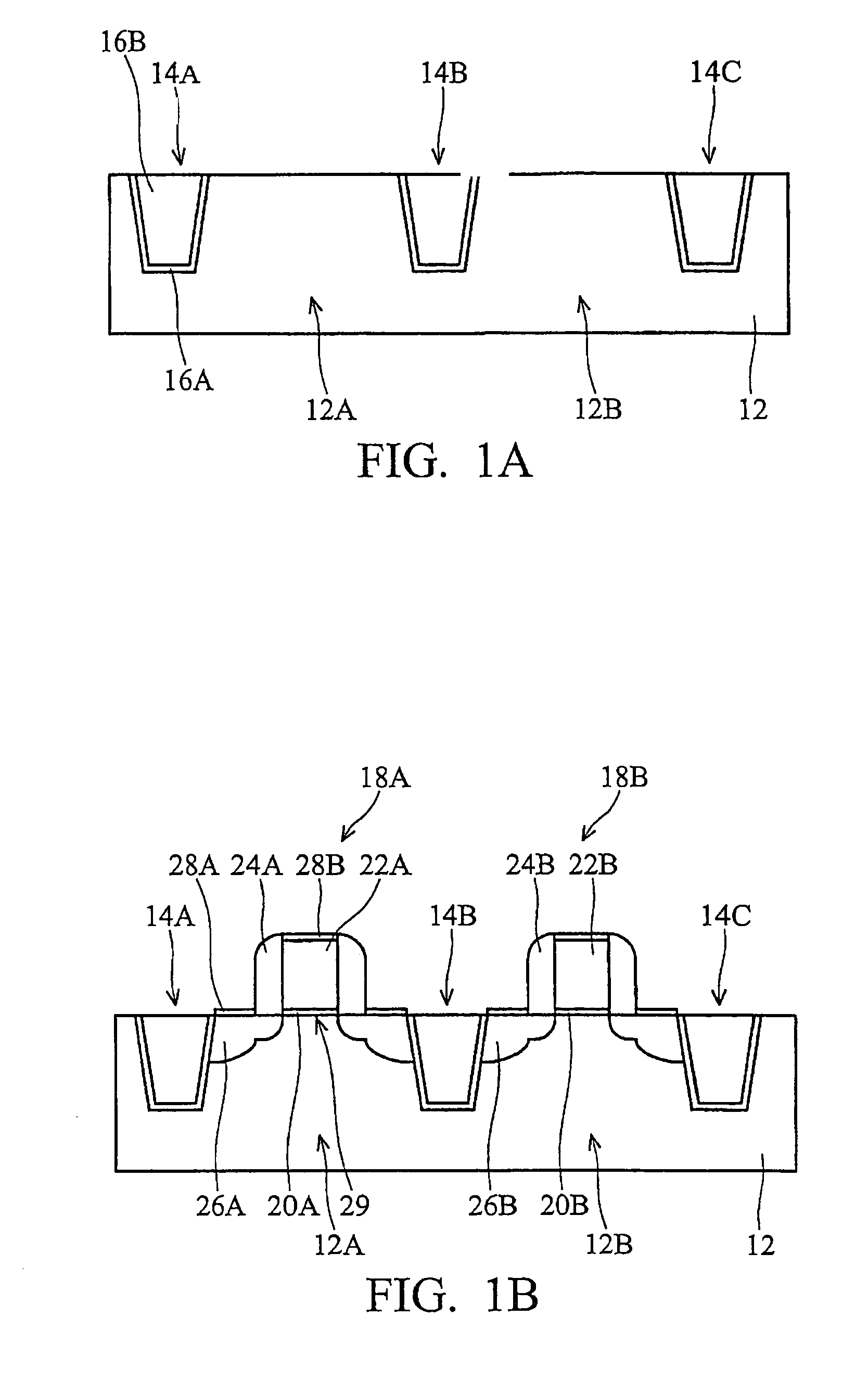

High performance strained channel mosfets by coupled stress effects

InactiveUS20050260806A1Improve device performanceReduce performanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETTensile strain

Strained channel transistors including a PMOS and NMOS device pair to improve an NMOS device performance without substantially degrading PMOS device performance and method for forming the same, the method including providing a semiconductor substrate; forming strained shallow trench isolation regions in the semiconductor substrate; forming PMOS and NMOS devices on the semiconductor substrate including doped source and drain regions; forming a tensile strained contact etching stop layer (CESL) over the PMOS and NMOS devices; and, forming a tensile strained dielectric insulating layer over the CESL layer.

Owner:TAIWAN SEMICON MFG CO LTD

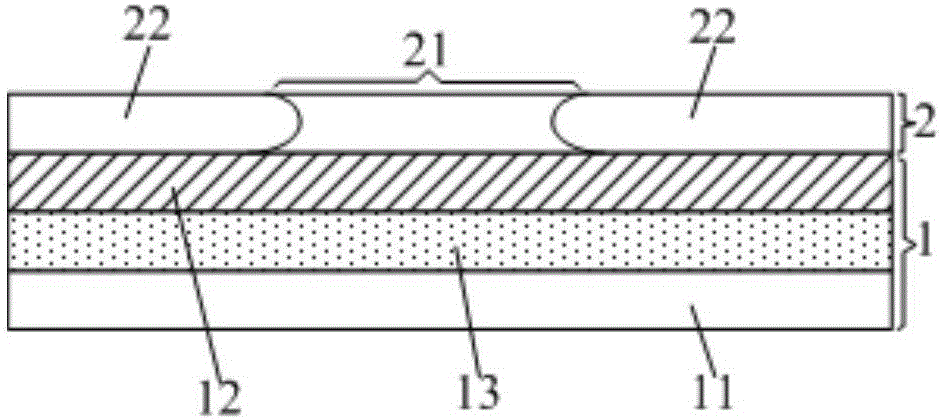

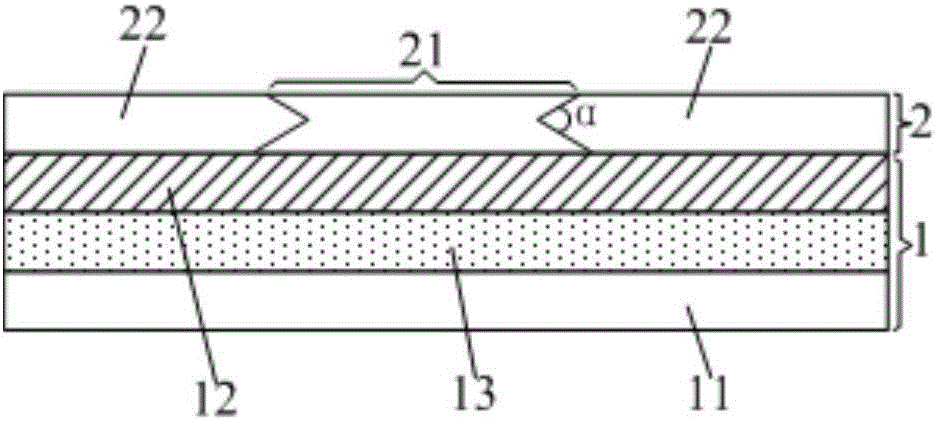

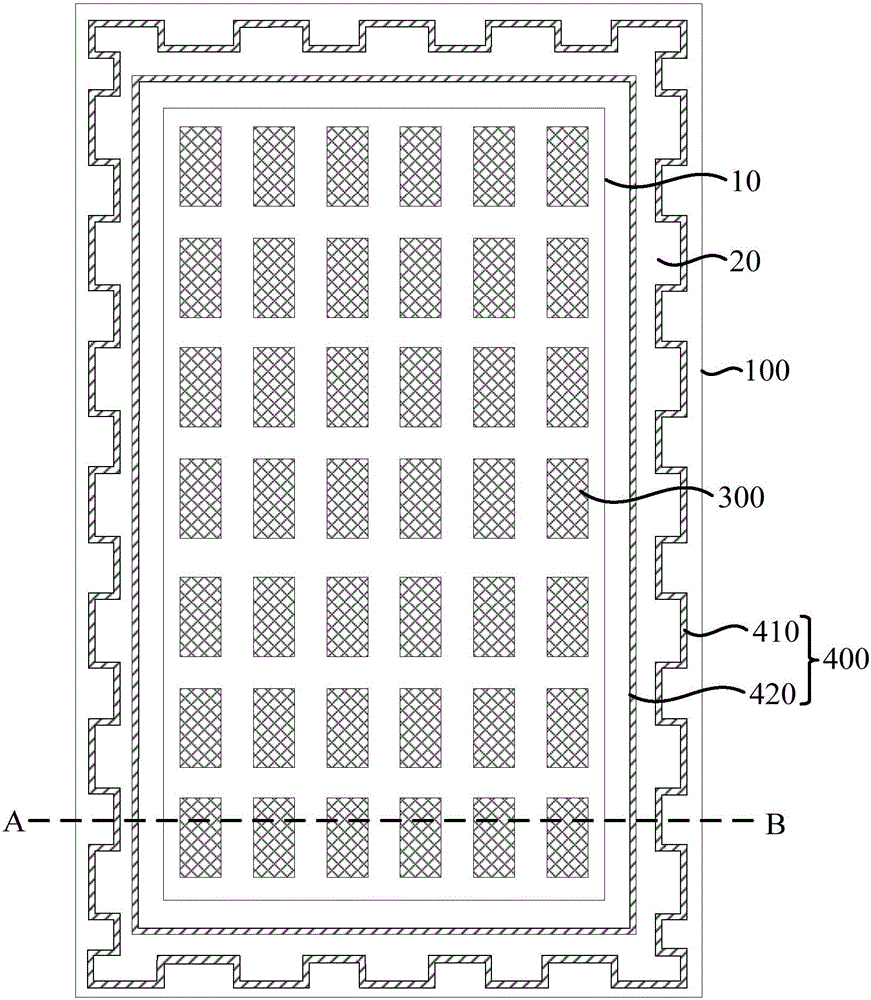

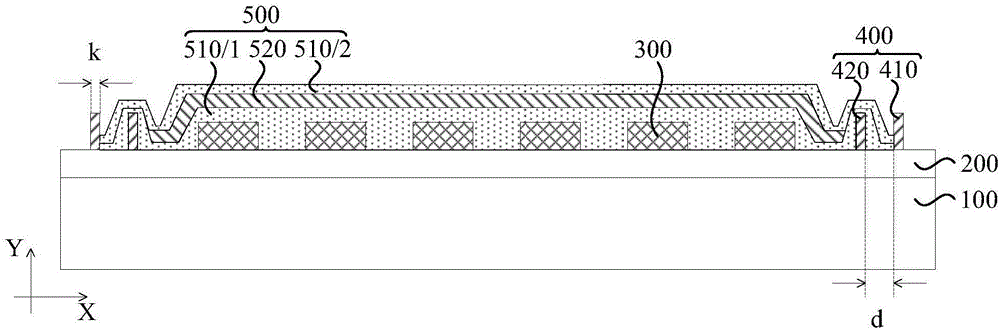

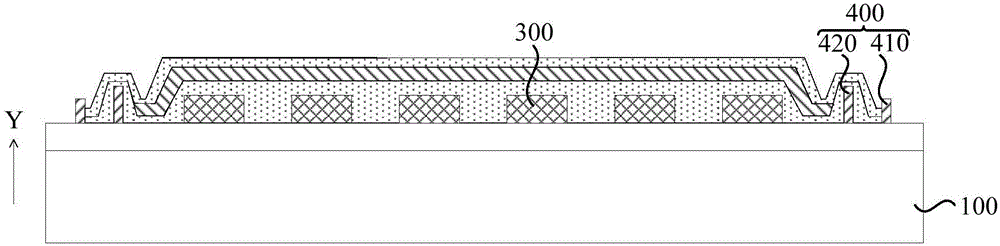

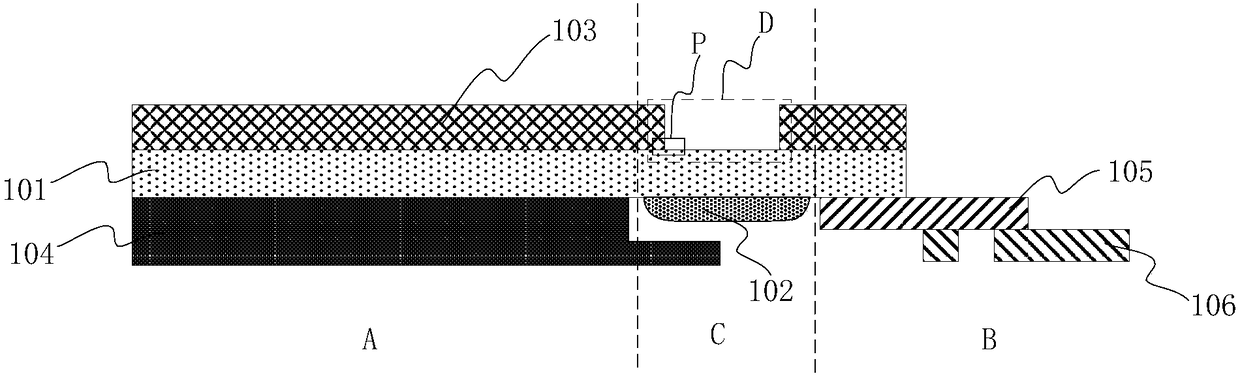

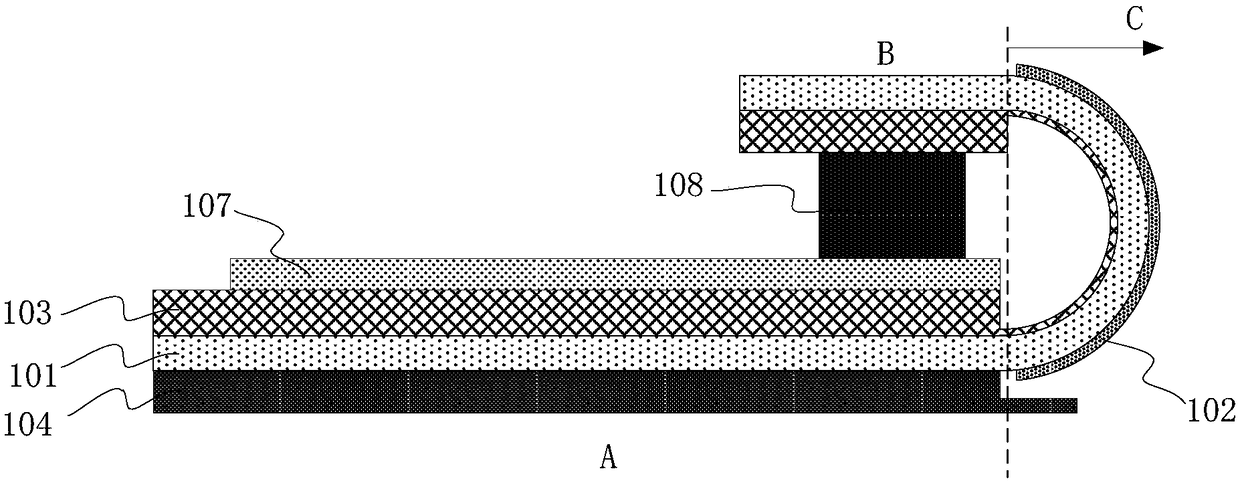

Display panel and display device

The invention provides a display panel and a display device. The display panel comprises a flexible display substrate and a protective cover plate. The display substrate is covered with the protective cover plate, the protective cover plate comprises a flexible area, and the flexible area corresponds to a folding area located on the flexible display substrate, and is made from a material with the elasticity modulus smaller than 100 MPa and the tensile strength larger than 50 MPa. When the display panel is bent, a neutral layer (namely, a film layer with the stress of 0 in the bending process) can move towards a device layer (namely, a luminescent device layer) in the flexible display substrate, and is closer to the device layer in the flexible display substrate accordingly, the stress of the device layer in the flexible display substrate is reduced, the strain after the device layer in the flexible display substrate suffers from the stress effect is further reduced, the display panel is bent and then can further recover the smooth stage in the short time, and finally, damage to all the film layers in the display-panel bending process is reduced or avoided.

Owner:BOE TECH GRP CO LTD

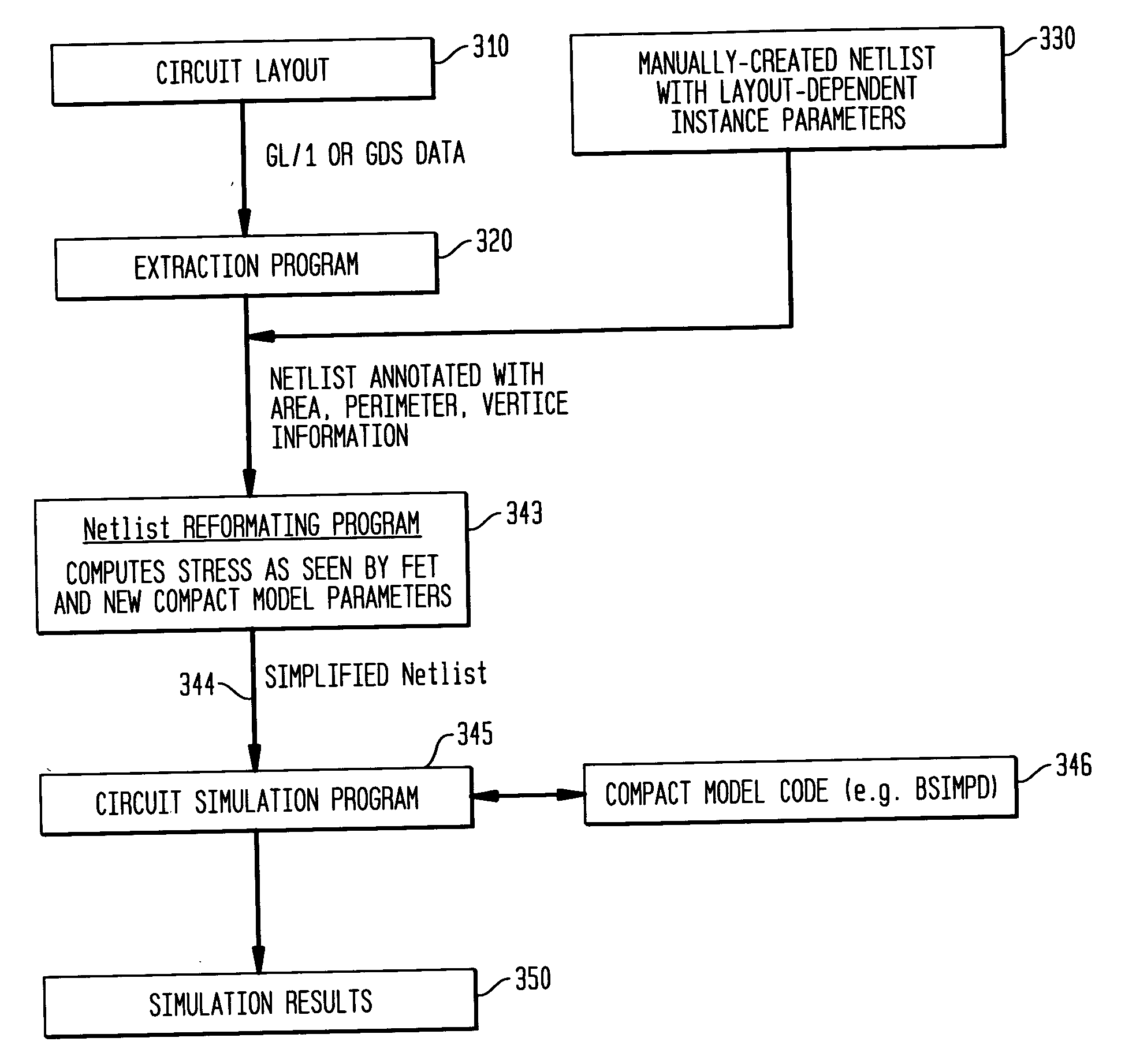

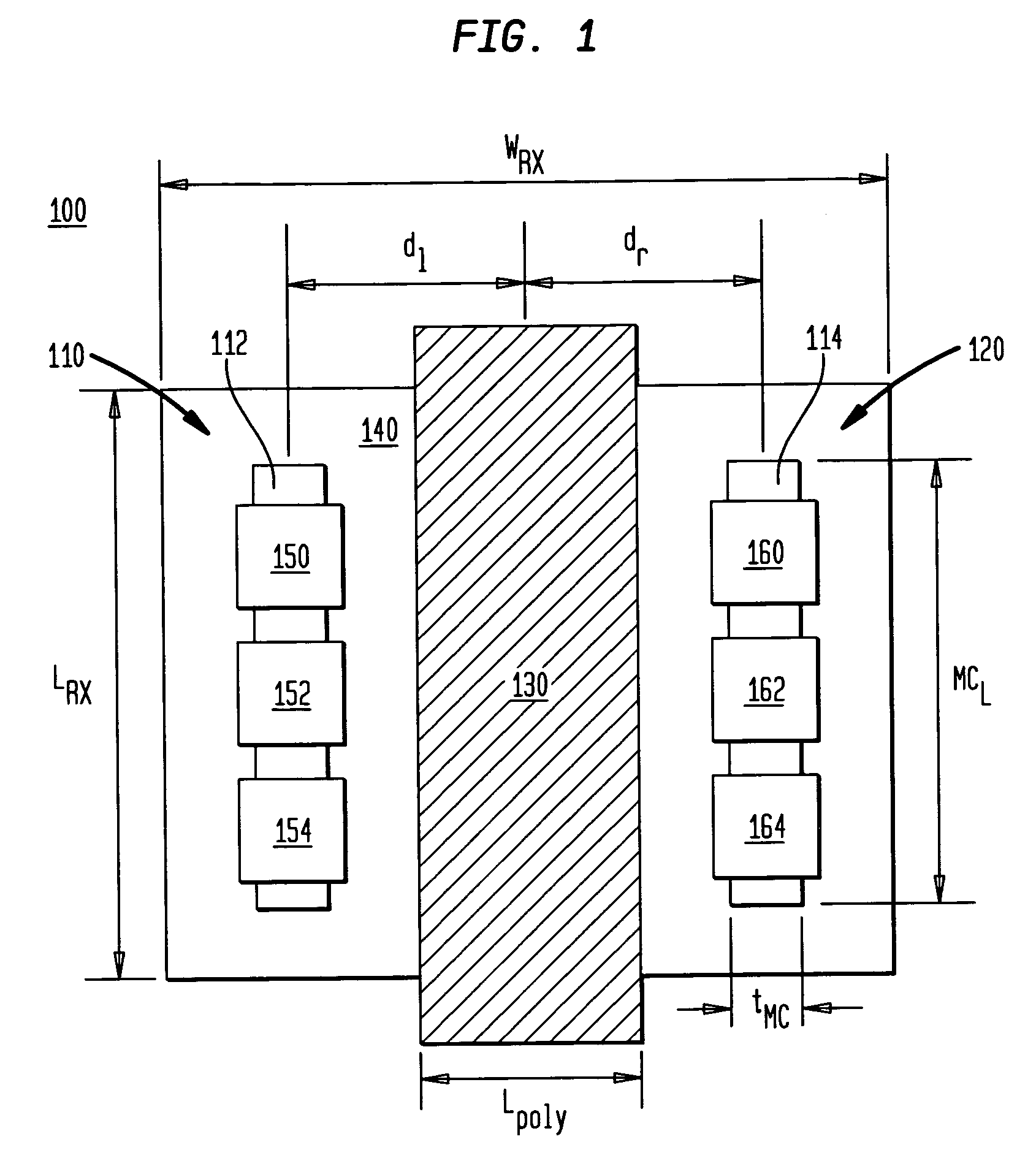

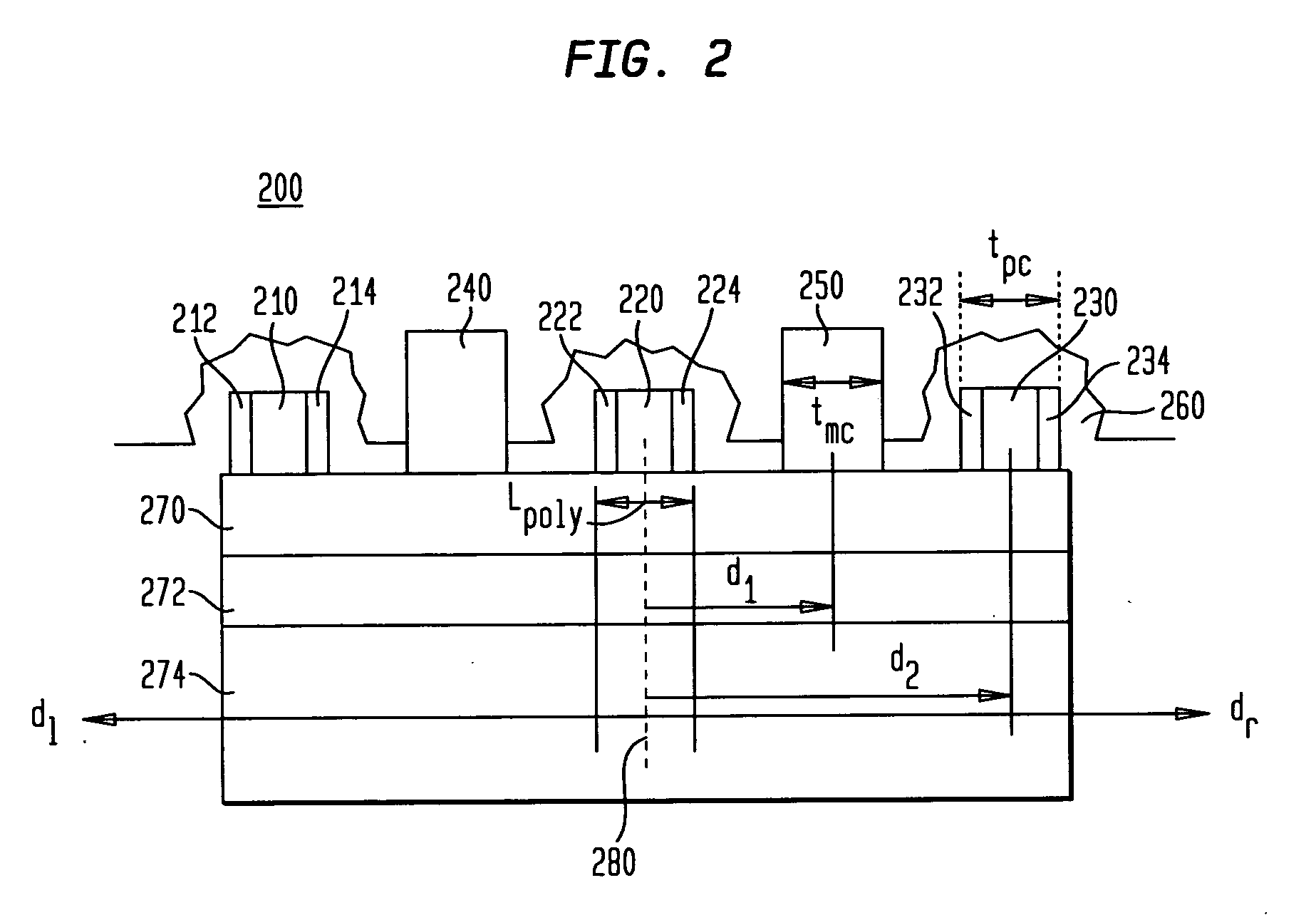

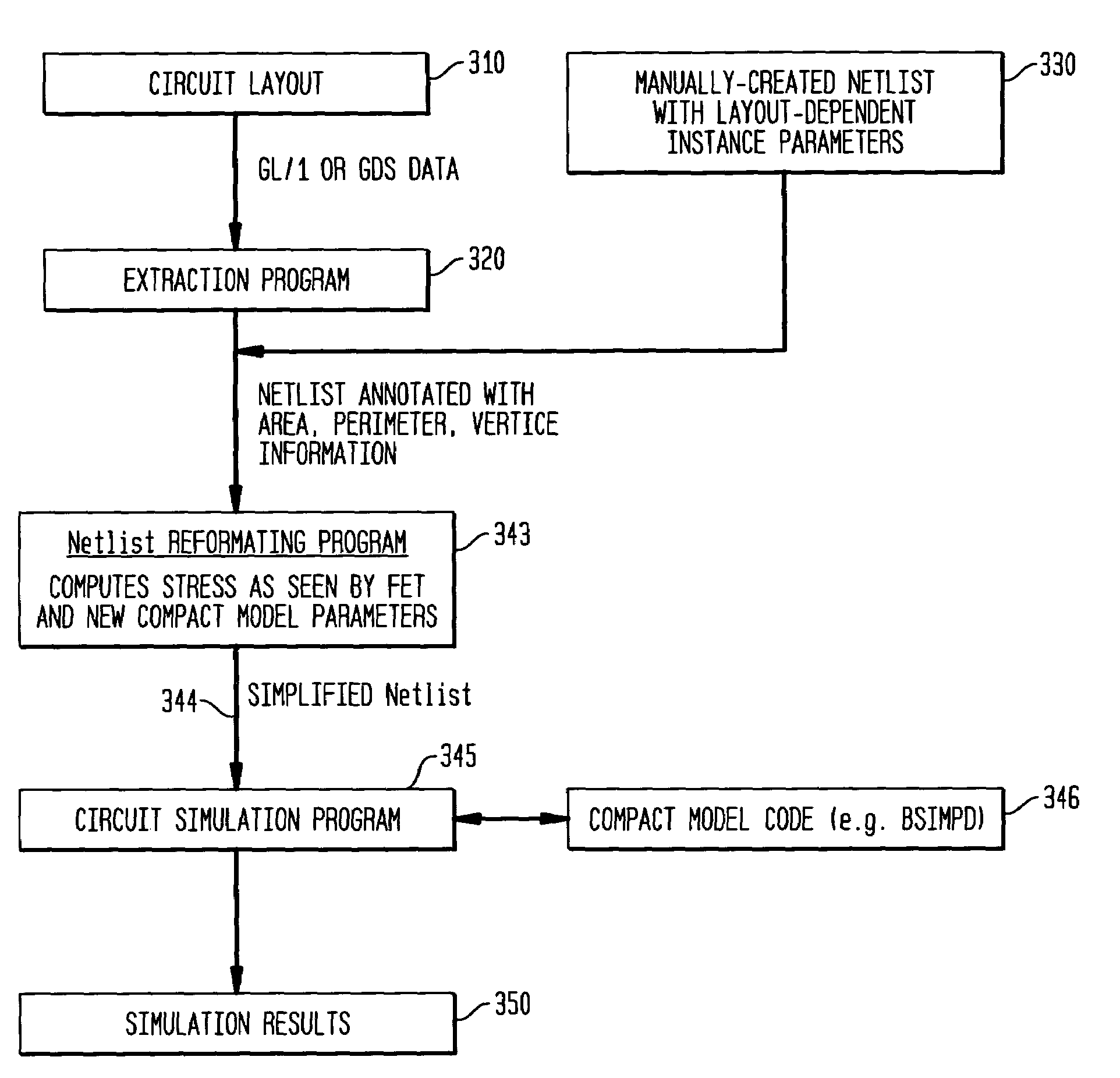

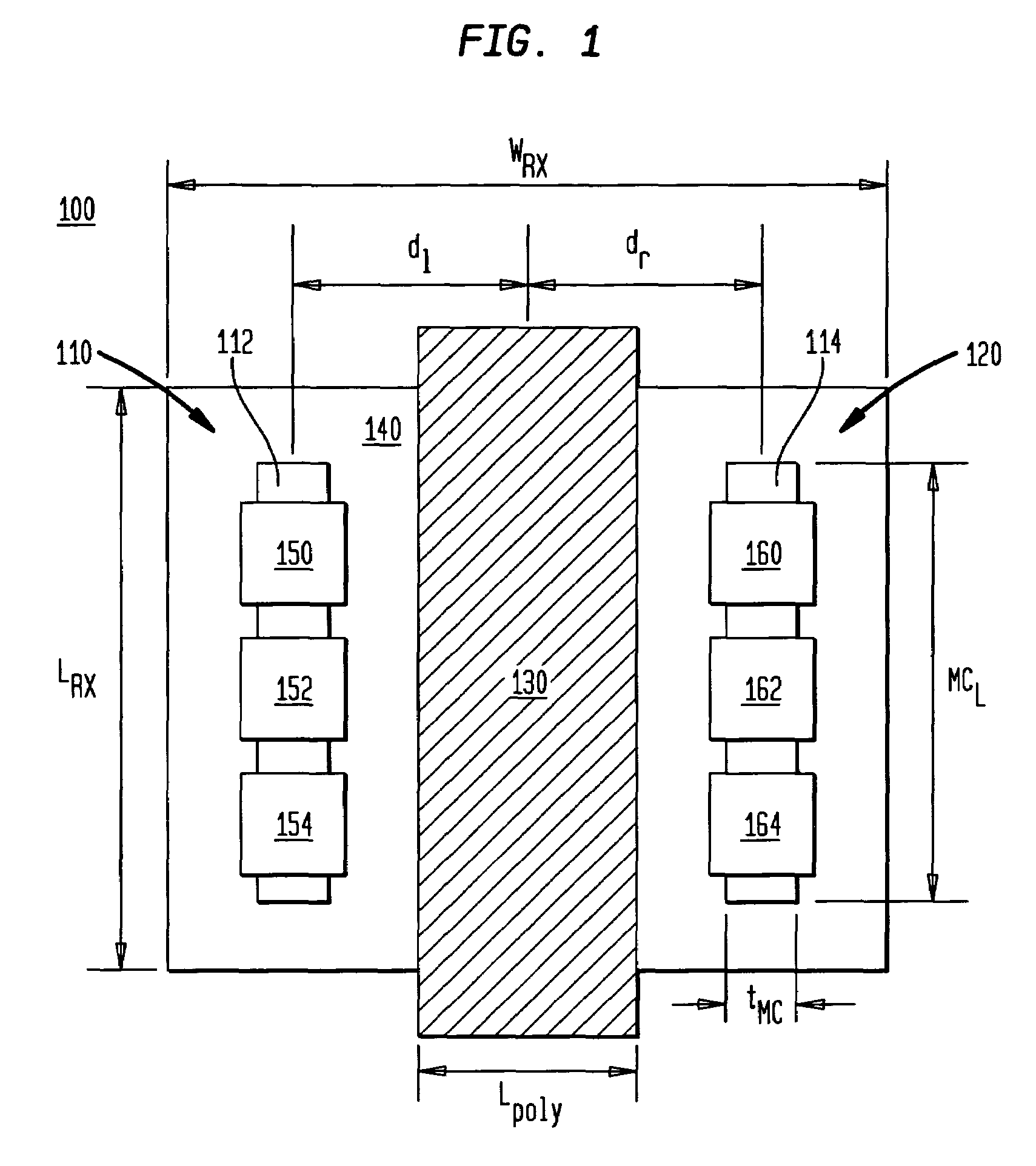

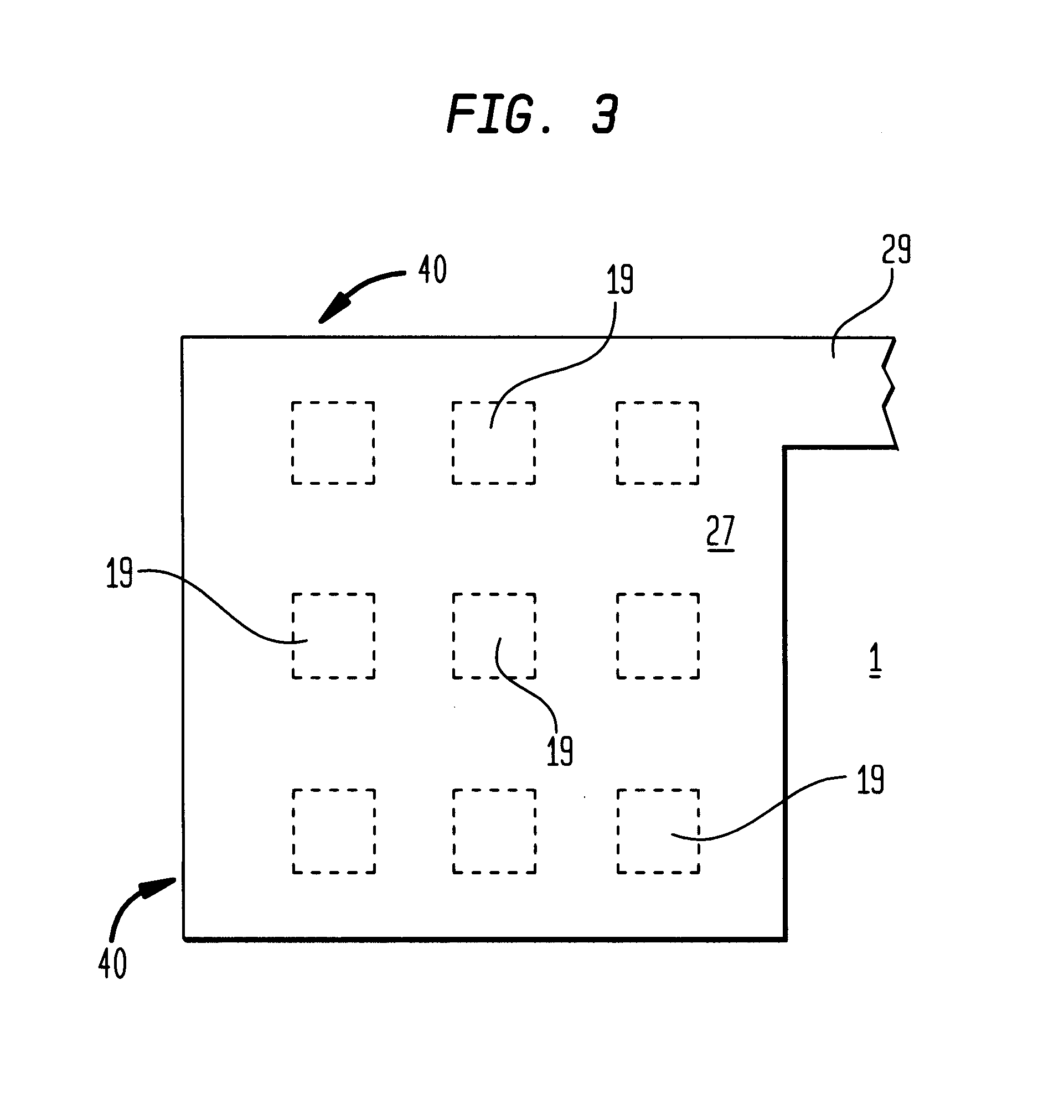

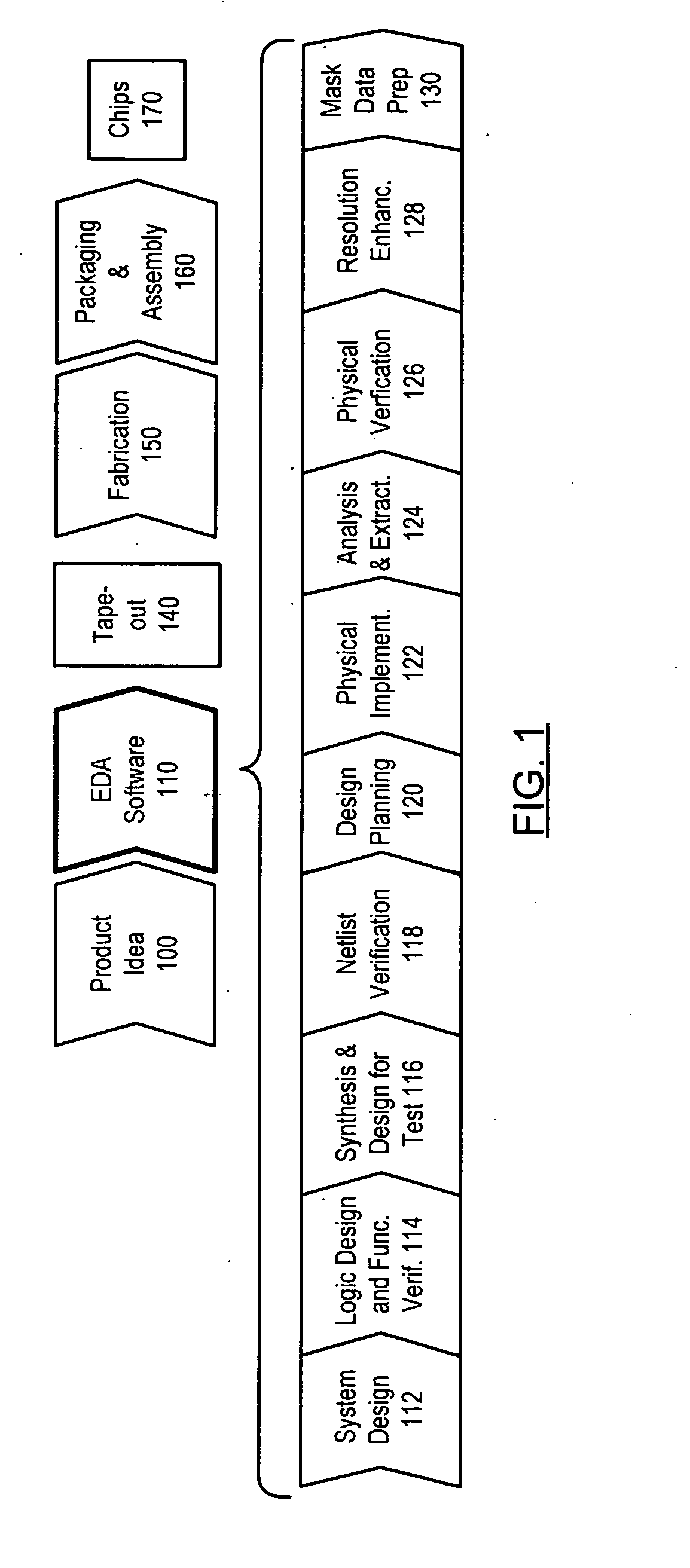

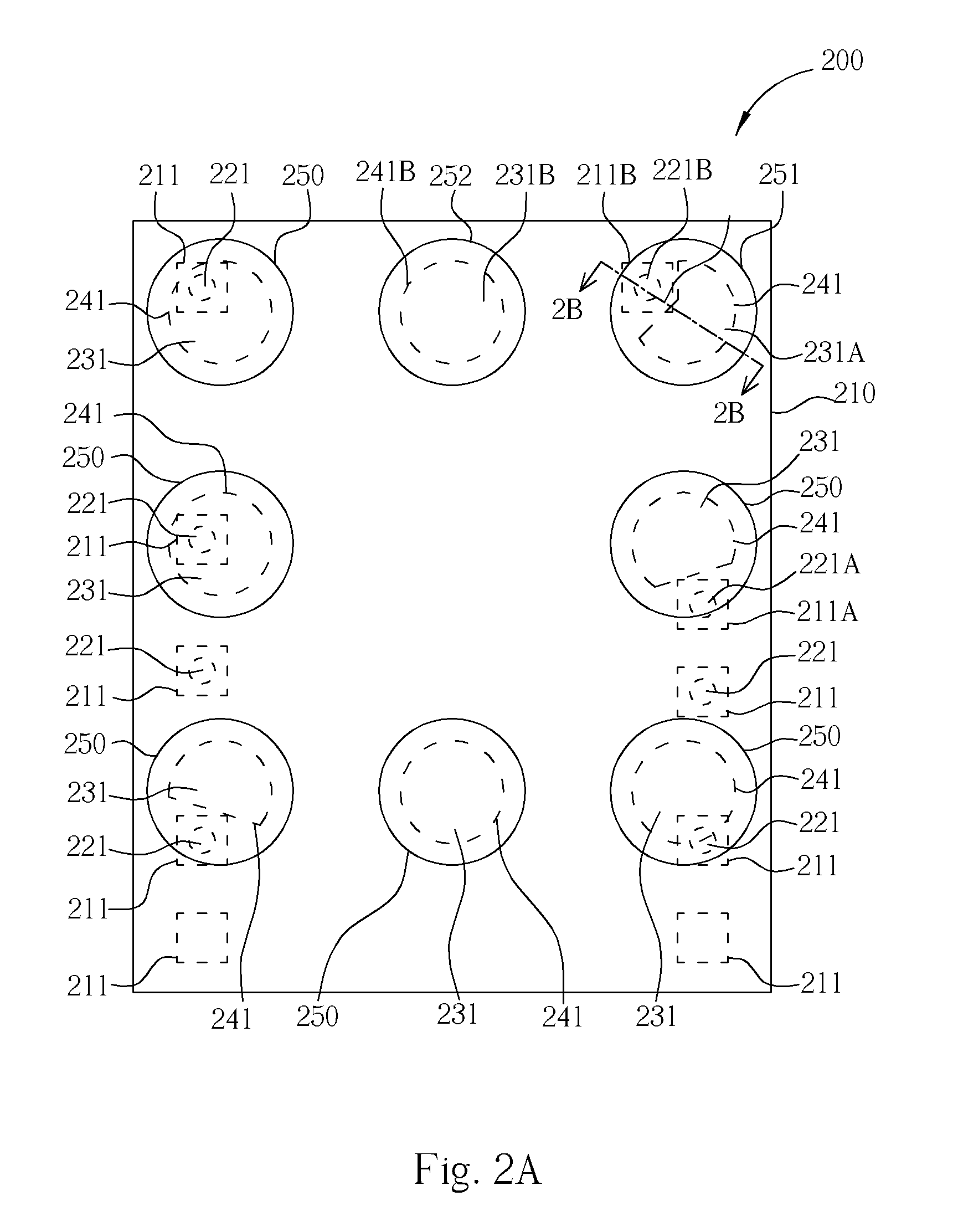

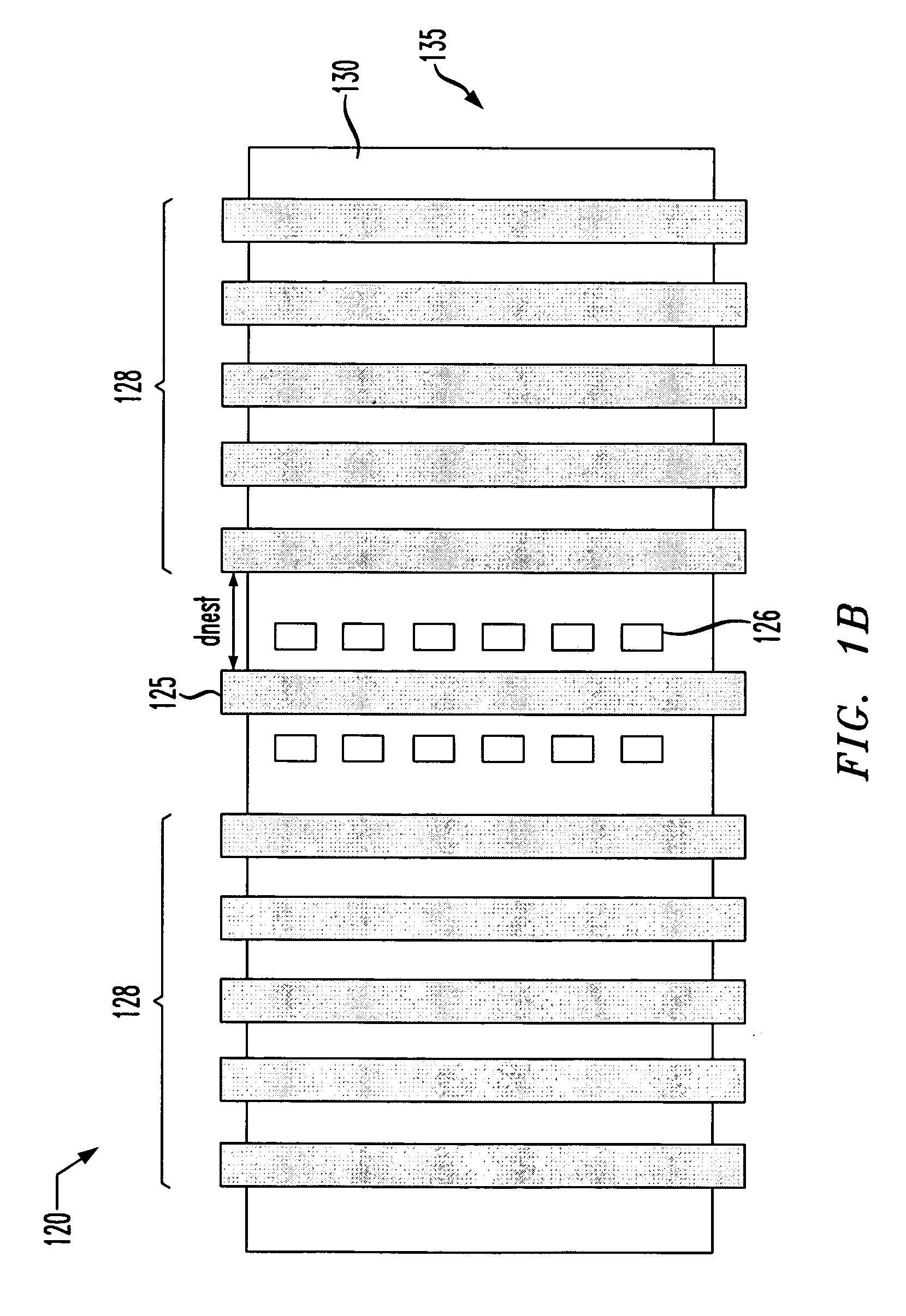

Methodology for layout-based modulation and optimization of nitride liner stress effect in compact models

ActiveUS20070028195A1CAD circuit designSoftware simulation/interpretation/emulationDevice materialModel system

System and method for compact model algorithms to accurately account for effects of layout-induced changes in nitride liner stress in semiconductor devices. The layout-sensitive compact model algorithms account for the impact of large layout variation on circuits by implementing algorithms for obtaining the correct stress response approximations and layout extraction algorithms for obtaining the correct geometric parameters that drive the stress response. In particular, these algorithms include specific information from search “buckets” that are directionally-oriented and include directionally-specific distance measurements for analyzing in detail the specific shape neighborhood of the semiconductor device. The algorithms are additionally adapted to enable the modeling and stress impact determination of a device having single stress liner film and dual-stress liners (two different liner films that abut at an interface).

Owner:GLOBALFOUNDRIES US INC

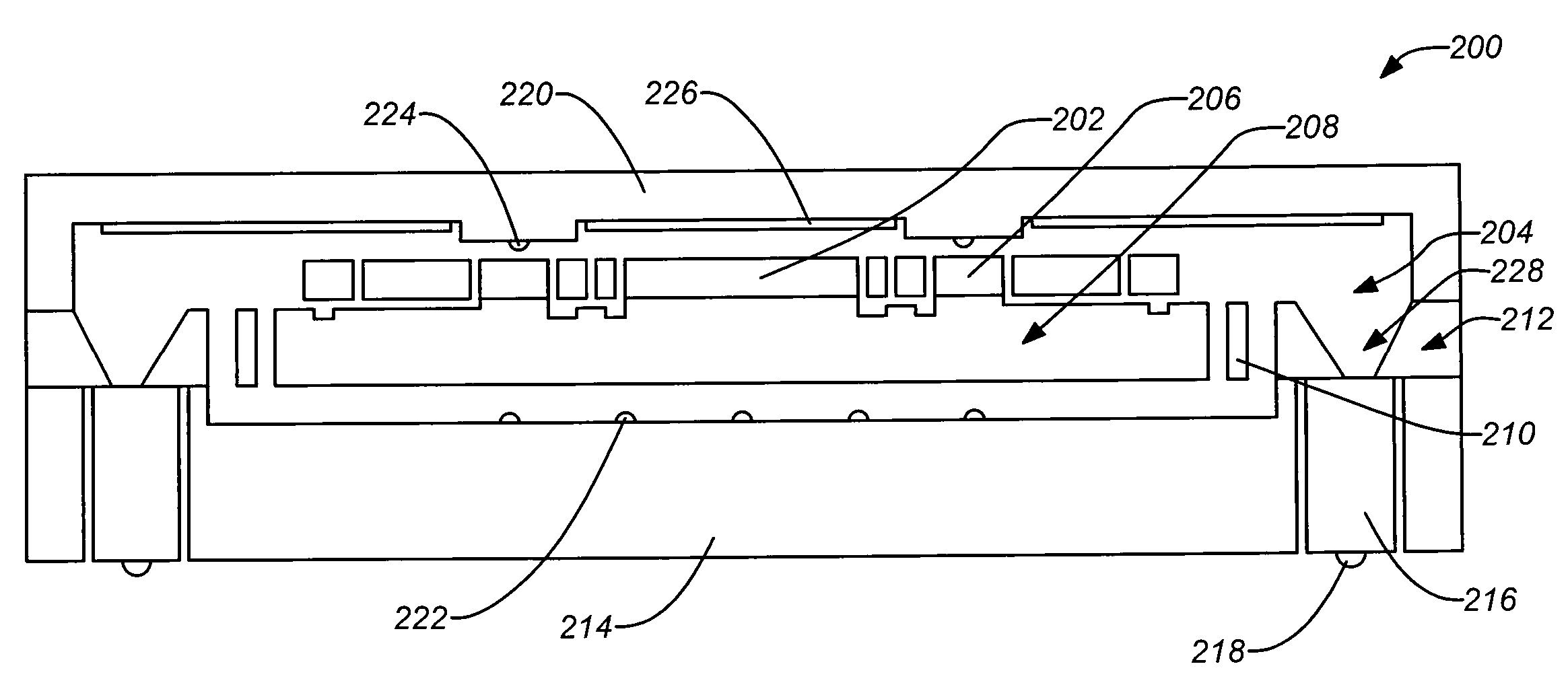

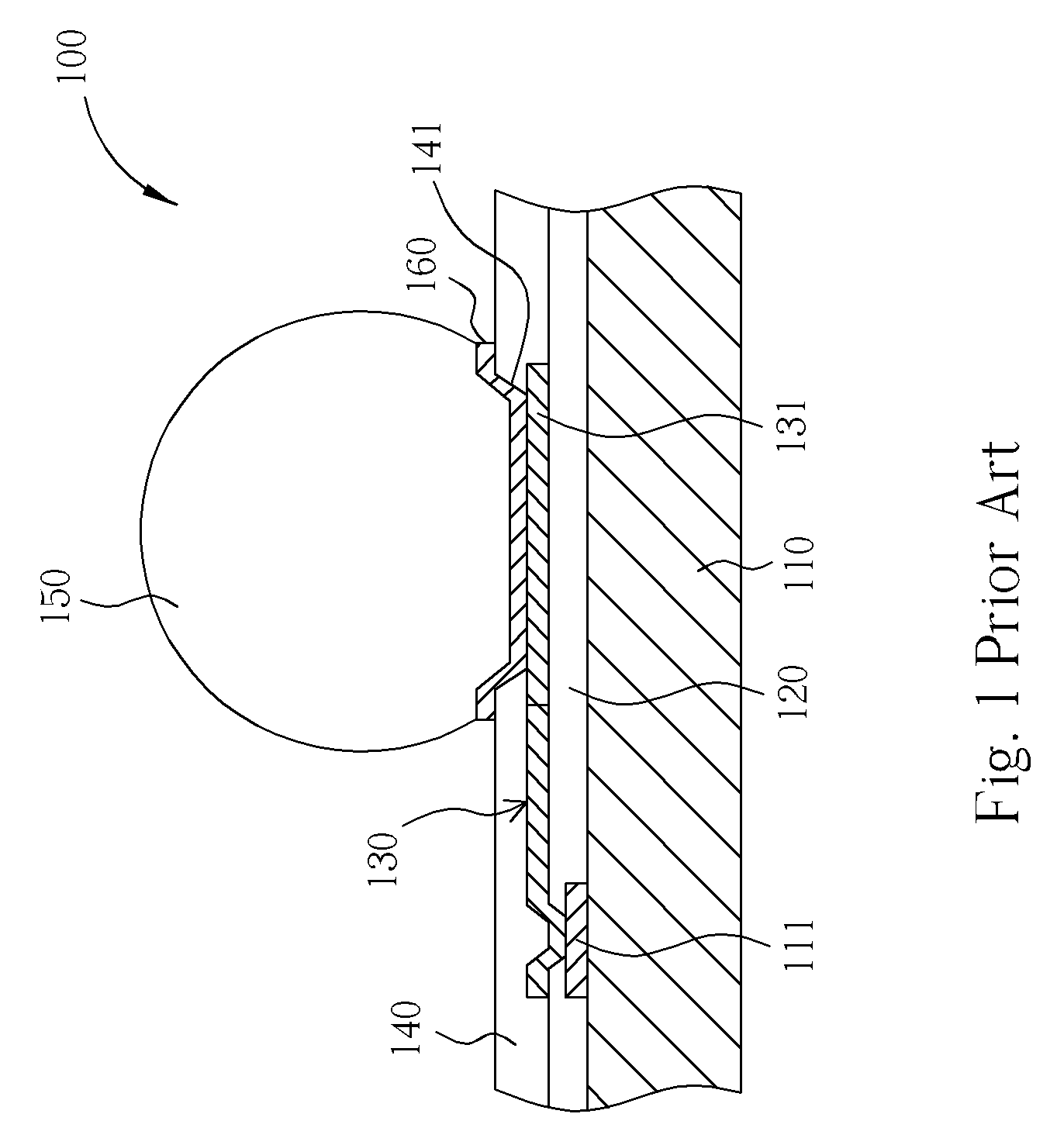

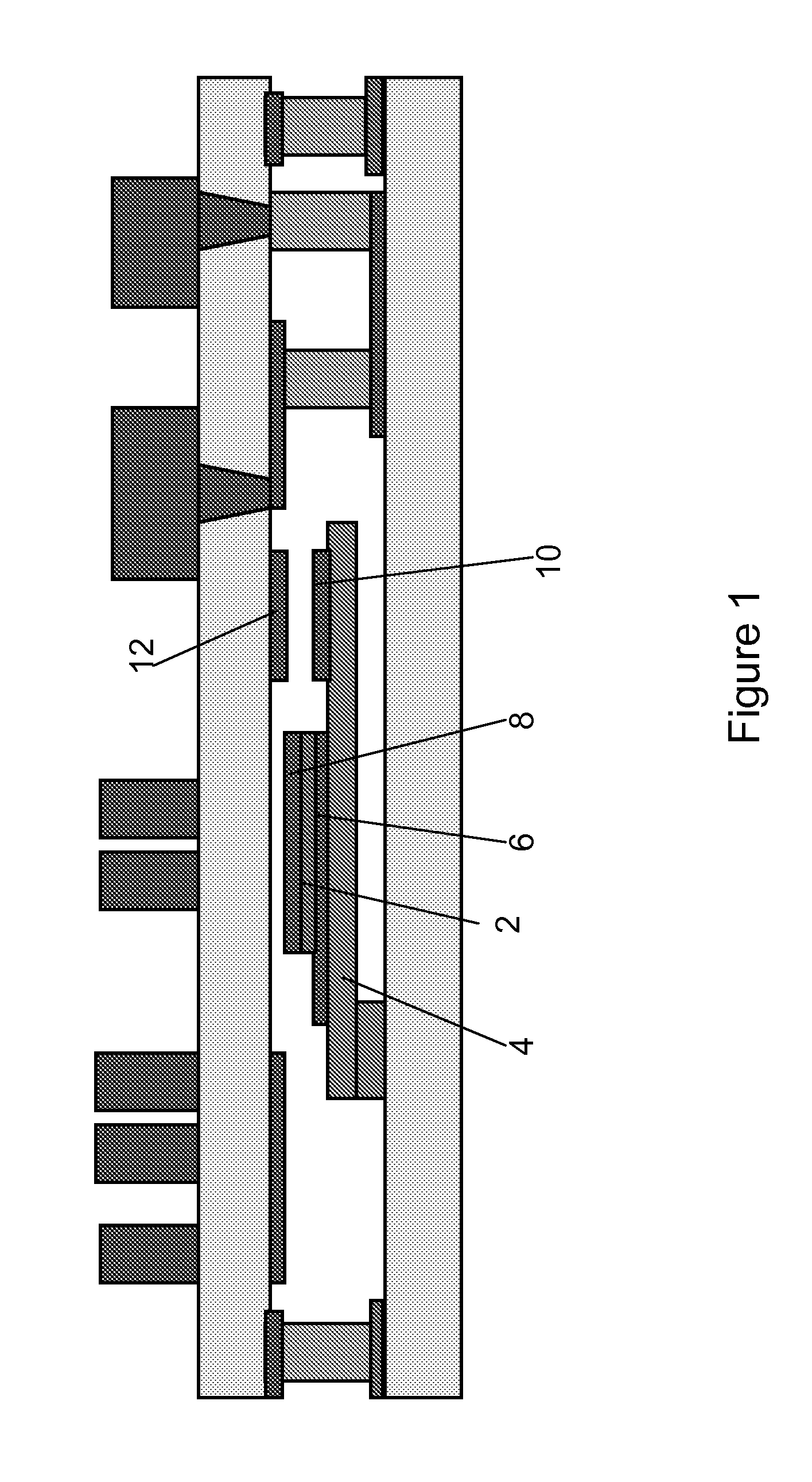

Environmentally robust disc resonator gyroscope

ActiveUS20100251818A1Reduce sensitivityImprove reliabilityAcceleration measurement using interia forcesLaminationManufacturing cost reductionGyroscope

Micromachined disc resonator gyroscopes (DRGs) are disclosed designed to be virtually immune to external temperature and stress effects. The DRG is a vibratory gyroscope that measures angular rate which is designed to have reduced sensitivity to external thermal and mechanical stress. The DRG features an integrated isolator that may be fabricated on the same wafer as the electrode wafer forming a plurality of integrated isolator beams. In addition, the DRG may include a wafer level hermetical vacuum seal, flip chip ball grid array (BGA), and vertical electrical feedthrough to improve reliability and to reduce manufacturing cost. An additional carrier layer may be used with shock stops, vertical electrical feedthrough, and the flip chip BGA. A pyrex or quartz cap with embedded getter and shock stops can be employed.

Owner:THE BOEING CO

Methodology for layout-based modulation and optimization of nitride liner stress effect in compact models

ActiveUS7337420B2CAD circuit designSoftware simulation/interpretation/emulationModel systemStress variation

System and method for compact model algorithms to accurately account for effects of layout-induced changes in nitride liner stress in semiconductor devices. The layout-sensitive compact model algorithms account for the impact of large layout variation on circuits by implementing algorithms for obtaining the correct stress response approximations and layout extraction algorithms for obtaining the correct geometric parameters that drive the stress response. In particular, these algorithms include specific information from search “buckets” that are directionally-oriented and include directionally-specific distance measurements for analyzing in detail the specific shape neighborhood of the semiconductor device. The algorithms are additionally adapted to enable the modeling and stress impact determination of a device having single stress liner film and dual-stress liners (two different liner films that abut at an interface).

Owner:GLOBALFOUNDRIES U S INC

Organic light-emitting display panel and organic light-emitting display device

InactiveCN106848107AIncreased stress surfacePrevent extensionSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

The invention discloses an organic light-emitting display panel and an organic light-emitting display device. The organic light-emitting display panel comprises a substrate, an organic light-emitting structure and at least one barricade, wherein the barricades surround the organic light-emitting structure and point to the edge along the geometric center of the substrate, and the barricades are sequentially arranged. In the direction perpendicular to the stacking direction of the substrate and the organic light-emitting structure, the barricade closest to the edge of the substrate is the first barricade, and the first barricade is formed by connecting one or more nonlinear sub barricades, so that the stress area of the first barricade is increased, the effect of dispersing stress generated on the edge when the organic light-emitting display device is bent is achieved, and then the phenomenon that cracks generated by the stress effect stretches to a display region is avoided.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

Dual damascene bond pad structure for lowering stress and allowing circuitry under pads

InactiveUS6838769B1Semiconductor/solid-state device detailsSolid-state devicesStress effectsBiomedical engineering

A bond pad is located over active circuitry formed within an integrated circuit device. A barrier film forms the bottom surface of the upper portion of a bond pad opening which also includes vias extending through the bottom surface to form a dual damascene structure. The bond pad is resistant to stress effects such as cracking, which can be produced when bonding an external wire to the bond pad, and therefore prevents leakage currents between the bond pads and the underlying circuitry.

Owner:BELL SEMICON LLC

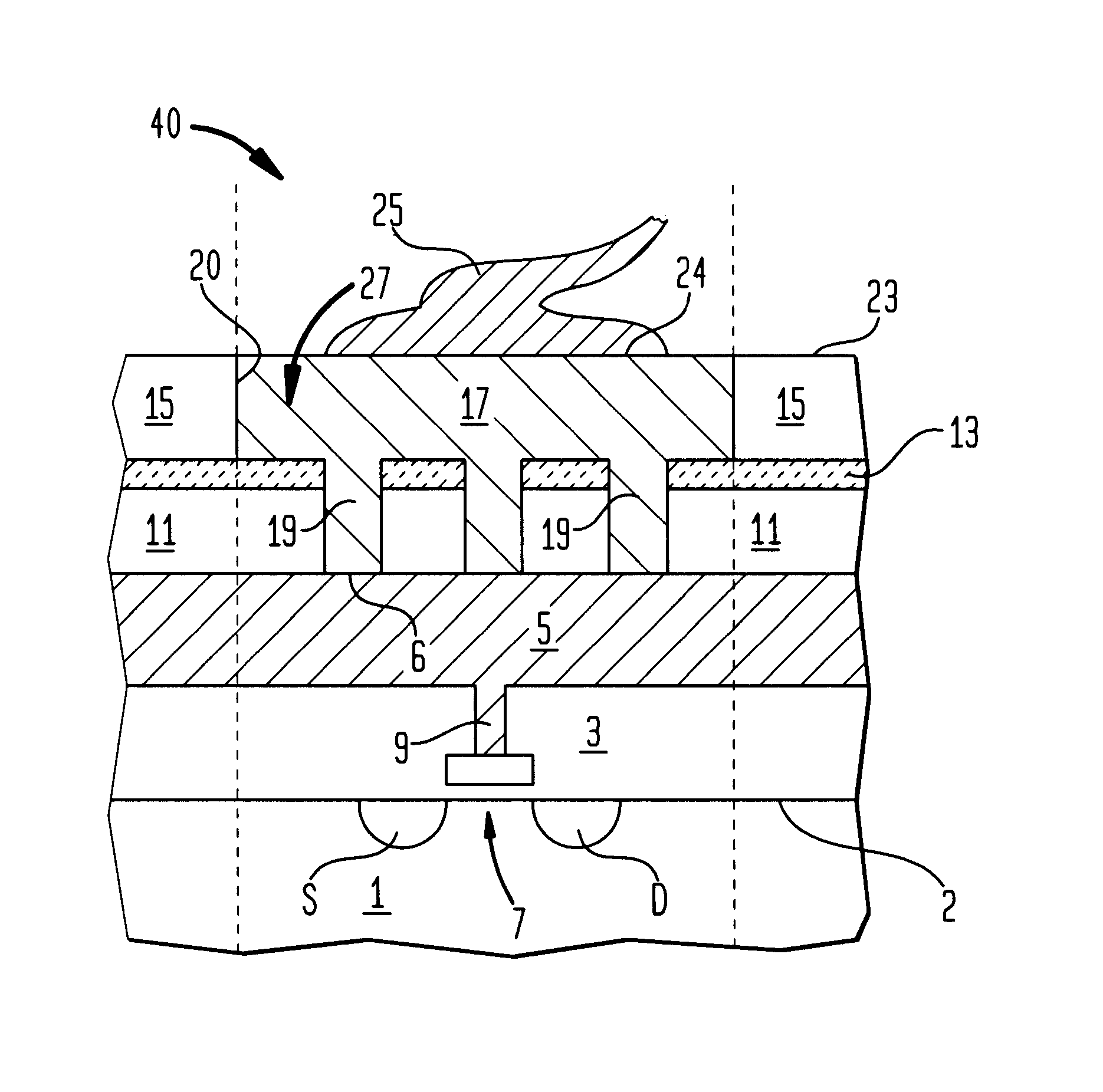

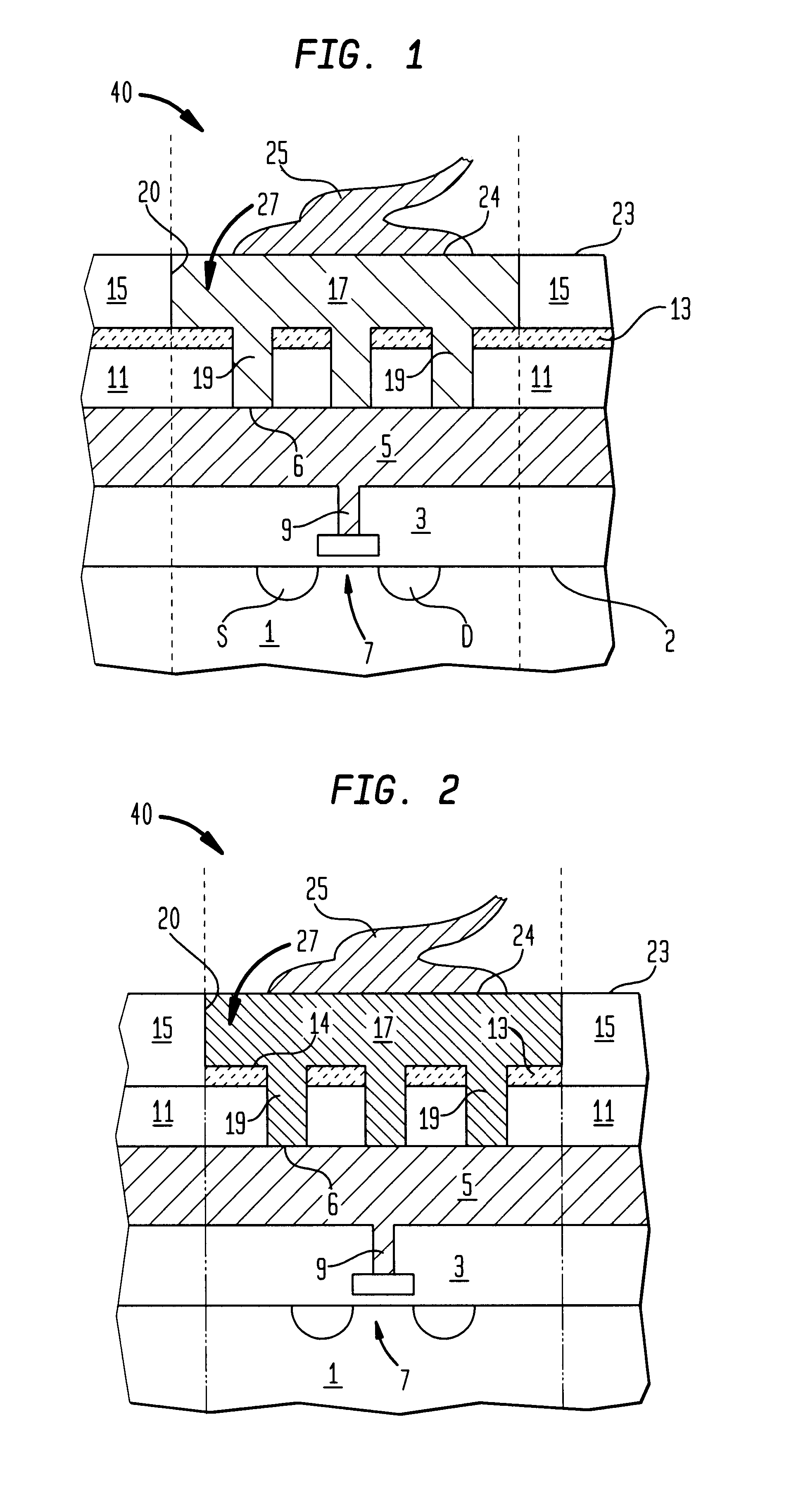

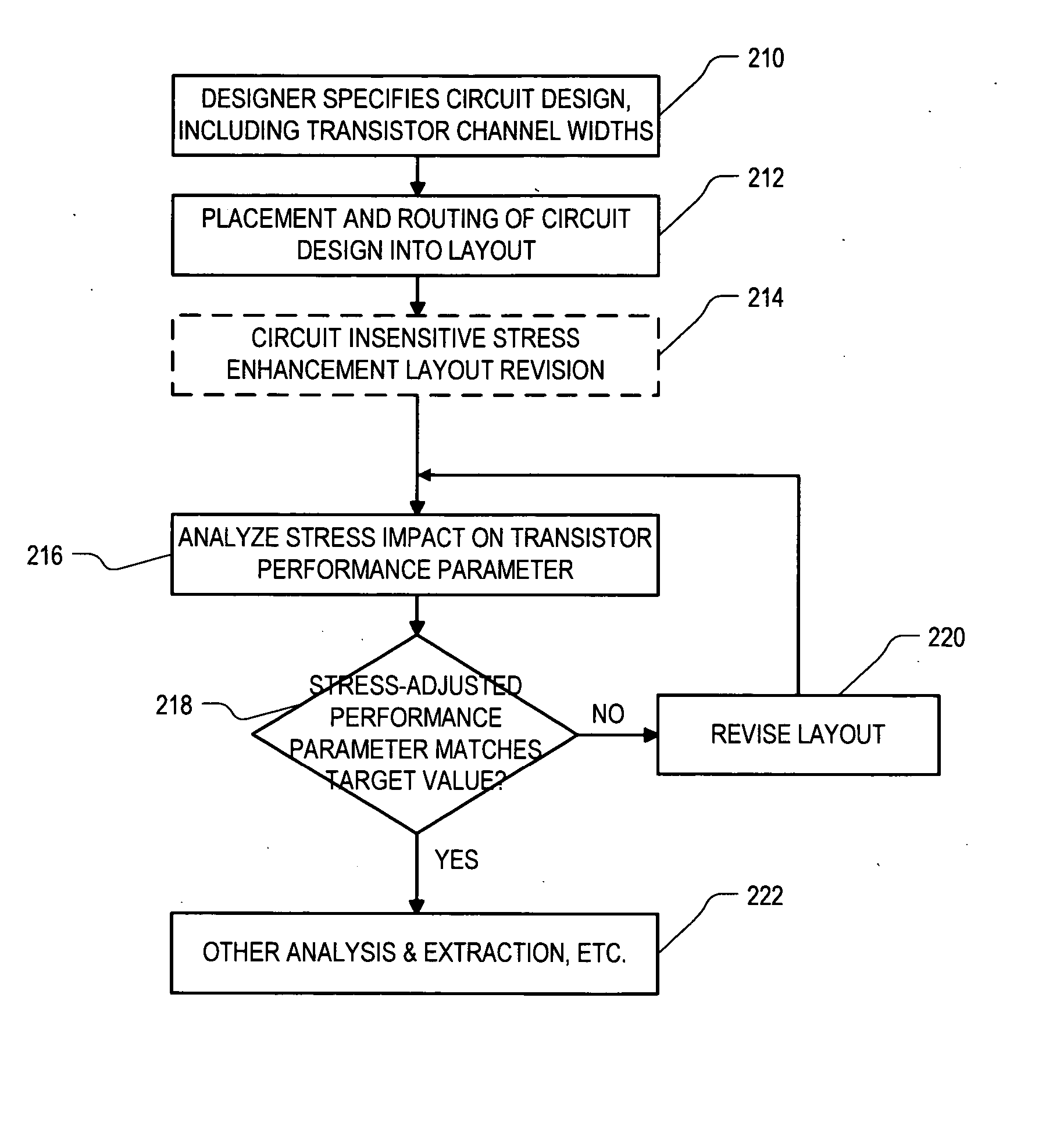

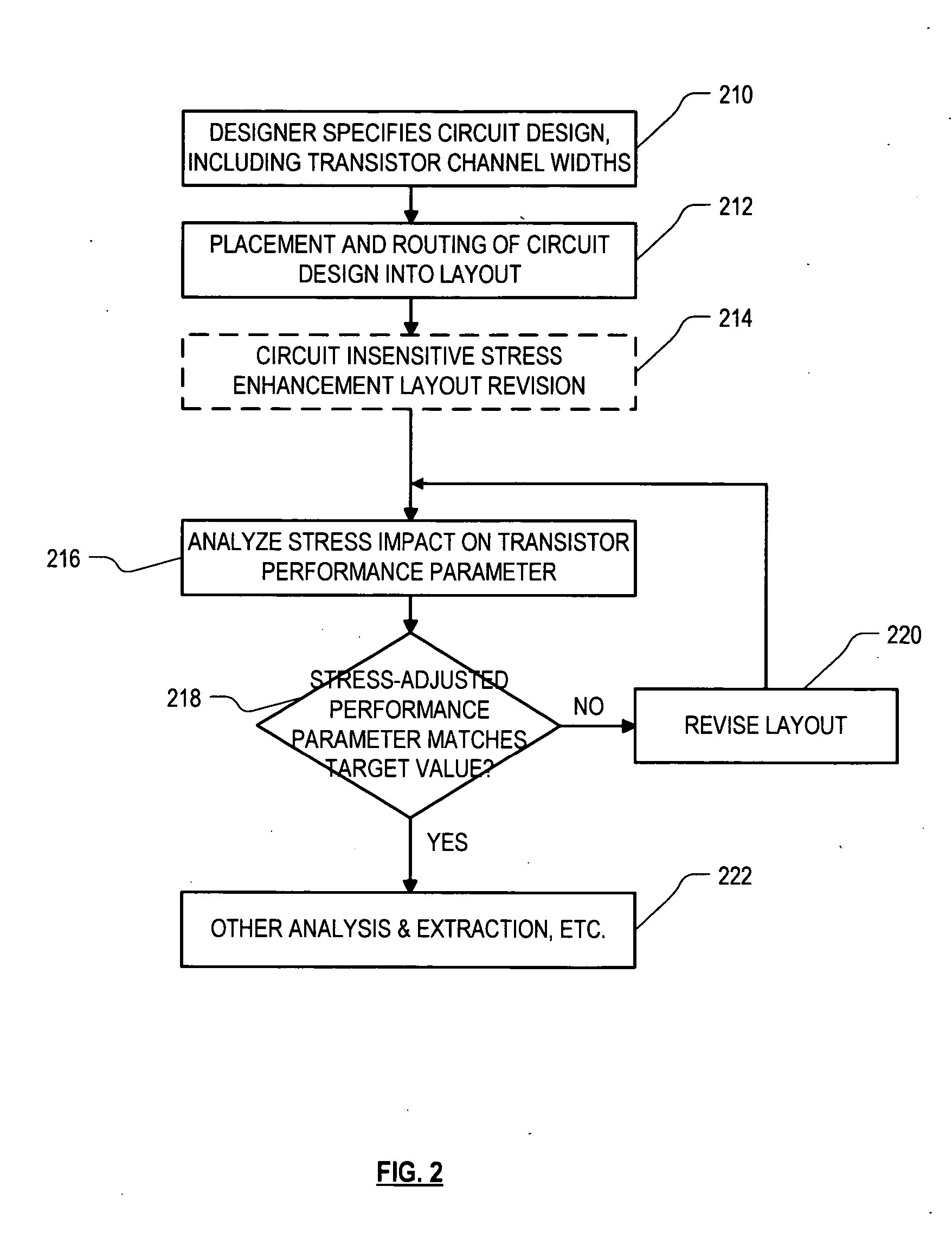

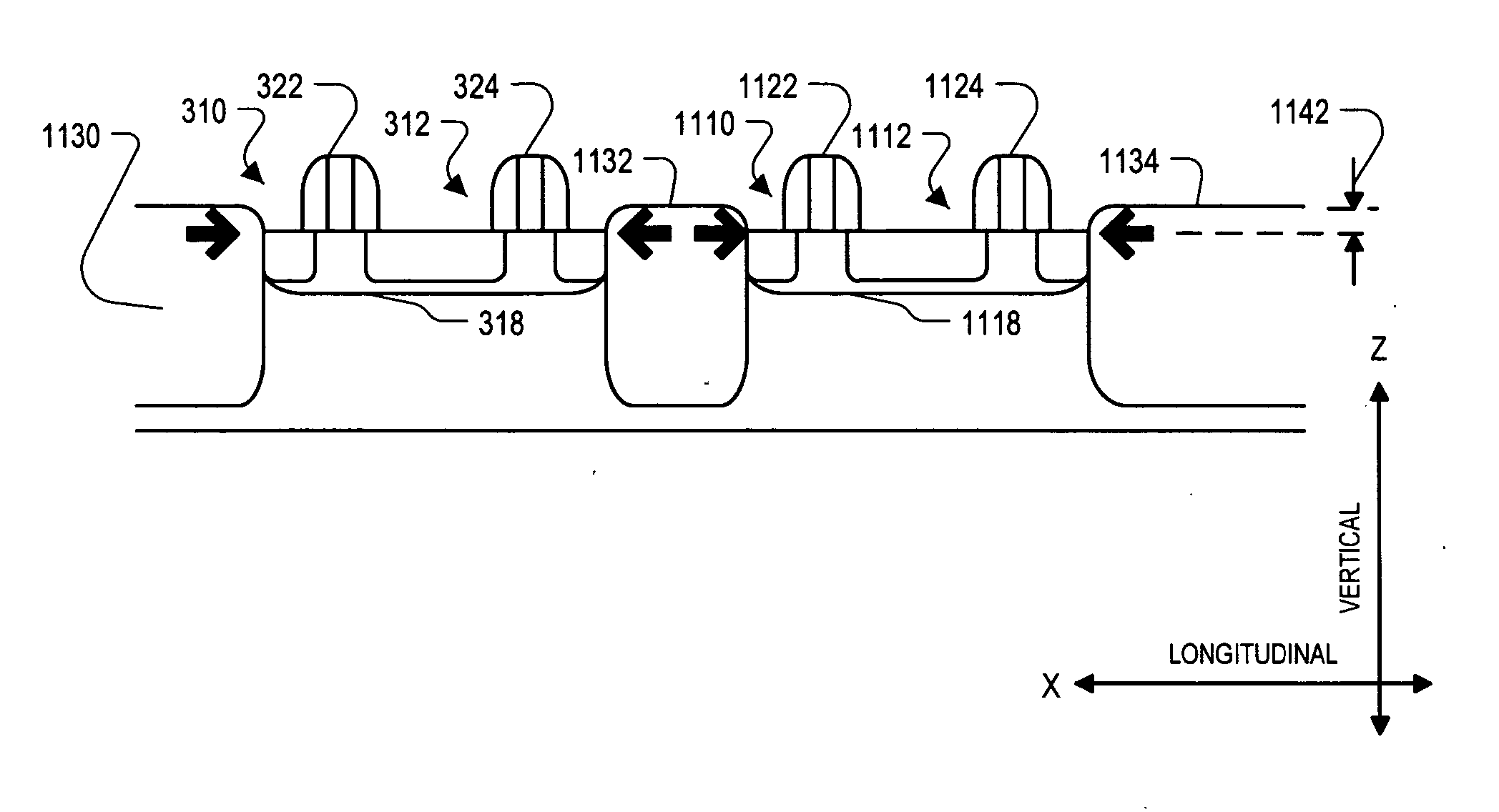

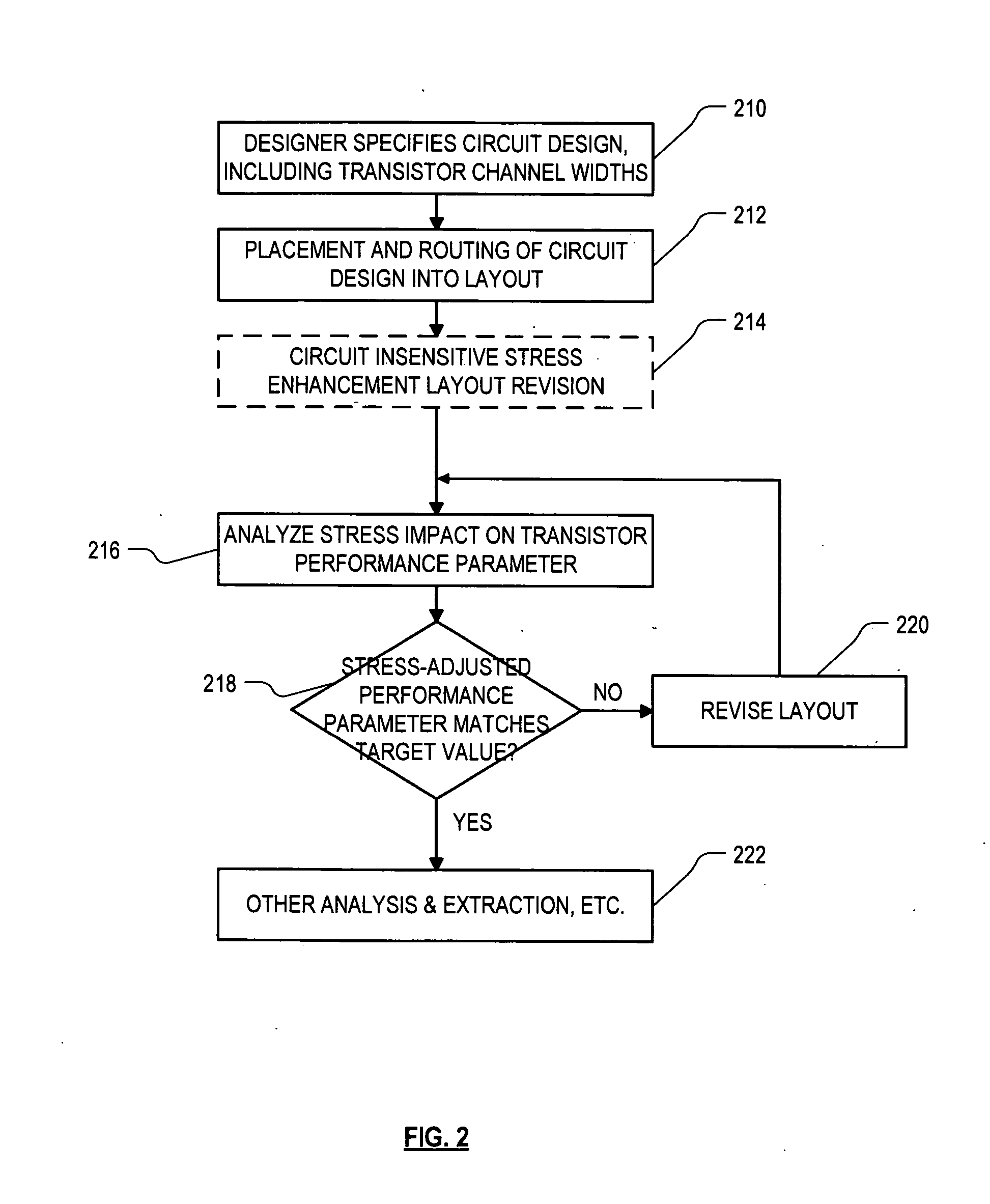

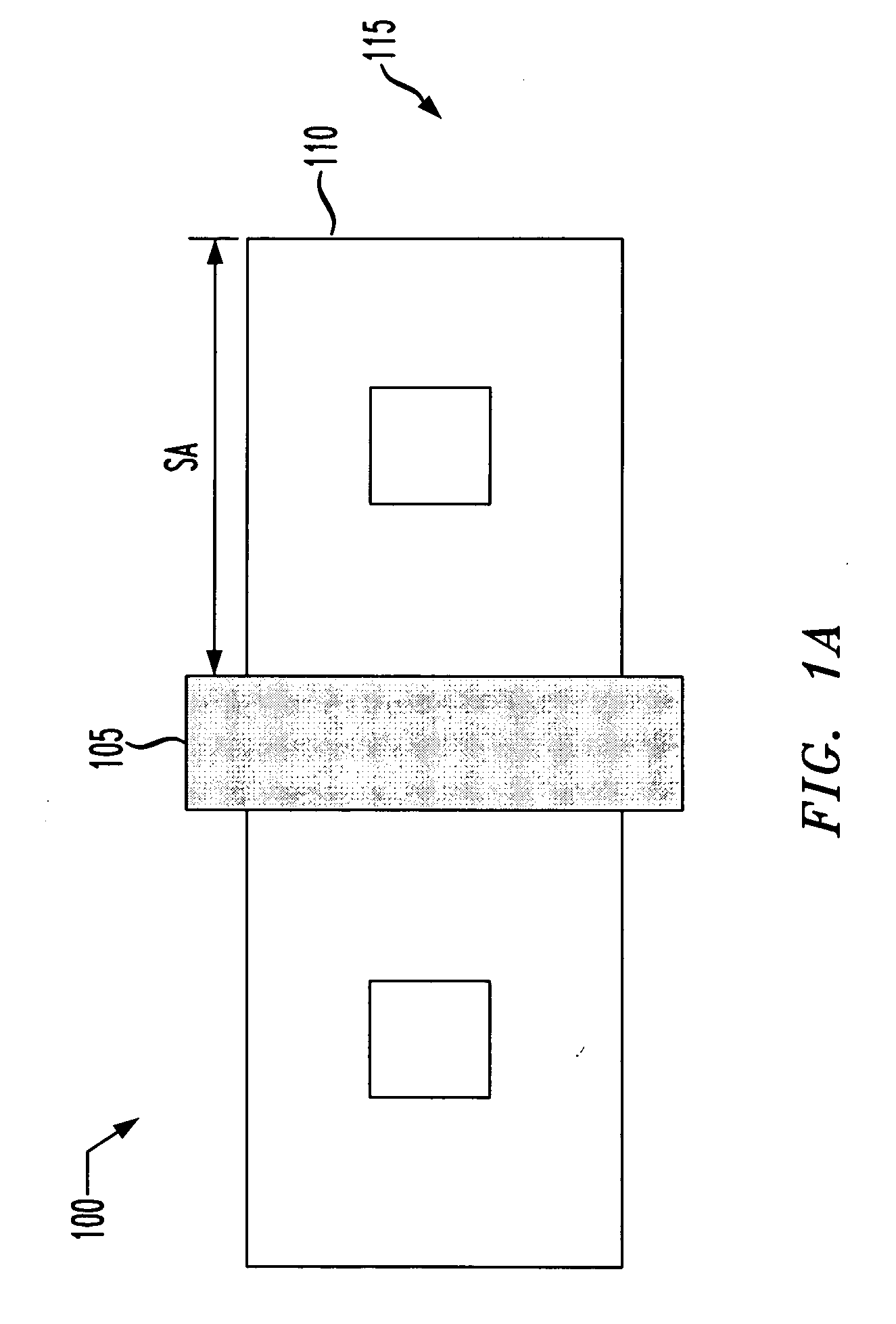

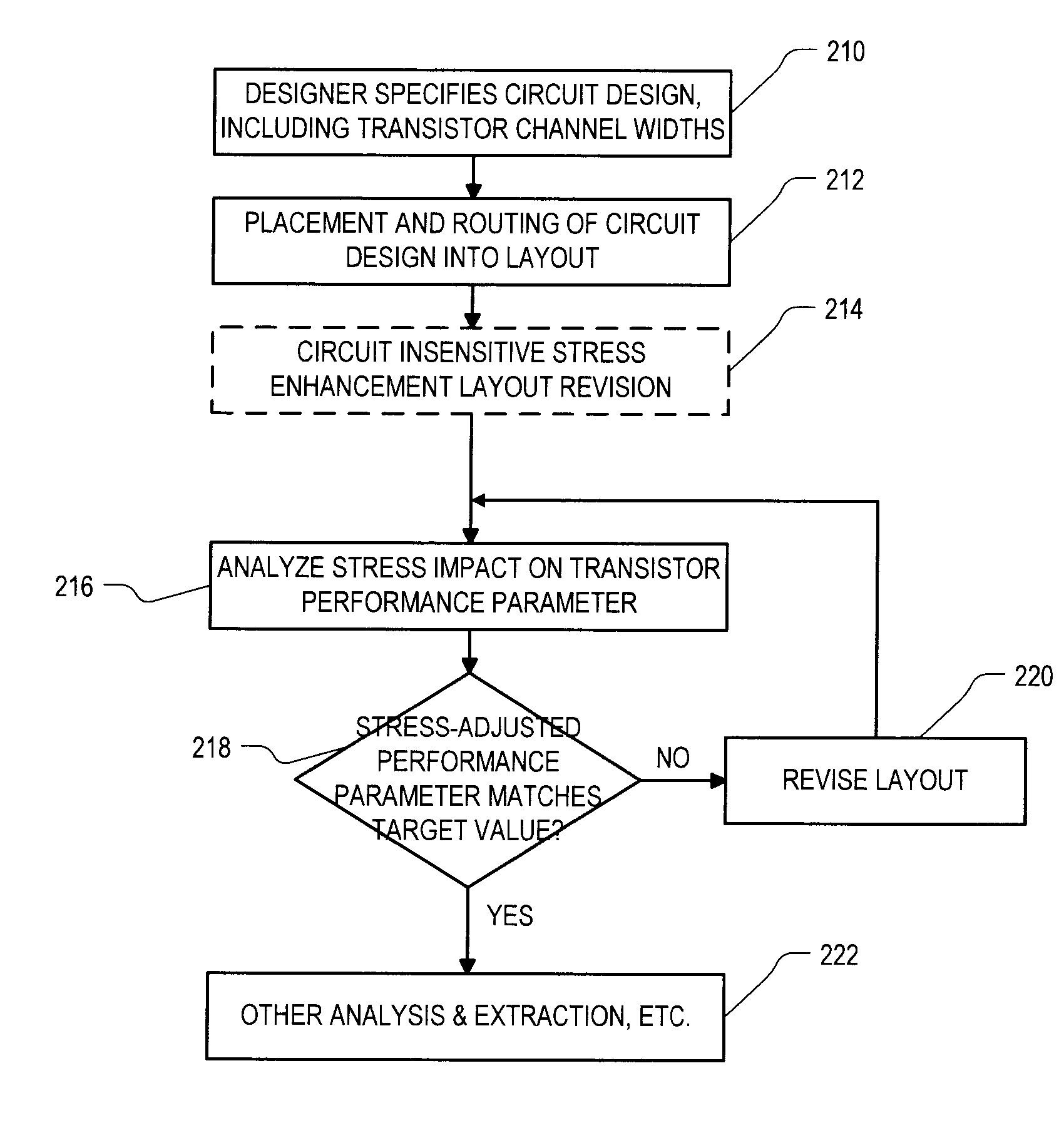

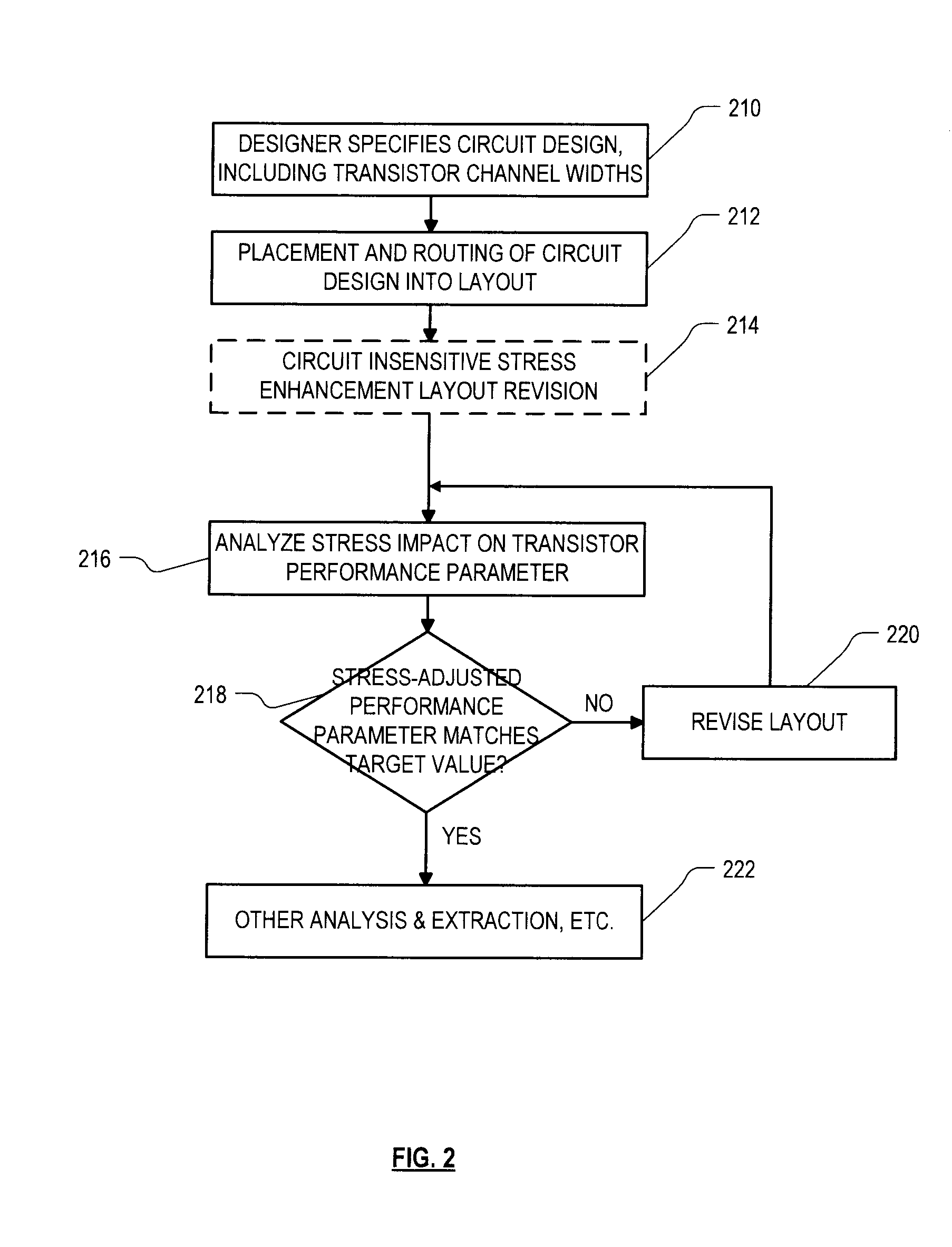

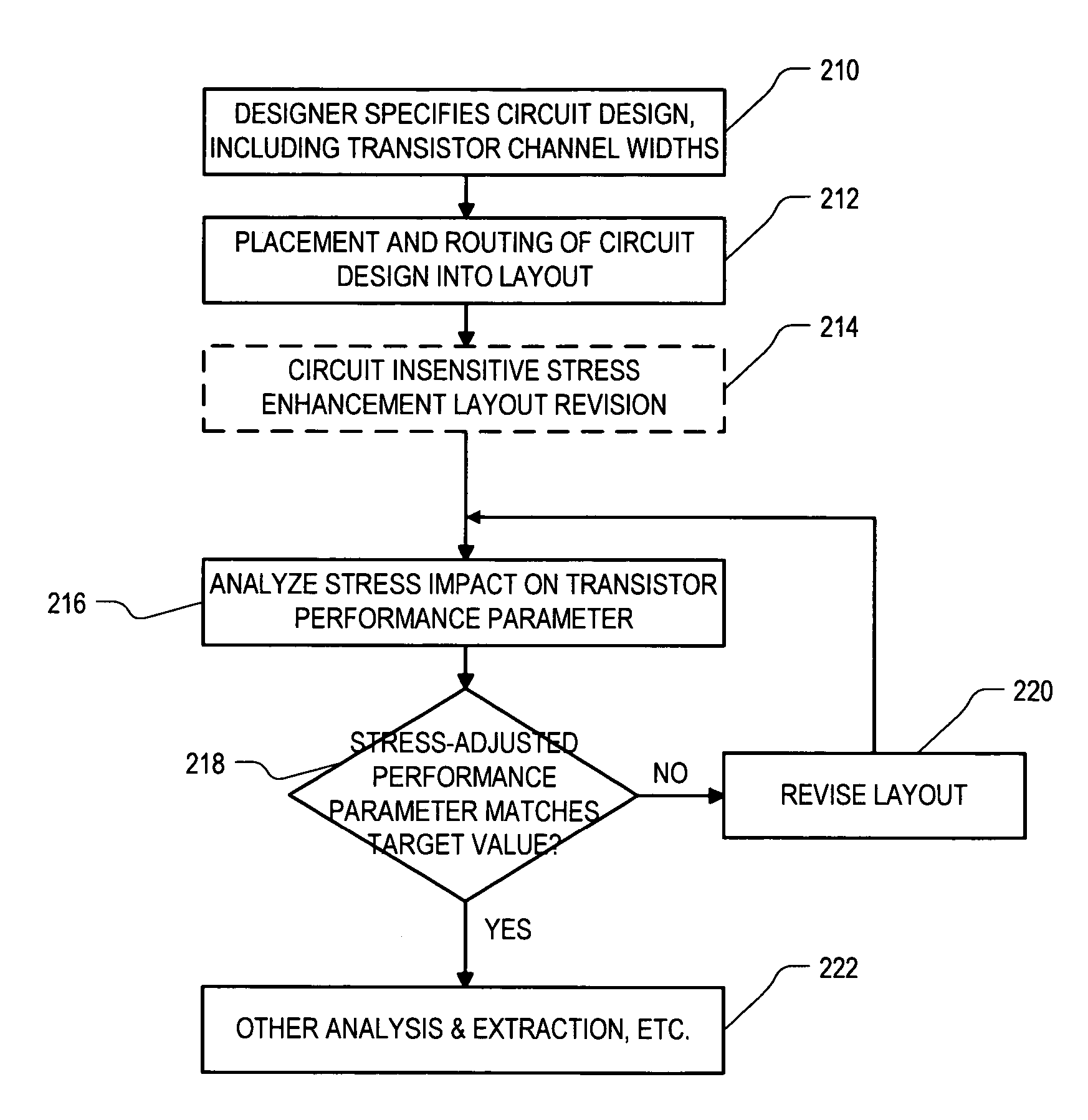

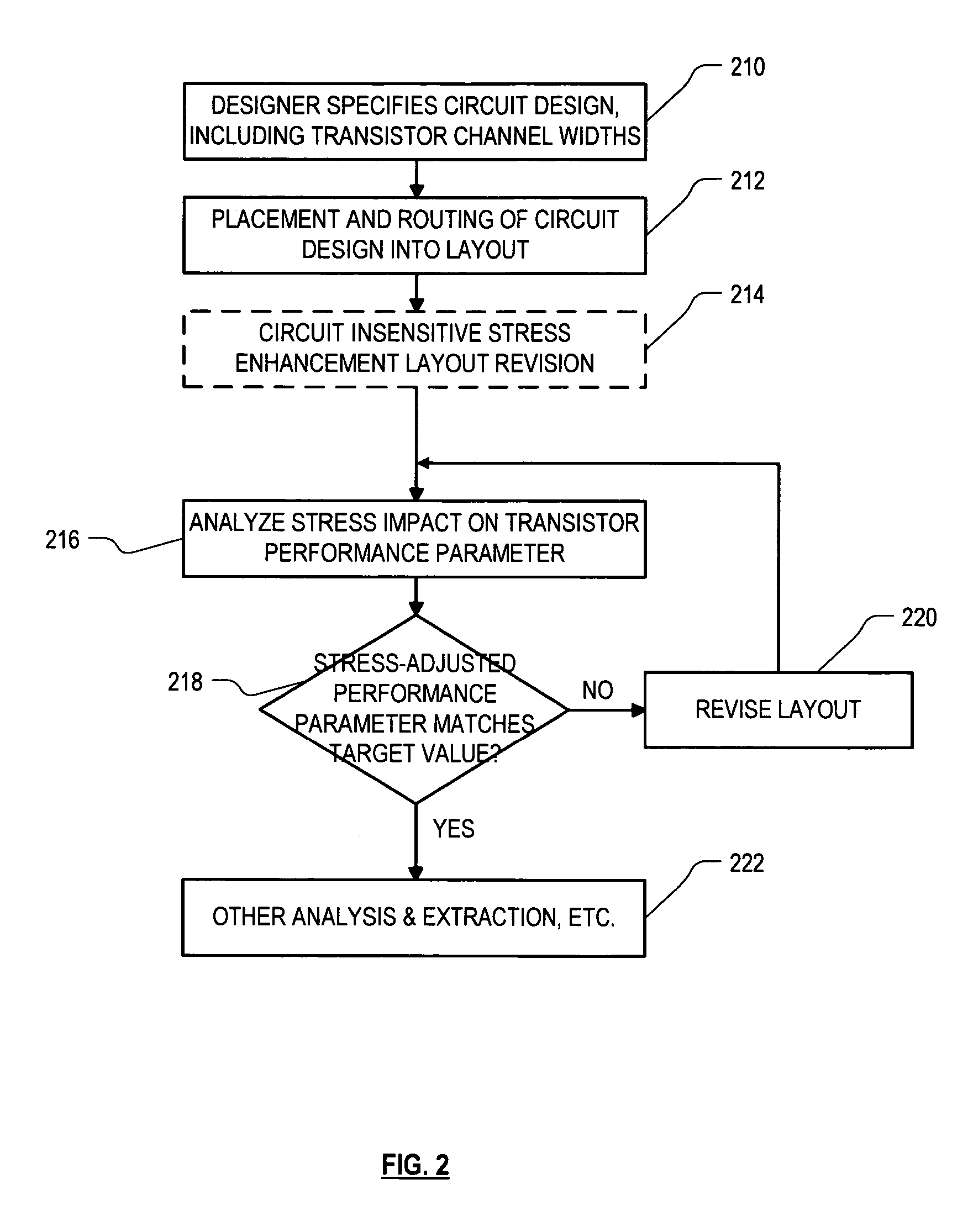

Stress-managed revision of integrated circuit layouts

ActiveUS20070204250A1Semiconductor/solid-state device manufacturingCAD circuit designTensile strainDiffusion

Roughly described, methods and systems for improving integrated circuit layouts and fabrication processes in order to better account for stress effects. Dummy features can be added to a layout either in order to improve uniformity, or to relax known undesirable stress, or to introduce known desirable stress. The dummy features can include dummy diffusion regions added to relax stress, and dummy trenches added either to relax or enhance stress. A trench can relax stress by filling it with a stress-neutral material or a tensile strained material. A trench can increase stress by filling it with a compressive strained material. Preferably dummy diffusion regions and stress relaxation trenches are disposed longitudinally to at least the channel regions of N-channel transistors, and transversely to at least the channel regions of both N-channel and P-channel transistors. Preferably stress enhancement trenches are disposed longitudinally to at least the channel regions of P-channel transistors.

Owner:SYNOPSYS INC

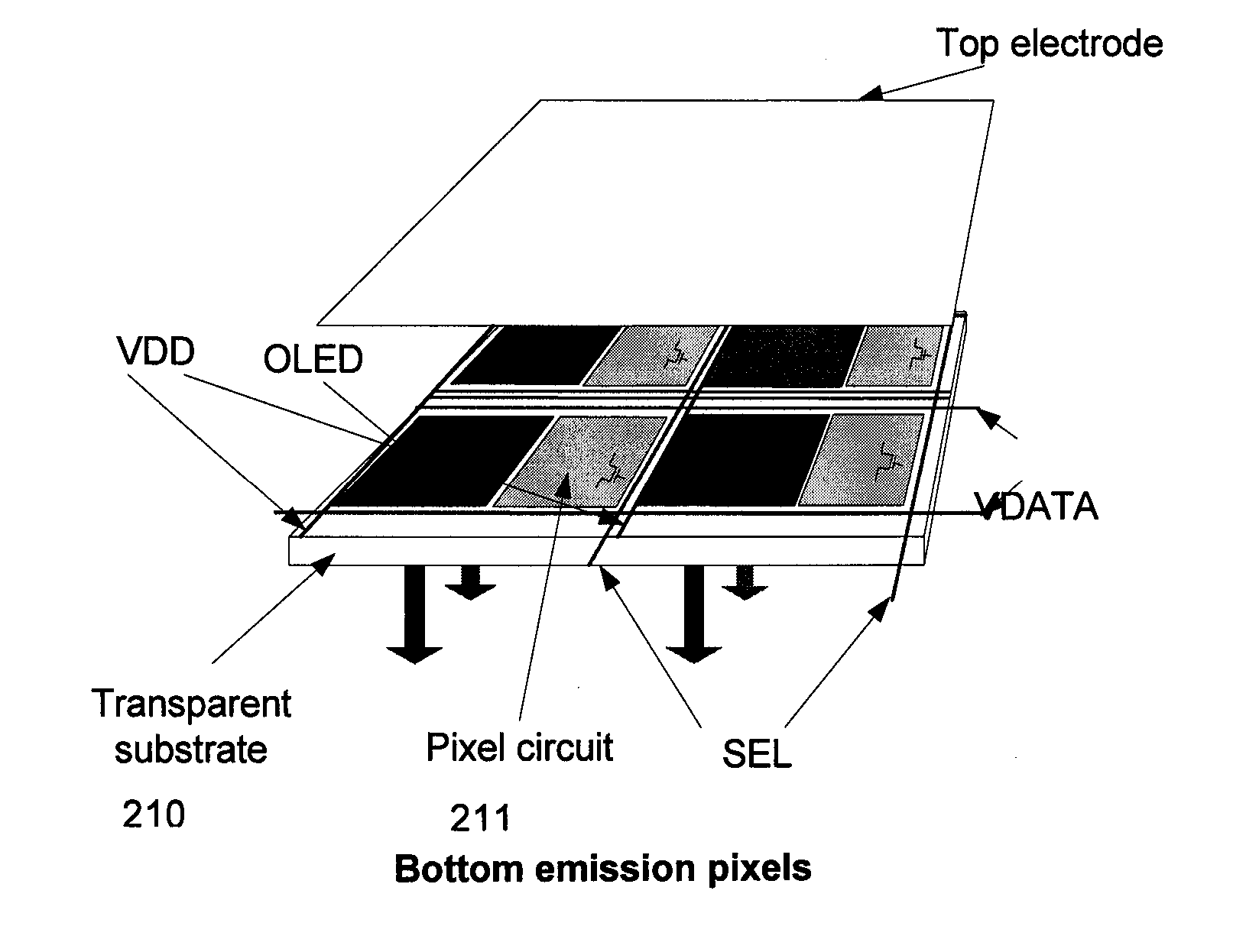

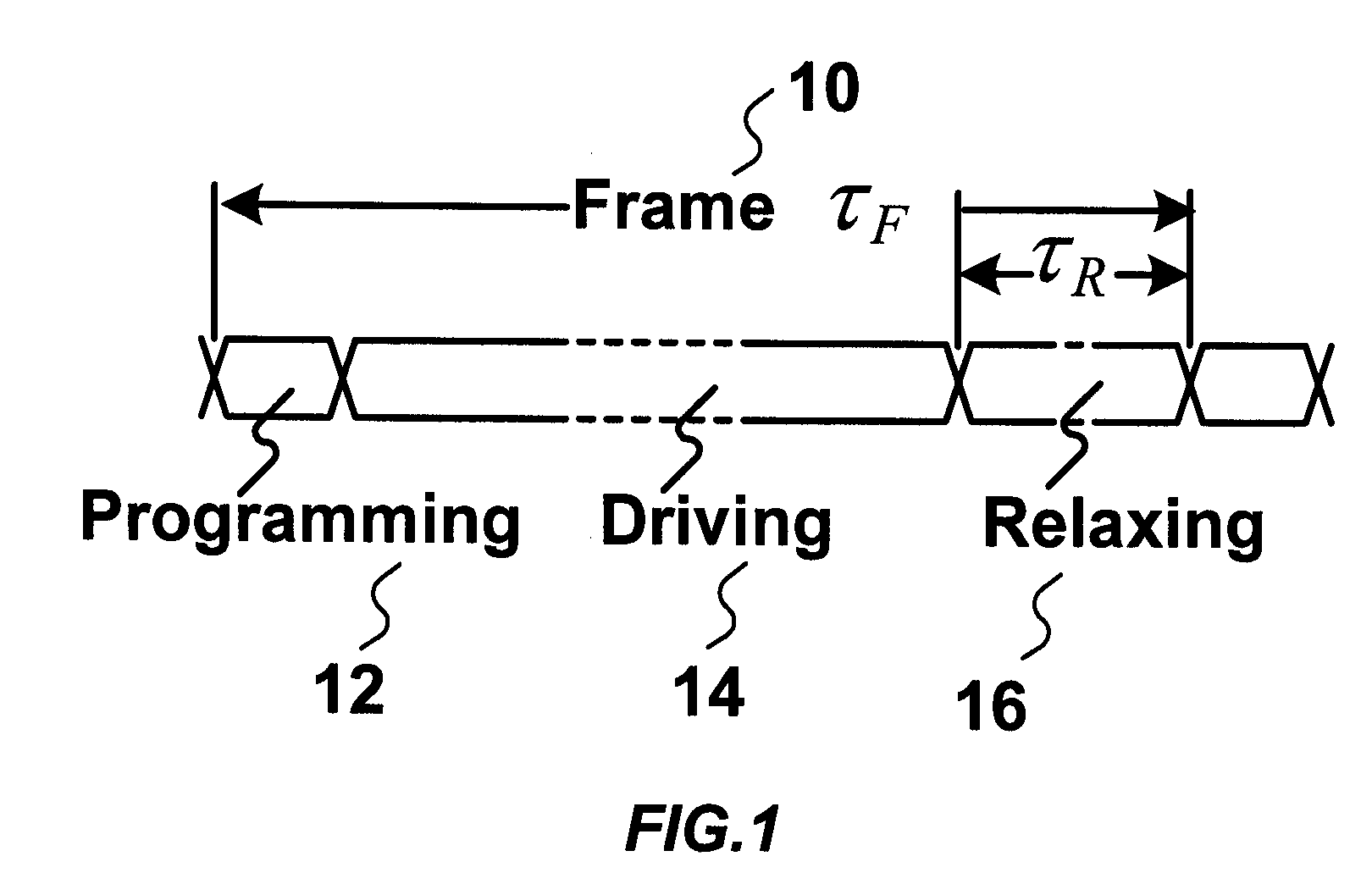

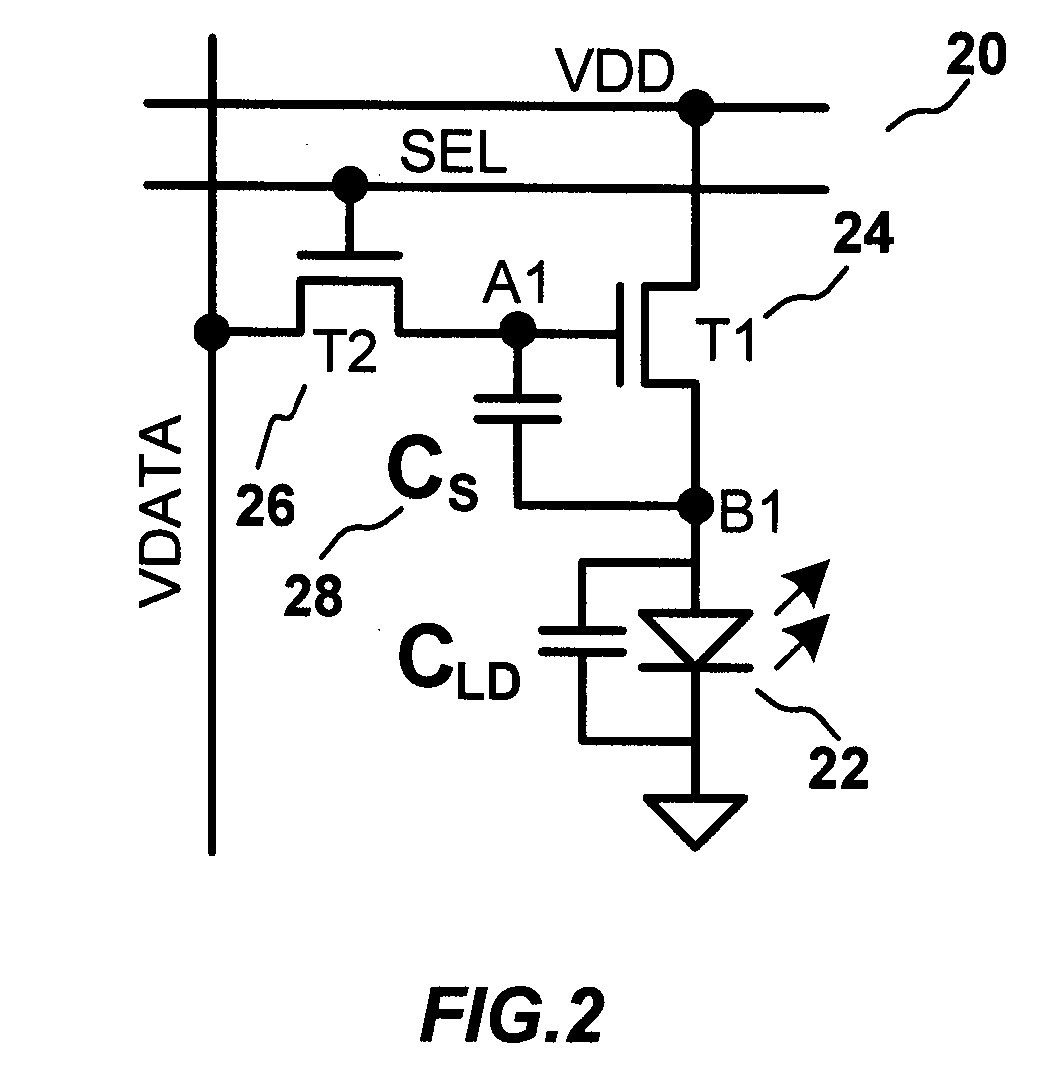

Stable driving scheme for active matrix displays

ActiveUS20070247398A1Cathode-ray tube indicatorsInput/output processes for data processingActive matrixLight emitting device

A method and system for operating a pixel array having at least one pixel circuit is provided. The method includes repeating an operation cycle defining a frame period for a pixel circuit, including at each frame period, programming the pixel circuit, driving the pixel circuit, and relaxing a stress effect on the pixel circuit, prior to a next frame period. The system includes a pixel array including a plurality of pixel circuits and a plurality of lines for operation of the plurality of pixel circuits. Each of the pixel circuits includes a light emitting device, a storage capacitor, and a drive circuit connected to the light emitting device and the storage capacitor. The system includes a drive for operating the plurality of lines to repeat an operation cycle having a frame period so that each of the operation cycle comprises a programming cycle, a driving cycle and a relaxing cycle for relaxing a stress on a pixel circuit, prior to a next frame period.

Owner:IGNIS INNOVATION

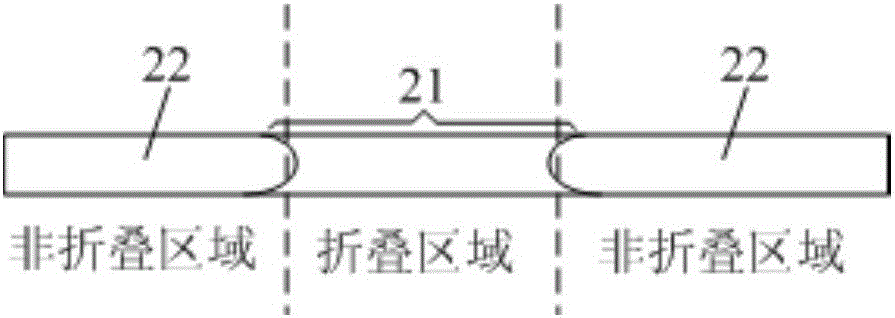

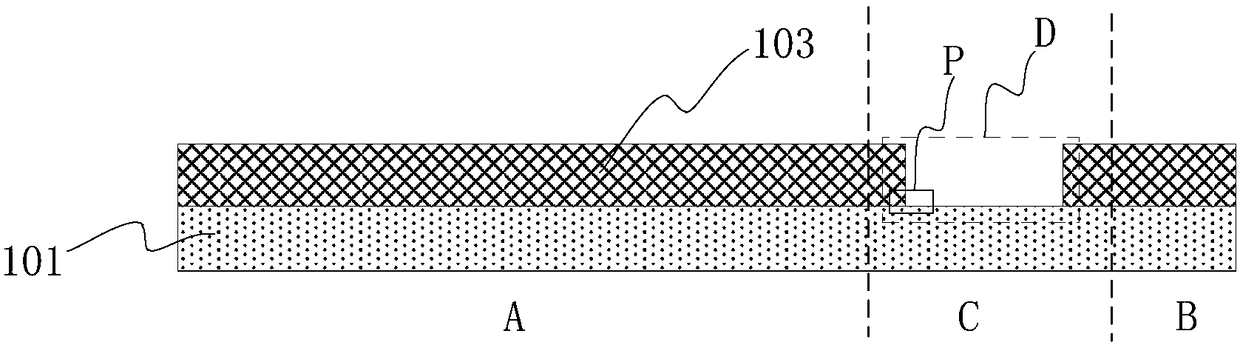

Display panel, bending method of display panel and display device

PendingCN108155219AAvoid disconnectionReduce stressSolid-state devicesPhotovoltaic energy generationDisplay deviceEngineering

The invention discloses a display panel, a bending method of the display panel and a display device. The display panel includes a display region, a wire arrangement region, and a bending region used for connecting the display region with the wire arrangement region. The bending region includes a first edge and second edges, the first edge refers to the edge on which the bending region is connectedwith the display region or the wire arrangement region, and the second edges refer to the edges, besides the first edge, of the bending region; at least one second edge includes inflection points, and the second edges are concaved toward the inside of the bending region at the positions of the inflection points. According to the display panel, at least one second edge of the bending region includes the inflection points, the second edges are concaved toward the inside of the bending region at the positions of the inflection points, thus the width, at the inflection points, of the bending region is thus very small, the inflection points easily become bending centers, and the situation that the bending centers are formed on the border of a protection layer is avoided; the stress effect applied by the protection layer on metal wires in the bending region in the bending process is reduced, and thus breaking of the metal wires in the bending region can be avoided.

Owner:BOE TECH GRP CO LTD +1

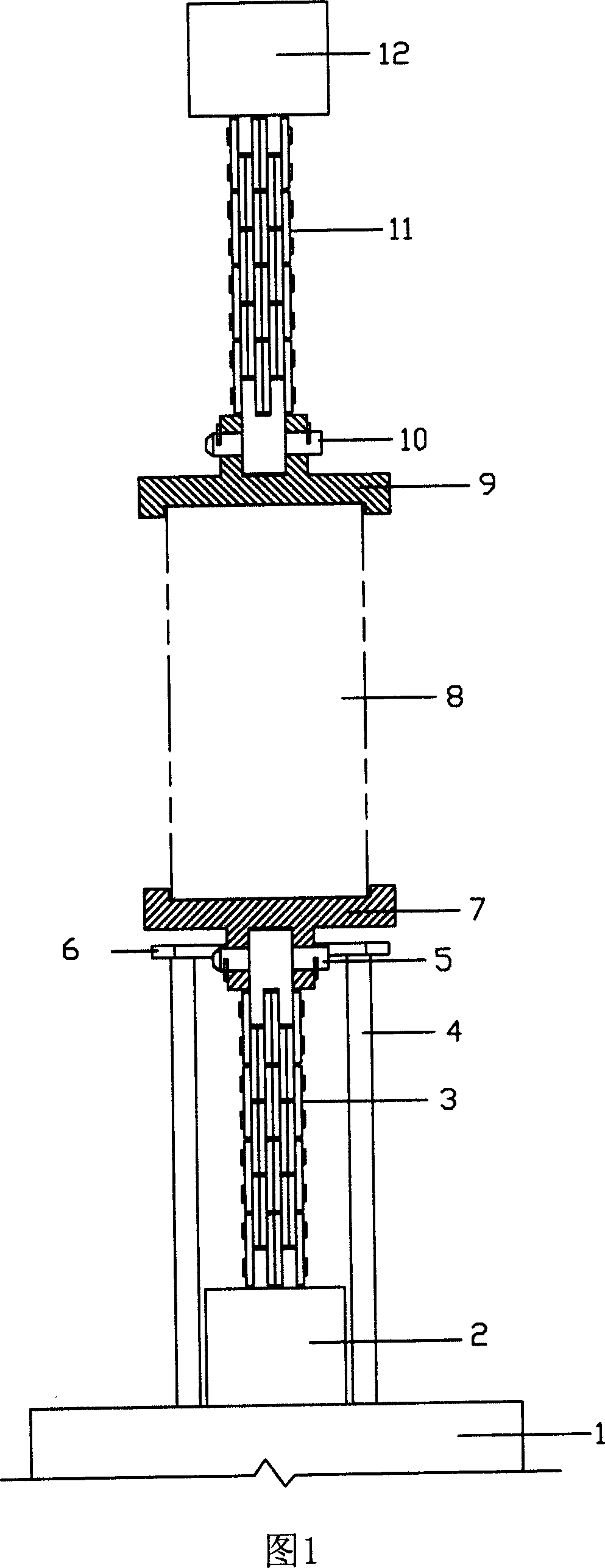

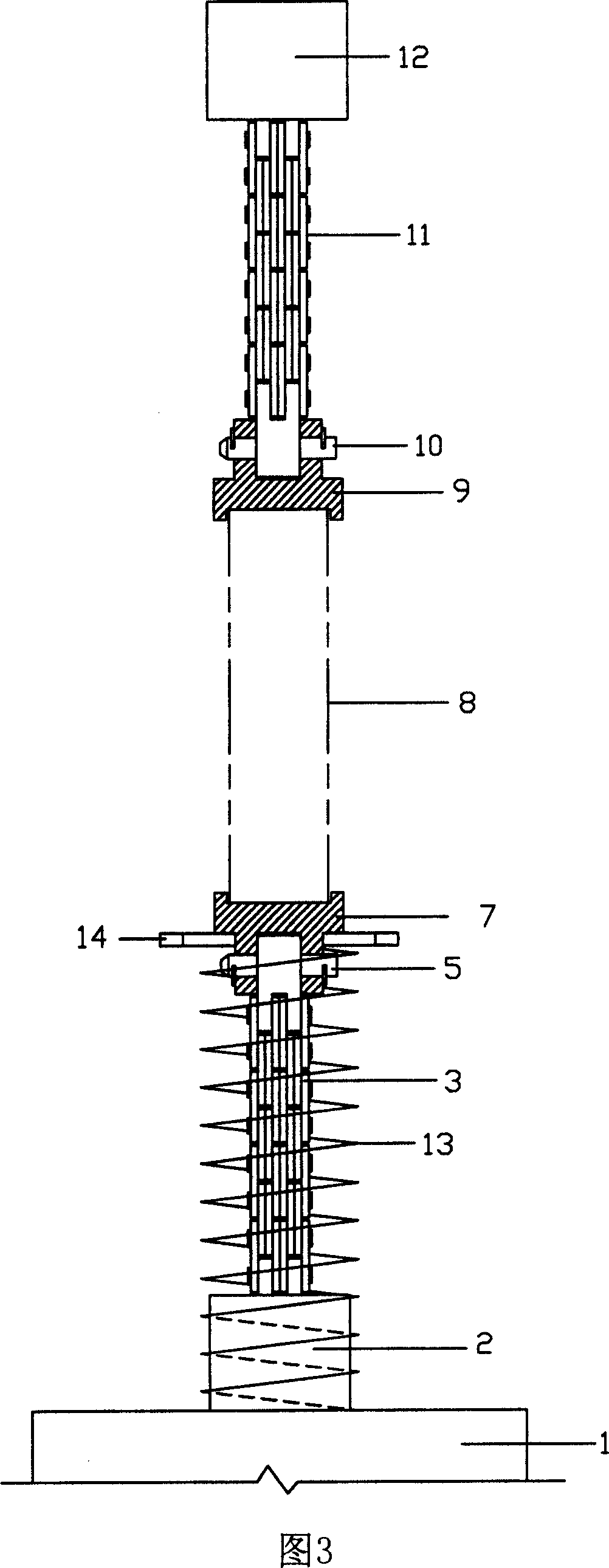

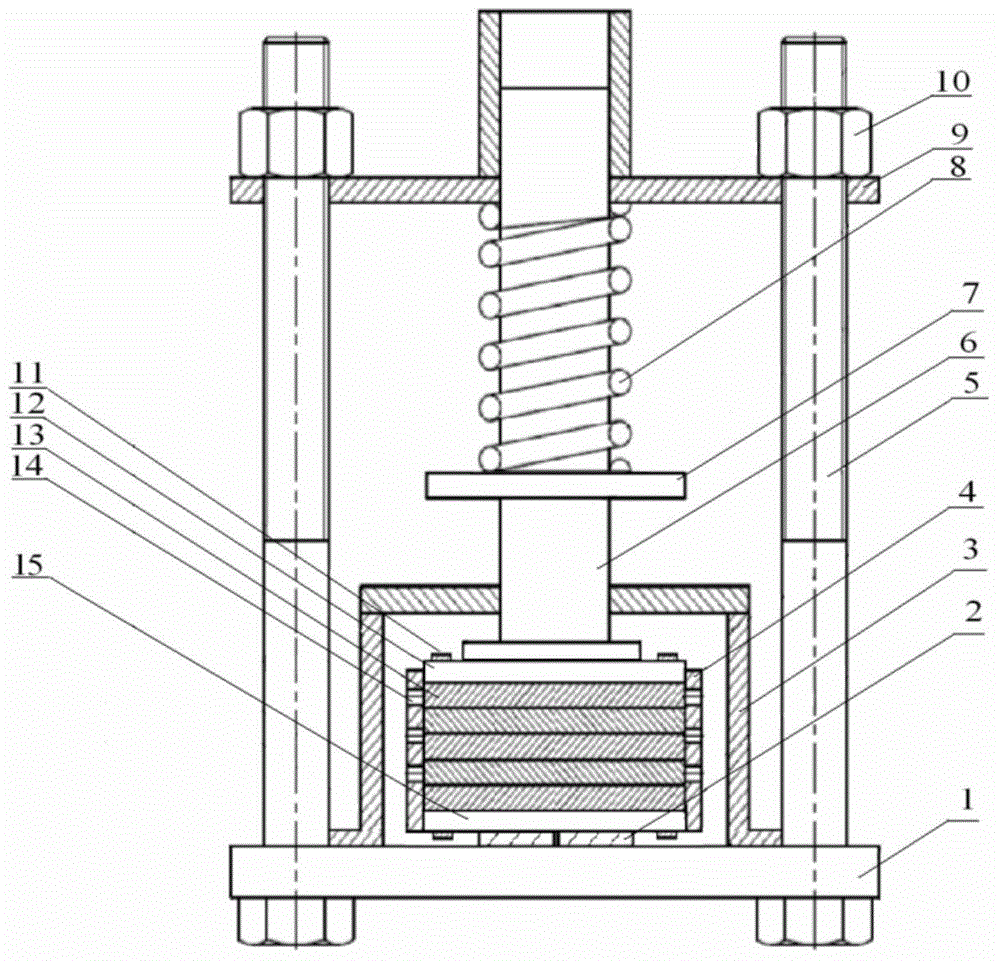

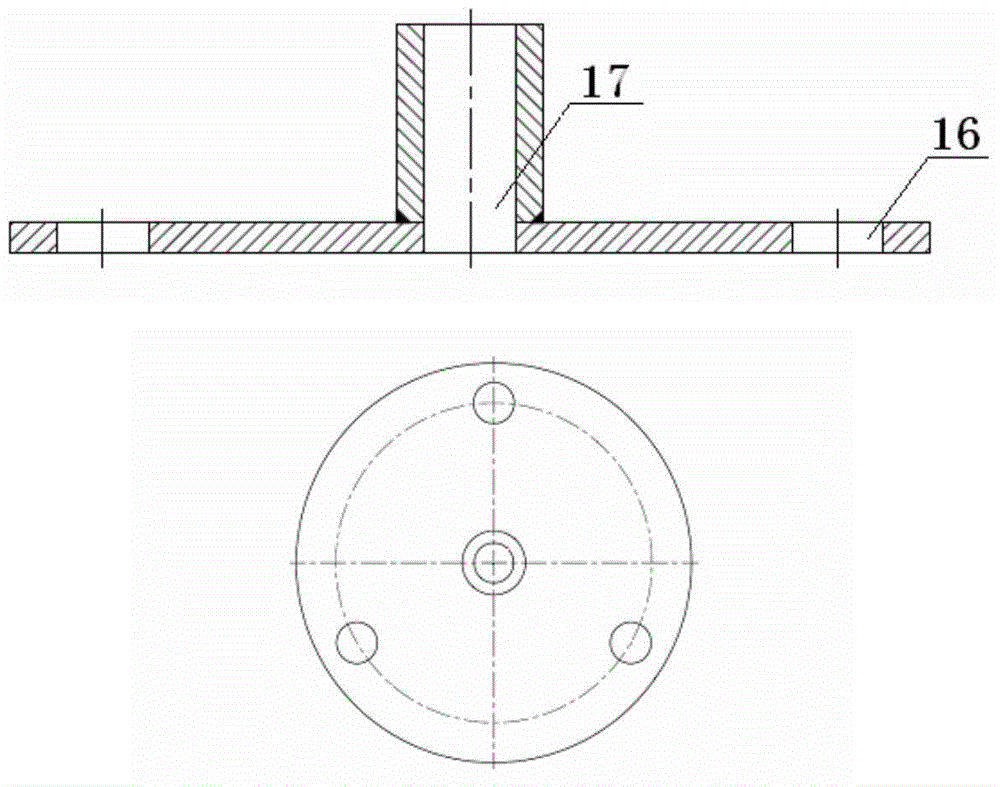

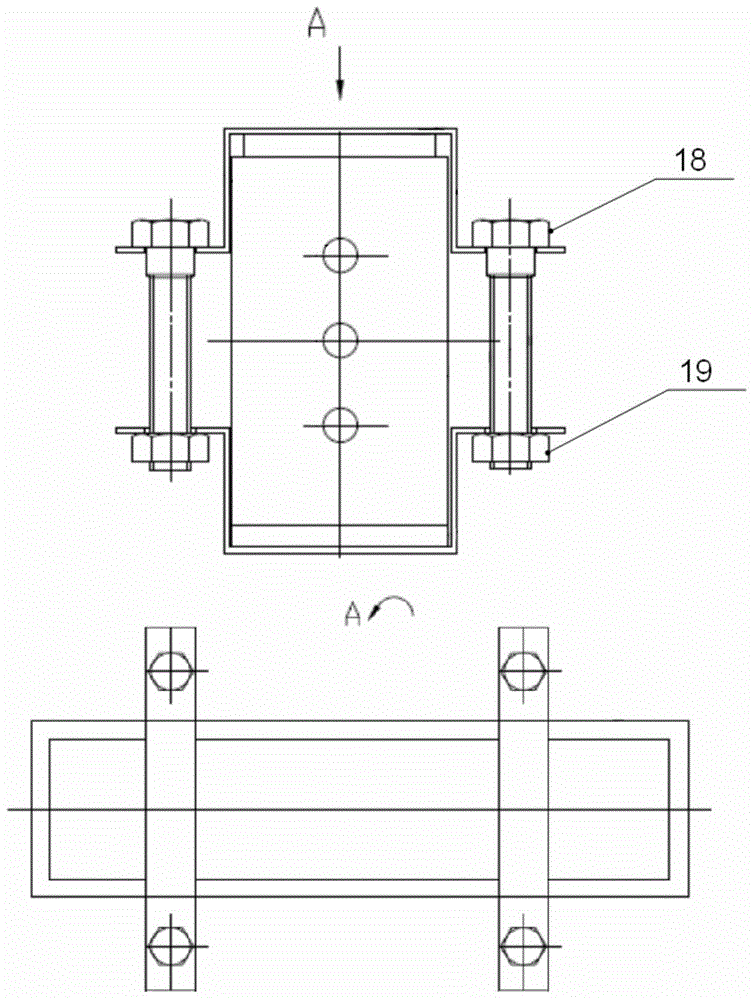

Spring thrust down clamp of direct tensile test

InactiveCN1952643AAvoid sudden destructionSimple structureMaterial strength using tensile/compressive forcesEngineeringTensile testing

Owner:SICHUAN UNIV

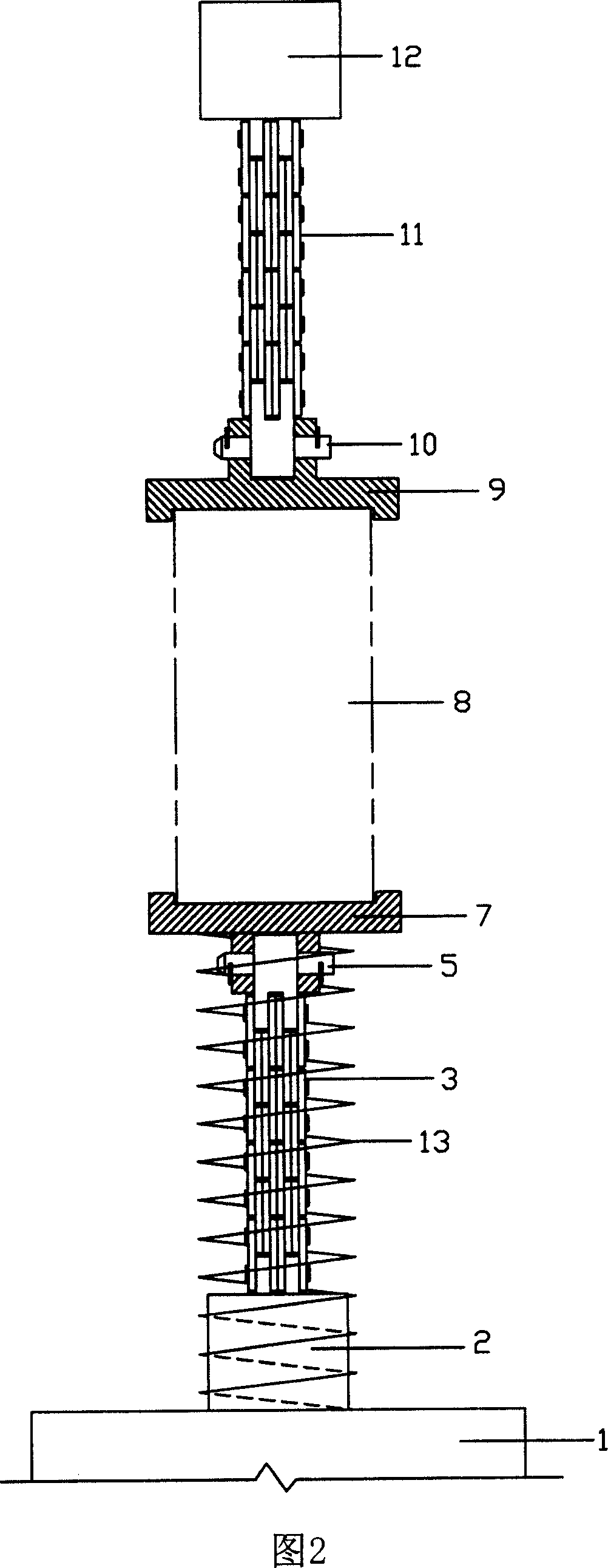

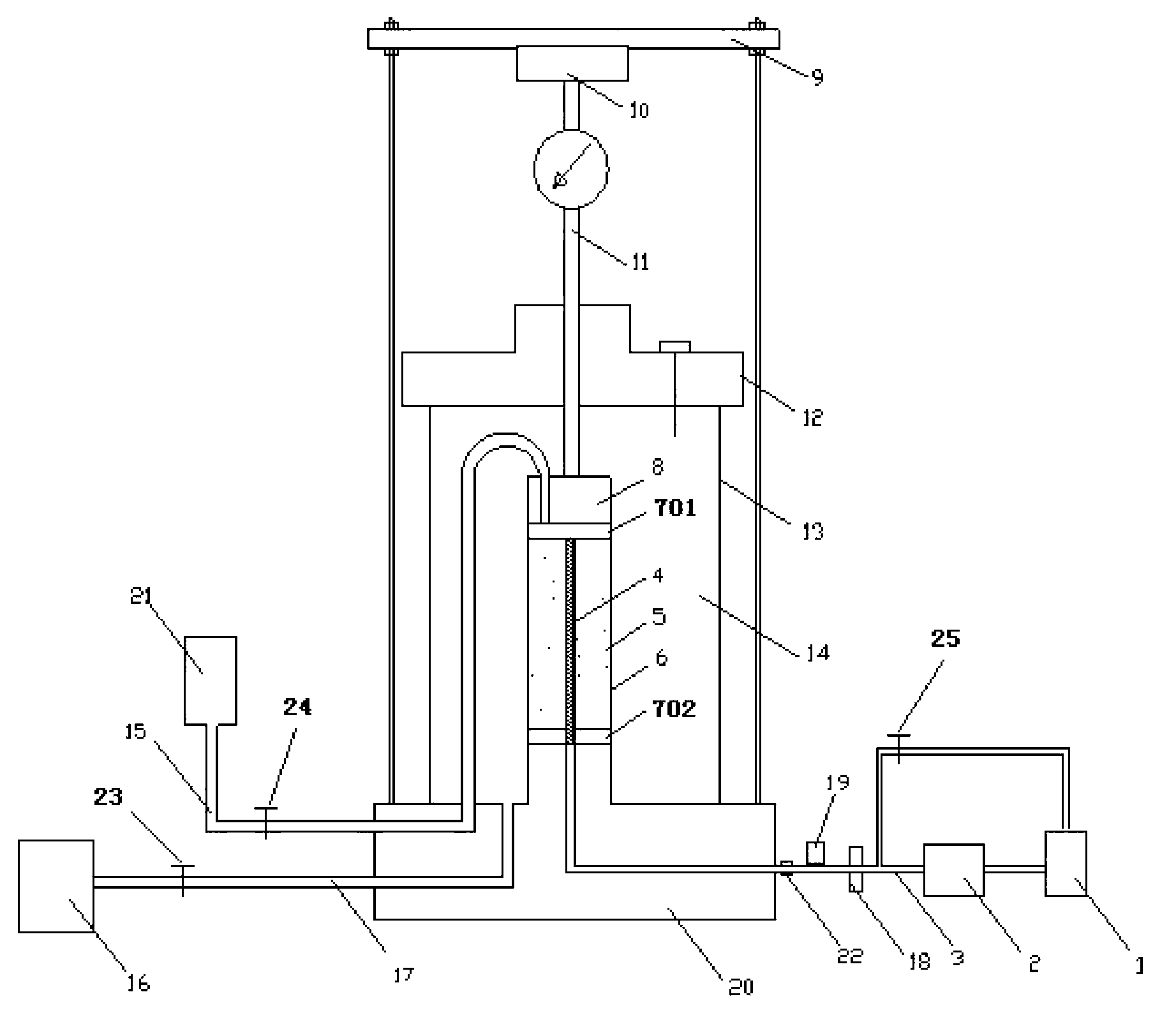

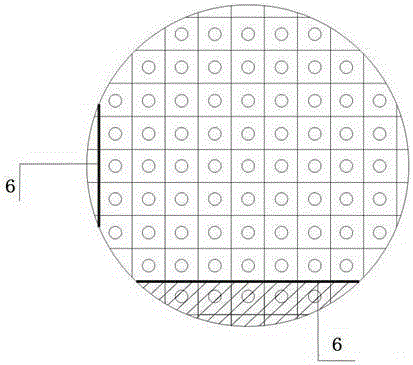

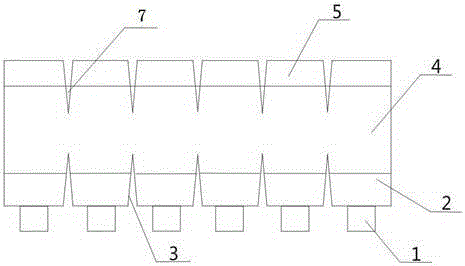

Indoor grouting testing device under simulation of complex stress effect and testing method thereof

InactiveCN103018152ASolve drainage problemsDoes not affect the drainage effectPermeability/surface area analysisRubber membranePressure system

Owner:HUNAN UNIV OF SCI & TECH

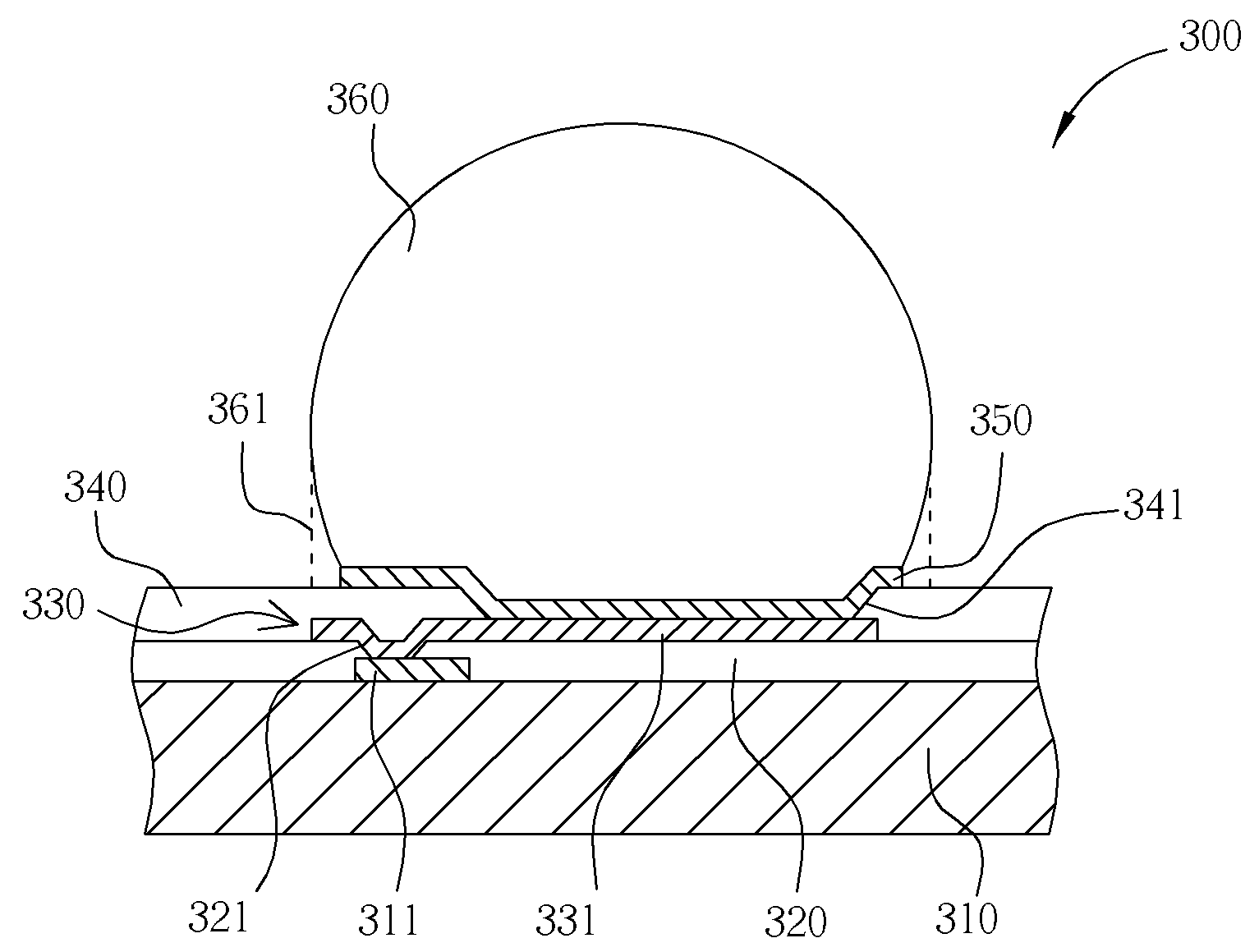

Redistribution connecting structure of solder balls

ActiveUS20070200239A1Increase bonding areaRelieve pressureSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerSolder ball

A redistribution connecting structure for solder balls is disclosed. A substrate includes a plurality of bonding pads. A plurality of dielectric layers, a redistribution conductive layer between the dielectric layer, and a plurality of solder balls are formed on the substrate. The redistribution layer has a redistribution pad disposed adjacent to one of the bonding pads without electrical connection with the redistribution pad. One of the dielectric layers covering the redistribution conductive layer has an opening to partially expose the redistribution pad, in which the opening is approximately circular and has a cut-off portion so that the opening is adjacent to an opening of another of the dielectric layers exposing one of the bonding pads without overlapping. Accordingly, bonding area of the redistribution pad for a bonding pad under one of the solder balls can be expanded to reduce stress effect.

Owner:ADVANCED SEMICON ENG INC

Managing integrated circuit stress using stress adjustment trenches

ActiveUS20070202663A1Semiconductor/solid-state device manufacturingSpecial data processing applicationsTensile strainManufacturing technology

Roughly described, methods and systems for improving integrated circuit layouts and fabrication processes in order to better account for stress effects. Dummy features can be added to a layout either in order to improve uniformity, or to relax known undesirable stress, or to introduce known desirable stress. The dummy features can include dummy diffusion regions added to relax stress, and dummy trenches added either to relax or enhance stress. A trench can relax stress by filling it with a stress-neutral material or a tensile strained material. A trench can increase stress by filling it with a compressive strained material. Preferably dummy diffusion regions and stress relaxation trenches are disposed longitudinally to at least the channel regions of N-channel transistors, and transversely to at least the channel regions of both N-channel and P-channel transistors. Preferably stress enhancement trenches are disposed longitudinally to at least the channel regions of P-channel transistors.

Owner:SYNOPSYS INC

Electromechanical transducer device and method of forming a electromechanical transducer device

ActiveUS20110233693A1Acceleration measurement using interia forcesFluid pressure measurement by electric/magnetic elementsDevice formEngineering

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES +1

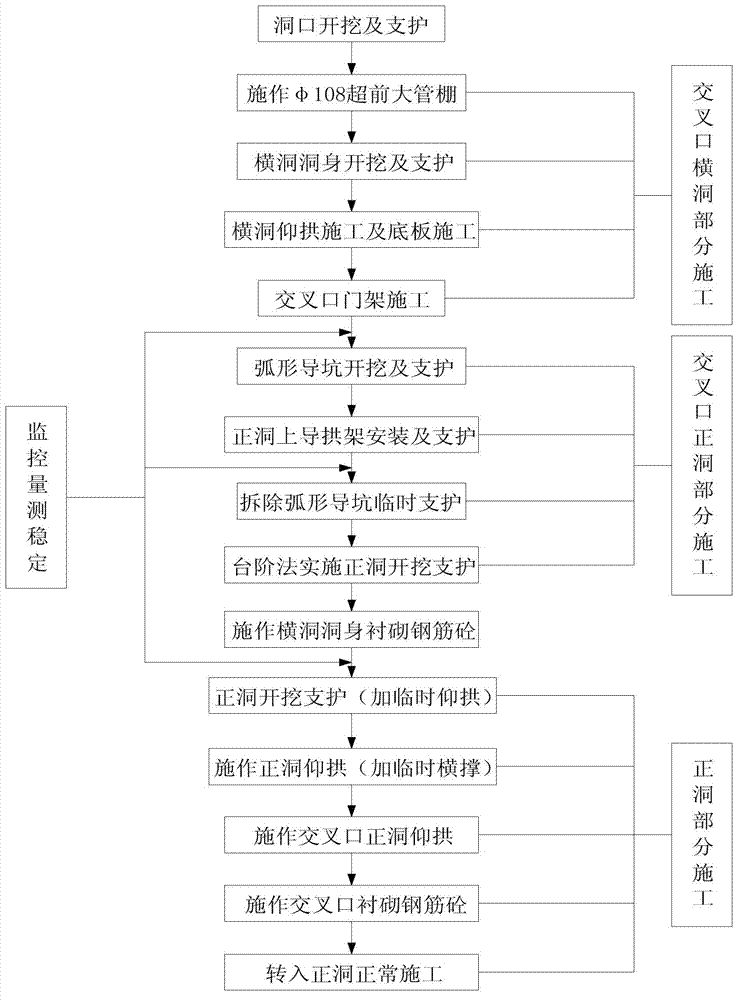

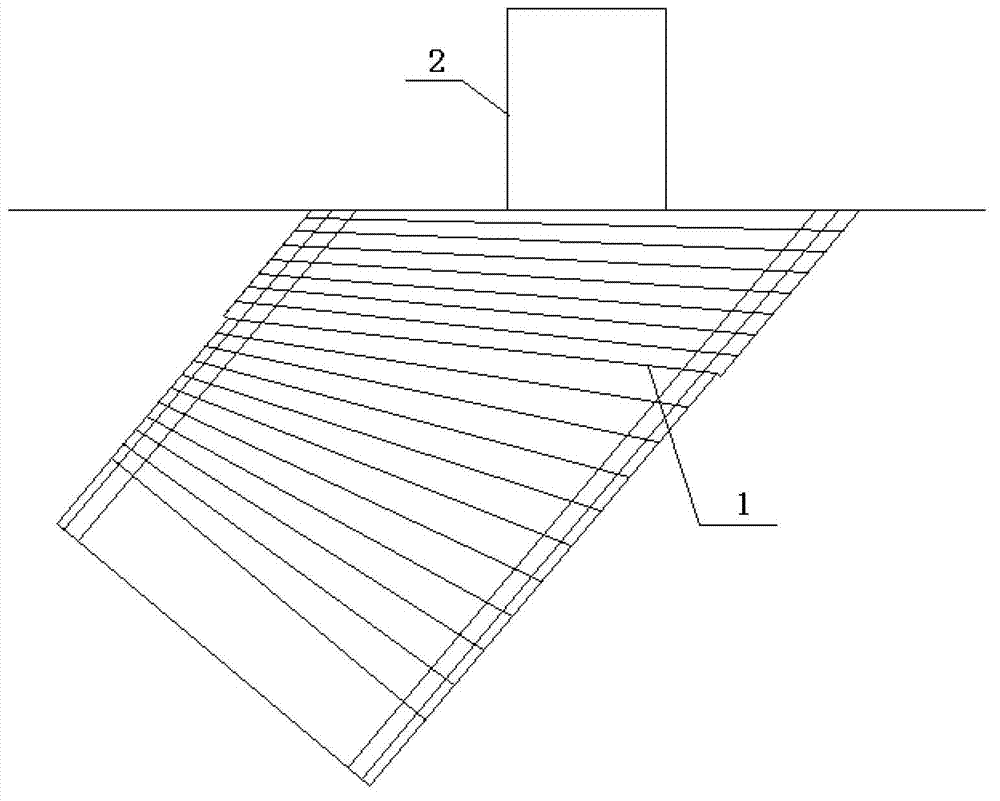

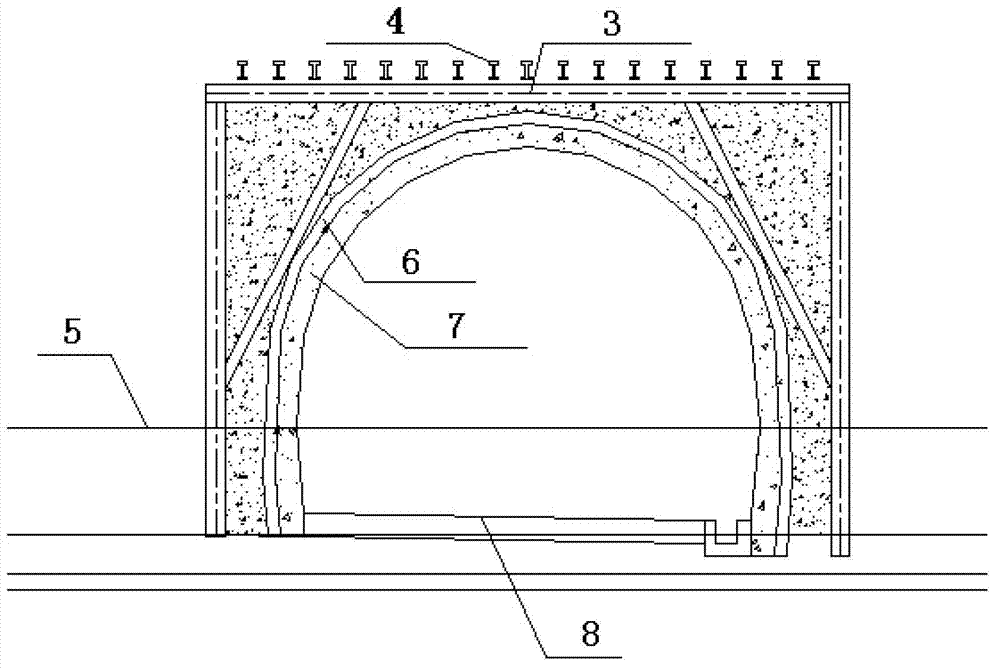

Weak surrounding rock, tunnel intersection and arc-shaped pilot tunnel construction method

InactiveCN103195432AAvoid safety hazardsImprove securityUnderground chambersTunnel liningReinforced concreteEngineering

The invention discloses a weak surrounding rock, tunnel intersection and arc-shaped pilot tunnel construction method. The method is characterized by consisting of the following steps: (1) excavating and supporting a mouth of a transverse hole; (2) constructing an advancing large pipe roof; (3) excavating and supporting a body of the transverse hole; (4) performing transverse hole inverted arch construction and bottom plate construction; (5) performing intersection door opening construction; (6) performing direct top brushing type excavation and supporting on an arc-shaped pilot tunnel; (7) mounting and supporting an upper guide arch frame of a front hole; (8) disassembling the temporary support of the arc-shaped pilot tunnel; (9) excavating and supporting the front hole by a step method; (10) constructing lining reinforced concrete on the body of the transverse hole; (11) excavating and supporting the front hole and adding a temporary inverted arch; (12) constructing a front hole inverted arch and adding a temporary cross brace; (13) constructing an inverted arch on the intersection front hole; (14) constructing lining reinforced concrete on the intersection; and (15) shifting to normal construction of the front hole. The arc-shaped pilot tunnel construction section is smaller than the front hole excavating section; the potential safety hazards of the arch change of the weak surrounding rock are avoided; the temporary work amount is small; the construction efficiency is high; the transverse hole at the intersection does not climb; and the stressed effect of the special-shaped arch frame of the front hole is good.

Owner:中铁二十二局集团第一工程有限公司 +1

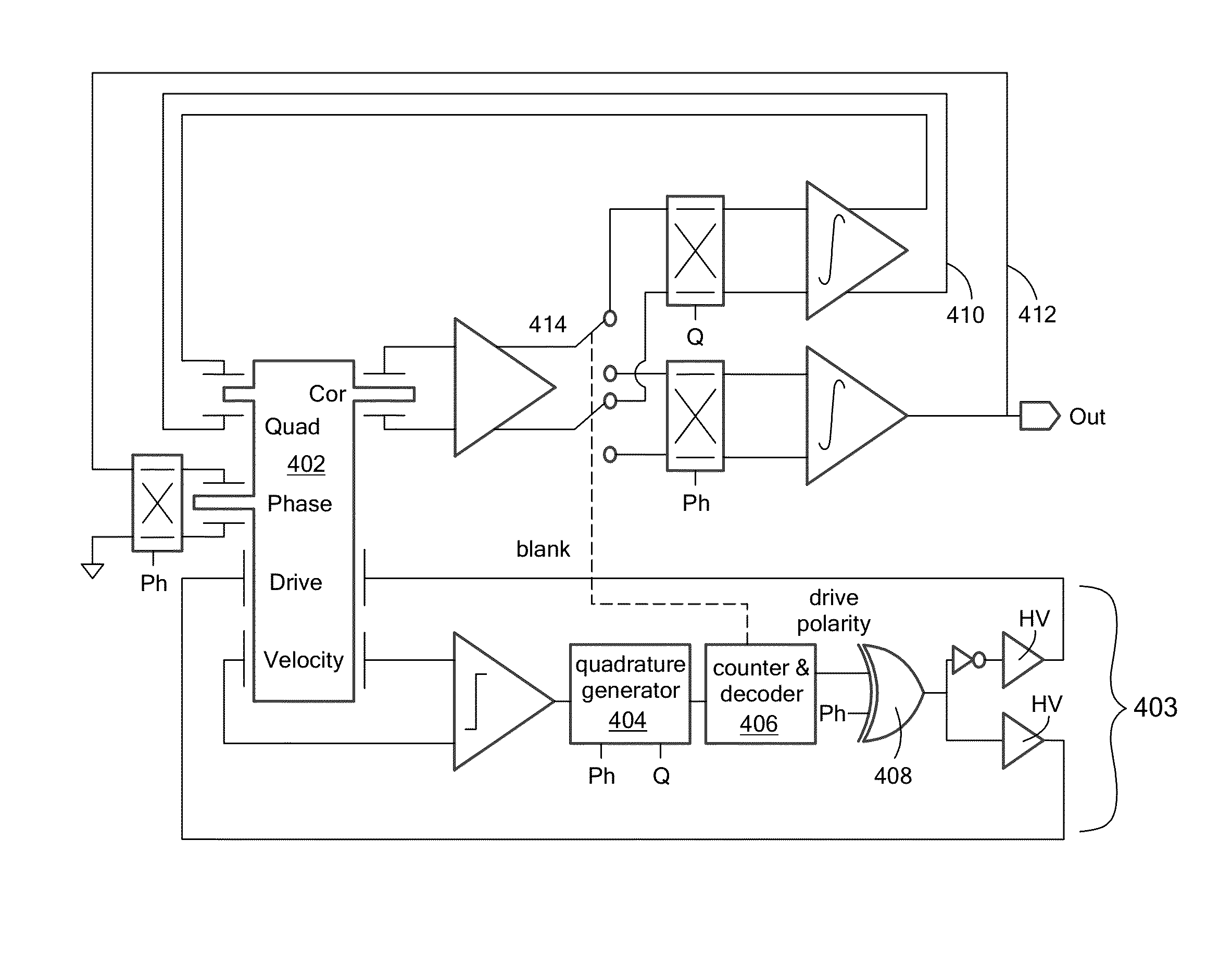

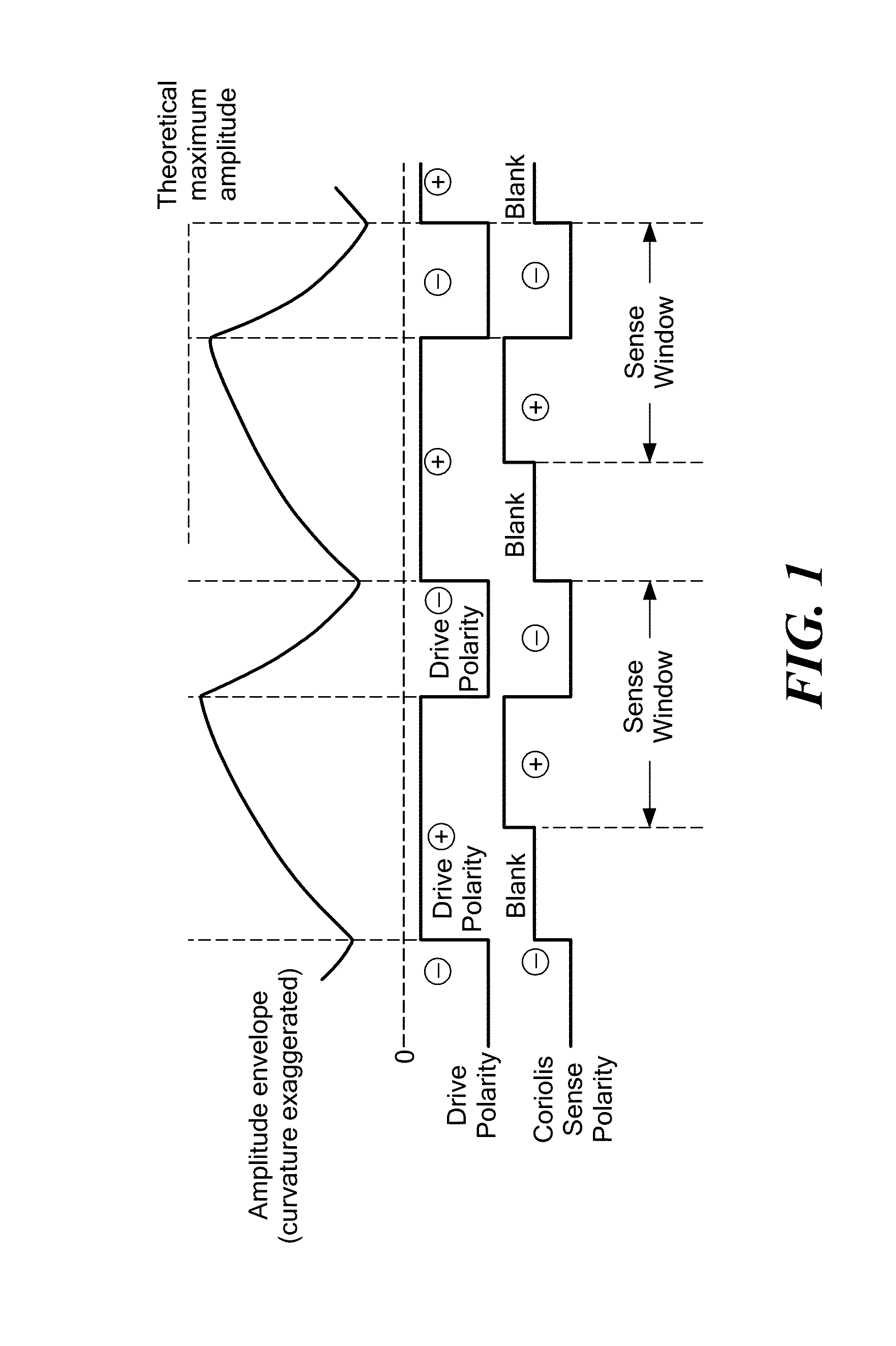

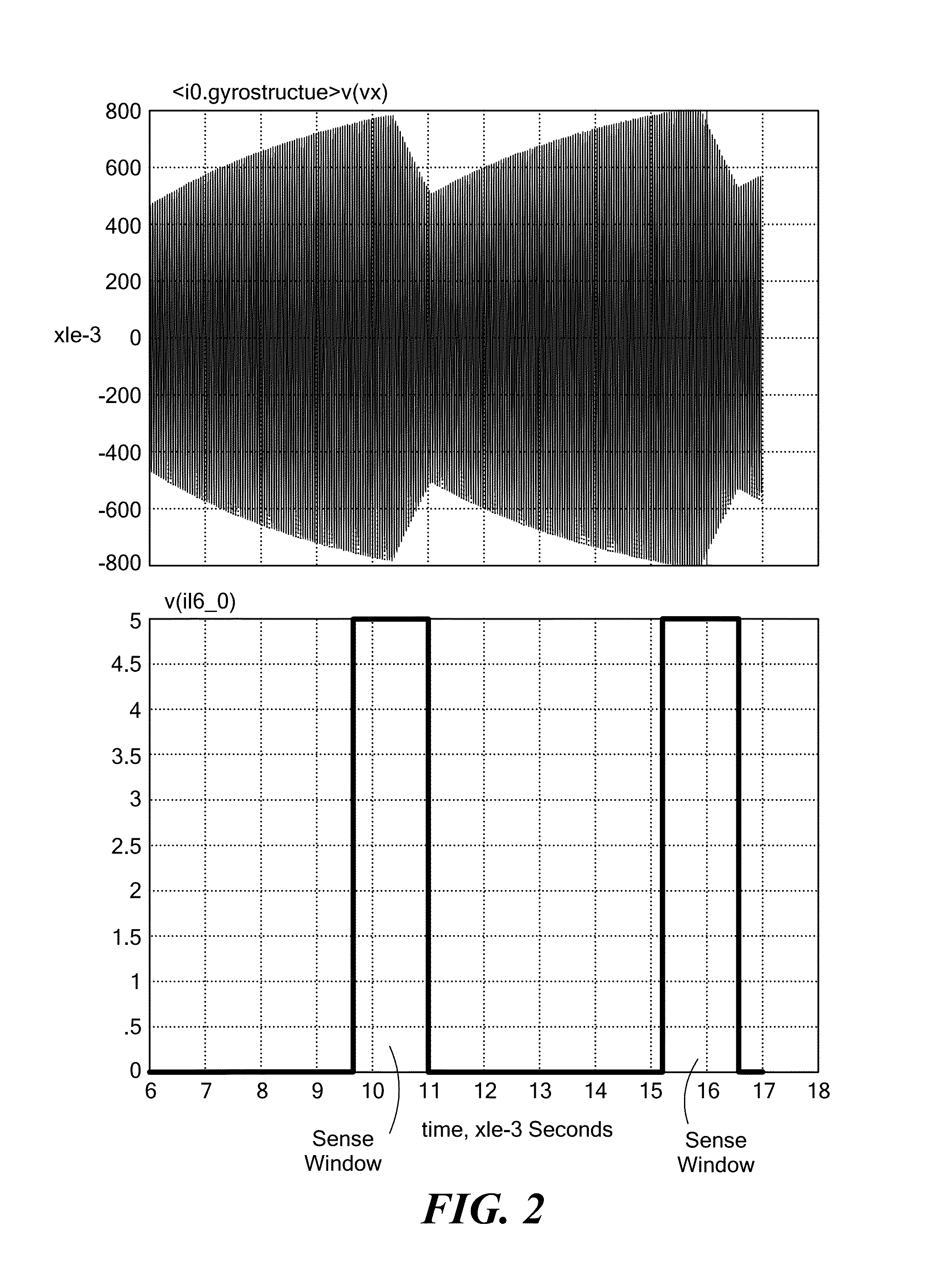

MEMS gyroscopes with reduced errors

ActiveUS20130283908A1Reducing drive-induced Coriolis accelerometerReducing drive-induced Coriolis accelerometer offsetAcceleration measurement using interia forcesSpeed measurement using gyroscopic effectsGyroscopeAccelerometer

In comb drive vibratory gyroscopes, drive-induced Coriolis accelerometer offset is effectively canceled by demodulating the output during equal times of in-phase and anti-phase drive of the shuttle with respect to the velocity signal used for angular rate demodulation. This reduces or eliminates the corresponding thermal and die-stress effects otherwise needing calibration.

Owner:ANALOG DEVICES INC

Application method of cold field plasma discharge assisted high energy ball milled powder and plasma assisted high energy ball milling device

The invention provides an application method of cold field plasma discharge assisted high energy ball milled powder and a plasma assisted high energy ball milling device using the cold field plasma discharge assisted high energy ball milling method. The method comprises the following steps: utilizing dielectric barrier discharge to generate plasmas, introducing a dielectric barrier discharge electrode bar into a high-speed vibrating ball-milling tank, on one hand, requiring a solid insulating medium on the outer layer of the electrode bar to simultaneously bear high-voltage discharge and mechanical shock failure of the grinding ball, and on the other hand, requiring the high-speed vibrating ball milling device to uniformly process the powder. The method is based on the ordinary ball milling technology; the processing efficiency and the effect of the ball mill can be greatly improved by the following steps: under a non-heat-balance discharge condition of the pressure that the discharge space pressure is set to be about 102-106 Pa, introducing the discharge plasmas to input another effective energy to the processed powder, promoting the powder to be processed to be subjected to combined action of the mechanical stress effect and the heat effect of the external electric field, and further accelerating refining of the powder and promoting the alloying progress.

Owner:SOUTH CHINA UNIV OF TECH

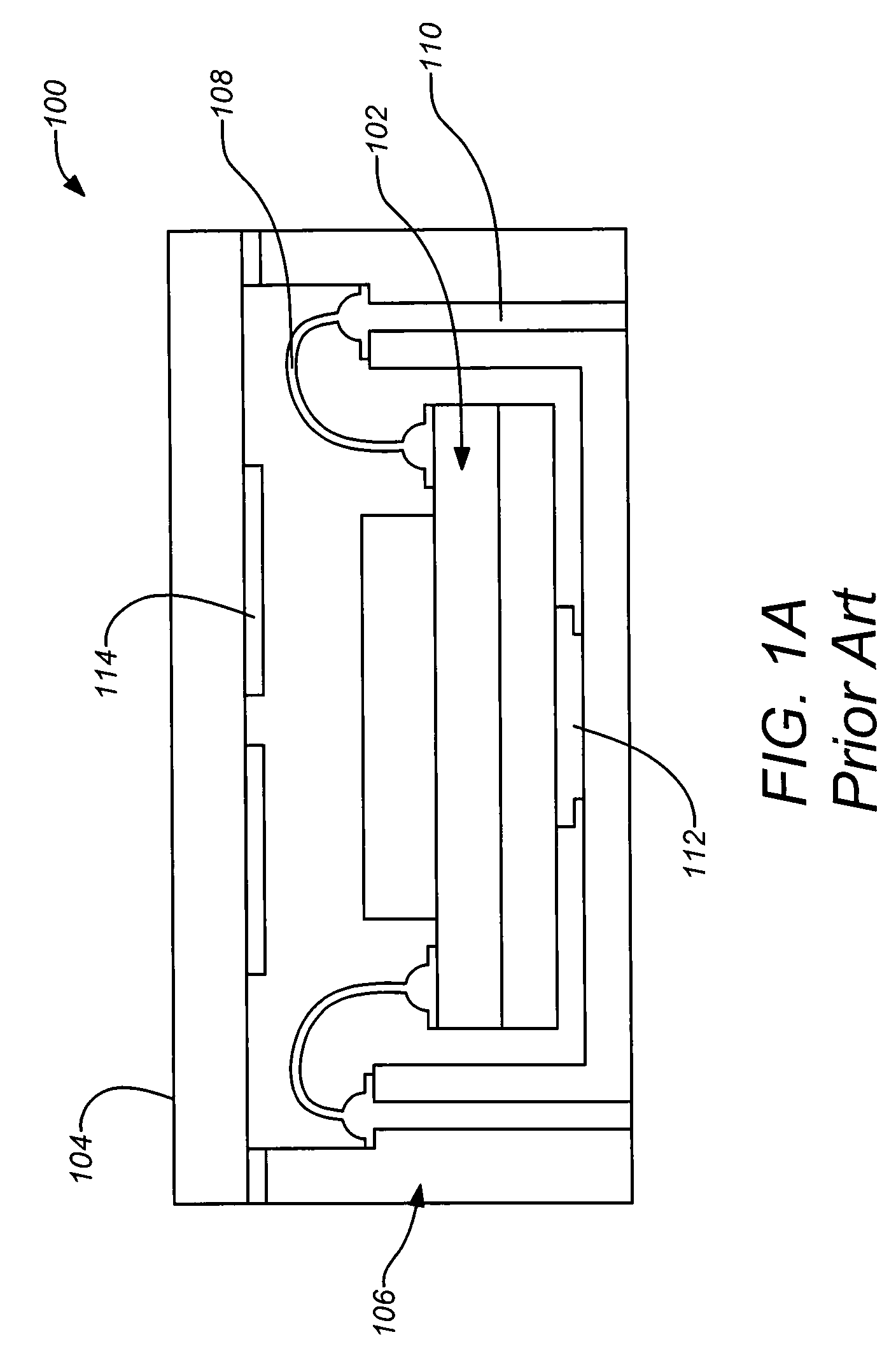

High performance strained channel MOSFETs by coupled stress effects

InactiveUS7119404B2Improve device performanceSemiconductor/solid-state device manufacturingSemiconductor devicesTensile strainMOSFET

Strained channel transistors including a PMOS and NMOS device pair to improve an NMOS device performance without substantially degrading PMOS device performance and method for forming the same, the method including providing a semiconductor substrate; forming strained shallow trench isolation regions in the semiconductor substrate; forming PMOS and NMOS devices on the semiconductor substrate including doped source and drain regions; forming a tensile strained contact etching stop layer (CESL) over the PMOS and NMOS devices; and, forming a tensile strained dielectric insulating layer over the CESL layer.

Owner:TAIWAN SEMICON MFG CO LTD

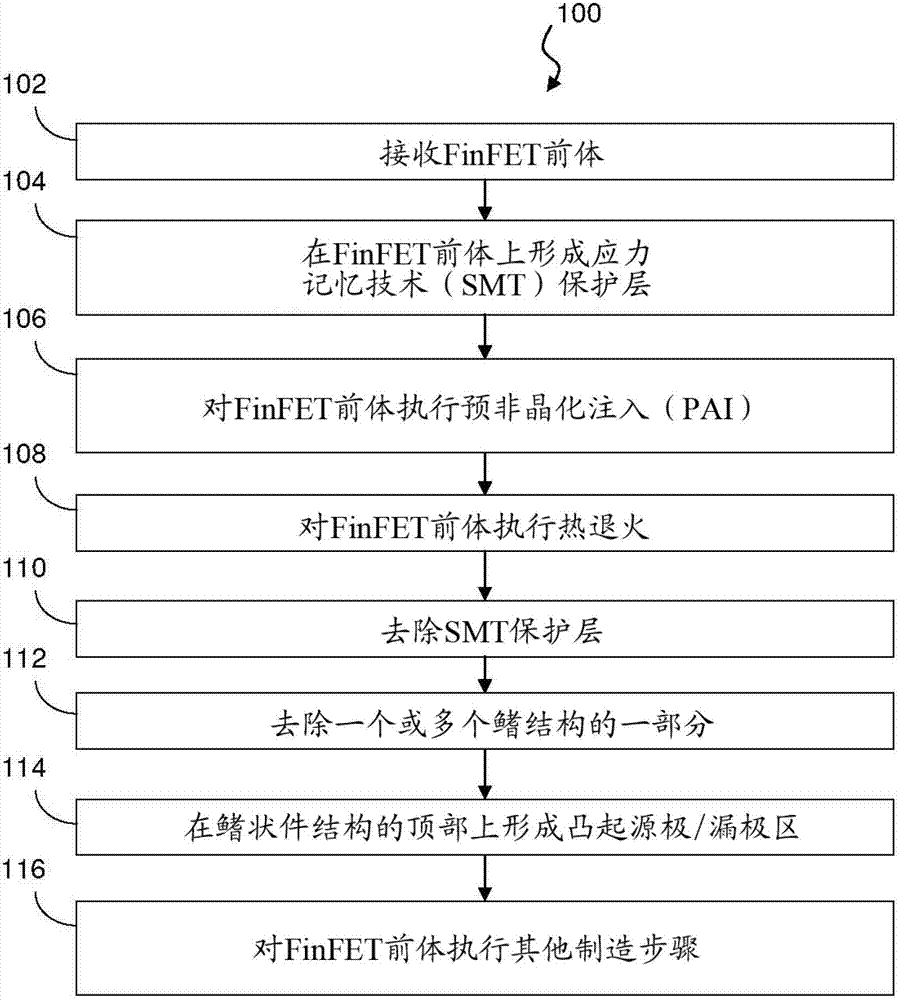

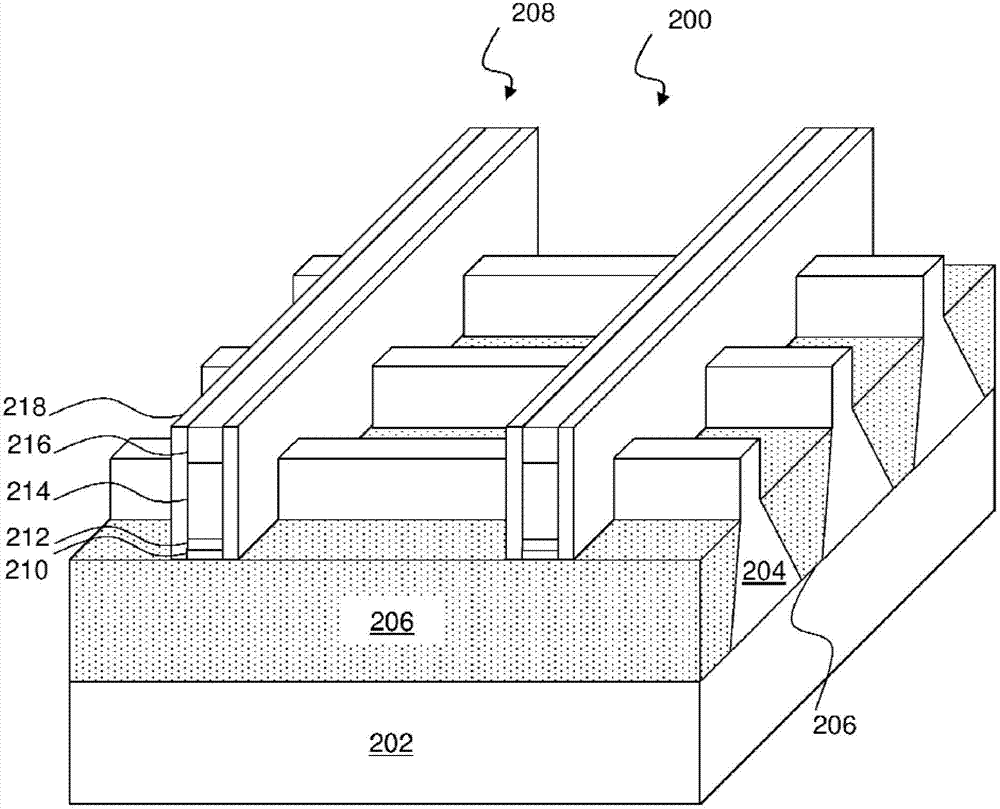

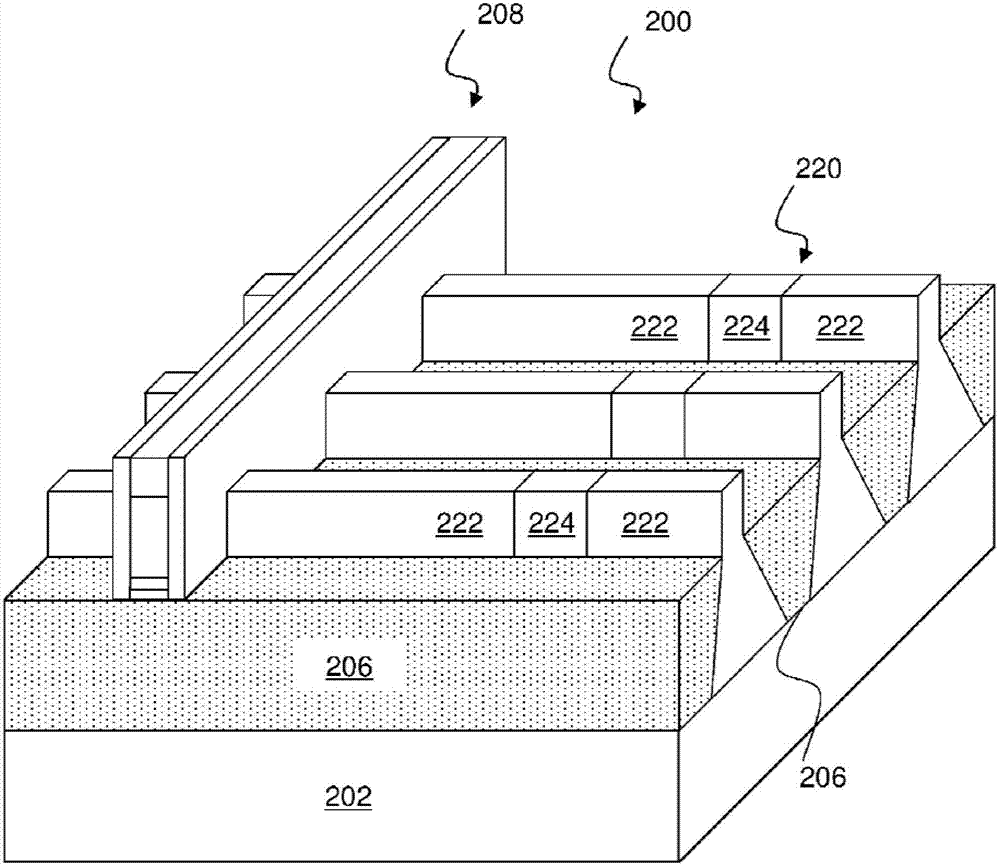

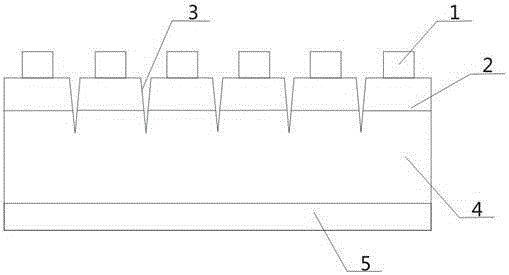

Dislocation SMT for FinFET device

ActiveCN103247535ASemiconductor/solid-state device manufacturingSemiconductor devicesGate stackDislocation

A method for performing a stress memorization technique (SMT) a FinFET and a FinFET having memorized stress effects including multi-planar dislocations are disclosed. An exemplary embodiment includes receiving a FinFET precursor with a substrate, a fin structure on the substrate, an isolation region between the fin structures, and a gate stack over a portion of the fin structure. The gate stack separates a source region of the fin structure from a drain region of the fin structure and creates a gate region between the two. The embodiment also includes forming a stress-memorization technique (SMT) capping layer over at least a portion of each of the fin structures, isolation regions, and the gate stack, performing a pre-amorphization implant on the FinFET precursor by implanting an energetic doping species, performing an annealing process on the FinFET precursor, and removing the SMT capping layer. The invention further provides dislocation SMT for the FinFET device.

Owner:TAIWAN SEMICON MFG CO LTD

GaAs-based LED chip cutting method

ActiveCN105226143AGuaranteed FusionImprove appearance qualitySemiconductor/solid-state device manufacturingFine working devicesSurface stressSurface mounting

The invention discloses a GaAs-based LED chip cutting method. The method comprises the following steps: (1) semi-cutting is carried out on a P surface, criss-cross cutting grooves are formed, and chip P surface electrodes are separated at equal intervals; (2) the chip P electrodes face a white film downwardly, N electrodes face upwardly and are attached to the white film; (3) chip N surface scribing is carried out along the cutting grooves formed by P surface semi-cutting, and chip N surface stress is relieved; (4) film inverting is carried out on the scribed chip, and the chip is transferred to a blue film from the white film; and (5) on the chip N surface, a bonding tool of a chip breaking machine is used for chip breaking along scratches, and the chip is processed into independent crystal grains. The improved surface mount method is used, a cutting method which combines advantages of a chip sawing machine and a laser chip scribing machine is adopted, the chip P surface stress and the N surface stress are relieved maximally, deformation stress effects caused by film laminating can be reduced and edge collapse and pipe core breaking phenomena after the chip is cut are reduced, and the appearance quality after the chip is cut is improved.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS

Composition and method for appetite and craving suppression and mood enhancement

A composition for suppressing appetite and cravings for substances such as nicotine, coffee, sweets or chocolate while improving energy and enhancing mood comprises theobromine or a salt thereof at an effective amount of from about 250 to 4000 mg. Using such relatively high proportions of theobromine, without added caffeine or ephedrine provides an effective method for promoting weight control or to halt substance cravings without the side effects associated with such stimulants. The composition also includes Rhodiola rosea extract to offset stress effects from reduced food or substance intake, and to further improve mood, and clarity of thought and ability to handle stress, and to also increase endurance while reducing muscle pain.

Owner:EURARK

Predicting method of large-size NEPE propellant loading storage life

The invention discloses a predicting method of large-size NEPE propellant loading storage life, which includes following steps: (1) performing constant-stress load single-temperature acceleration test, which includes operations of making an NEPE propellant acceleration aging test sample under constant-stress load and performing a single-temperature-stress level temperature acceleration life test; (2) researching the performance change law during an NEPE propellant loading aging process; (3) determining a failure model of the NEPE propellant loading; and (4) carrying out acceleration life tests at different temperatures and under different pressures to predict the large-size NEPE propellant loading storage life. In the method, by means of loading pressure to simulate the self weight on a large-size NEPE propellant during storage, the performance change law of the NEPE propellant under a temperature-pressure double-stress effect. In addition, with tensile strength as a failure parameter, the method of evaluating the NEPE propellant loading storage life is disclosed.

Owner:XIAN MODERN CHEM RES INST

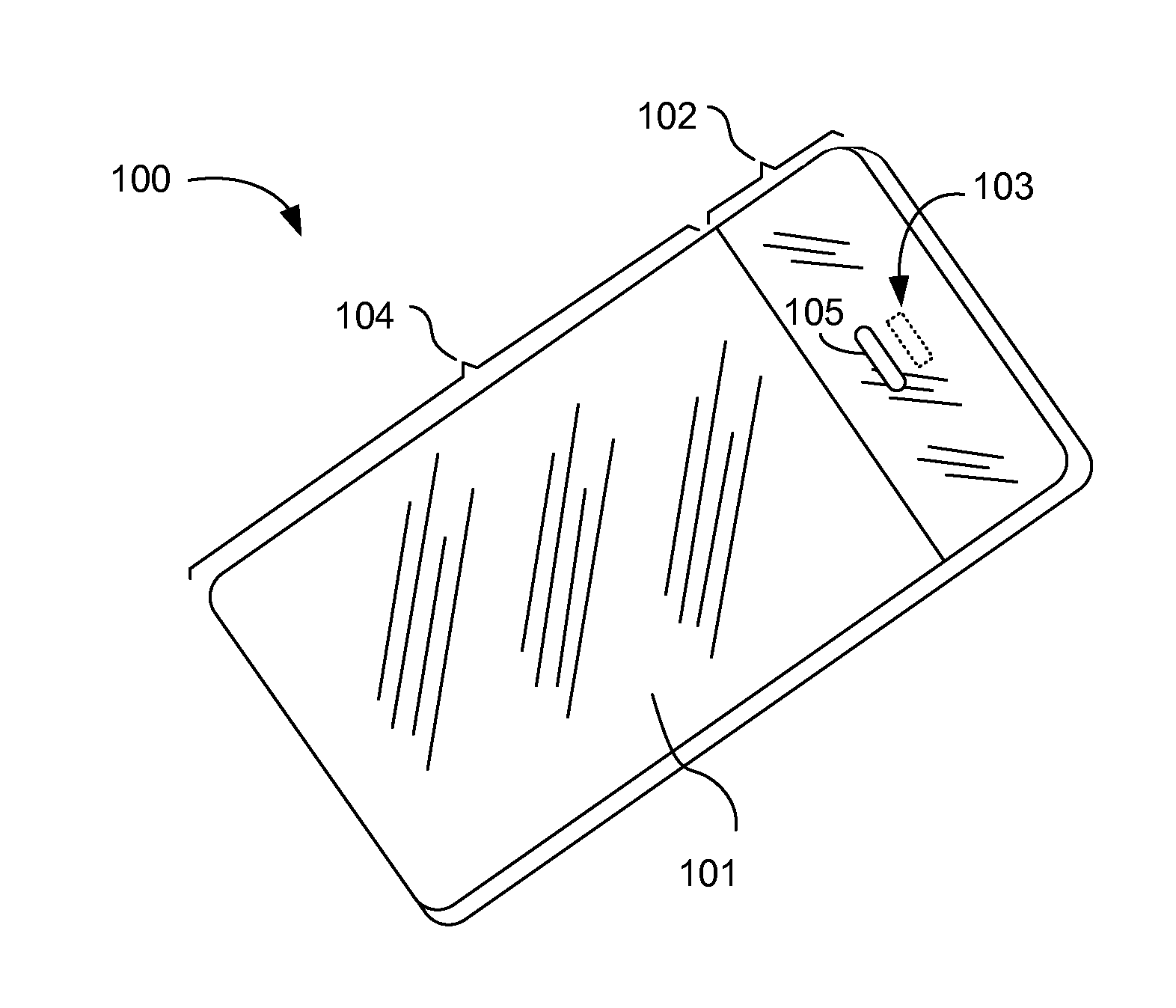

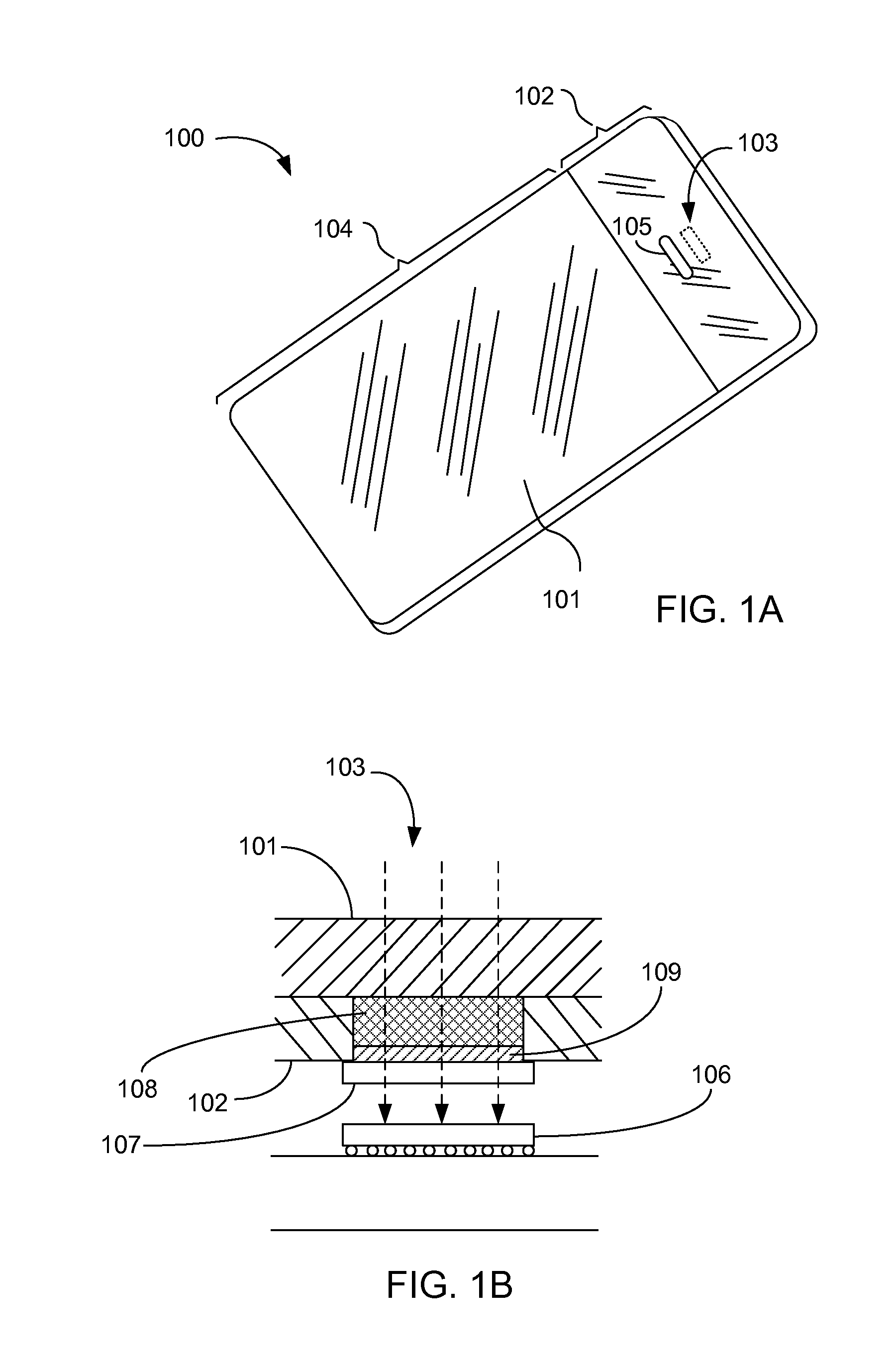

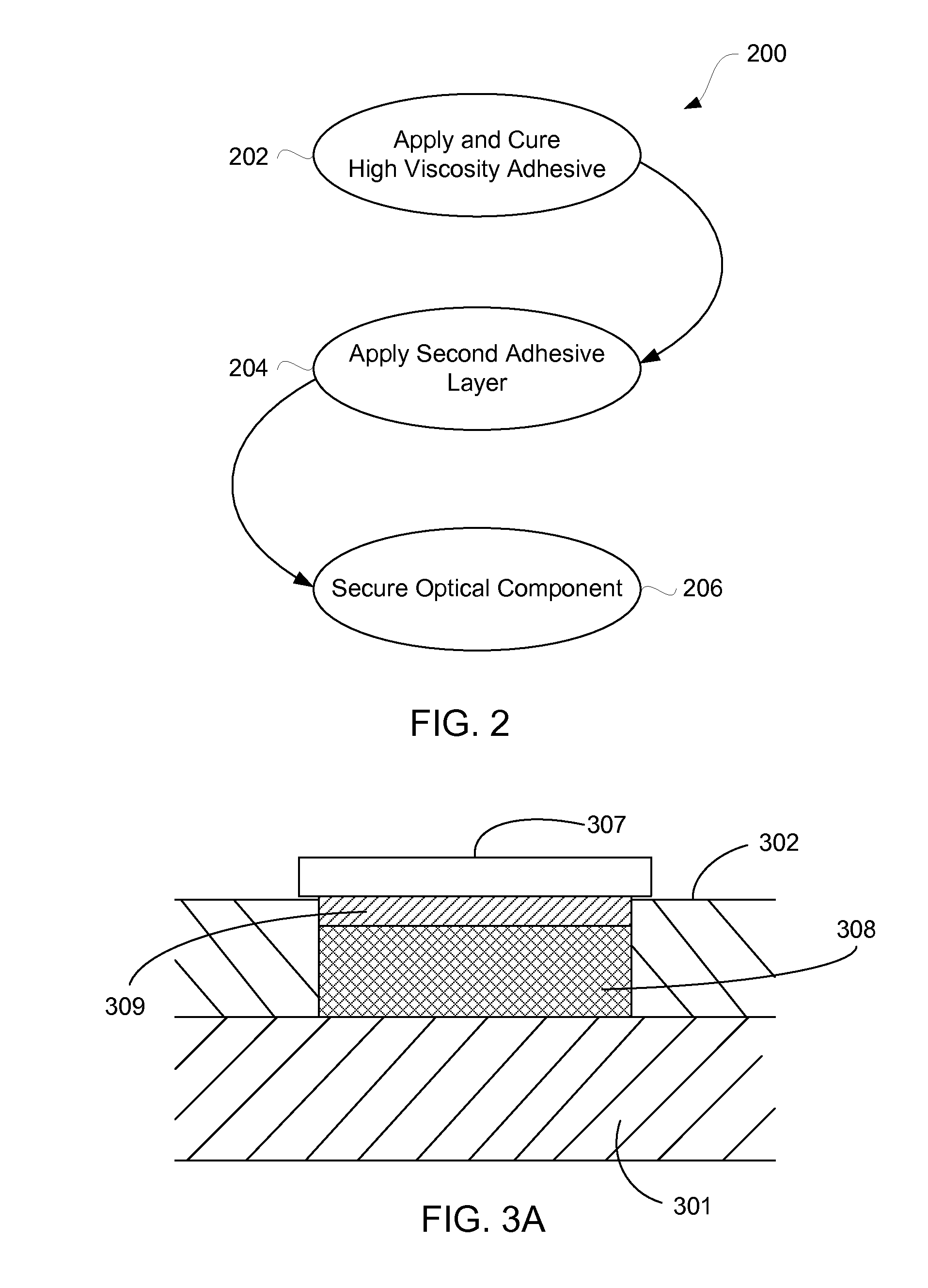

Multi-layer adhesive assemblies for electronic devices

InactiveUS20120275088A1Avoid optical distortionPaper-makingDigital data processing detailsAdhesiveEngineering

Techniques or processes for producing assemblies using adhesives and substrate material, such as glass. In one embodiment, the assemblies may be for portable electronic devices. For example, a cover glass of a portable electronic device may have a first layer of a self-leveling adhesive, which may be adhesively coupled with the cover glass. A second layer of a second adhesive, which may be different than the self-leveling adhesive of the first layer, may be adhesively coupled with the first layer. An optical component may be adhesively coupled with the second layer, so as to secure the optical component. The first layer may be cured prior to securing the optical component, so that the optical component may be substantially isolated from stress effects of adhesive cure shrinkage of the first layer. Flexure, warpage or optical distortion of the optical component due to adhesive cure shrinkage may be substantially avoided.

Owner:APPLE INC

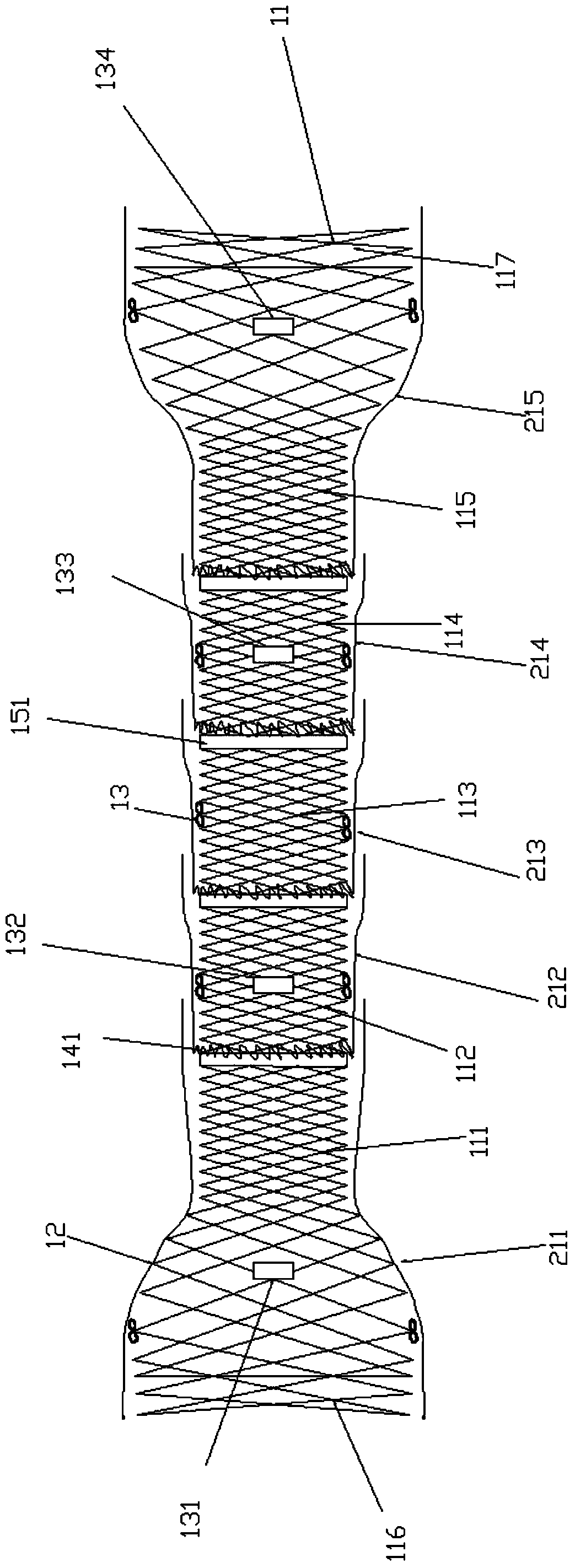

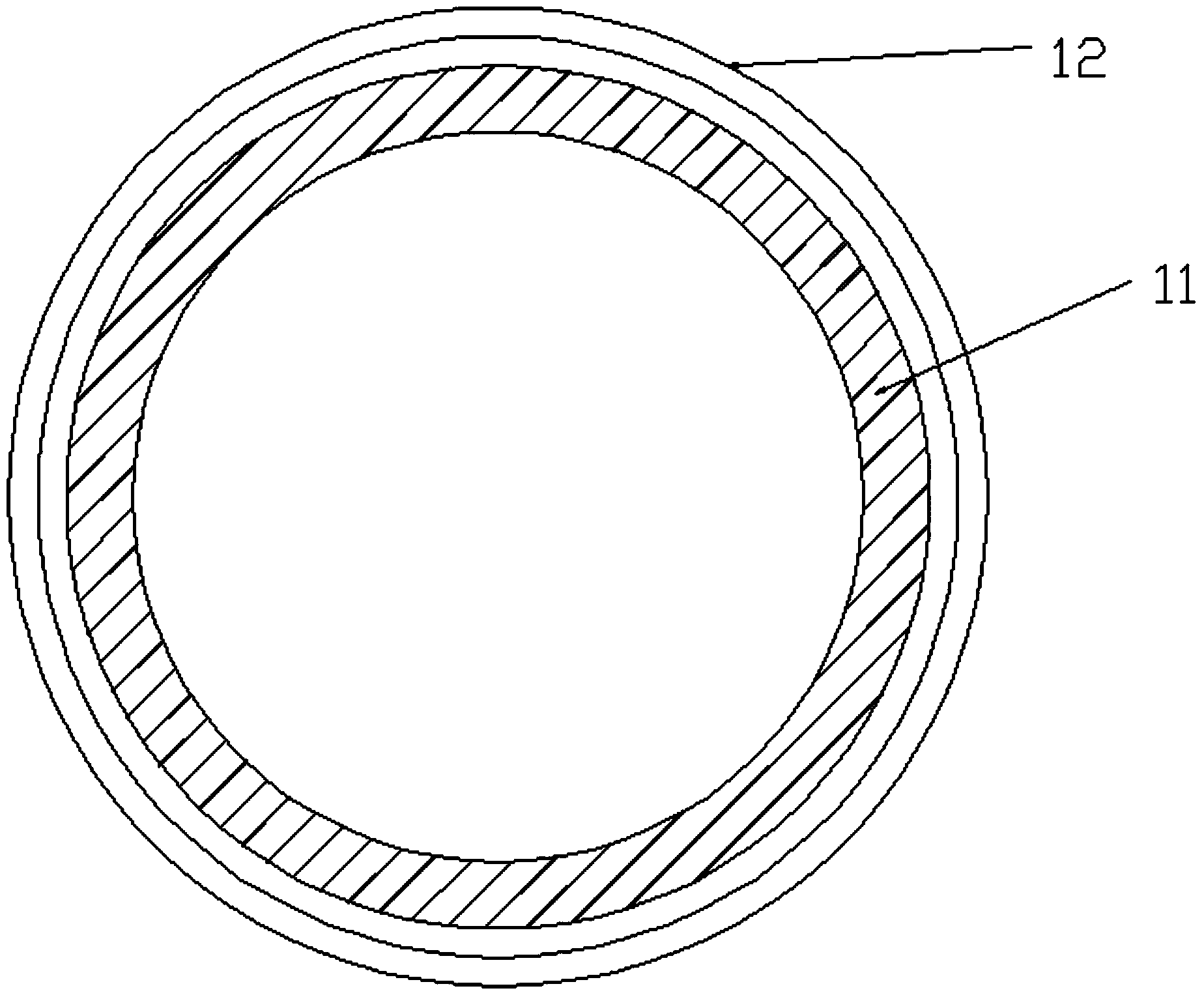

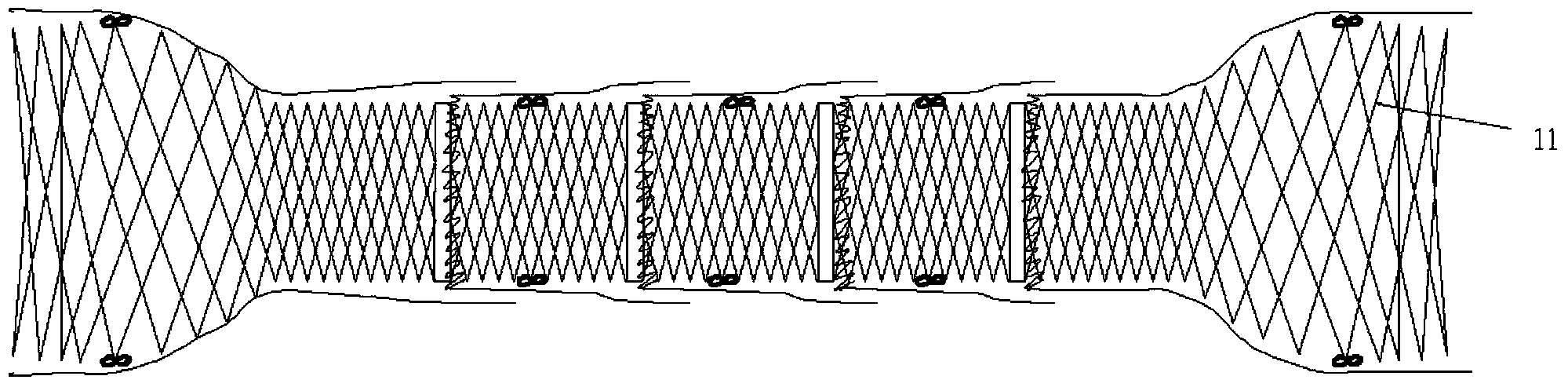

Degradable human body stent capable of effectively preventing transposition and reducing hyperplasia and manufacturing method

The invention relates to a degradable human body stent capable of effectively preventing transposition and reducing hyperplasia. The degradable human body stent is characterized by comprising a reticulate body structure, a skirt stacking type degradable laminating membrane, at least one developing sign and a covering membrane. The skirt stacking type degradable laminating membrane and the developing sign are additionally arranged on multiple sections of reticulate bodies to be used for identifying the human body implantation position of the human body stent during human body developing. The reticulate body structure is composed of the multiple sections of reticulate bodies, and the multiple sections of reticulate bodies are connected in series, so that the multiple sections of reticulate bodies are bent to a certain degree relative to others under the stress effect, and a channel is formed between the multiple sections of reticulate bodies. The multiple sections of reticulate bodies are formed by degradable materials. The peripheries of the multiple sections of reticulate bodies are covered by the covering membrane, the membranes of the whole stent are like fish scales, and one section of skirt is stacked below a next section of skirt. The one or more developing signs are additionally arranged on the multiple sections of reticulate bodies to be used for identifying the human body implantation position of the human body stent during human body developing.

Owner:施瑞华

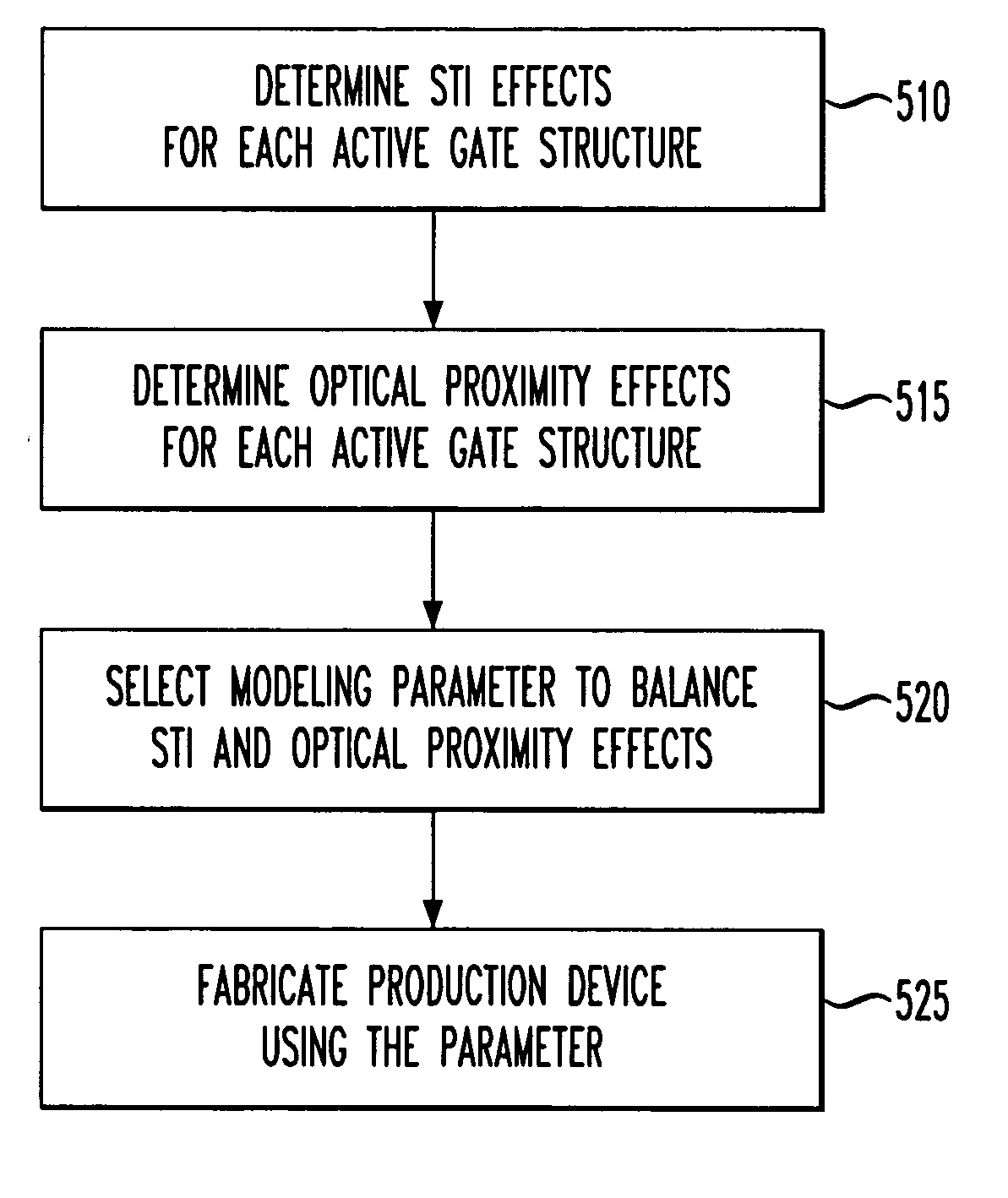

Method of making a semiconductor device by balancing shallow trench isolation stress and optical proximity effects

ActiveUS20060107243A1Semiconductor/solid-state device testing/measurementSolid-state devicesEngineeringSemiconductor

The present invention provides a method for manufacturing a semiconductor device, comprising: determining an isolation structure stress effect of a first semiconductor device, determining an optical proximity effect of a second semiconductor device, selecting a modeling design parameter such that the isolation structure stress effect is offset against the optical proximity effect on a fabrication model, and using the selected design parameter to construct a third semiconductor device.

Owner:BELL SEMICON LLC

Stress-managed revision of integrated circuit layouts

ActiveUS20090313595A1Semiconductor/solid-state device manufacturingCAD circuit designDiffusionTensile strain

Owner:SYNOPSYS INC

Stress-managed revision of integrated circuit layouts

ActiveUS7600207B2Semiconductor/solid-state device manufacturingCAD circuit designDiffusionTensile strain

Owner:SYNOPSYS INC

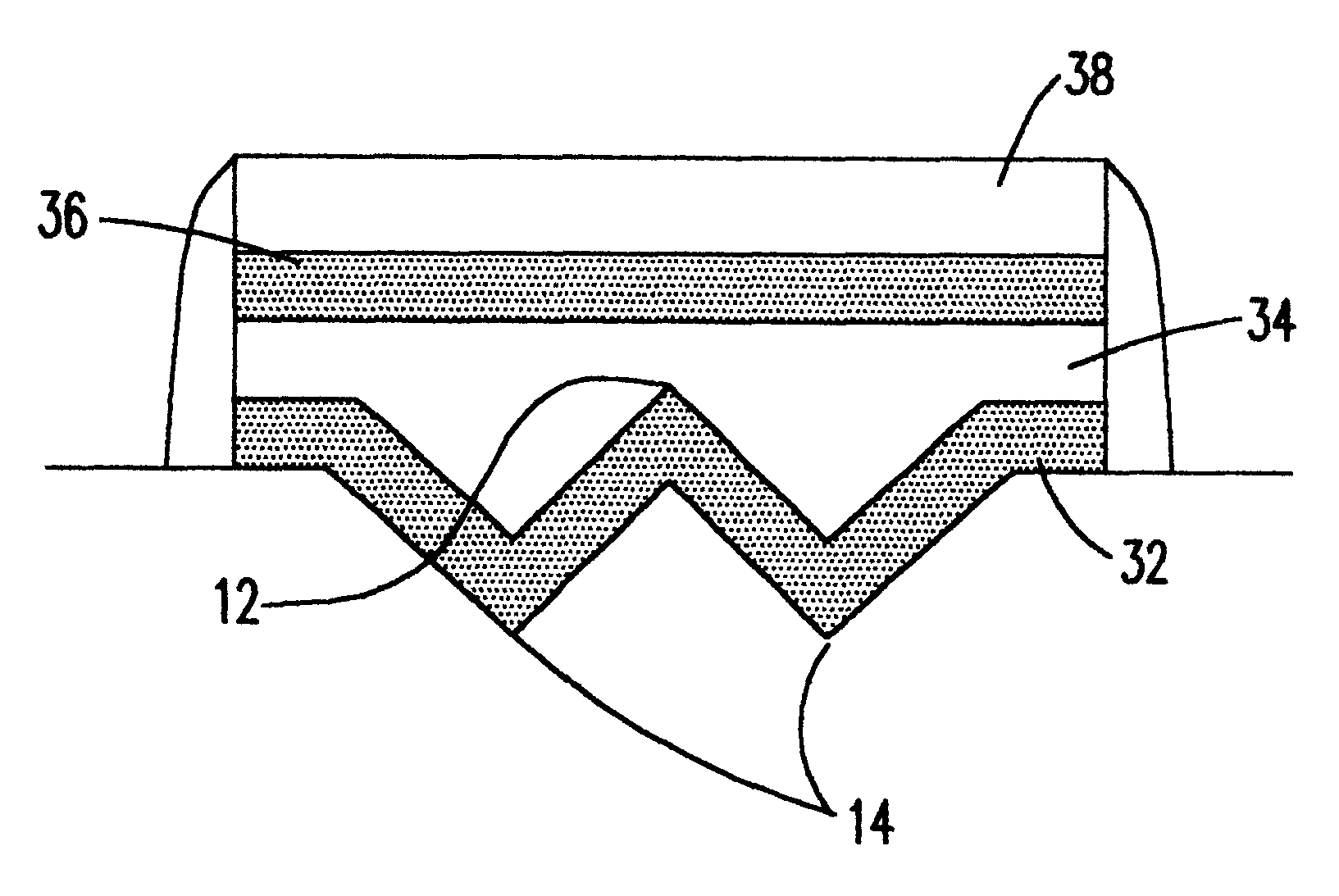

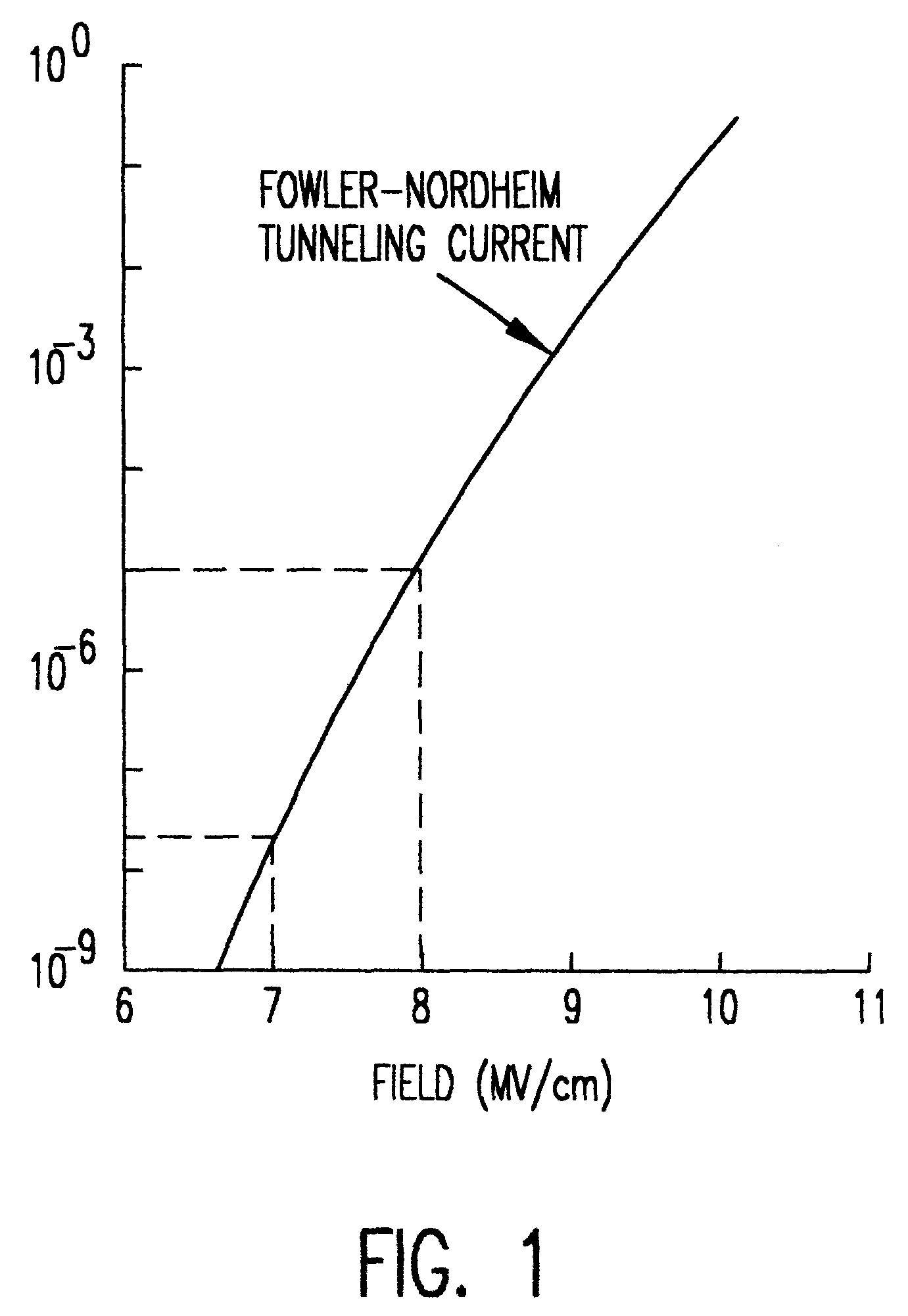

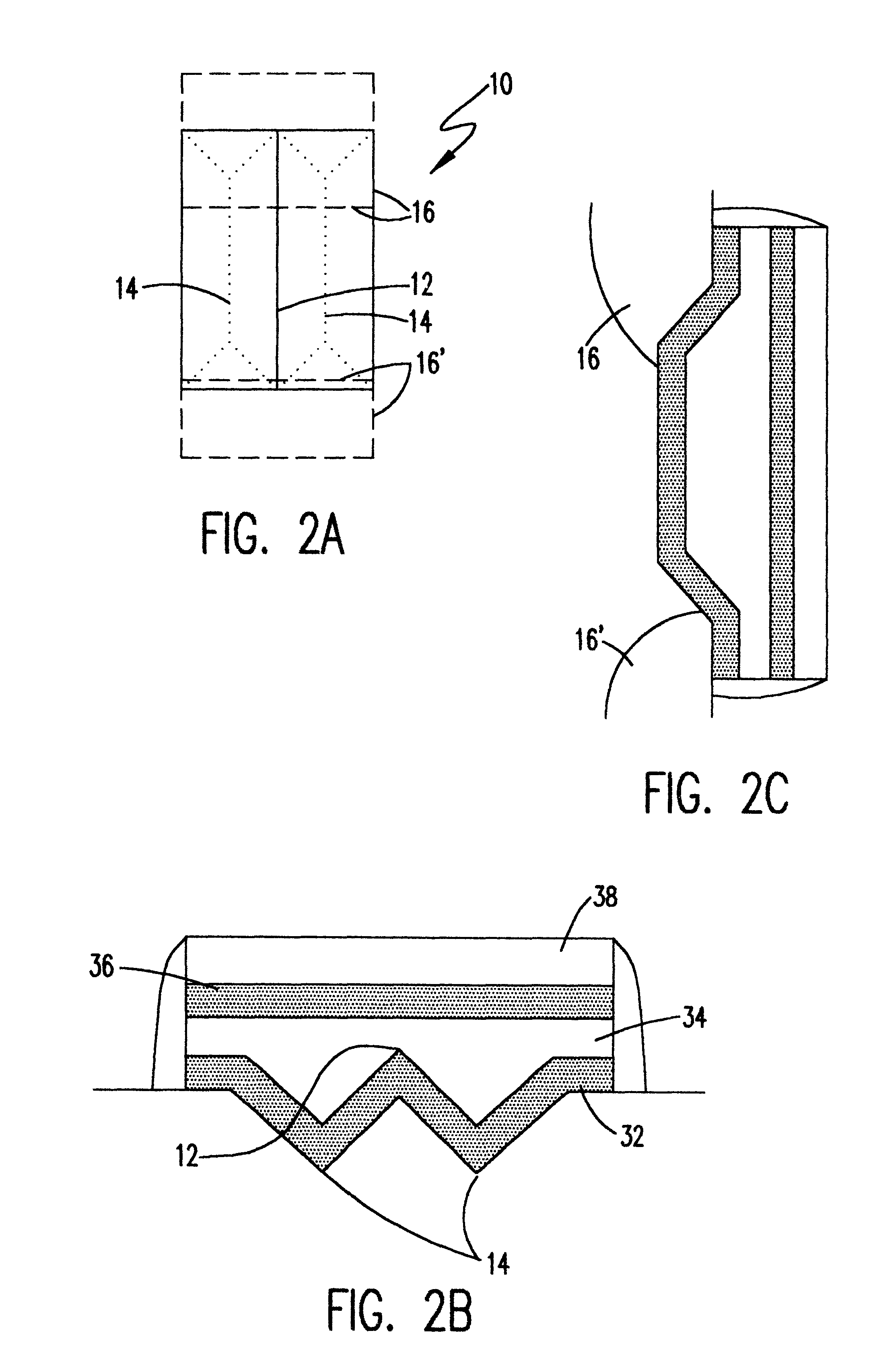

NVRAM array device with enhanced write and erase

InactiveUS6445029B1Increased write and erase tunnelling currentTransistorSolid-state devicesPreferential etchingGate insulator

Increased write and erase tunnelling currents are developed by enhancement of an electric field near a floating gate with a shaped edge structure overlapping a source / drain diffusion and developing increased floating gate area with angled regions joined by edges in order to reduce write and erase cycle times. The edge structure is formed by selective and preferential etching in accordance with the crystal structure of a monocrystalline semiconductor substrate. The sharpness of the edges and concentration of the electric field may be enhanced by consumption and stress effects of oxidation of the substrate to form a floating gate insulator.

Owner:GLOBALFOUNDRIES INC