Patents

Literature

144results about How to "Increase channel width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

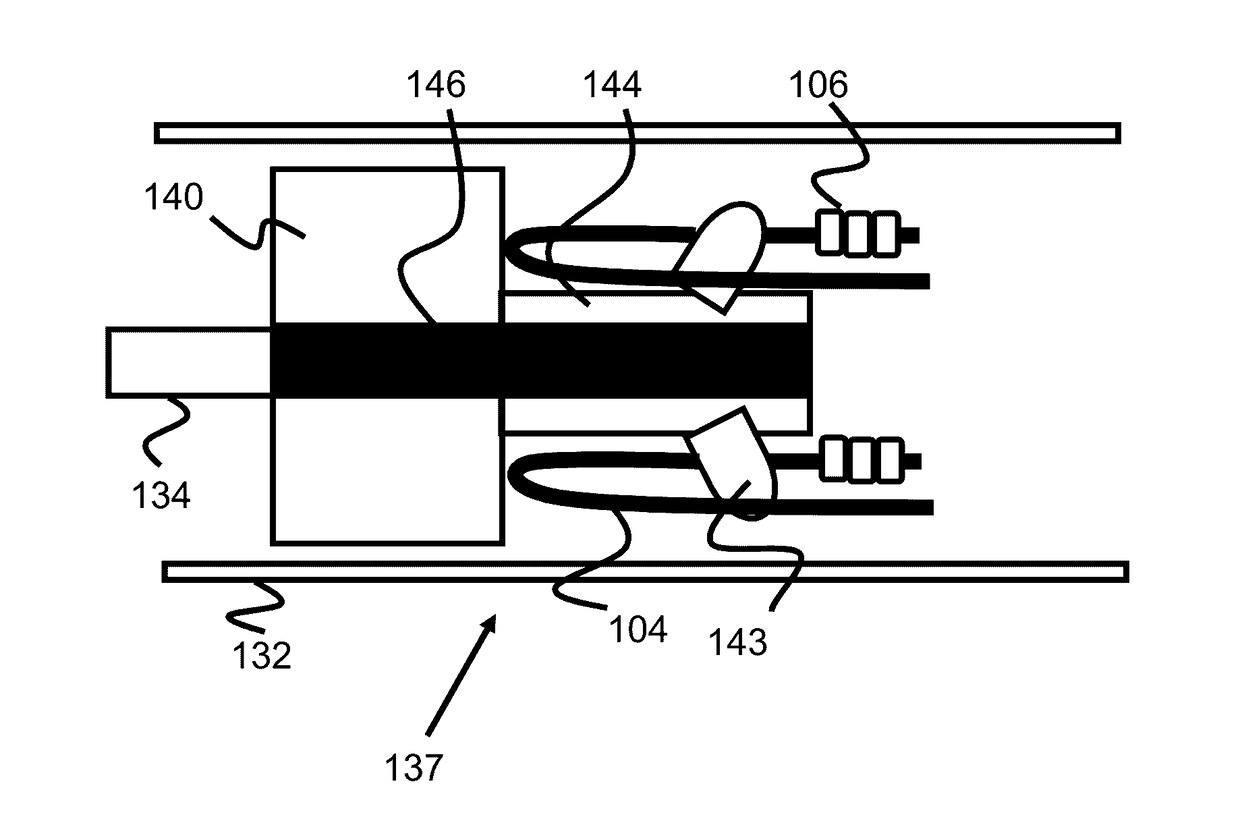

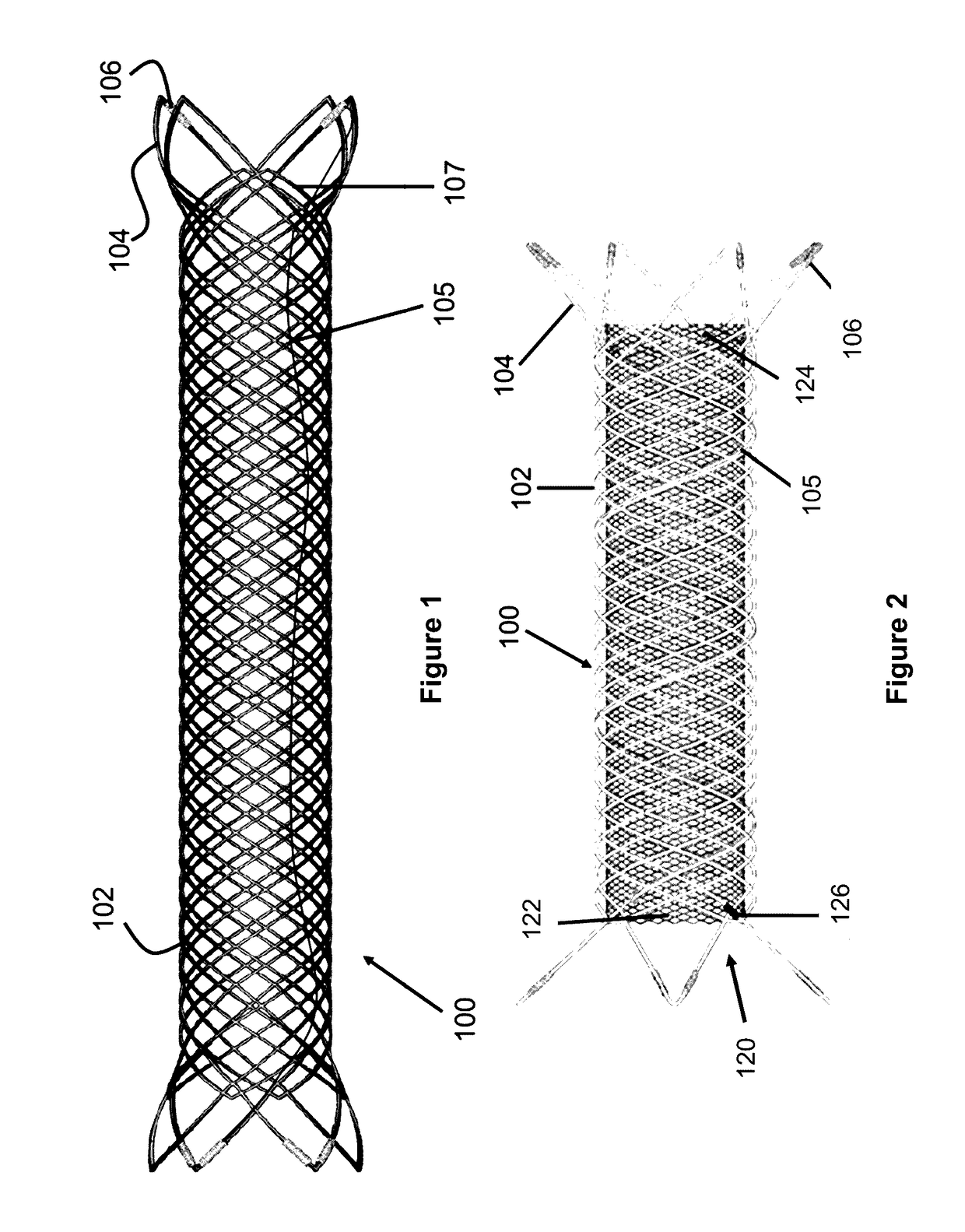

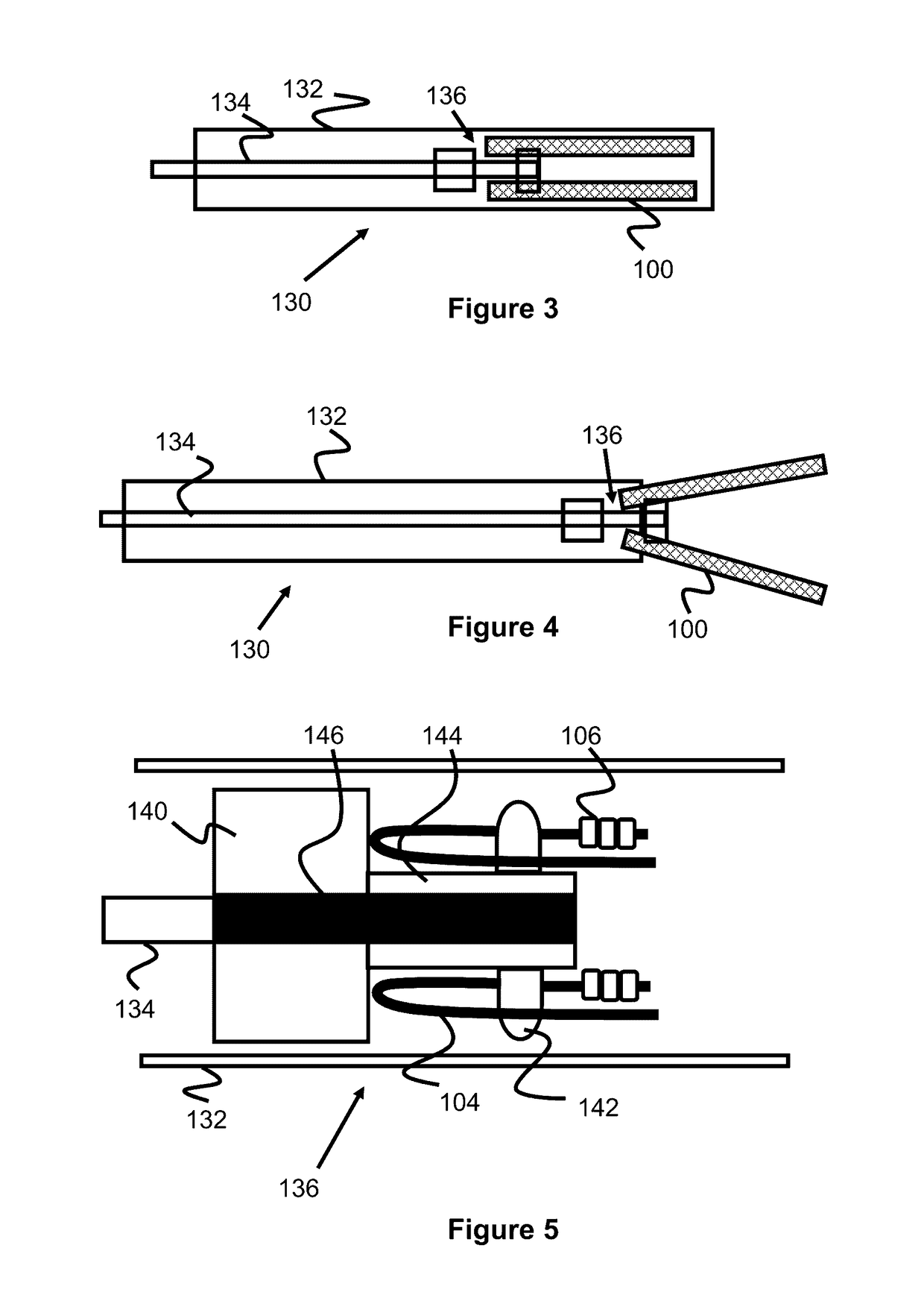

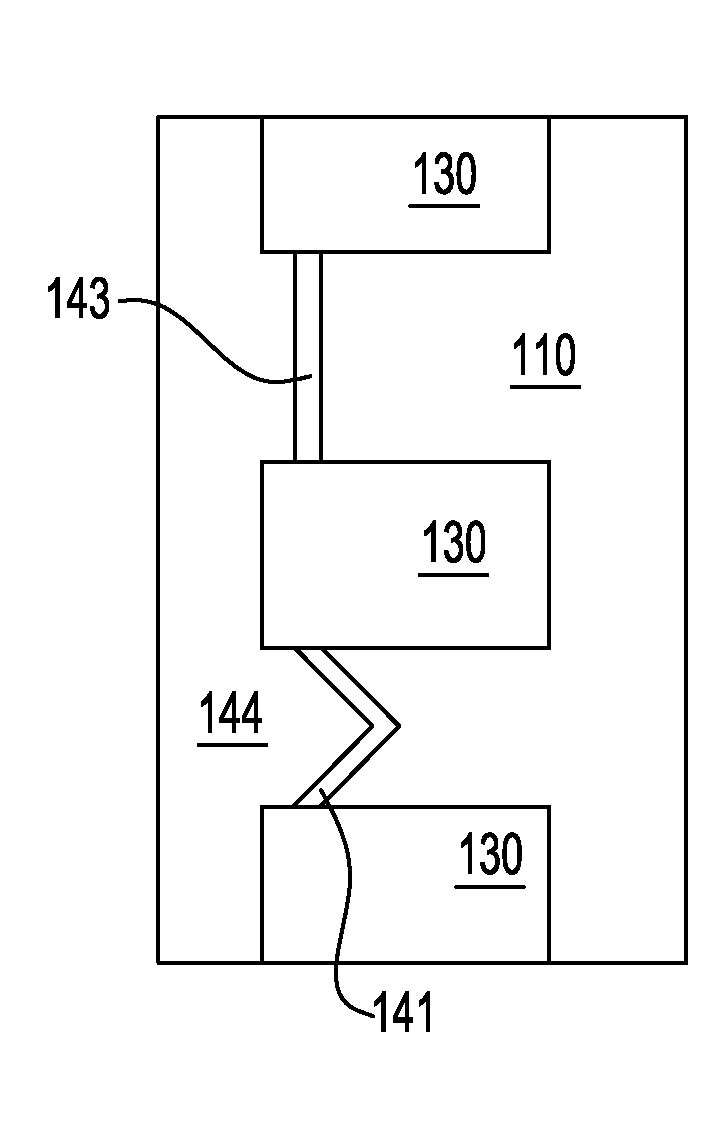

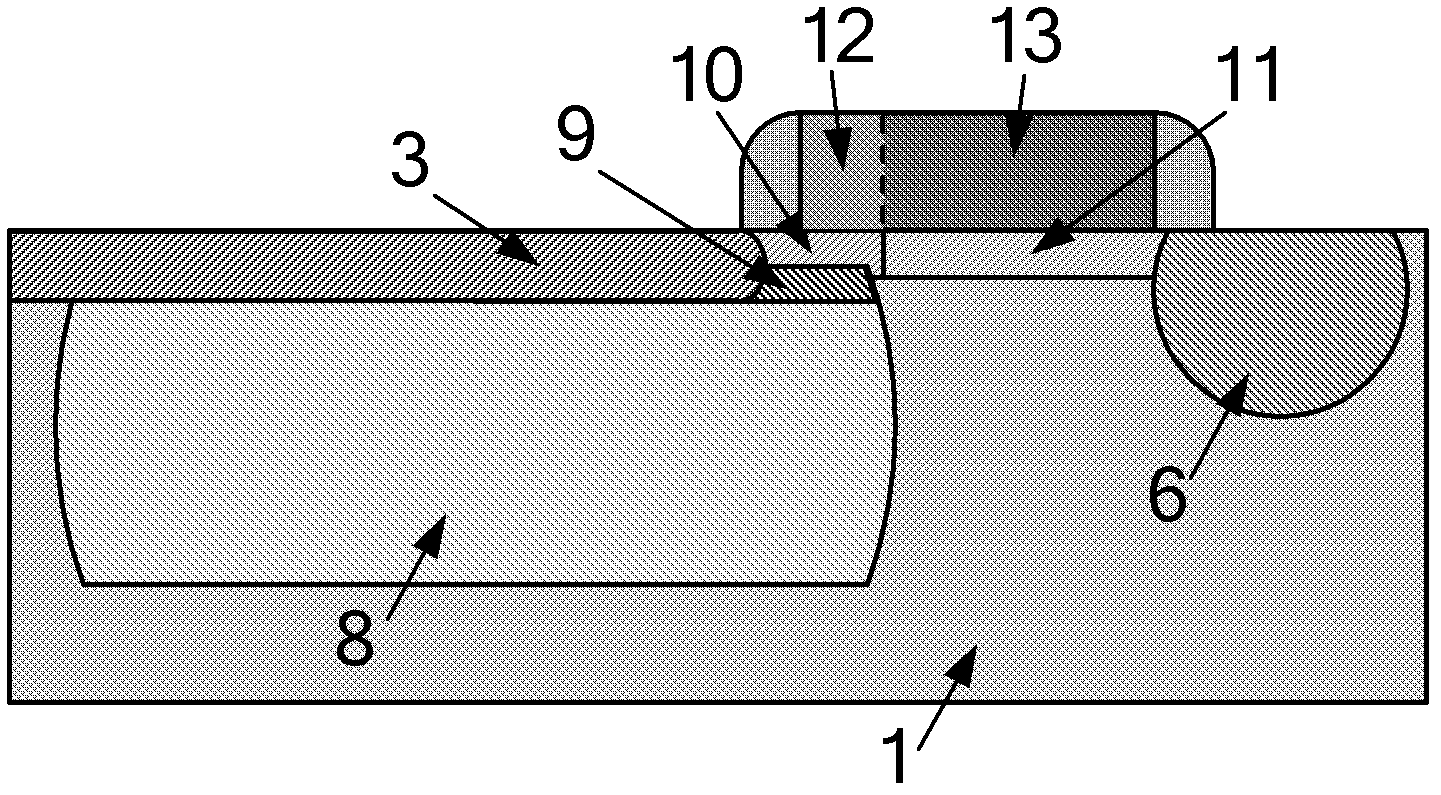

Releasable Delivery System

Implant engagement mechanisms are disclosed for maintaining engagement with a stent until it has been fully deployed and expanded from a catheter or sheath. The apparatus, method and system involving these engagement mechanisms allow a physician to withdraw or retract a sheath prior to full deployment, thereby allowing for redeployment of the stent at a more desirable position.

Owner:MICROVENTION INC

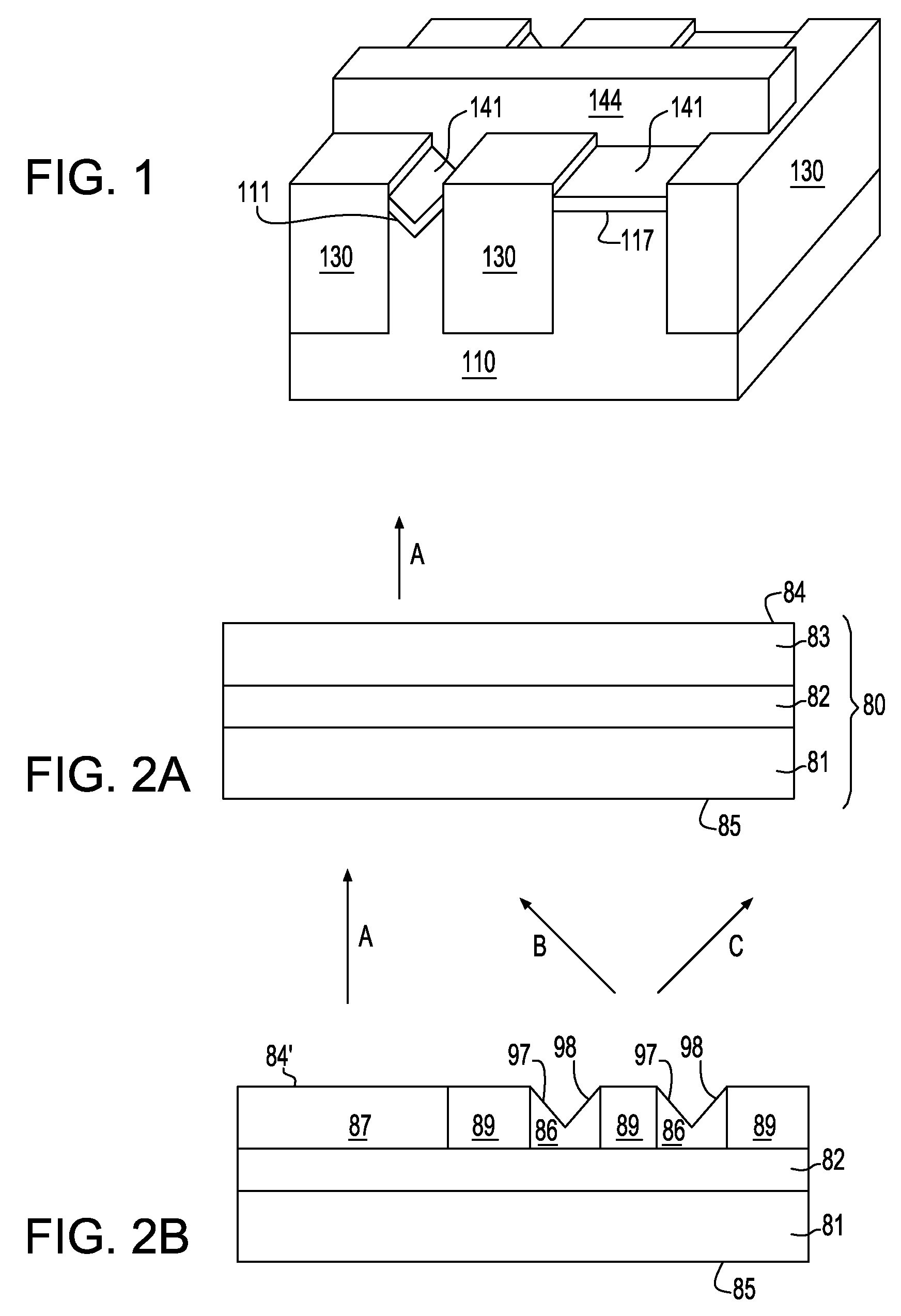

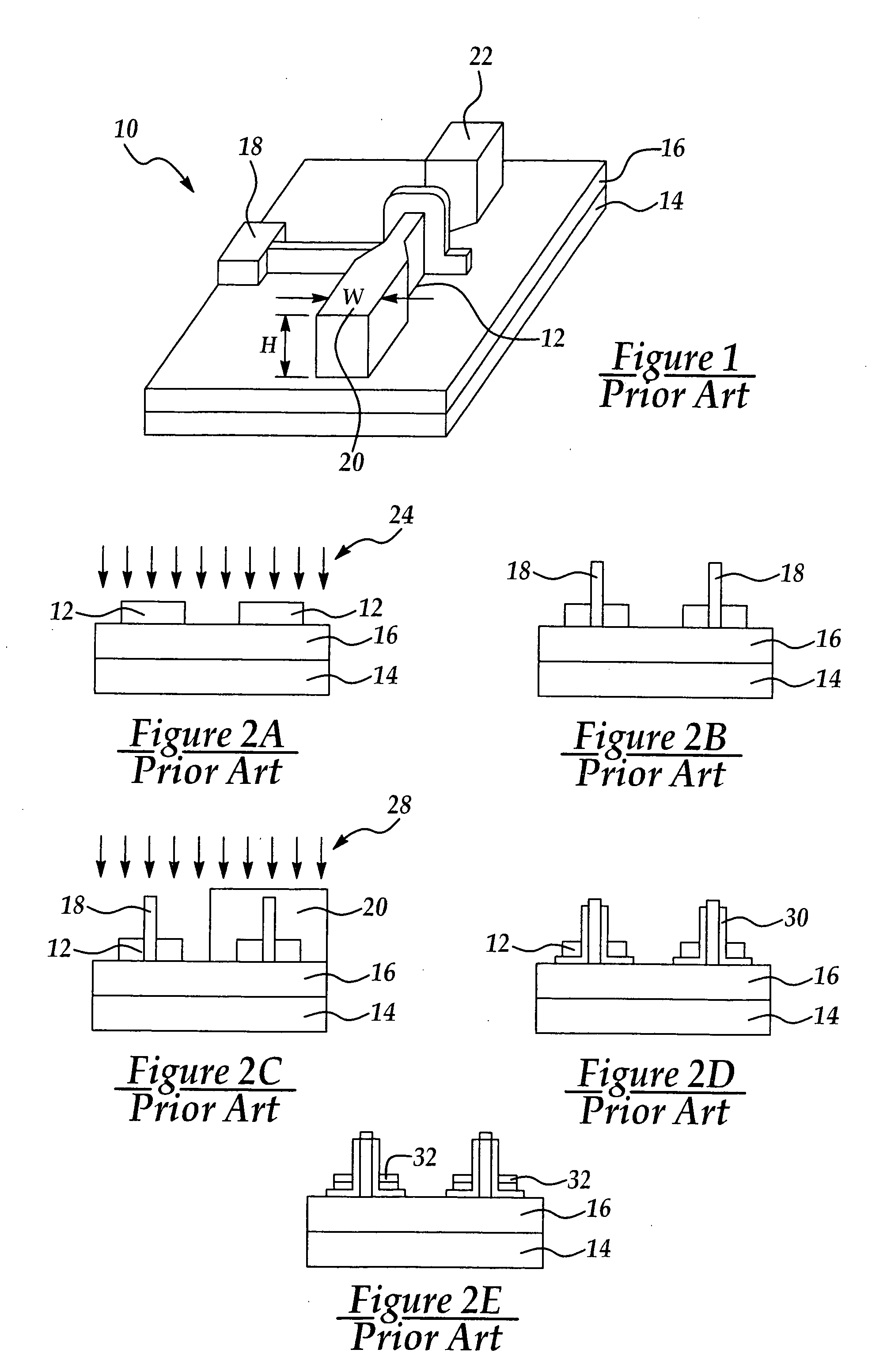

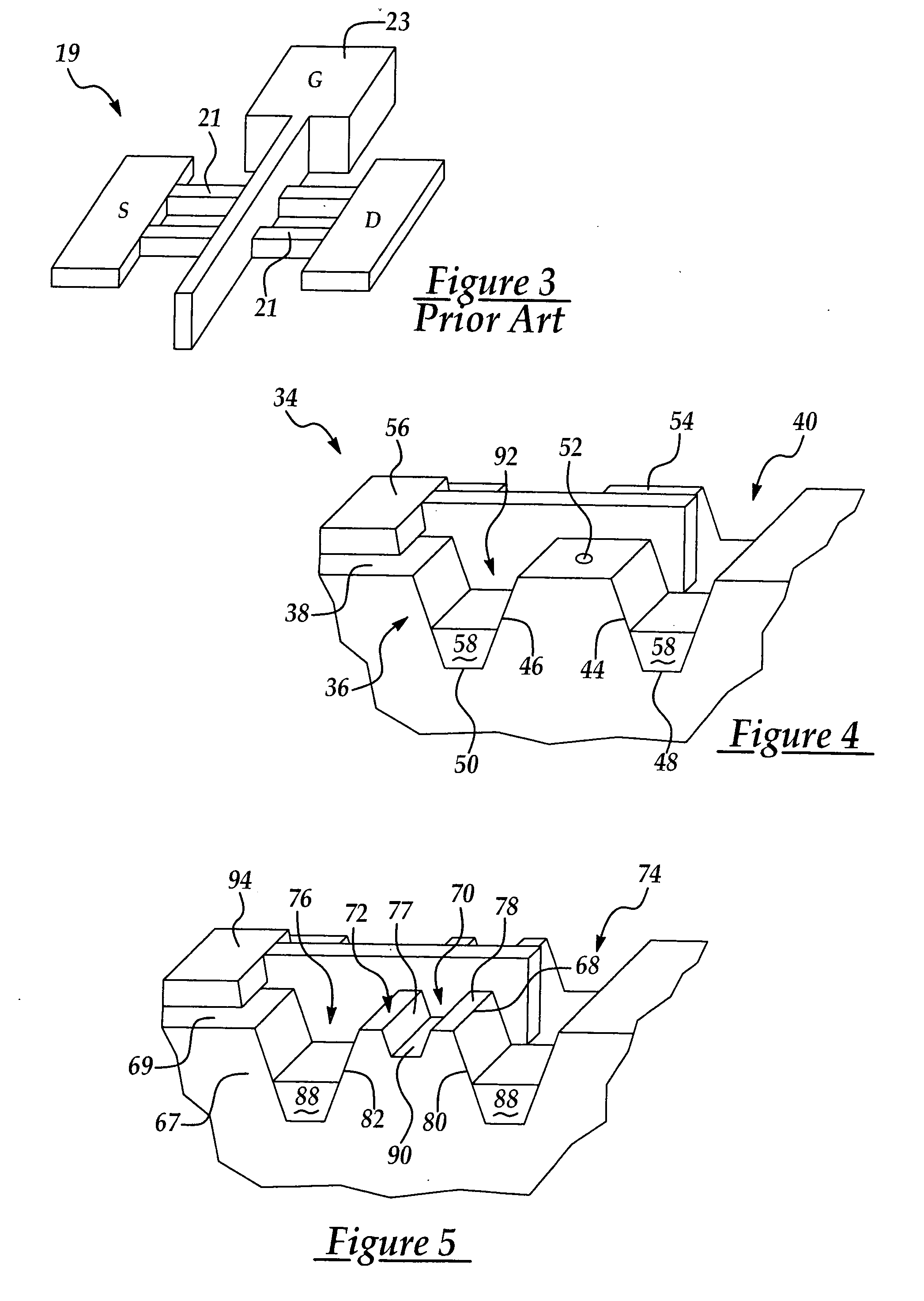

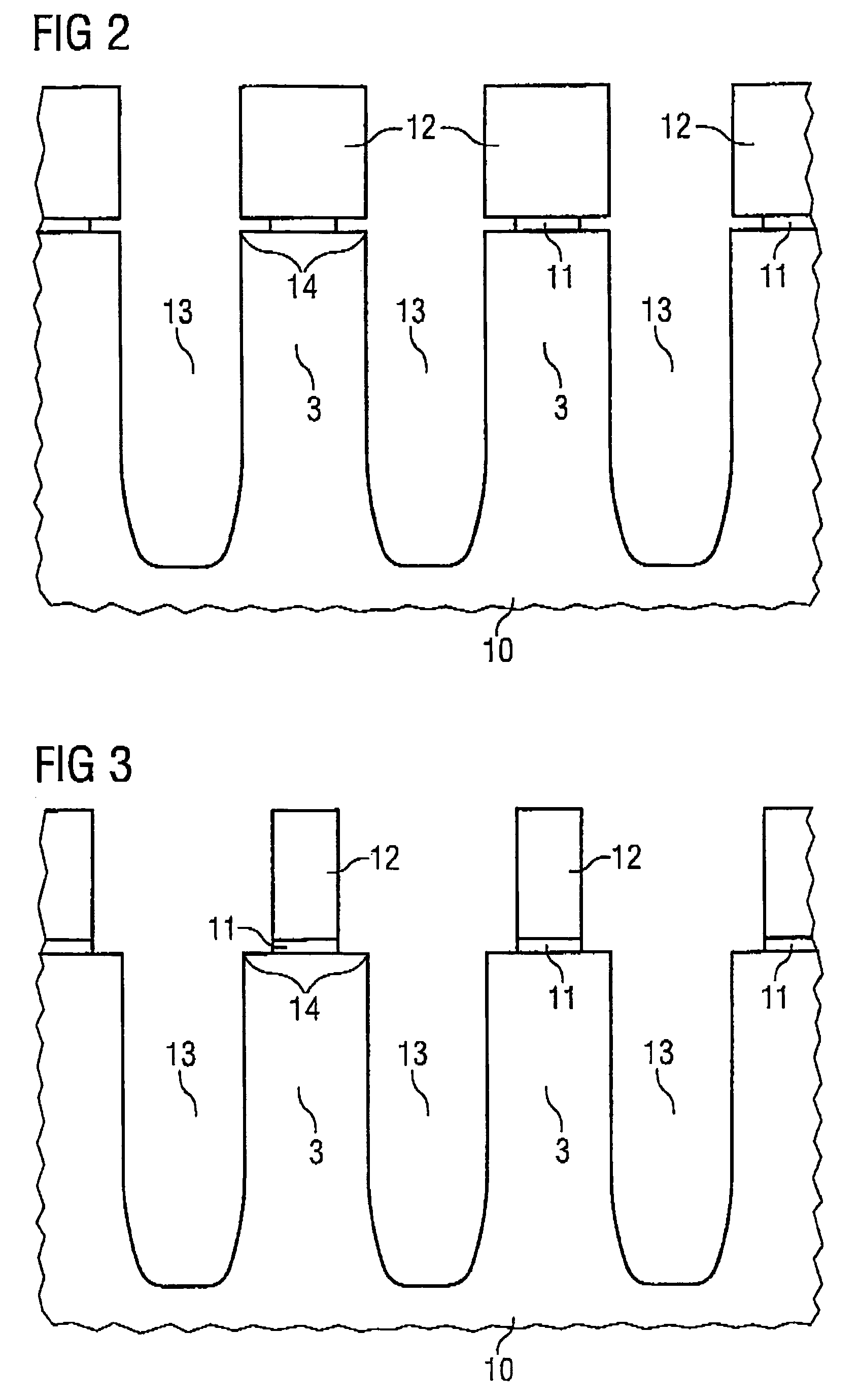

Enhanced mobility CMOS transistors with a v-shaped channel with self-alignment to shallow trench isolation

InactiveUS20080173906A1Improve performanceIncrease the on-currentTransistorSolid-state devicesCMOSCharge carrier mobility

The present invention provides structures and methods for a transistor formed on a V-shaped groove. The V-shaped groove contains two crystallographic facets joined by a ridge. The facets have different crystallographic orientations than what a semiconductor substrate normally provides such as the substrate orientation or orientations orthogonal to the substrate orientation. Unlike the prior art, the V-shaped groove is formed self-aligned to the shallow trench isolation, eliminating the need to precisely align the V-shaped grooves with lithographic means. The electrical properties of the new facets, specifically, the enhanced carrier mobility, are utilized to enhance the performance of transistors. In a transistor with a channel on the facets that are joined to form a V-shaped profile, the current flows in the direction of the ridge joining the facets avoiding any inflection in the direction of the current.

Owner:GLOBALFOUNDRIES INC

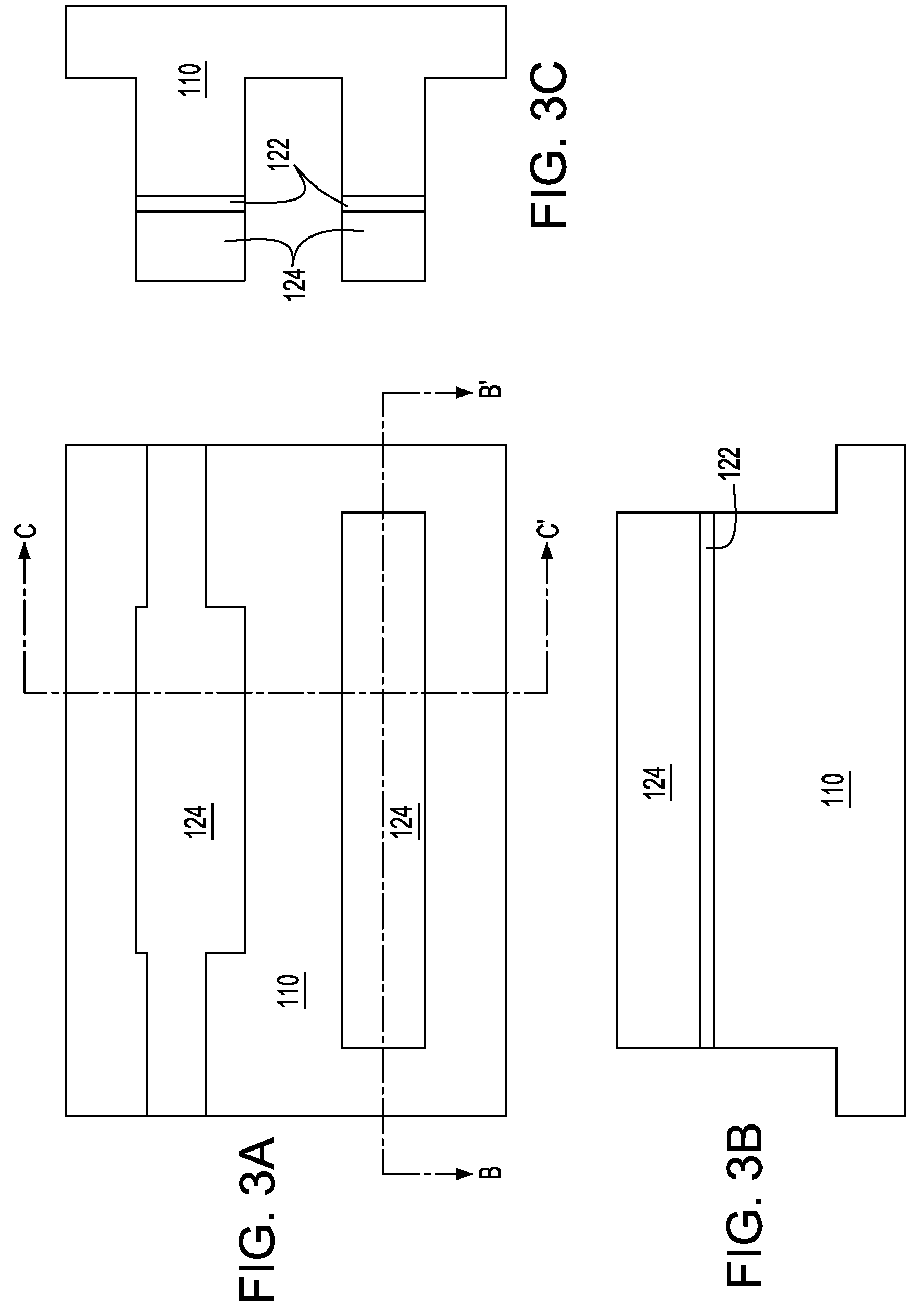

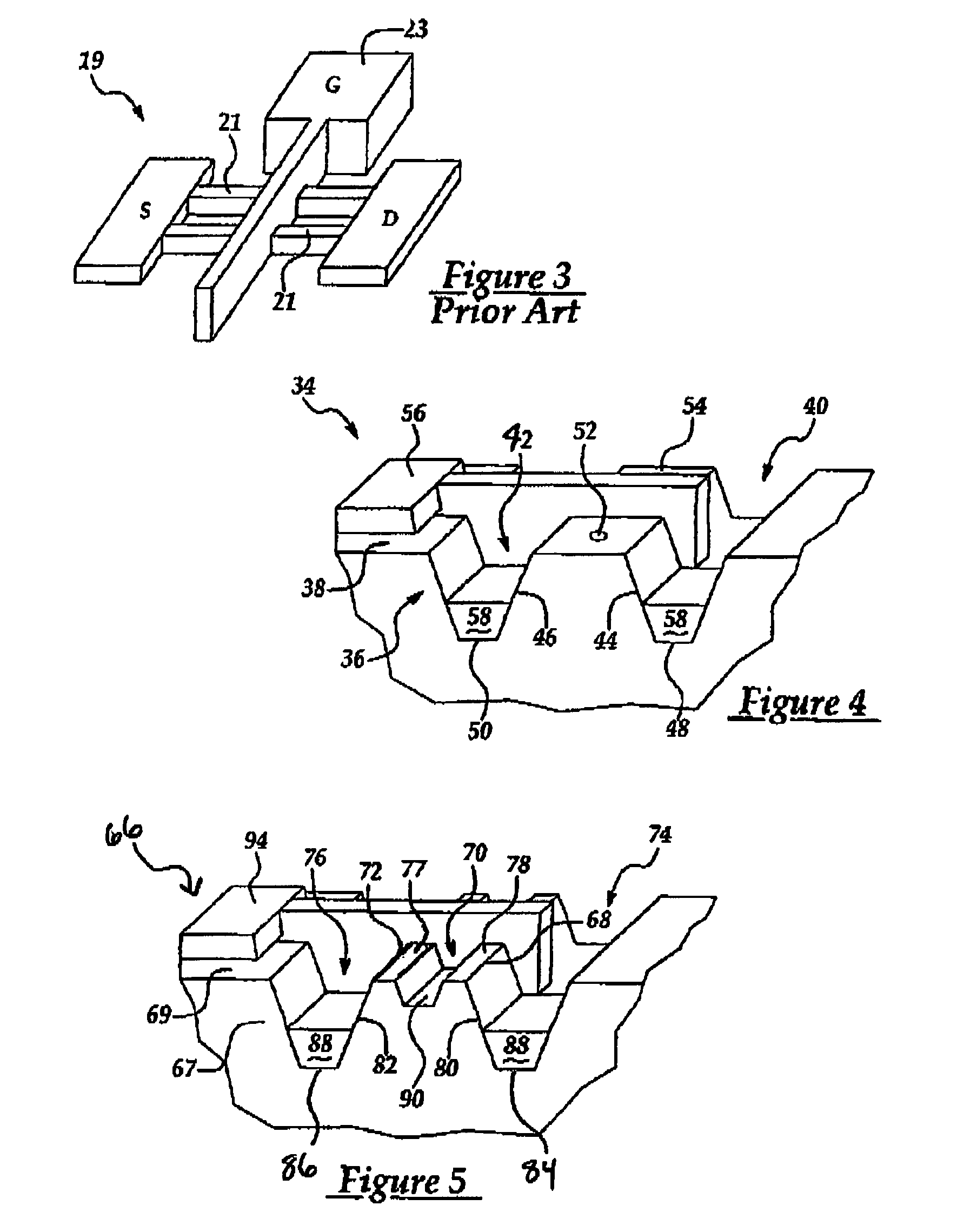

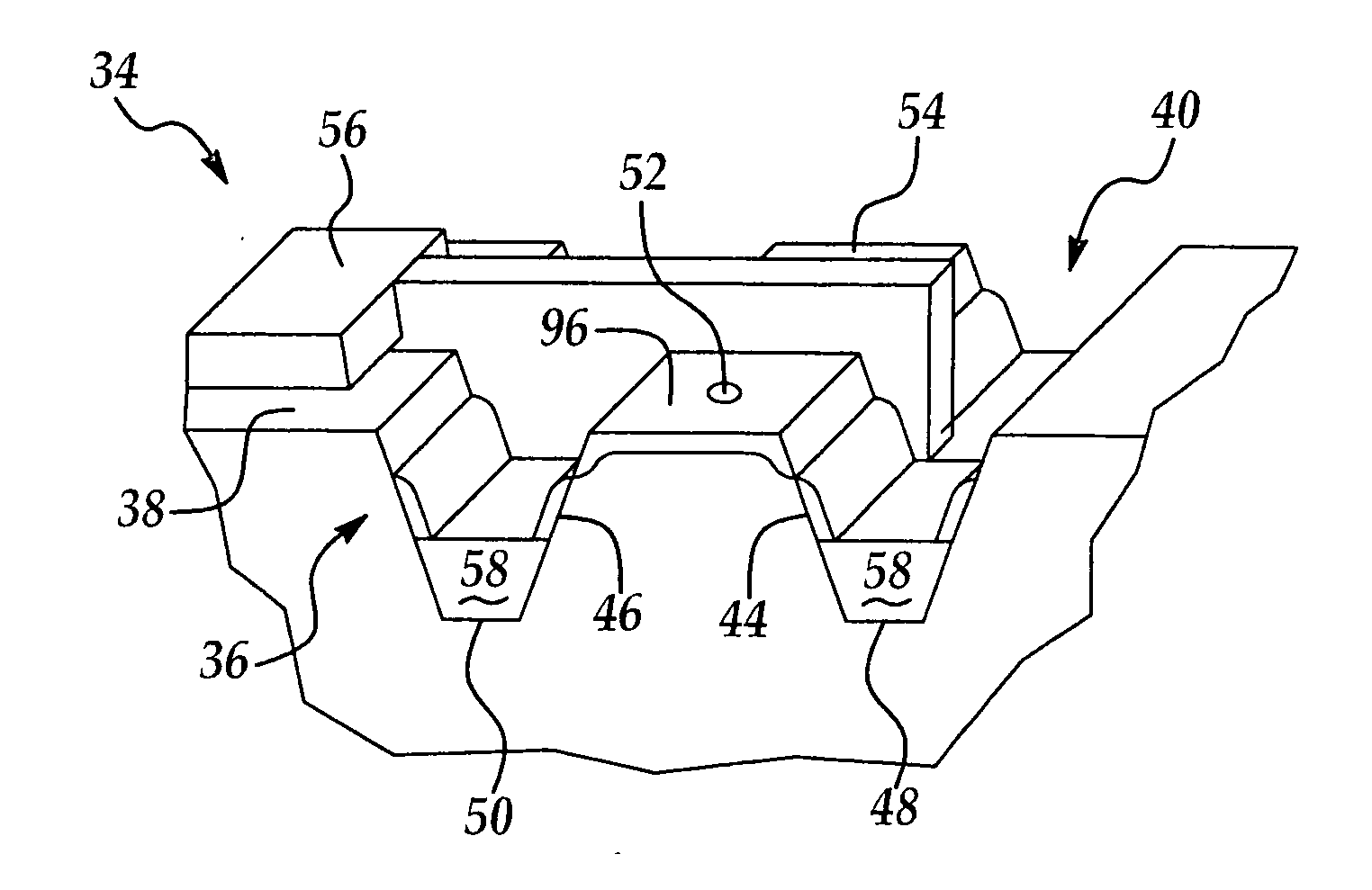

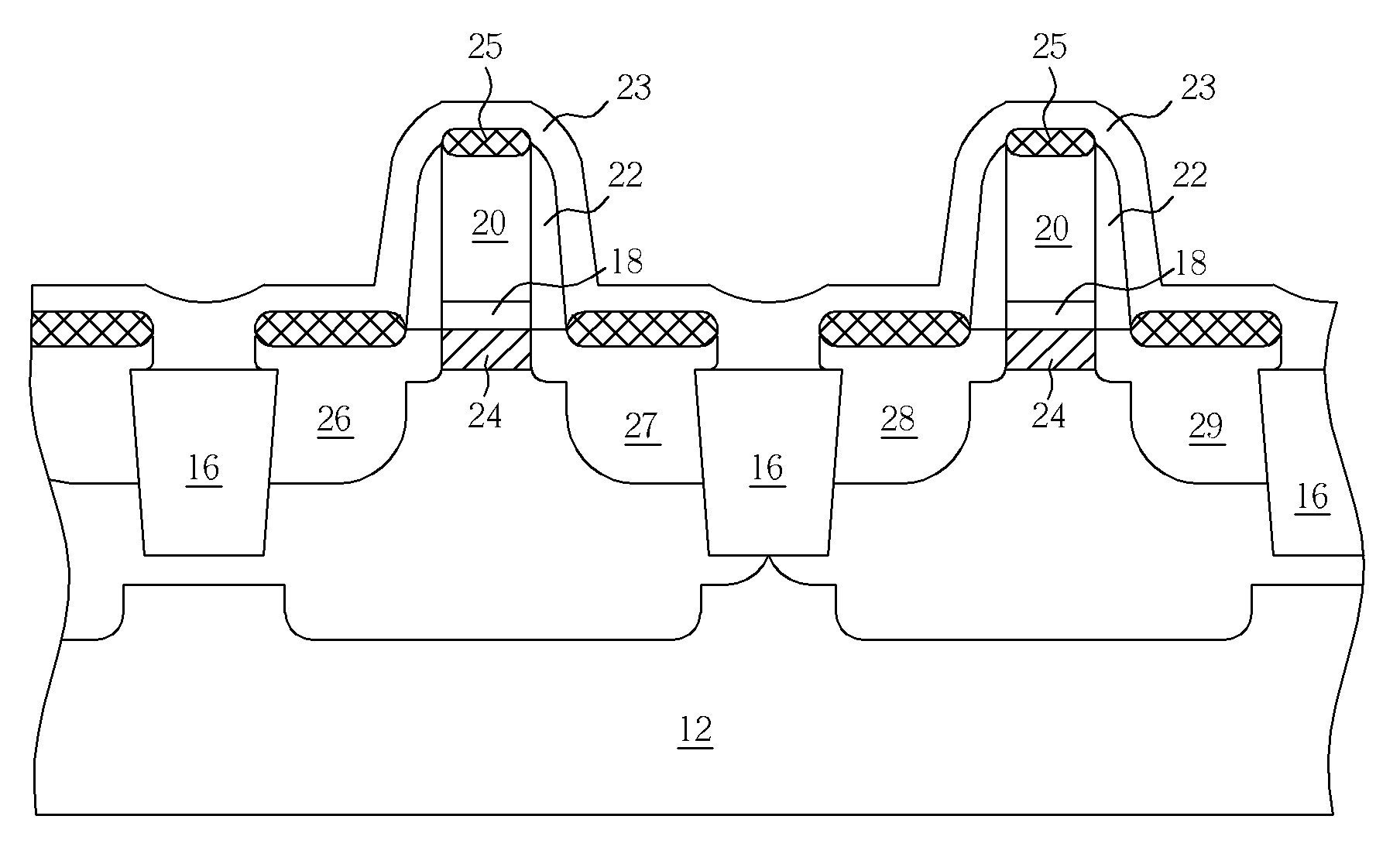

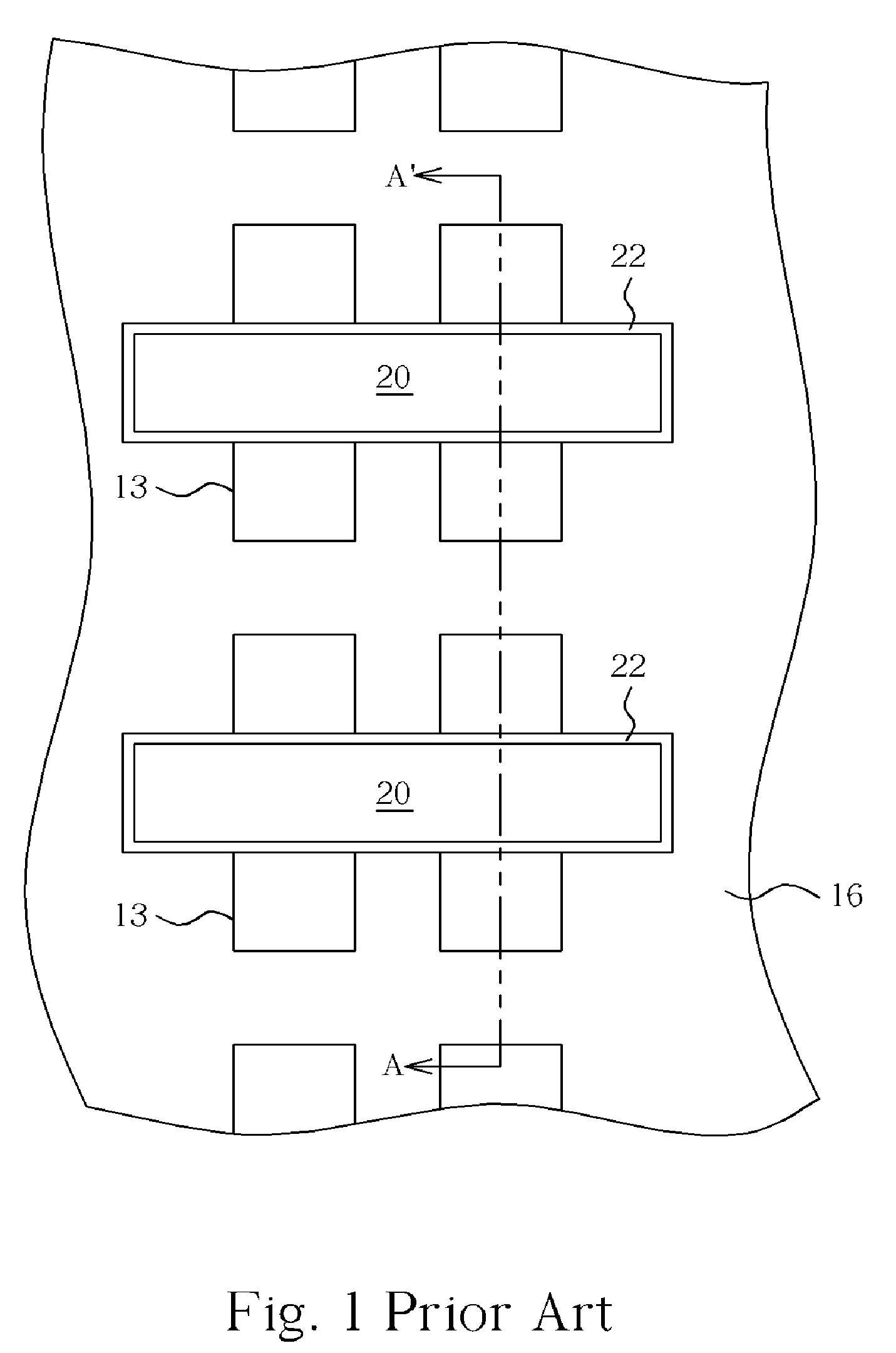

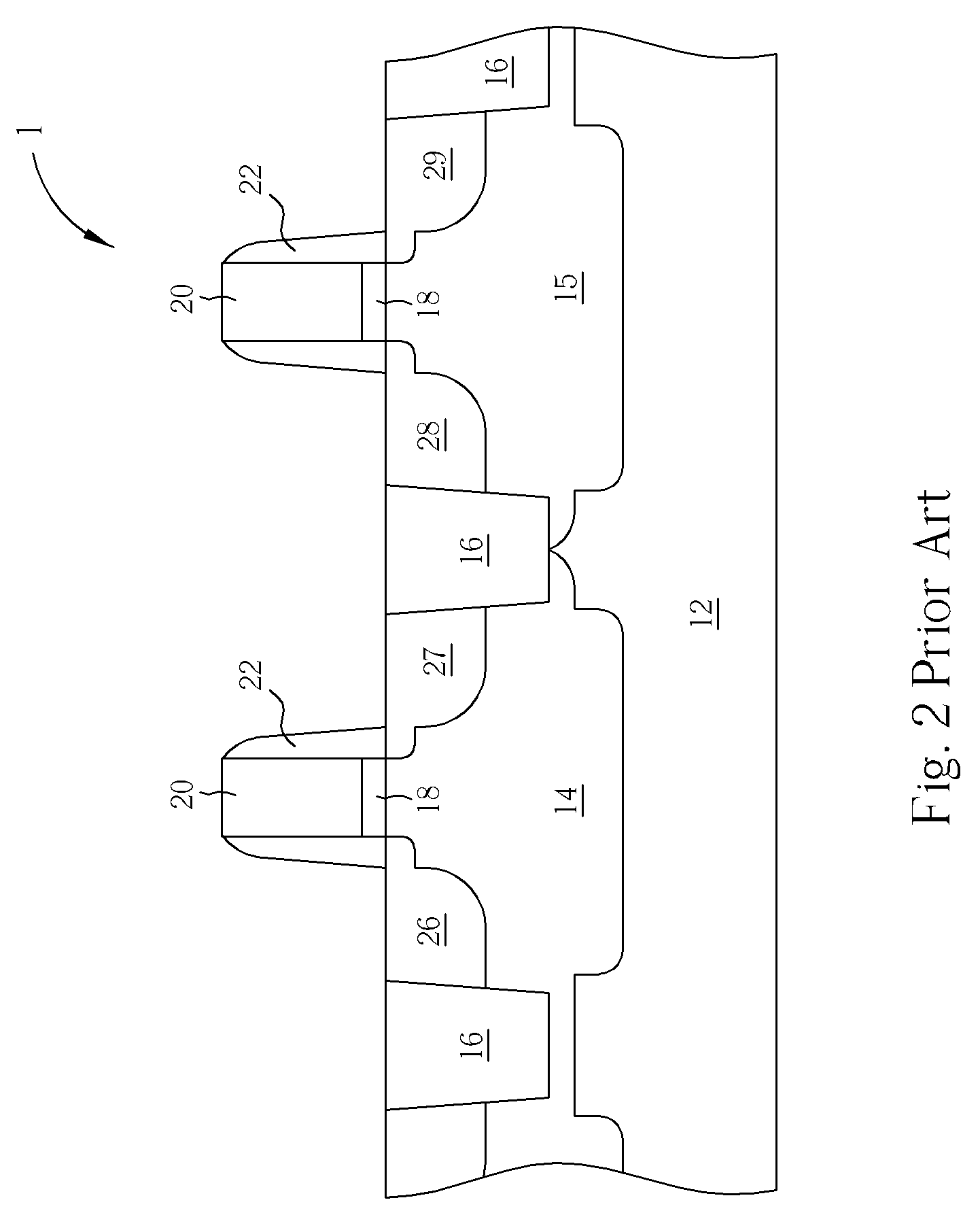

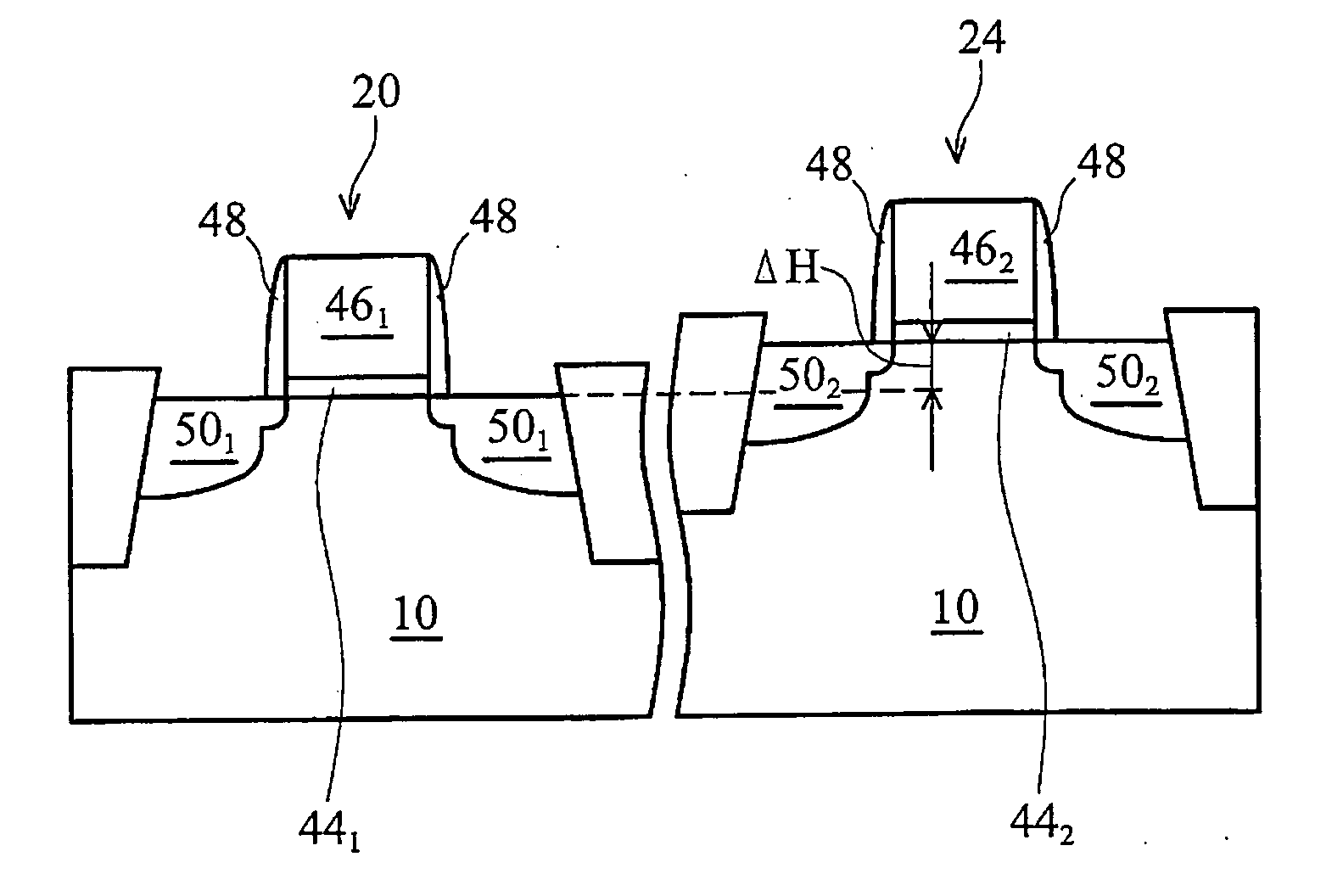

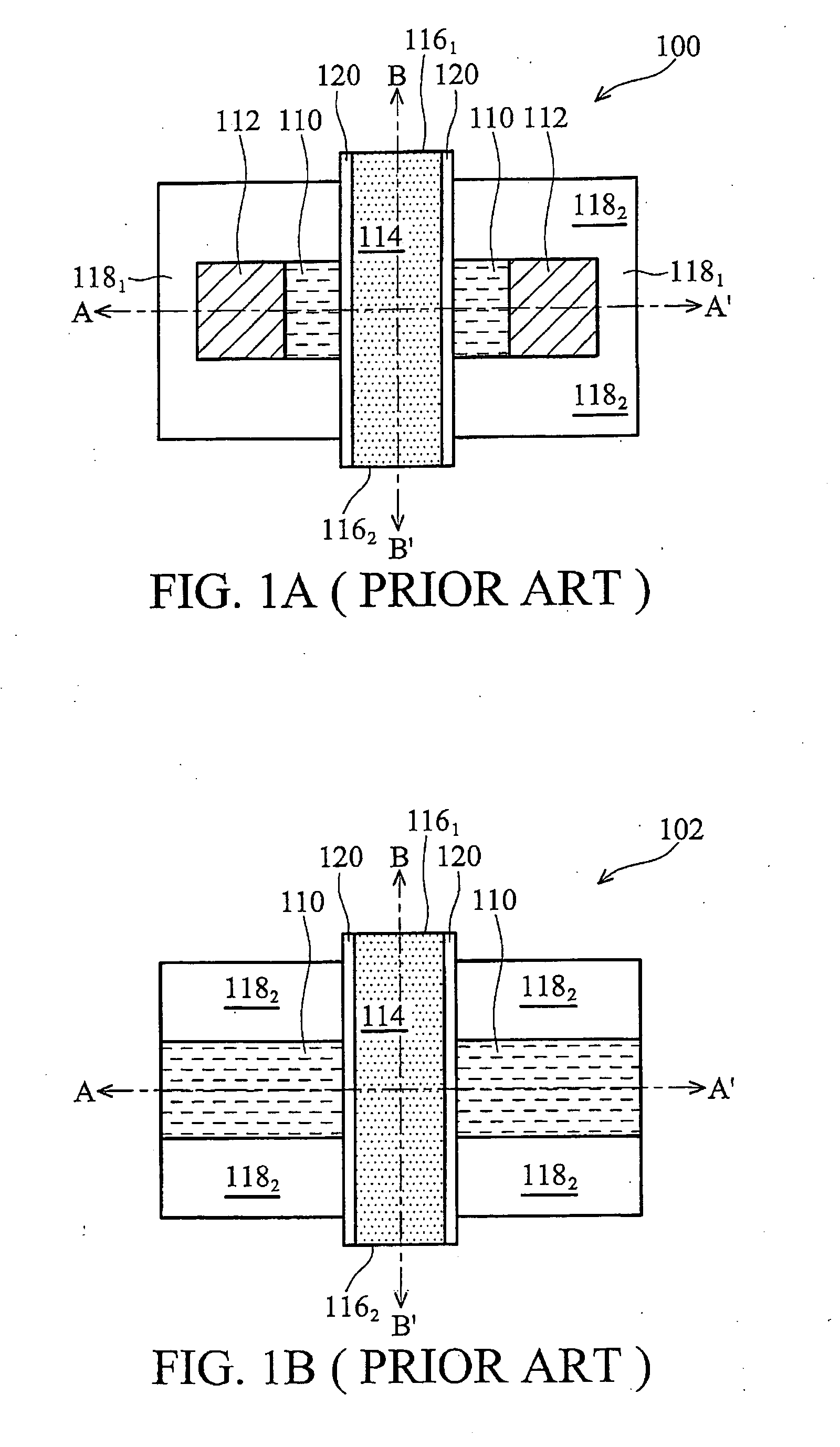

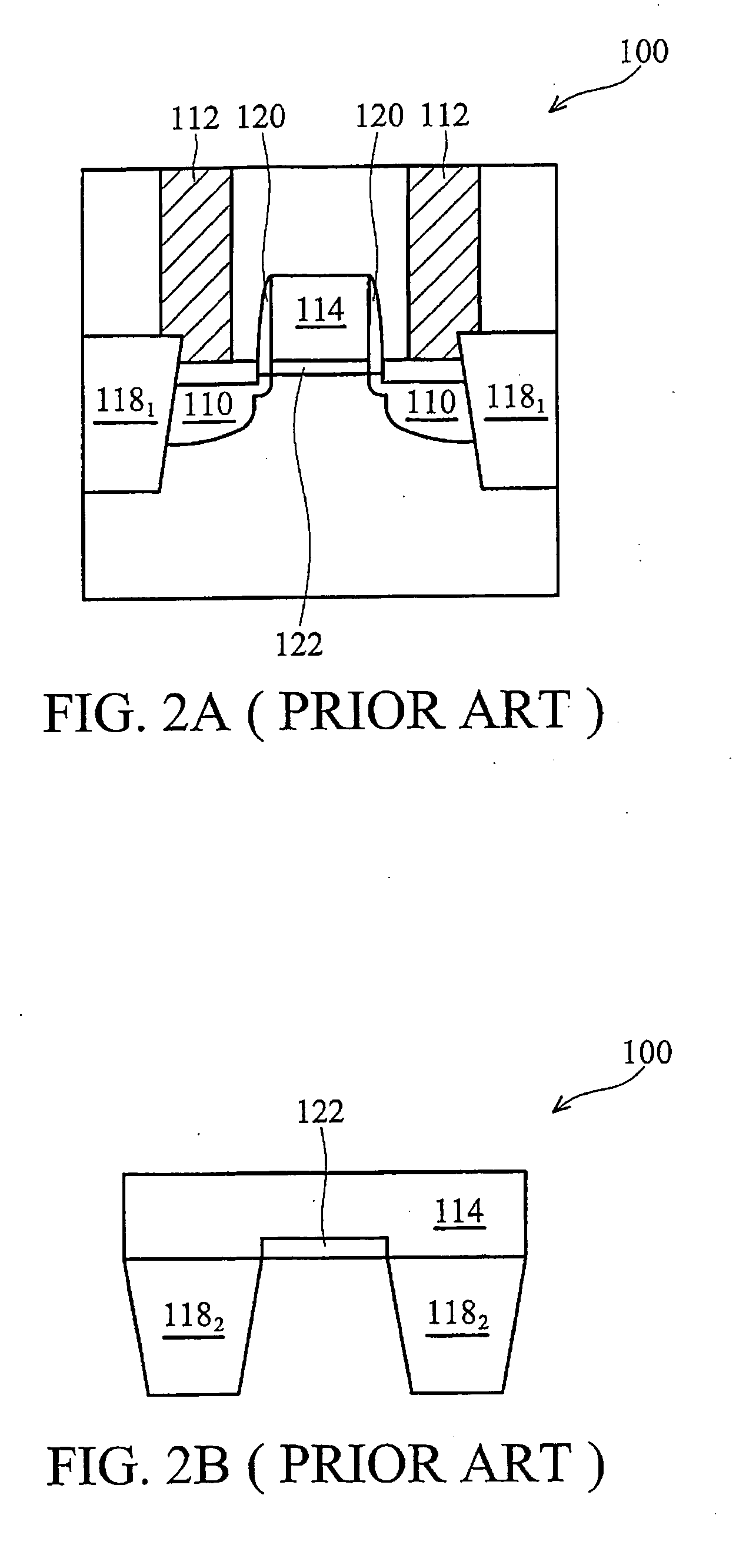

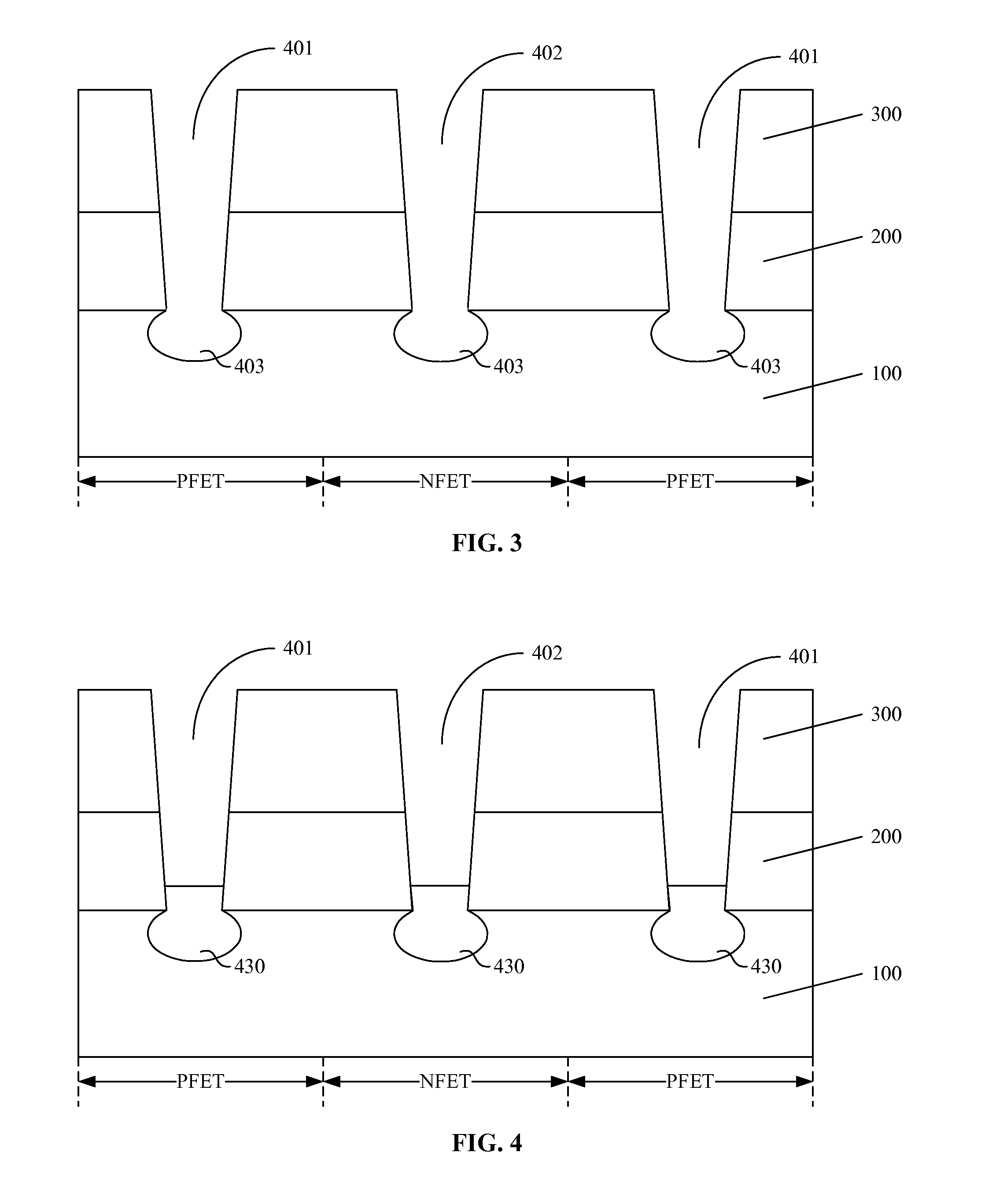

Quasi-plannar and FinFET-like transistors on bulk silicon

The types of quasi-planar CMOS and FinFET-like transistor devices on a bulk silicon substrate are disclosed. A first device has a doped and recessed channel formed in a shallow trench sidewall. A second device has a doped, recessed channel and has a plurality of edge-fins juxtaposed on an edge of an active region of the device. A third device has an undoped recessed channel formed in a sidewall of a shallow trench, wherein the undoped recessed channel further has a plurality of edge-fins disposed thereon. Additionally, an extra mask may be added to each device to allow for fabrication of both conventional transistors and FinFET-like transistors on bulk silicon. The extra mask may protect the source and drain areas from recess etching of the silicon substrate. Several methods of fabricating each device are also disclosed.

Owner:TAIWAN SEMICON MFG CO LTD

Quasi-plannar and FinFET-like transistors on bulk silicon

The types of quasi-planar CMOS and FinFET-like transistor devices on a bulk silicon substrate are disclosed. A first device has a doped and recessed channel formed in a shallow trench sidewall. A second device has a doped, recessed channel and has a plurality of edge-fins juxtaposed on an edge of an active region of the device. A third device has an undoped recessed channel formed in a sidewall of a shallow trench, wherein the undoped recessed channel further has a plurality of edge-fins disposed thereon. Additionally, an extra mask may be added to each device to allow for fabrication of both conventional transistors and FinFET-like transistors on bulk silicon. The extra mask may protect the source and drain areas from recess etching of the silicon substrate. Several methods of fabricating each device are also disclosed.

Owner:TAIWAN SEMICON MFG CO LTD

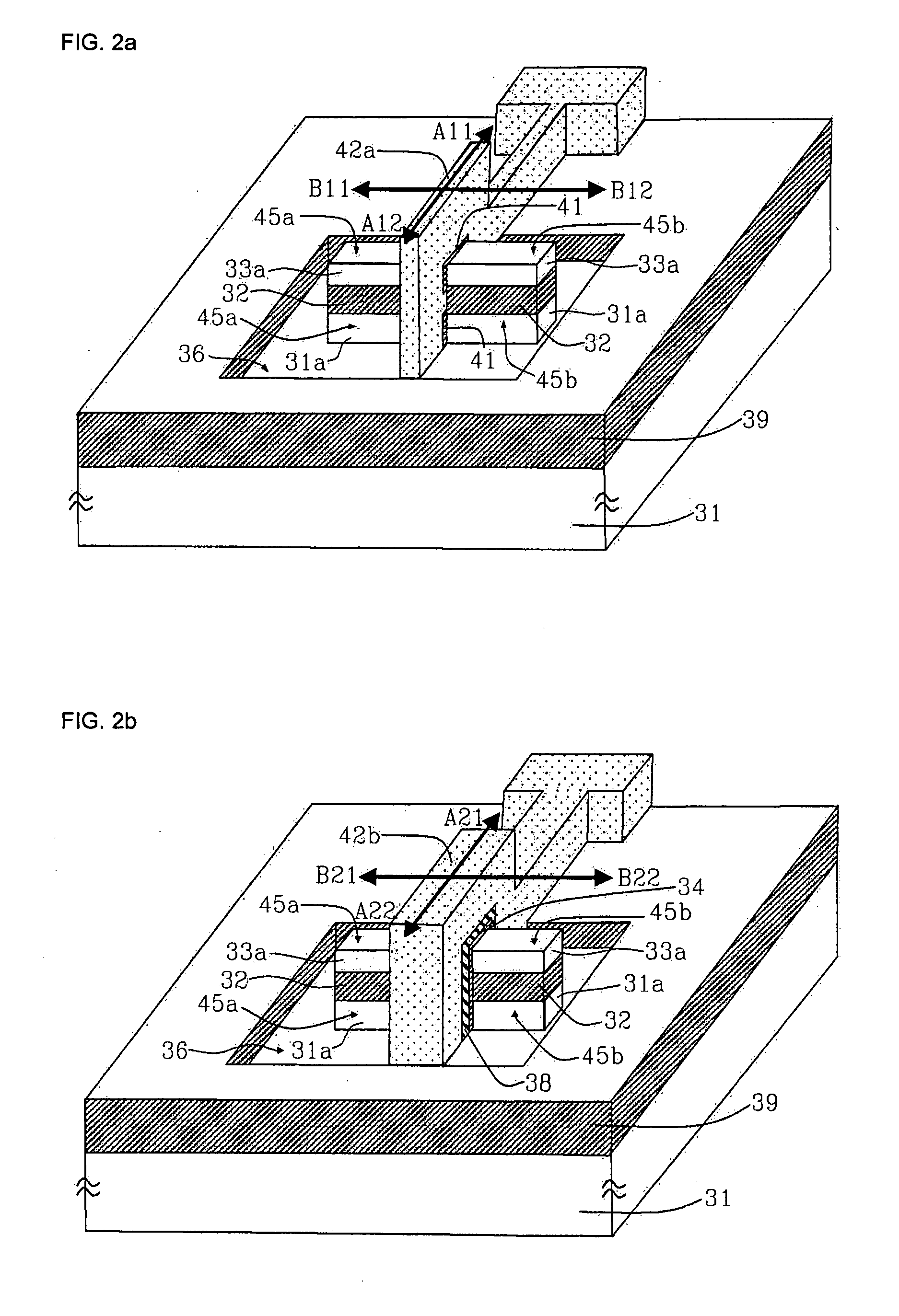

Multi-gate MOS transistor and method of manufacturing the same

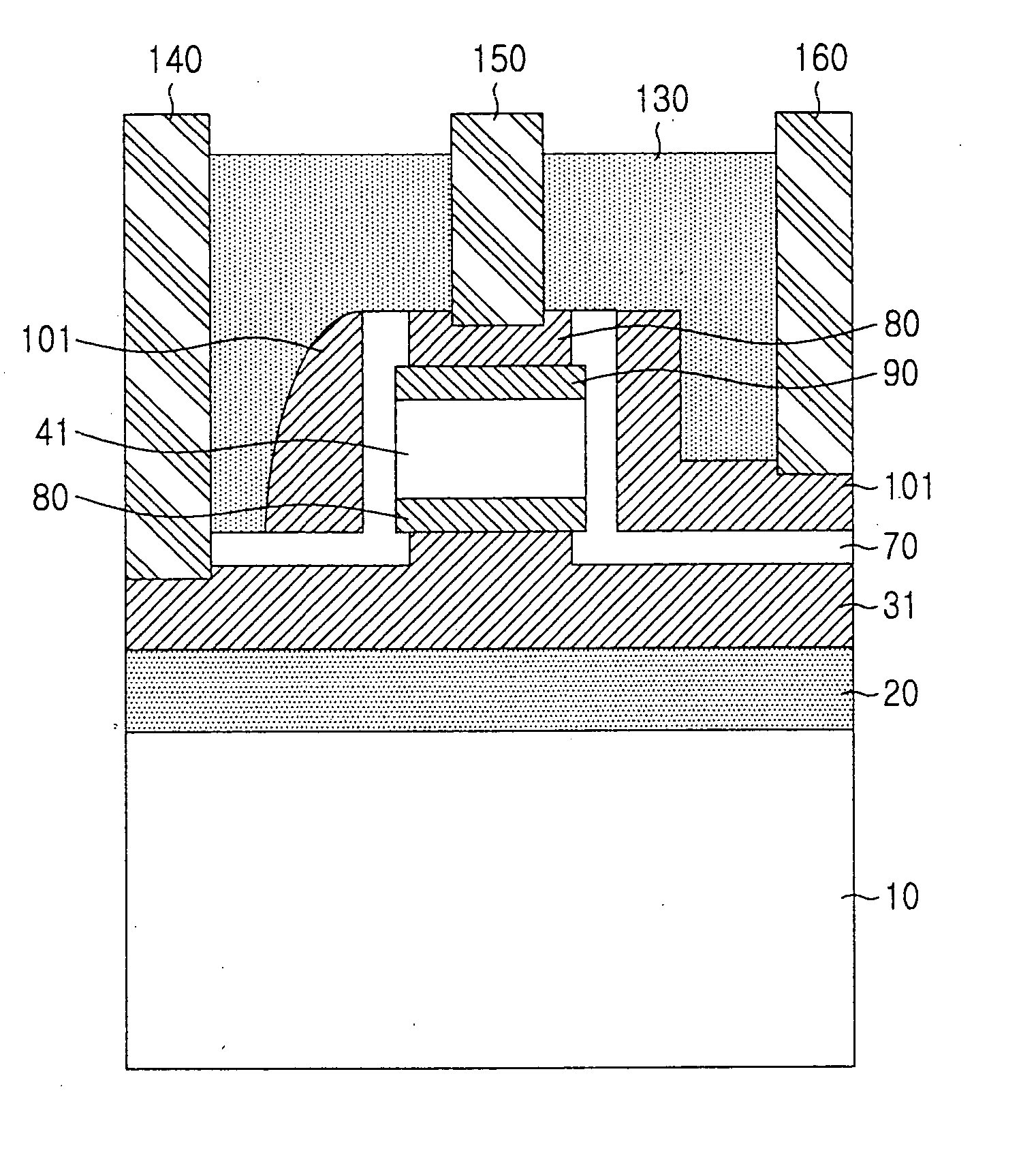

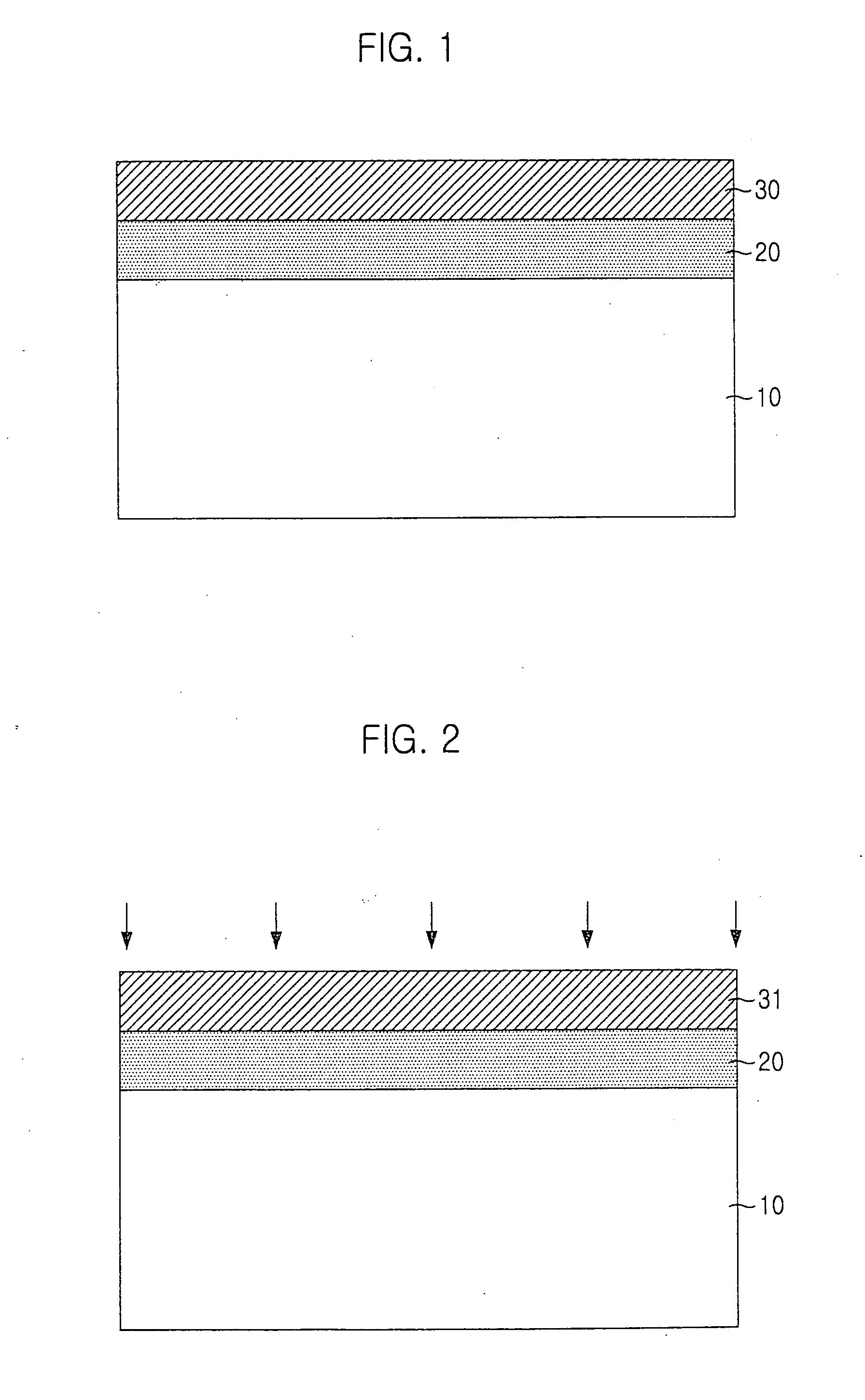

ActiveUS20050224880A1Drive capability can be improvedIncrease channel widthTransistorSolid-state devicesChannel widthSilicon on insulator

Provided are a multi-gate MOS transistor and a method of manufacturing the same. Two silicon fins are vertically stacked on a silicon on insulator (SOI) substrate, and four side surfaces of an upper silicon fin and three side surfaces of a lower silicon fin are used as a channel. Therefore, a channel width is increased, so that current driving capability of a device is improved, and high performance nano-level semiconductor IC and highly integrated memory IC can be manufactured through the optimization and stability of a process.

Owner:ELECTRONICS & TELECOMM RES INST

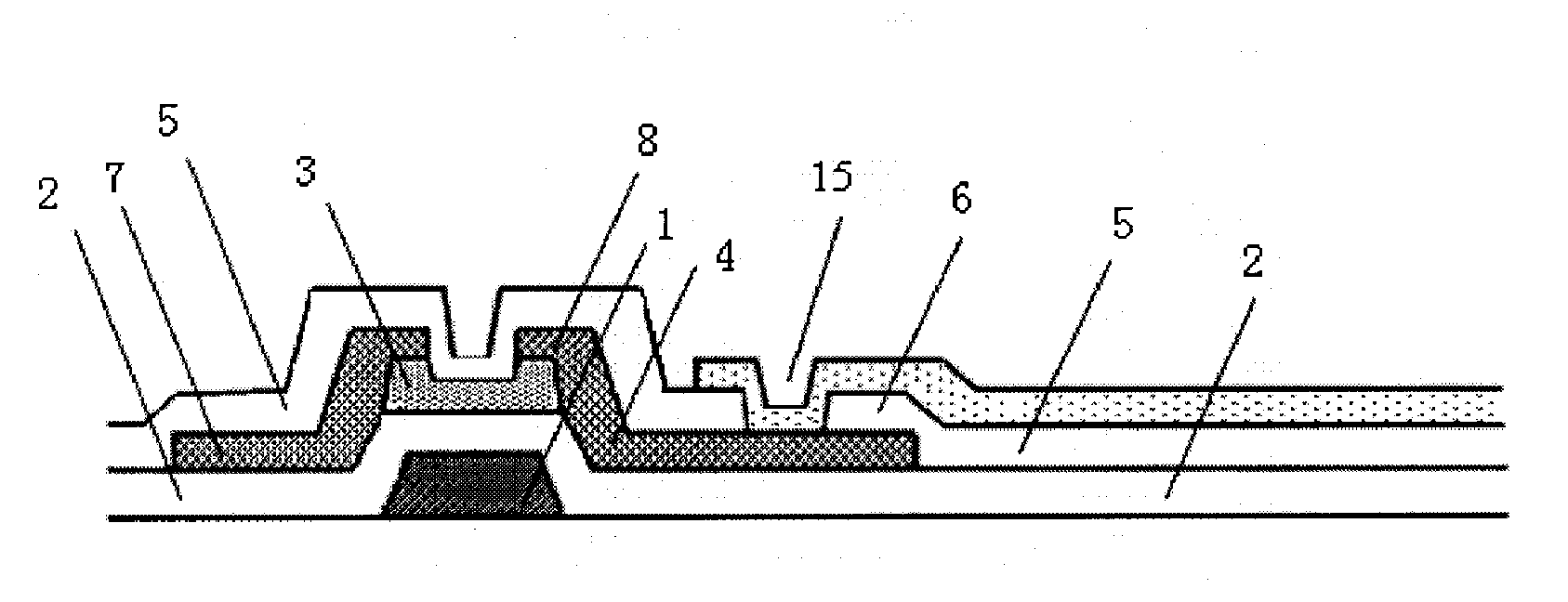

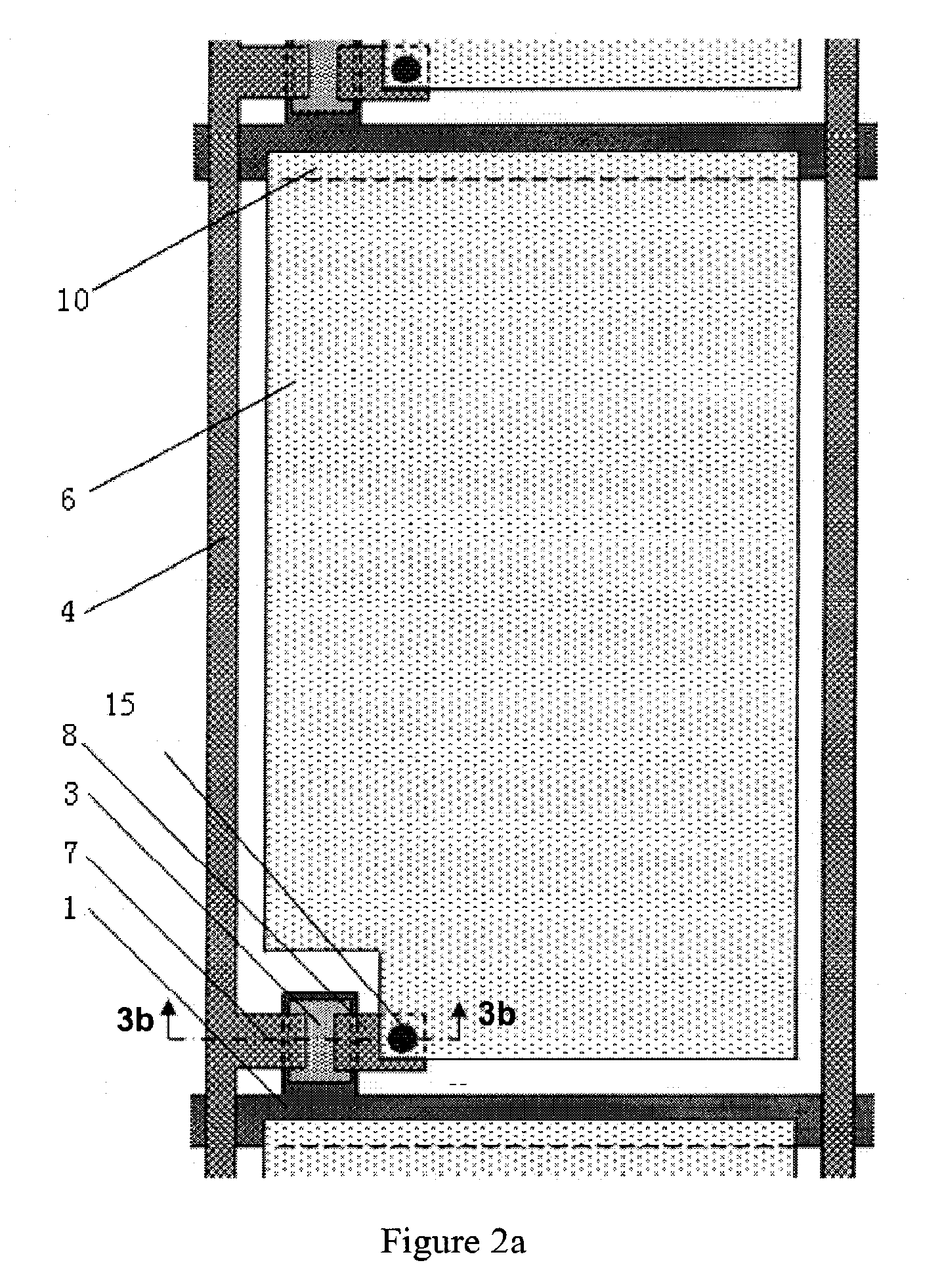

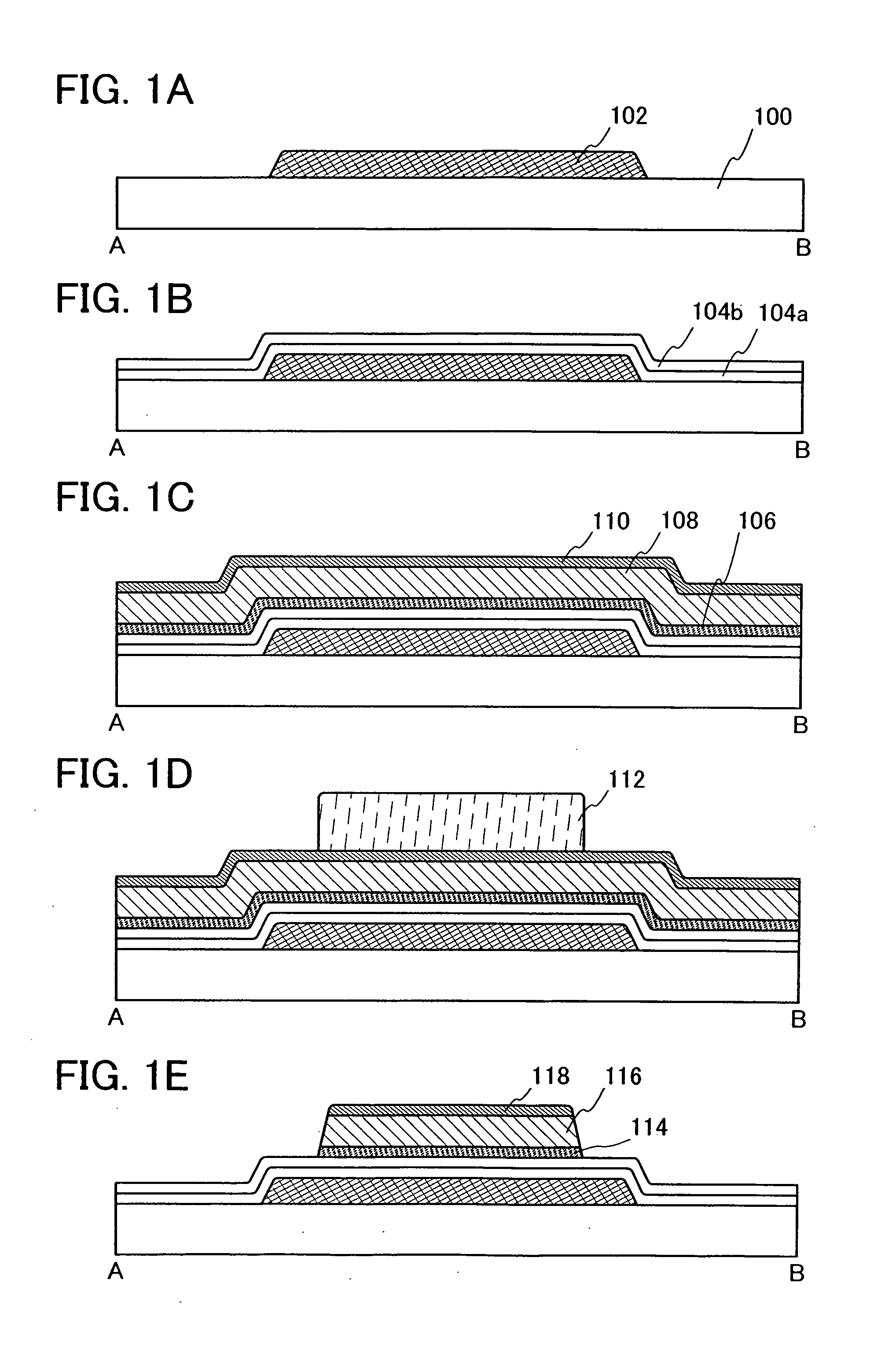

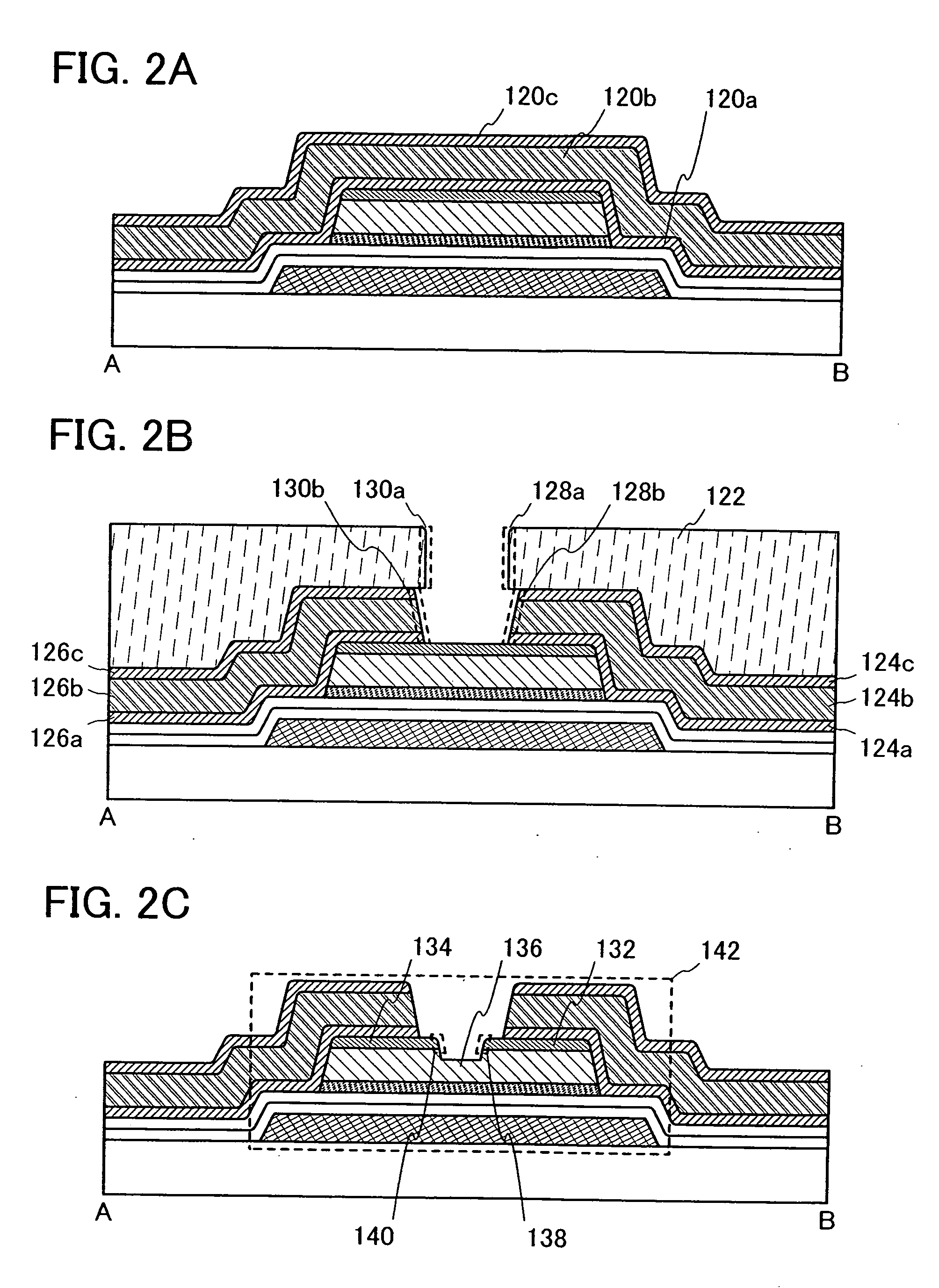

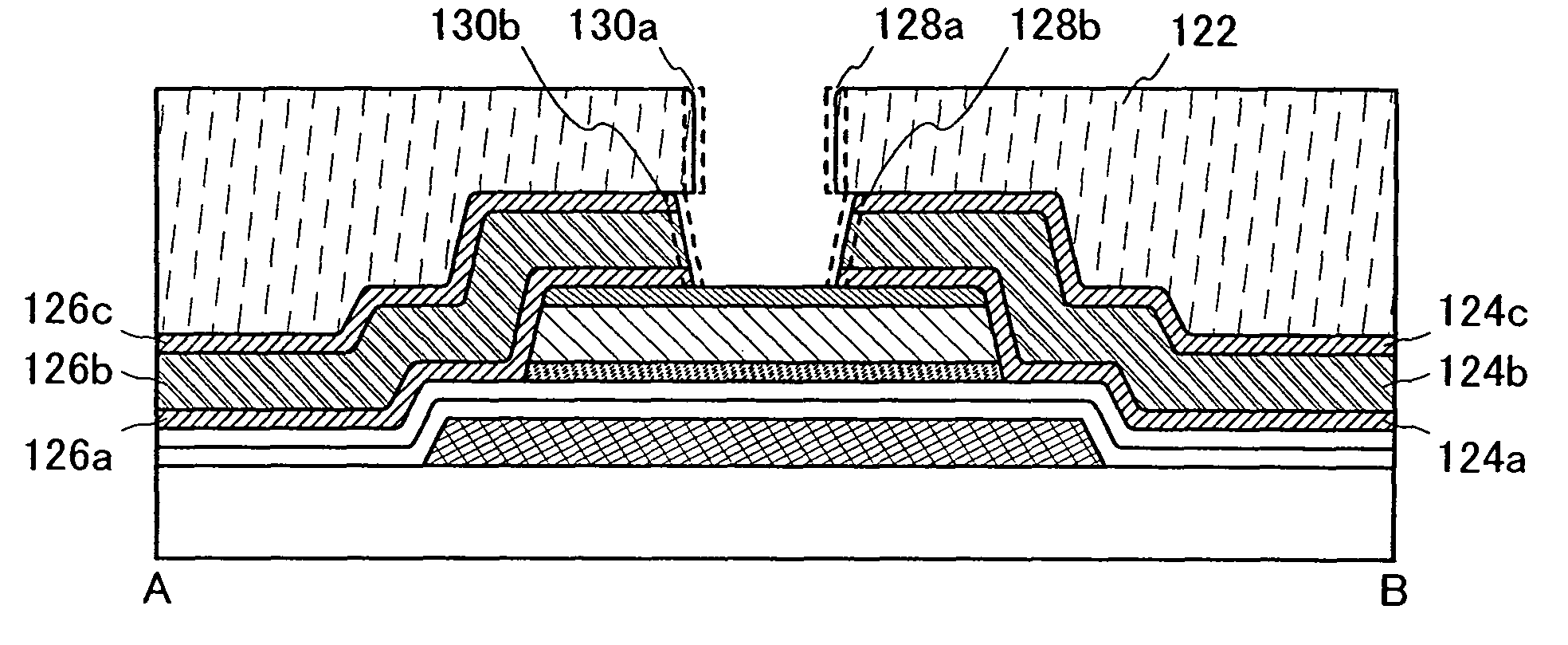

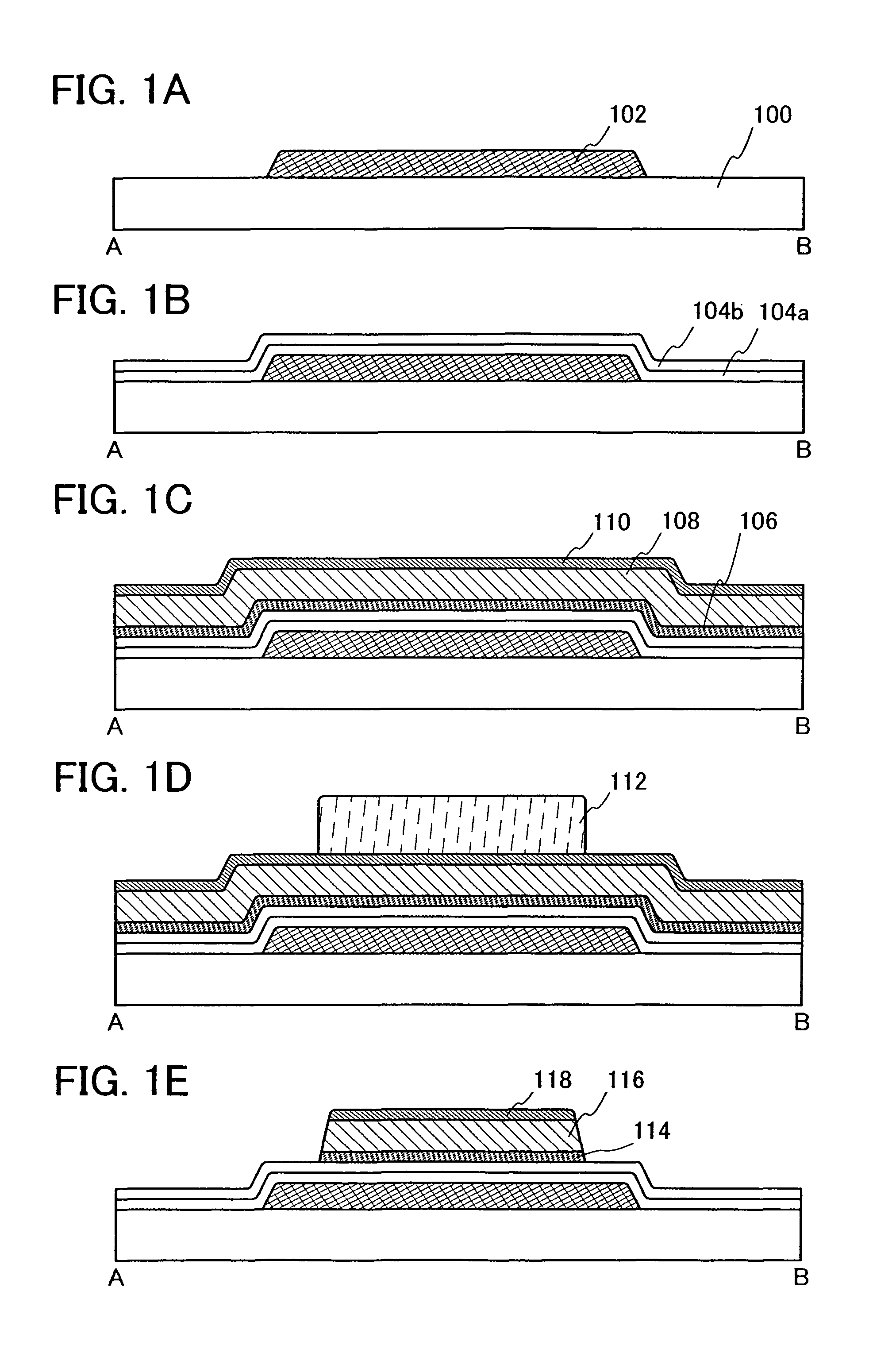

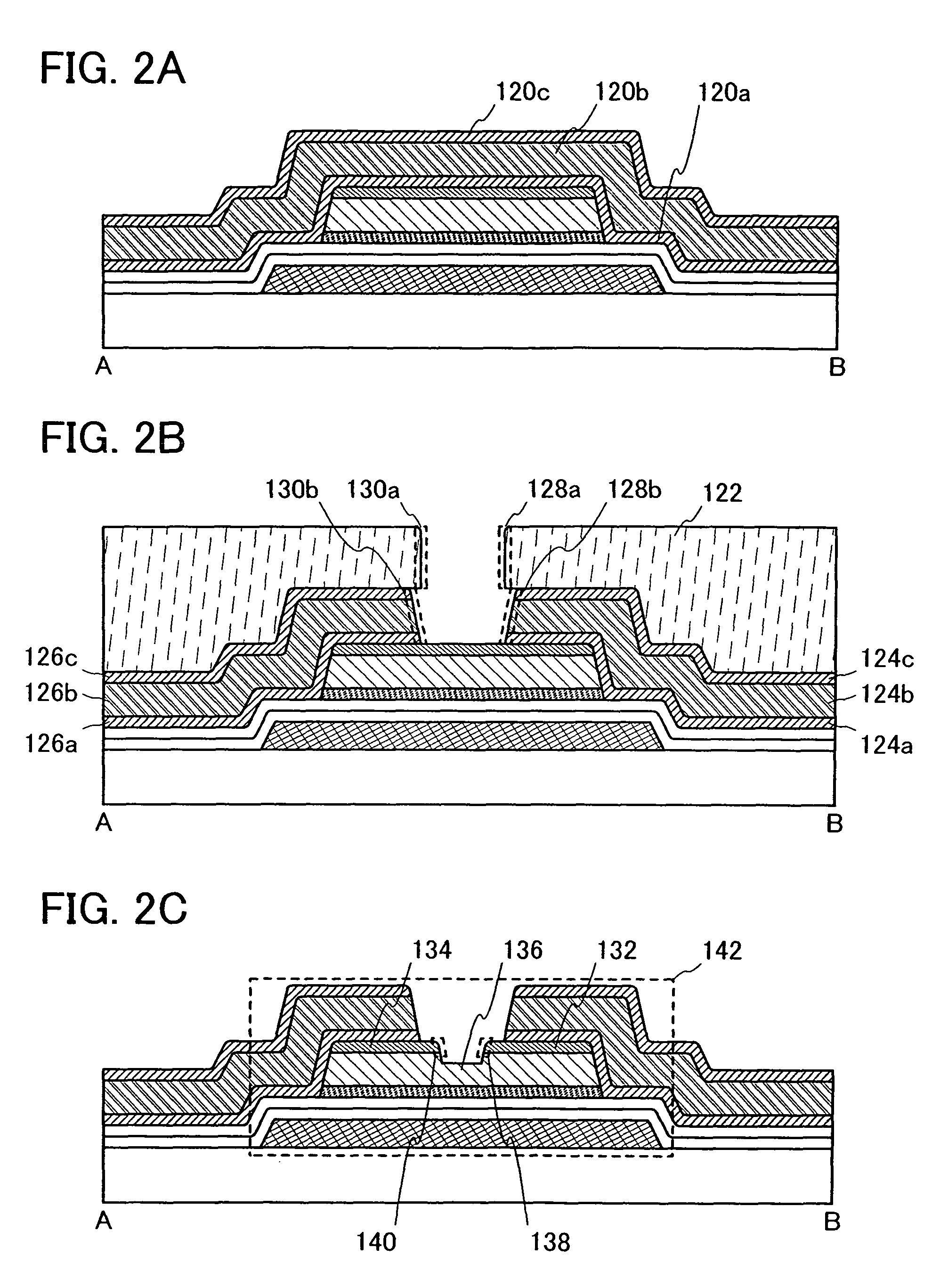

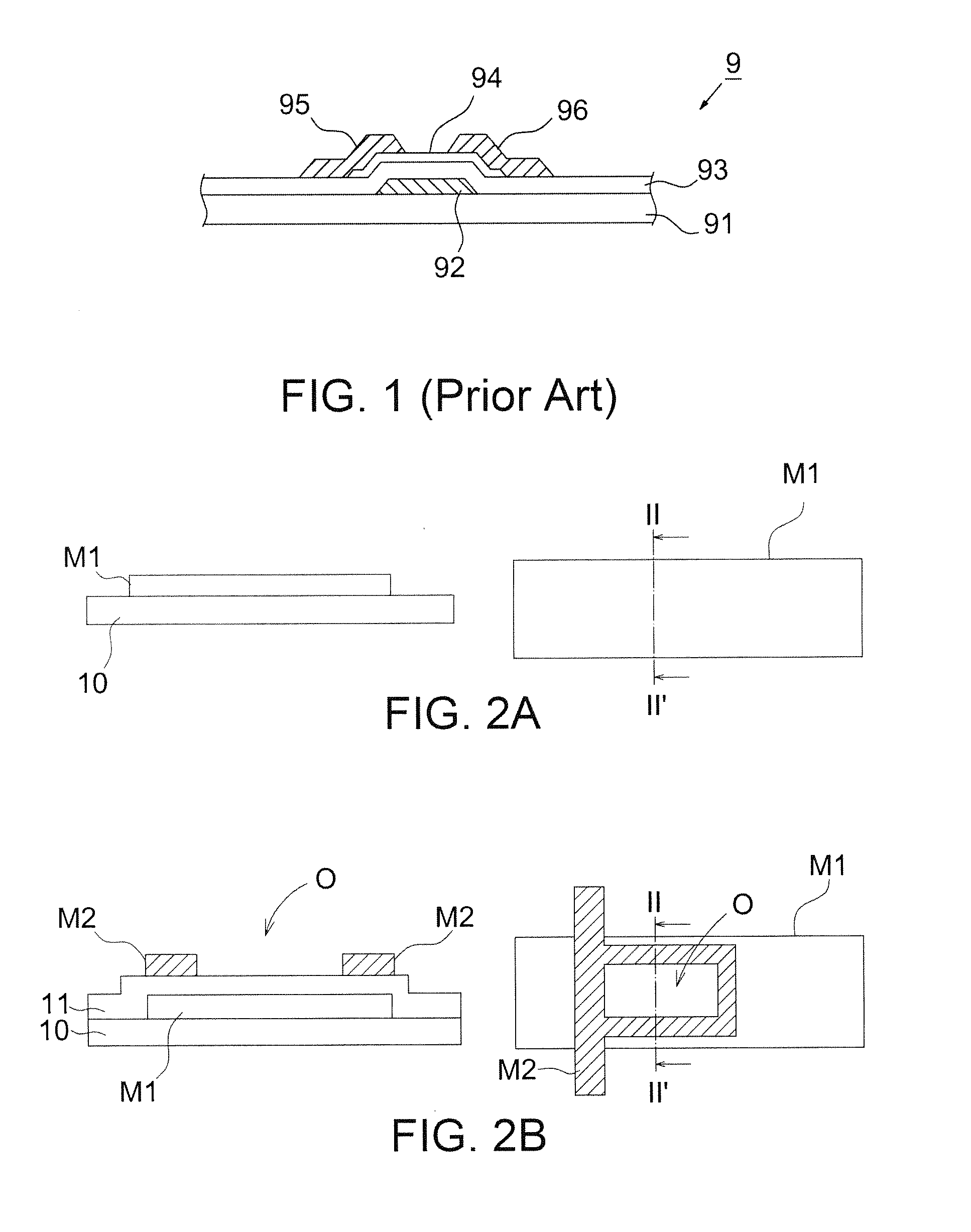

Thin film transistor, manufacturing method thereof, and TFT LCD using the same

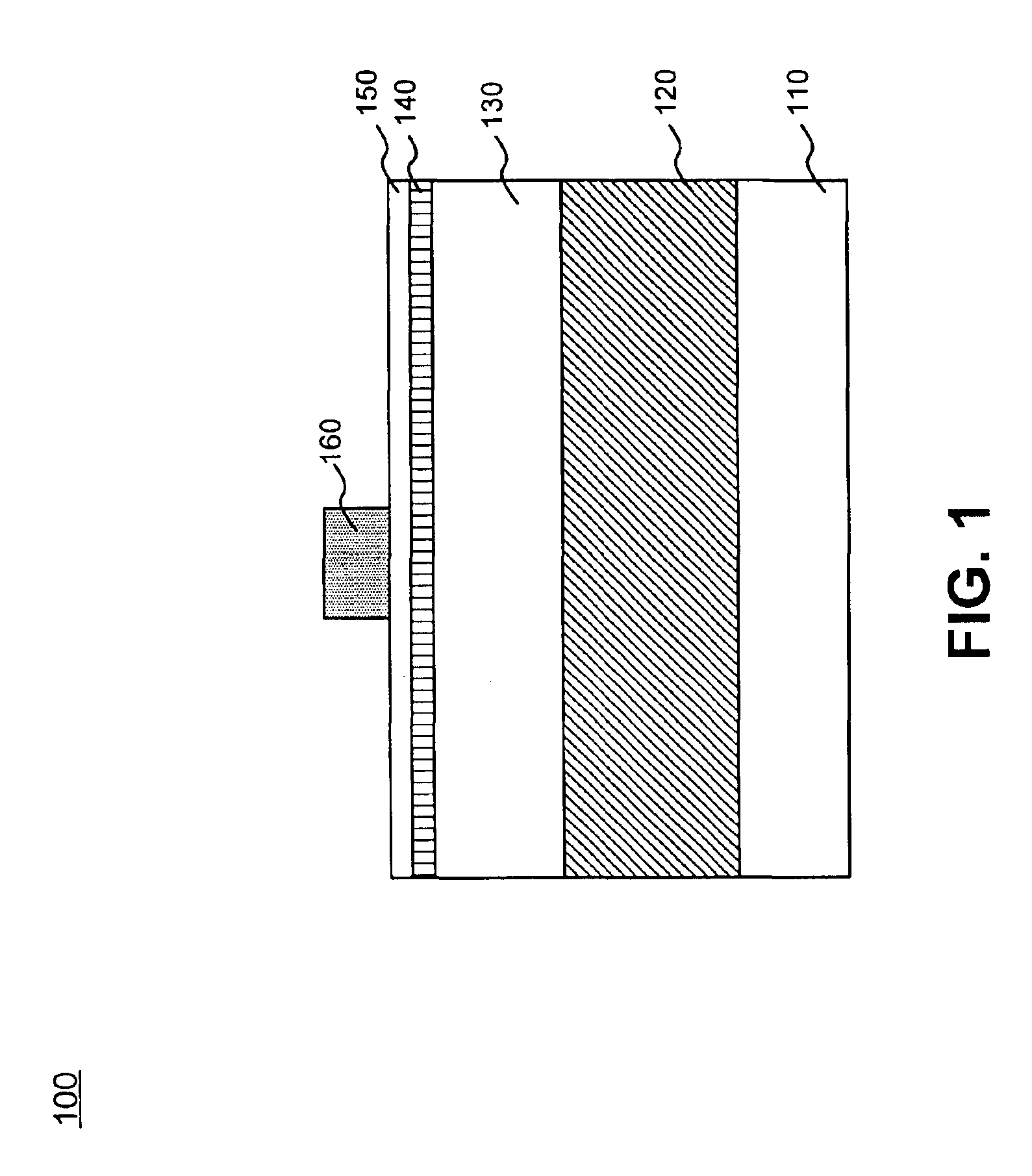

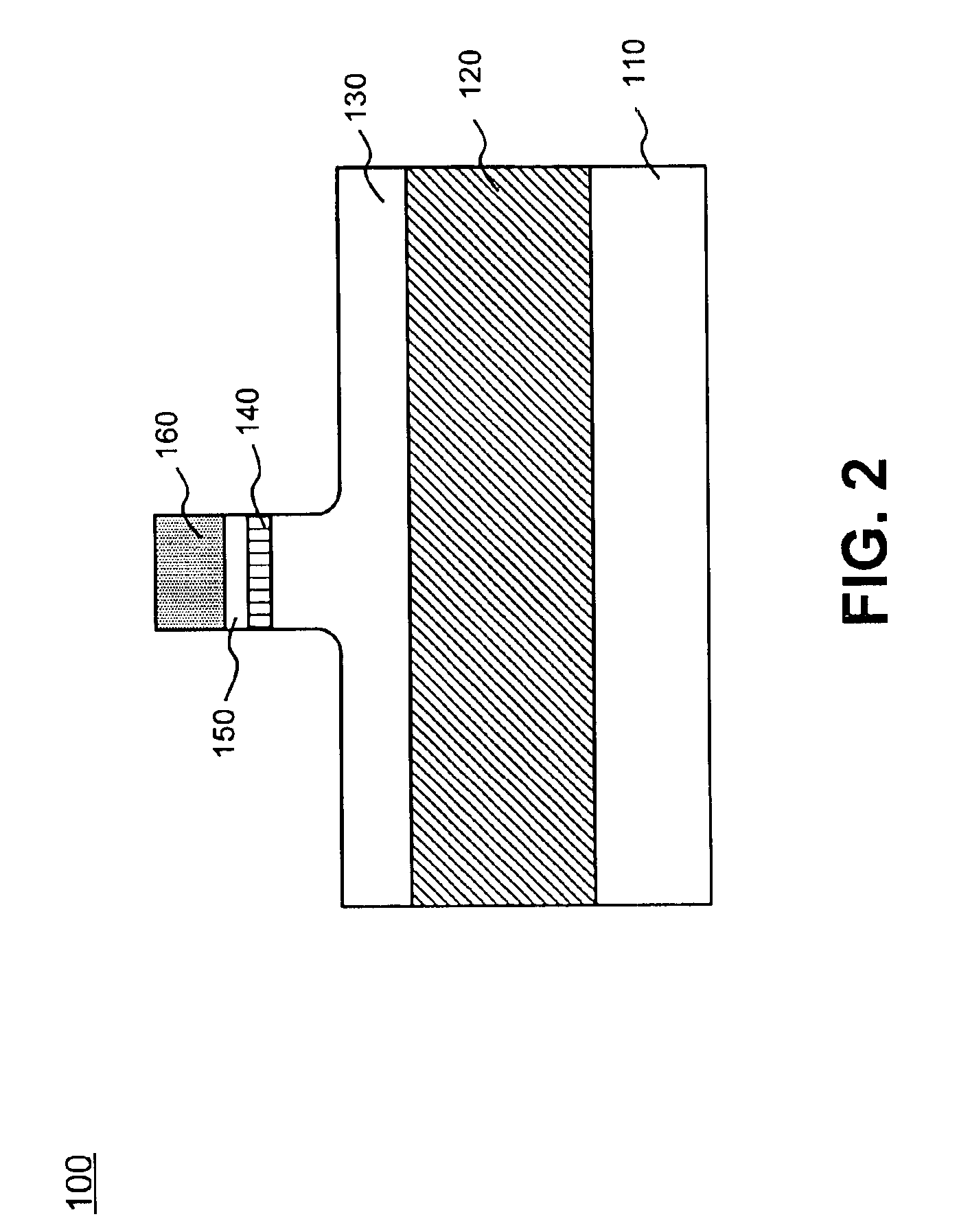

ActiveUS20080105874A1Cgs can be reducedImprove display qualitySolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

A thin film transistor (TFT) that comprises a gate electrode on a substrate, a gate insulation layer on the gate electrode, an active layer having a source region, a drain region, and a channel region on the gate insulation layer, and a source electrode and a drain electrode formed over the source region and drain region of the active layer respectively and facing each other with respect to the channel region. The profile of channel region between the source electrode and drain electrode is changed in a bend line. A method for forming the TFT is also provided.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD +1

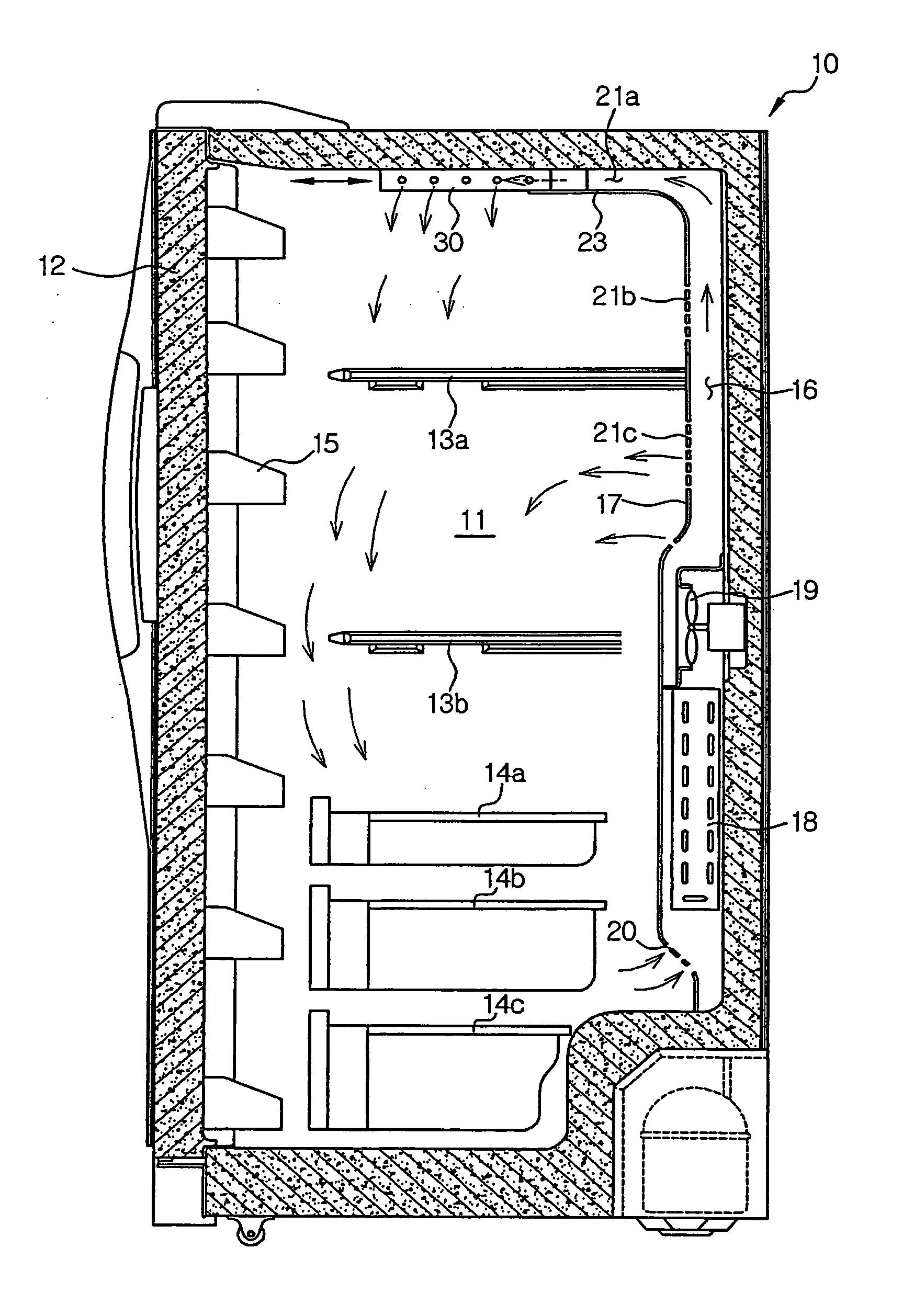

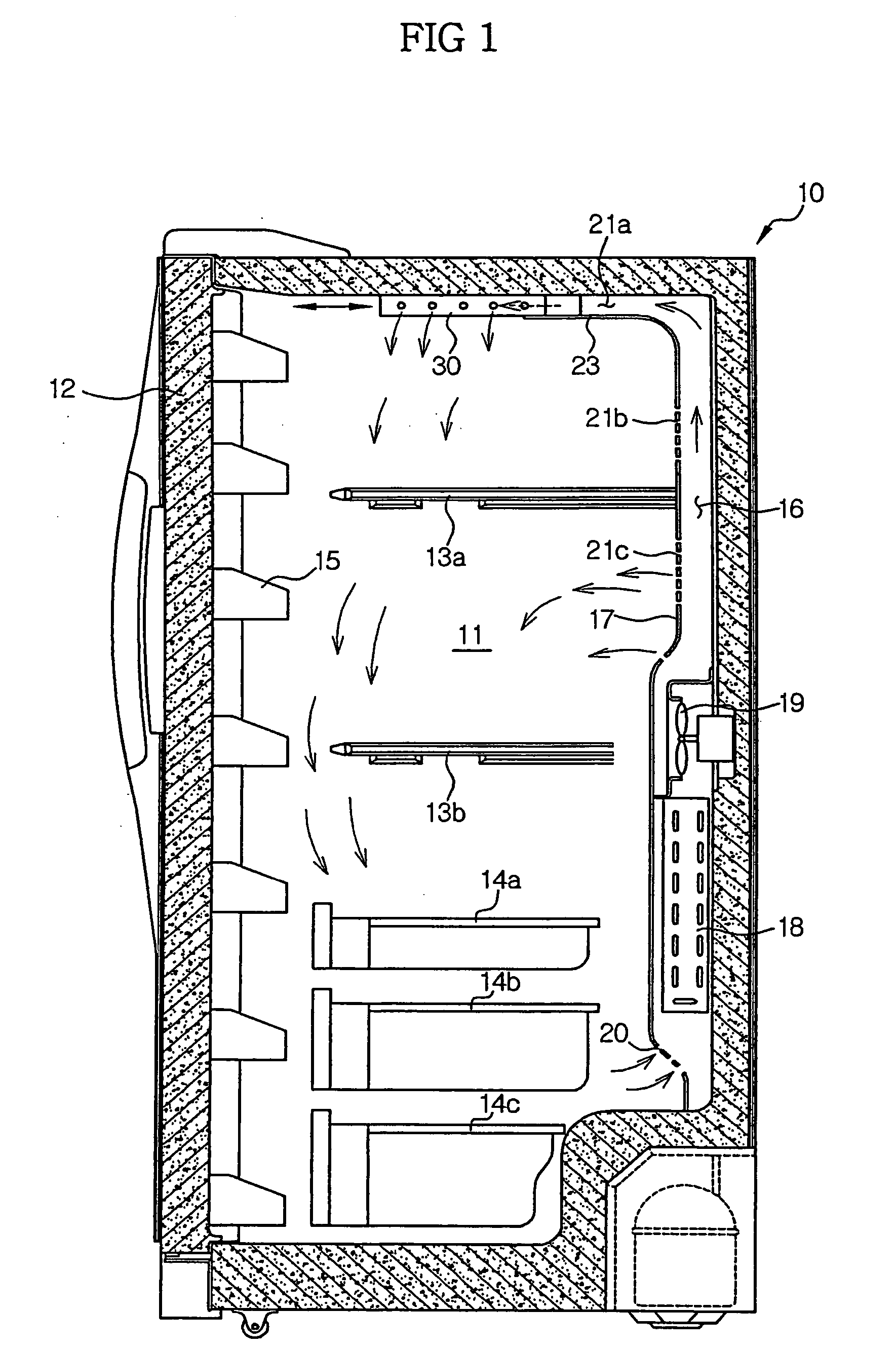

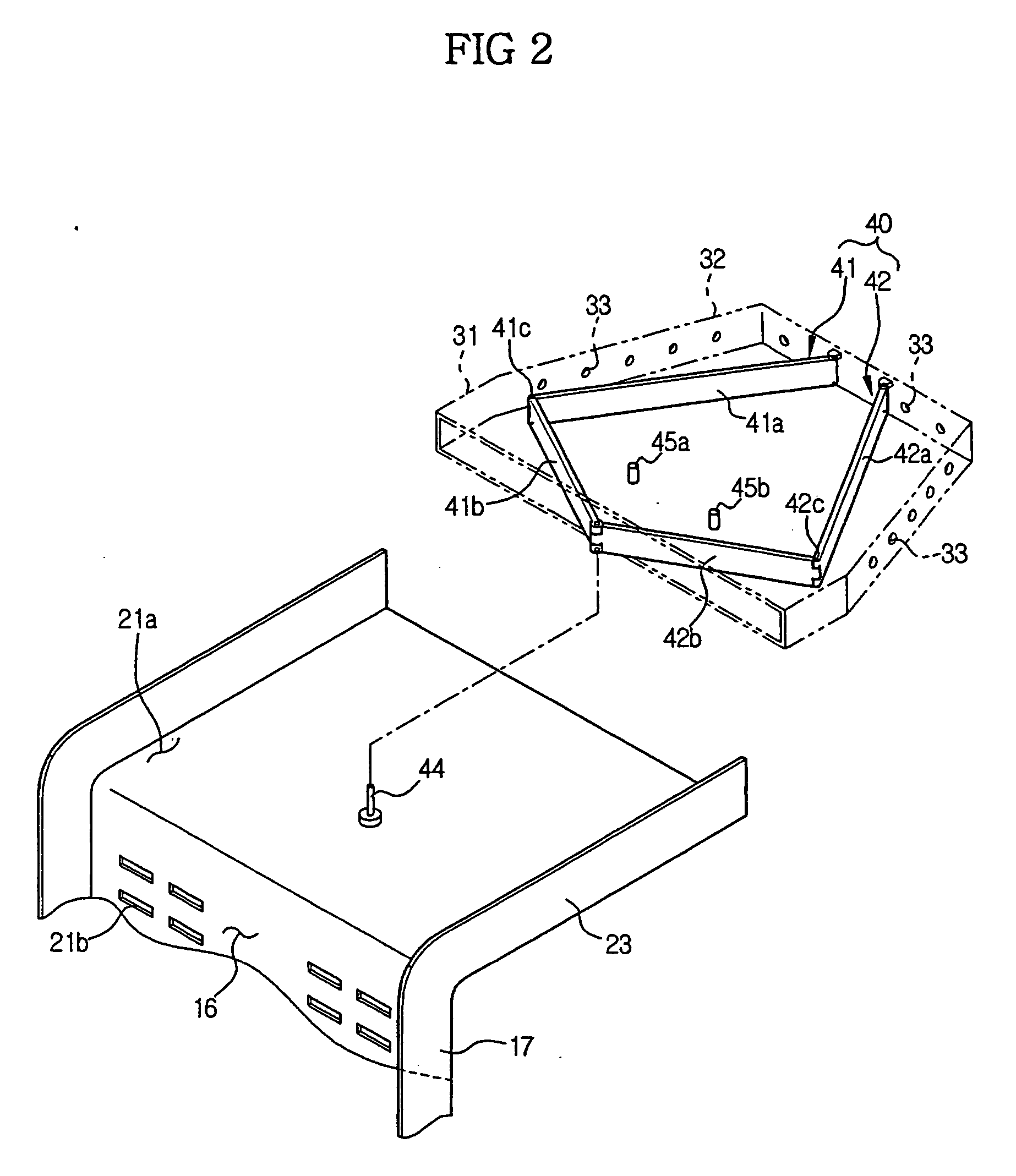

Refrigerator

InactiveUS20060070395A1Promotes even distributionSimple configurationLighting and heating apparatusCooling fluid circulationCold airRefrigerated temperature

A refrigerator capable of adjusting a discharge position and a quantity of cold air discharged into the refrigerator. The refrigerator includes an inner panel installed at a rear surface of a storage chamber and having cold air outlets for forming a cooling channel. The refrigerator also includes a variable duct installed at one of the cold air outlets such that the variable duct can move back and forth to vary a length of the cooling channel, and a plurality of cold air distribution holes formed in the variable duct.

Owner:SAMSUNG ELECTRONICS CO LTD

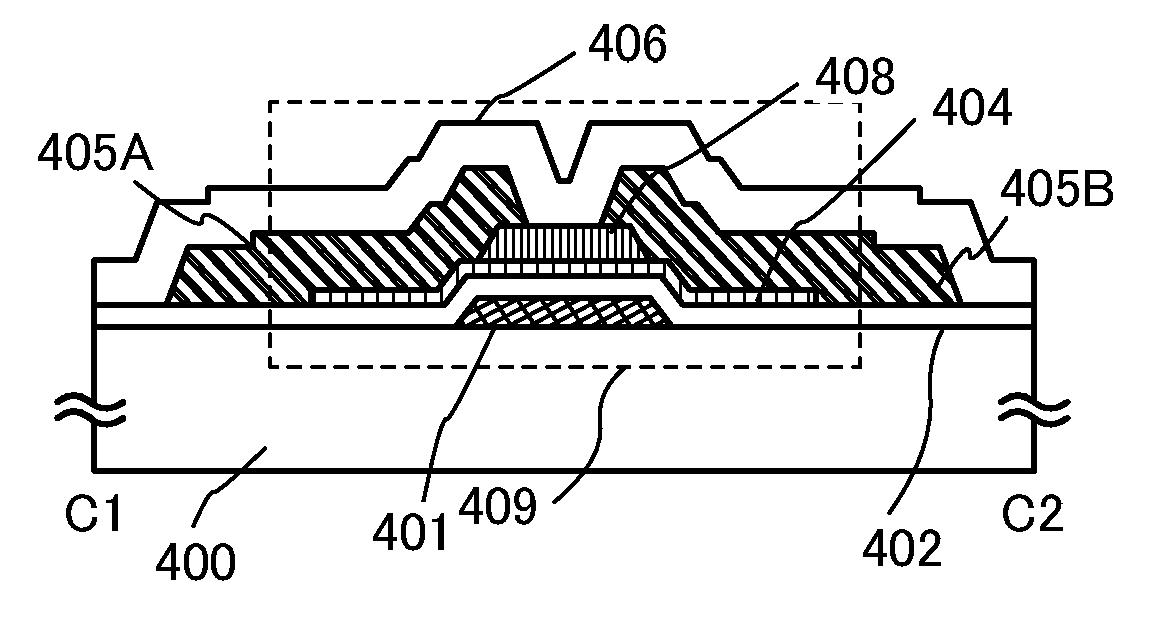

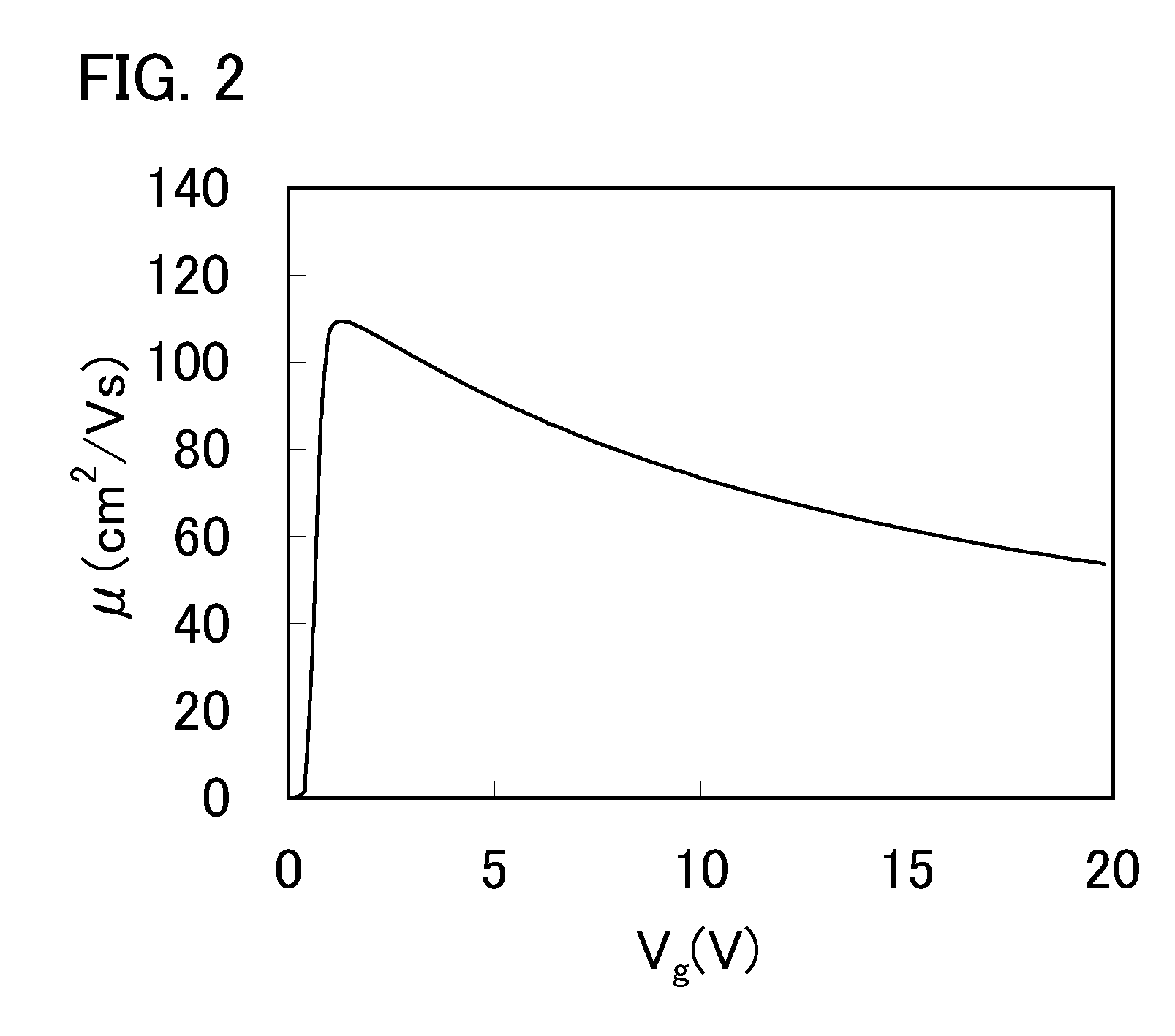

Display device and electronic device

ActiveUS20120286262A1Improve supply capacityAdequate dischargingTransistorSolid-state devicesDriver circuitDisplay device

An object is, in a structure where switch circuits in a signal line driver circuit is placed over the same substrate as a pixel portion, to reduce the size of transistors in the switch circuits and to reduce load in the circuits during charging and discharging of signal lines due to the supply of data. A display device is provided which includes a pixel portion receiving a video signal, and a signal line driver circuit including a switch circuit portion configured to control output of the video signal to the pixel portion. The switch circuit portion includes a transistor over an insulating substrate. The transistor has a field-effect mobility of at least 80 cm2 / Vs or more. The transistor includes an oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

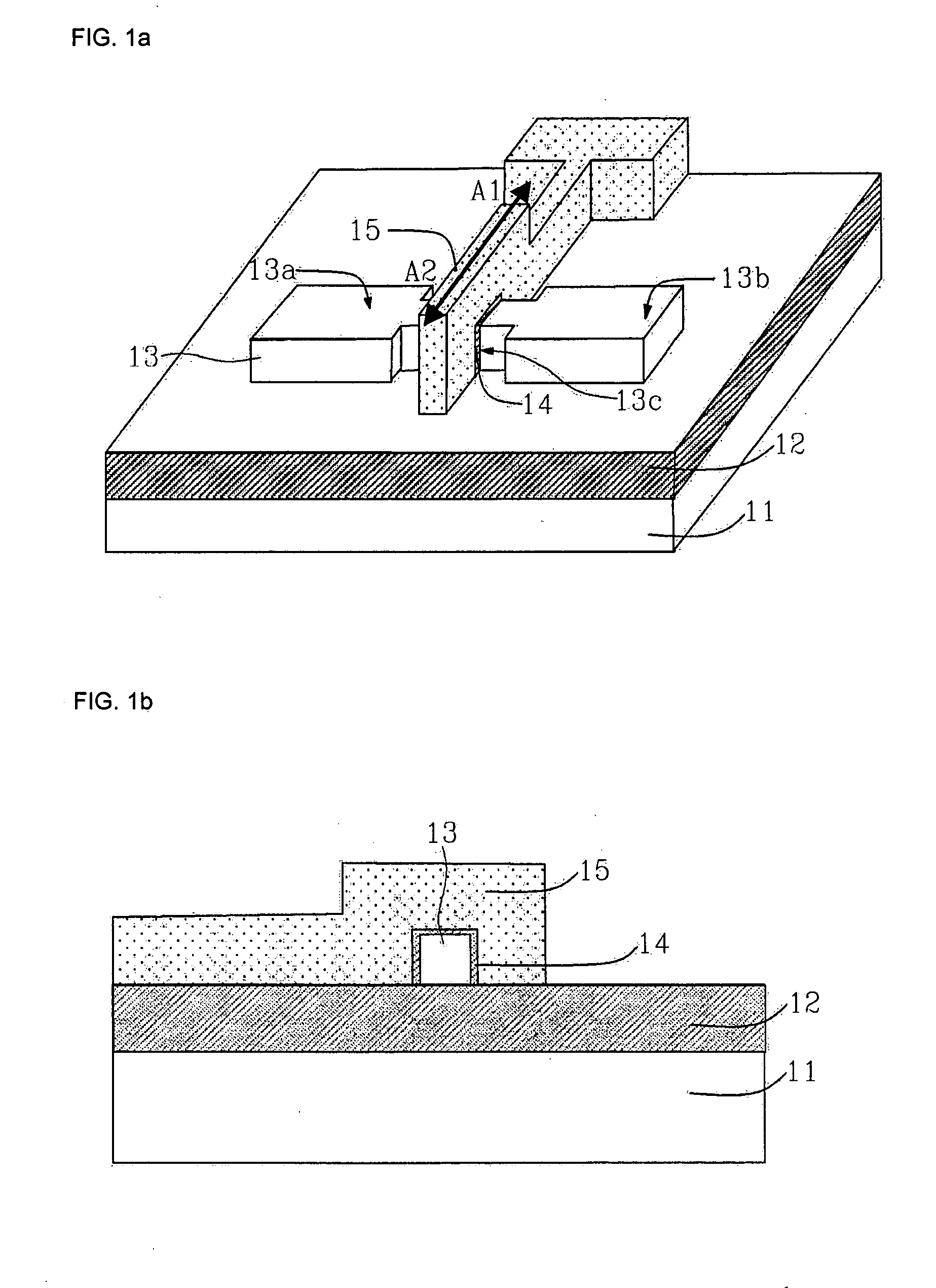

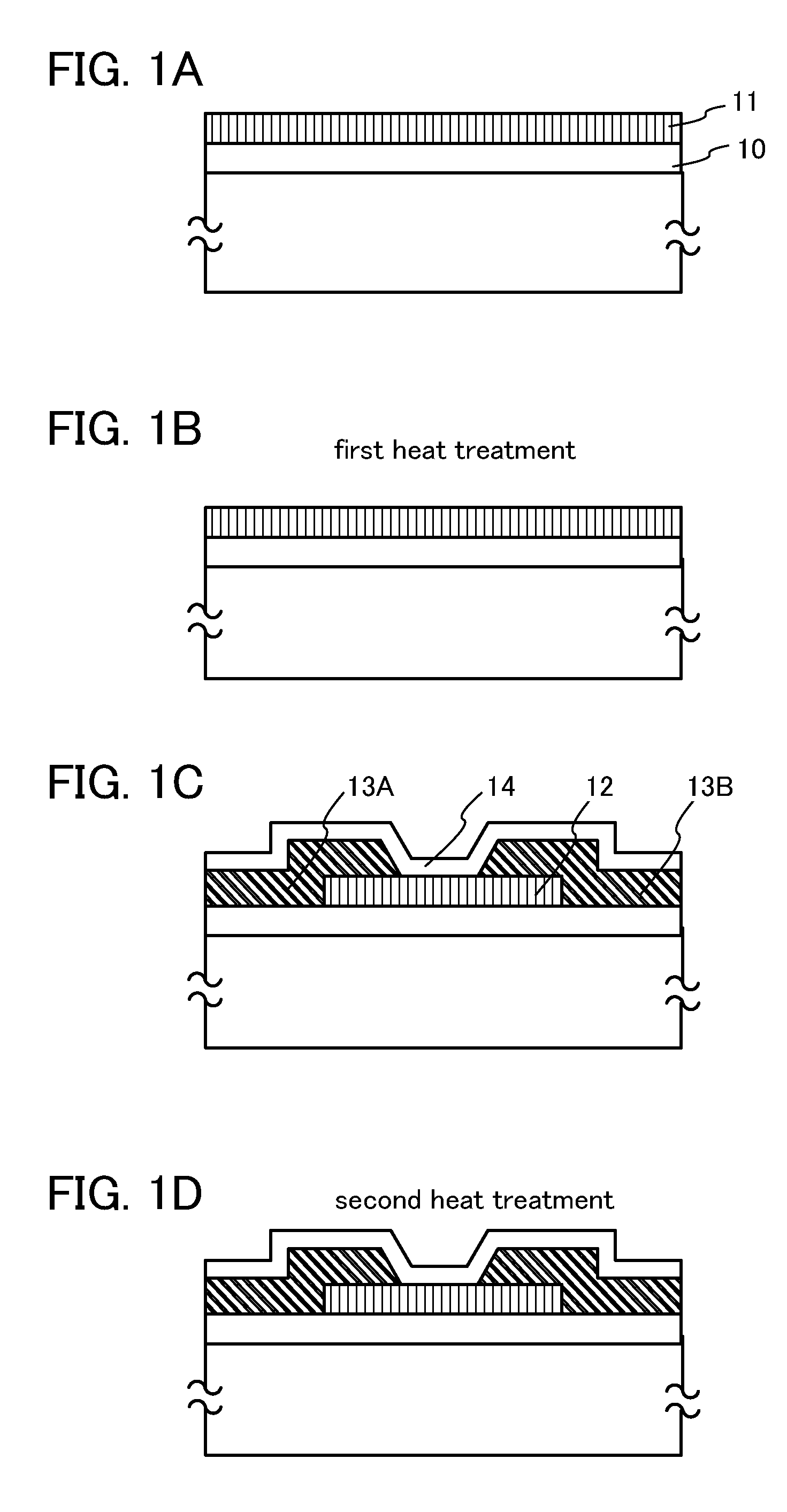

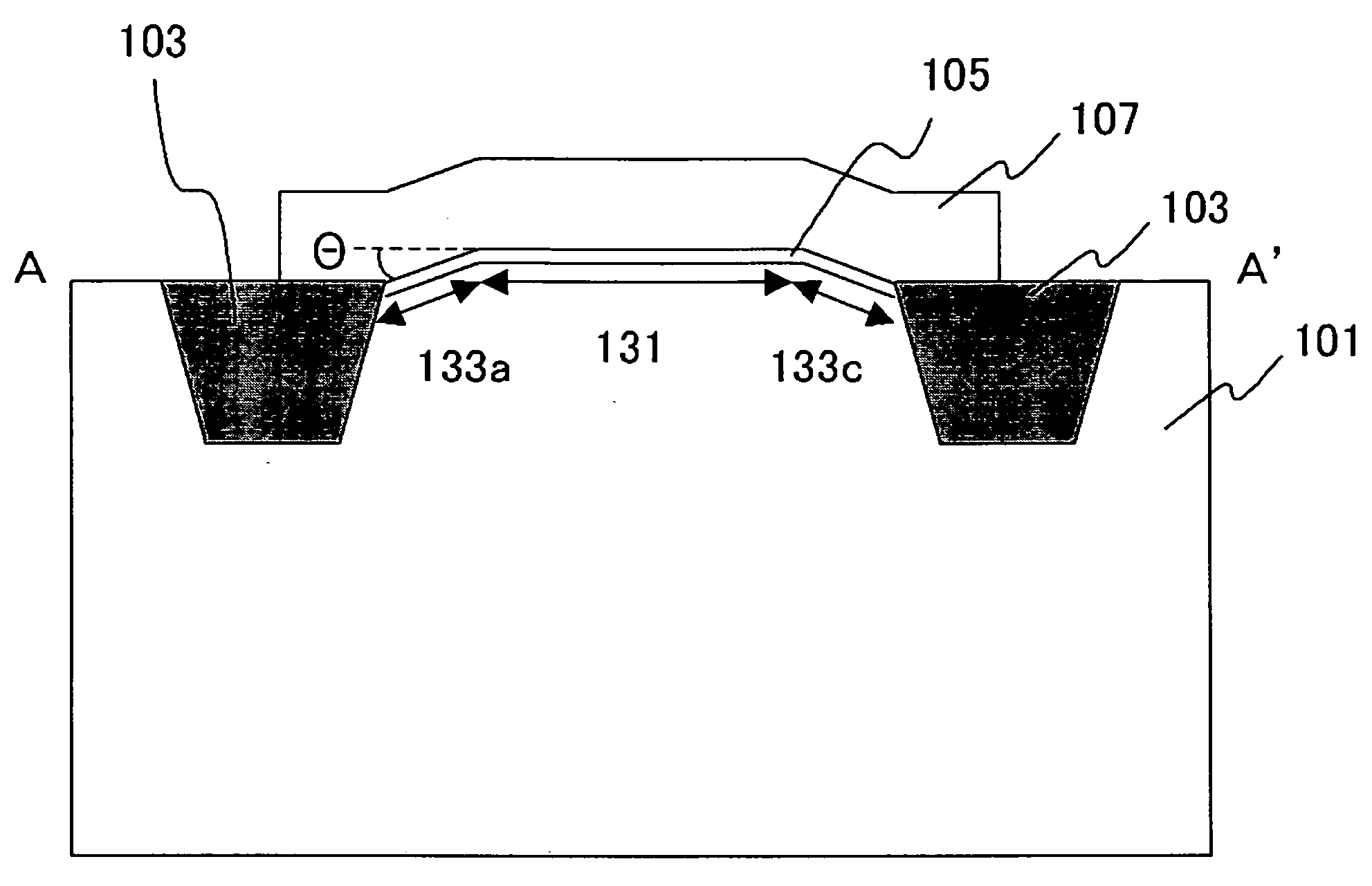

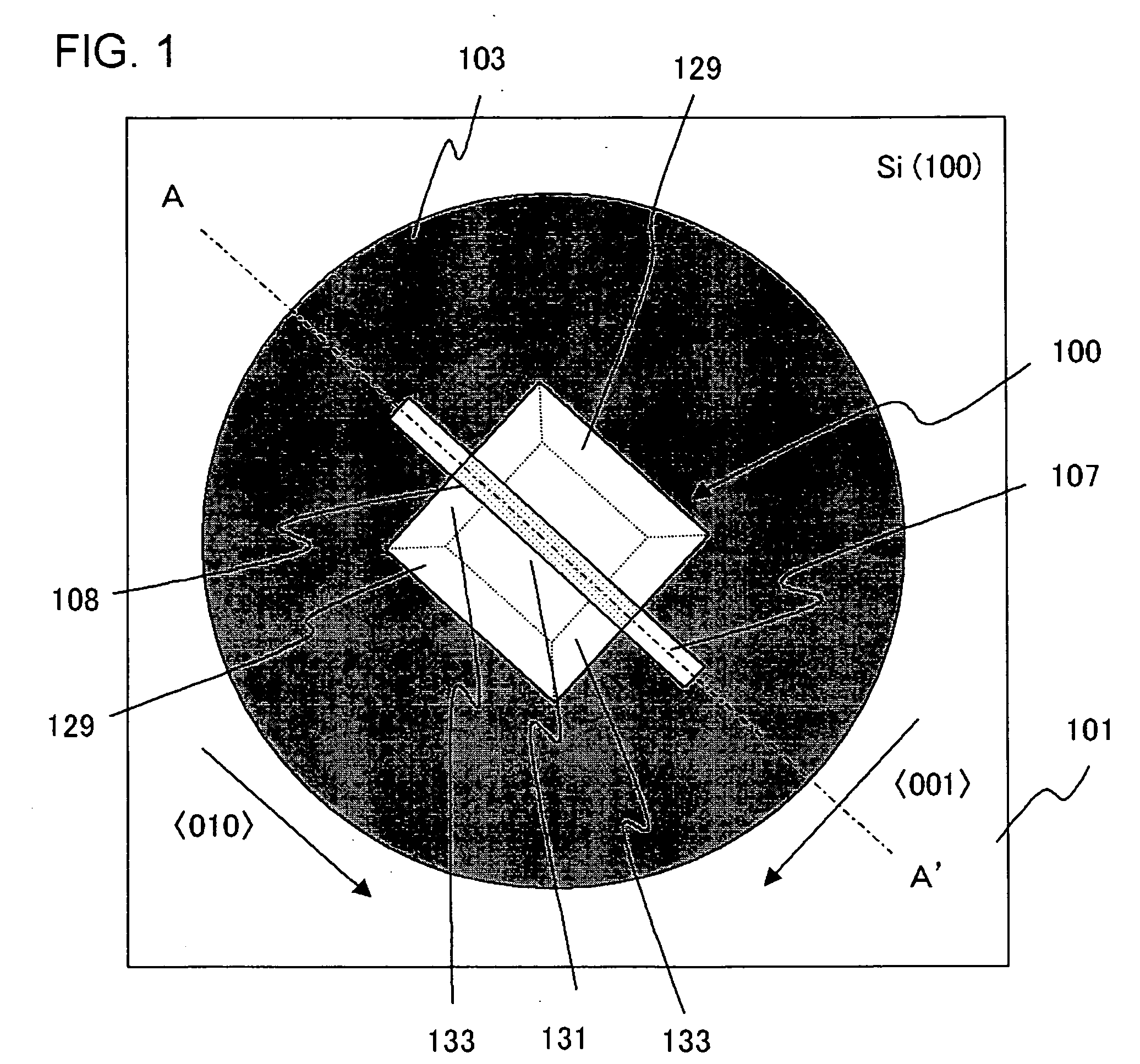

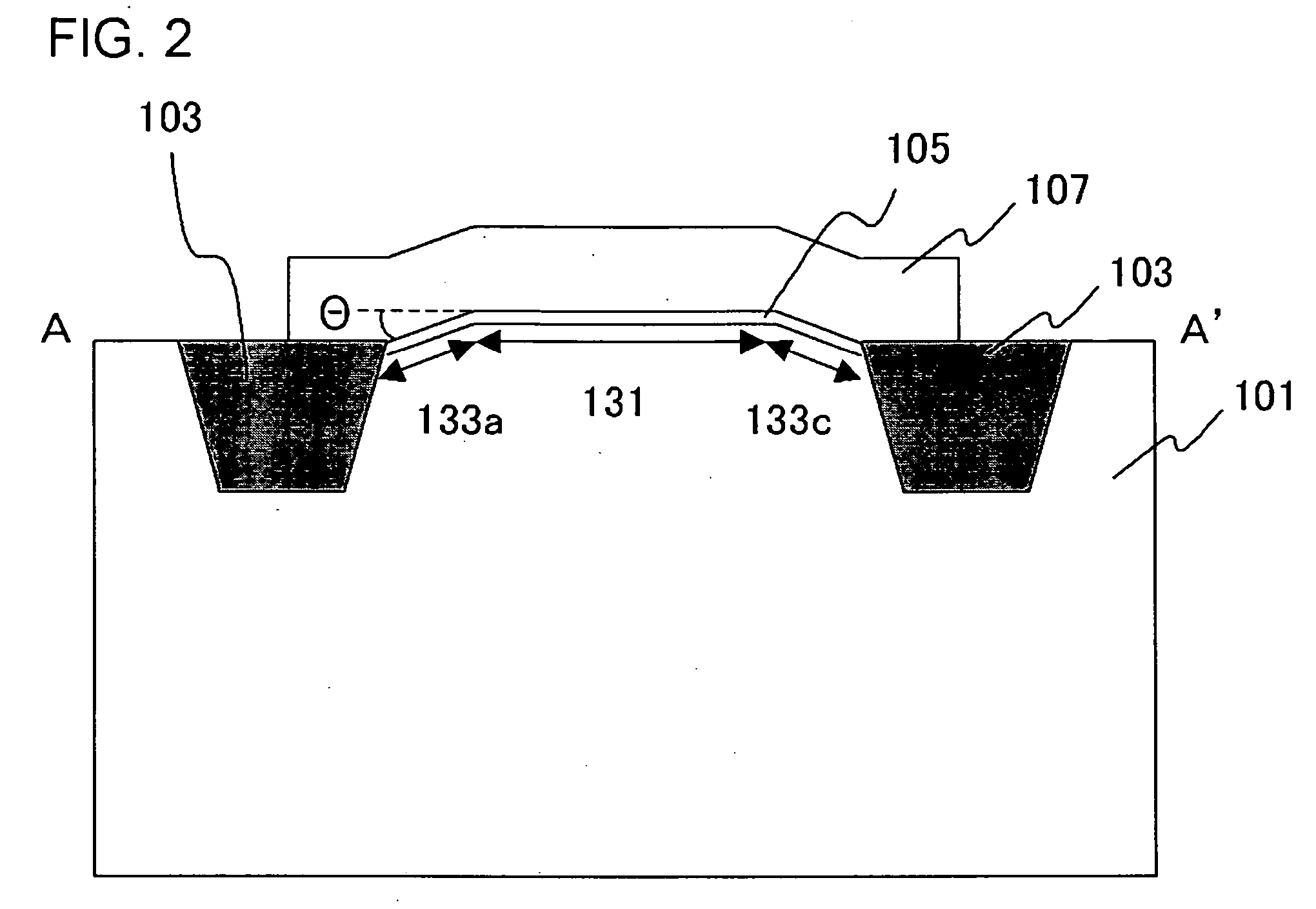

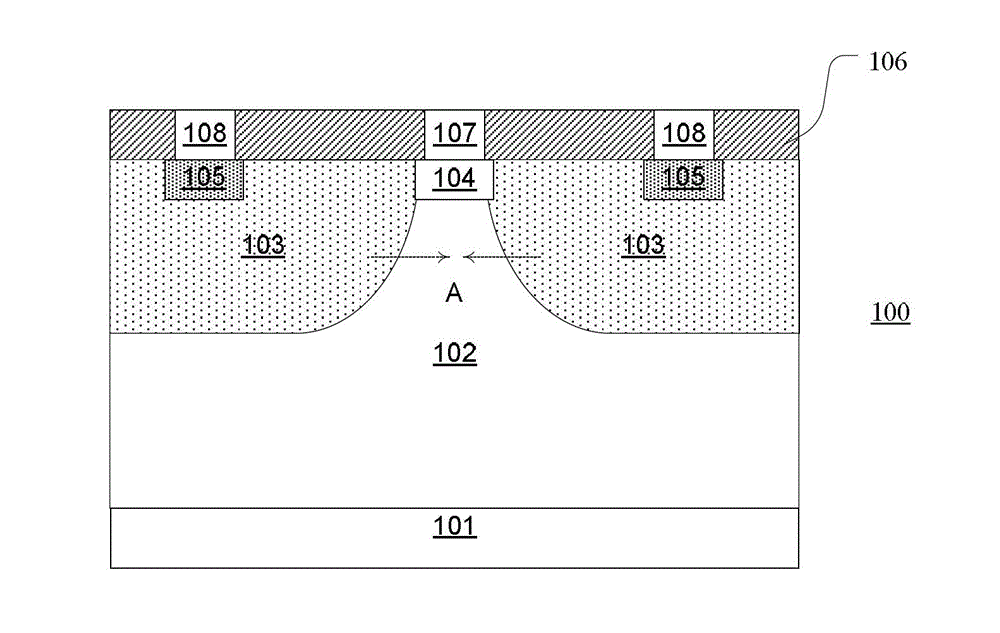

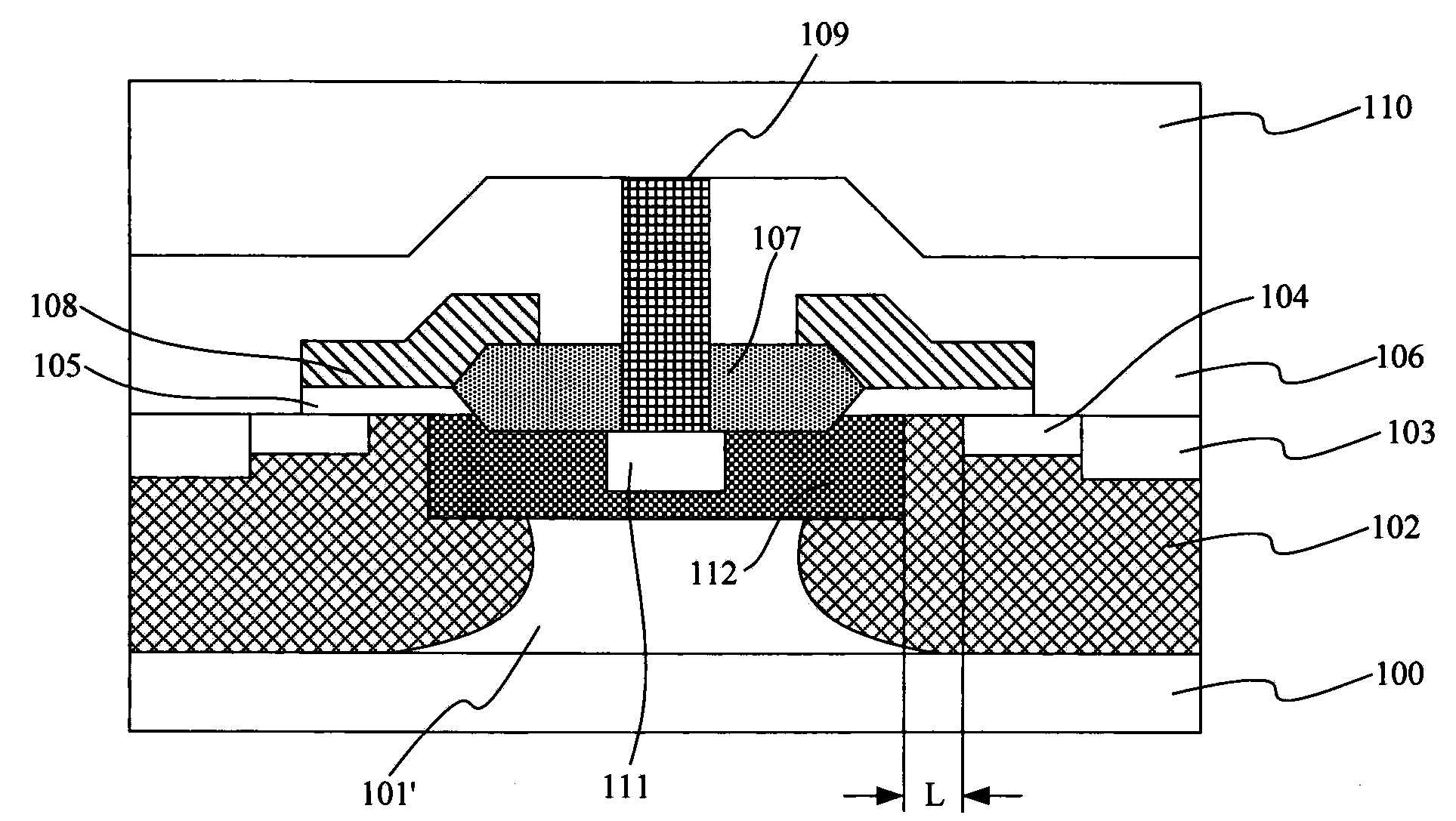

Field-effect transistor, complementary field-effect transistor, and method of manufacturing field-effect transistor

InactiveUS20060049430A1Improve channel mobilityDeterioration of ON-state can be suppressedTransistorSemiconductor/solid-state device manufacturingField-effect transistorPhysics

An objective of this invention is to improve an ON-state current of a field-effect transistor. For this purpose, on a single-crystal silicon substrate 101 having a {100} plane as a principal surface are formed a gate electrode 107 extending substantially in a <010> crystal axis direction of the single-crystal silicon or an axis direction equivalent to the <010> crystal axis direction, and in both sides of the gate electrode 107, source / drain regions 129 on the surface of the single-crystal silicon substrate 101. On the surface of the single-crystal silicon substrate 101 in a region directly below the gate electrode 107 are formed a principal surface and an inclined surface 133 oblique to the principal surface along the extension direction of the gate electrode 107.

Owner:NEC ELECTRONICS CORP +1

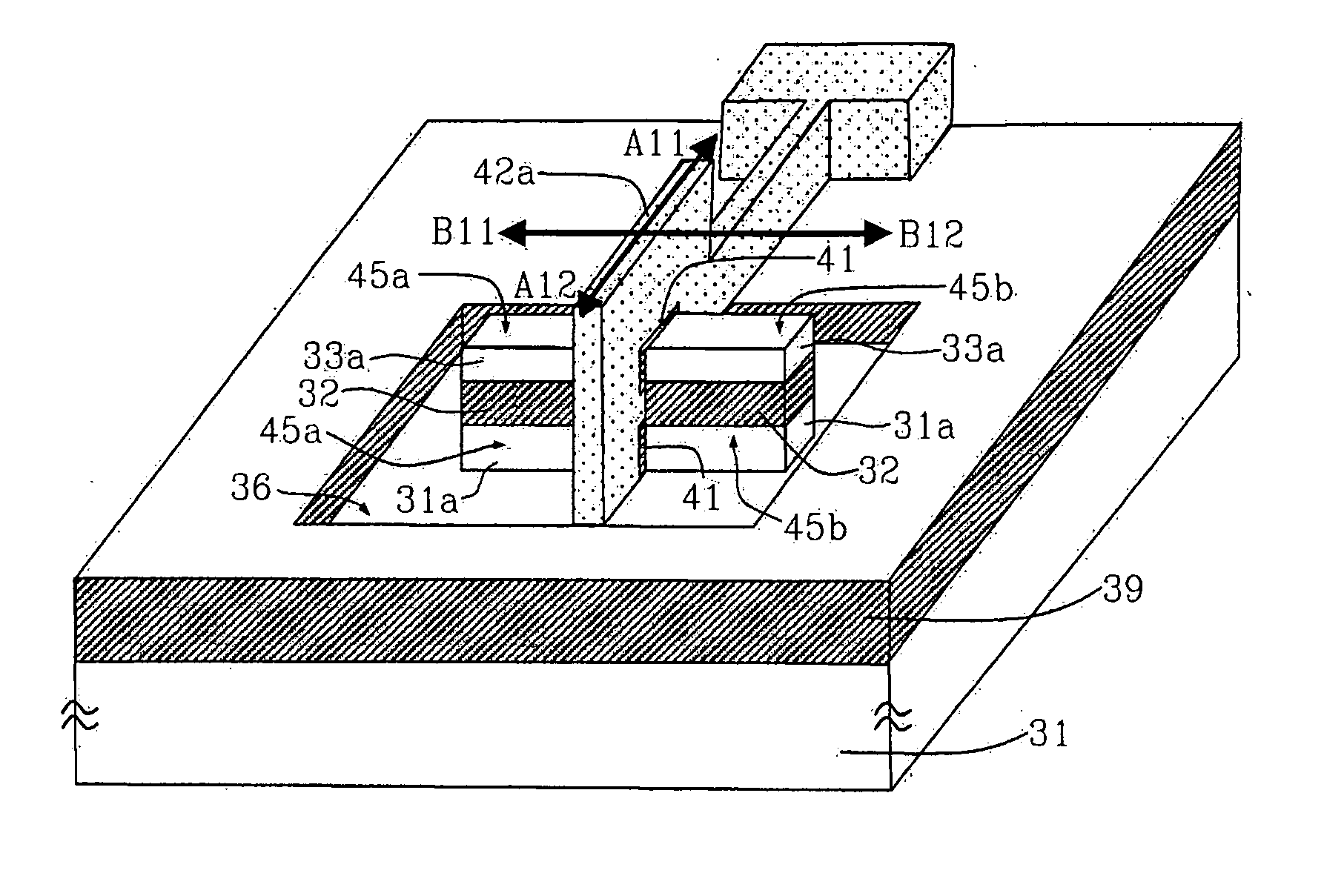

Semiconductor device having a gate structure surrounding a fin

ActiveUS6960804B1Increase channel widthTransistorSemiconductor/solid-state device manufacturingChannel widthSemiconductor

A double-semiconductor device includes a substrate, an insulating layer, a fin and a gate. The insulating layer is formed on the substrate and the fin is formed on the insulating layer. The fin has a number of side surfaces, a top surface and a bottom surface. The gate is formed on the insulating layer and surrounds the top surface, bottom surface and the side surfaces of the fin in the channel region of the semiconductor device. Surrounding the fin with gate material results in an increased total channel width and more flexible device adjustment margins.

Owner:ADVANCED MICRO DEVICES INC

Ultra small size vertical MOSFET device and method for the manufacture thereof

InactiveUS20040007737A1Increase drive currentIncrease channel widthTransistorNanotechMOSFETHigh concentration

The present invention relates to an ultra small size vertical MOSFET device having a vertical channel and a source / drain structure and a method for the manufacture thereof by using a silicon on insulator (SOI) substrate. To begin with, a first silicon conductive layer is formed by doping an impurity of a high concentration into a first single crystal silicon layer. Thereafter, a second single crystal silicon layer with the impurity of a low concentration and a second silicon conductive layer with the impurity of the high concentration are formed on the first silicon conductive layer. The second single crystal silicon layer and the second silicon conductive layer are vertically patterned into a predetermined configuration. Subsequently, a gate insulating layer is formed on entire surface. Then, an annealing process is carried out to diffuse the impurities in the first silicon conductive layer and the second silicon conductive layer into the second single crystal layer, thereby forming a source contact, a drain contact and a vertical channel. Finally, a gate electrode is formed on side walls of the vertical channel.

Owner:ELECTRONICS & TELECOMM RES INST

Liquid crystal display device and electronic device

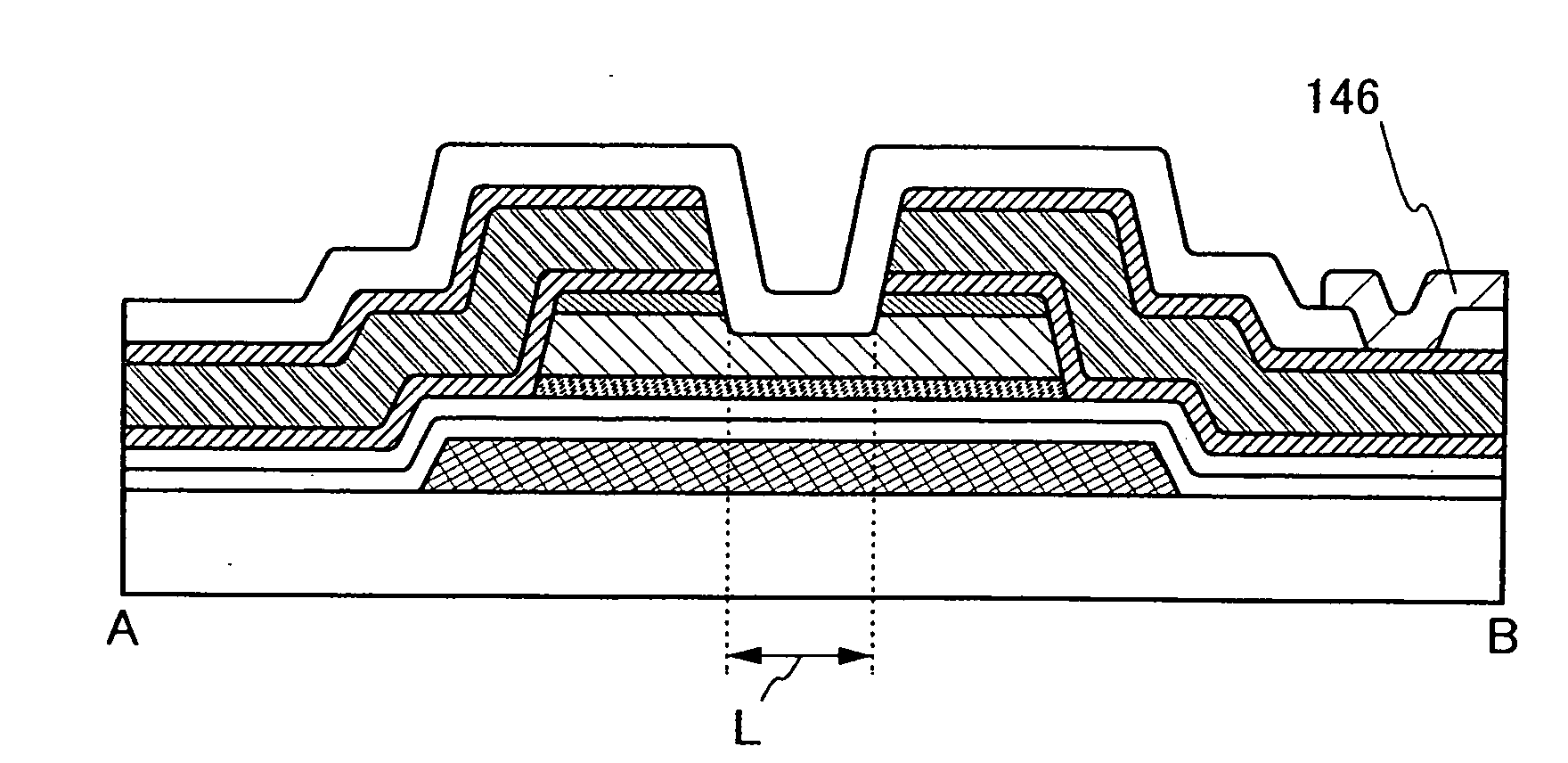

ActiveUS20090027580A1Improved aperture ratioHigh-qualitySolid-state devicesNon-linear opticsPhysicsChannel width

It is an object to provide a liquid crystal display device and an electronic device of which aperture ratio increases. The present invention includes a substrate having an insulating surface, a transistor formed over the substrate, a pixel electrode electrically connected to the transistor. The transistor includes a gate electrode, a gate insulating layer over the gate electrode, a semiconductor layer having a microcrystalline structure over the gate insulating layer, and a buffer layer over the semiconductor layer having the microcrystalline structure. The channel width W of the transistor and the channel length L of the transistor satisfy a relation of 0.1≦W / L≦1.7.

Owner:SEMICON ENERGY LAB CO LTD

Liquid crystal display device and electronic device

ActiveUS8330887B2High current drive capabilityLow leakage current characteristicSolid-state devicesNon-linear opticsLiquid-crystal displayChannel width

Owner:SEMICON ENERGY LAB CO LTD

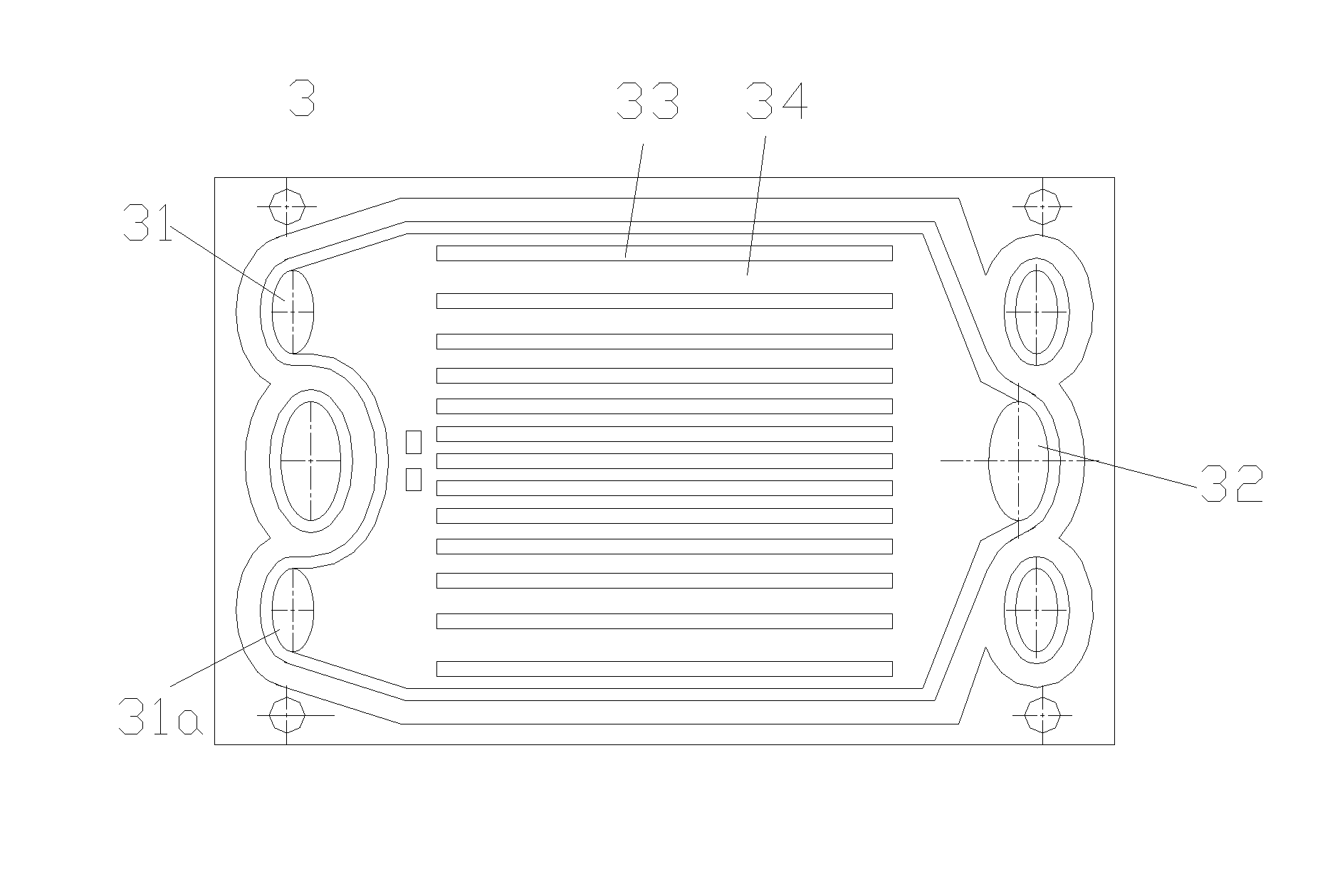

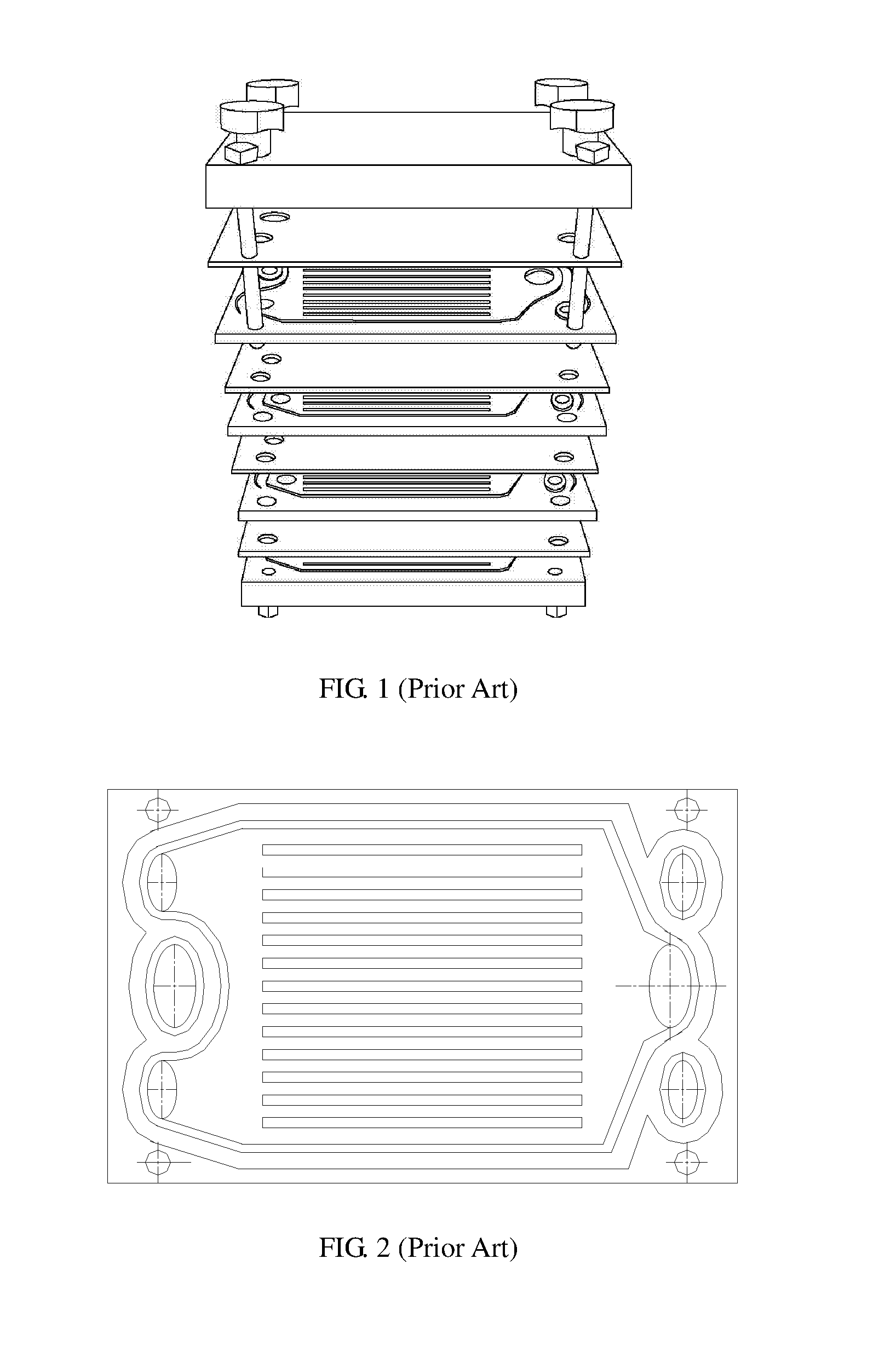

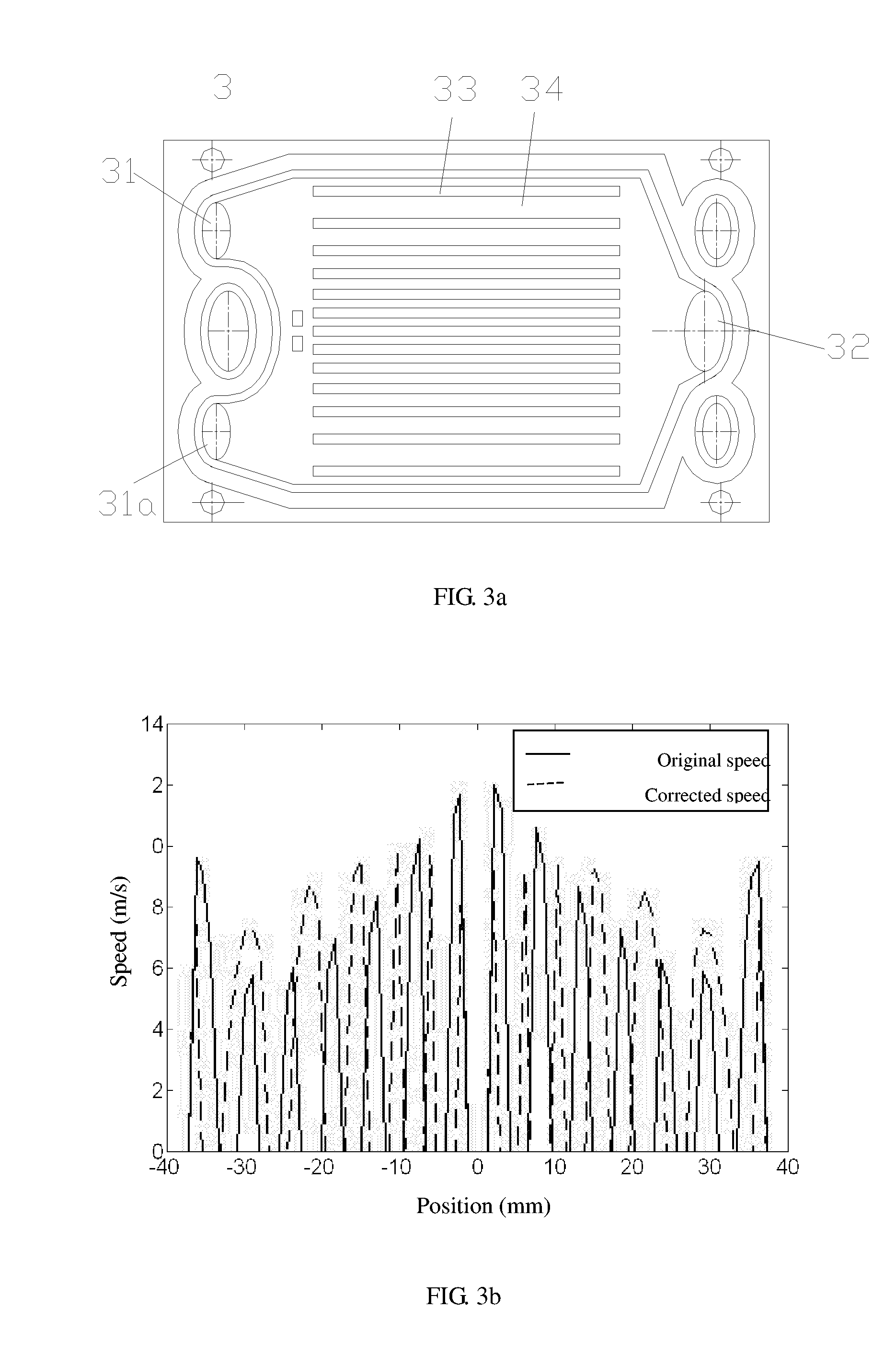

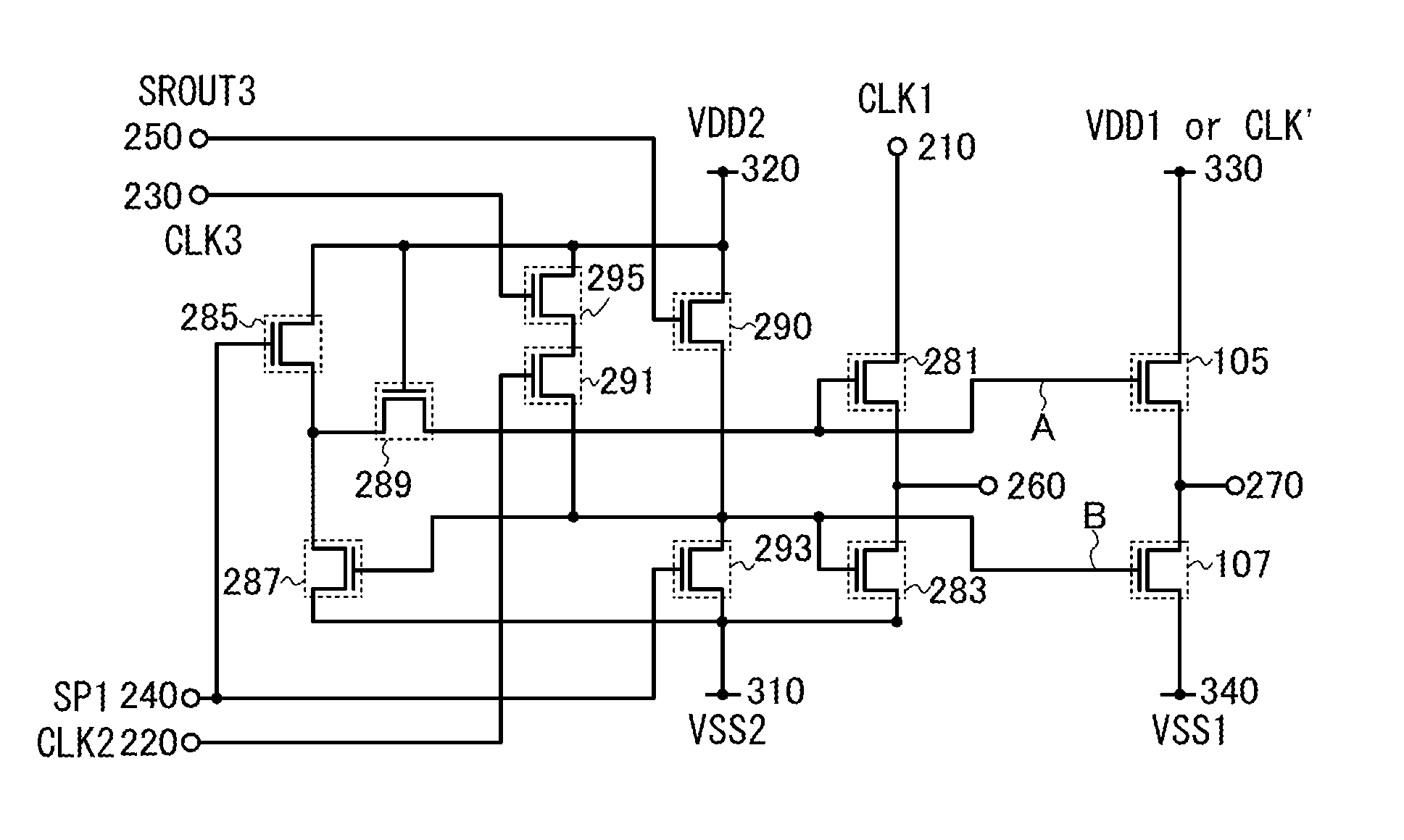

Improvement on the uniformity of fluid flow rate for interconnecting plate for planar solid oxide fuel cell

InactiveUS20070042257A1Increase distanceImprove uniformityLayered productsFuel cell auxillariesFuel cellsEngineering

A flat connecting plate designed for solid oxide fuel cell to improve the uniformity of fluid flow rate comprising a series of parallel ribs and grooves formed by the spaces between the ribs, the lengths of the ribs vary in accordance with the variation of the edge at proximity of fluid inlets, the widths of the grooves reduced in sequence from edges to center of the connecting plate, a series of diamond blocks placed at proximity of fluid outlet symmetrical to the center line of the connecting plate, and / or a series of fluid guide plates formed in parallel at the middle of two fluid inlets.

Owner:INST NUCLEAR ENERGY RES ROCAEC

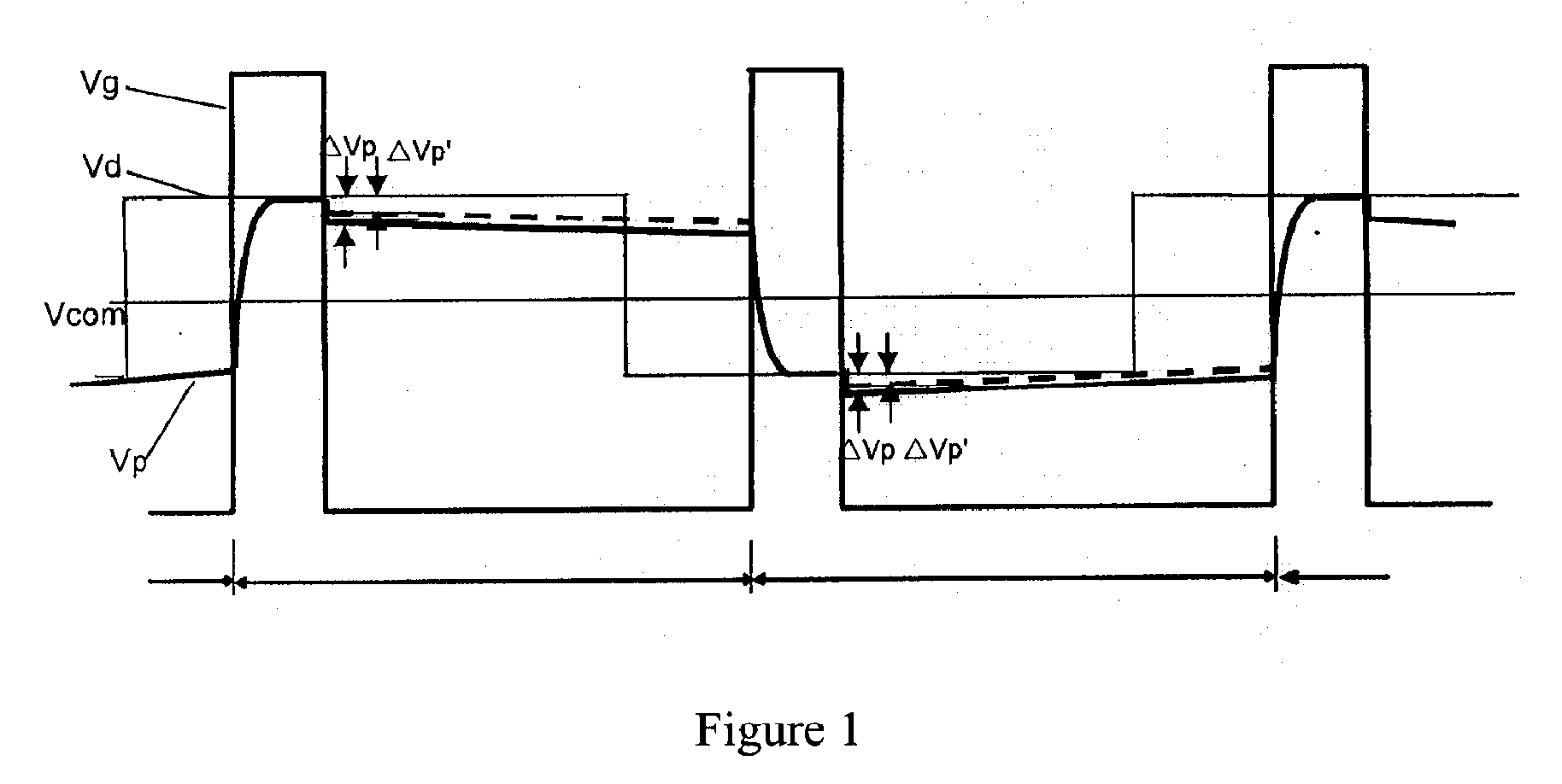

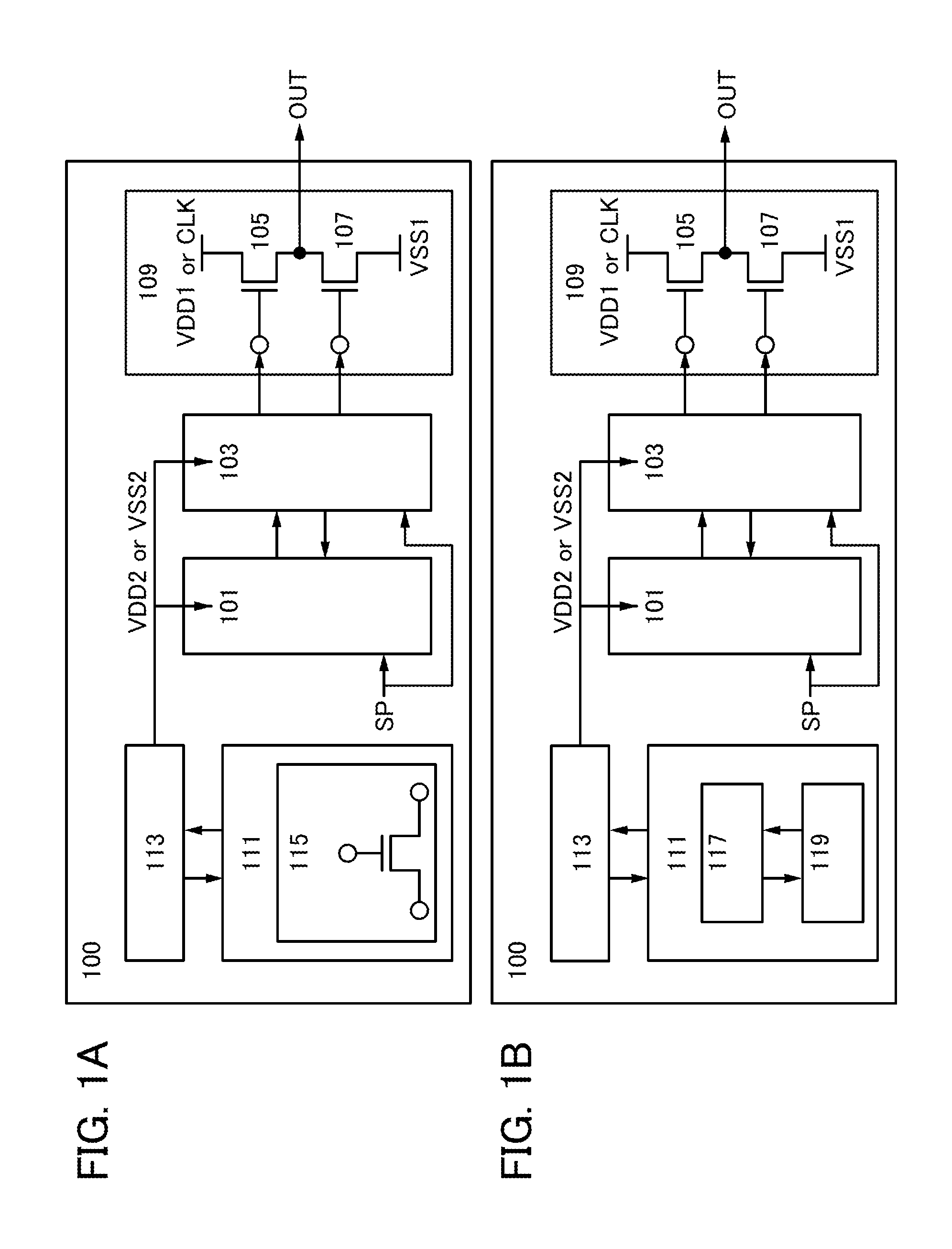

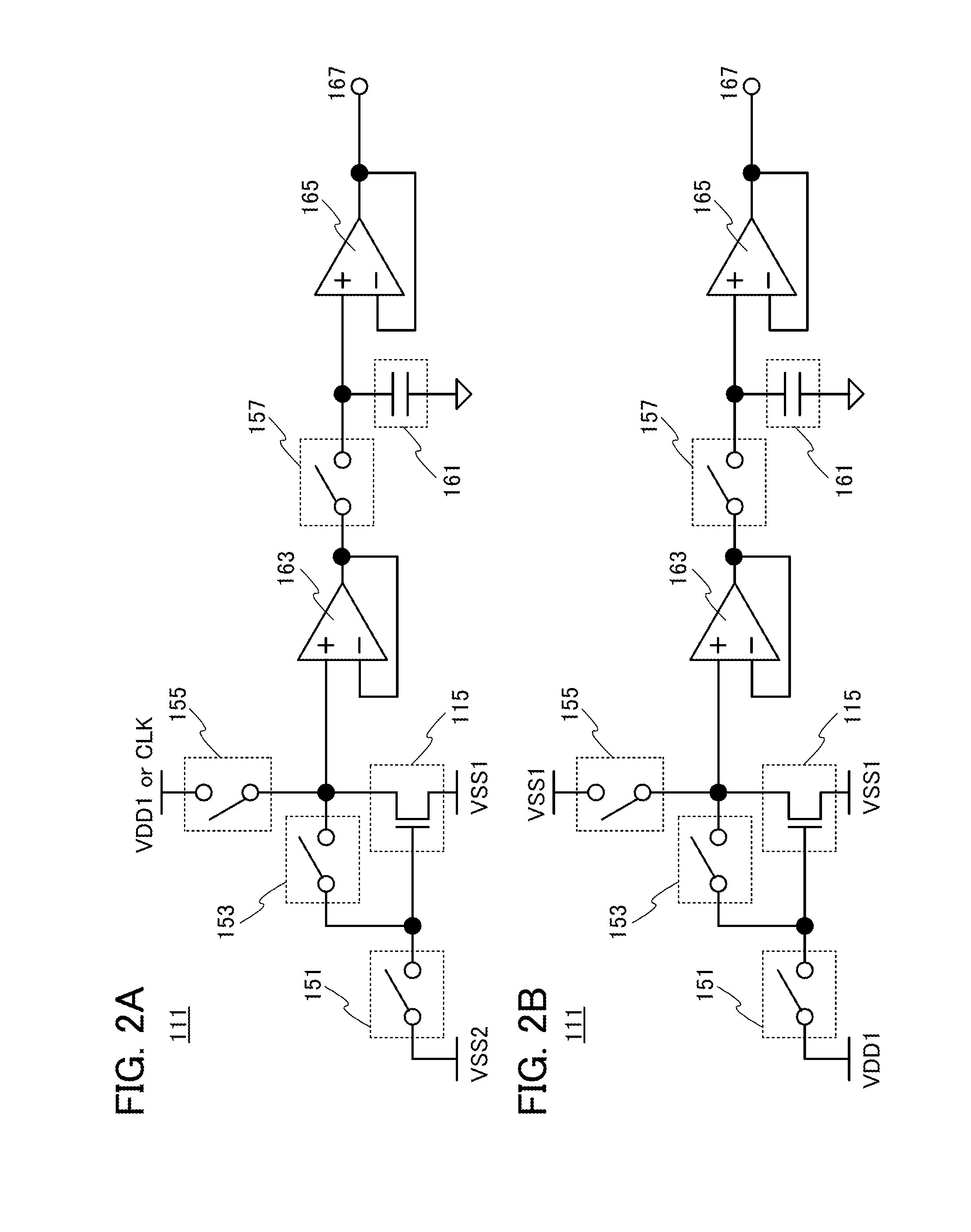

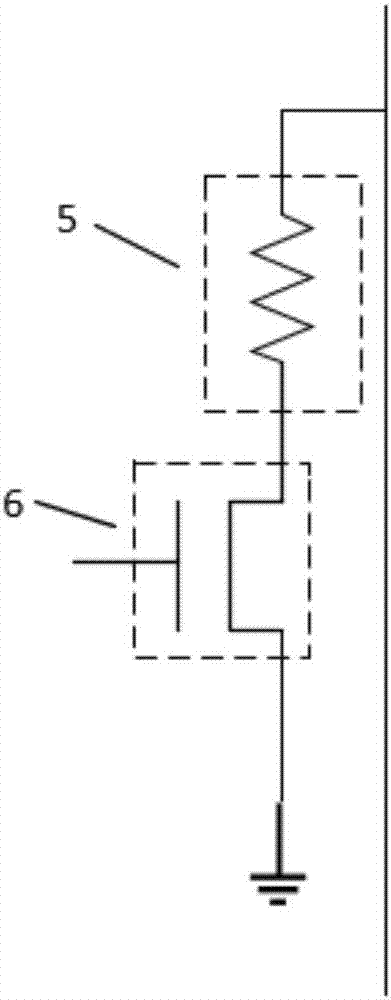

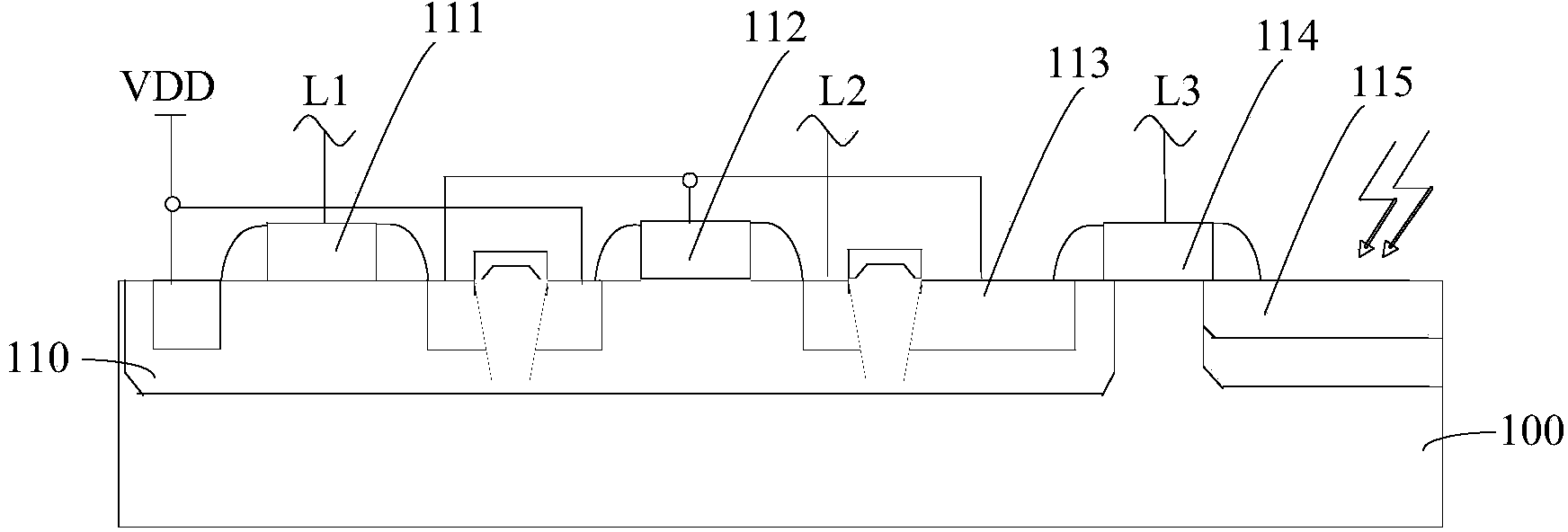

Pulse signal output circuit and shift register

InactiveUS20130322592A1Reduce power consumptionLong life-timeDigital storageElectric pulse generatorShift registerEngineering

To provide a pulse signal output circuit and a shift register which have lower power consumption, are not easily changed over time, and have a longer lifetime. A pulse signal output circuit includes a first input signal generation circuit; a second input signal generation circuit; an output circuit which includes a first transistor and a second transistor and outputs a pulse signal in response to a signal output from the first and second input signal generation circuits; a monitor circuit which obtains the threshold voltages of the first and second transistors; and a power supply output circuit which generates a power supply potential raised by a potential higher than or equal to a potential which is equal to or substantially equal to the threshold voltage and supplies the power supply potential to the first and second input signal generation circuits. A shift register includes the pulse signal output circuit.

Owner:SEMICON ENERGY LAB CO LTD

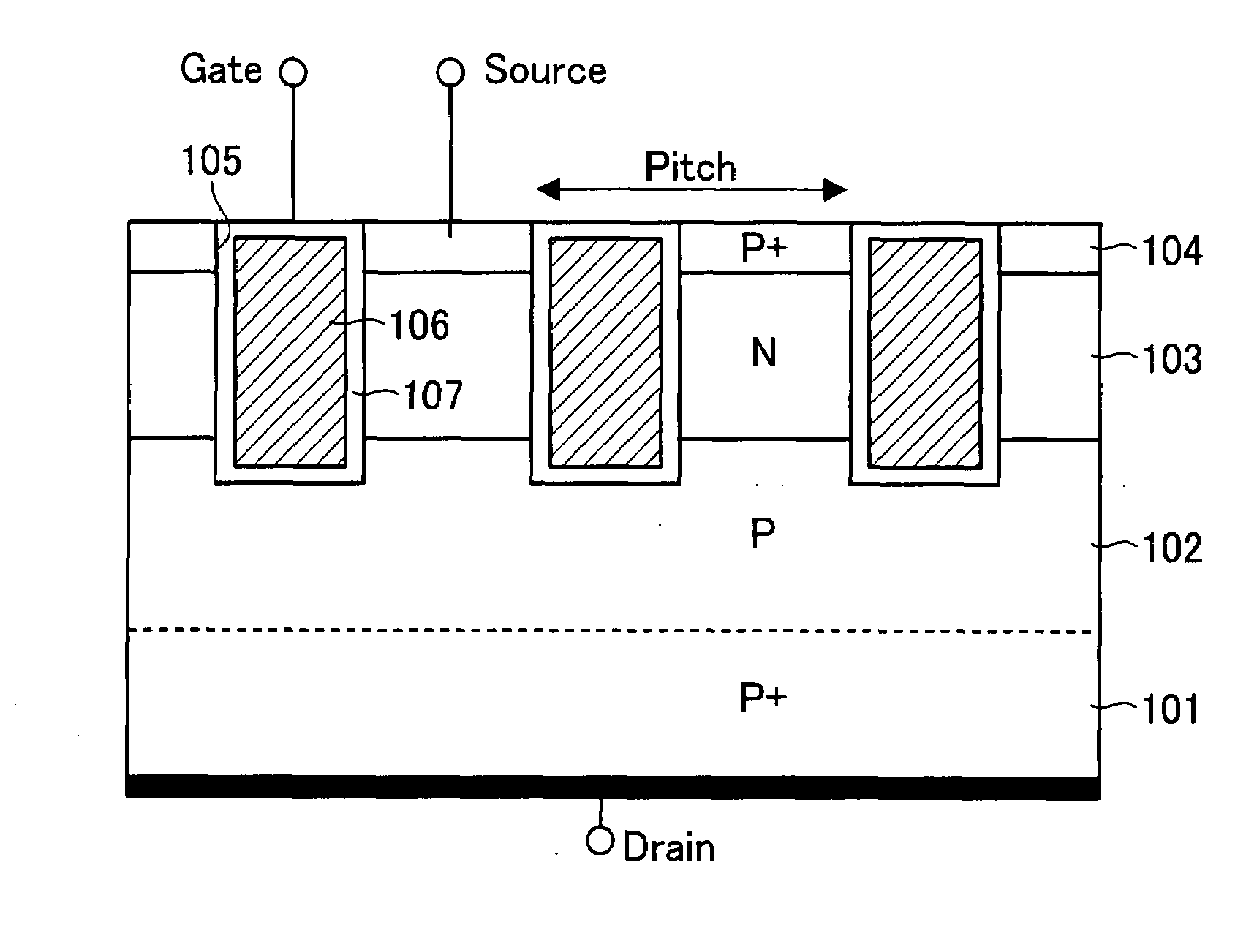

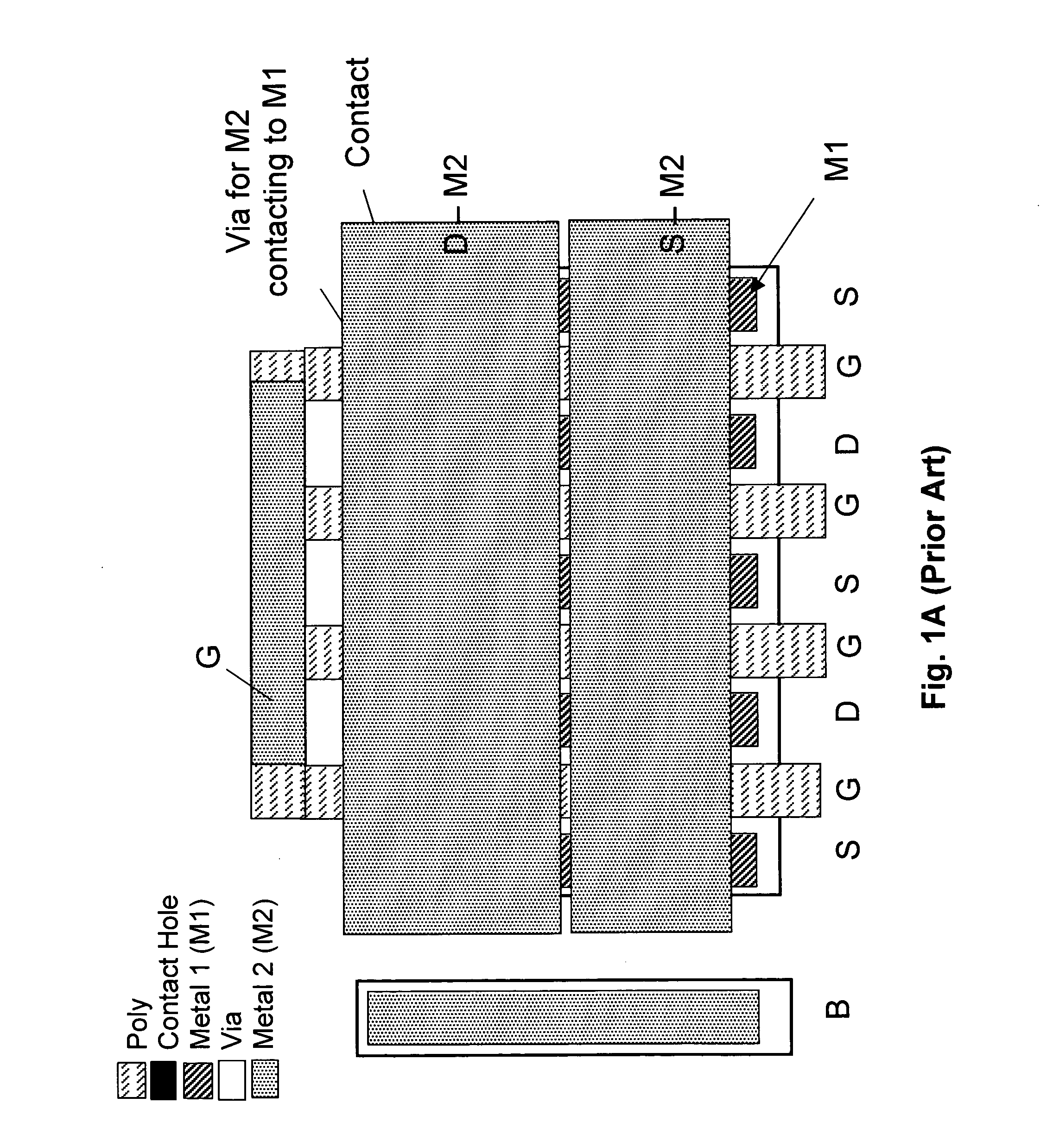

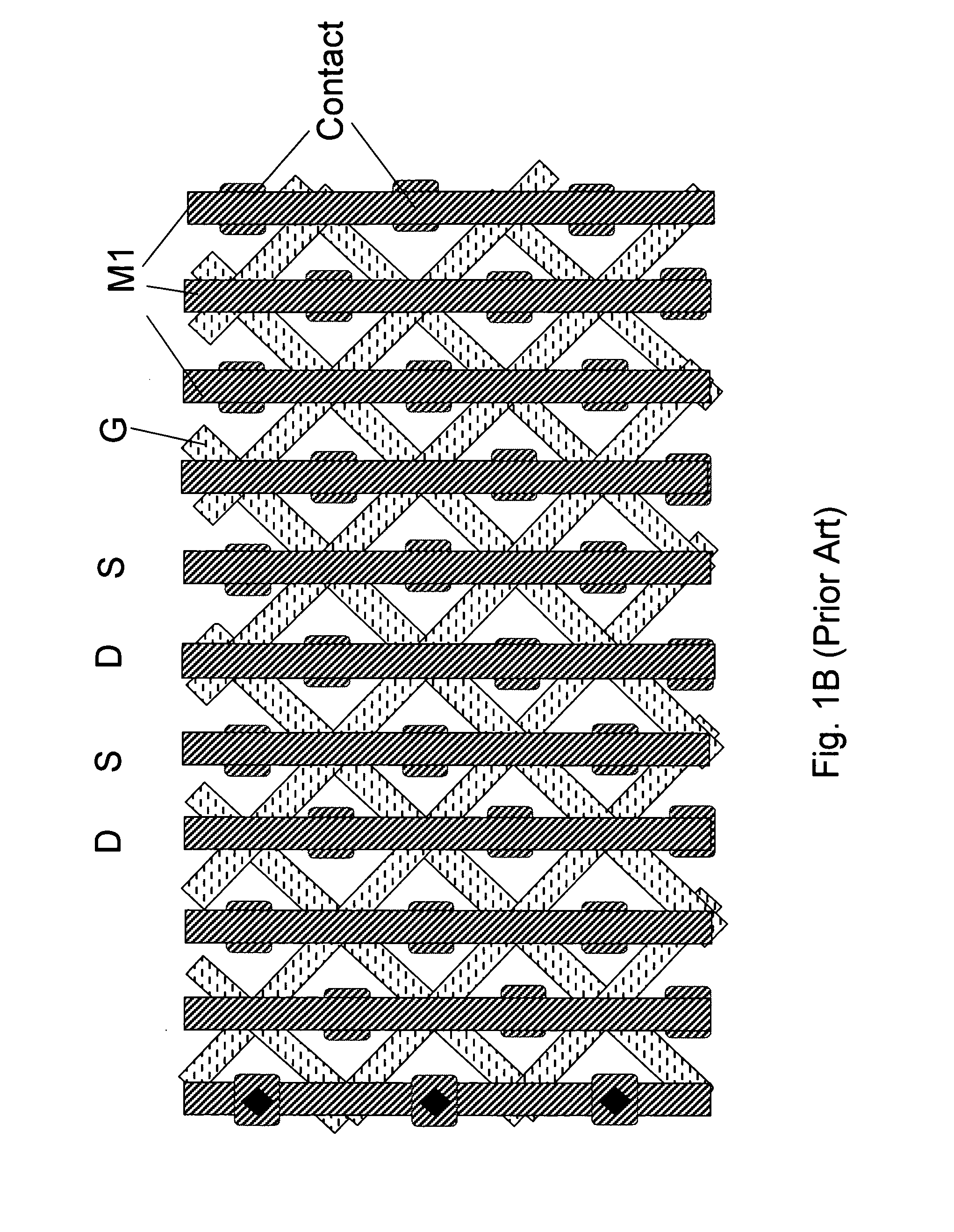

Closed cell configuration to increase channel density for sub-micron planar semiconductor power device

ActiveUS7956384B2High densityIncrease channel widthTransistorSemiconductor/solid-state device detailsChannel densityEngineering

Owner:ALPHA & OMEGA SEMICON LTD

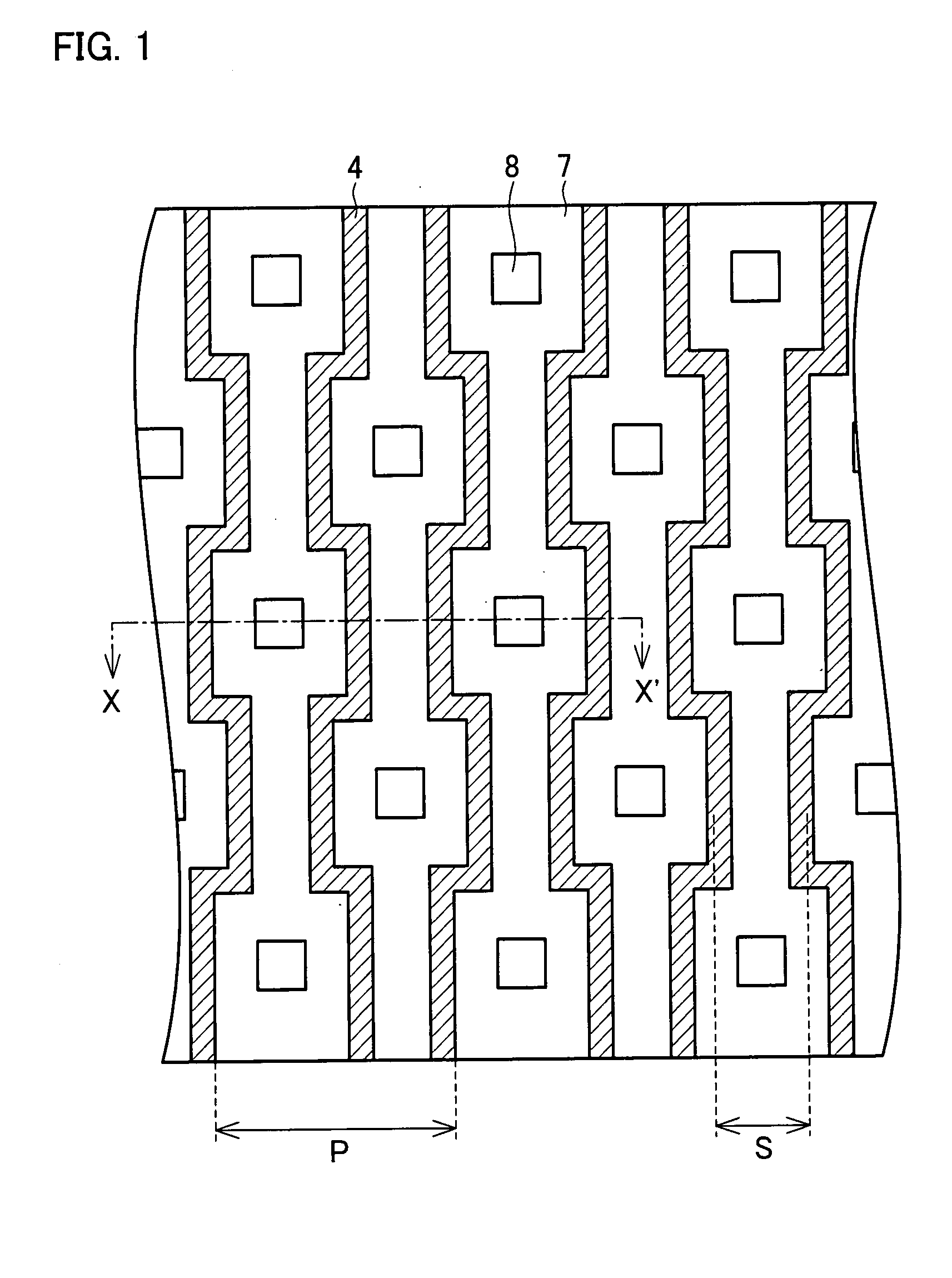

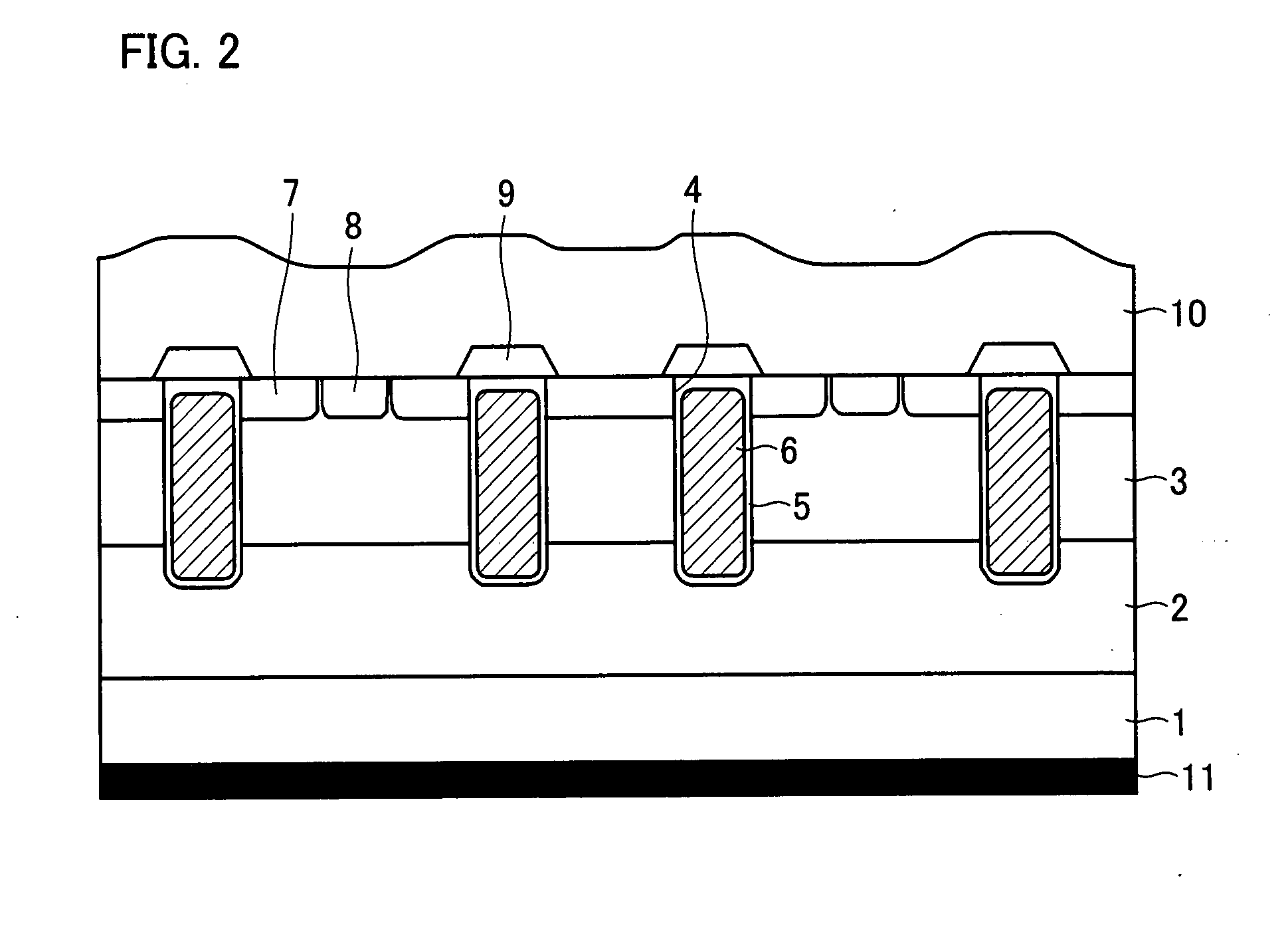

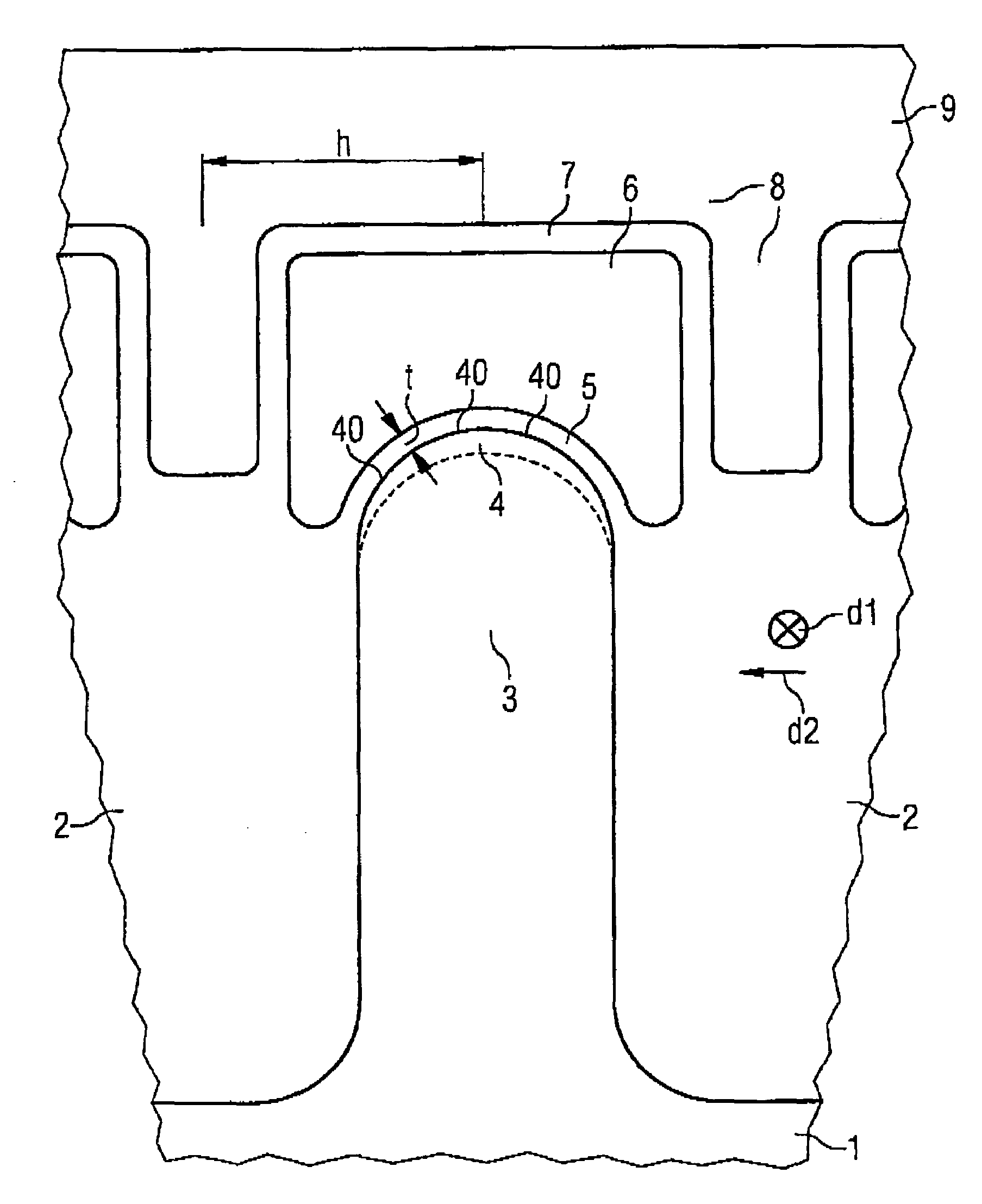

Trench misfet

InactiveUS20090072304A1Avoid widthIncrease channel widthSemiconductor devicesEngineeringElectrical and Electronics engineering

In one embodiment of the present invention, trench sections cause regions where source diffusion sections and body diffusion sections are formed to be partitioned into line regions. The trench sections are formed not in a straight line shape but in a zigzag shape. Two adjacent trench sections are provided to be axisymmetric, having an axis of symmetry in a longitudinal direction of the trench sections. A wide region and a narrow region are alternately formed in each of the regions, partitioned by the trench sections, in which regions the source diffusion sections and the body diffusion sections are formed. Each of the body diffusion sections is formed in the wide region. This makes it possible to realize an improved power MOSFET that achieves a reduction in an ON resistance per unit cell and an increase in a layout effect.

Owner:SHARP KK

Semiconductor device

ActiveUS20140048797A1Increase manufacture rangeIncrease channel widthTransistorSolid-state devicesContact holeSemiconductor

There is provided a semiconductor device including a first conductive layer, an insulating layer, a second conductive layer, a channel layer, a passivation layer and a third conductive layer. The insulating layer covers the first conductive layer. The second conductive layer is formed on the insulating layer and has an inner opening. The channel layer is formed on the inner opening of the second conductive layer to fully cover the inner opening. The passivation layer is formed upon the channel layer to cover the channel layer and has a contact hole inside the inner opening of the second conductive layer. The third conductive layer is formed in the contact hole.

Owner:HANNSTAR DISPLAY CORPORATION

Semiconductor memory device comprising memory cells with floating gate electrode and method of production

InactiveUS7250651B2InhibitionReduce impactTransistorSolid-state devicesDielectricSemiconductor materials

Owner:POLARIS INNOVATIONS LTD

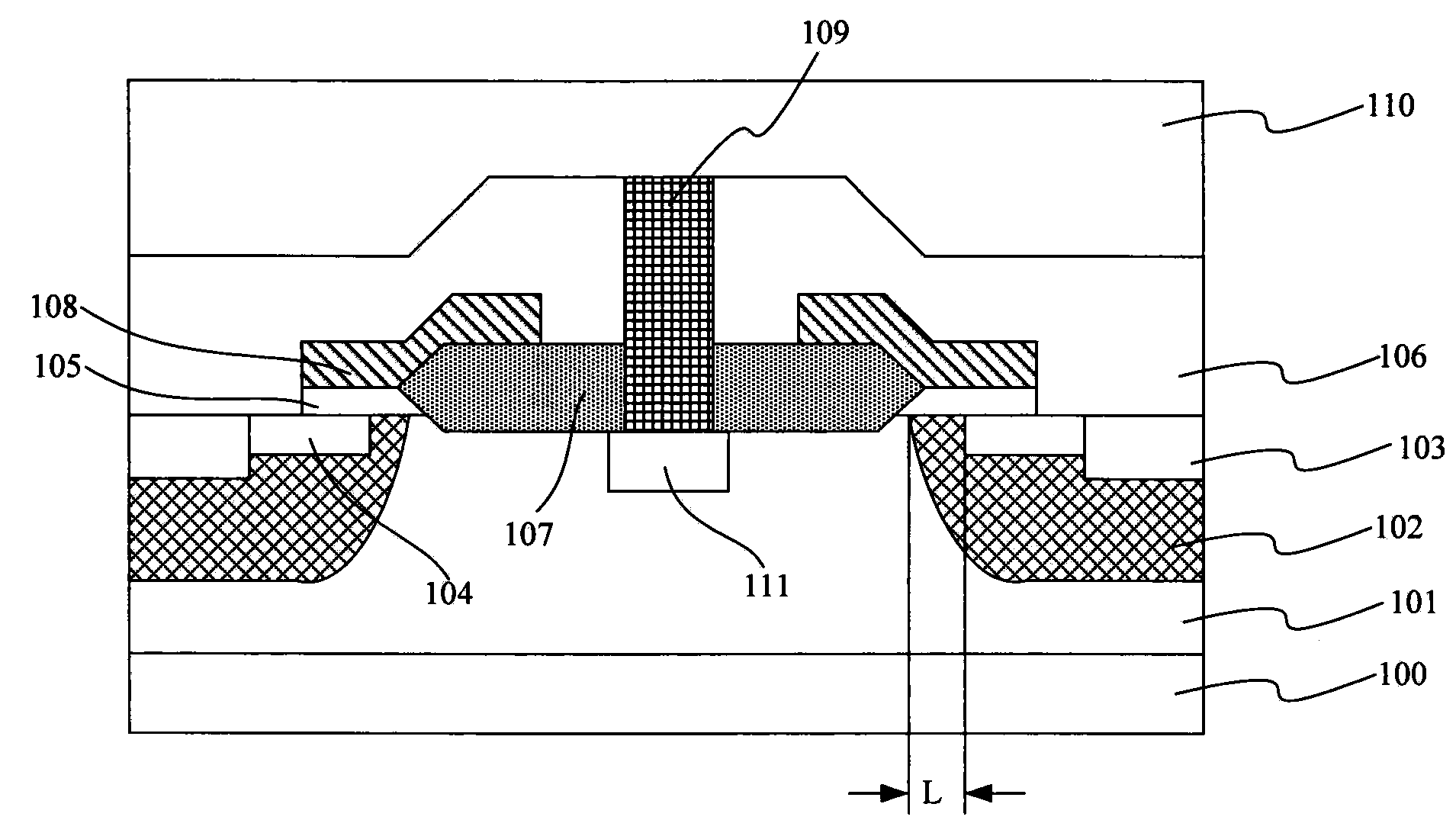

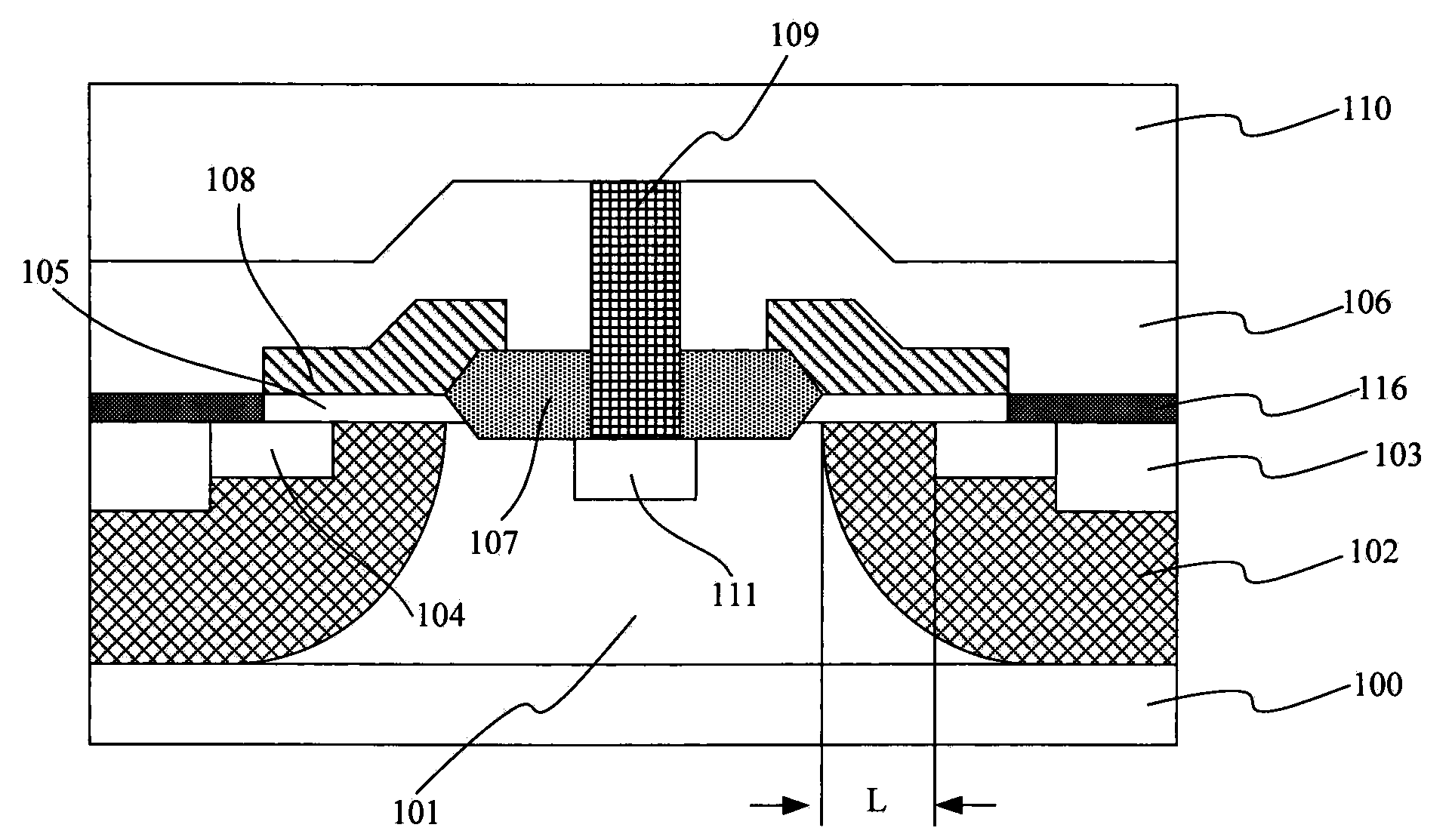

Metal-oxide-semiconductor transistor device, manufacturing method thereof, and method of improving drain current thereof

InactiveUS20080017931A1Easy to drainIncrease channel widthSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDrain current

A metal-oxide-semiconductor transistor device comprises a semiconductor substrate comprising an active region and an insulation region, a selective epitaxial layer between the active region and a gate structure, wherein a peripheral portion of the epitaxial layer is over a peripheral portion of the insulation region, such that the width of the channel is increased and a drain current is improved.

Owner:UNITED MICROELECTRONICS CORP

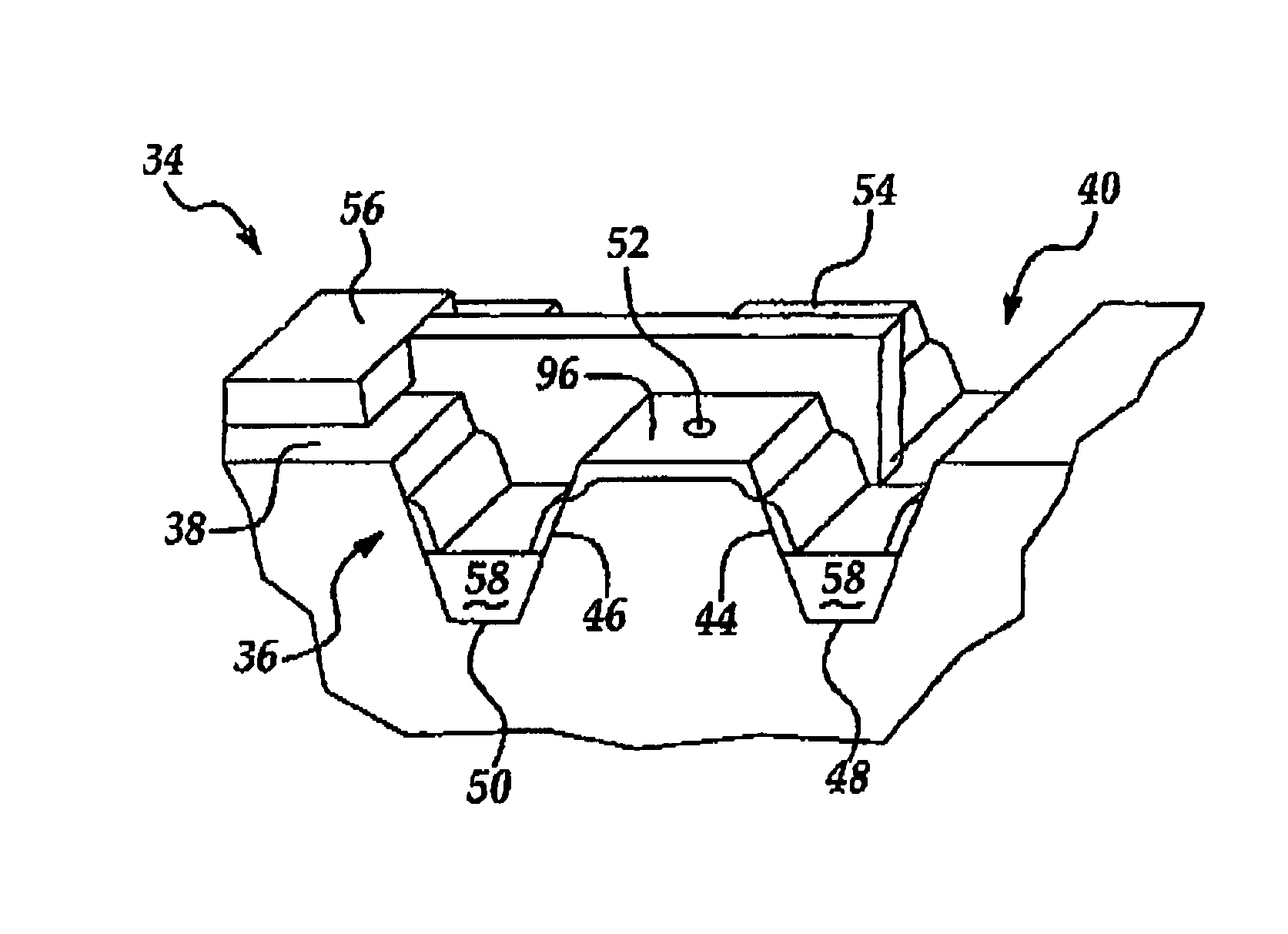

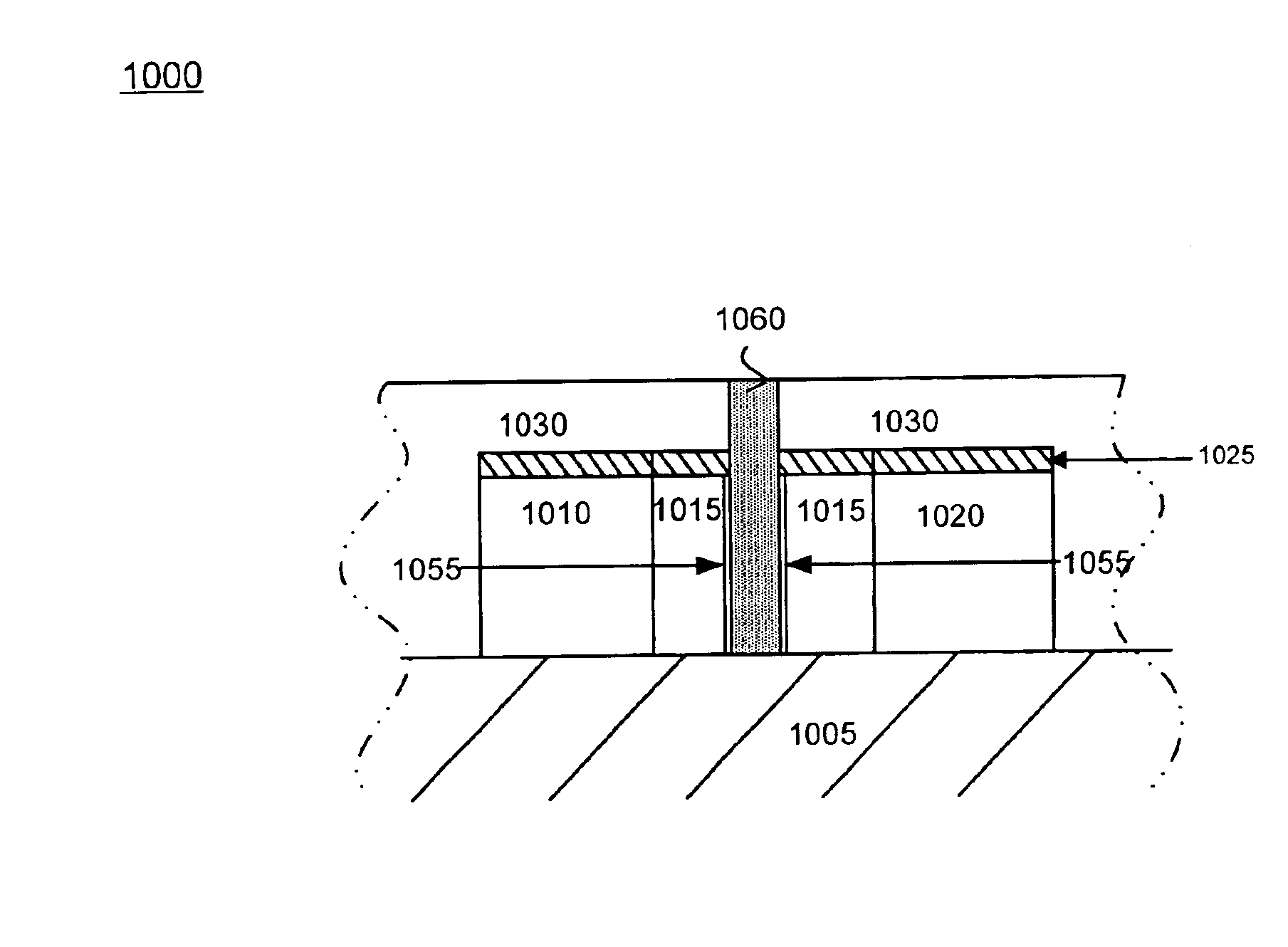

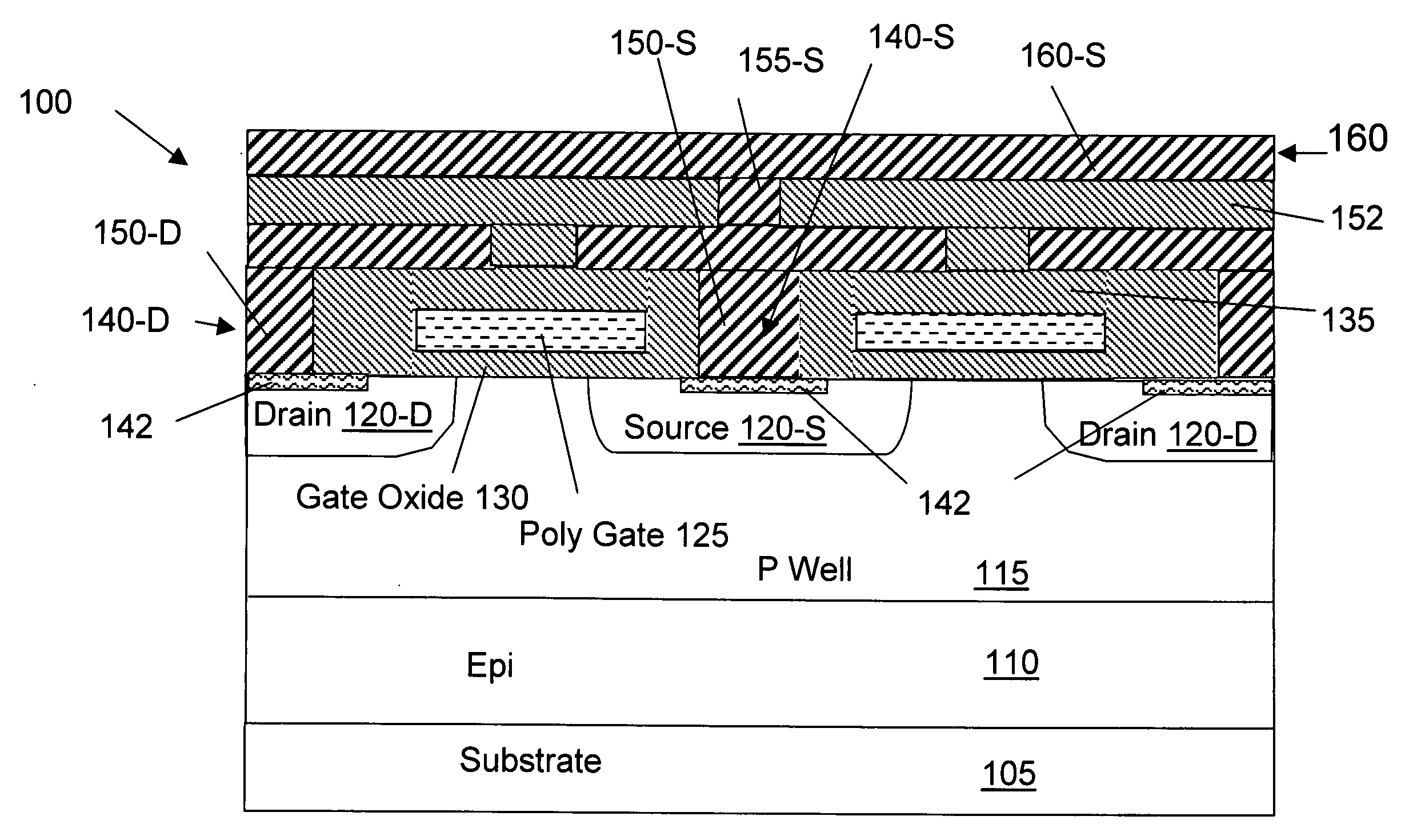

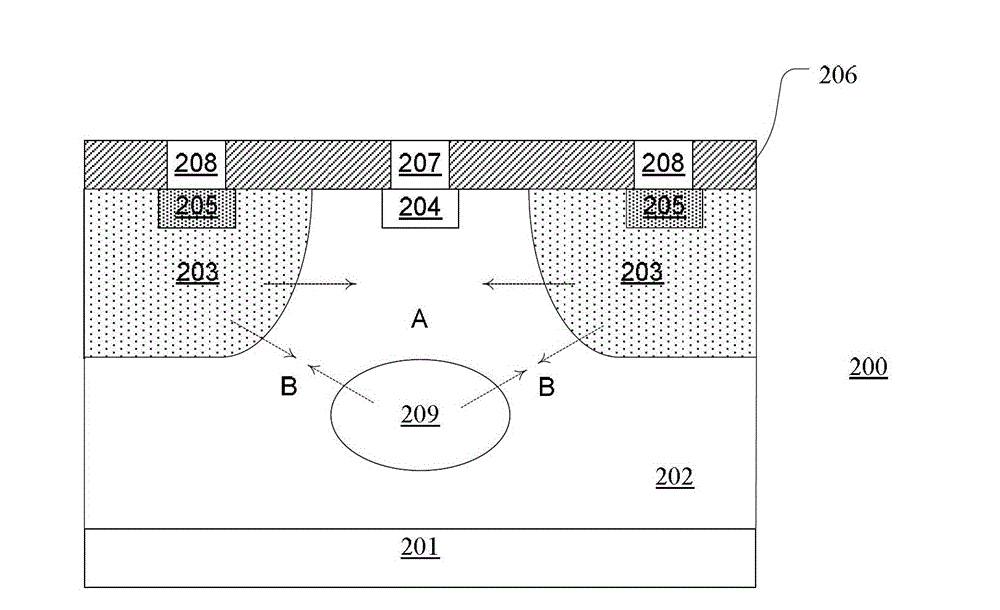

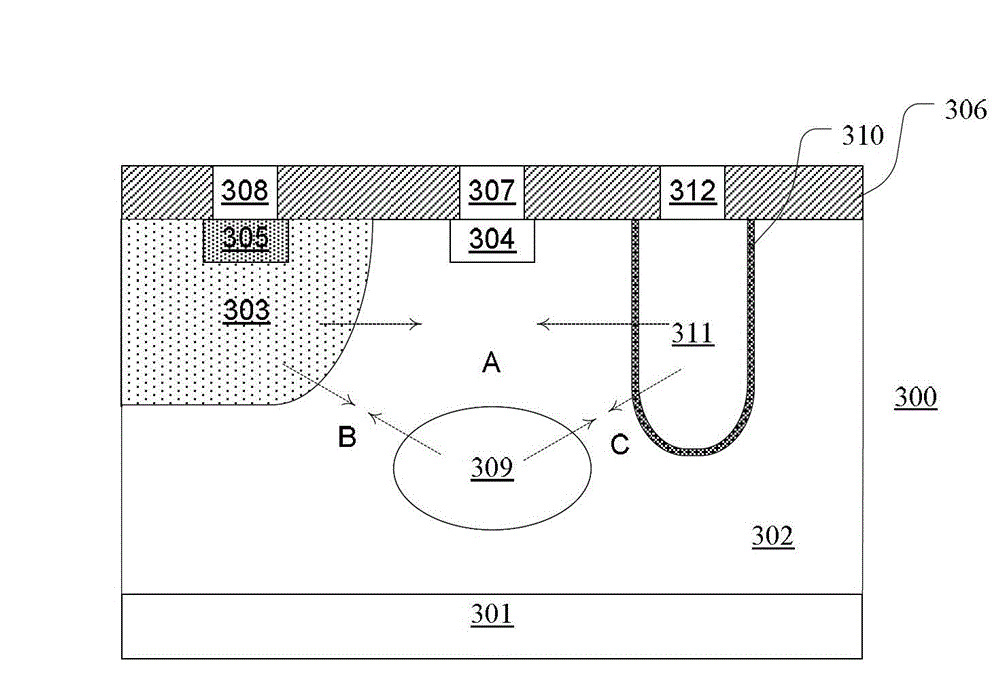

High performance device design

ActiveUS20070075377A1Increase channel widthTotal current dropSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentSemiconductor structure

A semiconductor structure having a recessed active region and a method for forming the same are provided. The semiconductor structure comprises a first and a second isolation structure having an active region therebetween. The first and second isolation structures have sidewalls with a tilt angle of substantially less than 90 degrees. The active region is recessed. By recessing the active region, the channel width is increased and device drive current is improved.

Owner:TAIWAN SEMICON MFG CO LTD

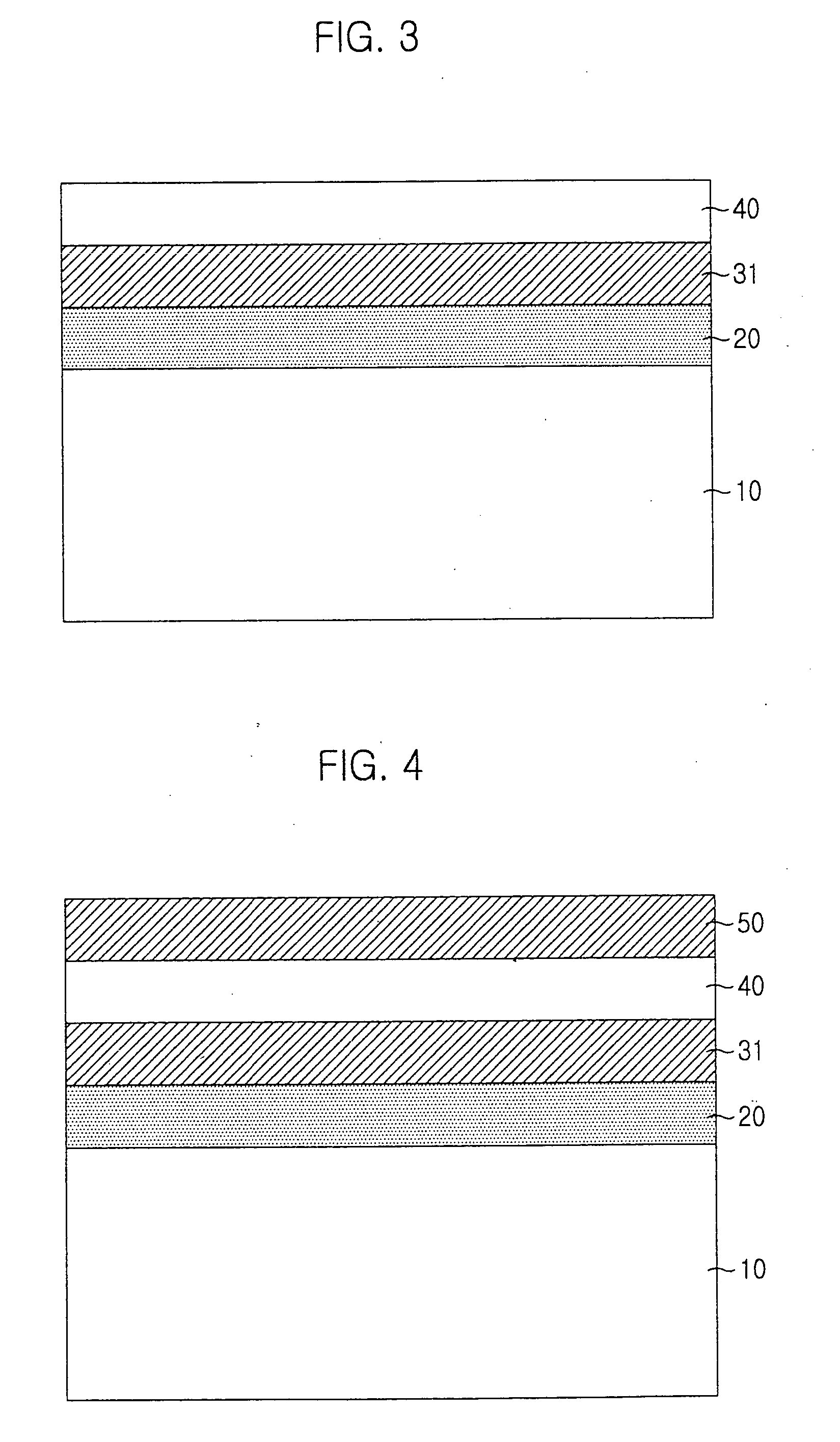

Phase change storage unit based on VOx gate tube

ActiveCN106992251AAchieve High Density StorageSimple preparation processElectrical apparatusDigital storagePhase-change memoryLow voltage

The invention discloses a phase change storage unit based on a VOx gate tube. The storage unit comprises a lower electrode layer, a VOx gating layer, a phase change function layer and an upper electrode layer. According to the invention, by use of the VOx, the gating of the phase change function layer is achieved; storage of the data is achieved on the basis of gating of the phase change function layer; by imposing voltage on the VOx, the state switching of the VOx is controlled, so an objective that the phase change storage unit is in a non-gating state during low voltage and in a gating system during high voltage can be achieved; through the switch control of the VOx, leakage current of the a phase change memory array can be effectively reduced and enough big Reset current is provided; a high-temperature technique condition is not required; preparation technique of the phase change memory is simplified; cost is reduced; and it is possible to commercialize the highly integrated phase change memory.

Owner:HUAZHONG UNIV OF SCI & TECH

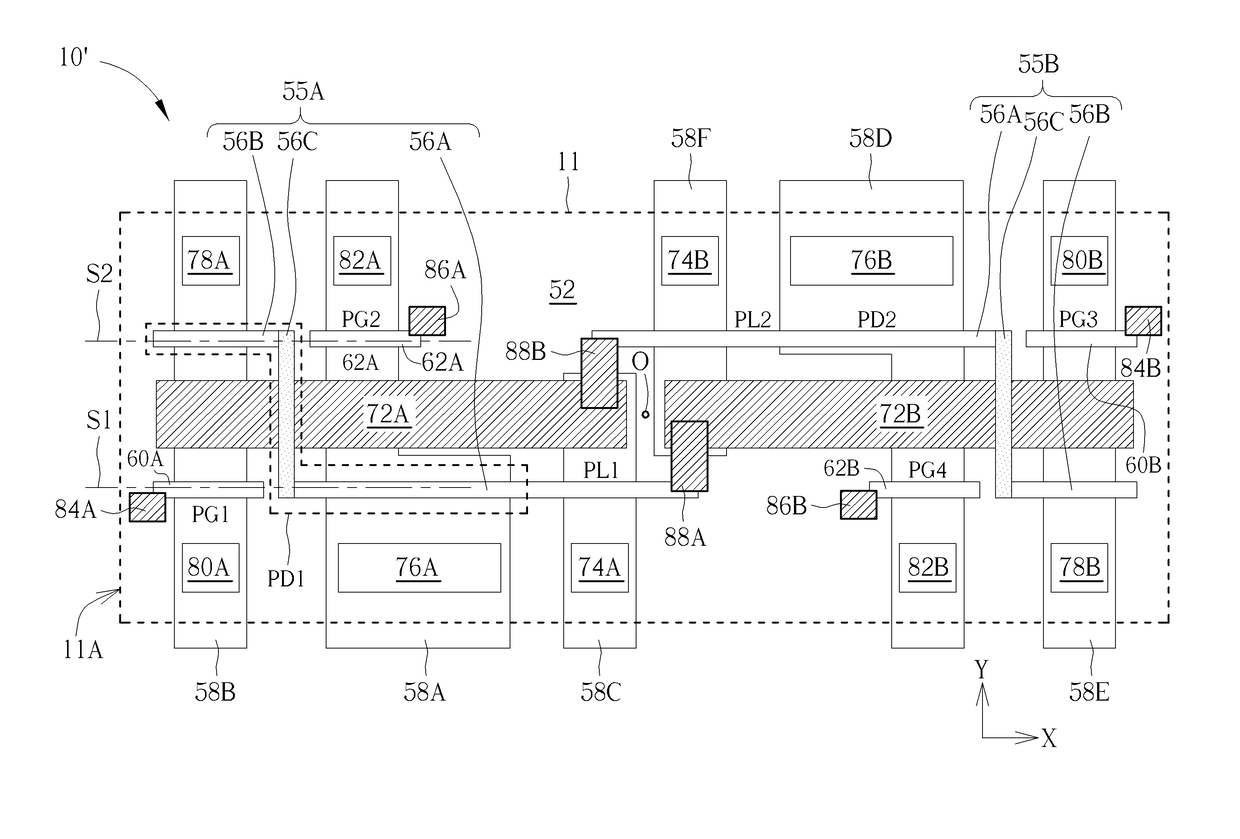

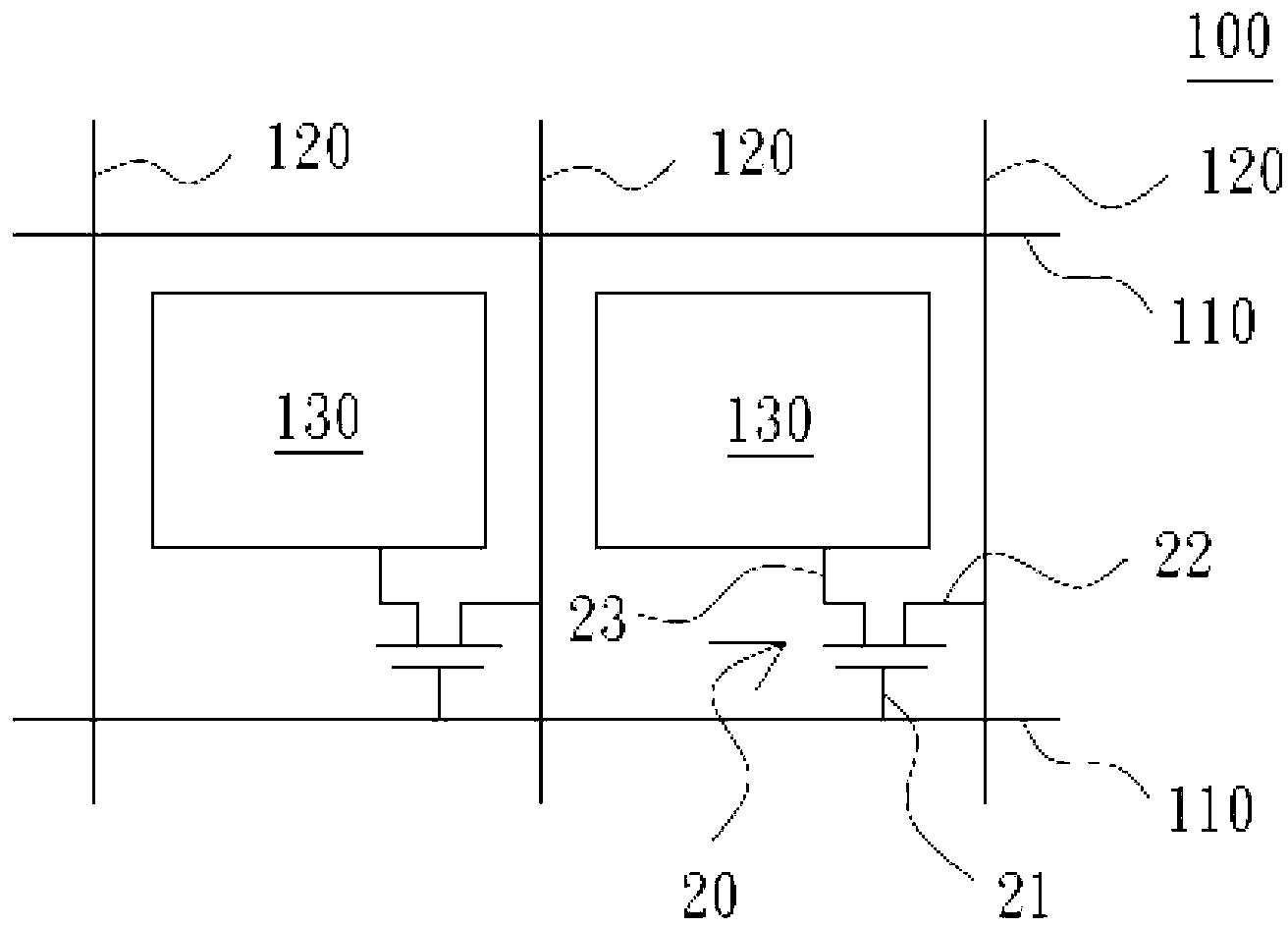

Layout pattern for static random access memory

ActiveUS9780099B1Increase channel widthIncrease currentTransistorSolid-state devicesEngineeringPass gate

A layout pattern of a static random access memory includes a pull-up device, a first pull-down device, a second pull-up device, a second pull-down device, a first pass gate device, a second pass gate device, a third pass gate device and a fourth pass gate device disposed on a substrate. A plurality of fin structures is disposed on the substrate, the fin structures including at least one first fin structure and at least one second fin structure. A step-shaped structure is disposed on the substrate, including a first part, a second part and a bridge part. A first extending contact feature crosses over the at least one first fin structure and the at least one second fin structure.

Owner:UNITED MICROELECTRONICS CORP

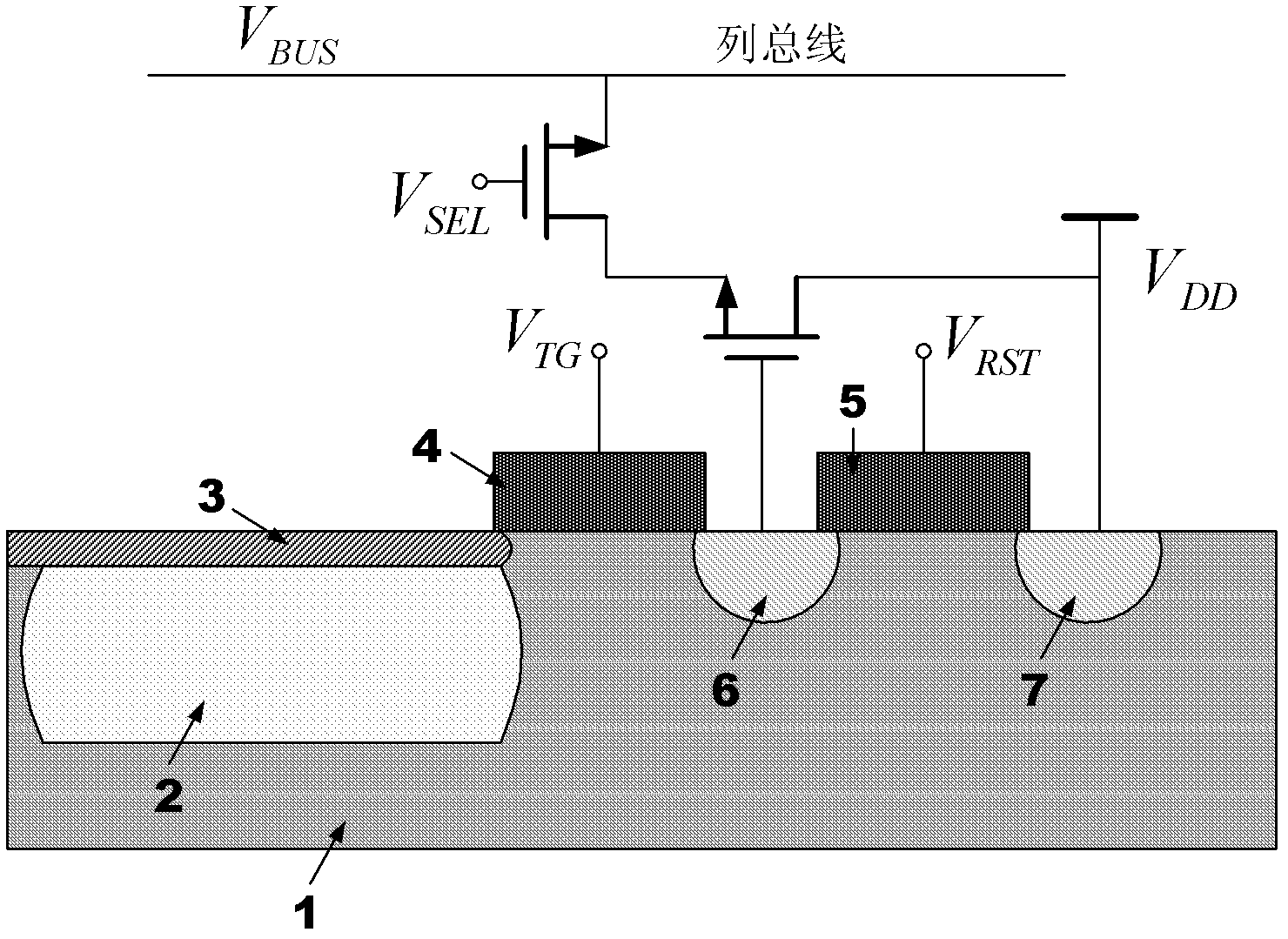

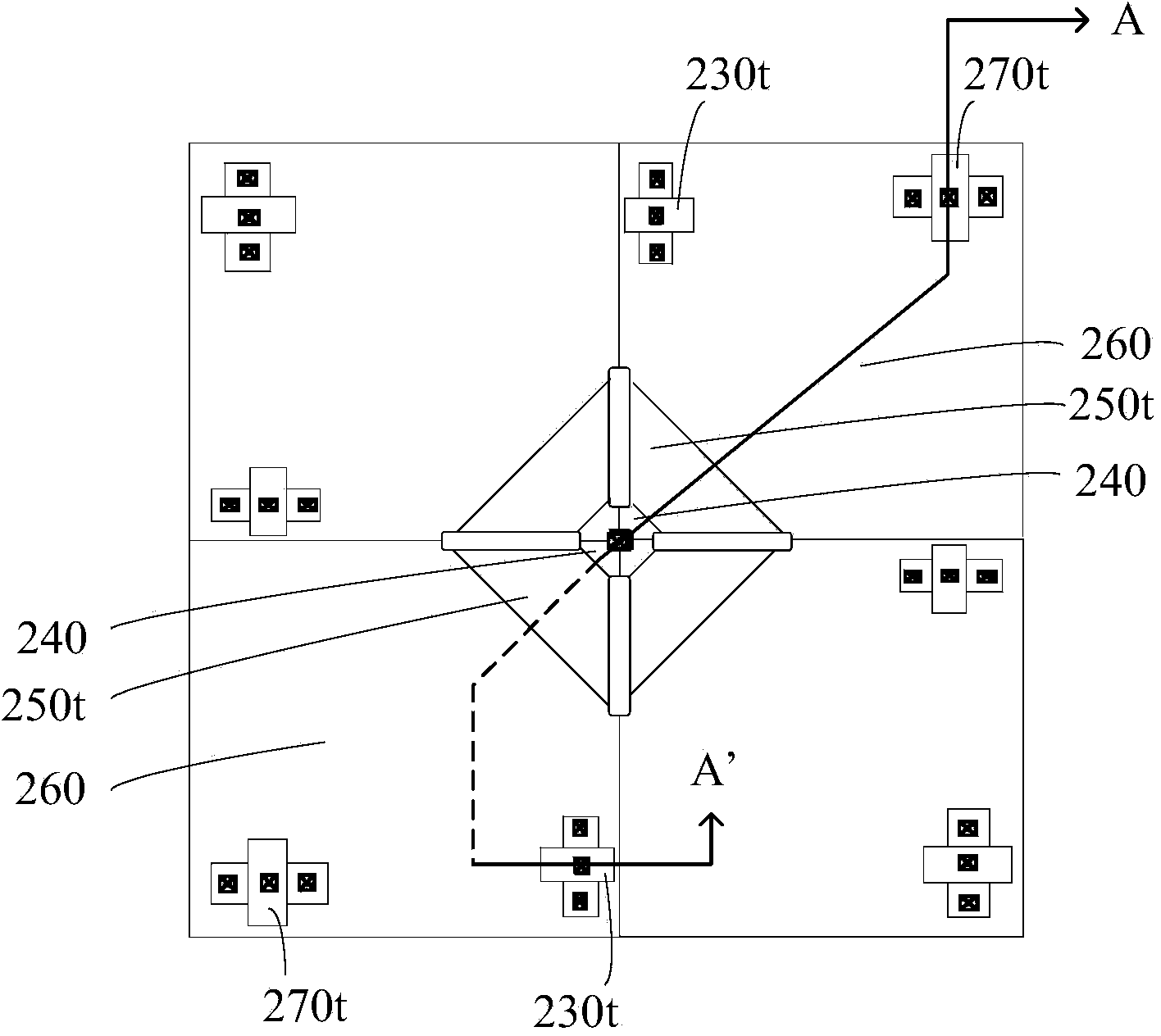

Four-tube active pixel of rapid charge transfer and making method thereof

ActiveCN102324430AEasy transferIncrease channel widthTransistorSolid-state devicesP type siliconPolysilicon gate

The invention belongs to the field of integrated circuit design and integrated circuit process of microelectronics and relates to a four-tube active pixel of rapid charge transfer. The four-tube active pixel of the rapid charge transfer comprises a photoelectric diode, a transmission tube, a reset tube, a source follower and a gate tube which are made on a P type substrate, wherein a region N of the photoelectric diode comprises a first N type injection layer and a second N type injection layer with lower dosage concentration, wherein the second N type injection layer is arranged on the firstN type injection layer; layout positions of the two N type injection layers and a polysilicon gate of the transmission tube exist an overlapped region; a P type silicon semiconductor injection layer with unbalanced dosage concentration is arranged in the overlapped region and an under-gate region of the transmission tube; the dosage concentration of the P type silicon semiconductor injection layer is highest in the overlapped region; the dosage of the grid of the polycrystalline silicon of the transmission tube is N- dosage on one side of the overlapped region and N+ dosage on one side of a non-overlapped region; and a clamping layer is arranged between the non-overlapped region of the region N of the photoelectric diode and the silicon surface. Meanwhile, the invention provides a making method of the active pixel. The pixel provided by the invention can obtain rapid charge transfer without tailing.

Owner:TIANJIN UNIV

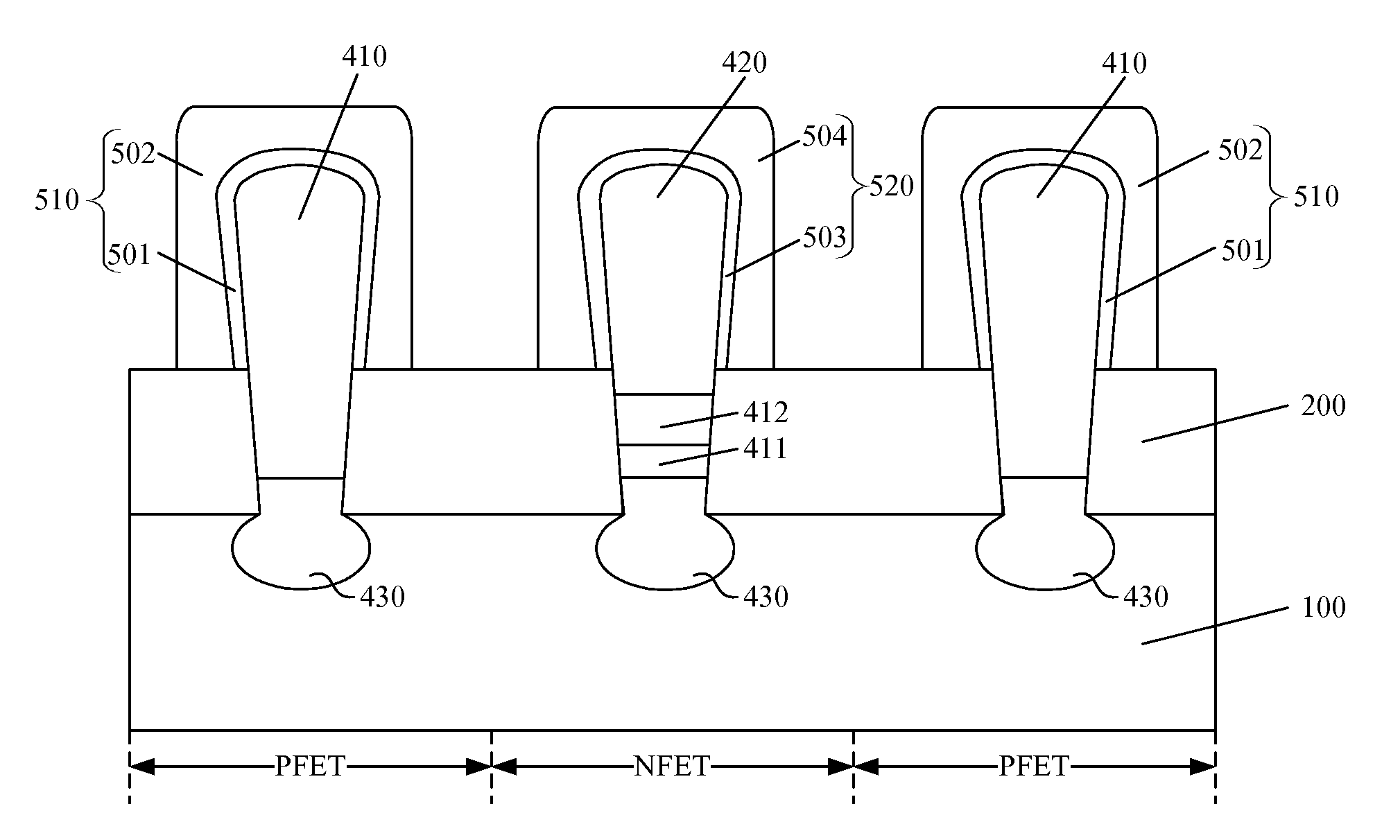

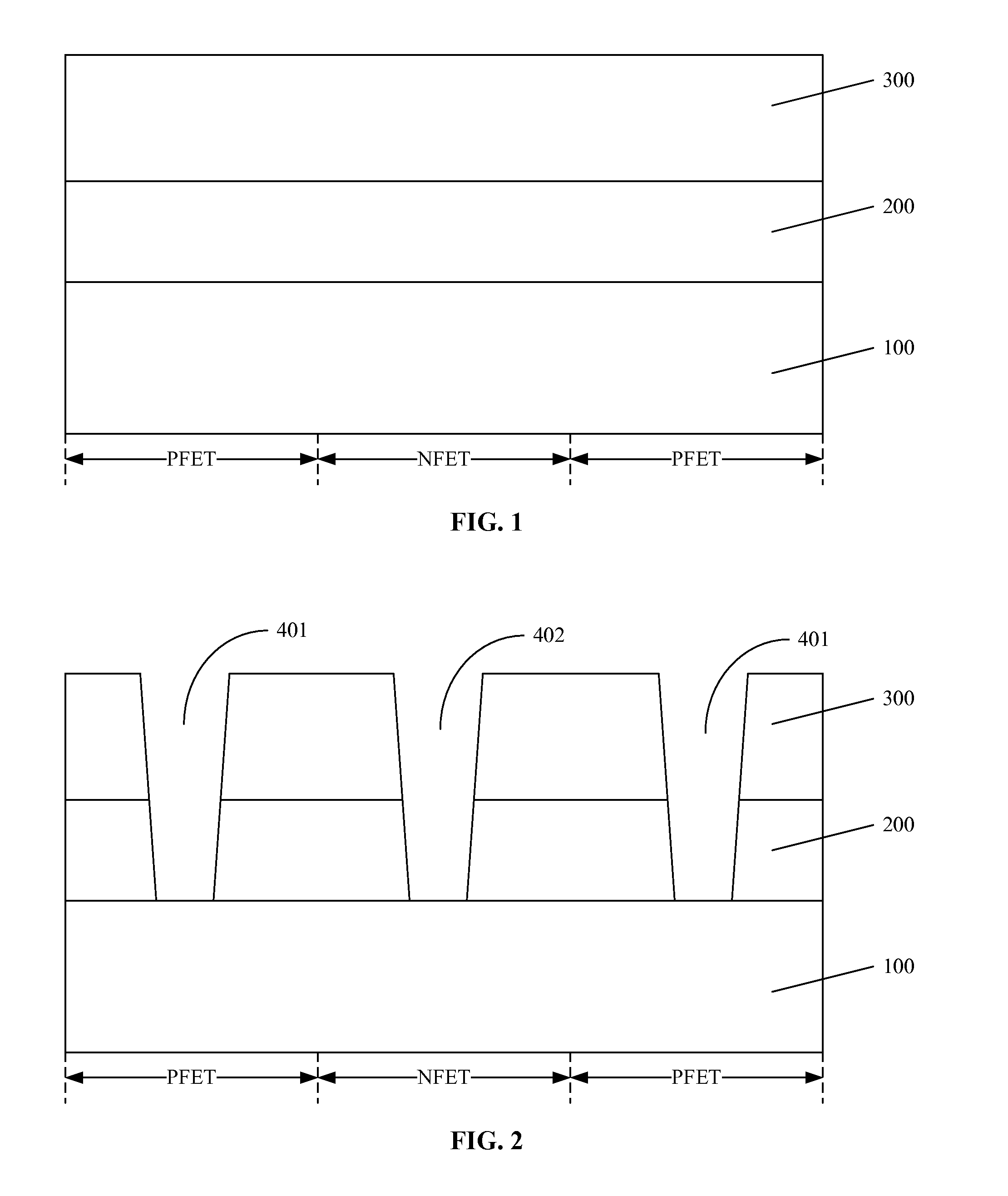

Semiconductor structures and fabrication methods thereof

ActiveUS20160064289A1Reduce difficultyImprove performanceTransistorSolid-state devicesElectrical conductorInsulation layer

A method for forming a semiconductor structure includes sequentially providing a semiconductor substrate having NFET regions and NFET regions; forming an insulation layer on the semiconductor substrate; forming a sacrificial layer on the insulation layer; forming first trenches in the PFET regions, and second trenches in in the NFET regions; forming a third trench on the bottom of each of the first trenches and the second trenches; forming a first buffer layer in each of the first trenches and the second trenches by filling the third trenches; forming a first semiconductor layer on each of the first buffer layers in the first trenches and the second teaches; removing the first semiconductor layers in the second trenches; forming a second buffer layer with a top surface lower than the insolation layer in each of second trenches; and forming a second semiconductor layer on each of the second buffer layers.

Owner:SEMICON MFG INT (SHANGHAI) CORP

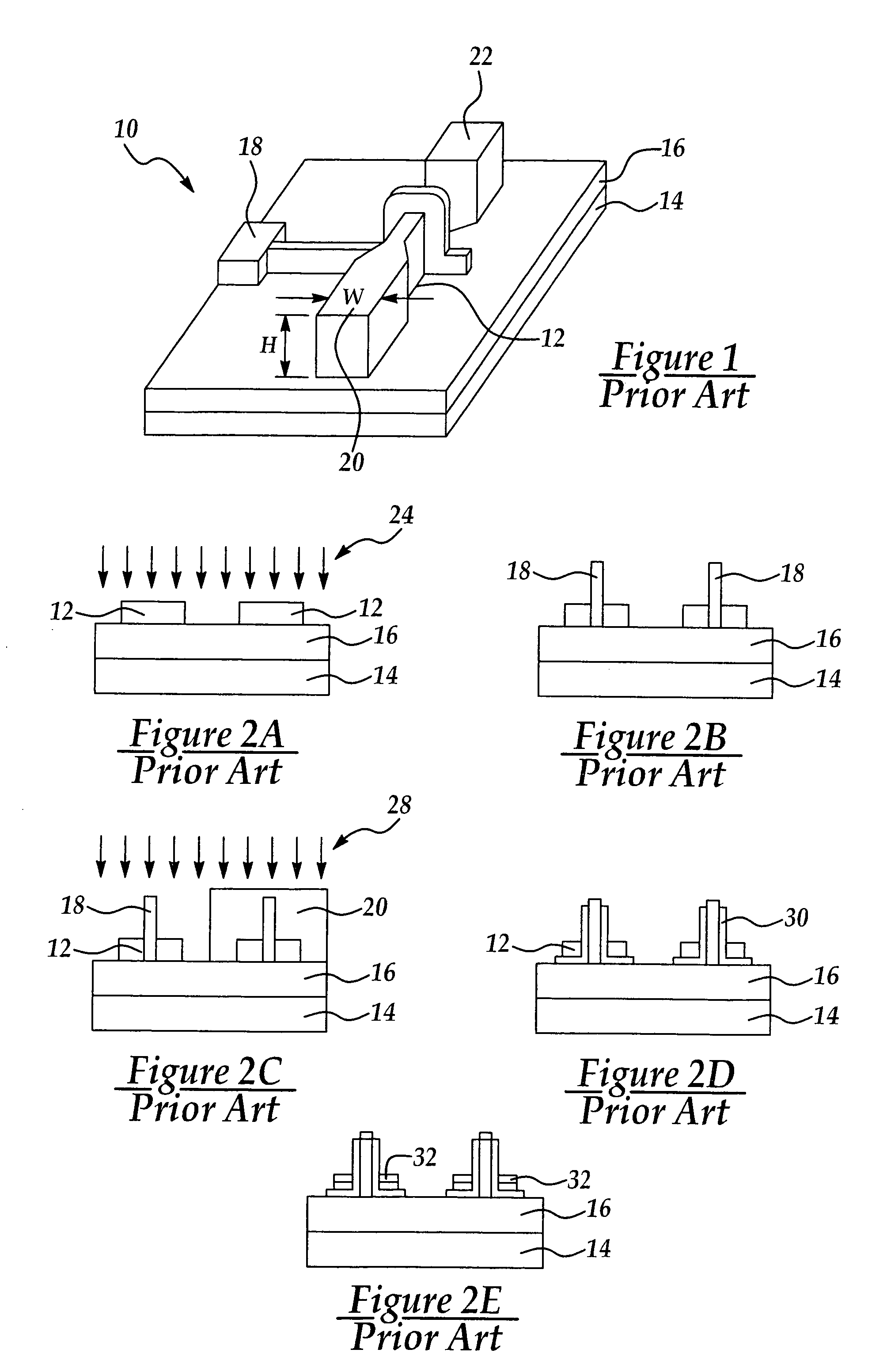

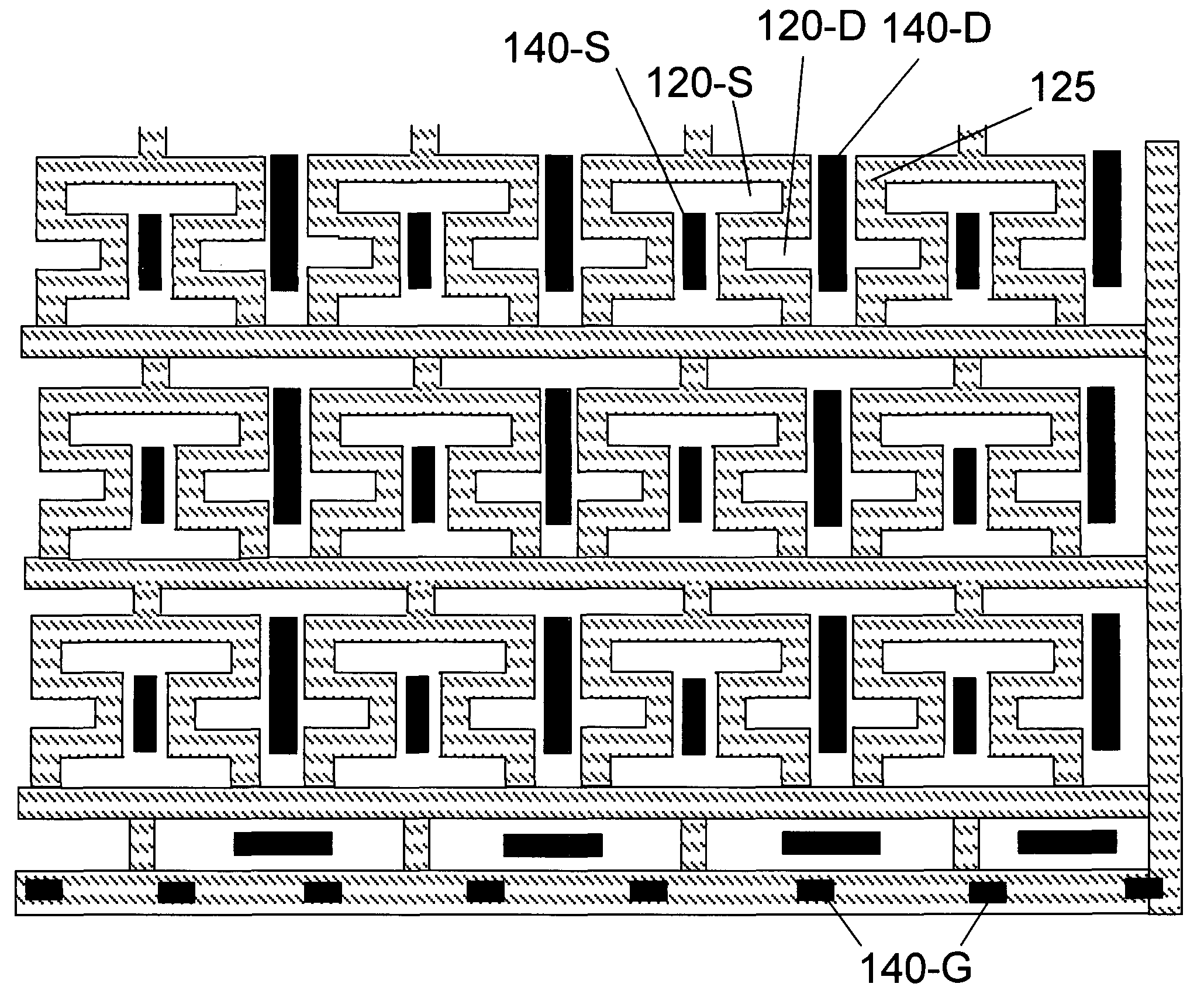

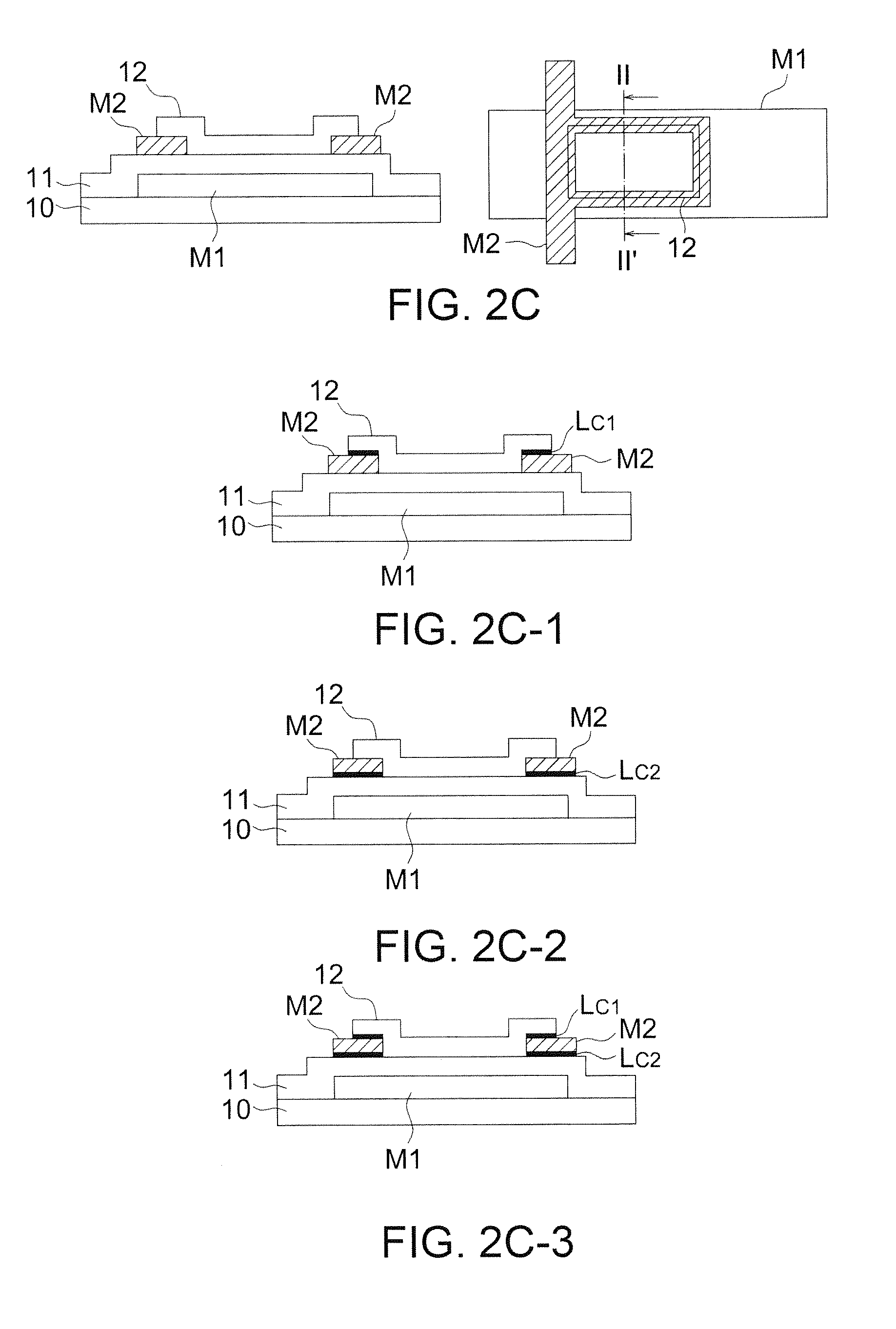

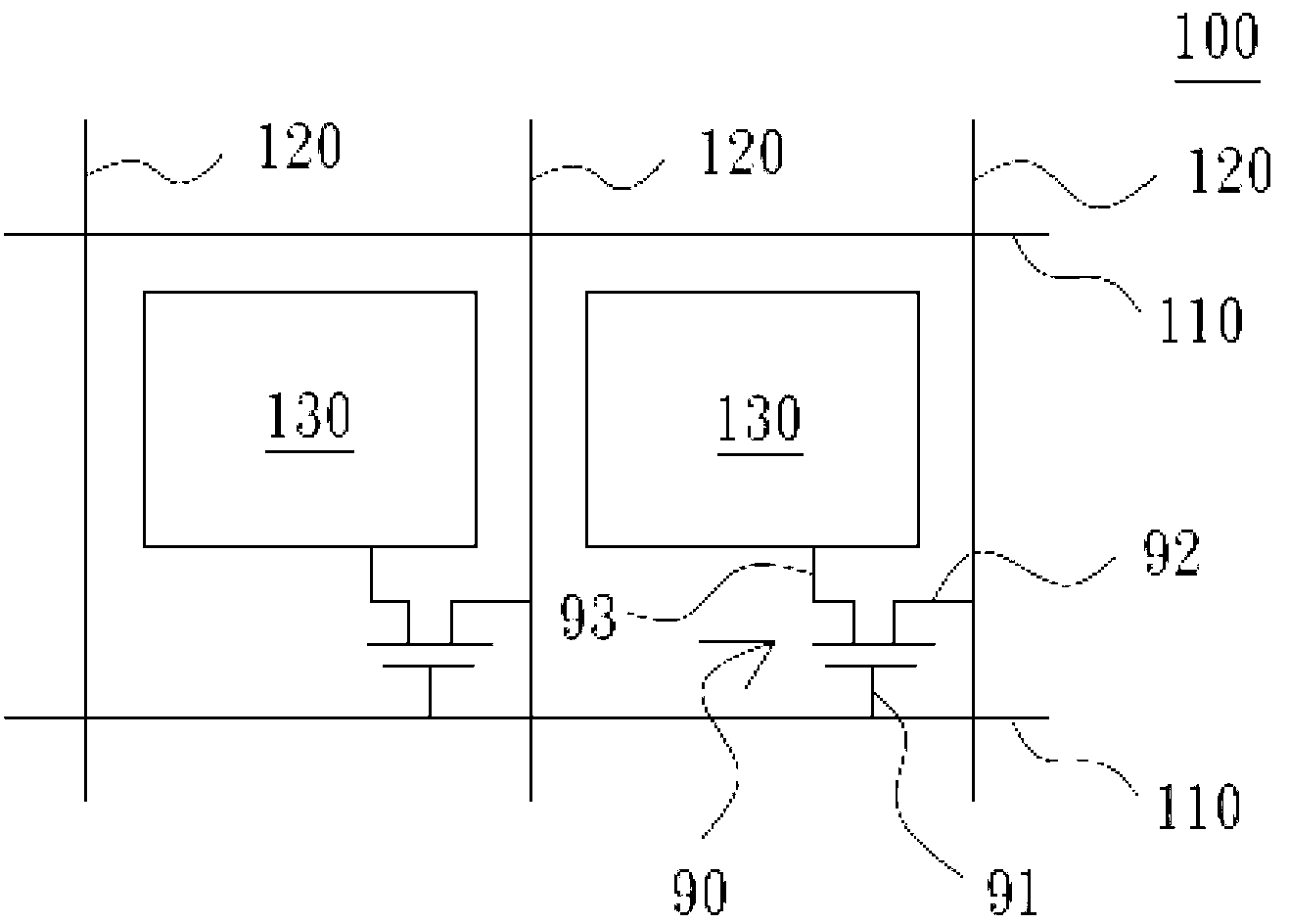

Closed cell configuration to increase channel density for sub-micron planar semiconductor power device

ActiveUS20070295996A1Increase channel width per unit areaIncrease the on-resistanceTransistorSemiconductor/solid-state device detailsChannel densityEngineering

A semiconductor power device supported on a semiconductor substrate that includes a plurality of transistor cells, each cell has a source and a drain region disposed on opposite sides of a gate region in the semiconductor substrate. A gate electrode is formed as an electrode layer on top of the gate region for controlling an electric current transmitted between the source and the drain regions. The gate electrode layer disposed on top of the semiconductor substrate is patterned into a wave-like shaped stripes for substantially increasing an electric current conduction area between the source and drain regions across the gate.

Owner:ALPHA & OMEGA SEMICON LTD

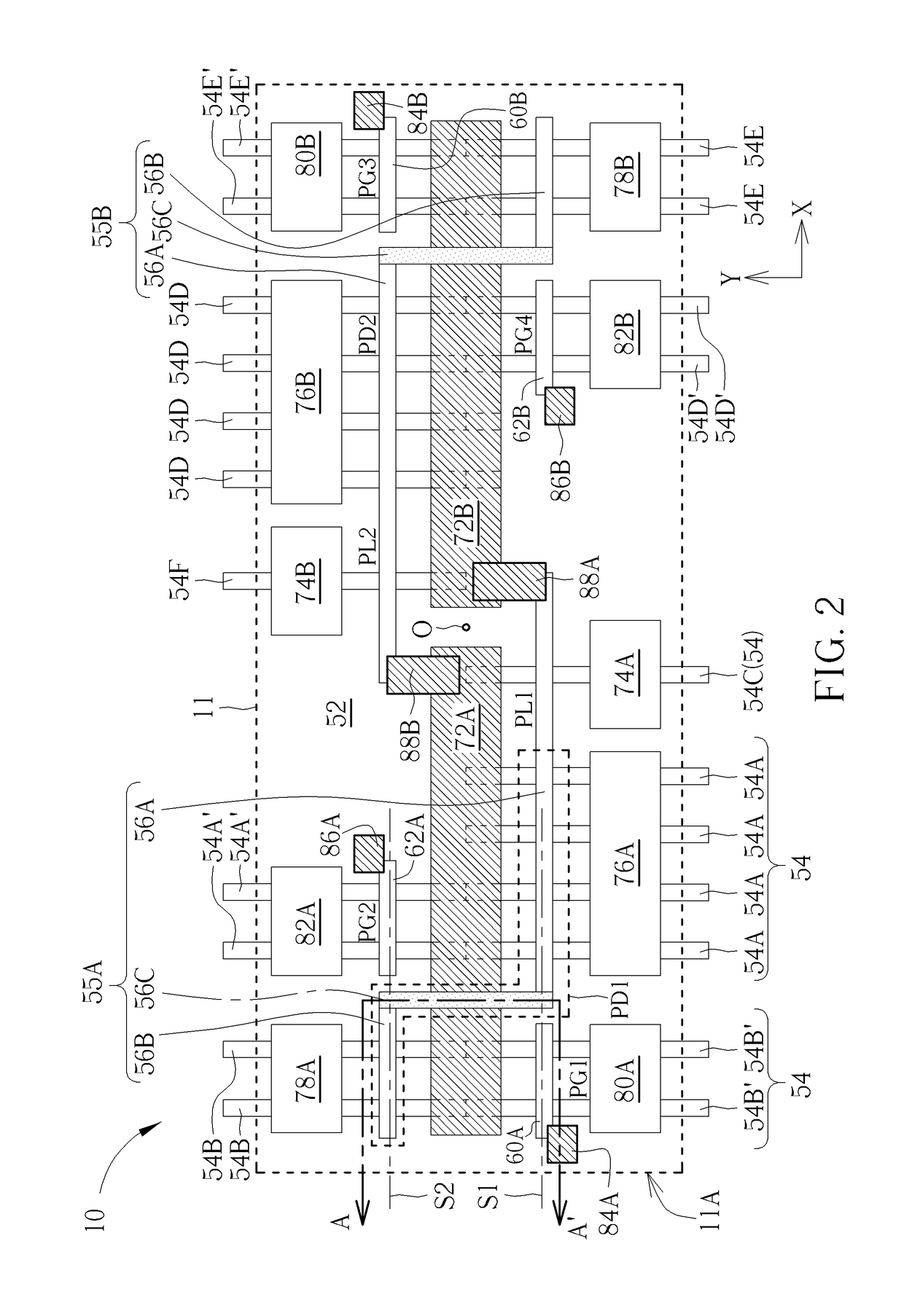

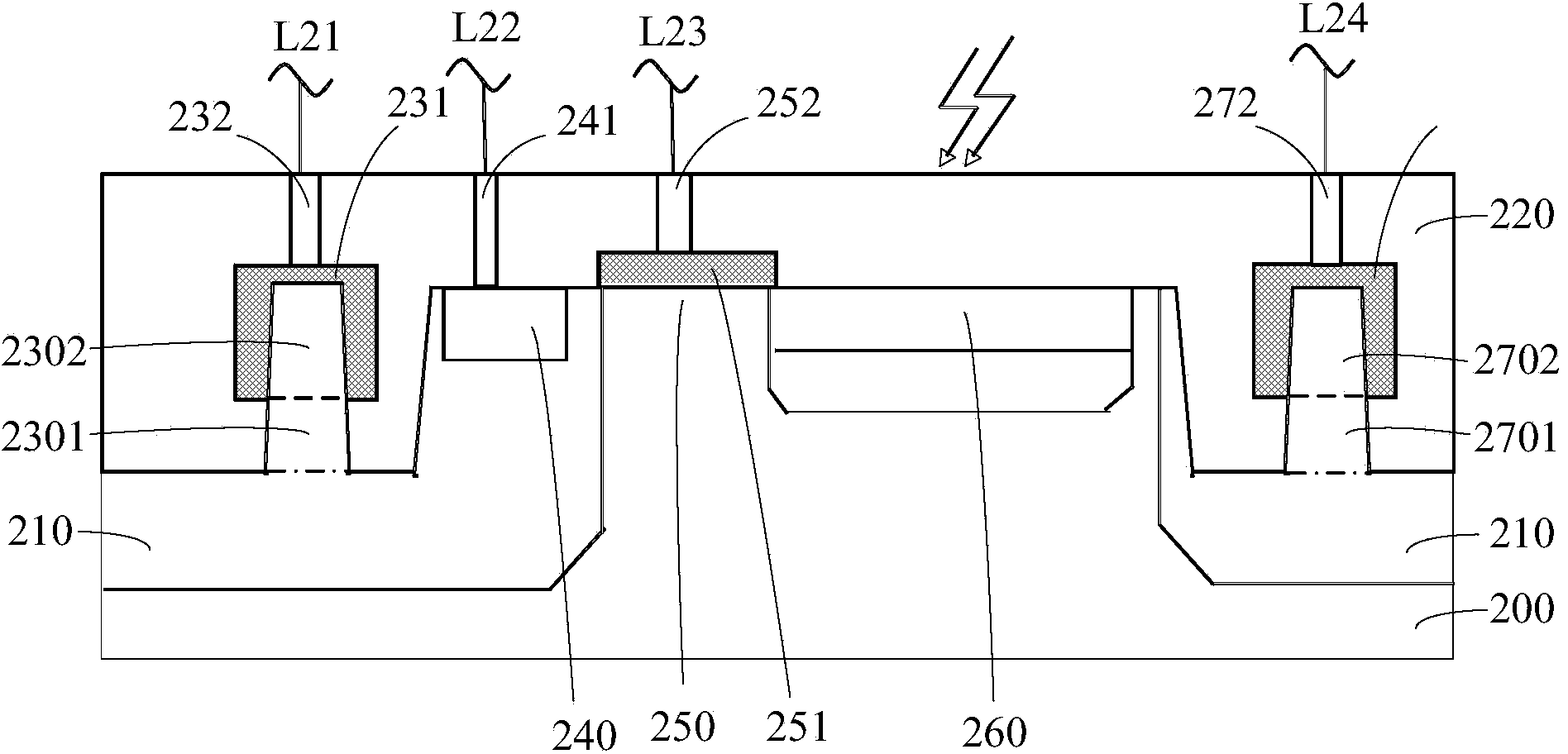

Image sensor and forming method thereof

ActiveCN103928486AFlexible controlImprove performanceRadiation controlled devicesEngineeringFloating diffusion

The invention discloses an image sensor and a forming method thereof. The image sensor comprises a pixel array, and the pixel array comprises a plurality of pixel units which are arranged in an array mode. Each pixel unit comprises a semiconductor substrate, a photodiode, a floating diffusion region, a transfer transistor and a source-follower transistor, wherein the photodiode is placed in the semiconductor substrate, the floating diffusion region is placed in the semiconductor substrate, the transfer transistor comprises a source electrode and a drain electrode which are placed in the semiconductor substrate, the source electrode and the drain electrode are electrically connected with a photovoltaic conversion element and the floating diffusion region respectively, the source-follower transistor comprises a grid electrode placed on the semiconductor substrate, the grid electrode is electrically connected with the floating diffusion region, a channel region of the source-follower transistor is of a cross beam structure, the cross beam structure is provided with a top face and two side faces, and the grid electrode of the source-follower transistor covers at least one of the top face and the two side faces. The performance of the image sensor is improved, and cost is lowered.

Owner:GALAXYCORE SHANGHAI

Semiconductor device comprising junction type filed effect transistor and manufacturing method thereof

ActiveCN102916049AEnhanced pinch-off effectLower pinch-off voltageTransistorSolid-state devicesDevice materialEngineering

The invention discloses a semiconductor device comprising a junction type field effect transistor and a manufacturing method thereof. The semiconductor device comprises a junction type field effect transistor, wherein the junction type field effect transistor comprises a semiconductor underlay, an epitaxial layer, a body region, a source electrode region and a grid region, wherein the semiconductor underlay is provided with a first doping type and taken as a drain region of the junction type field effect transistor; the epitaxial layer is located on the semiconductor underlay and provided with a first doping type; the body region is located in the epitaxial layer and provided with a second doping type, and the types of the second doping type and the first doping type are reverse; the source electrode is located in the epitaxial layer and provided with a first doping type; and the grid region is located in the body region and provided with the second doping type, wherein the junction type field effect transistor further comprises a shielding layer, the shielding layer is provided with the second doping type, which is located in the epitaxial layer, and is also located in a conduction path between the source electrode region and the drain region. With the adoption of the shielding layer, a new pinch-off region is generated in the junction type field effect transistor, so as to reduce pinch-off voltage.

Owner:CHENGDU MONOLITHIC POWER SYST

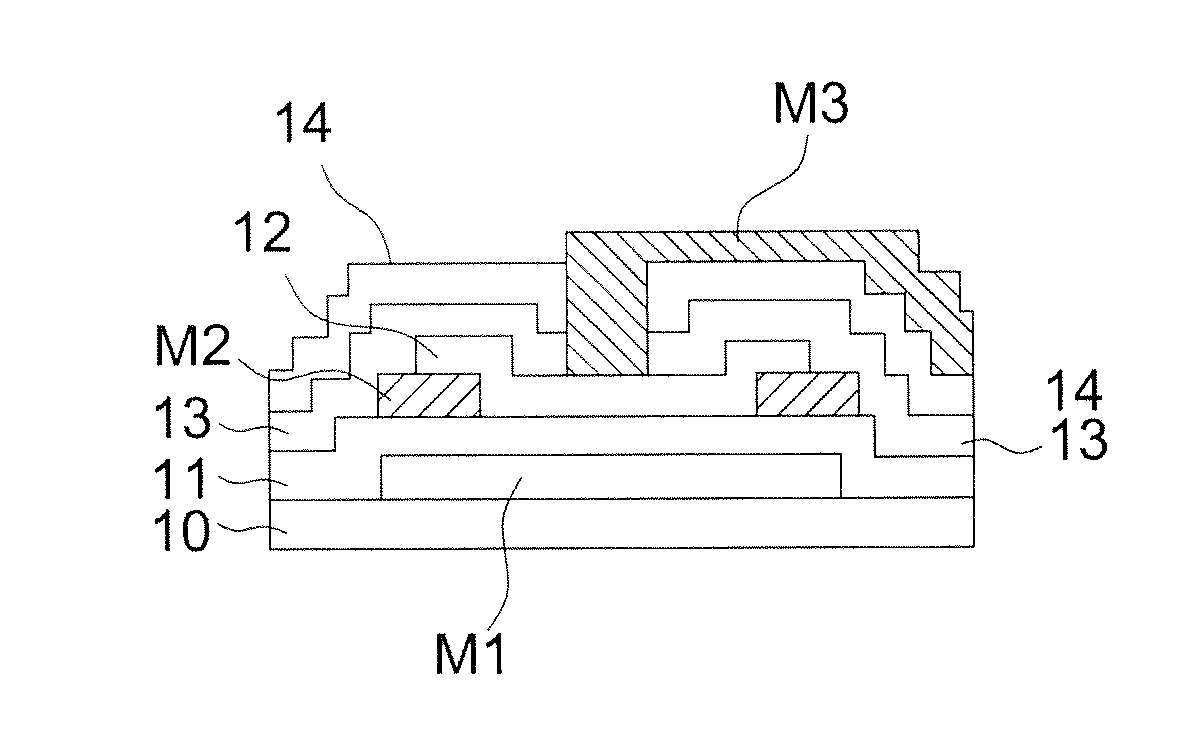

LDMOS transistor and manufacturing method thereof

ActiveCN103390645AIncrease channel widthReduced source areaSemiconductor/solid-state device manufacturingSemiconductor devicesP type dopingPolycrystalline silicon

The invention discloses an LDMOS which comprises a P-type substrate, an N-type epitaxial layer, a P trap, a first N-type doping region, a groove, a first metal layer and a source-electrode metal layer. The P trap is located in the N-type doping region, the first N-type doping region is arranged in the P trap, and the groove penetrates through the first N-type doping region, the P trap and the N-type epitaxial layer until the P-type substrate. A first oxidation layer is arranged on the side wall of the groove. The groove is filled with first polycrystalline silicon of P-type doping. The upper surface of the first polycrystalline silicon is located inside the P trap and is lower than the first N-type doping region. The first metal layer covers the upper surface of the first polycrystalline silicon and covers the first N-type doping region. The source-electrode metal layer is located on the back face of the P-type substrate. The invention further discloses a manufacturing method of the LDMOS. A source electrode is led out from the back face of the substrate instead of being originally led out from the front face of the substrate, the design area of the original source electrode region on the front face is effectively reduced, the design width of a channel in a gate region is increased, and the on resistance is reduced.

Owner:WILL SEMICON (SHANGHAI) CO LTD

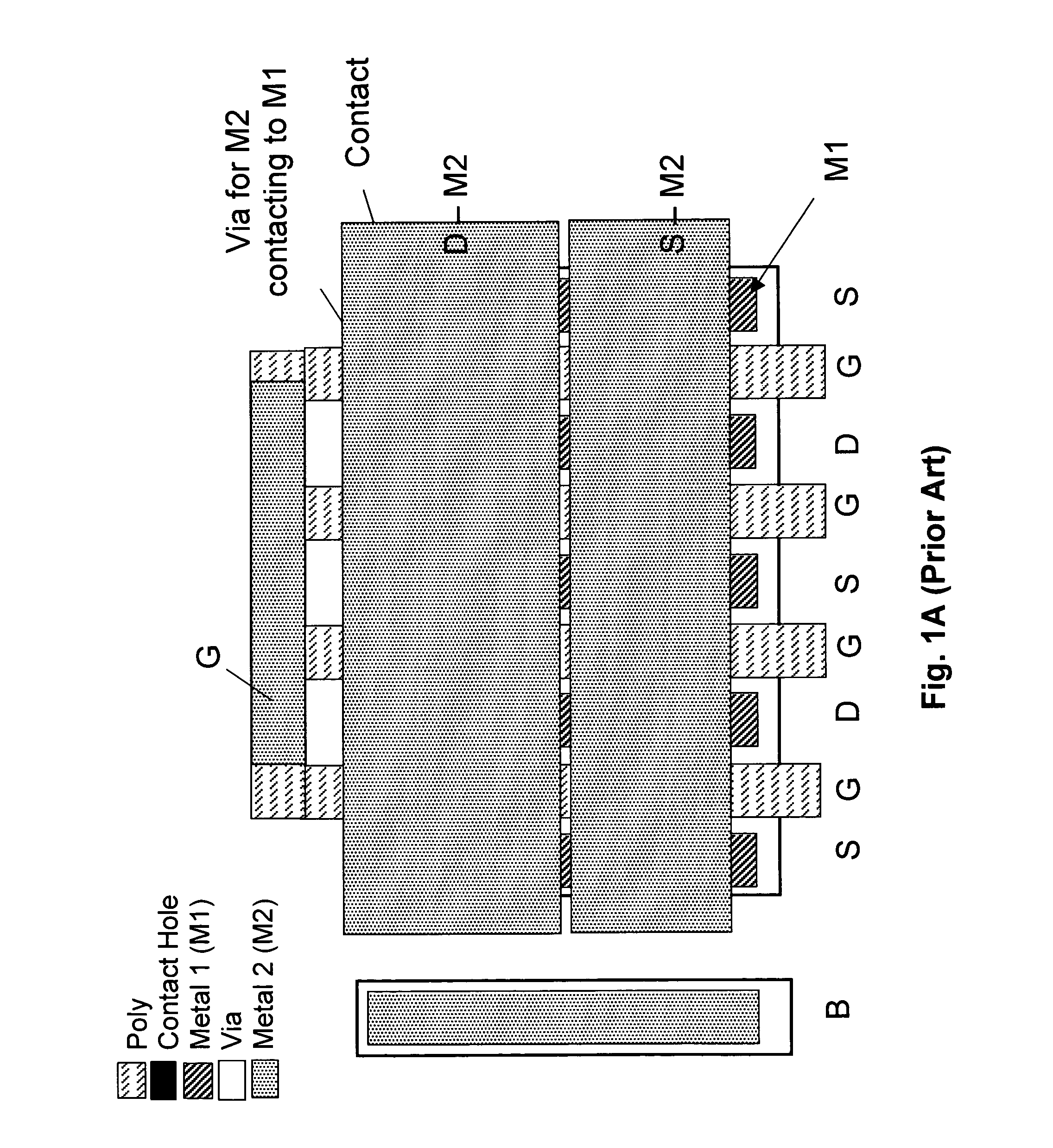

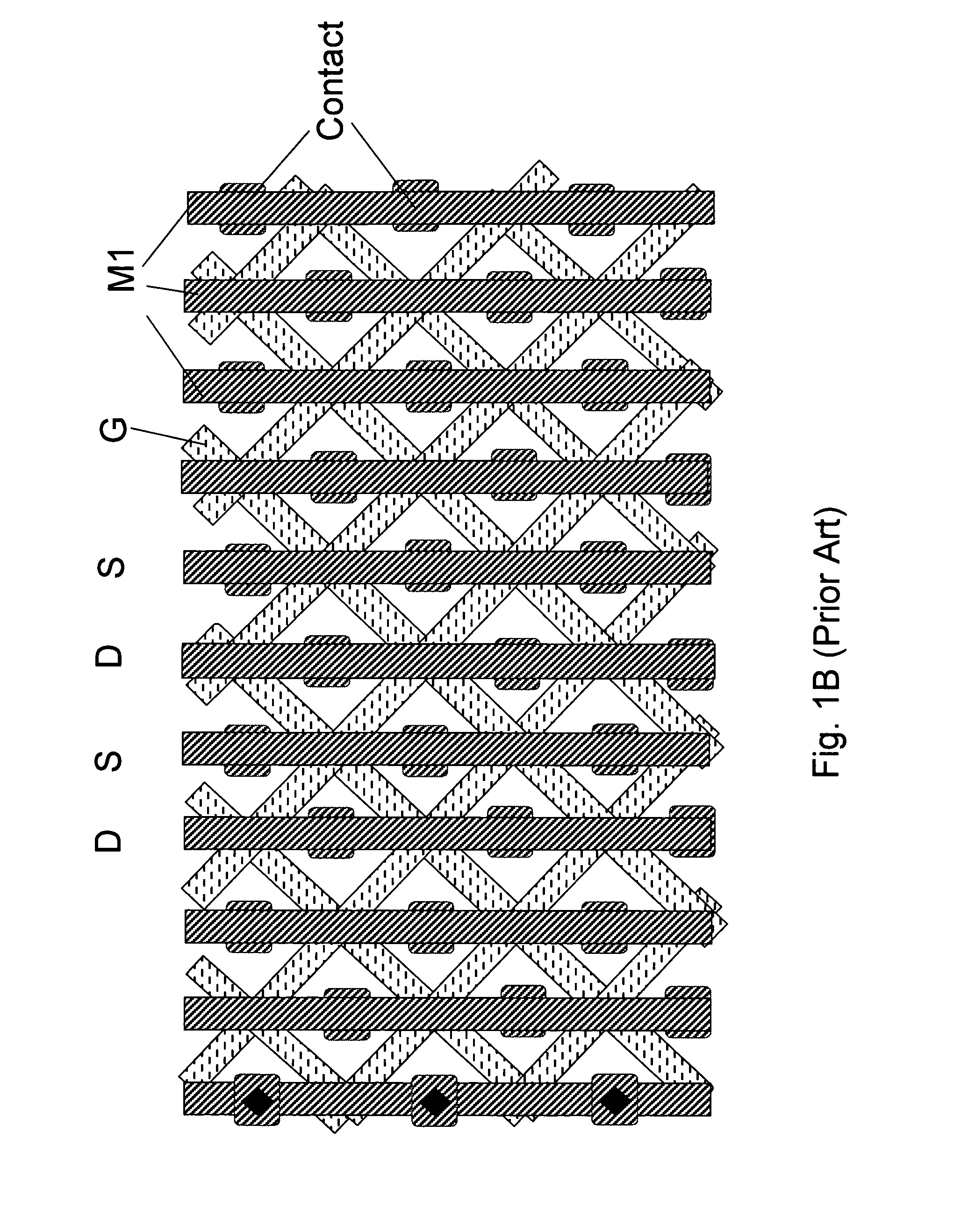

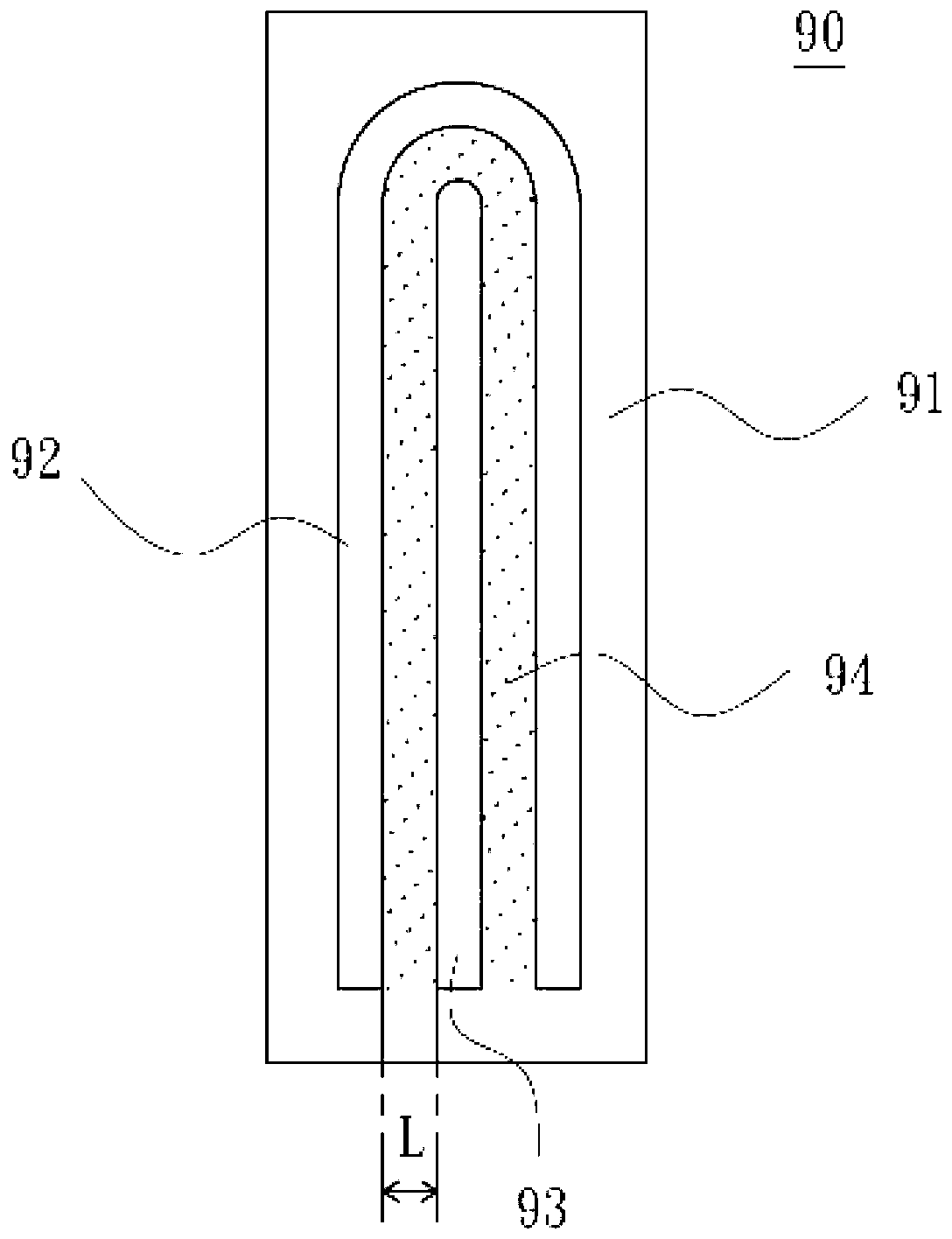

Thin film transistor construction with large channel width and thin film transistor substrate circuit

InactiveCN102800692AImprove charging effectIncrease channel widthSolid-state devicesNon-linear opticsOptoelectronicsChannel width

The invention discloses a thin film transistor construction with large channel width. The thin film transistor construction comprises a grid electrode, a source electrode and a drain electrode, wherein the source electrode and the drain electrode are helix and are symmetrical and corresponding to each other, and a double-helix configuration. In the thin film transistor construction, the source electrode and the drain electrode are designed into double-helix shape, the width of a channel between the source electrode and the drain electrode is increased, and the width to length ratio of the channel is increased so as to improve the charging capacity of the thin film transistor.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD