Patents

Literature

397results about How to "Reduce voltage difference" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Touch Sensitive Screen

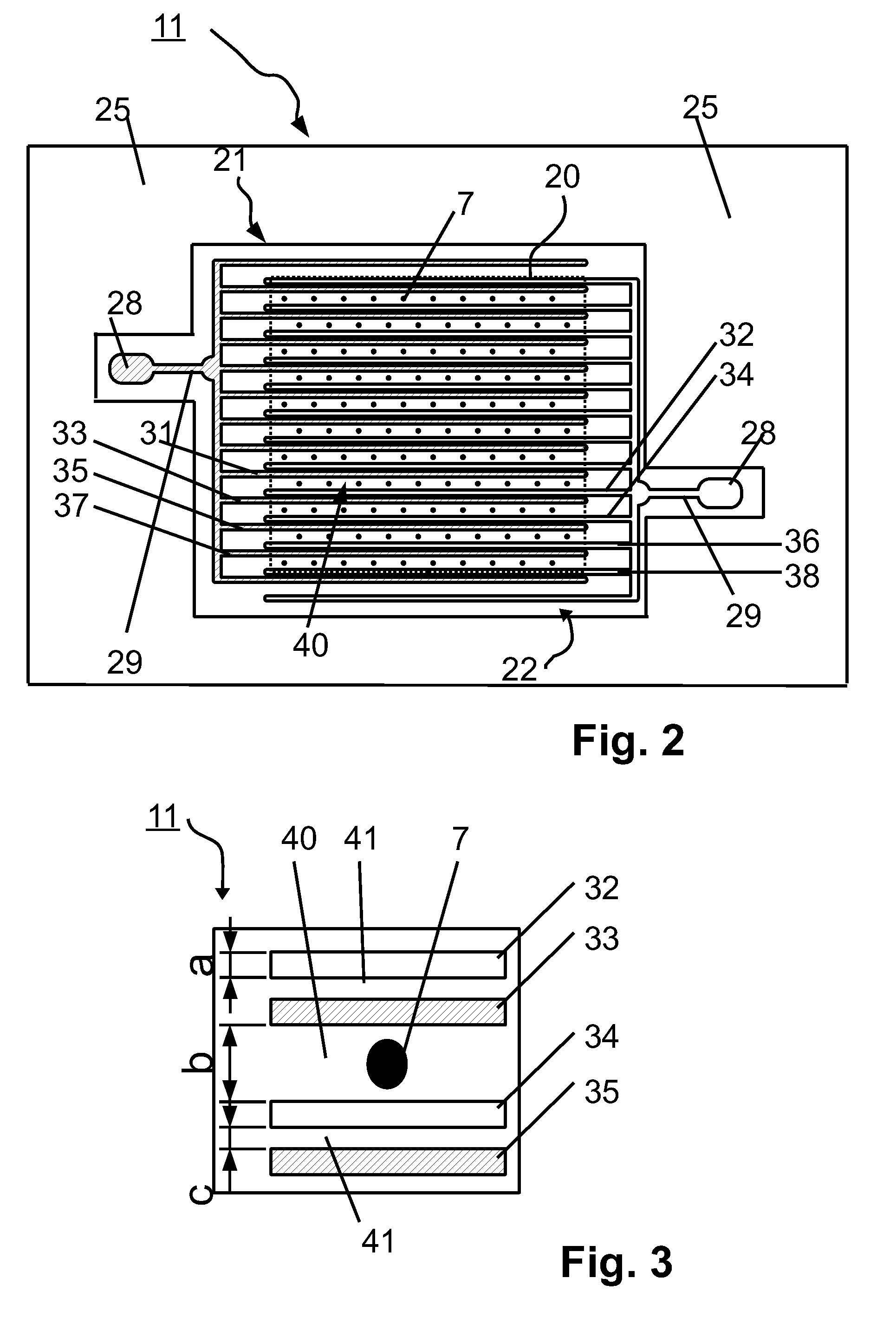

ActiveUS20070062739A1Lower impedanceEfficient couplingTransmission systemsInput/output processes for data processingElectrical resistance and conductancePlastic materials

A capacitive sensor for determining the presence of an object, such as a user's finger or a stylus, is provided. The sensor comprises a substrate, for example made of transparent plastics material, such as PET, on which electrodes are deposited. A resistive drive electrode for example formed of transparent ITO, is arranged on one side of the substrate and a resistive sense electrode, which again may be of transparent ITO, is arranged on the other side of the substrate. Thus an overall transparent sensor may be provided. A shorting connection is also provided which is configured to connect between two locations on one of the electrodes. The electrodes are connected to respective drive and sense channels. By providing the shorting connection between two locations on one or other (or both) of the electrodes, a lower resistance connection is provided between other locations on the electrode and the corresponding drive or sense channel.

Owner:NEODRON LTD

Touch sensitive screen

ActiveUS7932898B2Lower impedanceEfficient couplingTransmission systemsCathode-ray tube indicatorsElectrical resistance and conductancePlastic materials

A capacitive sensor for determining the presence of an object, such as a user's finger or a stylus, is provided. The sensor comprises a substrate, for example made of transparent plastics material, such as PET, on which electrodes are deposited. A resistive drive electrode for example formed of transparent ITO, is arranged on one side of the substrate and a resistive sense electrode, which again may be of transparent ITO, is arranged on the other side of the substrate. Thus an overall transparent sensor may be provided. A shorting connection is also provided which is configured to connect between two locations on one of the electrodes. The electrodes are connected to respective drive and sense channels. By providing the shorting connection between two locations on one or other (or both) of the electrodes, a lower resistance connection is provided between other locations on the electrode and the corresponding drive or sense channel.

Owner:NEODRON LTD

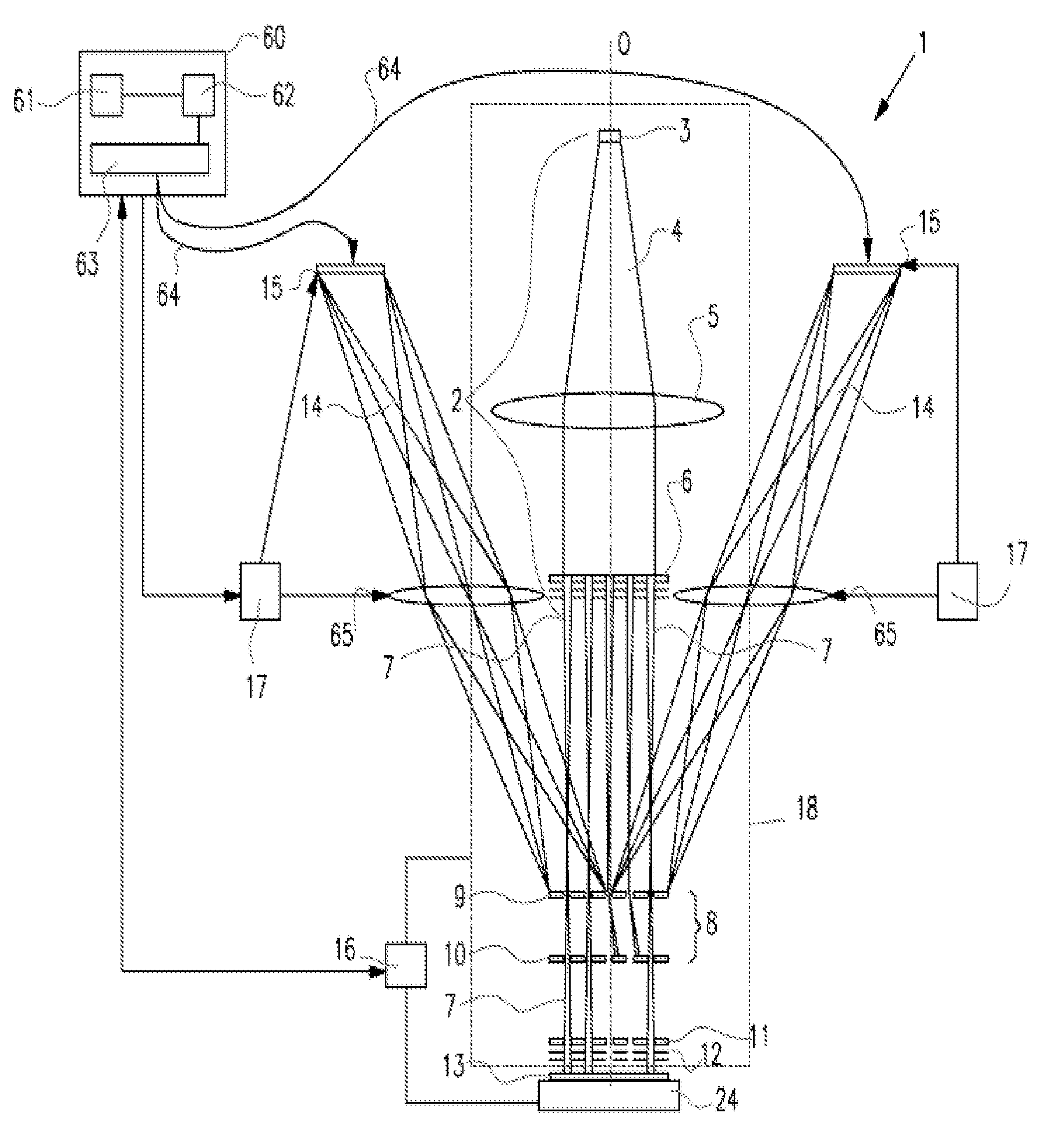

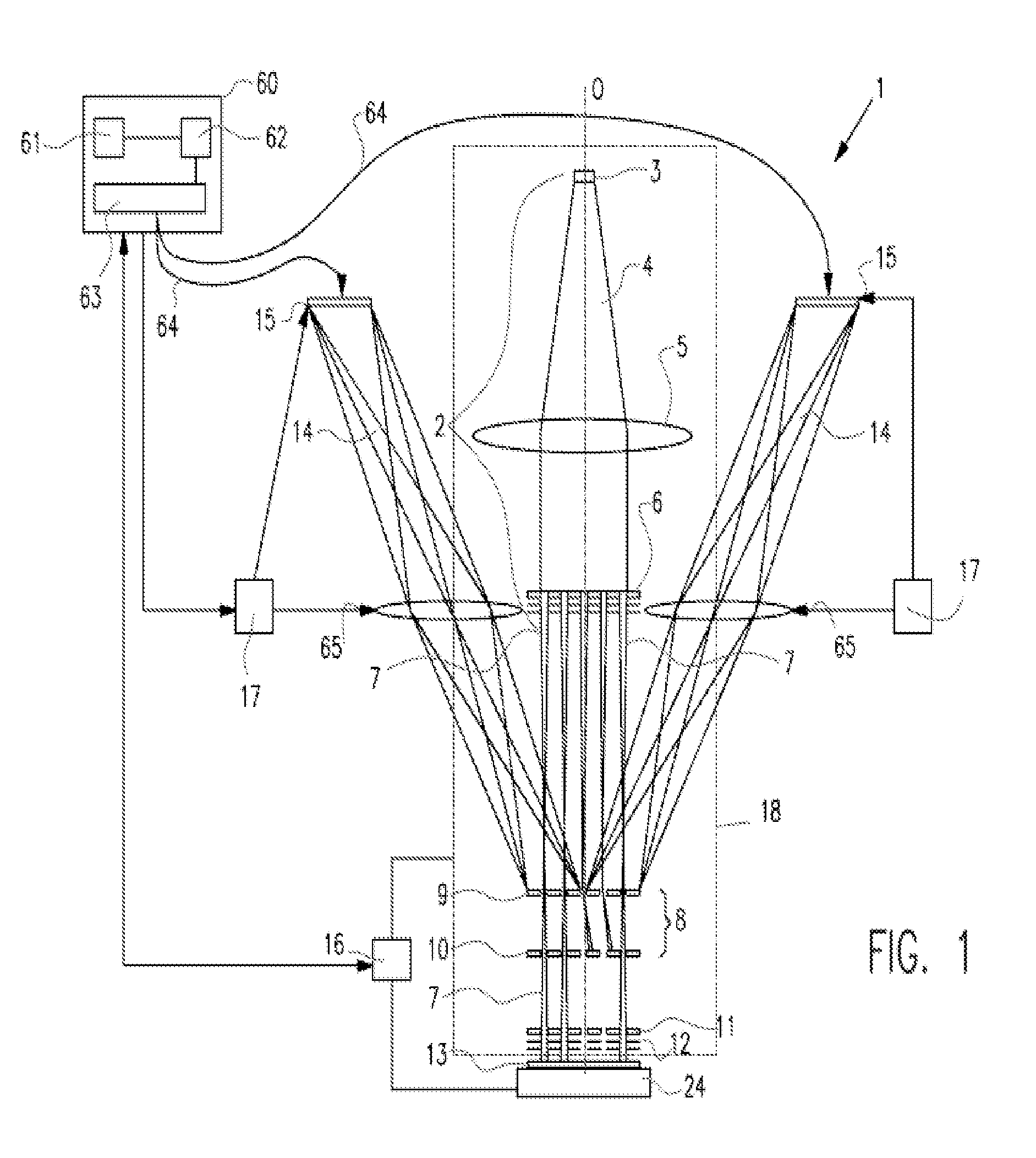

Charged particle optical system comprising an electrostatic deflector

ActiveUS20100276606A1Improve uniformitySufficient speedStability-of-path spectrometersBeam/ray focussing/reflecting arrangementsElectric fieldAtomic physics

A charged particle optical system comprising a beamlet generator for generating a plurality of beamlets of charged particles and an electrostatic deflector for deflecting the beamlets. The electrostatic deflector comprises first and second electrodes adapted for connection to a voltage for generating an electric field between the electrodes for deflection of the beamlets, the electrodes being at least partially freestanding in an active area of the electrostatic deflector. The electrodes define at least one passing window for passage of at least a portion of the beamlets between the electrodes, the passing window having a length in a first direction and a width in a transverse direction. The system is adapted to arrange the beamlets in at least one row and to direct a single row of the beamlets through the passing window of the electrostatic deflector, the beamlets of the row extending in the first direction. A substantial part of the electrostatic deflector extends beyond the passing window in the first direction.

Owner:ASML NETHERLANDS BV

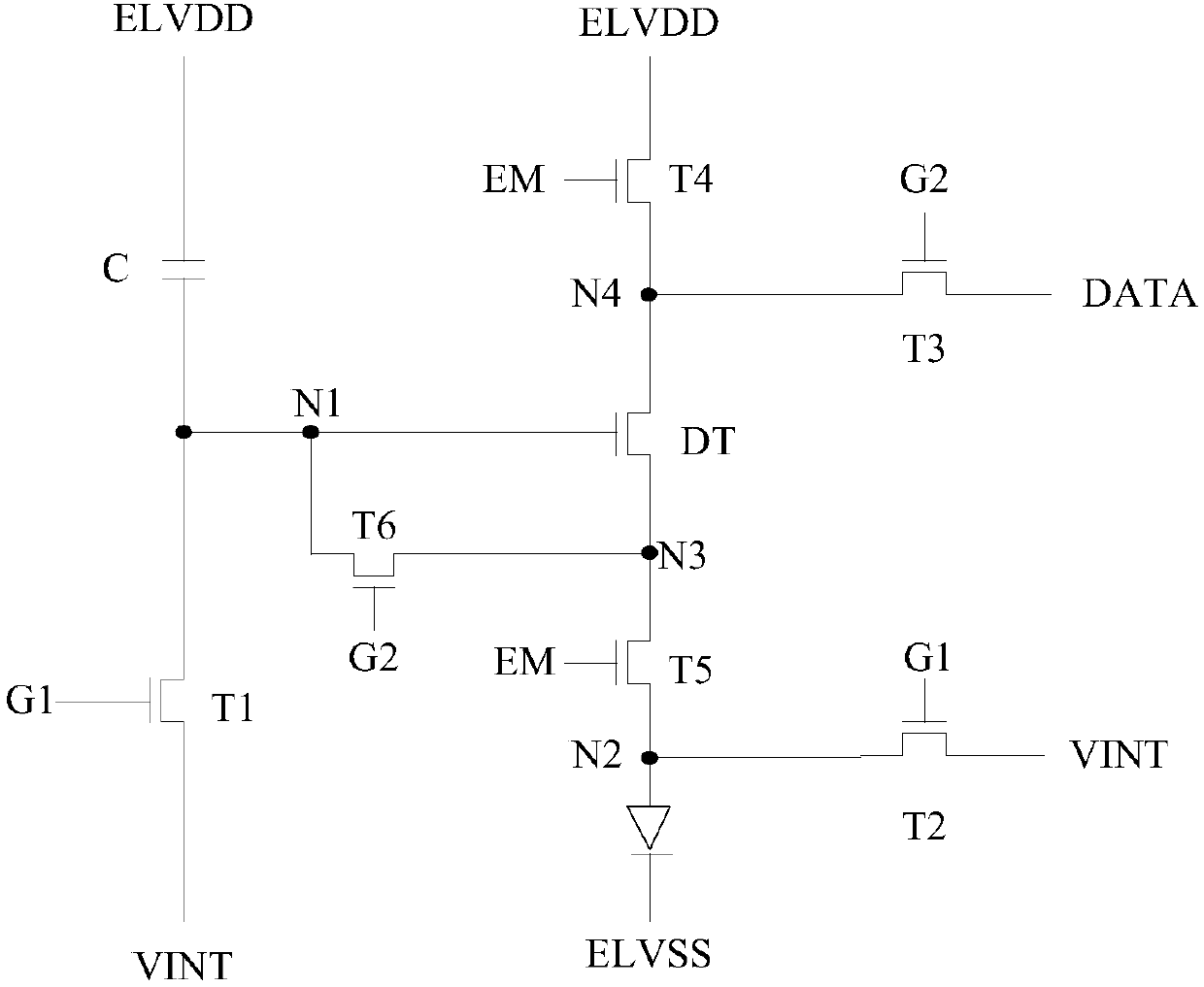

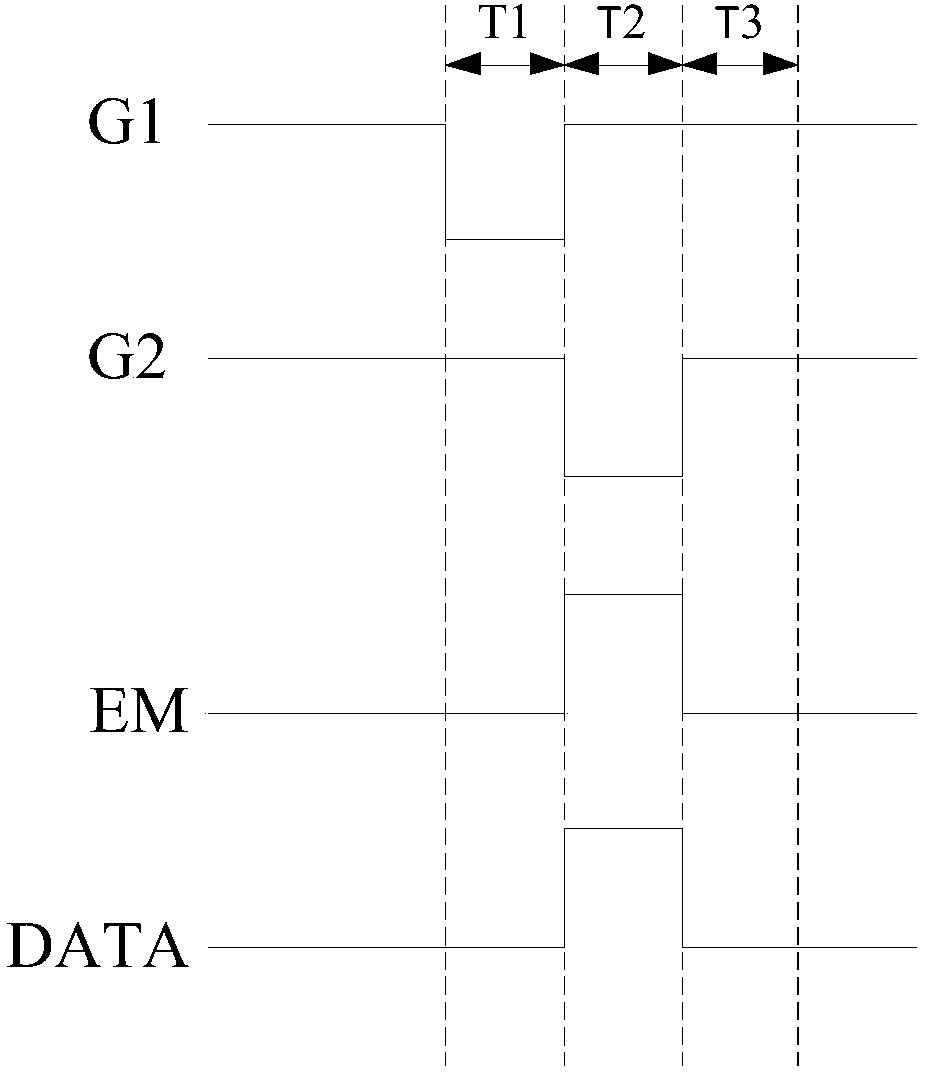

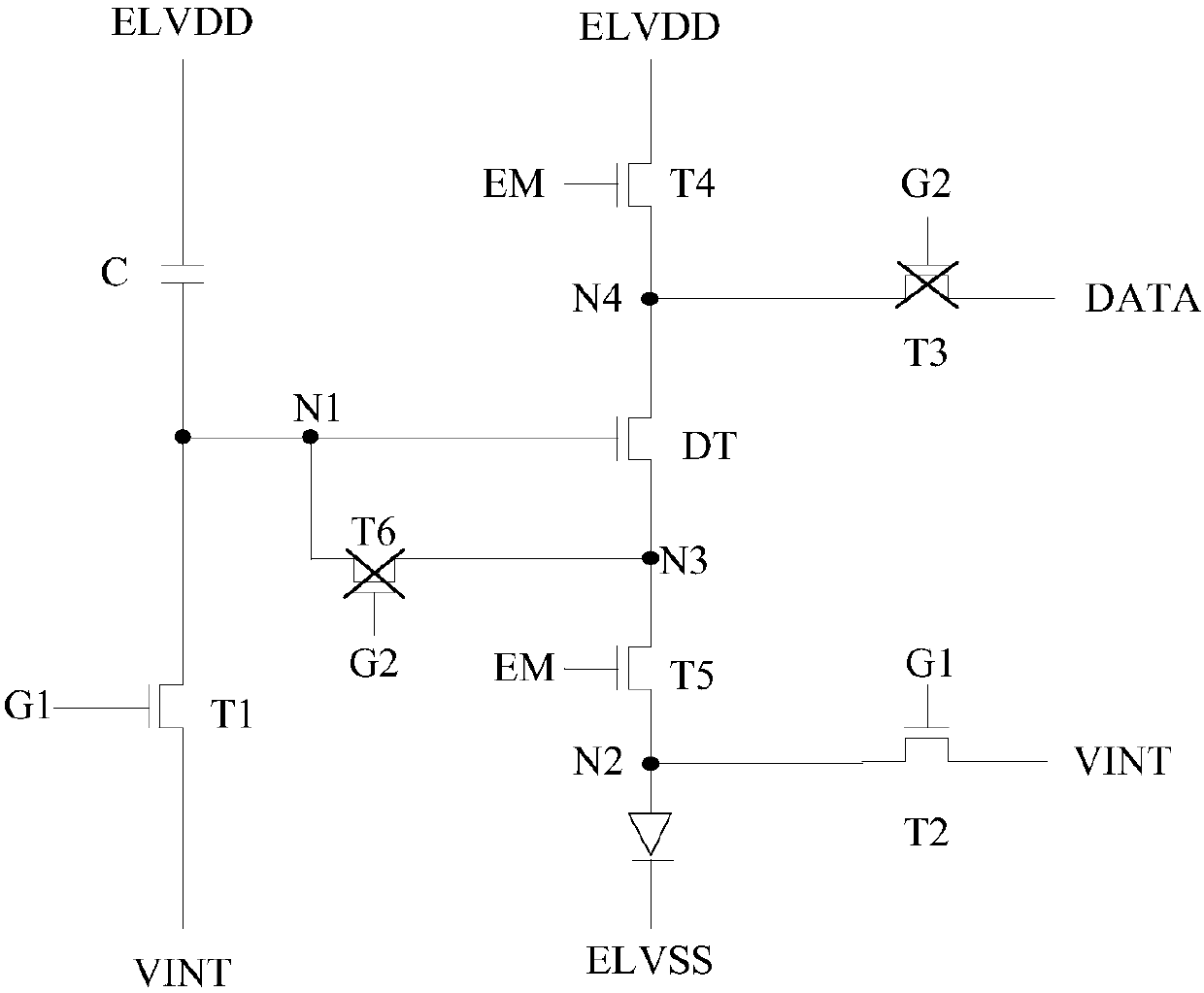

Pixel driving circuit and method, and display device

InactiveCN107767819AIncrease contrastImprove short-term afterimage problemStatic indicating devicesHysteresisCapacitance

The disclosure provides a pixel driving circuit, a driving method, and a display device, which are applied to the field of display technology. The pixel driving circuit includes a first switching element, a second switching element, a third switching element, a fourth switching element, a fifth switching element, a sixth switching element, a driving transistor, and a storage capacitor. According to the disclosure, the short-term afterimage problem caused by a hysteresis effect is improved, the display quality is improved, the influence of a threshold voltage of the driving transistor on a driving current is also eliminated and therefore, the uniformity of display luminance of each pixel is ensured.

Owner:BOE TECH GRP CO LTD

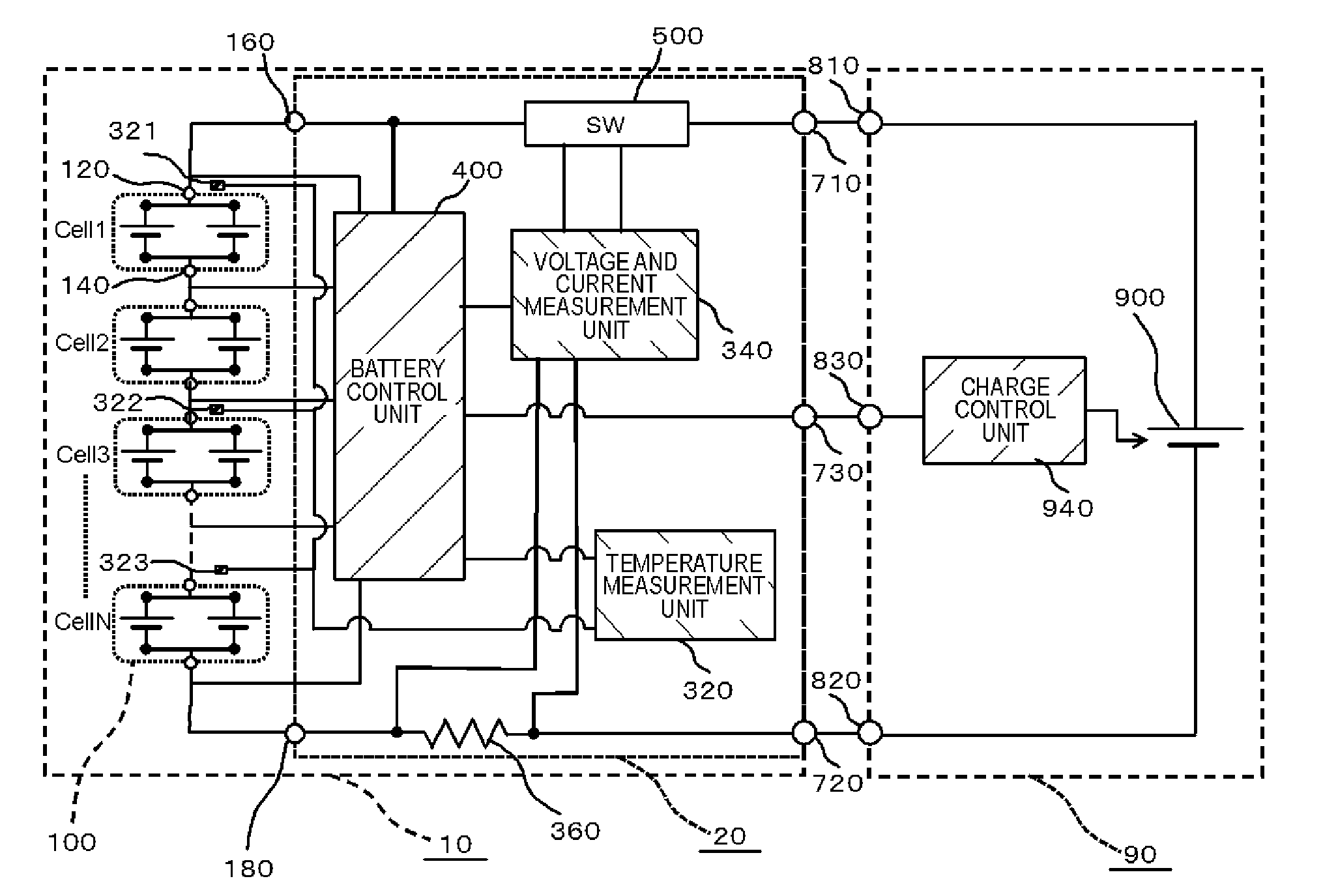

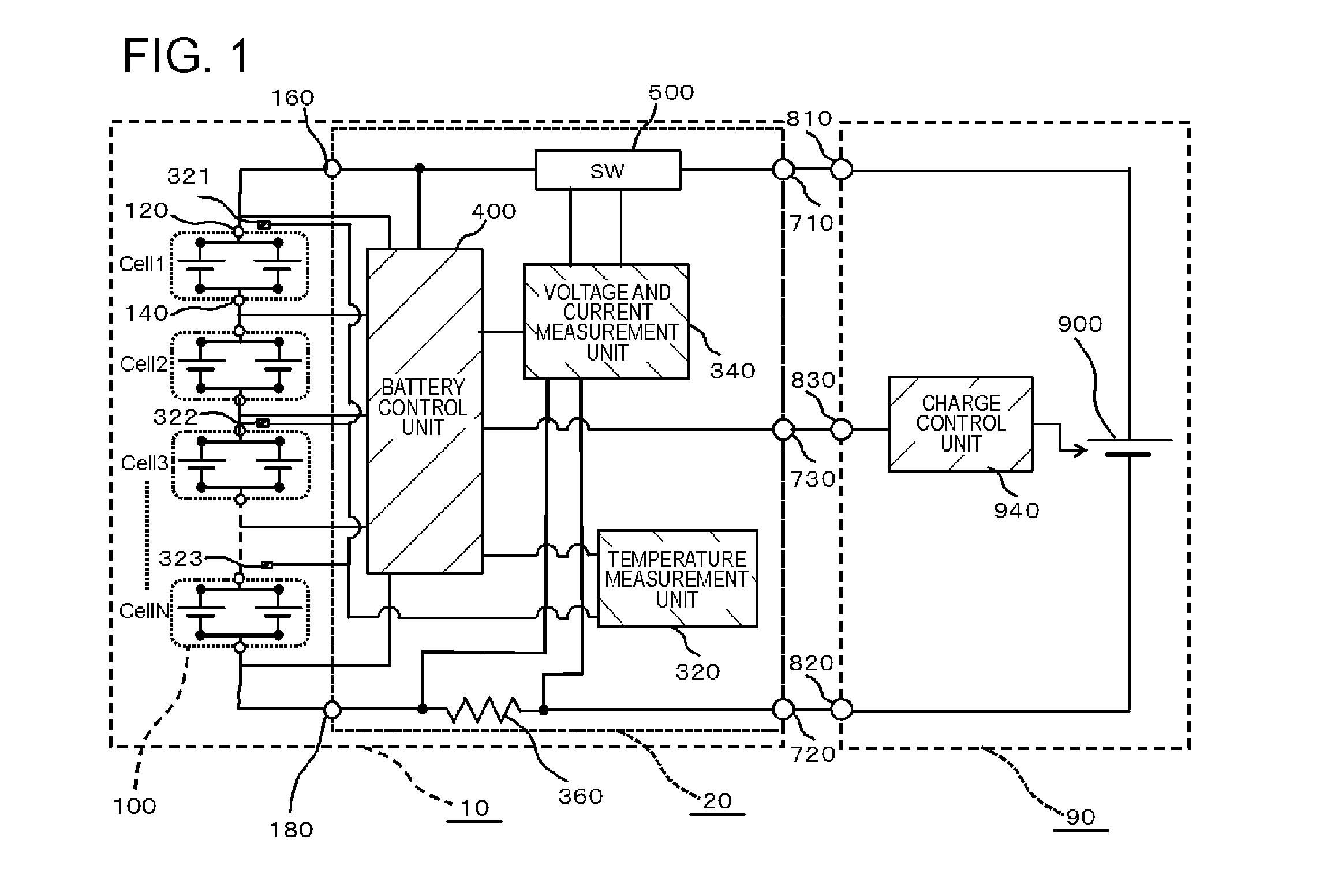

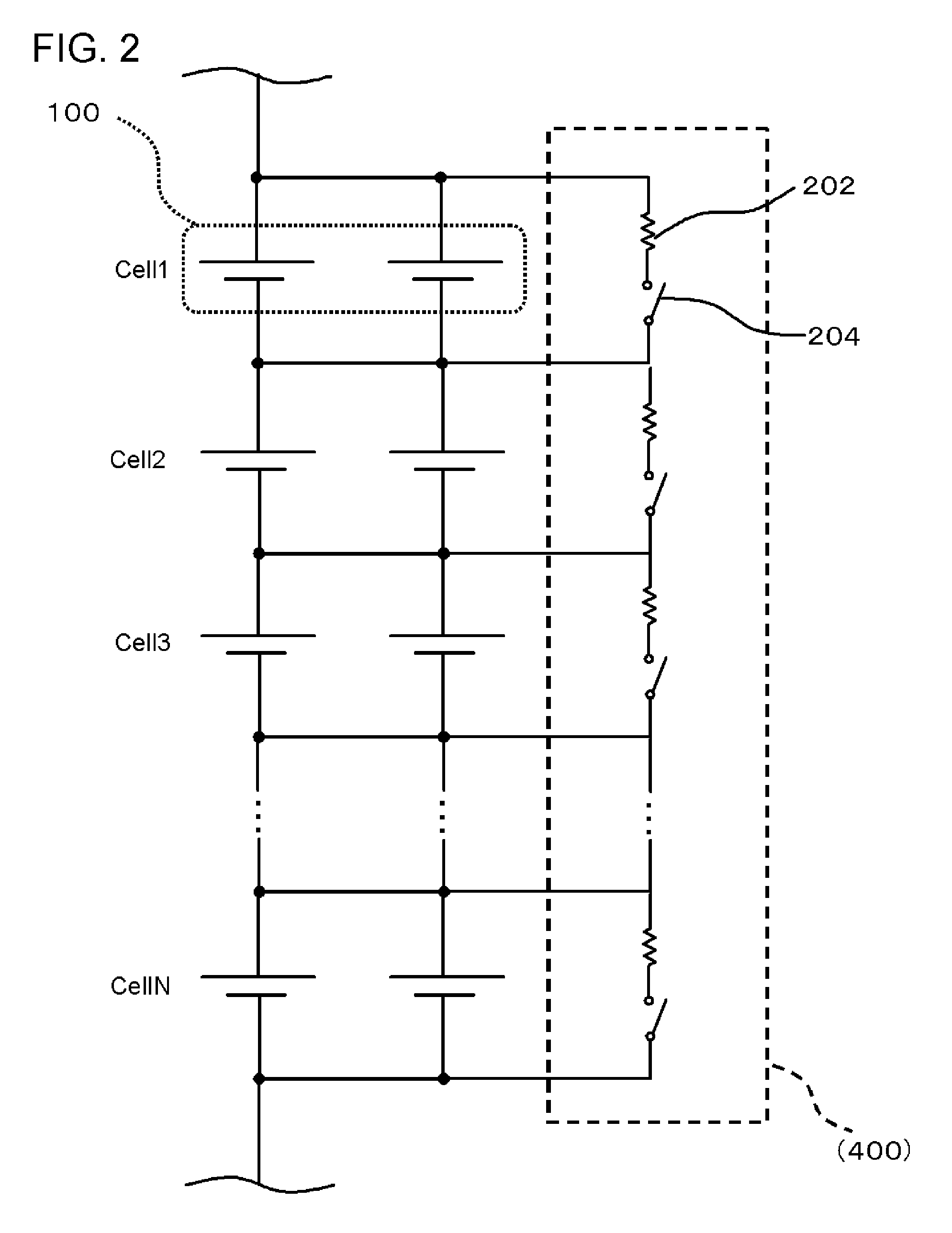

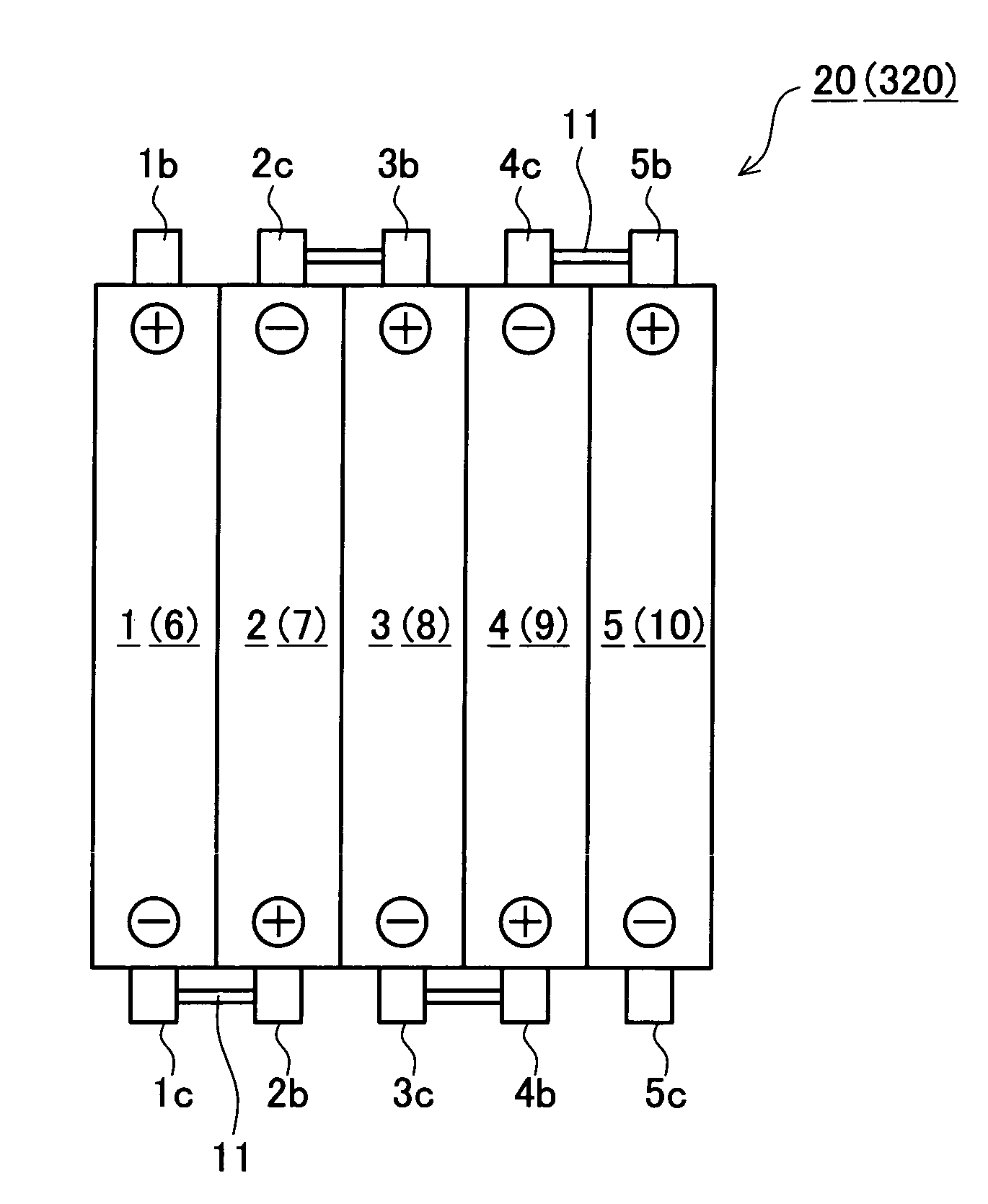

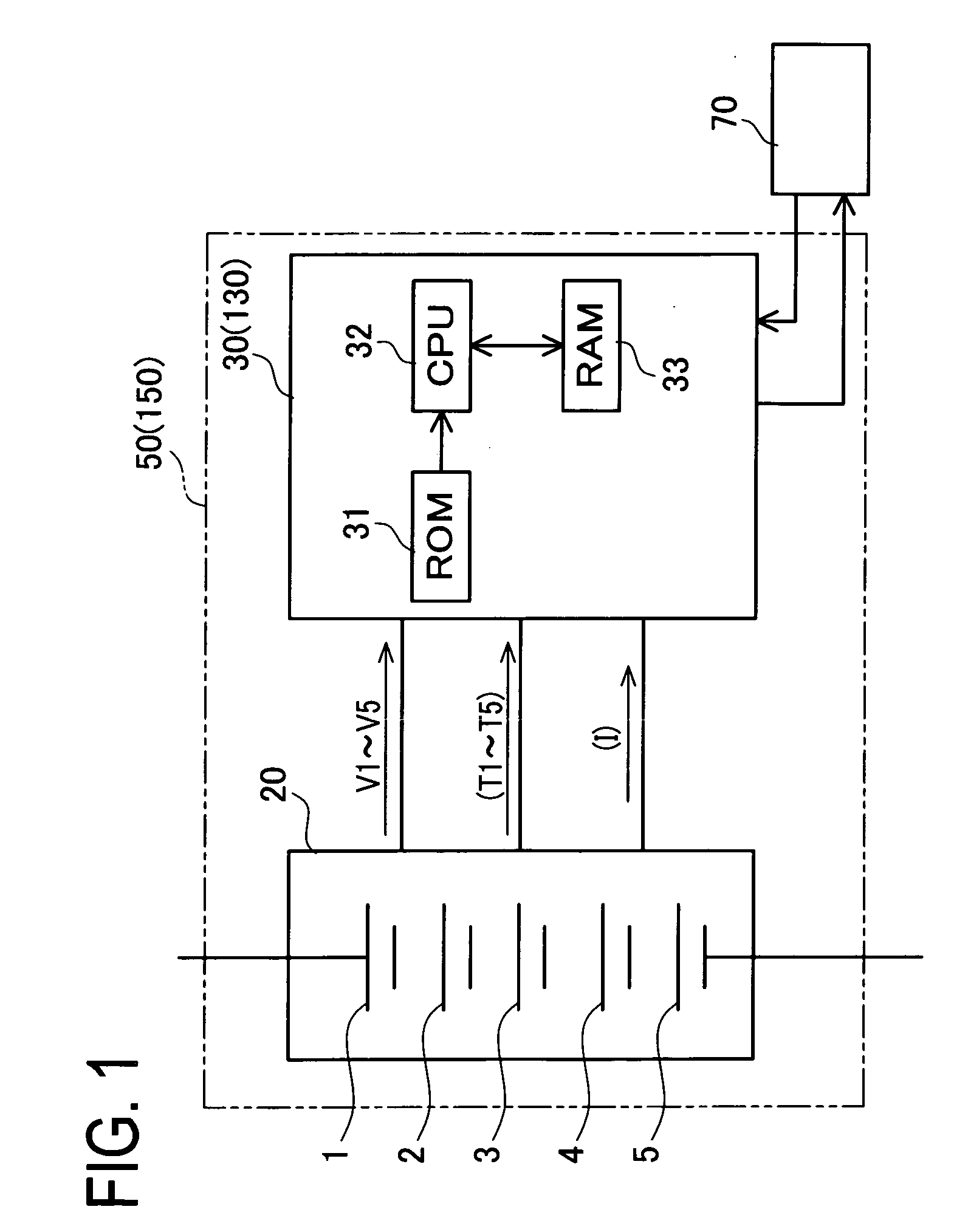

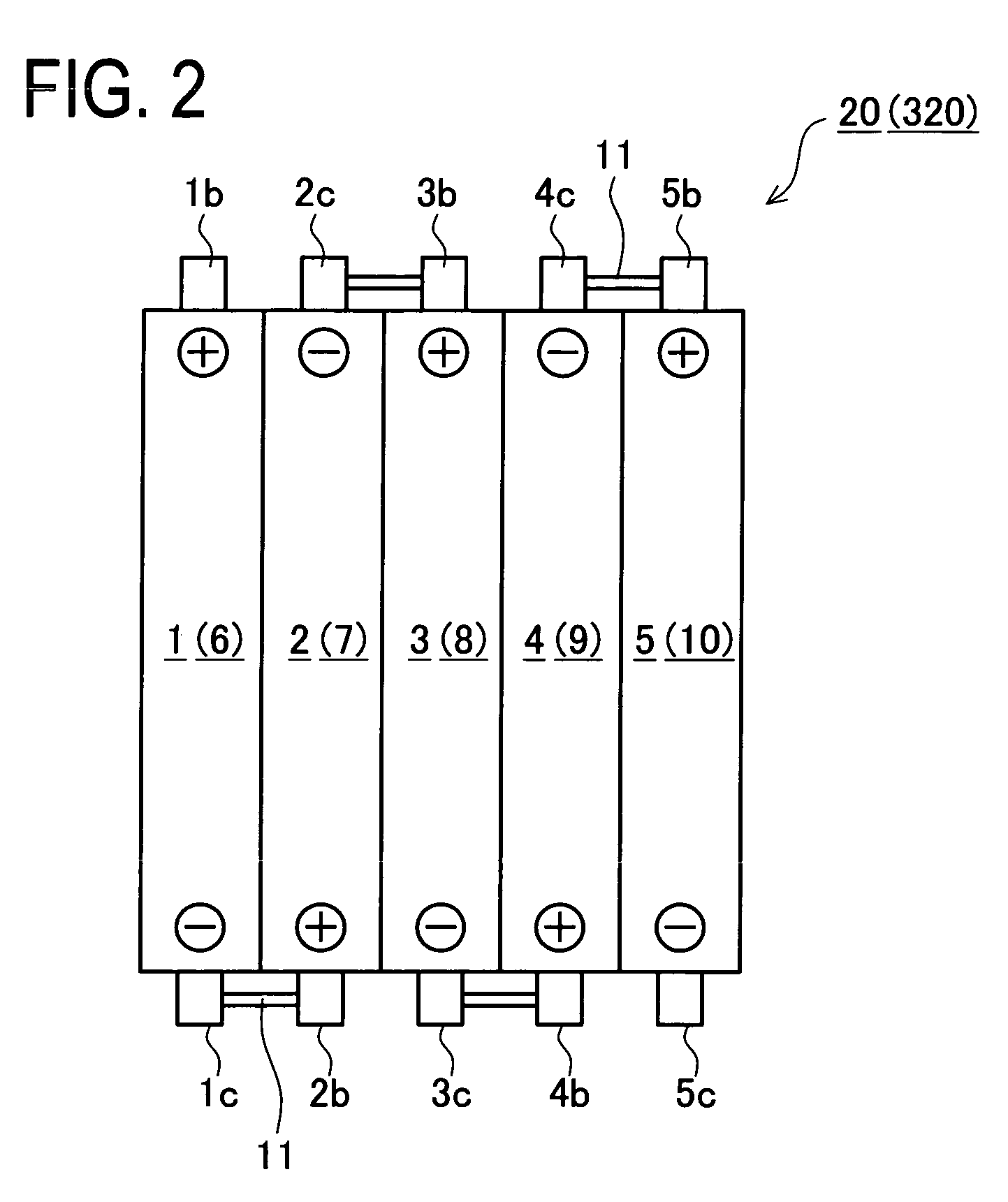

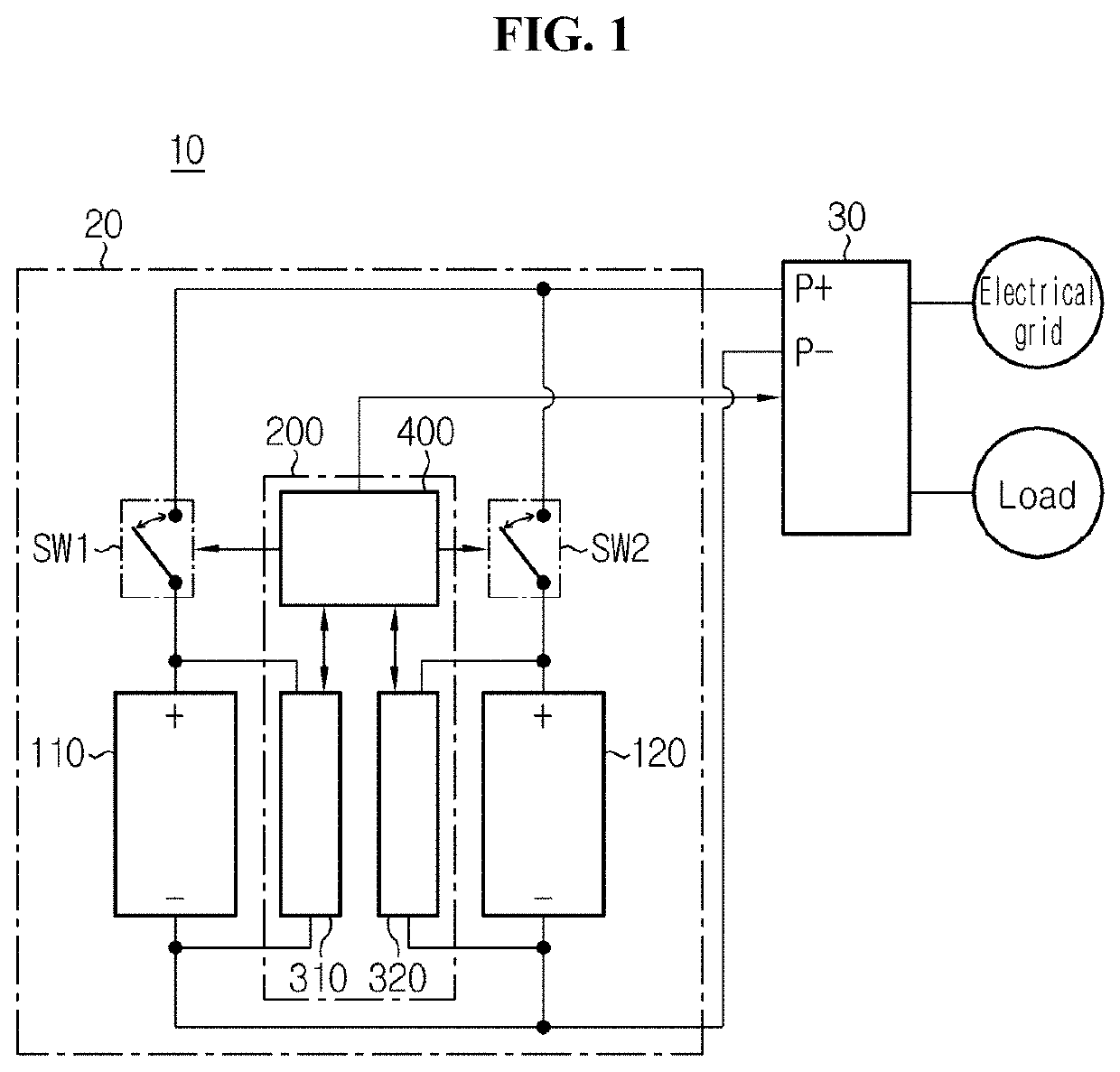

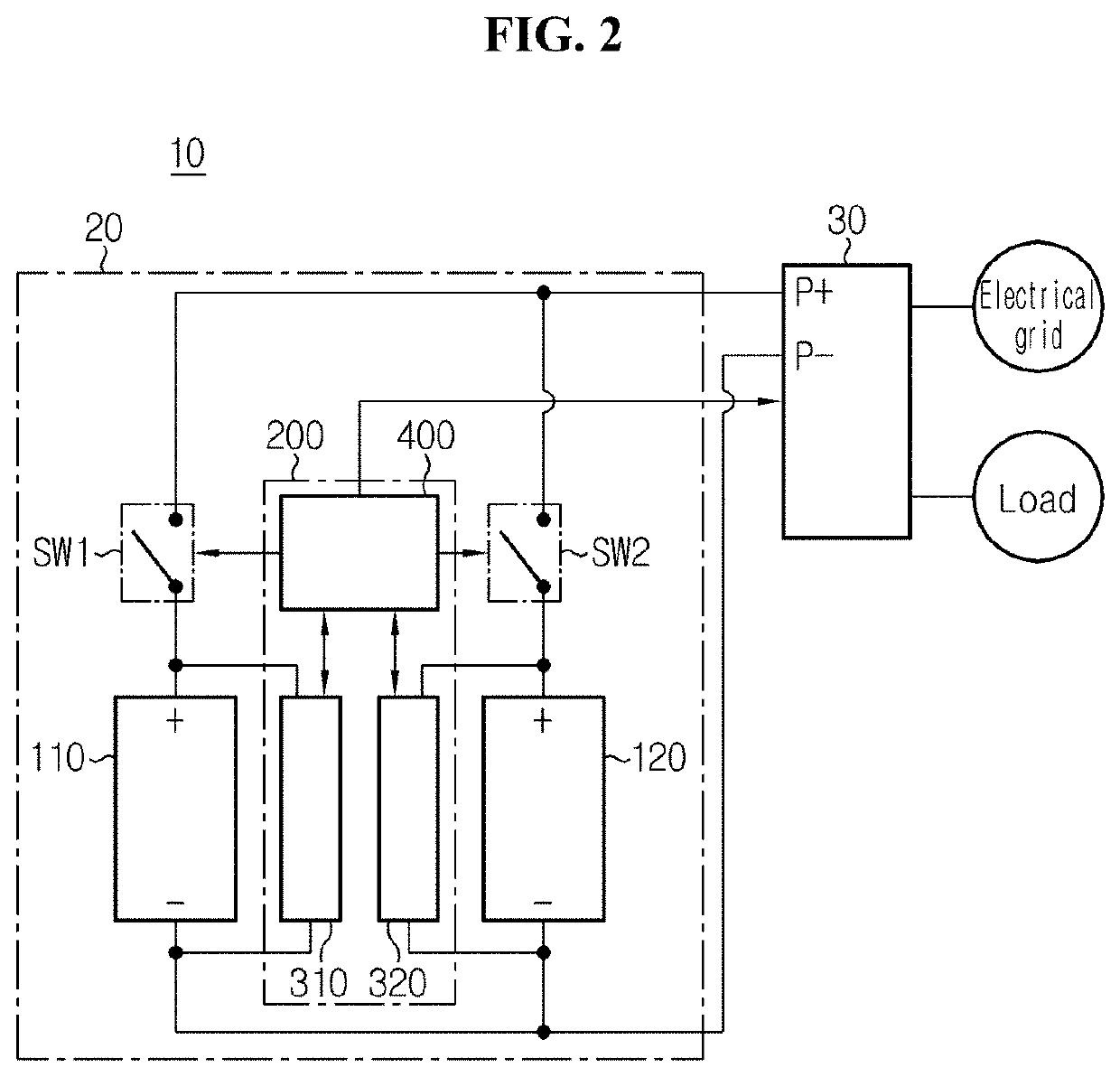

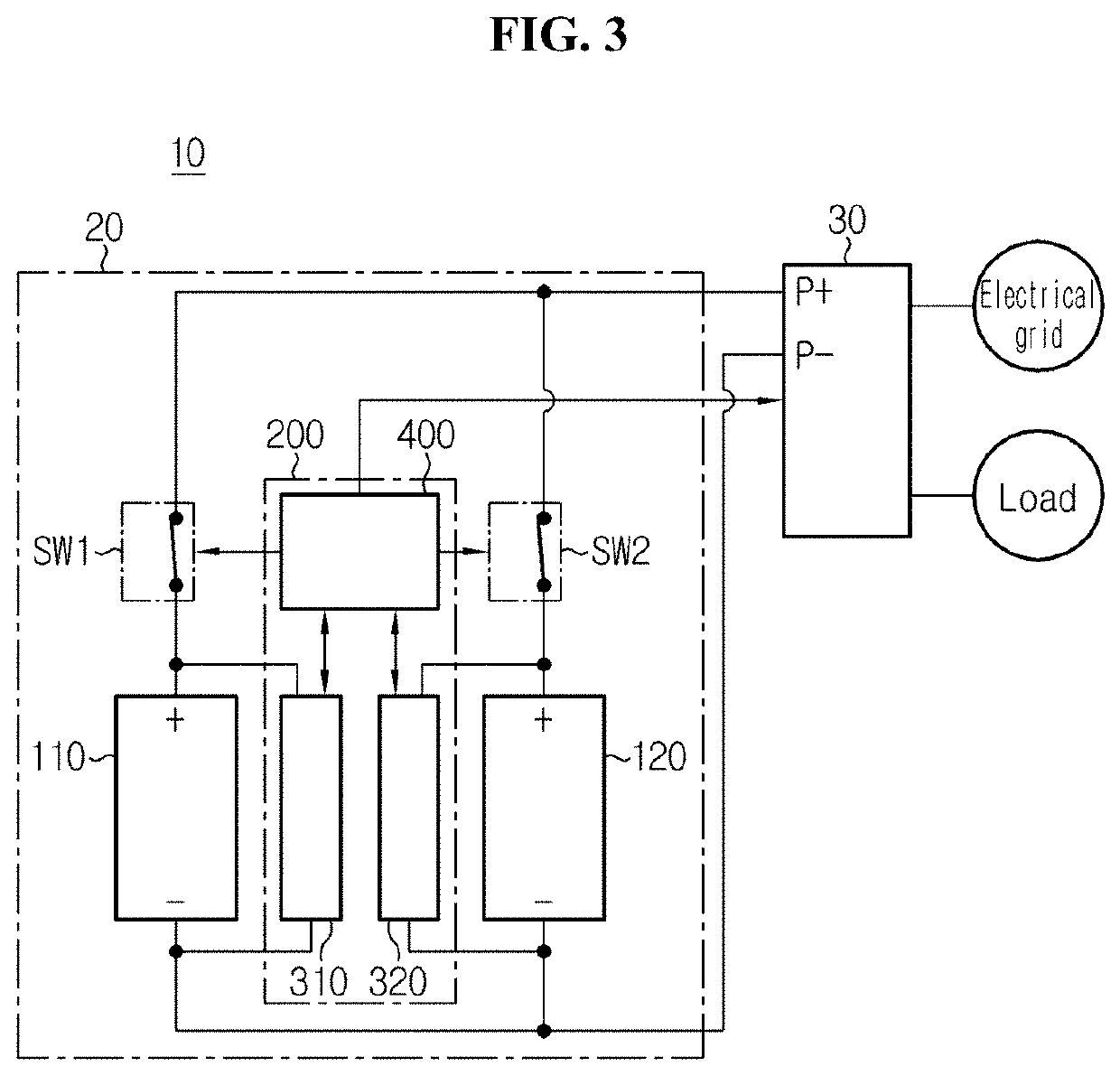

Battery control system and battery pack

ActiveUS20150035495A1Reduce differenceUnnecessary balance controlCharge equalisation circuitCircuit monitoring/indicationCharge and dischargeTemperature measurement

A battery control unit (400) controls charge and discharge of battery cells (100) on the basis of temperatures measured by a temperature measurement unit (320) and voltages measured by the voltage and current measurement unit (340). In addition, the battery control unit (400) specifies a lowest temperature cell having the lowest temperature and a highest temperature cell having the highest temperature on the basis of the temperatures measured by the temperature measurement unit (320), when a current is greater than 0. In addition, the battery control unit (400) performs balance control for equalizing voltages of all the battery cells (100), on the basis of the voltages measured by the voltage and current measurement unit (340), when a first temperature condition in which a temperature difference ΔT between the highest temperature cell and the lowest temperature cell is equal to or greater than a reference value T1 is not satisfied. On the other hand, when the temperature difference ΔT satisfies the first temperature condition, the battery control unit (400) does not perform the balance control.

Owner:NEC ENERGY DEVICES LTD

Battery pack and battery pack producing method

InactiveUS20090011327A1Voltage differenceSimilar battery voltagePrimary cell to battery groupingBatteries circuit arrangementsBattery packVoltage

A battery pack capable of sufficiently exhibiting performance of each secondary battery constituting the battery pack and its producing method are provided. The battery pack producing method of the invention comprises an obtaining process for obtaining a charge amount voltage curve C during charging and a charge amount voltage curve D during discharging, a selecting process for selecting more than one of the used secondary batteries close to each other in curves C and D from a group of the used secondary batteries whose curves C and D have been obtained, and an assembling process for combining the selected used secondary batteries to constitute the battery pack.

Owner:PANASONIC EV ENERGY CO LTD

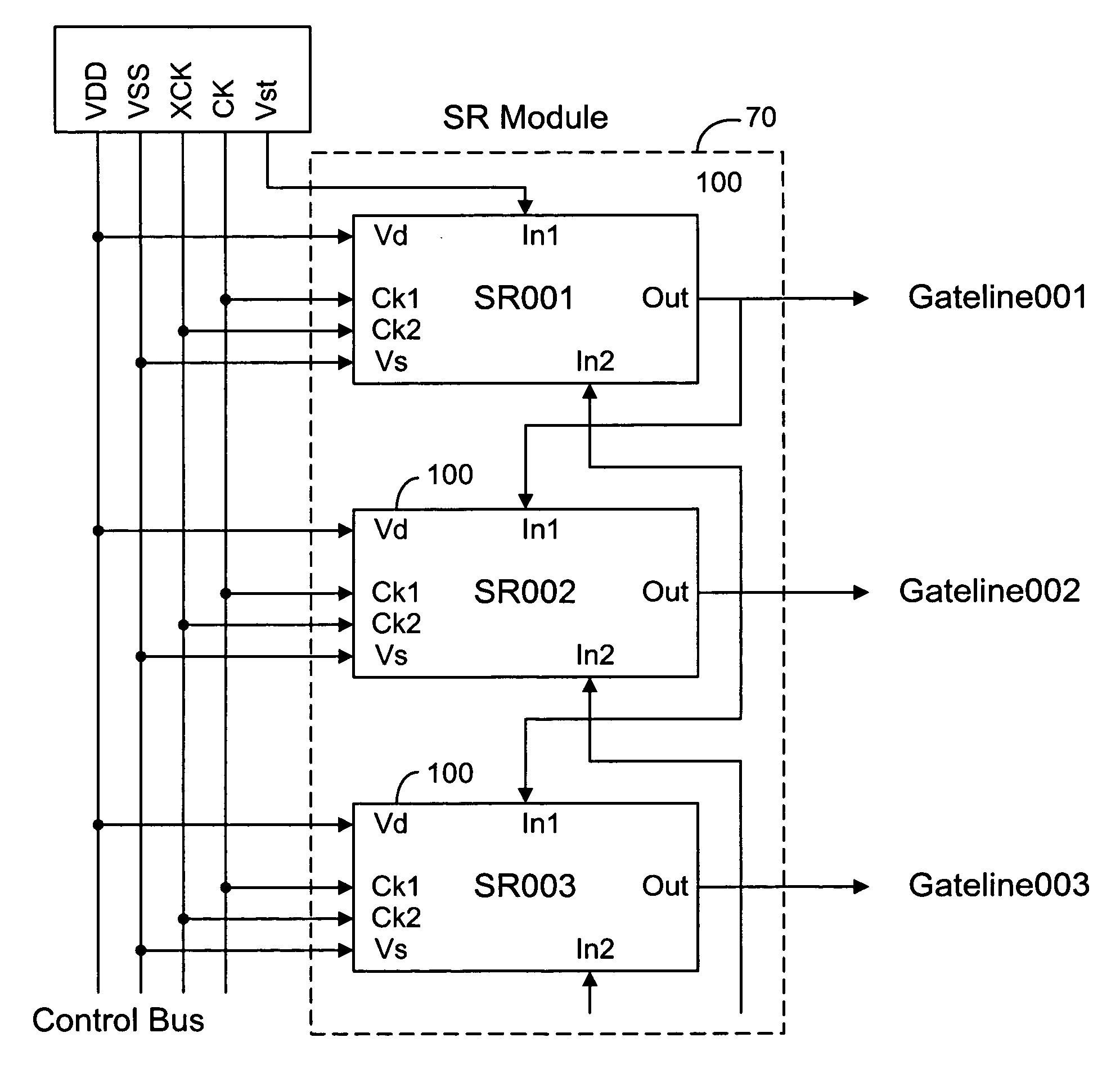

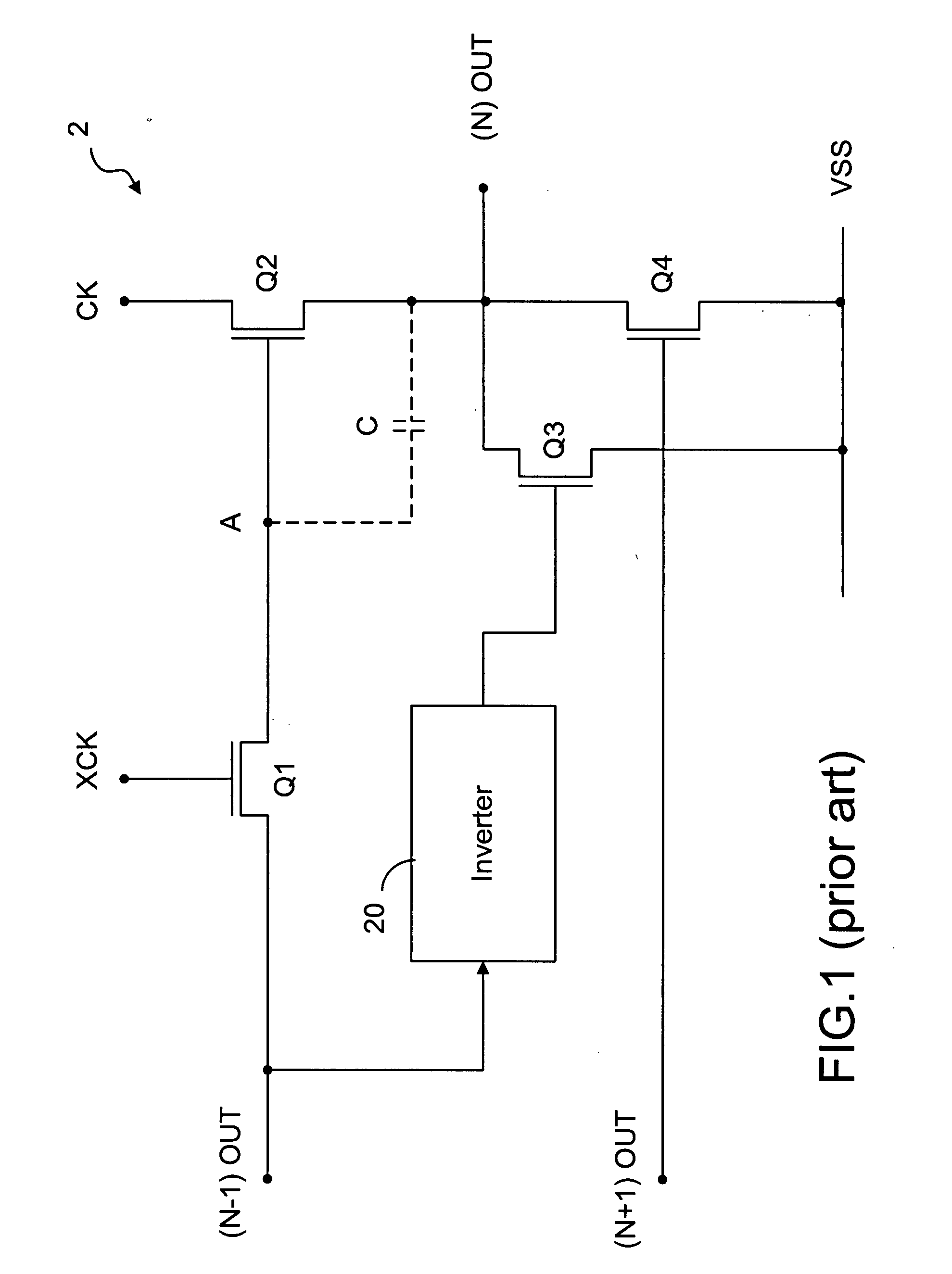

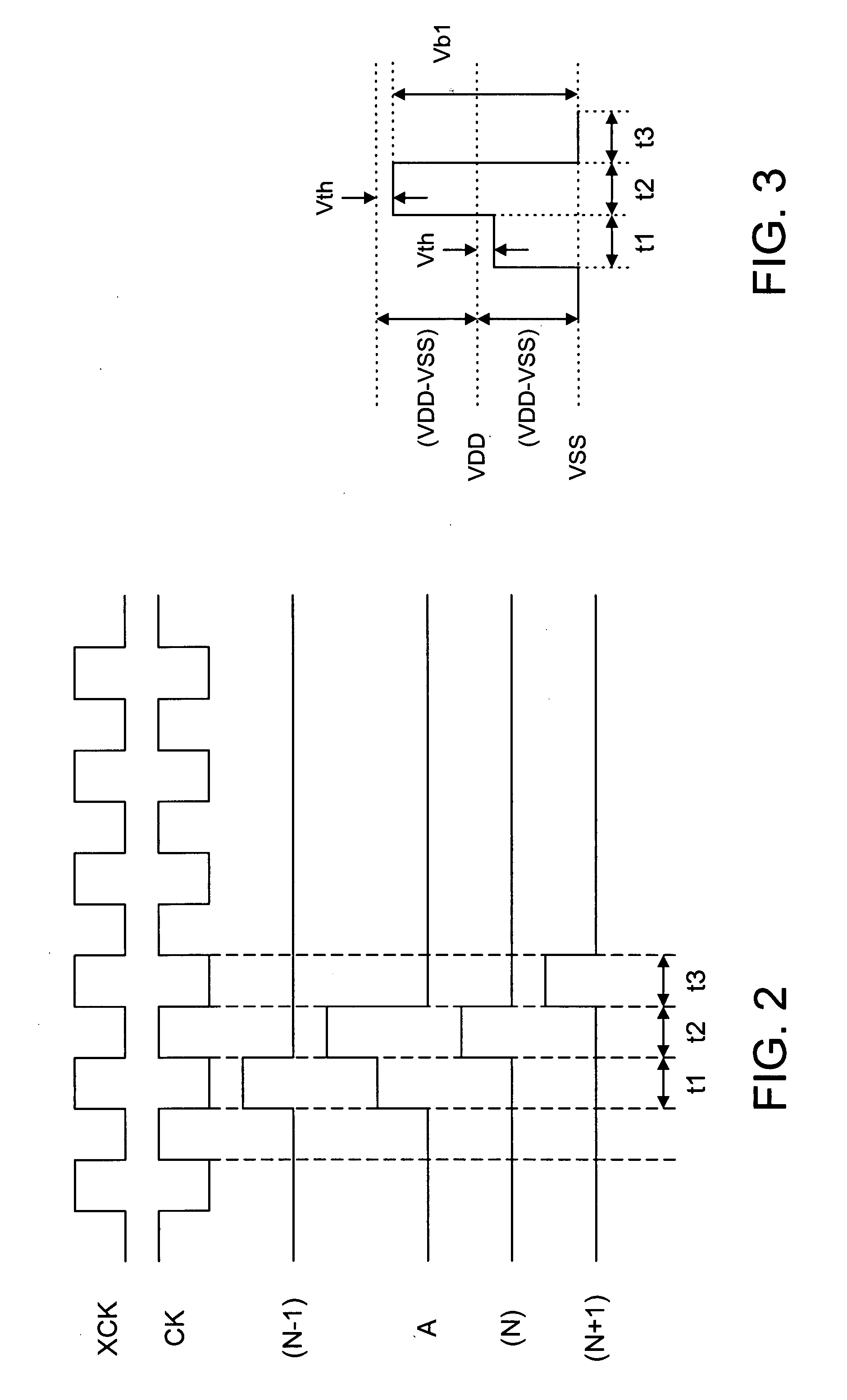

Method and device for reducing voltage stress at bootstrap point in electronic circuits

ActiveUS20090051639A1Relieve pressureReduce voltage differenceStatic indicating devicesDigital storageShift registerEngineering

A discharging device is used to reduce the voltage level at a bootstrap point in an electronic circuit such as a shift register circuit. In such a circuit, a first transistor in a conducting state receives an input pulse and conveys it to the gate terminal of a second transistor, causing the second transistor to be in a conducting state. This gate terminal is known as a bootstrap point. After receiving the input pulse, an output pulse is produced at one drain / source terminal of the second transistor. During the time period of the output pulse, the first transistor is in a non-conducting state and the voltage level at the bootstrap point is high, imposing a stress upon the first transistor. A discharging circuit consisting of at least one transistor is coupled to the bootstrap point in order to reduce the voltage level at the output pulse period.

Owner:AU OPTRONICS CORP

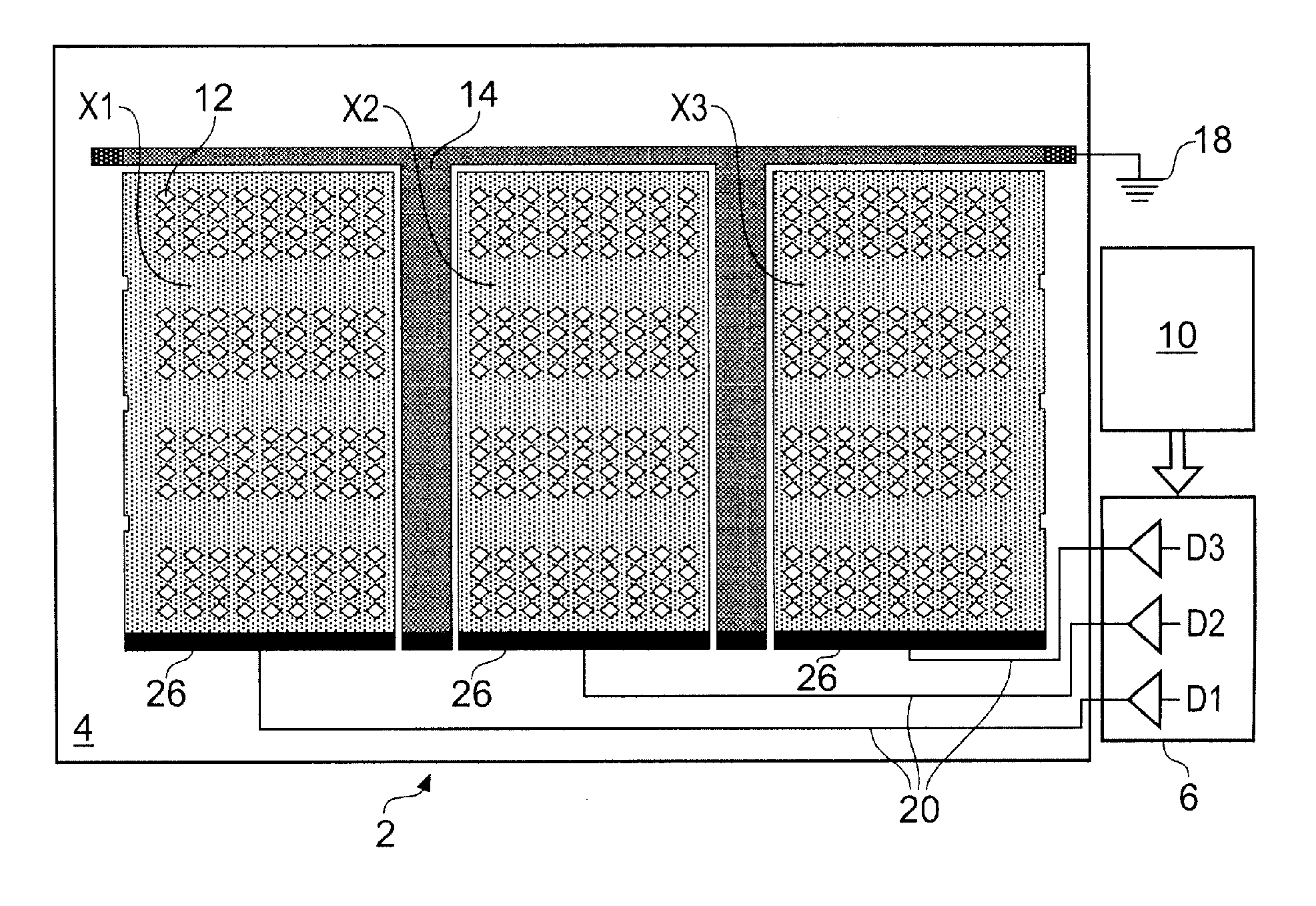

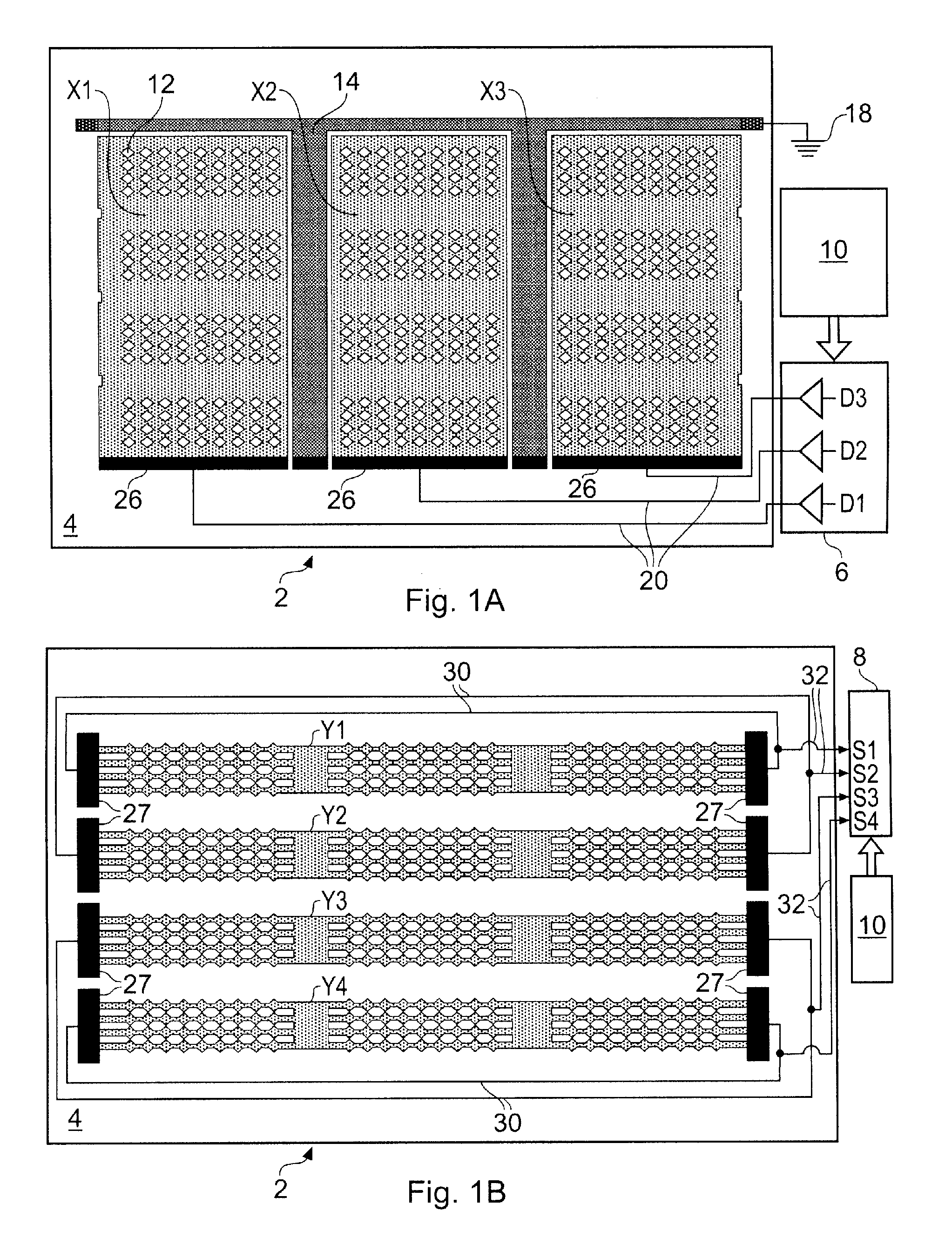

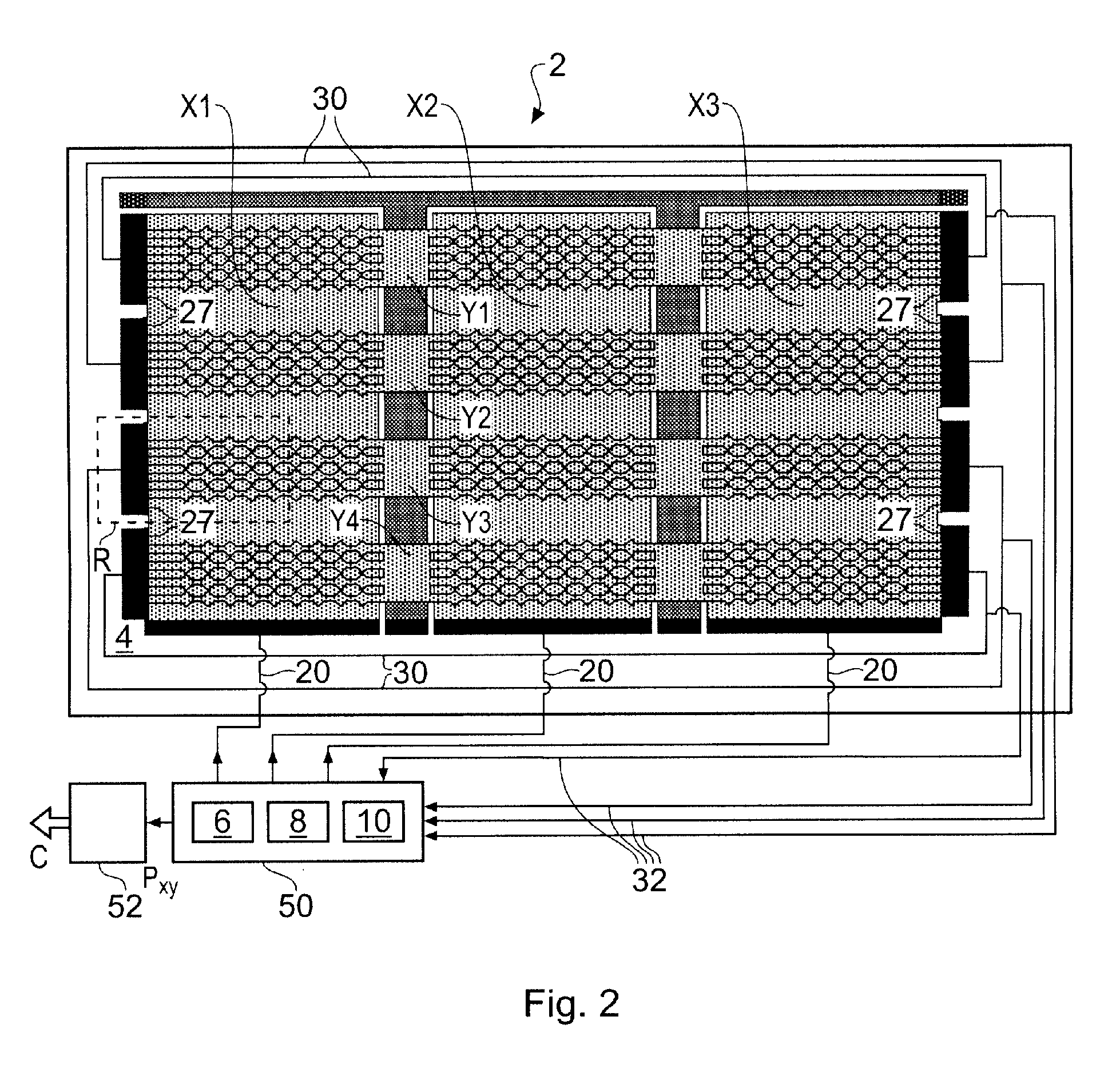

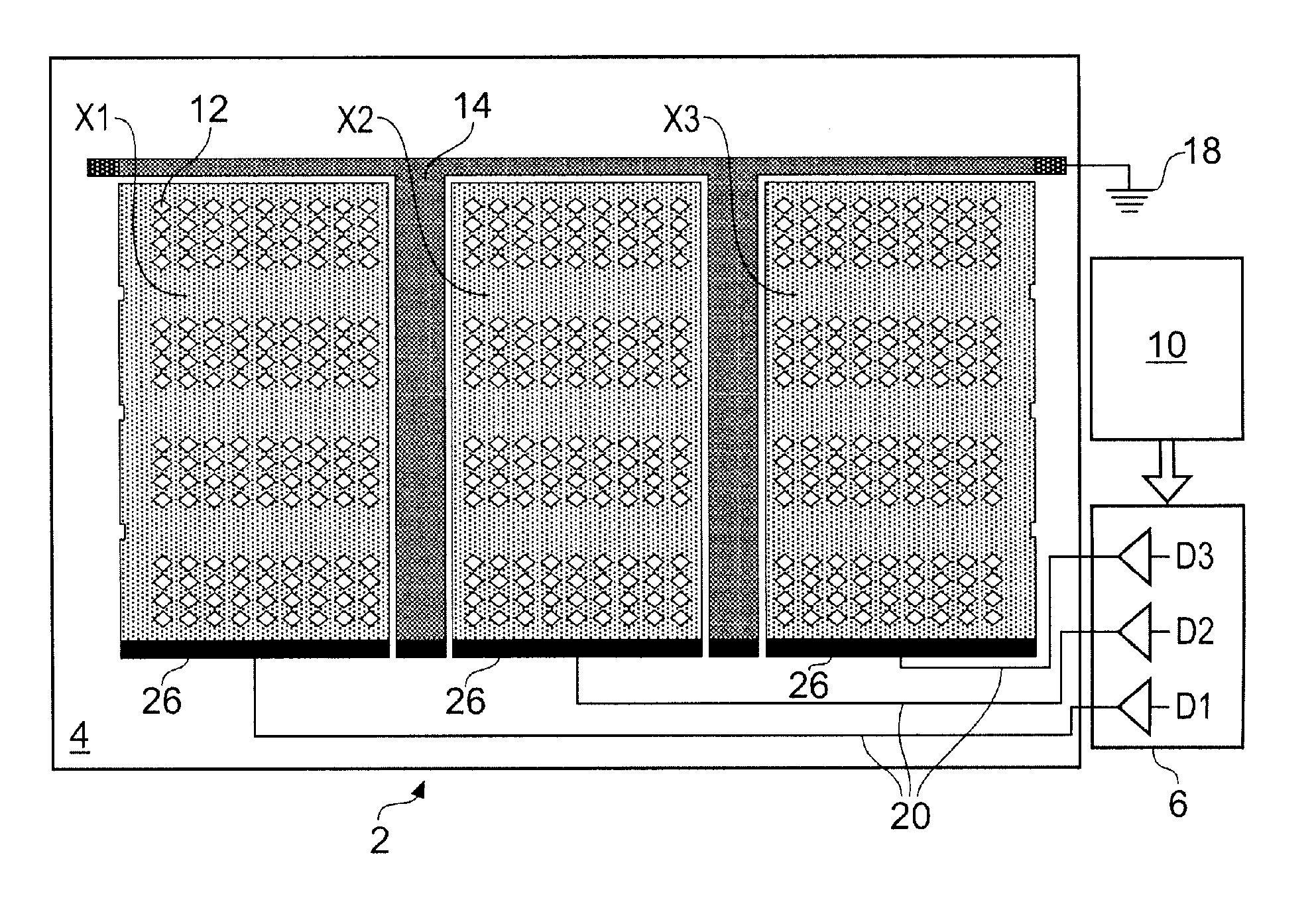

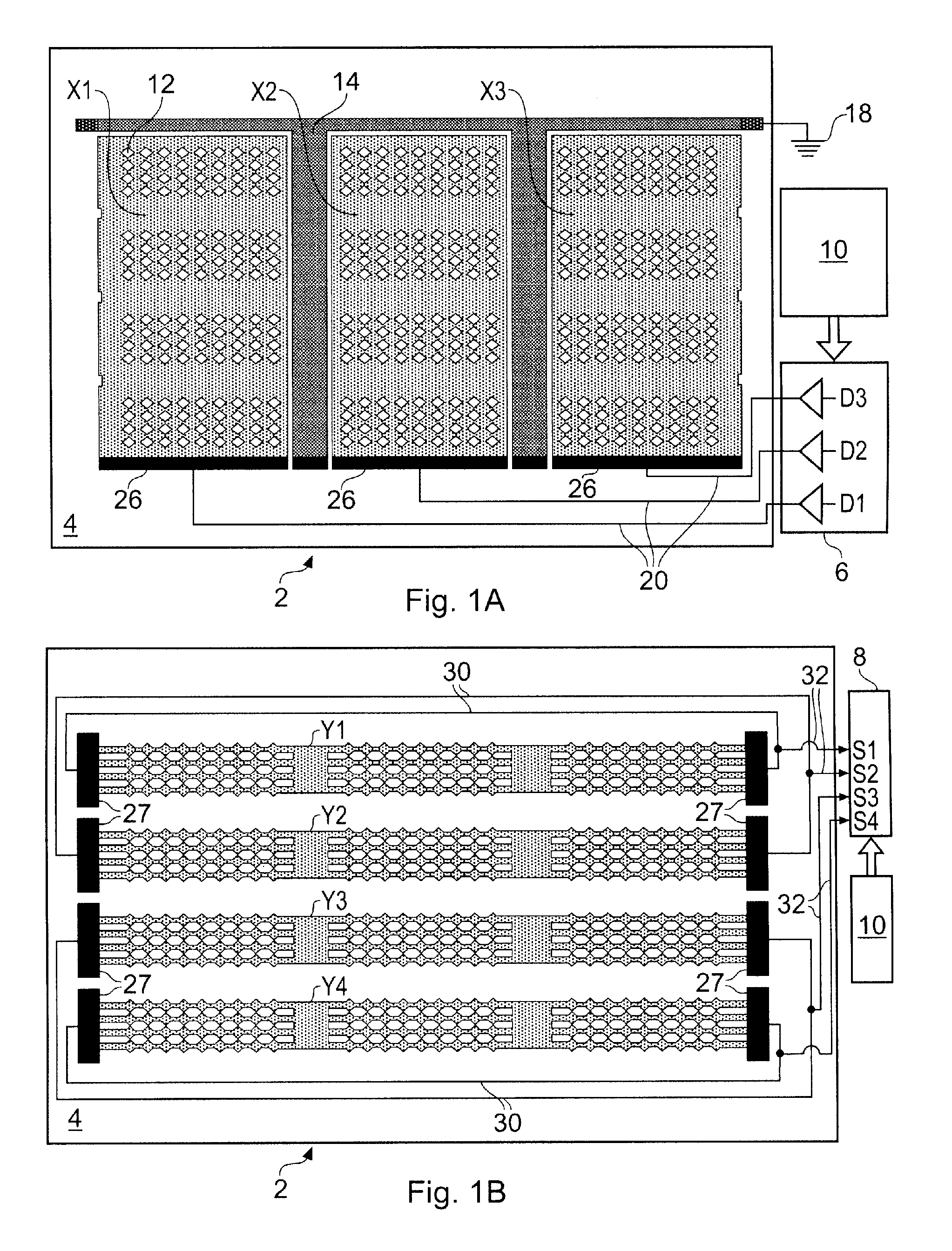

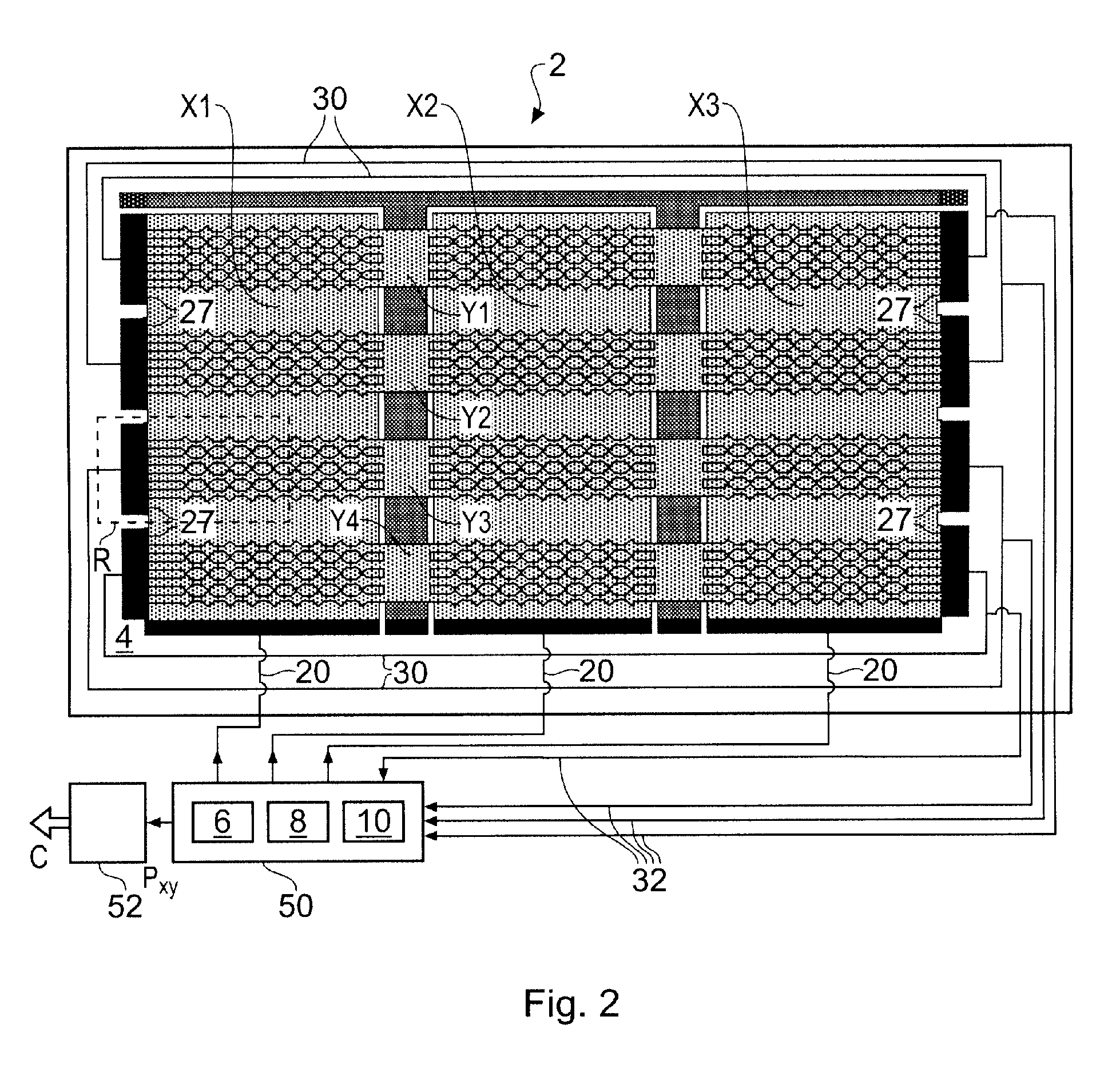

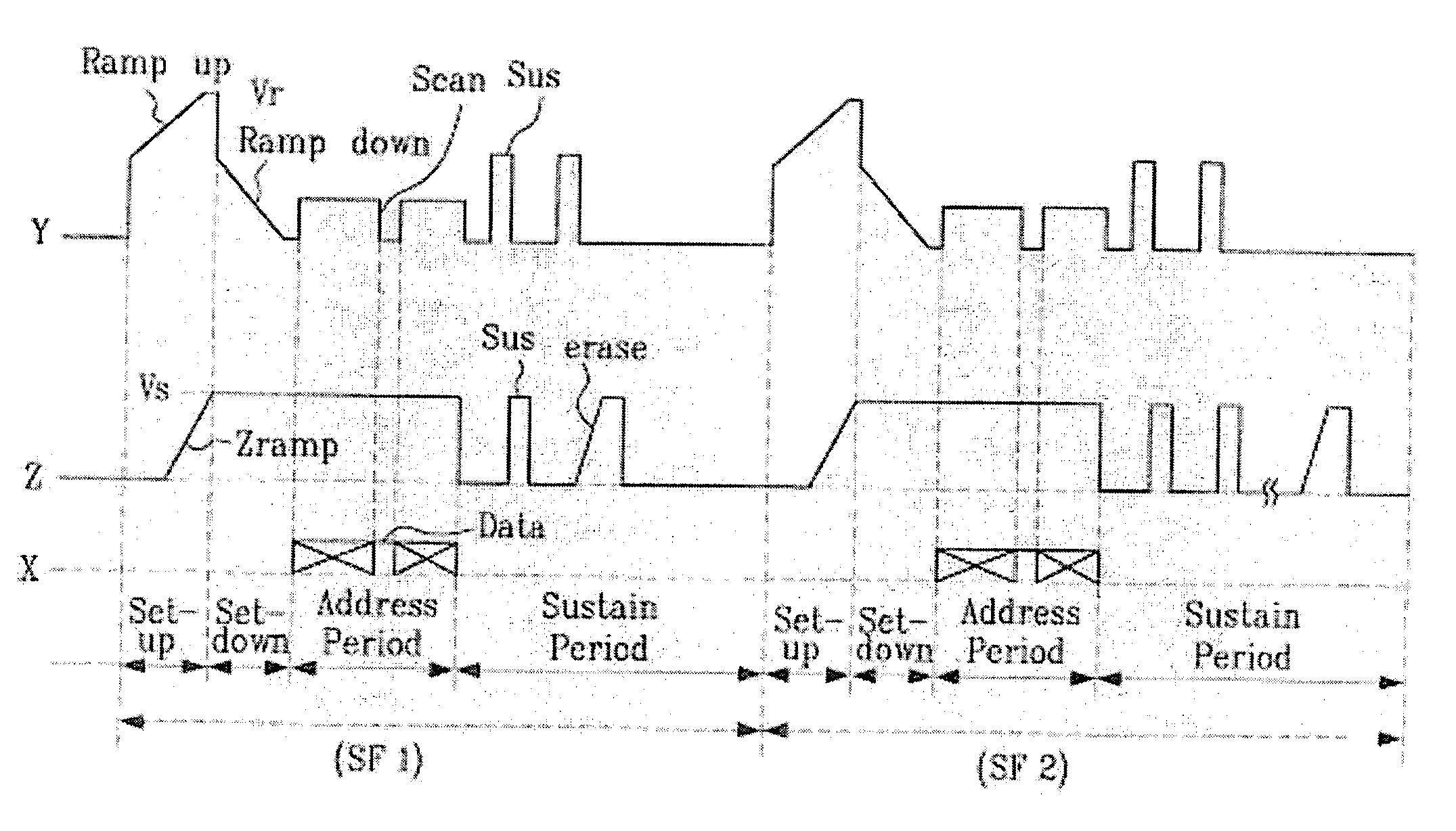

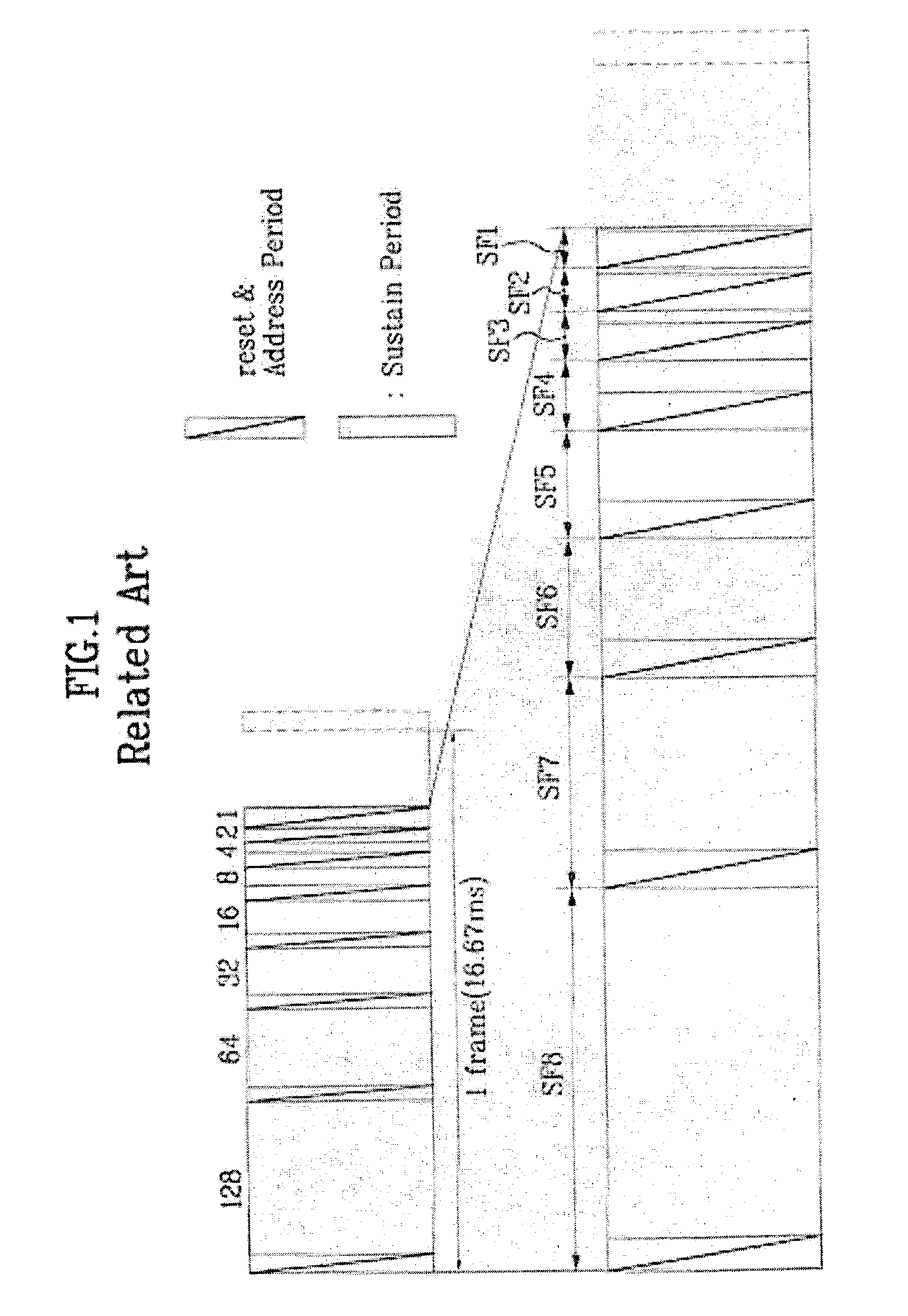

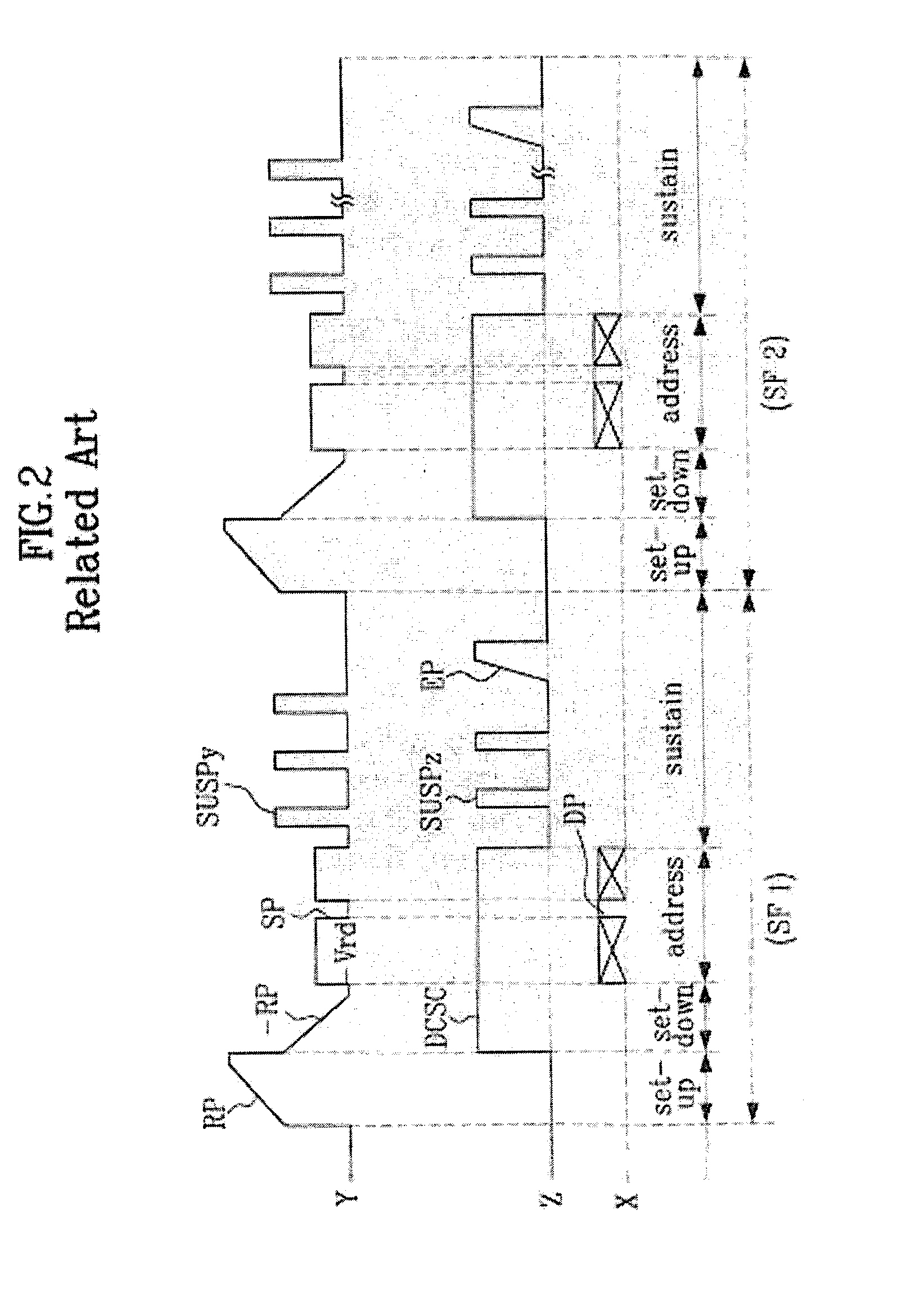

Method of driving plasma display panel

InactiveUS7012579B2Reduce voltage differenceImproved contrast characteristicsStatic indicating devicesEngineeringContrast ratio

Disclosed is a method of driving a plasma display panel enabling to improve an overall contrast characteristic of the plasma display panel by reducing a voltage difference between scan and sustain electrodes Y and Z to decrease an emission amount of light generated by a discharge between the scan and sustain electrodes Y and Z. The present invention includes a first step of applying a reset pulse to the scan electrode to form predetermined wall charges on the electrodes for a set-up period and a second step of applying a pulse of a predetermined level to the sustain electrode to reduce a voltage difference between the scan and sustain electrodes while the reset pulse is applied.

Owner:INTELLECTUAL DISCOVERY CO LTD

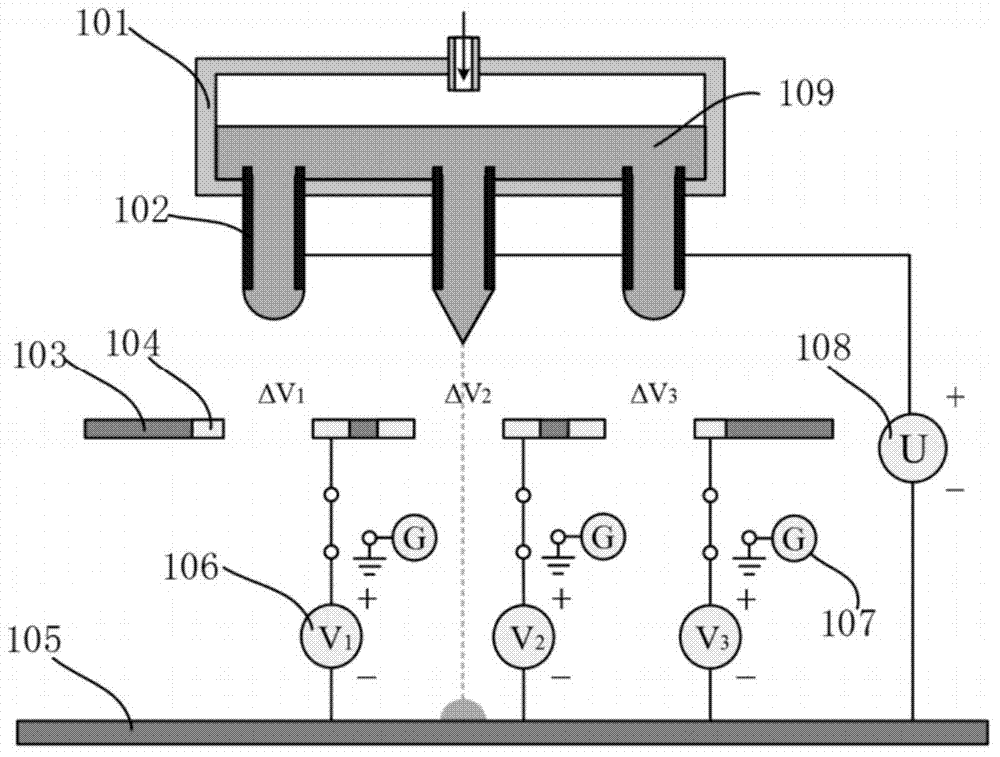

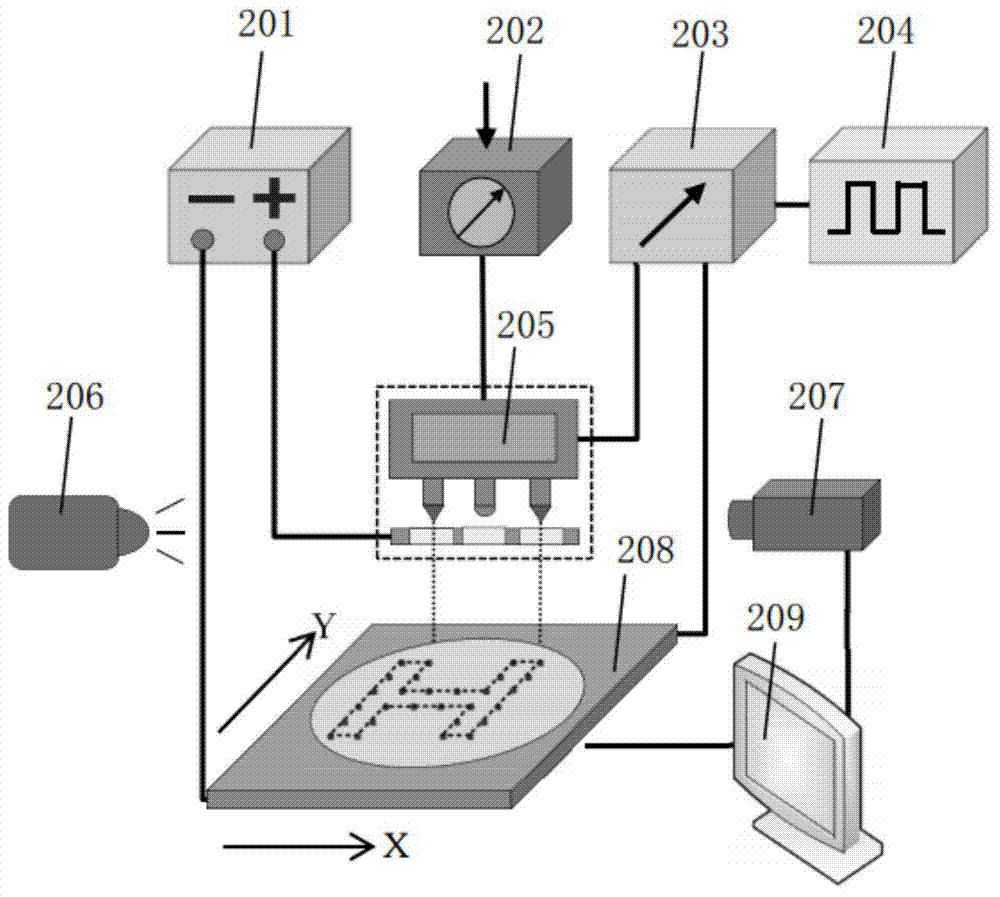

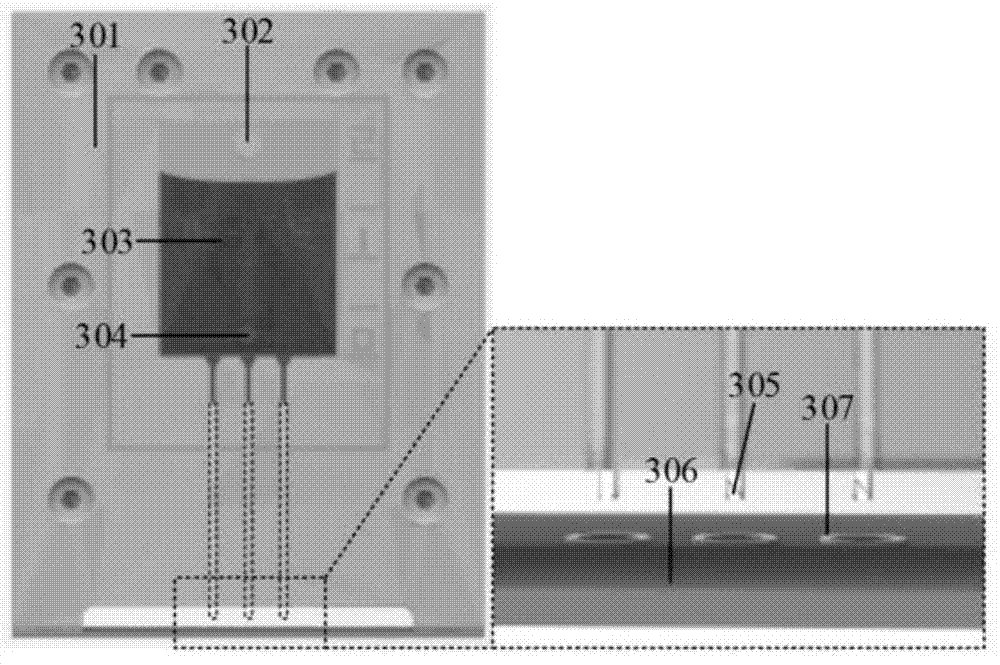

Array electric fluid jet printing head characterized by independently controllable nozzle jet and realization method of independent control of jet of nozzles

ActiveCN104191819AAchieve independent controllable injectionSimple structurePrintingSpray nozzleEngineering

The invention discloses an array electric fluid jet printing head characterized by independently controllable nozzle jet. The array electric fluid jet printing head comprises a guide electrode layer arranged between a nozzle array and a receiving plate, and a plurality of round holes corresponding to nozzles in number are formed in the guide electrode layer; the centers of the round holes are collinear with the centers of the nozzles; a circle of conducting ring is coaxially disposed on the outer periphery of each round hole in the guide electrode layer, and is connected with one voltage source; and the nozzle array is connected with the jet voltage sources; and the voltage value of each voltage source is properly adjusted, so that the voltage differences of the nozzles required for jet printing and the corresponding conducting rings are greater than the voltage differences of the remaining nozzles, the field strength of the nozzles for jet is greater than the field strength needed to start the jetting, the field strength of the nozzles not required for jetting is lower than the field strength needed to start the jetting, and the independent control of all the nozzles can be realized. The invention further discloses a realization method of the independent control of the jet of the nozzles. The array electric fluid jet printing head and the realization method can solve the problems of complex structure and incapability of large-scale integrated use in the conventional independent jet control to printing heads.

Owner:HUAZHONG UNIV OF SCI & TECH

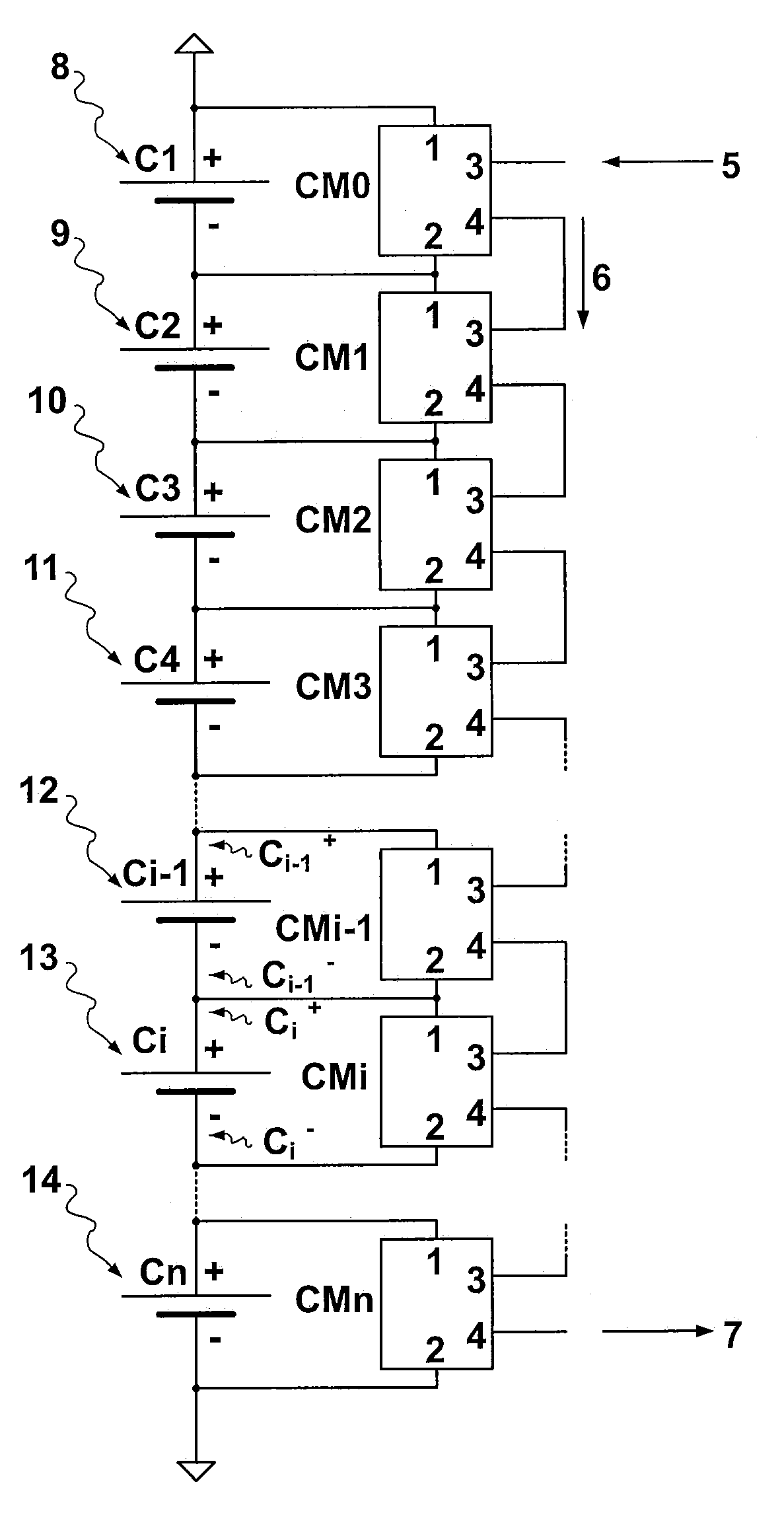

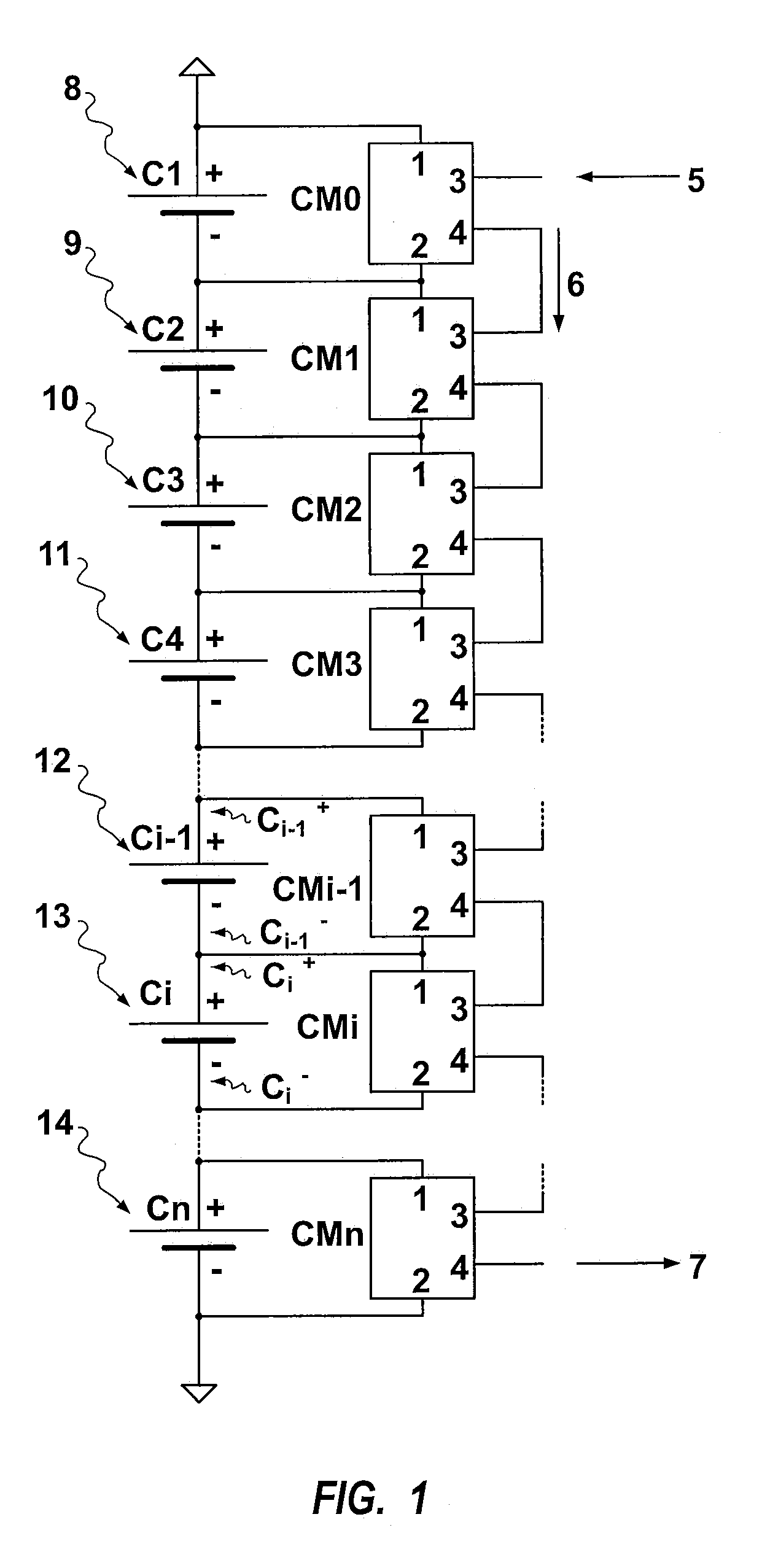

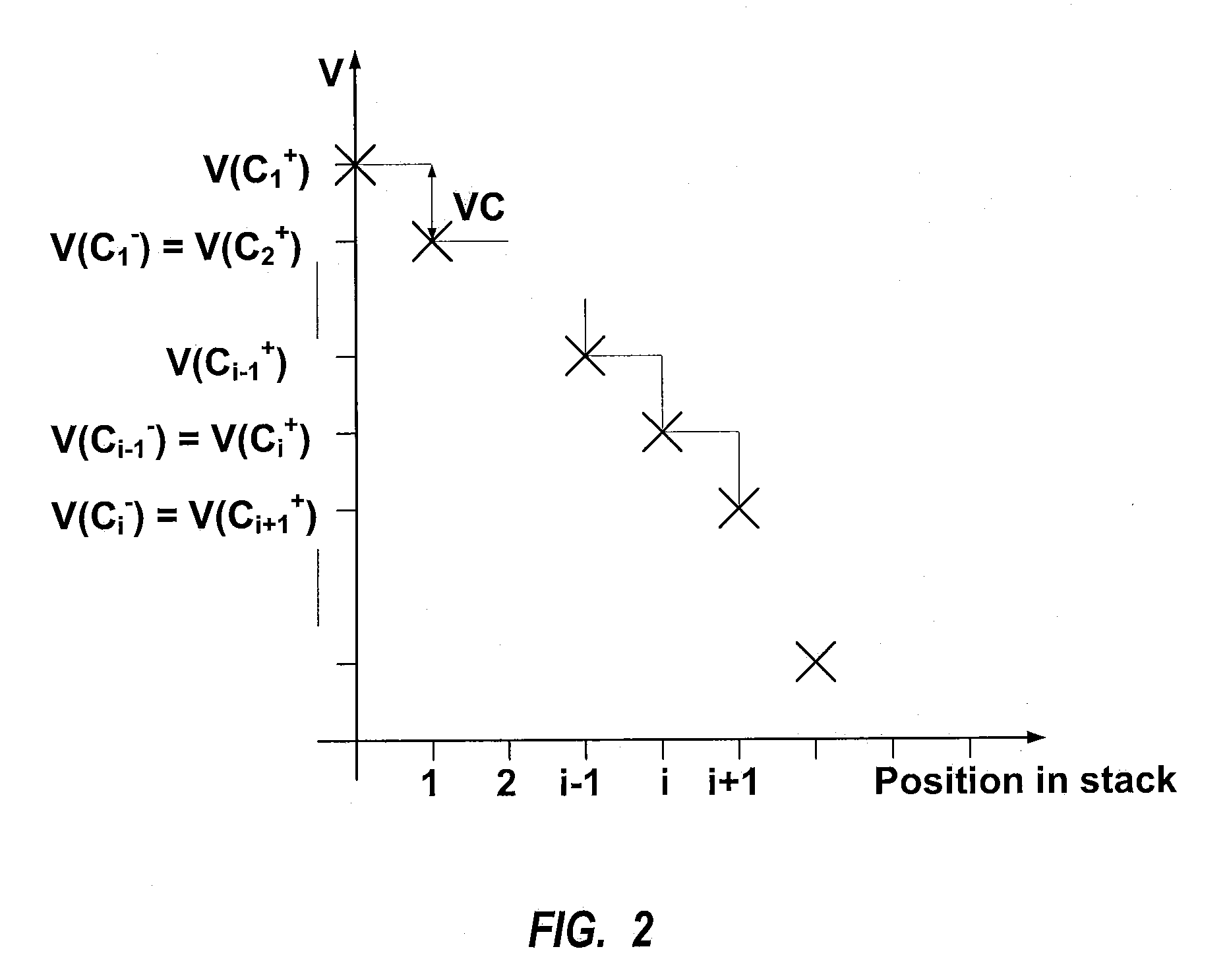

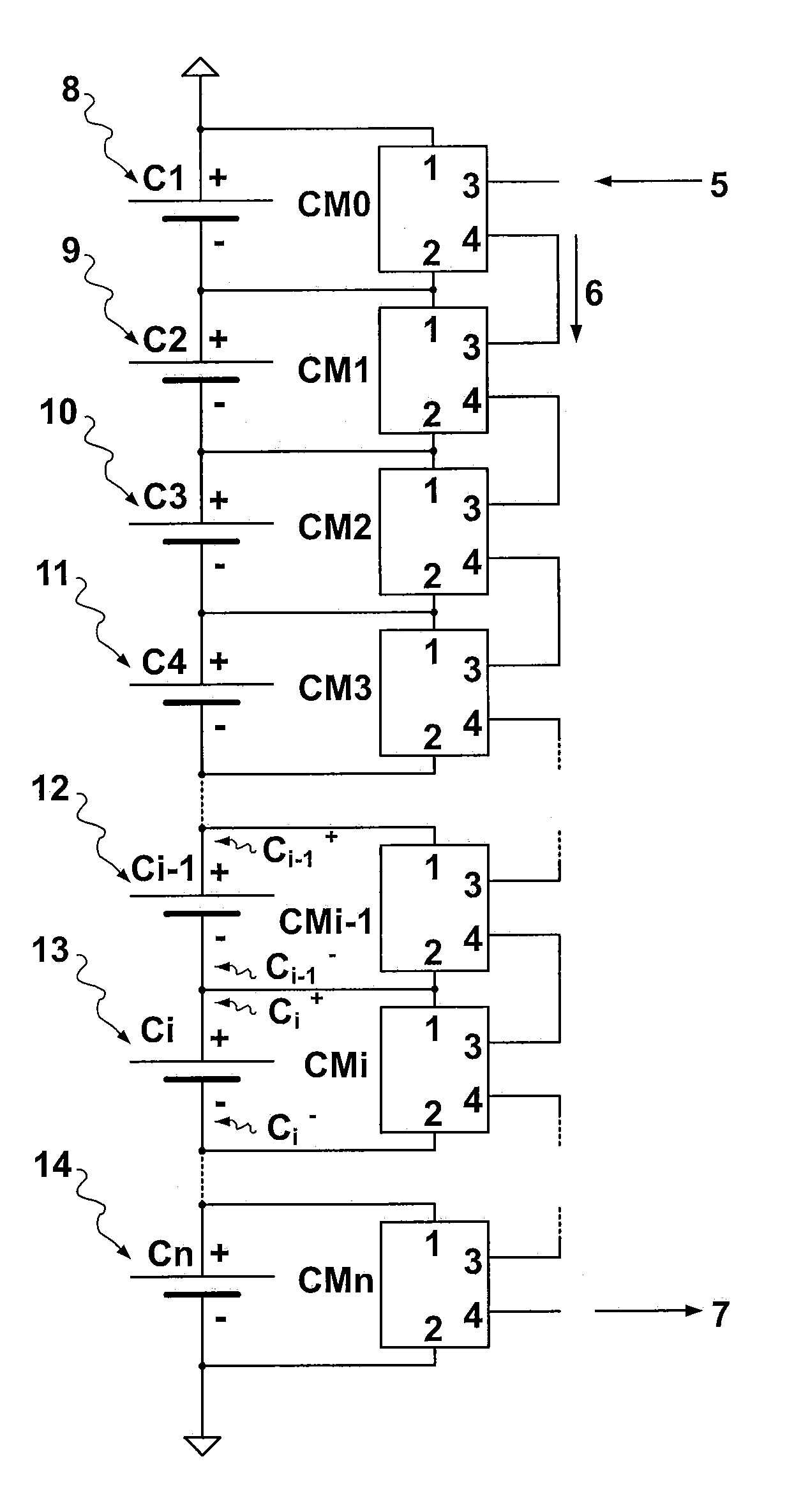

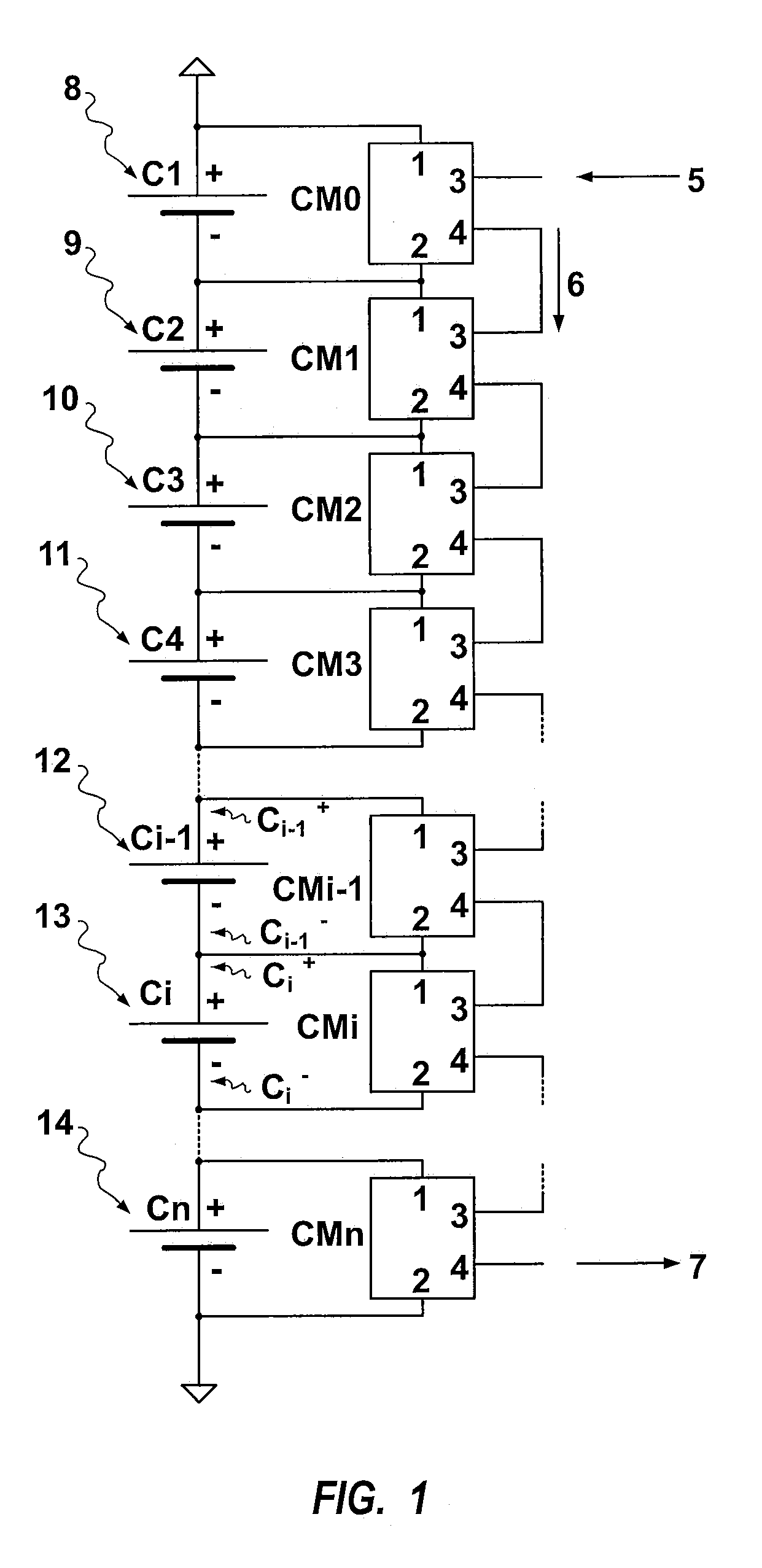

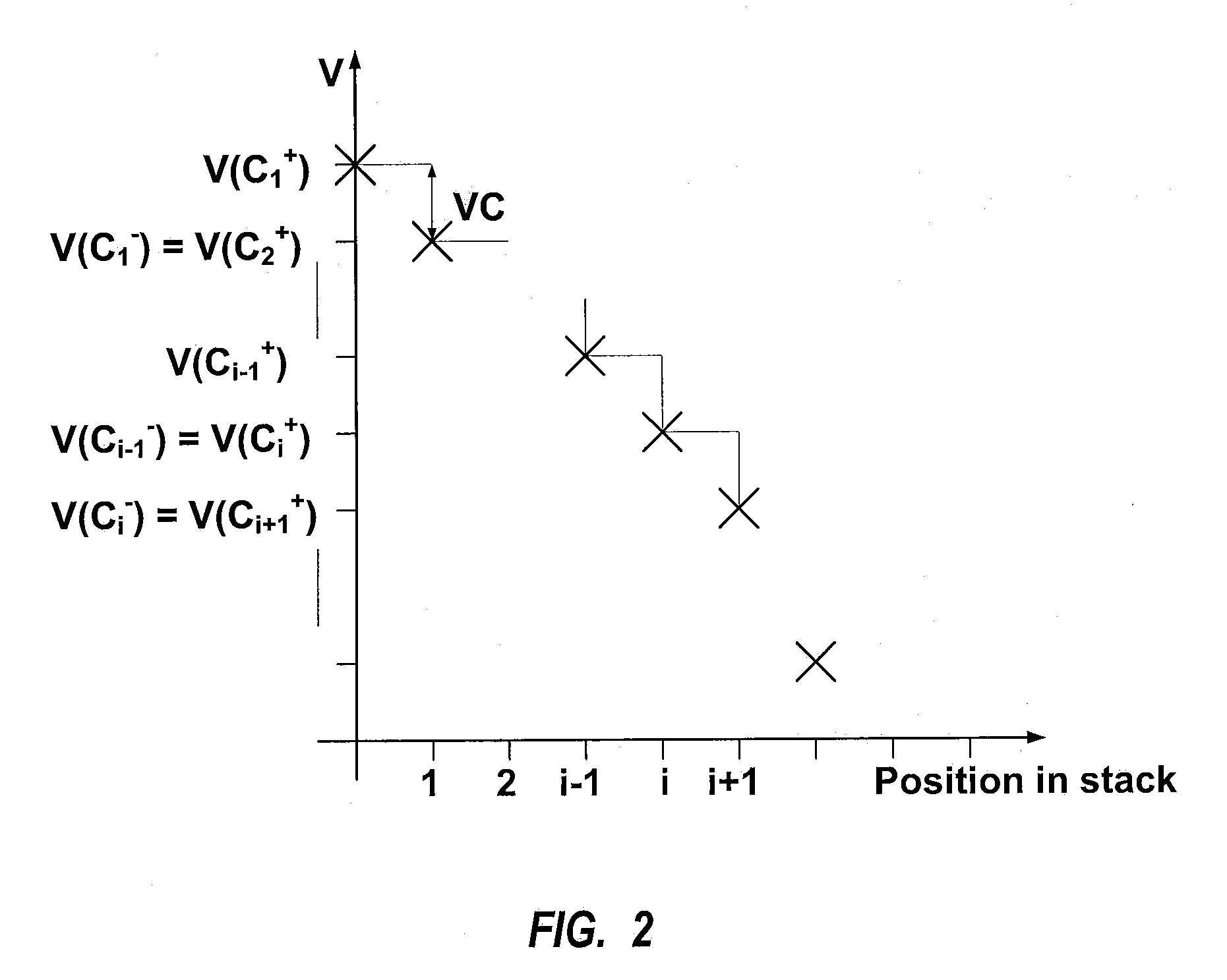

Power cell monitoring

ActiveUS20080143543A1Easy to optimizeReduce voltage differenceCircuit monitoring/indicationCharge equalisation circuitElectrical batteryInformation delivery

The invention relates to a signaling system for use in a system for monitoring and / or controlling a stack of power cells. The stack of power cells is series connected, i.e. the negative terminal of one power cell is connected to the positive electrode of the adjacent power cell. A monitoring device is associated with each power cell to monitor characteristics of the power cell (temperature, voltage). Every monitoring device is powered by the power cell it is associated. The monitoring device monitors the status of the cell (e.g. it measures the difference of potential between the positive terminal and the negative terminal of that cell but it may also measure the temperature of the power cell, the pH of the electrolyte if the power cell Ci is a battery, etc. and communicates information on the status of the cell to other monitoring devices. The monitoring devices are daisy chained. Data cannot be exchanged between a monitoring device from one cell and a monitoring device from another cell without that the data sent by the one device transits by the other devices in the chain.

Owner:AMI SEMICON BELGIUM

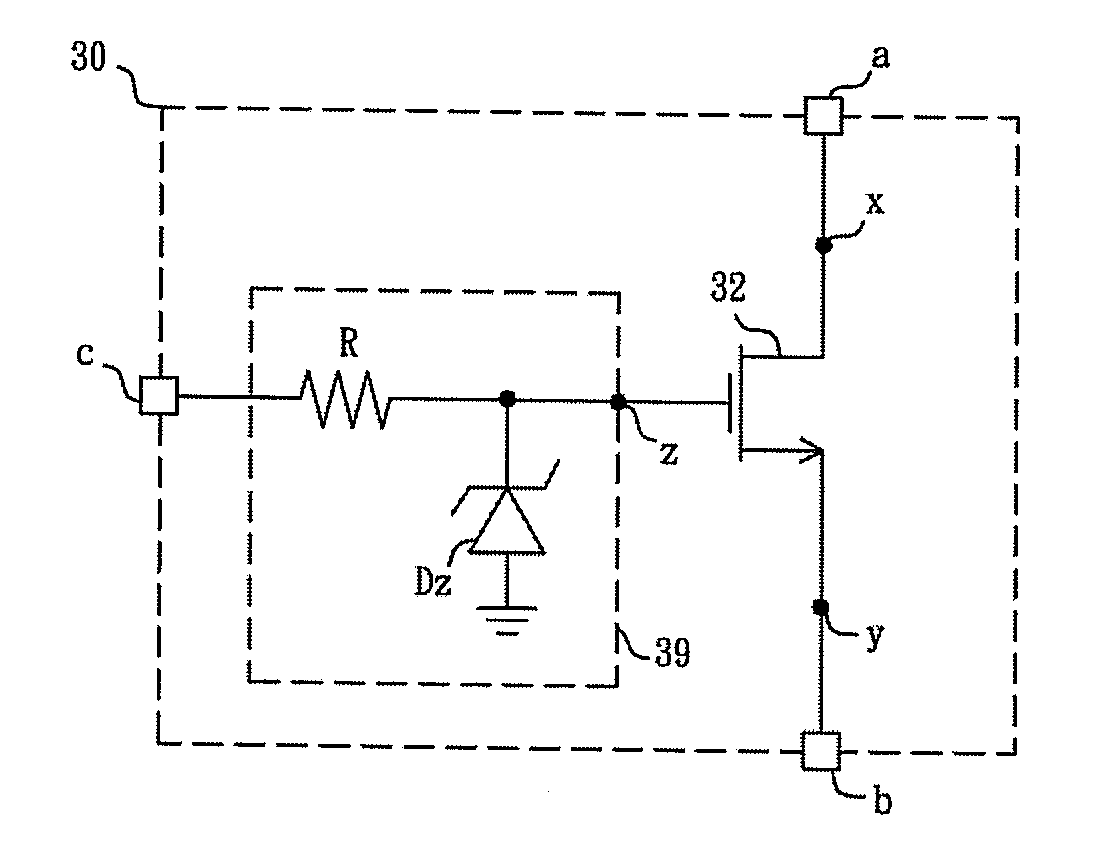

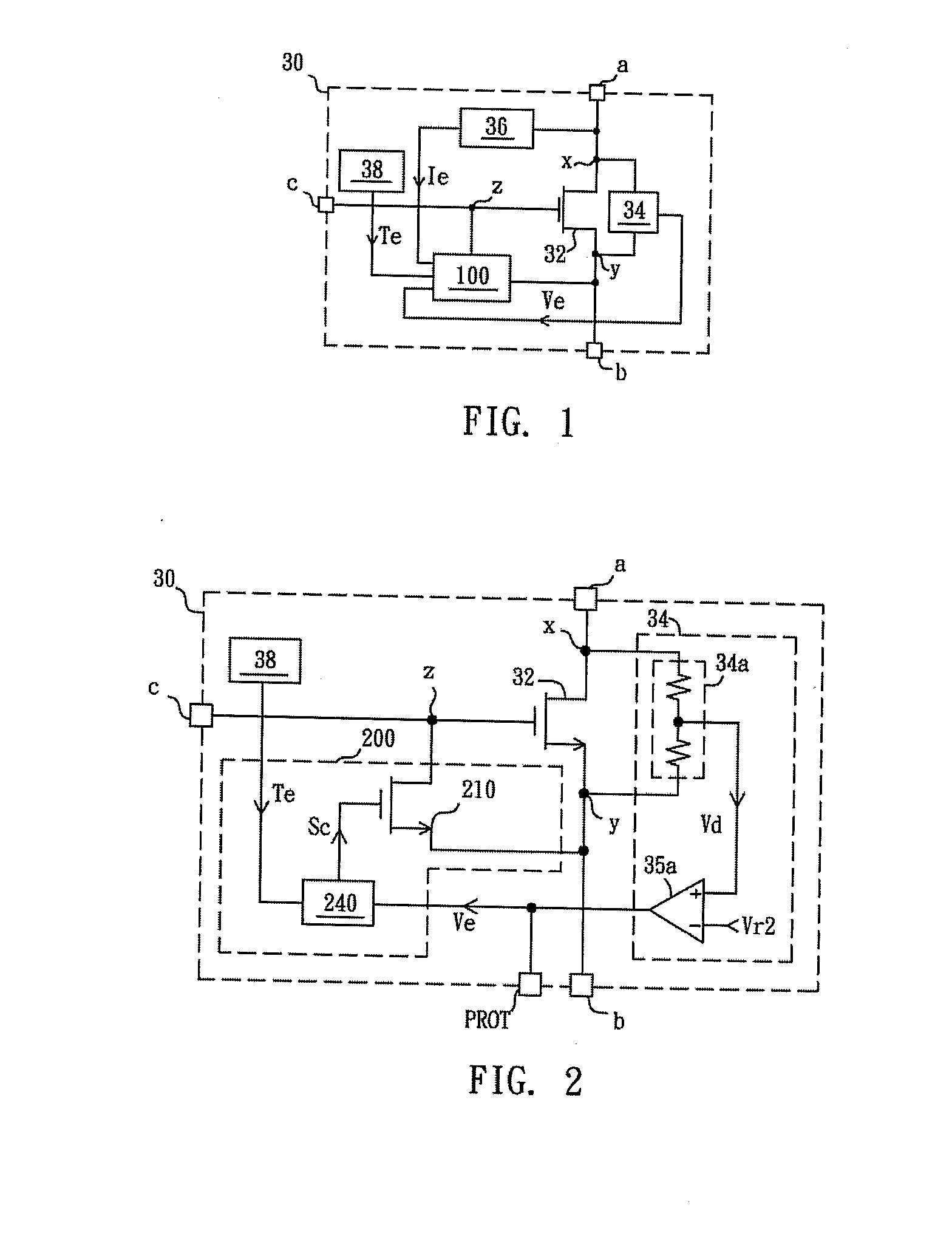

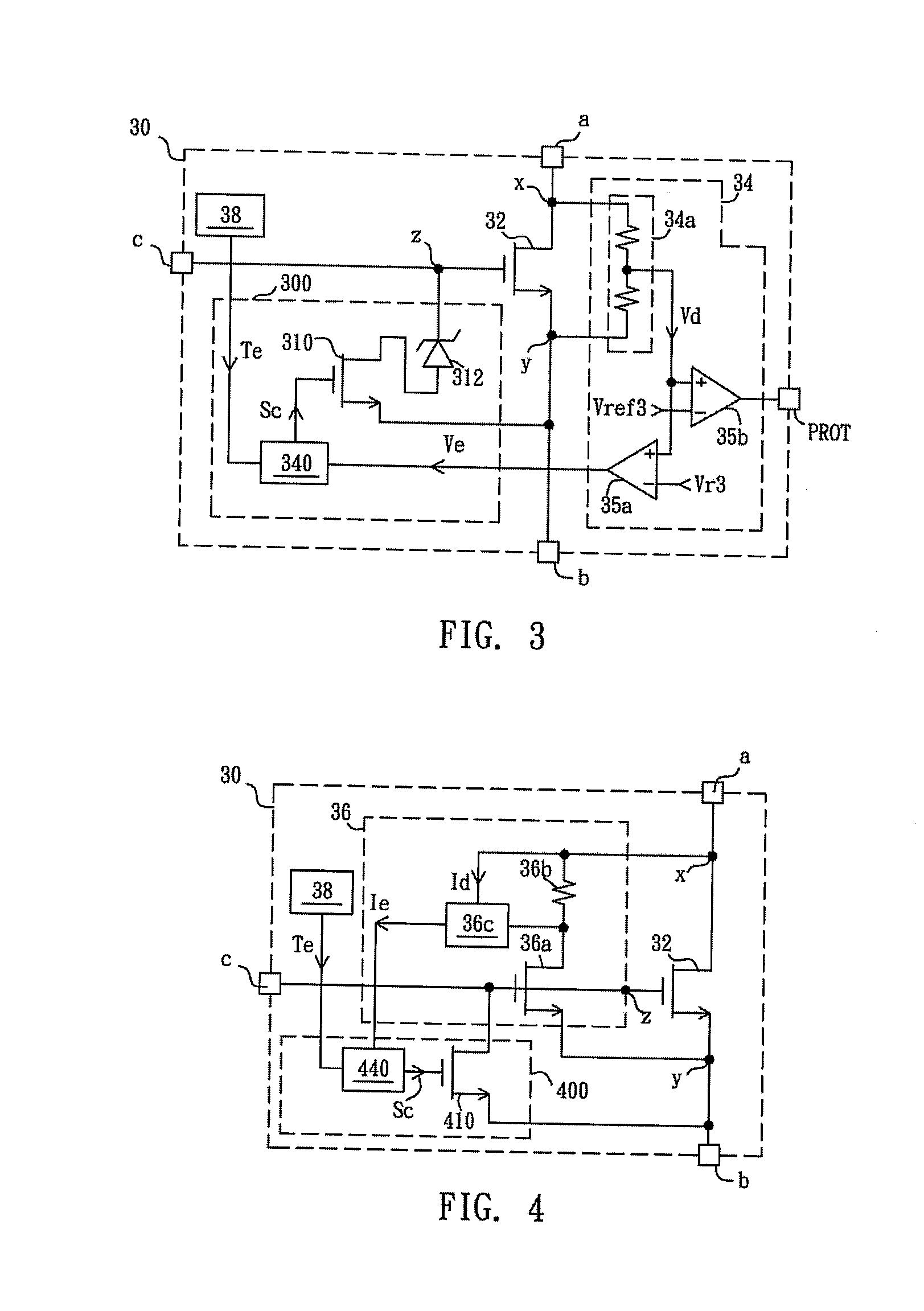

Transistor circuit with protecting function

InactiveUS20120236456A1Low costHigh yield rateTransistorElectroluminescent light sourcesPower flowVoltage drop

The present invention provides a transistor circuit with protecting function. The transistor circuit includes a transistor, a voltage detecting unit, a current detecting unit, a temperature detecting unit, and a protecting unit. The voltage detecting unit detects a voltage drop of the transistor and generates an over-voltage protection signal. The current detecting signal detects a current flowing through the transistor and generates an over-current protection signal. The temperature detecting unit detects a temperature of the transistor circuit and generates an over-temperature protection signal. The protecting unit is coupled to the control terminal to control a state of the transistor according to the over-voltage protection signal, the over-current protection signal, and the over-temperature protection signal to reduce the voltage difference between the control terminal and the second terminal, such that the voltage drop of the transistor is decreased or decreased to zero.

Owner:GREEN SOLUTION TECH CO LTD

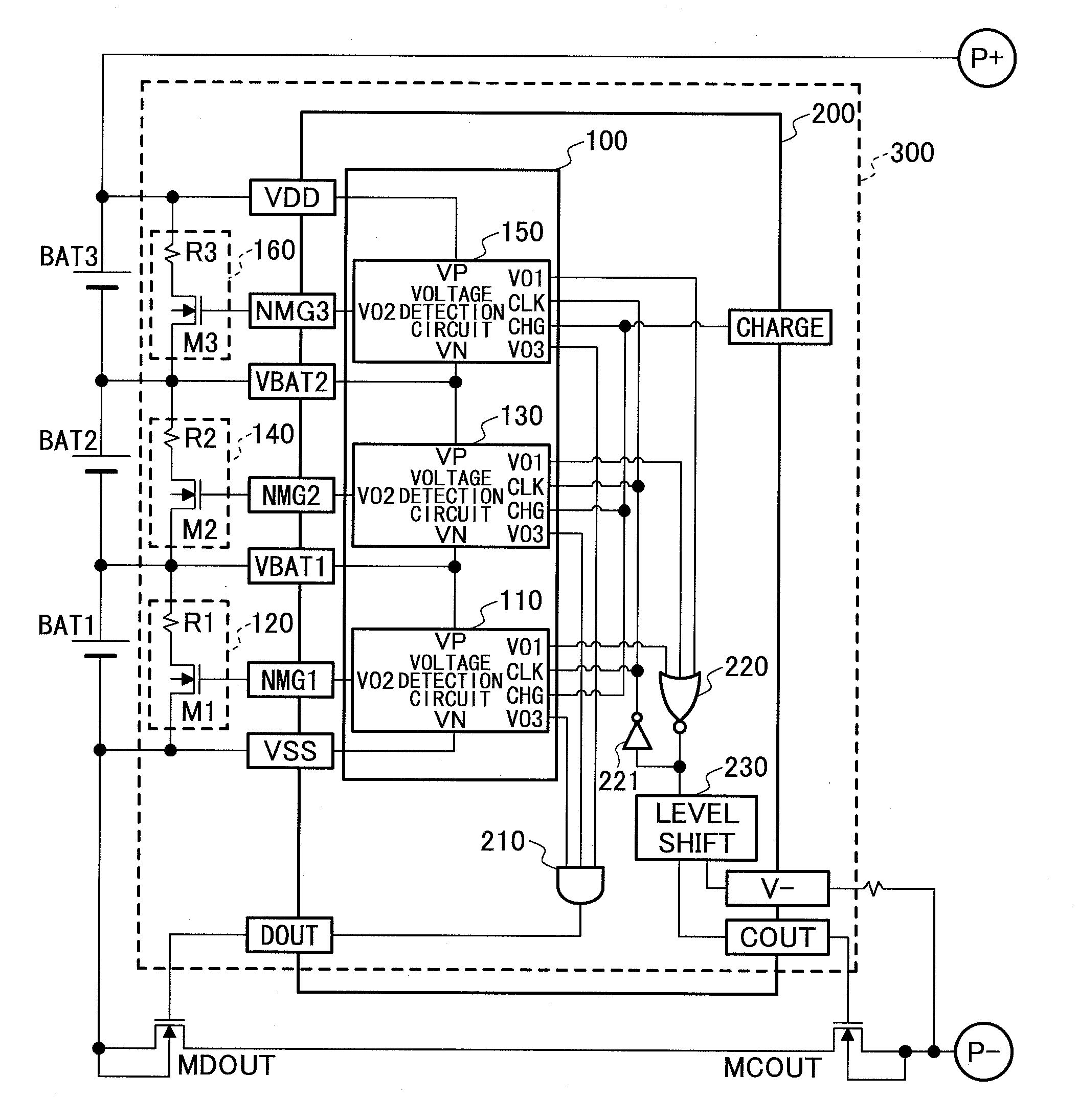

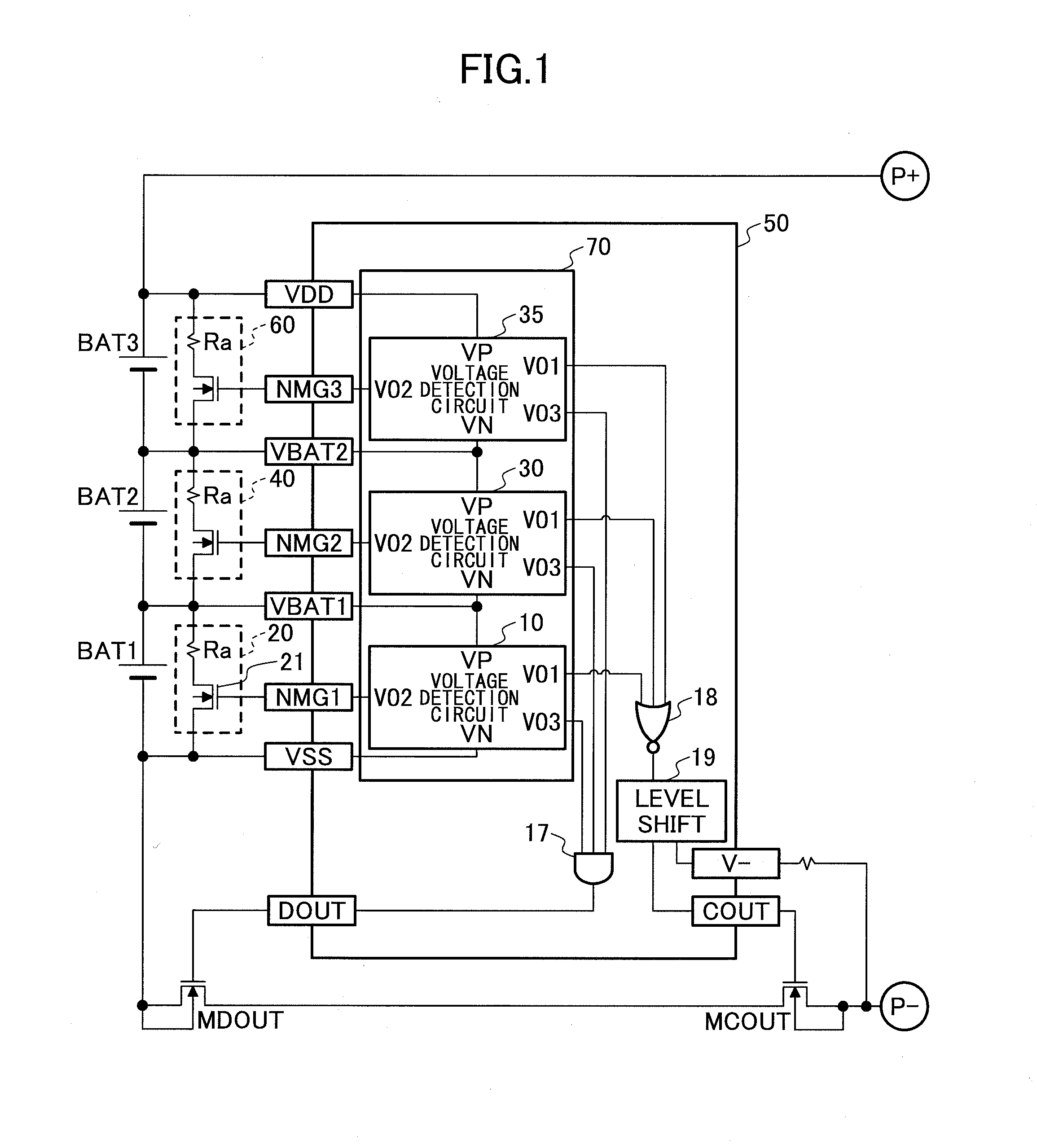

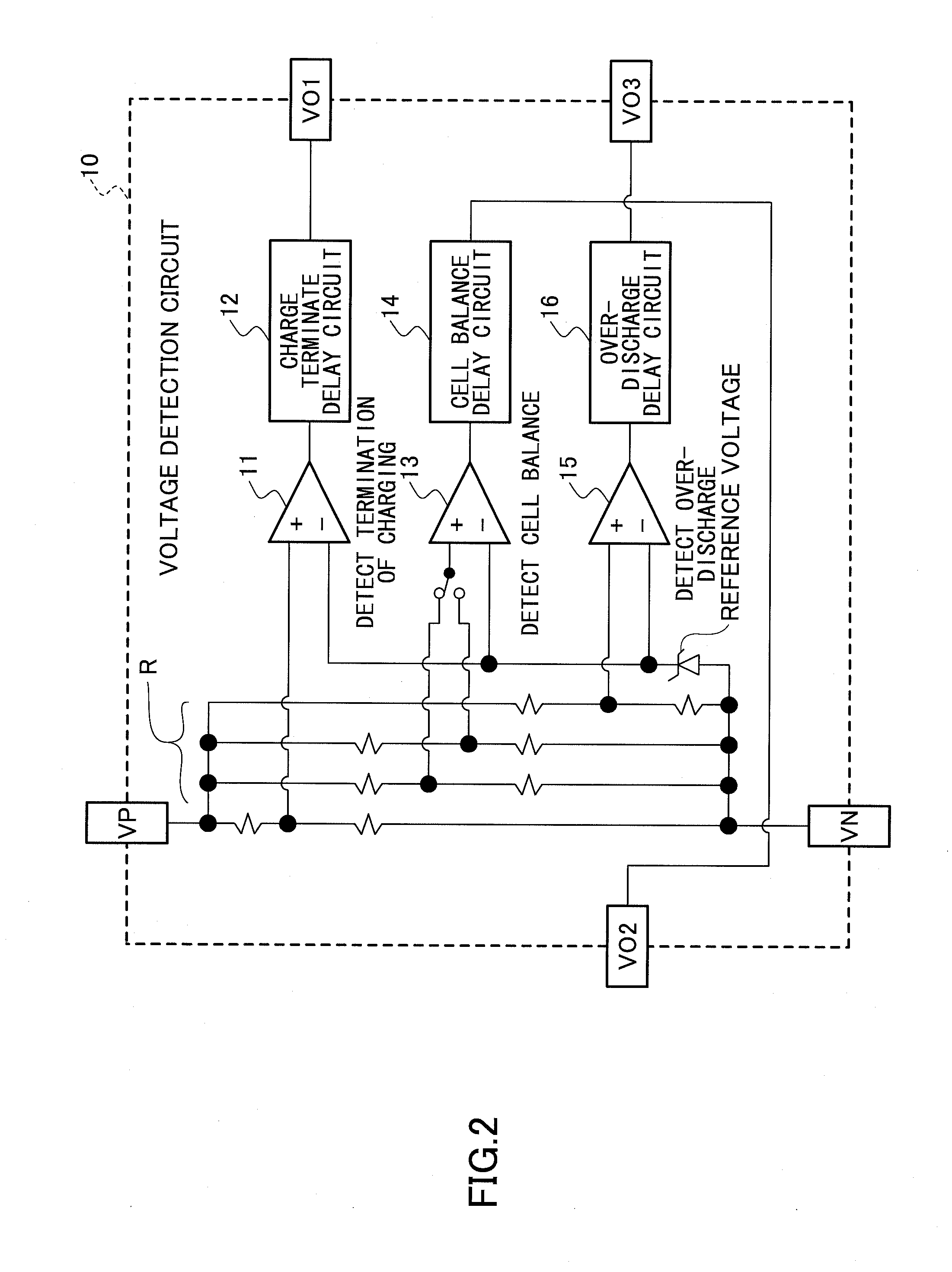

Charge-discharge control circuit, semiconductor integrated circuit, method of controlling charging and discharging, and charging and discharging control program

ActiveUS20120206105A1Improve efficiencyExtended service lifeCharge equalisation circuitSecondary cellsElectrical batteryIntegrated circuit

A charge-discharge control circuit includes a cell balance detection circuit that detects that a voltage of a cell reaches a predetermined voltage; a memory circuit that stores the cell that reaches the predetermined voltage first among plural of the cells; bypass circuits respectively connected to the plural cells in parallel, each of the bypass circuits including a switch unit for bypassing the current that flows through the corresponding cell when charging; and a control circuit that controls the switch units, wherein the control circuit controls the switch unit based on the cell stored in the memory circuit so that an ON / OFF status of the switch unit is maintained from a start to an end of a next charging operation subsequent to a charging operation during which the cell is stored in the memory circuit.

Owner:MITSUMI ELECTRIC CO LTD

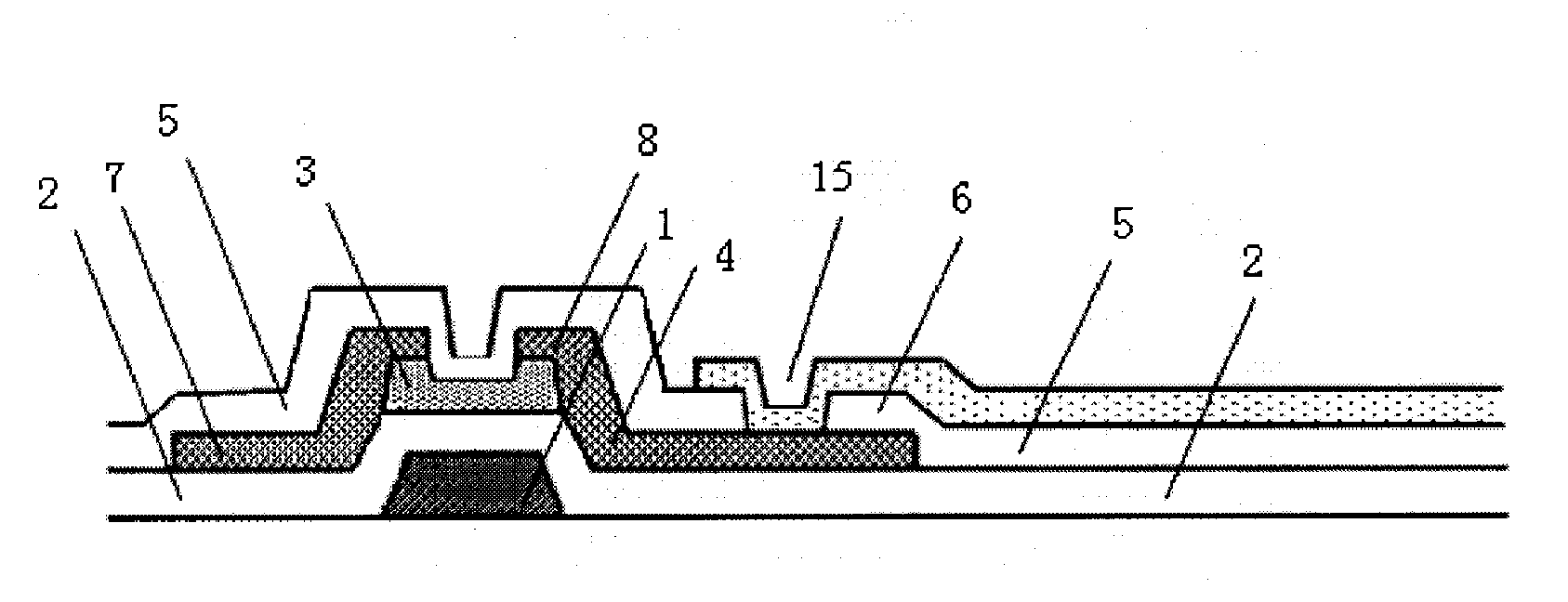

Thin film transistor, manufacturing method thereof, and TFT LCD using the same

ActiveUS20080105874A1Cgs can be reducedImprove display qualitySolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

A thin film transistor (TFT) that comprises a gate electrode on a substrate, a gate insulation layer on the gate electrode, an active layer having a source region, a drain region, and a channel region on the gate insulation layer, and a source electrode and a drain electrode formed over the source region and drain region of the active layer respectively and facing each other with respect to the channel region. The profile of channel region between the source electrode and drain electrode is changed in a bend line. A method for forming the TFT is also provided.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD +1

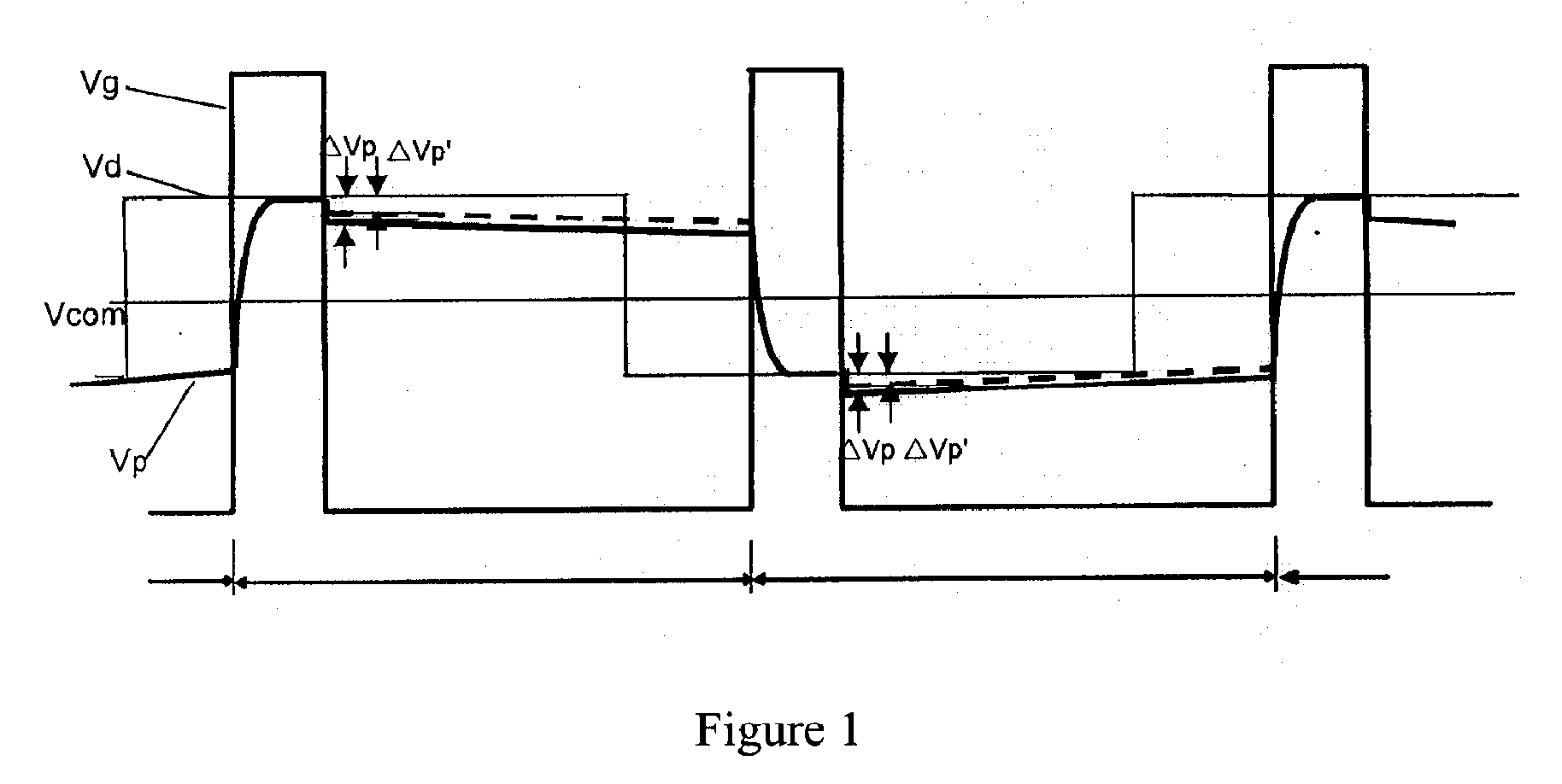

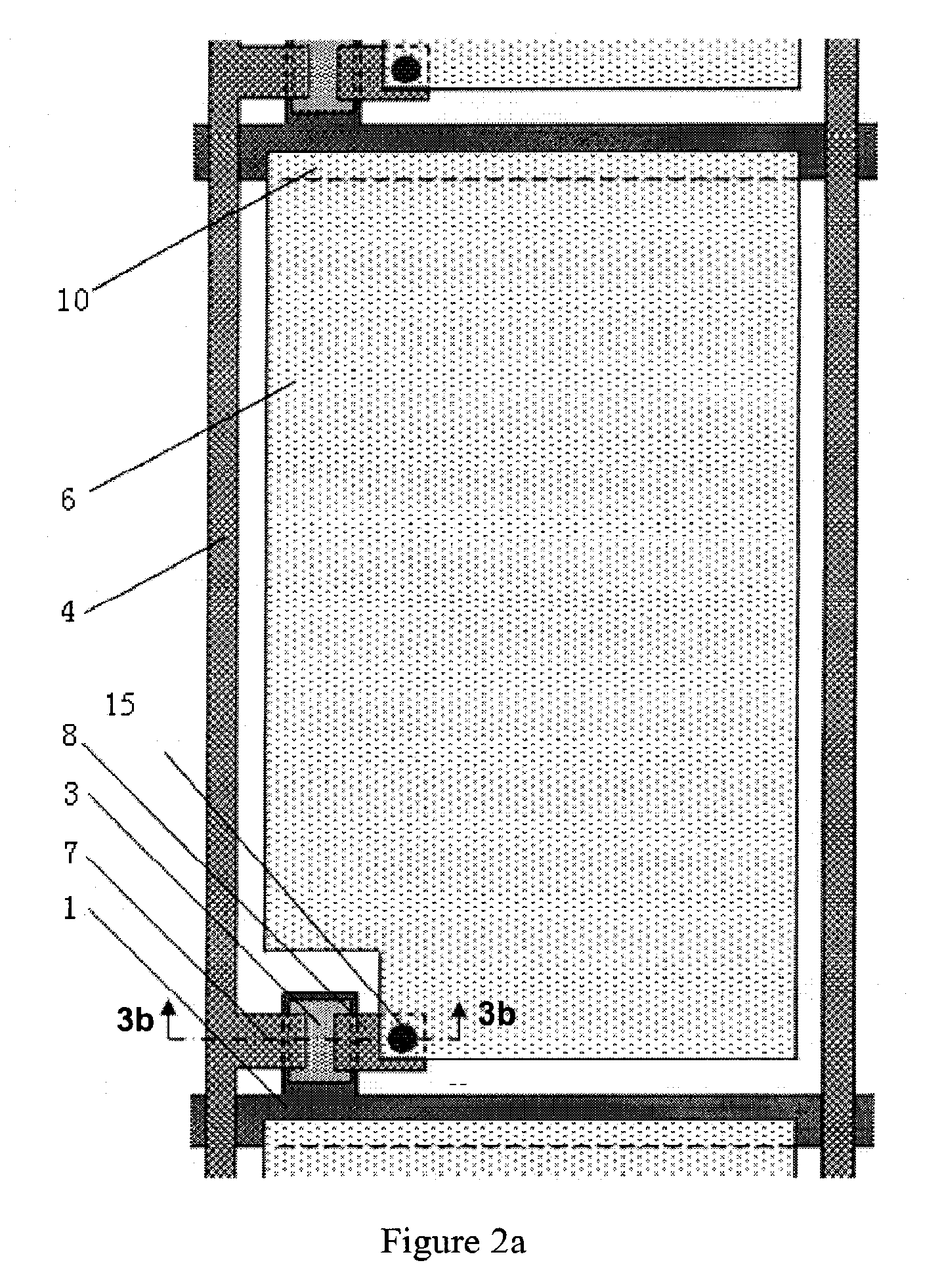

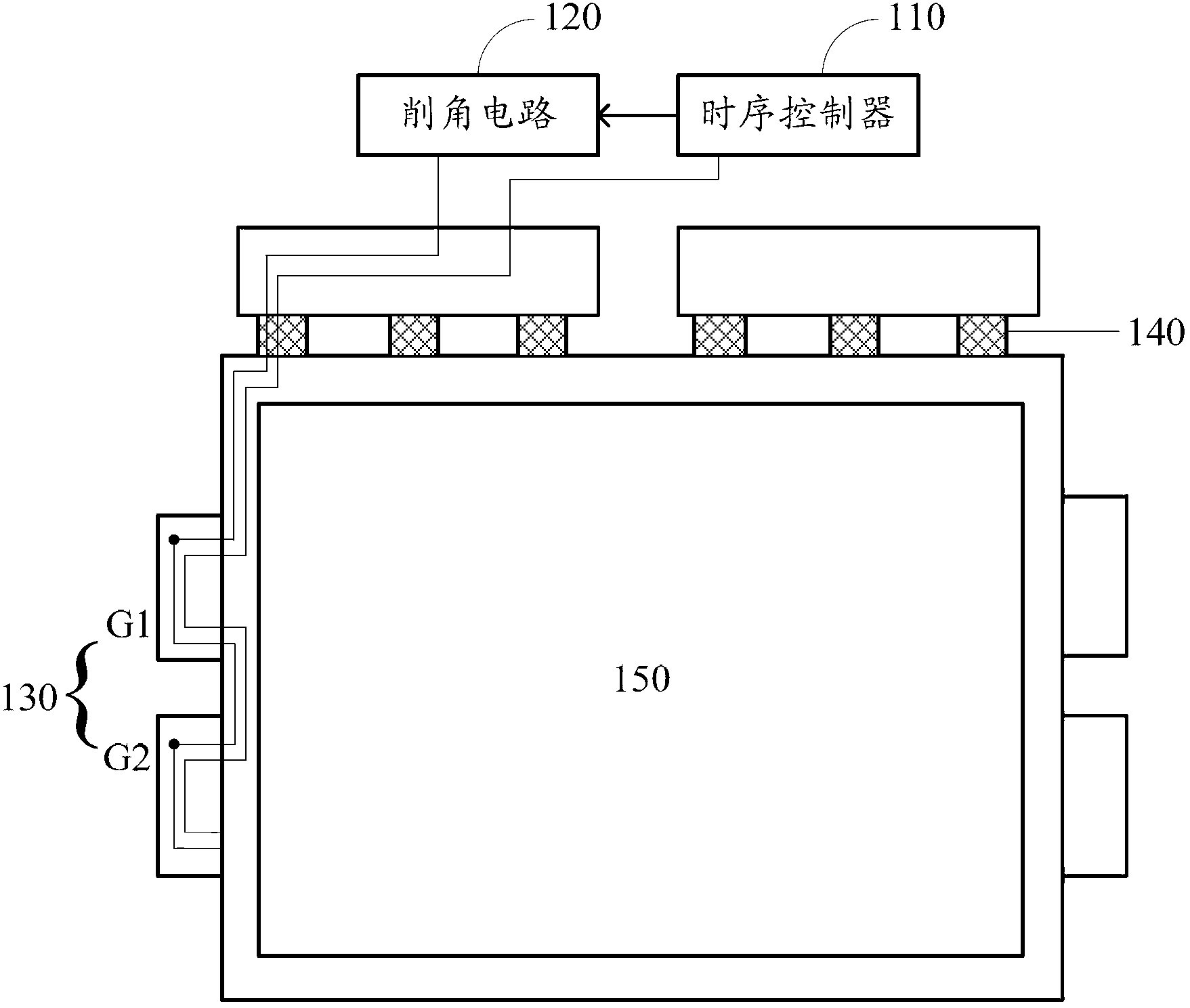

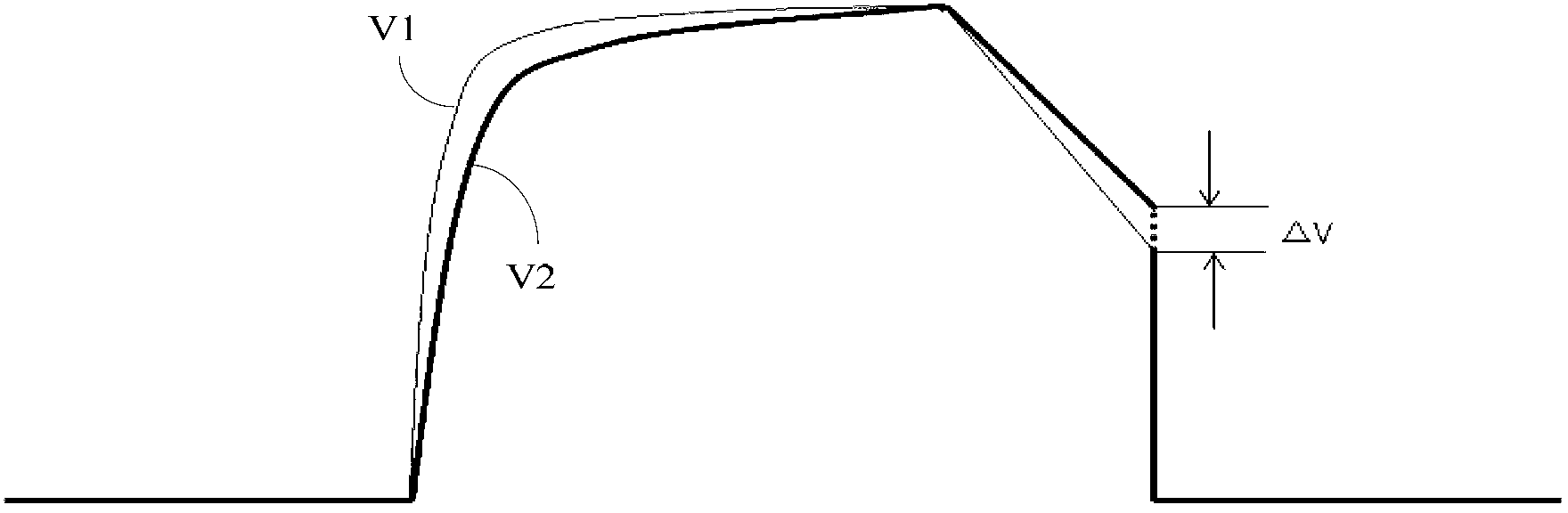

Chamfering circuit and control method thereof

ActiveCN103247280AReduce voltage differenceEliminate uneven brightnessStatic indicating devicesSequence signalEngineering

The invention provides a chamfering circuit and a control method thereof. The chamfering circuit comprises a direct current voltage input terminal, a chamfering voltage output terminal, a first switching circuit, a second switching circuit, a switching circuit, a first discharging circuit and a second discharging circuit, wherein the switching circuit selectively connects the second switching circuit to the first discharging circuit or the second discharging circuit under the control of a third sequence signal, so as to form a first chamfering voltage with the first discharging slope at the chamfering voltage output terminal, or to form a second chamfering voltage with the second discharging slope at the chamfering voltage output terminal; and the first discharging slope is different from the second discharging slope. Through the invention, the phenomenon of nonuniform brightness in the vertical direction of a display picture can be eliminated, and the display quality of a liquid crystal device is improved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

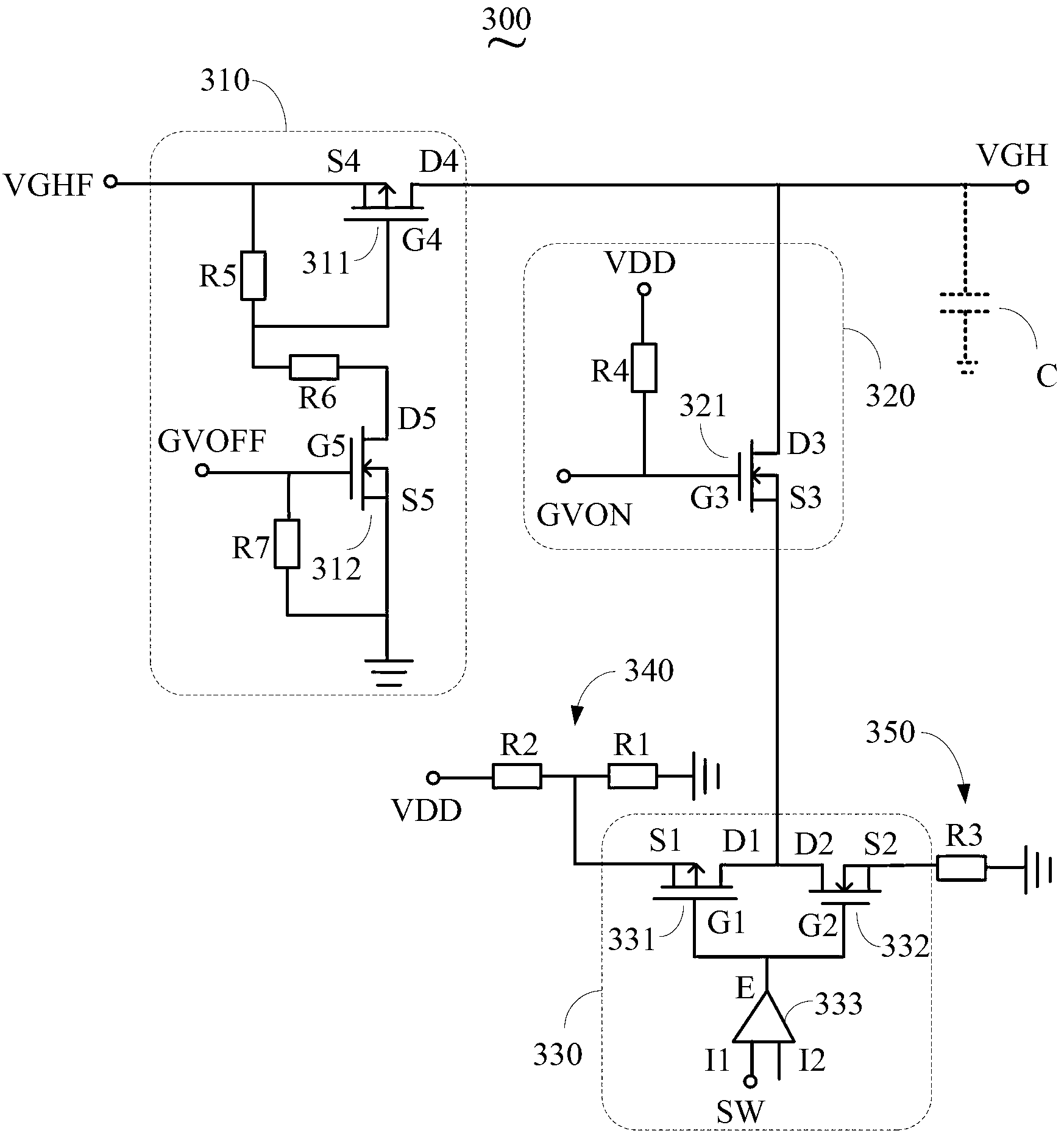

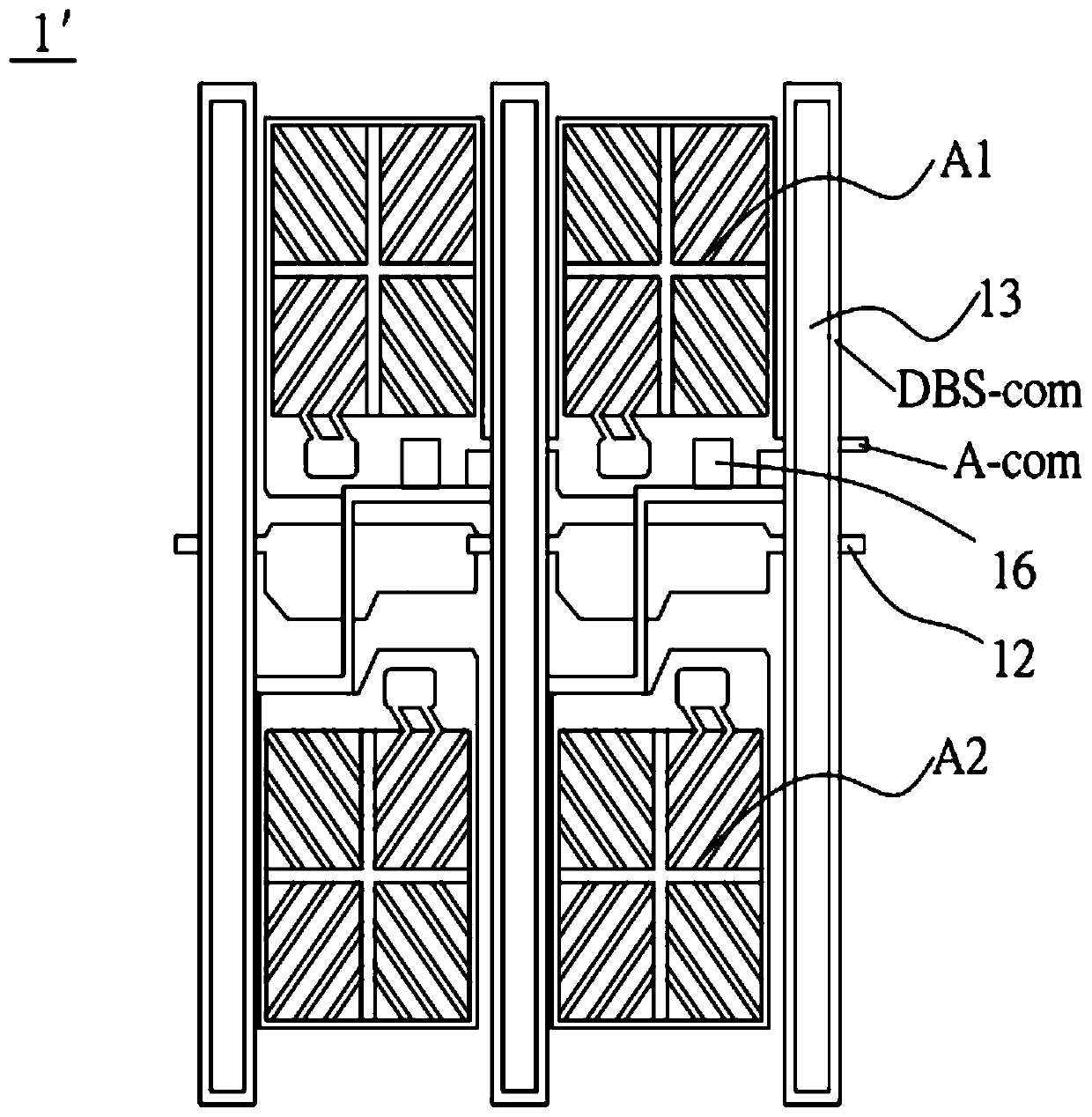

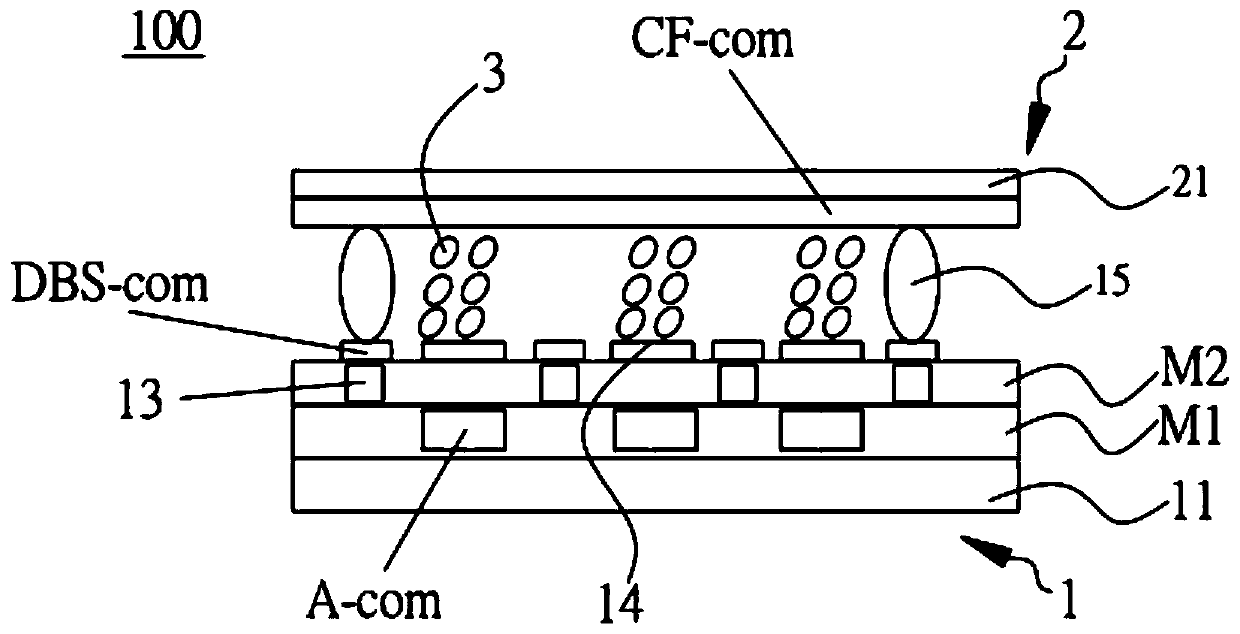

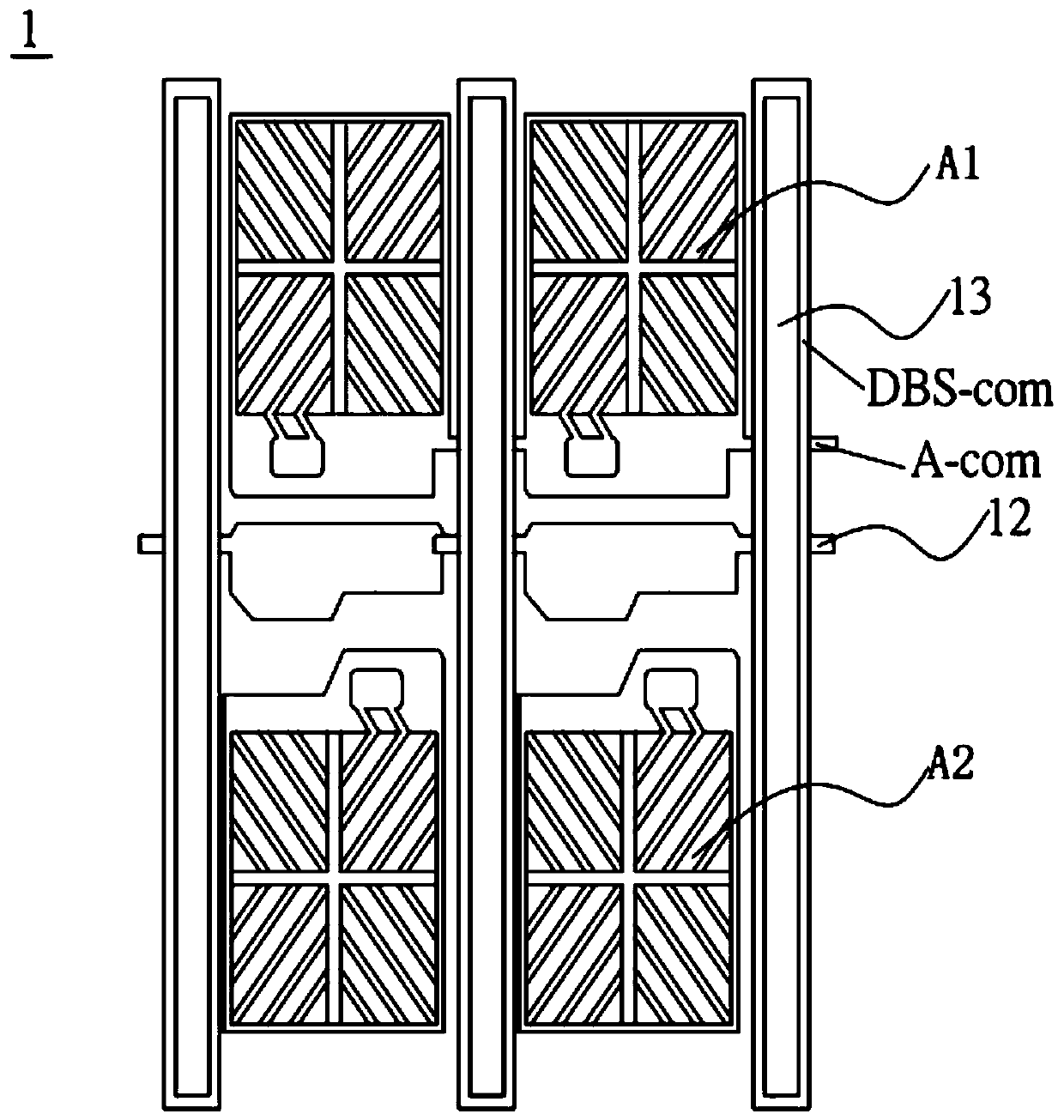

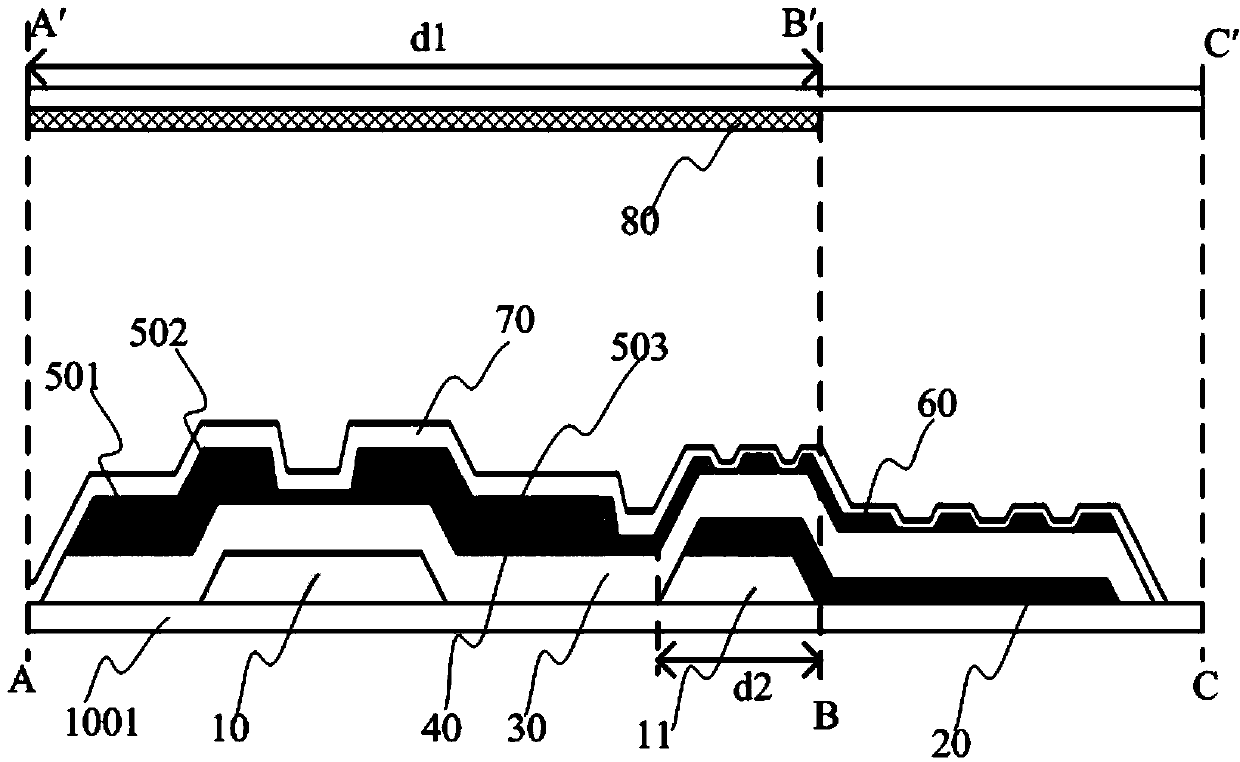

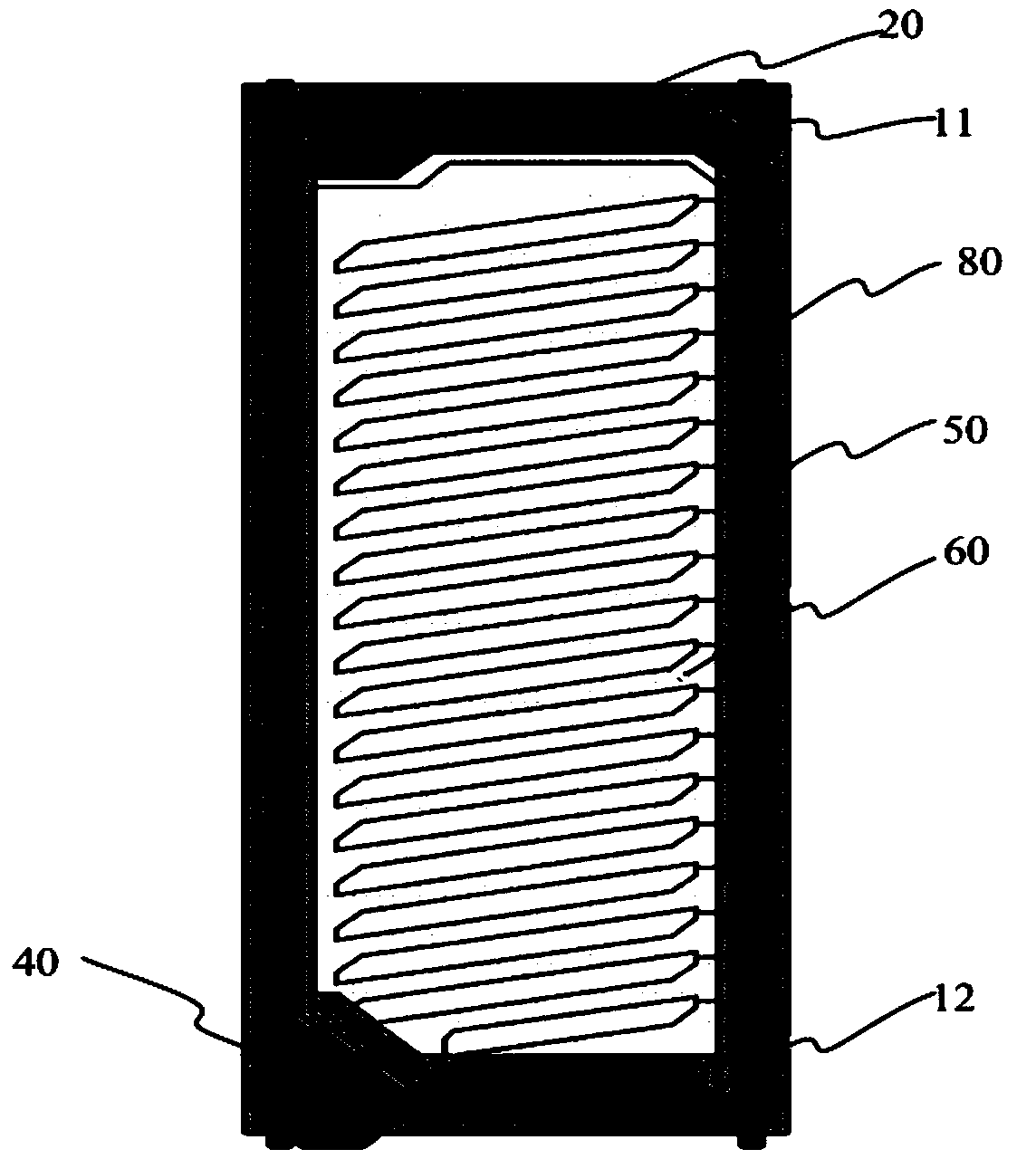

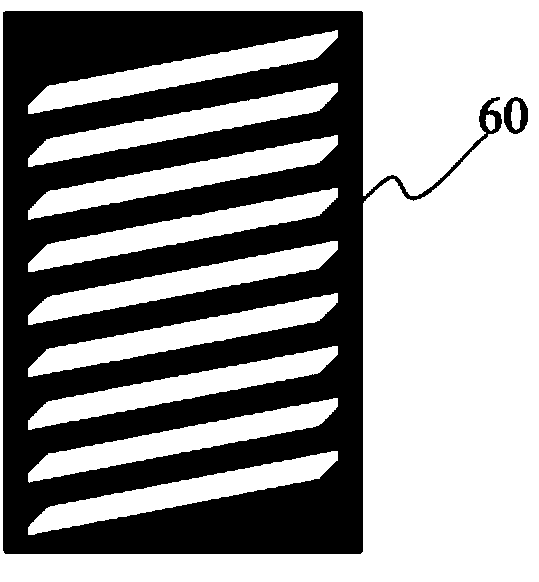

Liquid crystal display panel and display device

InactiveCN110082970AReduce foreign body sensationReduce voltage differenceNon-linear opticsForeign matterElectricity

The invention provides a liquid crystal display panel and a display device. The liquid crystal display panel comprises an array substrate, a color film substrate as well as a liquid crystal layer arranged between the array substrate and the color film substrate, wherein the array substrate comprises multiple scanning lines, multiple data lines, multiple pixel units defined by multiple scanning lines and multiple data lines as well as multiple DBS common electrode wires arrange above multiple data lines, partial DBS common electrode wires located at the periphery of the pixel units are electrically connected with a common electrode layer of the color film substrate, and partial DBS common electrode wires located at the inner sides of the pixel units are not connected with a common electrodewire of the array substrate, so that under the premise that an overall design architecture of the pixel units is not changed, voltage difference between the DBS common electrode wires and the commonelectrode layer of the color film substrate is reduced when the liquid crystal display panel performs light phase matching, burn caused by conductive foreign matters is avoided, foreign body sensationof the liquid crystal display panel is reduced, and yield is improved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

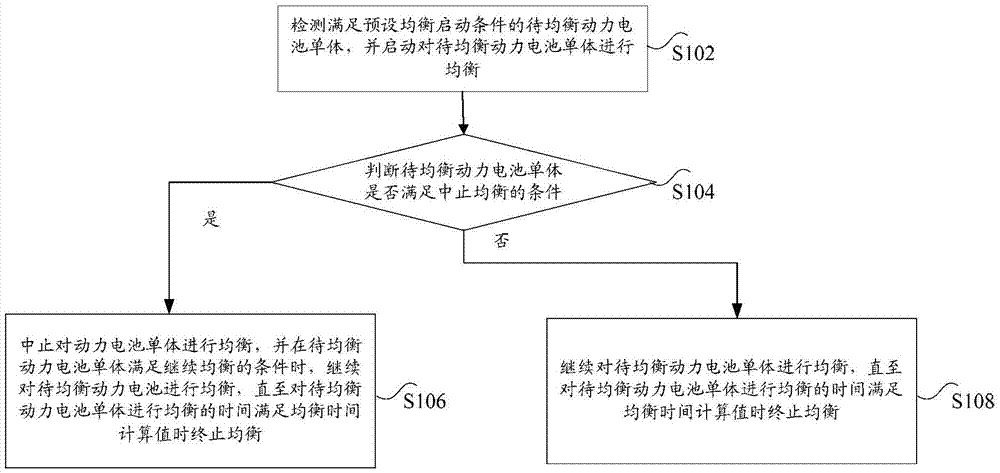

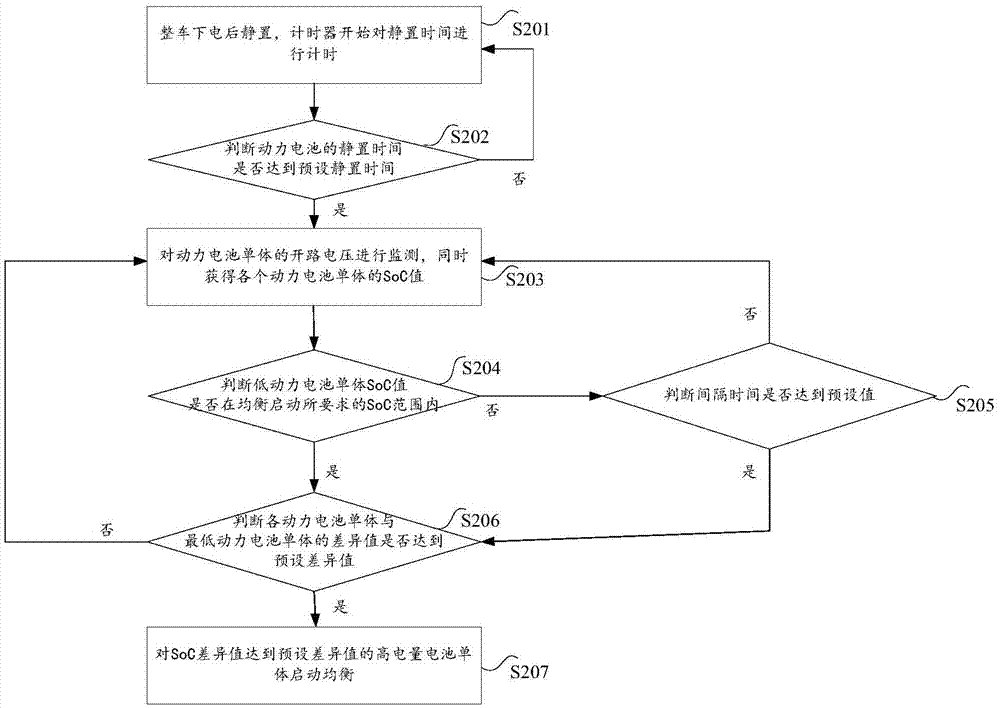

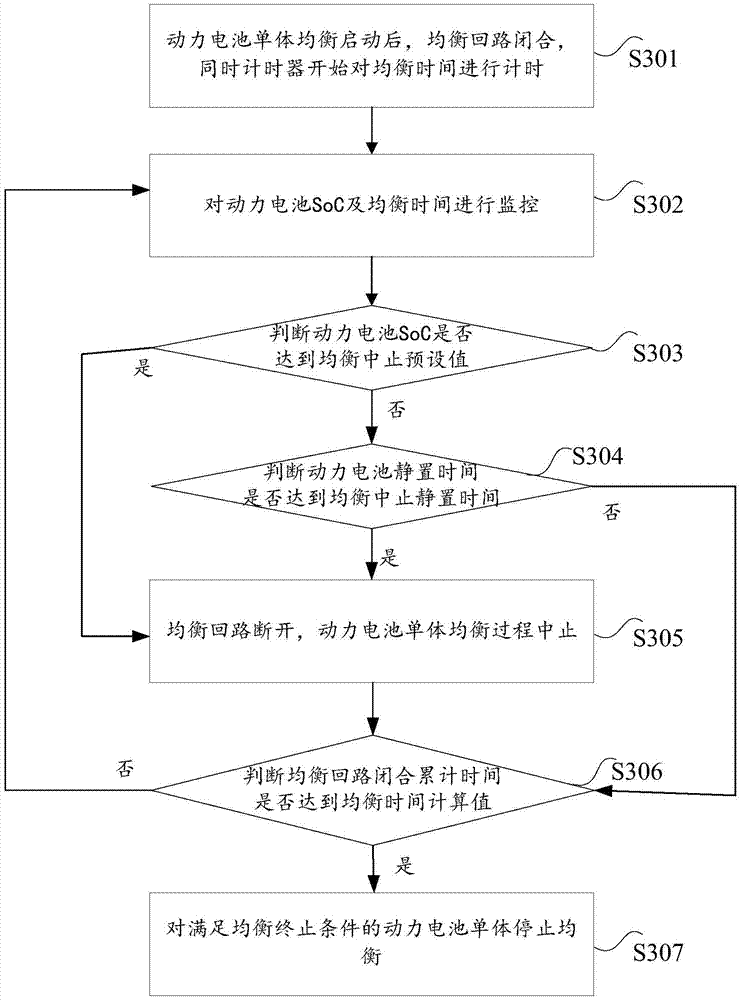

Power battery balance control method, apparatus and circuit

ActiveCN105449295ASolve technical problems with relatively low equilibrium efficiencyImprove balance efficiencyCircuit monitoring/indicationCharge equalisation circuitPower batteryEngineering

The invention discloses a power battery balance control method, apparatus and circuit. The power battery balance control method comprises the steps of detecting a to-be-balanced single power battery satisfying a preset balance start condition, and balancing the to-be-balanced single power battery; judging whether the to-be-balanced single power battery satisfies a balance discontinuation condition or not in the balancing process for the to-be-balanced single power battery; if so, discontinuing the balance on the to-be-balanced single power battery, and continuing to balance the to-be-balanced single power battery when the to-be-balanced single power battery satisfies a balance continuation condition; or otherwise, continuing to balance the to-be-balanced single power battery until the balancing time for the to-be-balanced single power battery satisfies a balancing time calculated value, and stopping the balancing. The technical problem of relatively low balance efficiency of the power battery is solved by the power battery balance control method, apparatus and circuit.

Owner:BEIJING ELECTRIC VEHICLE

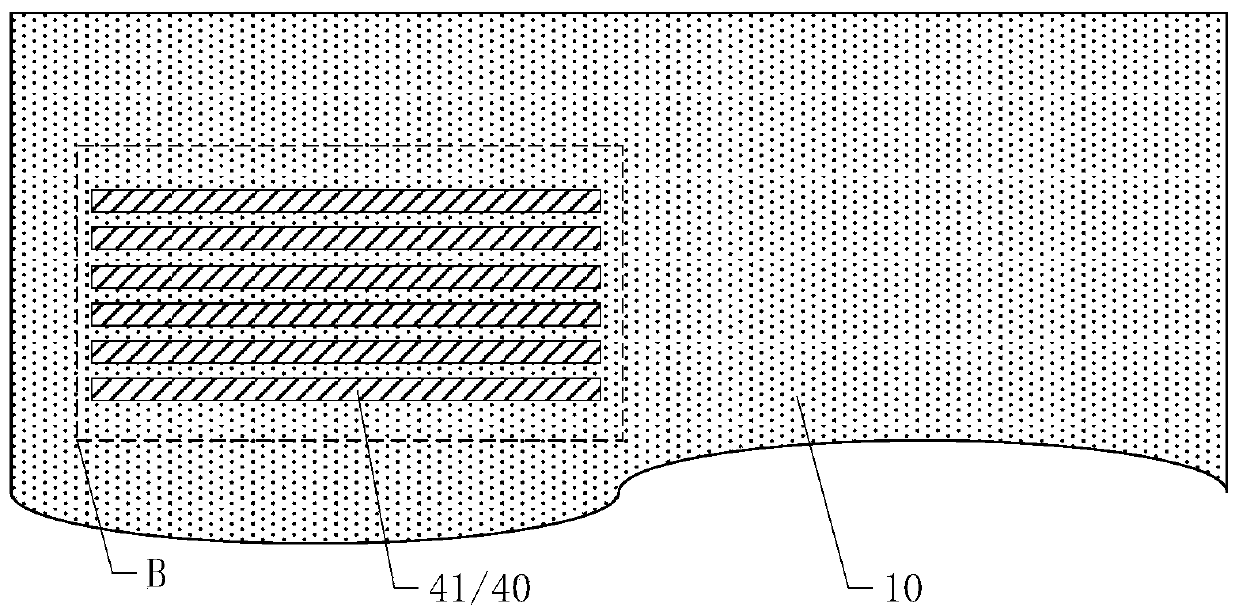

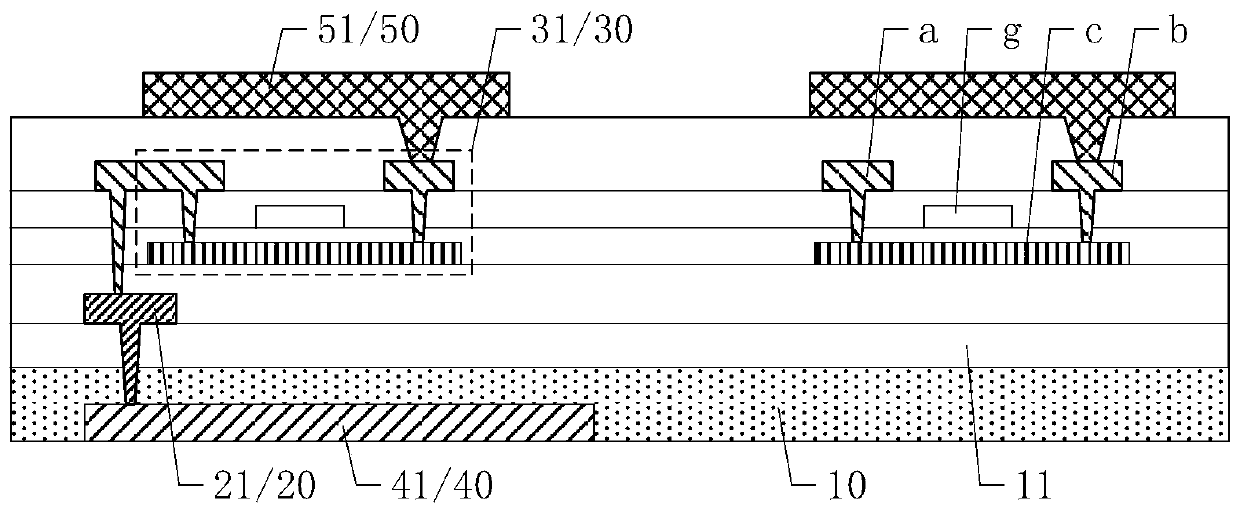

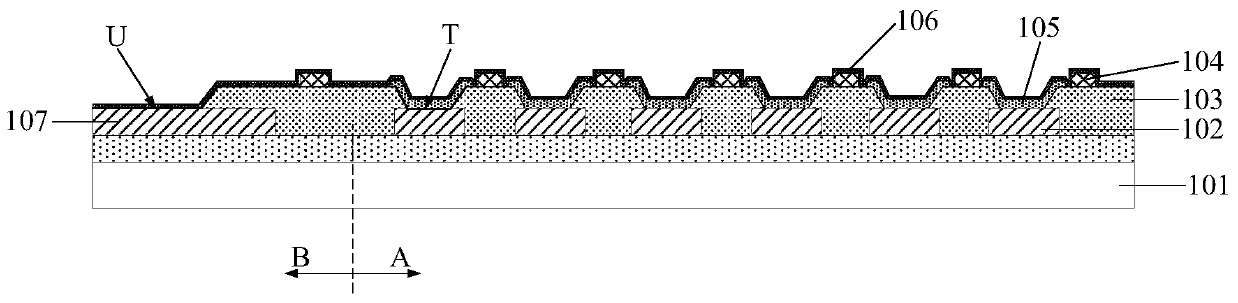

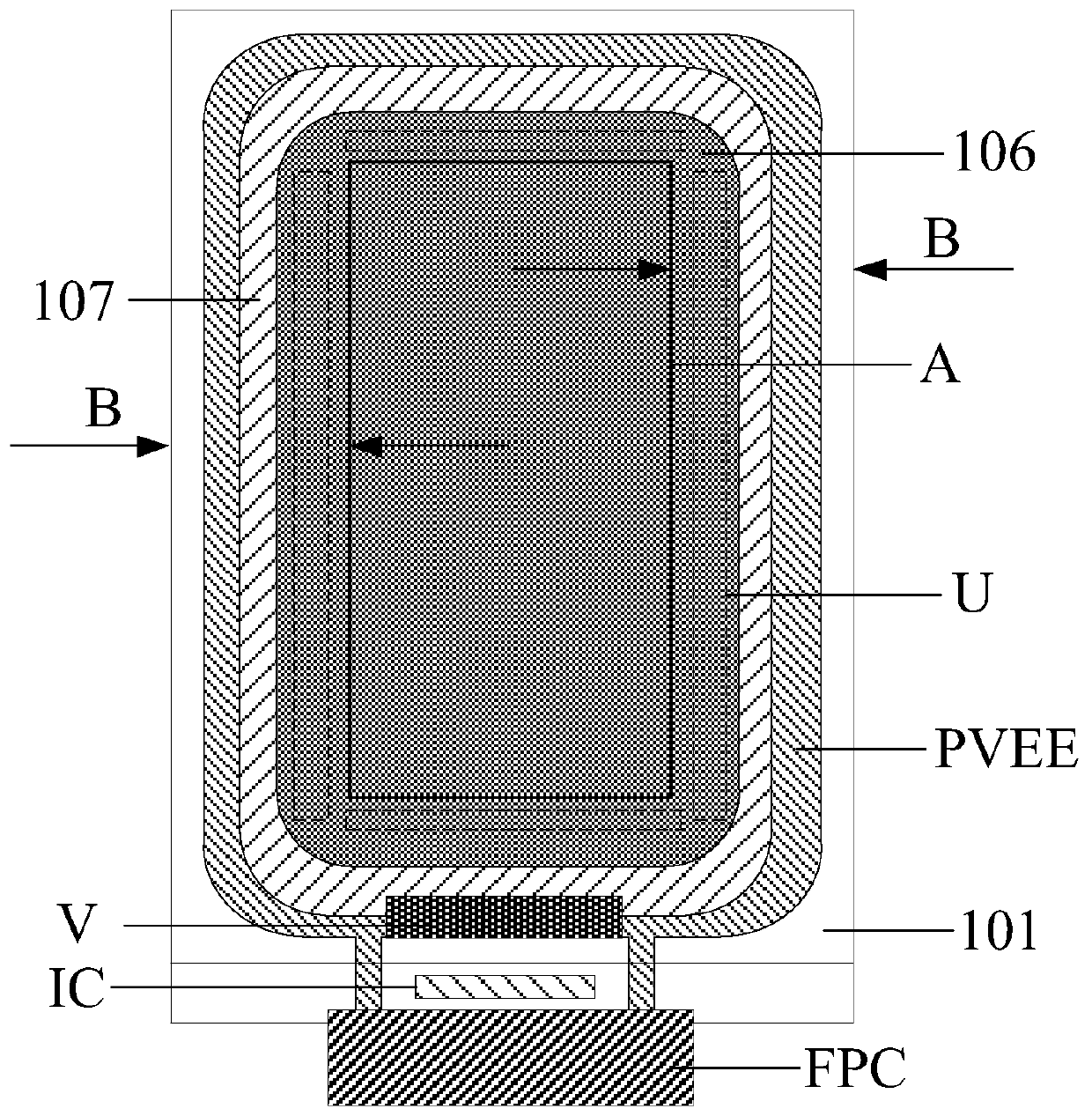

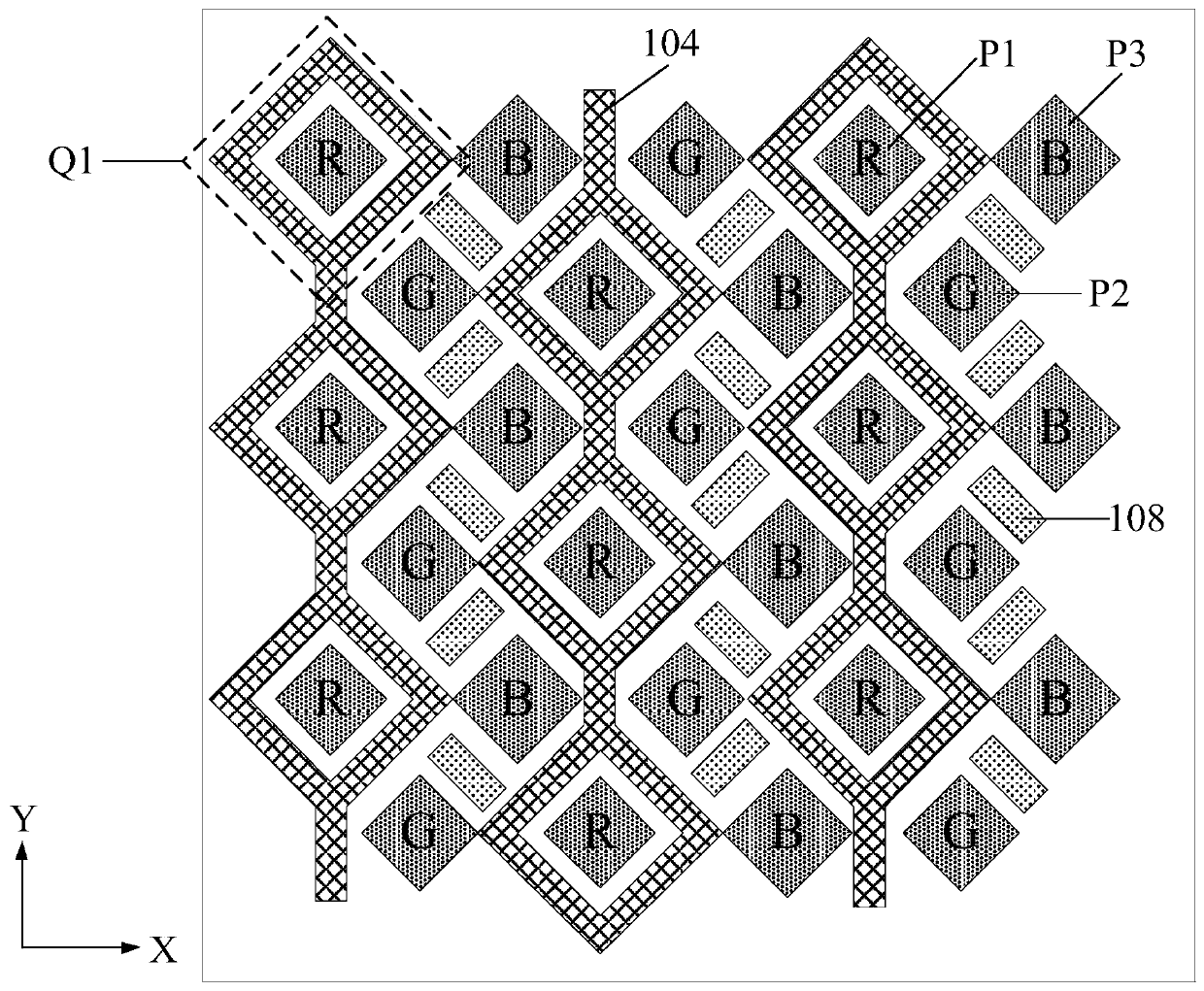

Array substrate and preparation method and display device of array substrate

ActiveCN103474432AReduce widthLower the resistance valueSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOptoelectronics

The invention provides an array substrate and a preparation method and display device of the array substrate, which are used for reducing the voltage difference of common electrode layers among different pixel units, and increasing the pixel aperture ratio. The array substrate comprises a substrate, grid lines arranged on the substrate in an intersecting way, data lines, and pixel units which are formed by the division of the grid lines and the data lines and are in matrix arrangement, wherein thin film transistors, pixel electrodes and common electrode layers are arranged in the pixel units, and the thin film transistors comprise grid electrodes, first insulating layers, source electrodes, drain electrodes and active layers. The array substrate also comprises black matrixes with conductivity, which are arranged in non-display areas of the pixel units and electrically connected with the common electrode layers, and second insulating layers which are used for insulating the black matrixes and the common electrode layers from the thin film transistors, wherein the coverage areas of the second insulating layers are overlapped with the coverage areas of the black matrixes and the common electrode layers.

Owner:HEFEI BOE OPTOELECTRONICS TECH +1

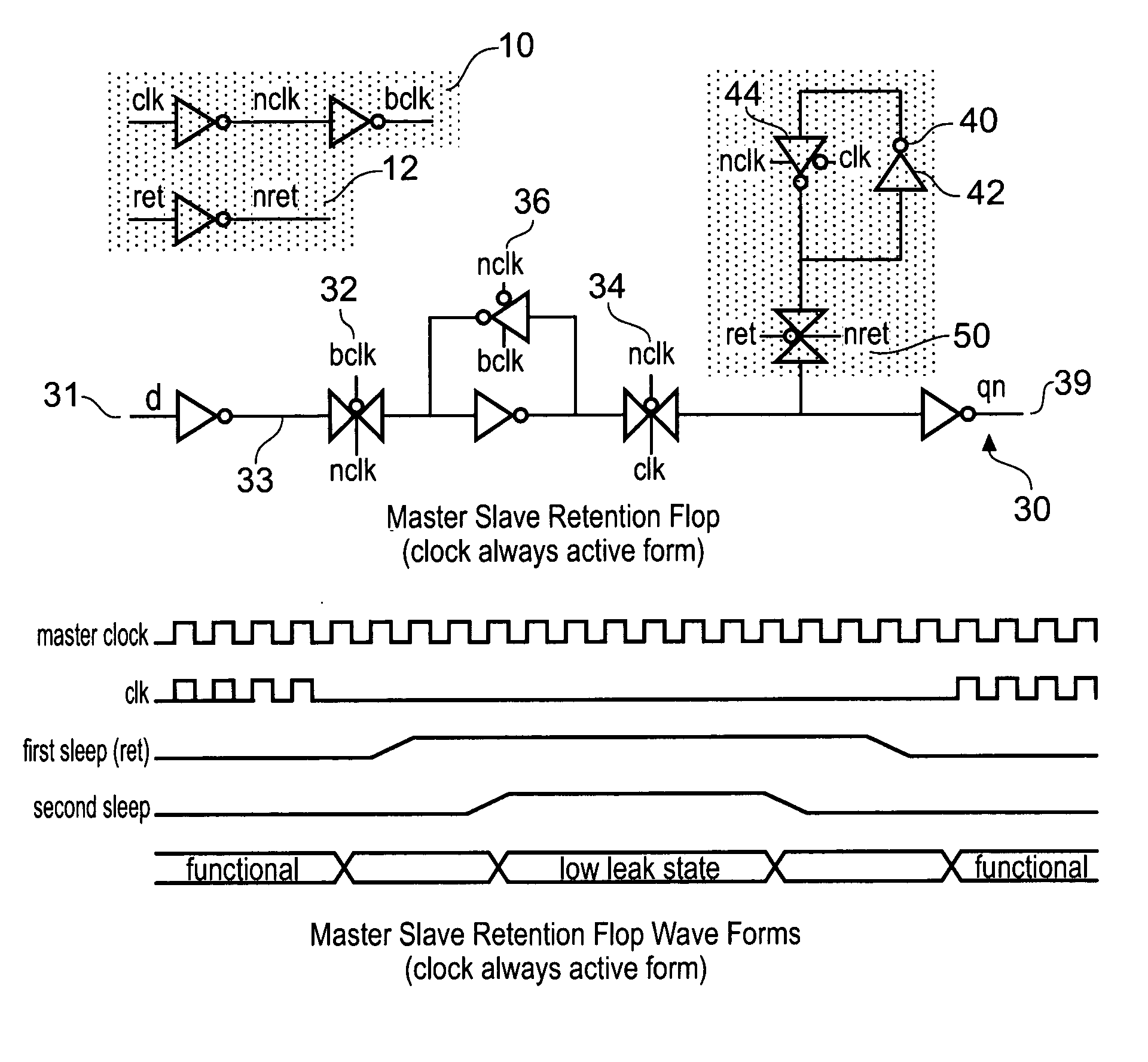

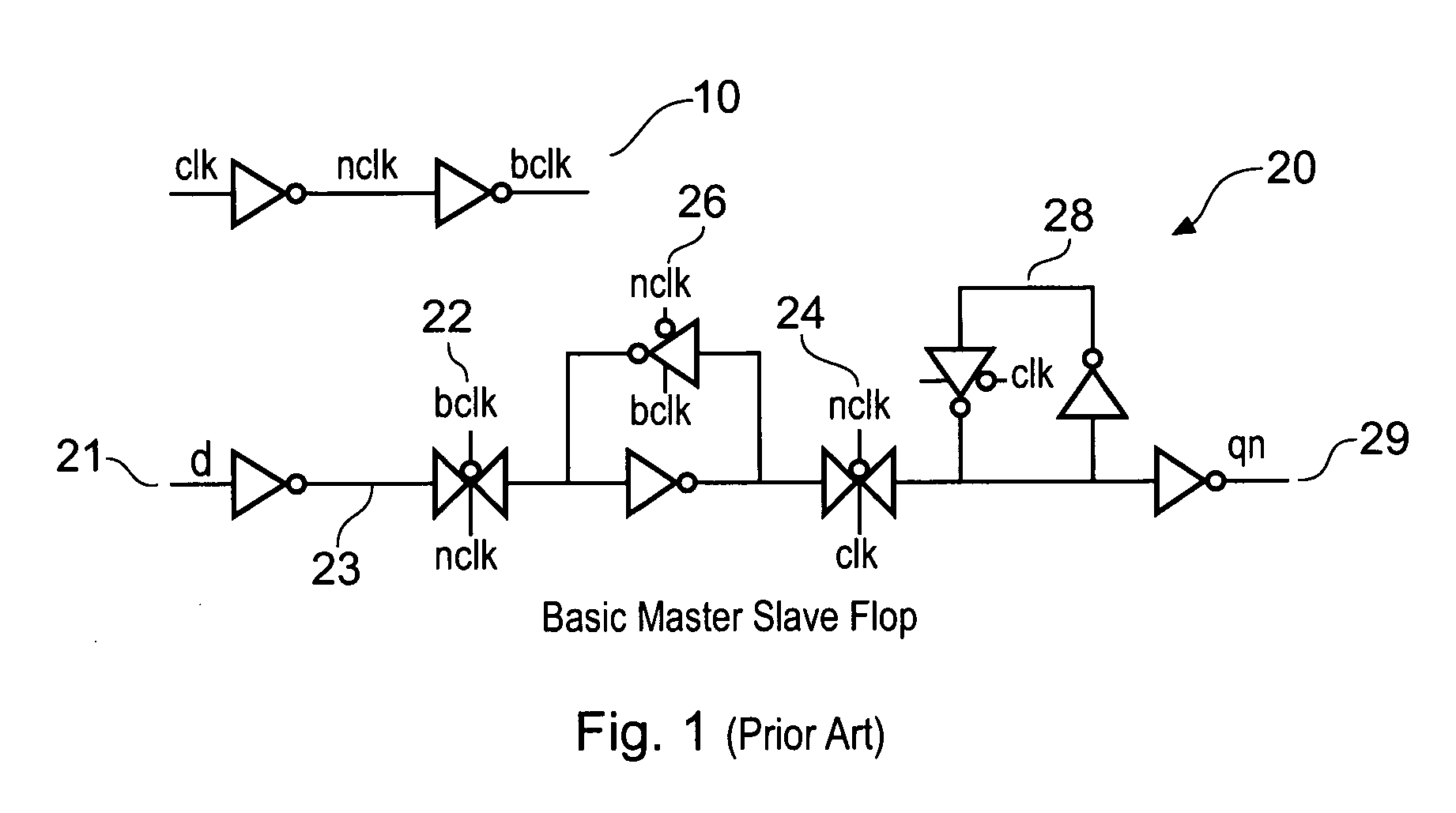

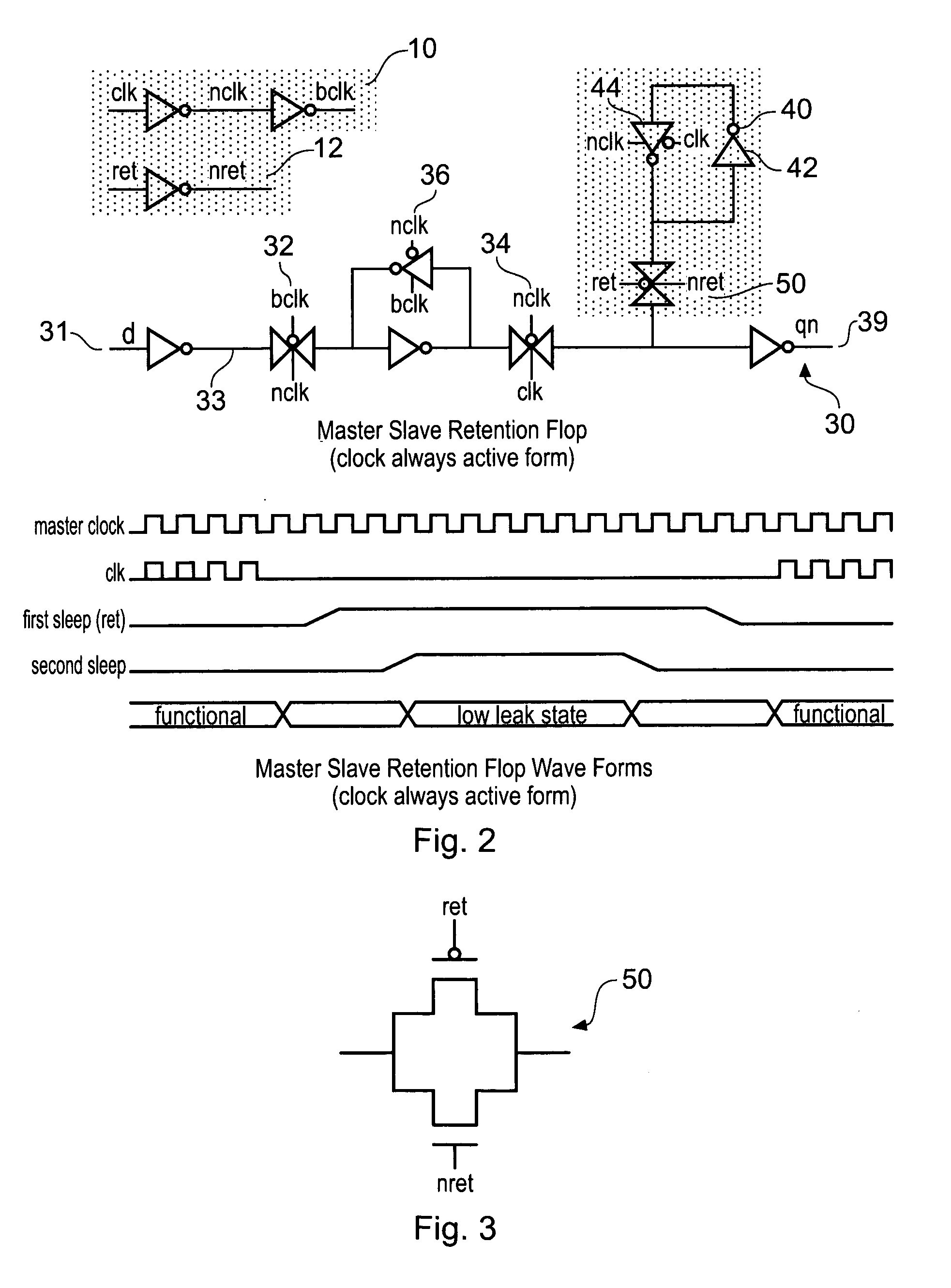

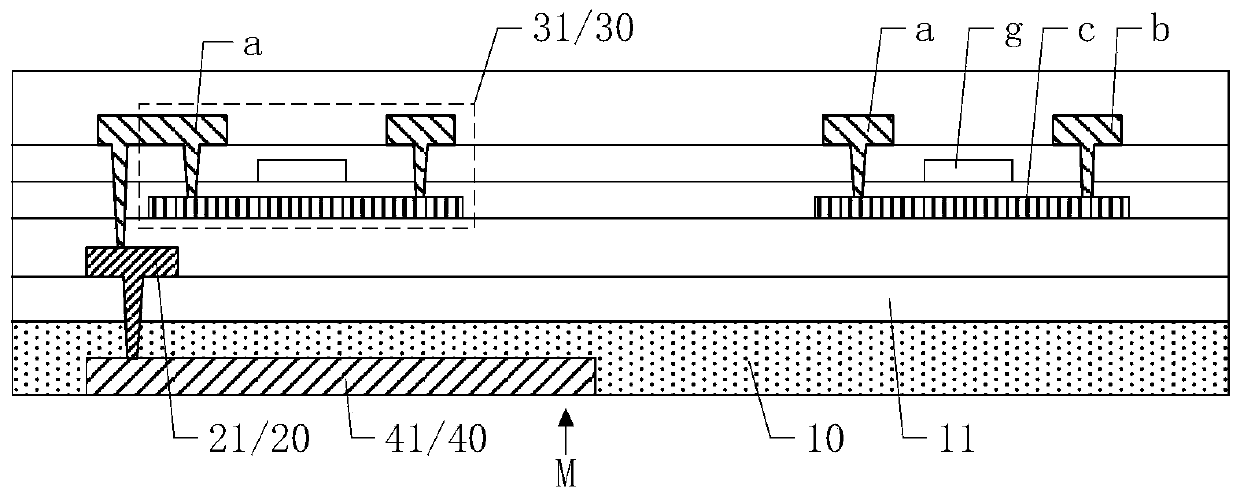

Data retention in operational and sleep modes

InactiveUS20070085585A1Reduce voltage differenceLow static power lossElectric pulse generatorVoltageData input

A circuit is disclosed for retaining a signal value during a sleep mode while a portion of said circuit is powered down comprising: a clock signal input operable to receive a clock signal; at least one latch clocked by said clock signal; a data input, a data output and a forward data path therebetween, wherein a signal value is operable to be received at said data input, is clocked through said at least one latch and passes to said data output along said forward data path; at least one of said at least one latch comprises a retention latch operable to retain a signal value during said sleep mode, said retention latch not being located on said forward data path; and a bidirectional tristateable device, said bidirectional tristateable device being arranged between said forward data path and said retention latch and being operable to selectively isolate said retention latch from said forward data path in response to receipt of a first sleep signal; wherein in response to receipt of a second sleep signal, said second sleep signal being received after said first sleep signal, said circuit is operable to enter said sleep mode such that a voltage difference across said portion of said circuit is reduced such that said portion of said circuit is powered down, and a voltage difference across said retention latch and said bidirectional tristateable device is maintained.

Owner:ARM LTD

Display panel, manufacturing method of display panel and display device

ActiveCN110034150ASmall seam widthImprove uniformitySolid-state devicesPhotovoltaic energy generationDisplay deviceEngineering

The invention discloses a display panel, a manufacturing method of the display panel and a display device. The display panel comprises a first flexible substrate, a metal wiring layer, a thin film transistor layer and a first conductive layer, wherein the metal wiring layer is positioned on one of the sides of the first flexible substrate, and the metal wiring layer comprises at least one first power line; at least one binding area is arranged on the side, far away from the metal wiring layer, of the first flexible substrate; the thin film transistor layer is located on the side, far away fromthe first flexible substrate, of the metal wiring layer, and the thin film transistor layer comprises a plurality of first thin film transistors, wherein the first electrodes of the first thin film transistors are electrically connected with the first power lines; the first conductive layer comprises a plurality of conductive portions, wherein the plurality of conductive portions are located in the binding area; and the first power line is electrically connected with at least one conductive portion. Compared with the prior art, when a plurality of display panels are spliced, the width of a splicing seam between two adjacent display panels can be relatively small, so that the continuity of image display is ensured, and the visual effect is improved.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

Closed loop control method comprising multi-microgrid power distribution network

ActiveCN103746374AFully play the regulatory roleIncrease success rateAc network circuit arrangementsMicrogridLoop closing

The invention discloses a closed loop control method comprising a multi-microgrid power distribution network. A micorgrid is subjected to equivalence processing to establish a power distribution network closed loop optimization control model which takes the microgrid into the account; active and reactive output of the microgrid is used as a control variable; the minimum voltage difference of two sides of a switching-on point is used as a control target; a constraint condition comprises power balance constraint, node voltage upper and lower limit constraint, the limiting value of the active and reactive output of the microgrid and the maximum allowing tide constraint of a line; the genetic algorithm of a belt sparse block migration strategy is combined to carry out optimization regulation on the operation state of each microgrid; and the voltage difference of two sides of a closed loop point can be effectively reduced so as to reduce closed loop current and improve the success rate of the loop closing operation. The closed loop control method has the advantage of comprehensive model, the microgrid controllability can be fully utilized, and the theoretical basis can be provided for the thermal conductivity loop closing operation after the microgrid is accessed into the power distribution network.

Owner:STATE GRID CORP OF CHINA +1

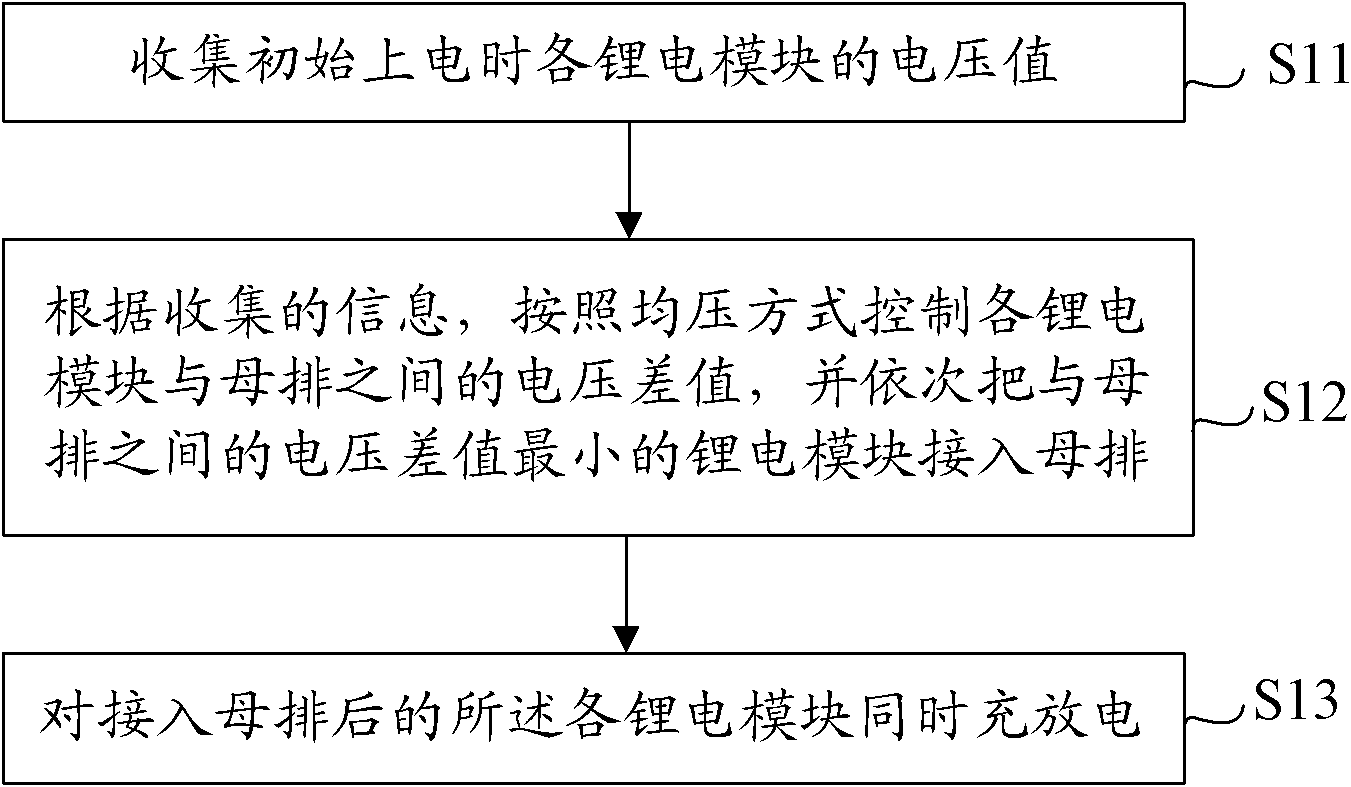

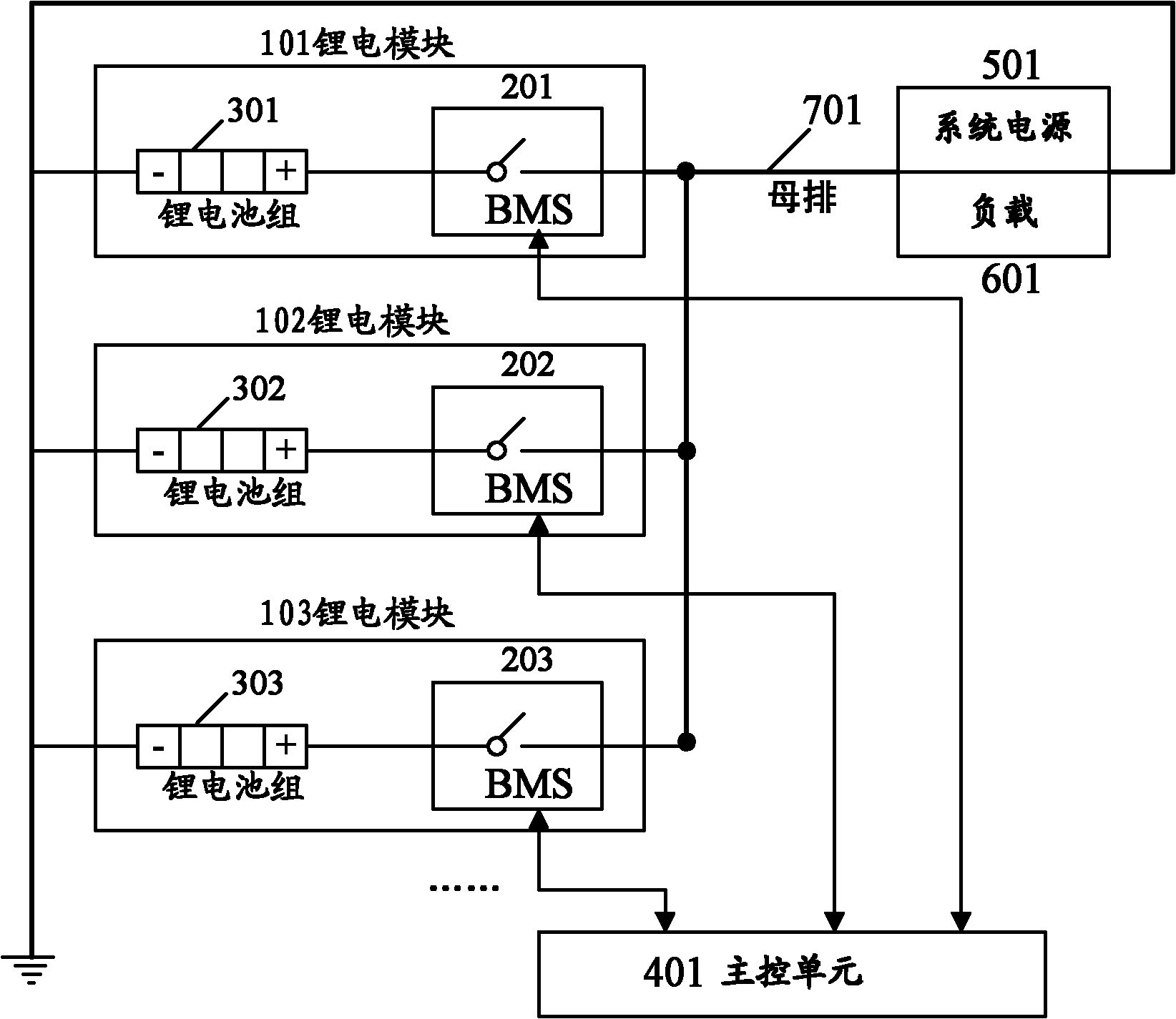

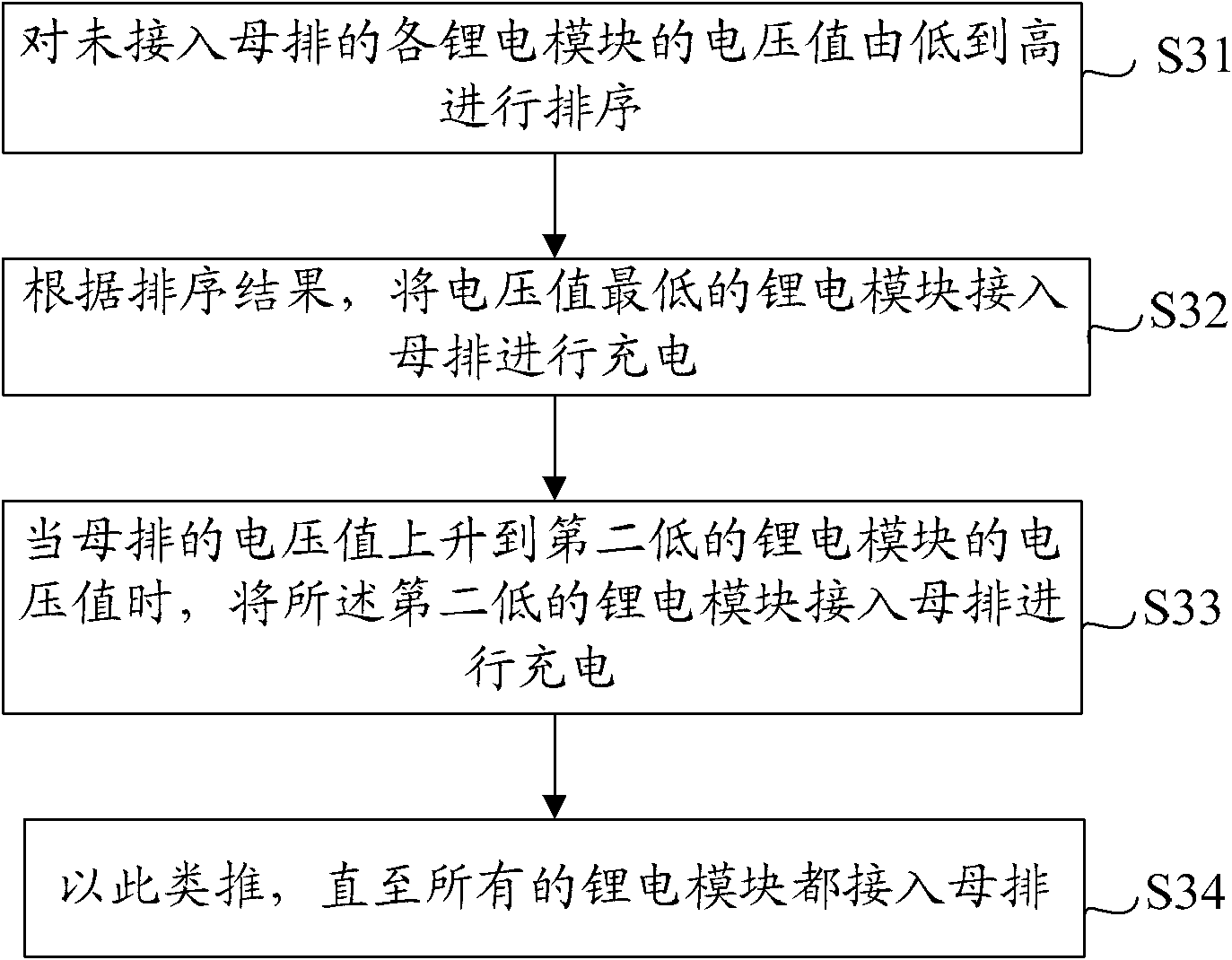

Method and system for parallel use of lithium battery modules

ActiveCN102082307AImprove securityReduce voltage differenceSecondary cells charging/dischargingElectricityPower flow

The embodiment of the invention provides a method and system for parallel use of lithium battery modules. The method comprises the following steps: collecting a voltage value of each lithium battery module at the time of initial power-on; and controlling a voltage D-value between each lithium battery module and a busbar based on a voltage-sharing mode in accordance with the collected information,connecting the lithium battery modules to the busbar in sequence, wherein the lithium battery modules have minimum voltage D-values between the lithium battery modules and the busbar, and simultaneously charging and discharging the lithium battery modules which are connected to the busbar. According to the invention, the lithium battery modules can be connected in parallel after the voltage D-values of the lithium battery modules are kept within a range, thus reducing voltage difference among the lithium battery modules and avoiding large current impact among the lithium battery modules, thereby reducing damages to a battery management system (BMS) circuit and improving the safety of the parallel use of the lithium battery modules.

Owner:HUAWEI TECH CO LTD

Power cell monitoring

ActiveUS7760106B2Reduce voltage differenceConvenient ArrangementCircuit monitoring/indicationCharge equalisation circuitElectrical batteryDevice Monitor

Owner:AMI SEMICON BELGIUM

Display panel, manufacturing method of display panel and display device

ActiveCN110752243AReduce in-plane resistanceImprove display uniformitySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceElectrical connection

The invention discloses a display panel, a manufacturing method of the display panel and a display device. The display panel comprises an underlayer substrate, a plurality of first electrodes, a pixeldefining layer, a connecting metal layer, an organic light-emitting function layer and a second electrode, wherein the pixel defining layer and the first electrodes are located on the same side of the underlayer substrate, and the pixel defining layer comprises a plurality of openings for exposing the first electrodes respectively; the connecting metal layer is located on the side, which deviatesfrom the underlayer substrate, of the pixel defining layer, and the orthographic projection of a pattern of the connecting metal layer on the underlayer substrate at least half surrounds the openings; the second electrode is located on the sides, which deviate from the underlayer substrate, of the organic light-emitting function layer and the pixel defining layer, and the orthographic projectionof the second electrode on the underlayer substrate covers the orthographic projection of the pixel defining layer and the orthographic projection of the first electrodes on the underlayer substrate;and the second electrode is electrically connected with the connecting metal layer. Due to the fact that the connecting metal layer is connected with the second electrode in parallel, the in-plane resistance of the second electrode is reduced, the voltage drop in the display area is reduced, the voltage distribution in the display area is more uniform, and the display uniformity of the display panel is improved.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

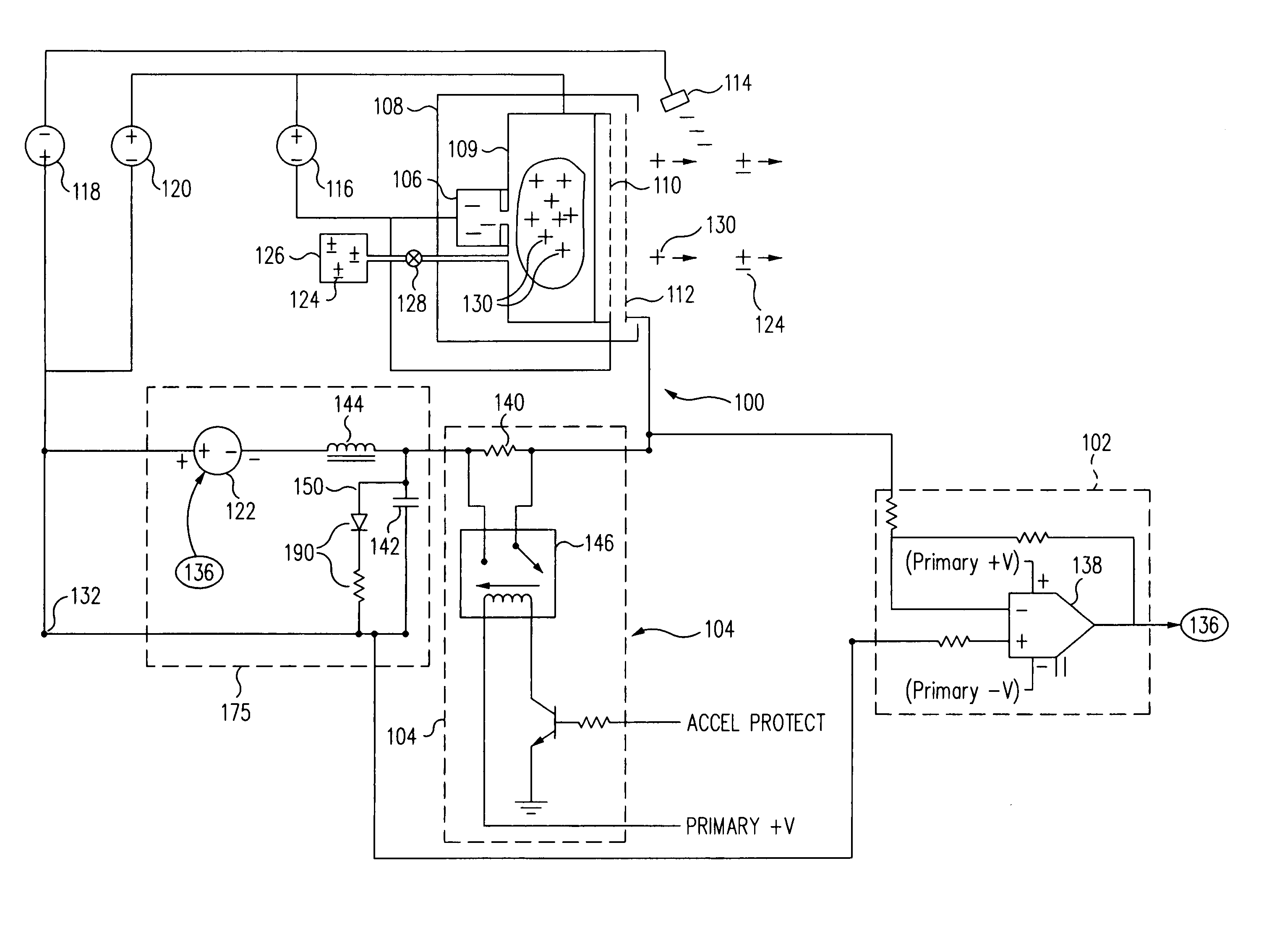

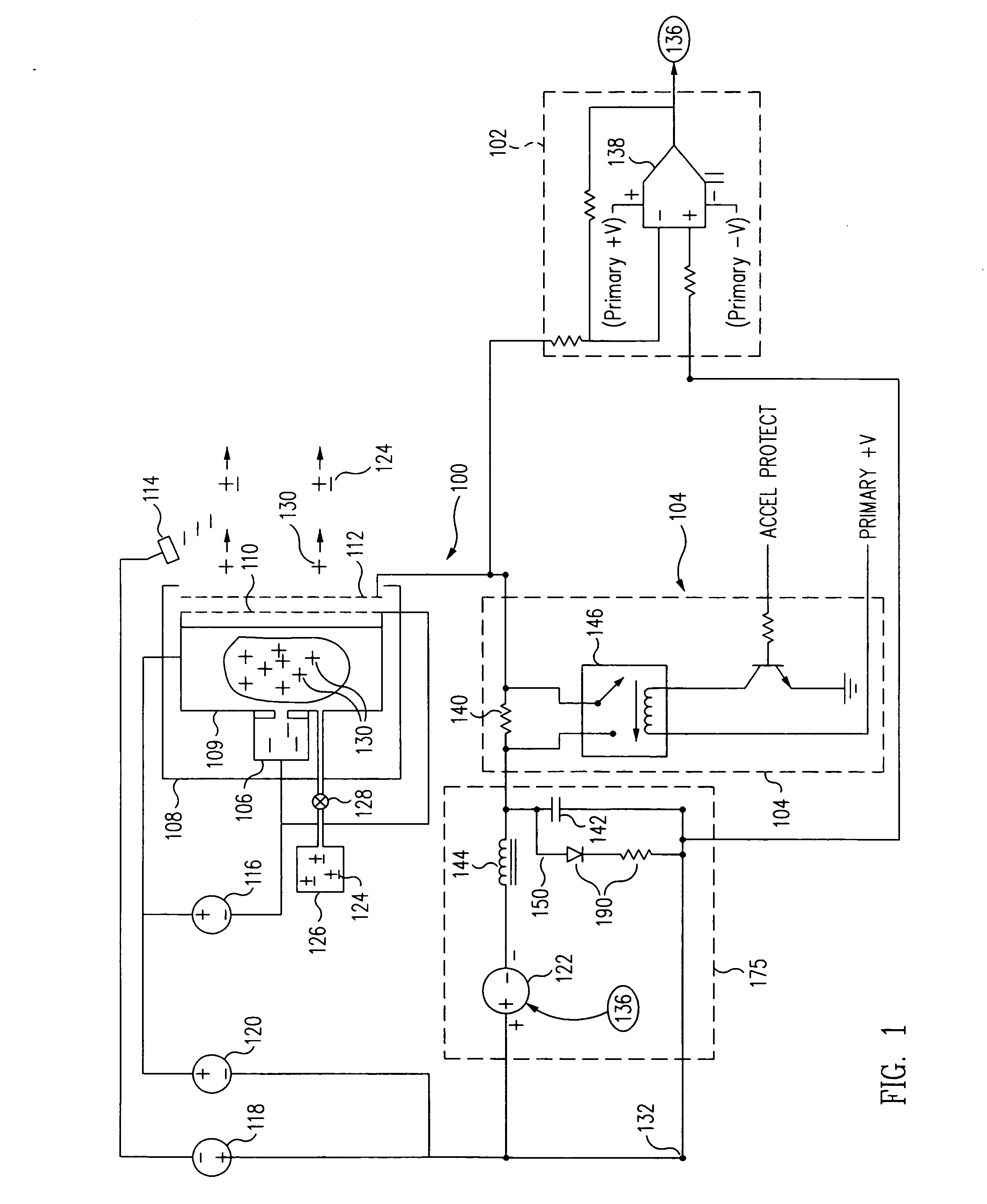

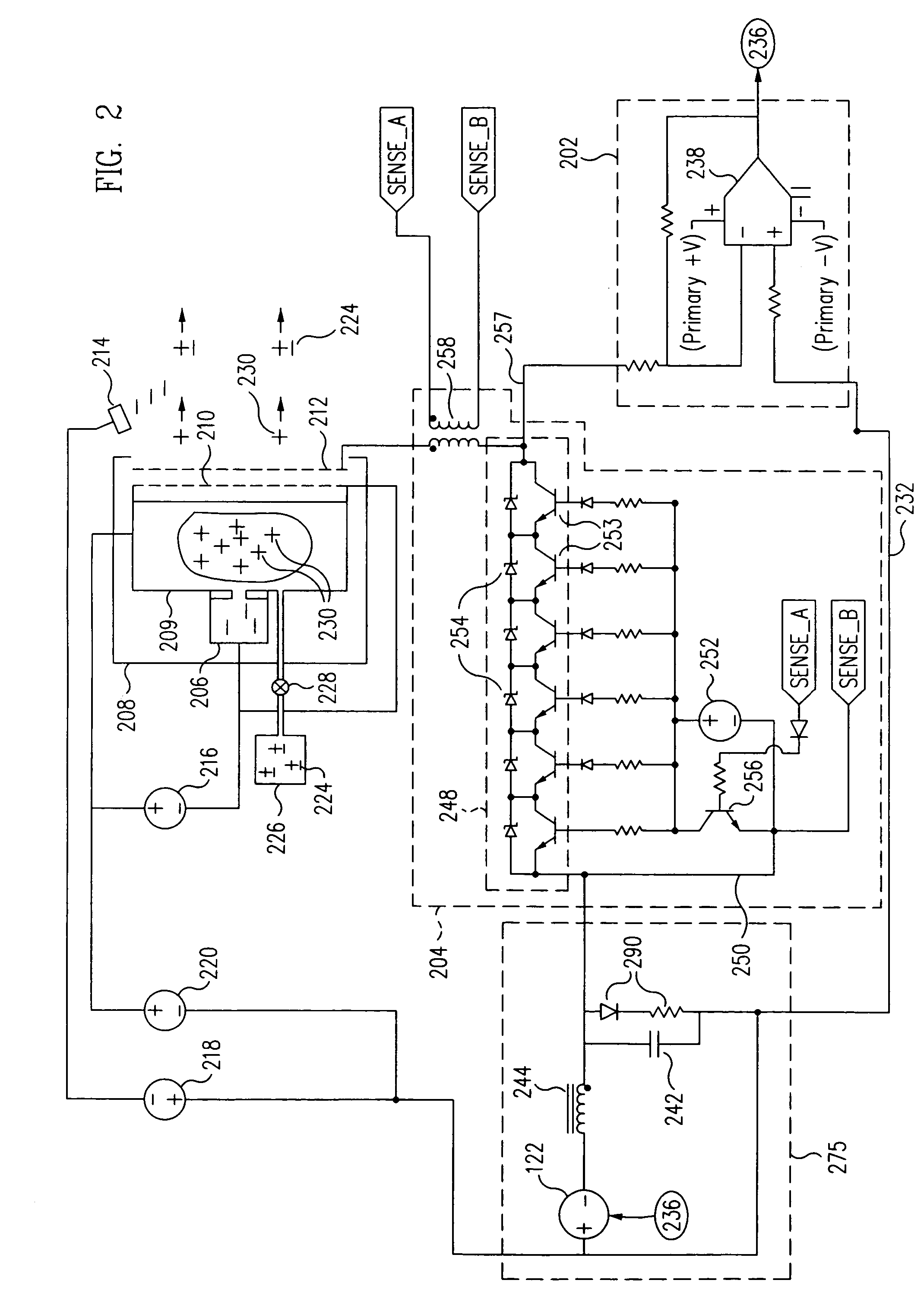

Ion engine grid arcing protection circuit

InactiveUS20060075739A1Reduce harmMinimizing energyCosmonautic vehiclesCosmonautic propulsion system apparatusIonGate current

An arcing protection circuit for the screen and accelerator grids of an ion thruster engine includes an impedance, which in one embodiment, is fixed, and in another, is variable, coupled in series between the accelerator grid of the engine and a current return path of the grid in such a way that an increase in accelerator grid current resulting from a plasma arc occurring between the screen grid and the accelerator grid is converted by the impedance into a rapid reduction in the voltage difference between the screen and accelerator grids, thereby extinguishing the arc. The arcing protection circuit also includes a monitoring circuit coupled to the accelerator grid that senses an increase in the voltage on the accelerator grid resulting from the plasma arc, and in response thereto, causes the accelerator grid power supply to reduce the voltage on the accelerator grid.

Owner:L 3 COMM ELECTRON TECH

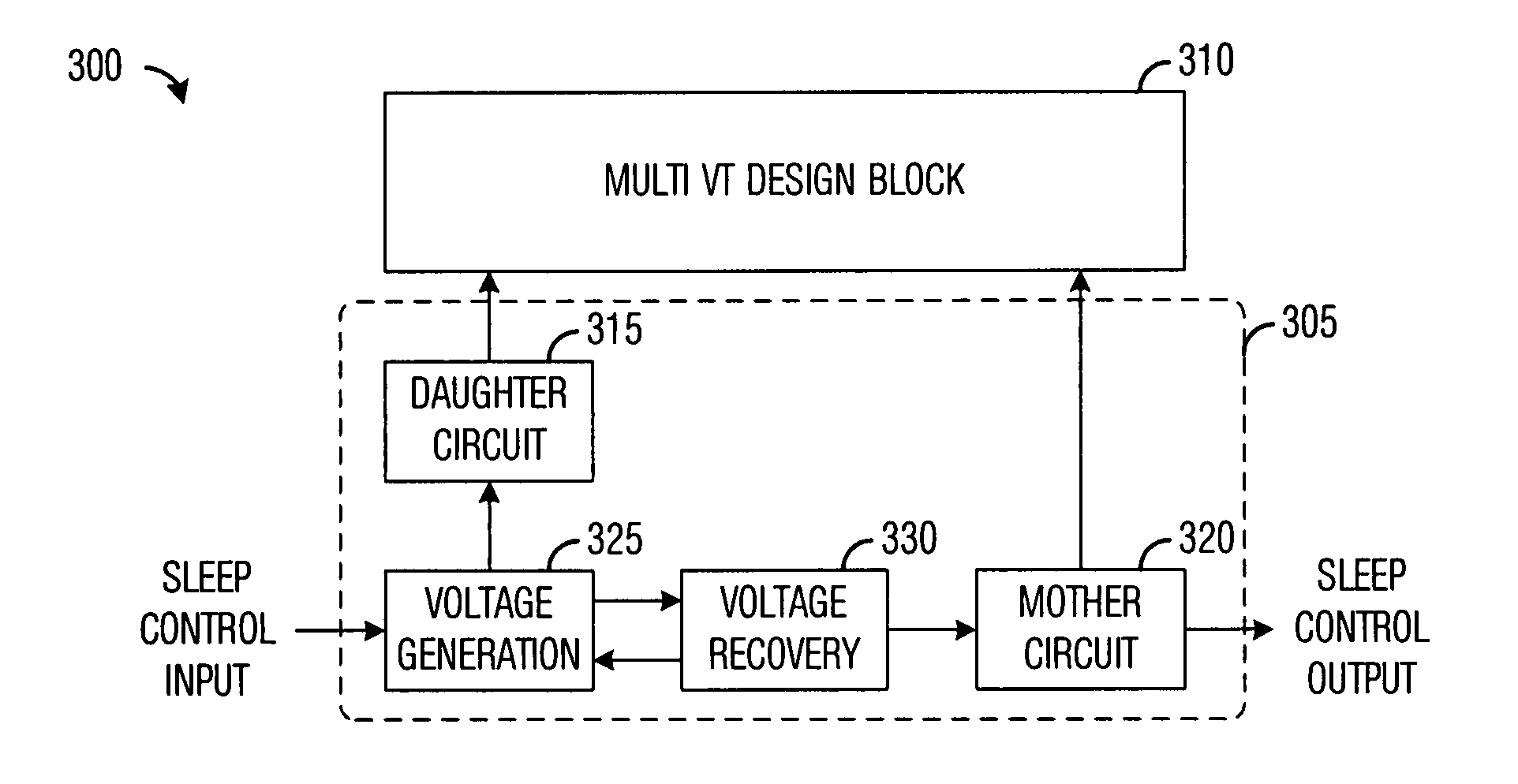

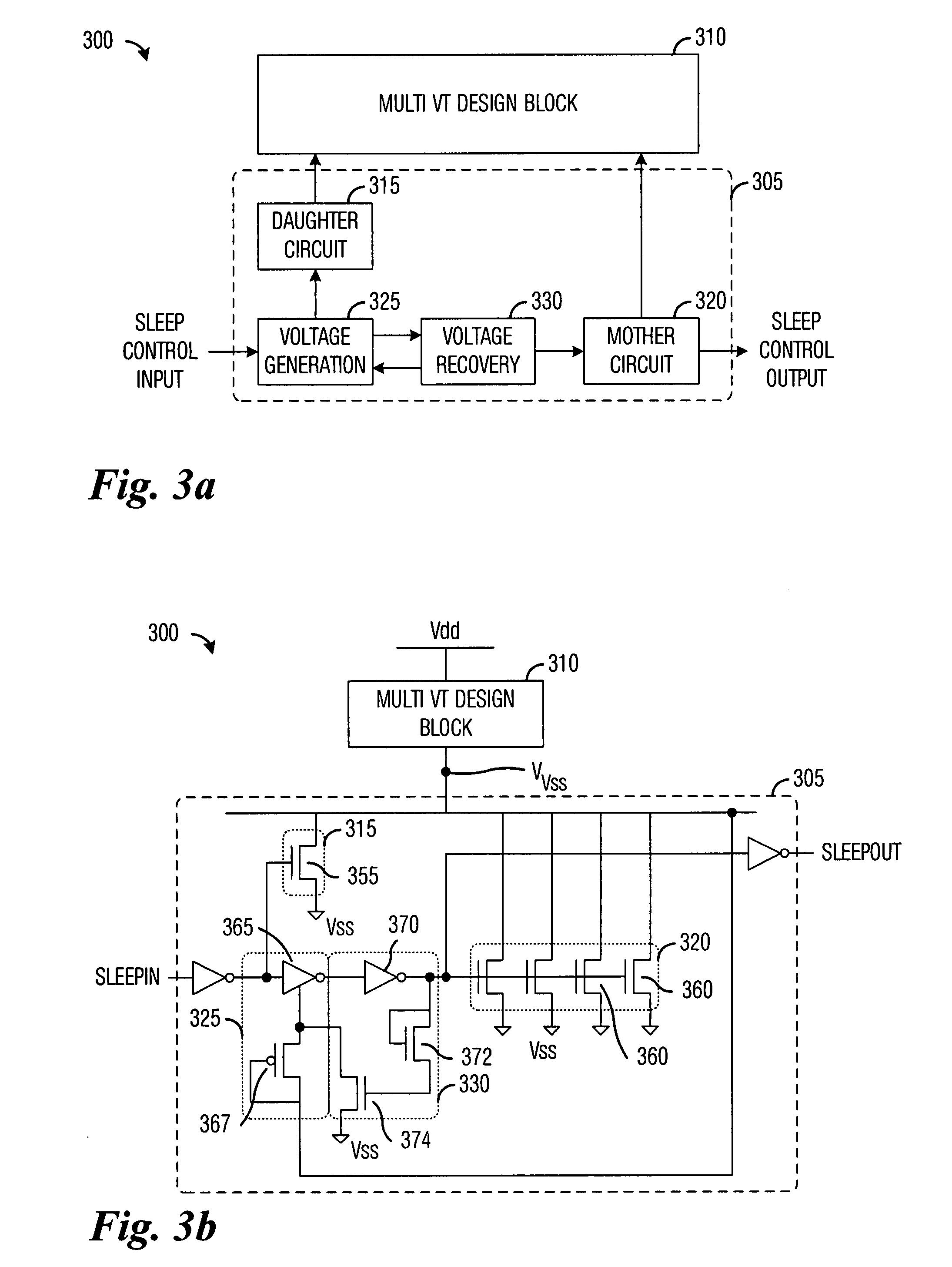

Mother/daughter switch design with self power-up control

InactiveUS20080270813A1Good power-on response timeReduced power-on transient glitchHardware monitoringPower supply for data processingElectricityControl system

System and method for providing power to integrated circuitry with good power-on responsive time and reduced power-on transient glitches. A preferred embodiment comprises a daughter switch coupled to a circuit block, a first control circuit coupled to the daughter circuit, a second control circuit coupled to the first control circuit, and a mother circuit coupled to the circuit block and to the second control circuit. After the daughter switch is turned on by a control signal, the mother switch is not turned on until the daughter switch has discharged (charged) the voltage potential across power rails of the mother circuit to a point where glitches are minimized. The second control circuit turns on the mother circuit when the reduced voltage potential is reached, with a signal produced by the first control circuit reflects the voltage potential. Furthermore, a bypass circuit can be used to reduce leakage current.

Owner:TAIWAN SEMICON MFG CO LTD

Battery control apparatus and energy storage system including same

ActiveUS20200244075A1Reduce voltage differenceReduce unnecessary energy consumptionCircuit monitoring/indicationCharge equalisation circuitElectrical batteryThreshold voltage

Provided is a battery control apparatus, a battery control method and an energy storage system including the battery control apparatus. The battery control apparatus according to an embodiment of the present disclosure includes a first battery pack, a second battery pack, a first switch connected in series to the first battery pack between the first terminal and the second terminal, a second switch connected in series to the second battery pack between the first terminal and the second terminal, and a control unit. The control unit is configured to turn on both the first switch and the second switch when a voltage difference between the first battery pack and the second battery pack at a time point at which both the first switch and the second switch are turned off is less than a threshold voltage.

Owner:LG ENERGY SOLUTION LTD

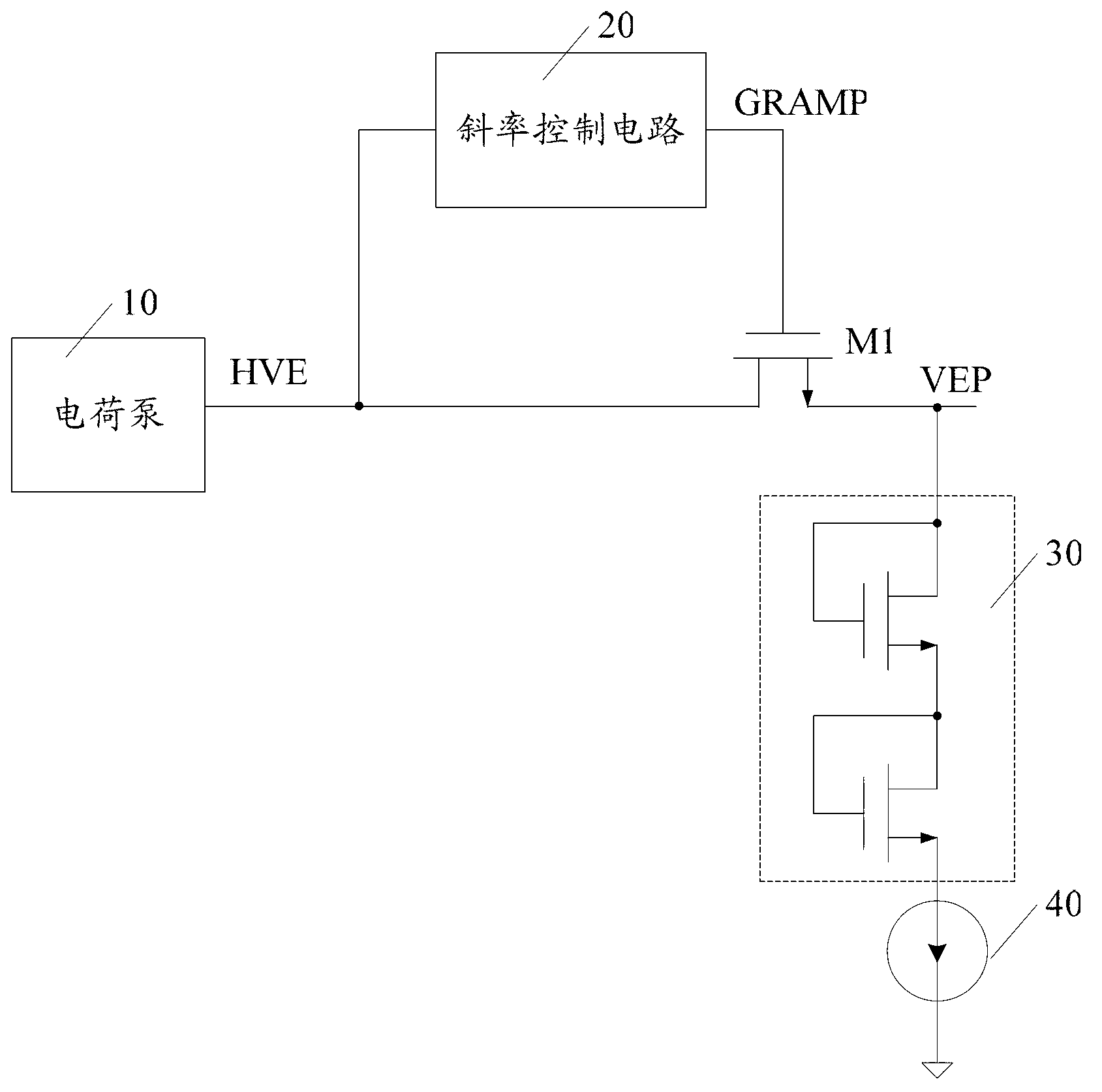

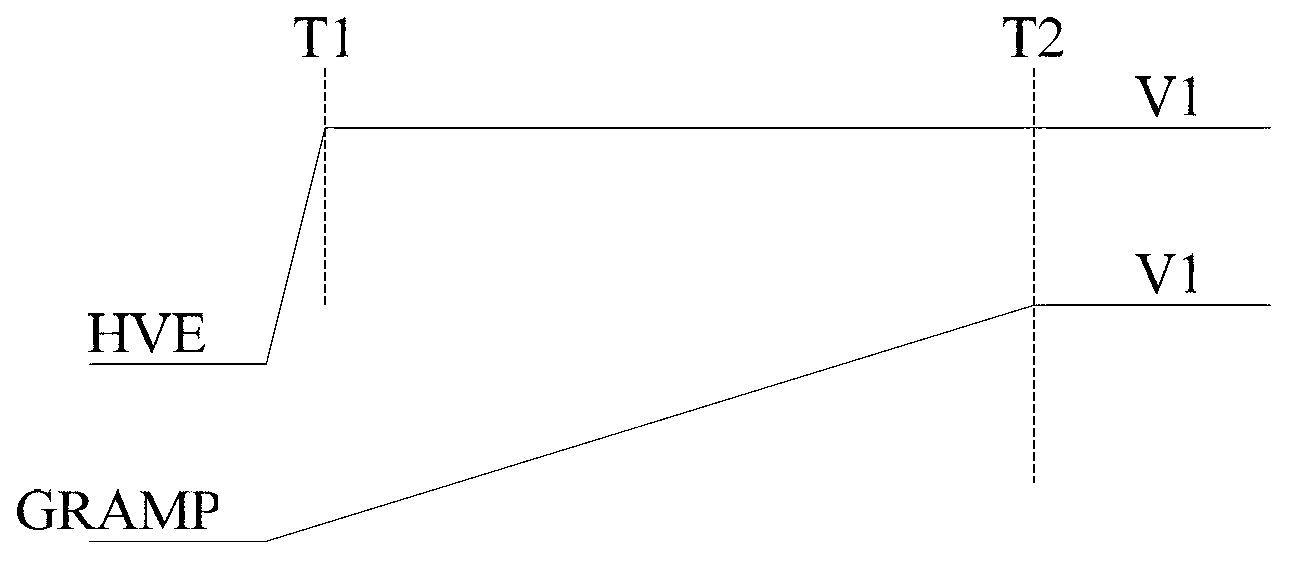

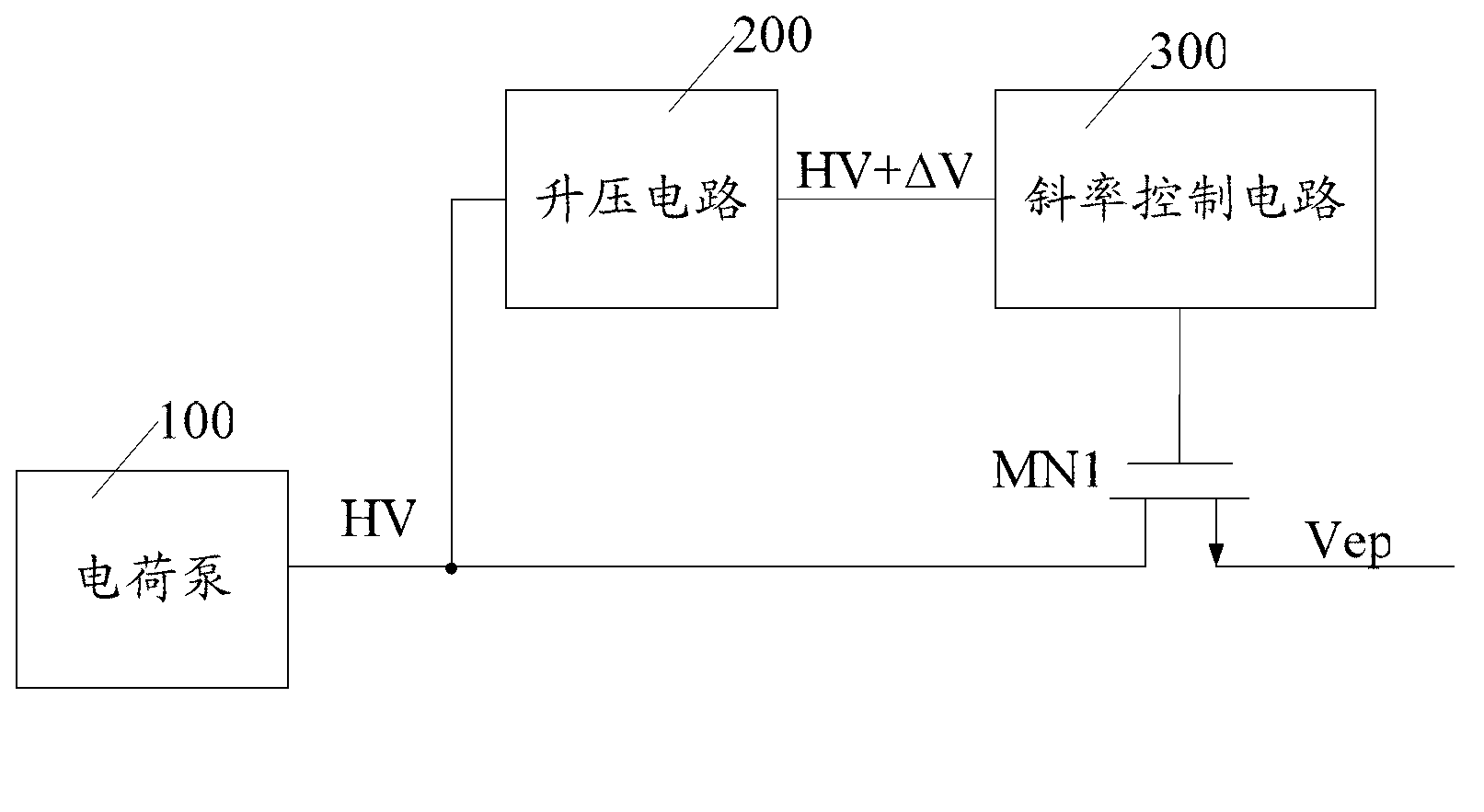

Charge pump output voltage regulating circuit and storage device

ActiveCN103236789AStable output voltageImprove accuracyRead-only memoriesApparatus without intermediate ac conversionEngineeringVoltage variation

The invention discloses a charge pump output voltage regulating circuit and a storage device. The circuit comprises a booster circuit, a slope control circuit and an output transistor, wherein the input end of the booster circuit is connected with the output end of a charge pump, the booster circuit is suitable for boosting the output voltage of the charge pump to a first voltage, and the voltage difference between the first voltage and the output voltage of the charge pump is more than the threshold voltage of the output transistor; the input end of the slope control circuit is connected with the output end of the booster circuit, the output end of the slope control circuit is connected with the grid of the output transistor, the output voltage of the slope control circuit varies along with the input voltage of the slope control circuit to the first voltage, and the voltage change rate of the output voltage of the slope control circuit is less than the voltage change rate of the input voltage of the slope control circuit; and the drain electrode and the source electrode of the output transistor are respectively connected with the output end of the charge pump and the output end of the regulating circuit. The output voltage of the regulating circuit is stable, so that the misoperation of a subsequent storage unit in an erasing process is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

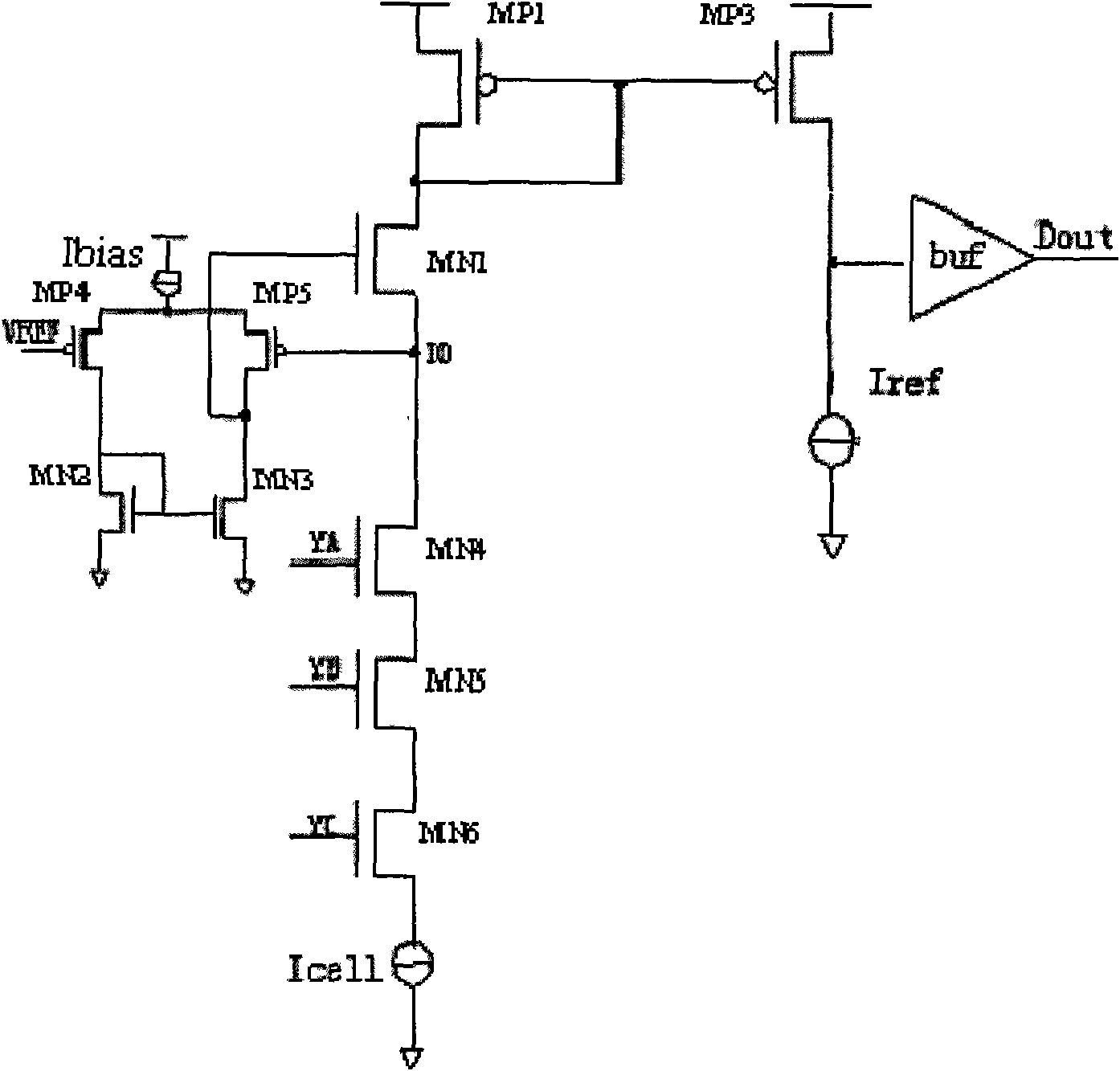

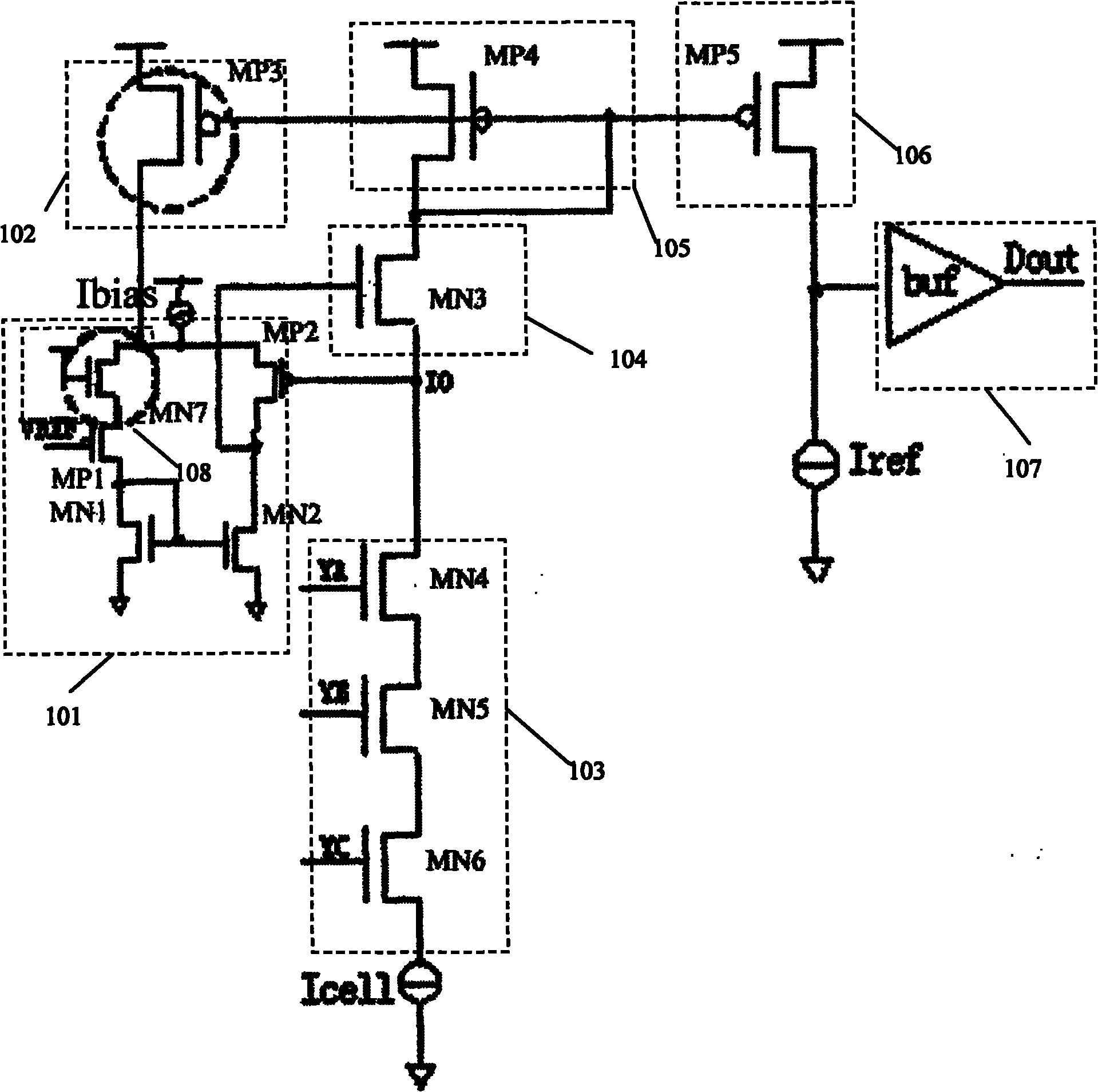

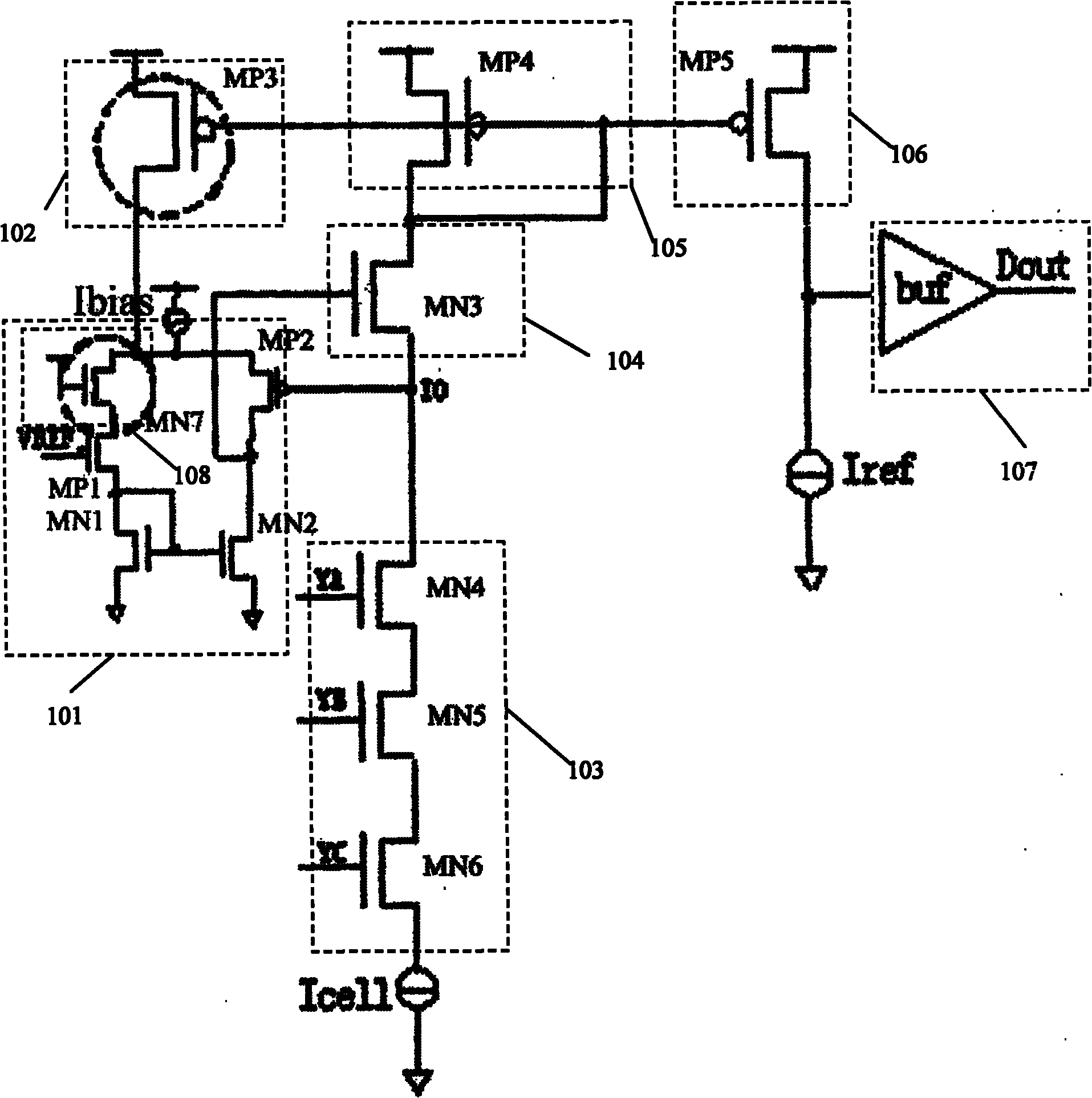

Readout amplifier with process and current compensation

ActiveCN101777374AImprove performanceImprove access speedDigital storageBit lineAudio power amplifier

The invention discloses a readout amplifier with process and current compensation. By additionally arranging an imag mirroring circuit for mirroringimaging current signals formed by an access memory cell at the source electrode of a second differential amplifying tube and the grid electrode of a current transferring circuit of a memory cell, and additionally arranging a seventh NMOS (N-channel metal oxide semiconductor) tube between the source electrode of a first differential amplifying tube and the source electrode of the second differential amplifying tube, when the current signals of the memory cell are larger, the grid source voltage of a third NMOS tube is increased, and when the current signals of the memory cell are smaller, the grid source voltage of the third NMOS tube is reduced, thereby achieving the purpose of reducing the voltage difference of bit lines and improving the performance of the readout amplifier and the access speed of the memory.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

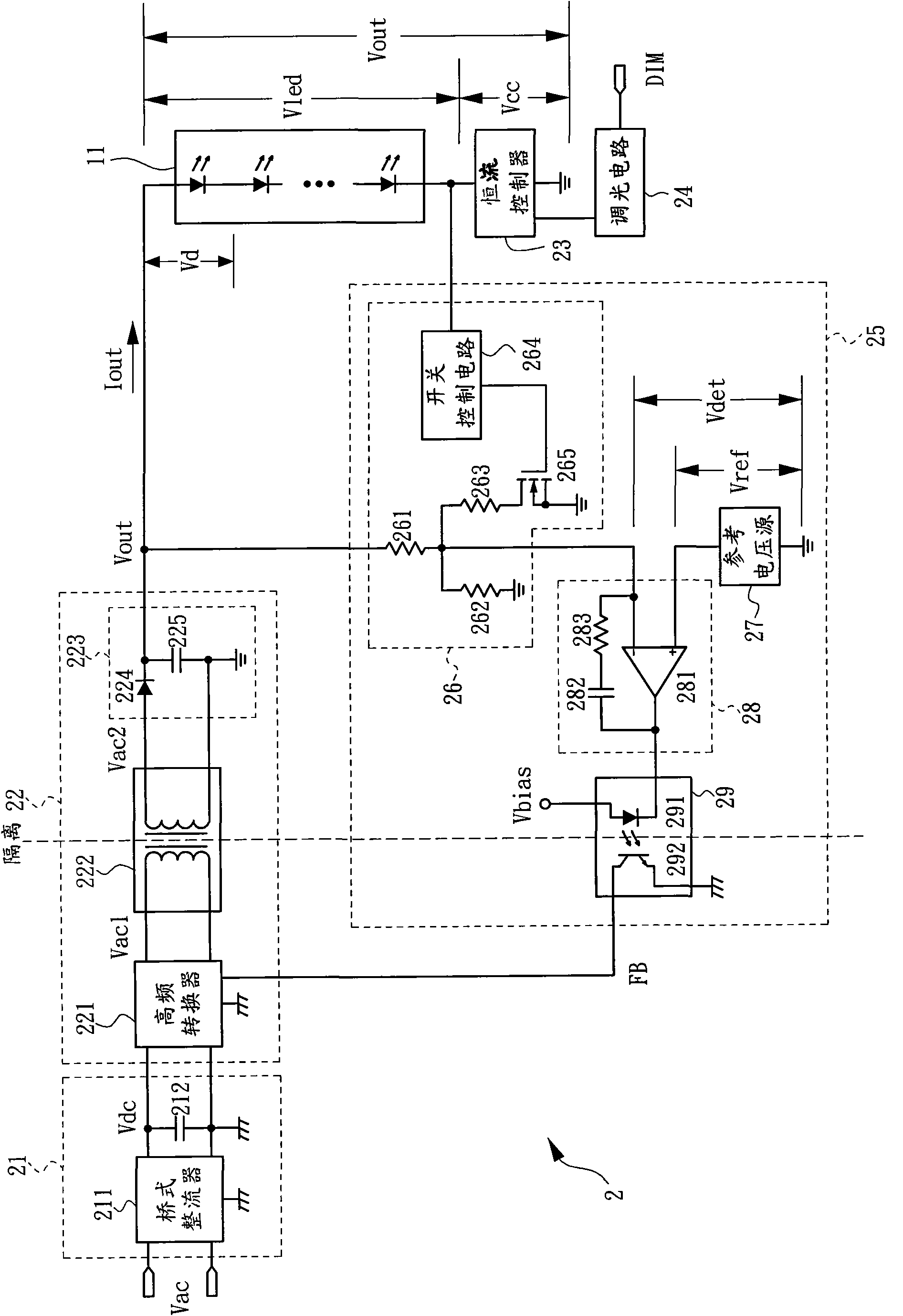

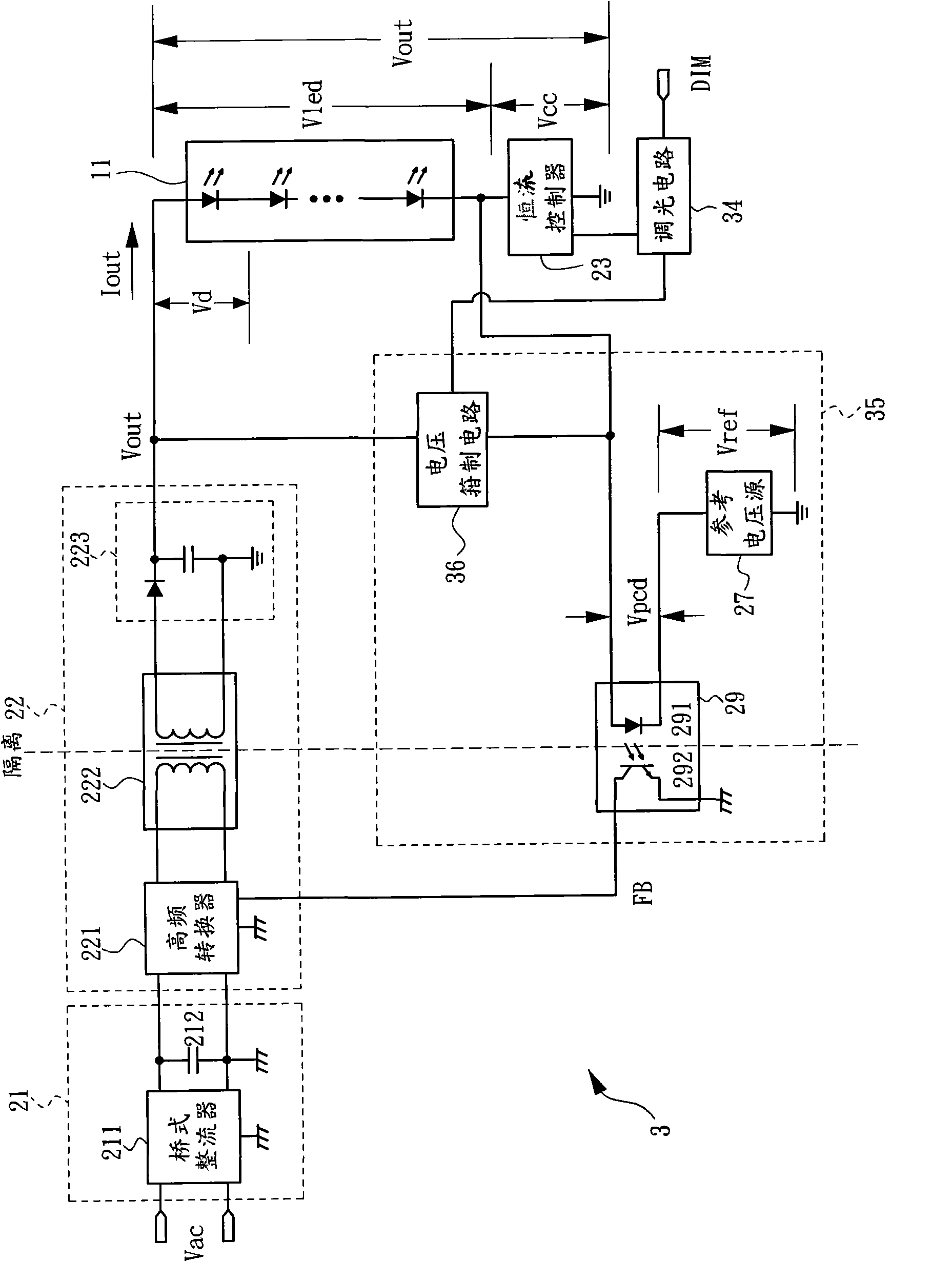

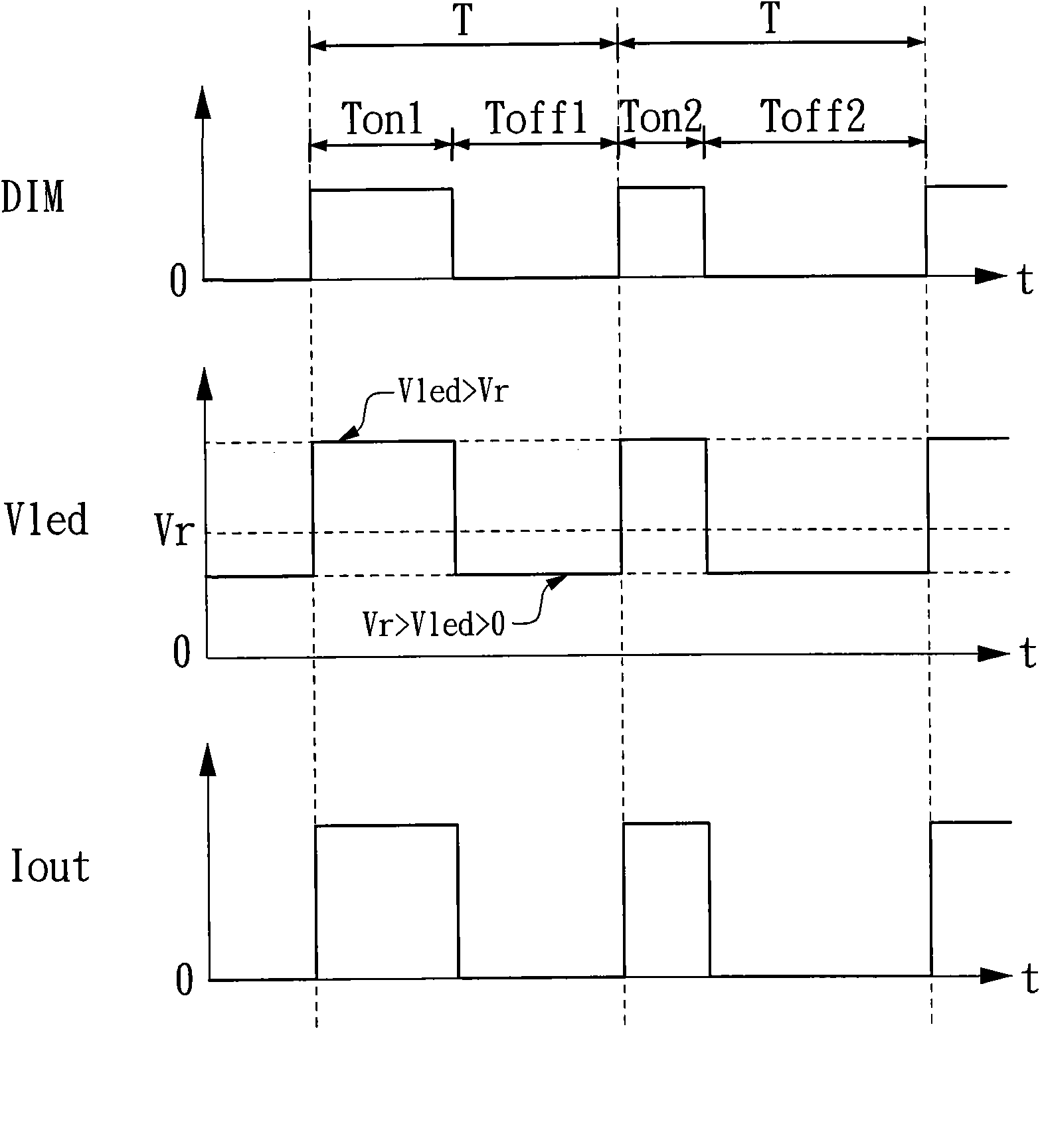

Direct drive light-emitting diode (LED) driver

InactiveCN102387625AImprove stabilityImprove performanceElectric light circuit arrangementPower flowElectromagnetic interference

The invention belongs to the field of electronics and discloses a direct drive light-emitting diode (LED) driver. The driver adopts an isolation circuit to connect the output end of an LED lamp string and a constant current controller in coupling mode, output voltage of the driver changes automatically along with working voltage of the LED lamp string, and the driver can be applied to driving of the LED lamp string with various kinds of different working voltage. Accordingly, an error detection amplifying circuit in a feedback path is omitted, and stability and bandwidth of a return circuit are improved. Pulse width modulation (PWM) dimming can be conducted in a dimming range from 1% to 100% in uninterrupted mode. By means of the characteristics that when the working voltage of the LED lamp string is smaller than cut-in voltage of the LED lamp string, the current is zero, voltage difference of output voltage in an enabling period and a disabling period during PWM dimming is reduced, so that ripple voltage and electromagnetic disturbance are reduced.

Owner:TOP VICTORY INVESTMENTS

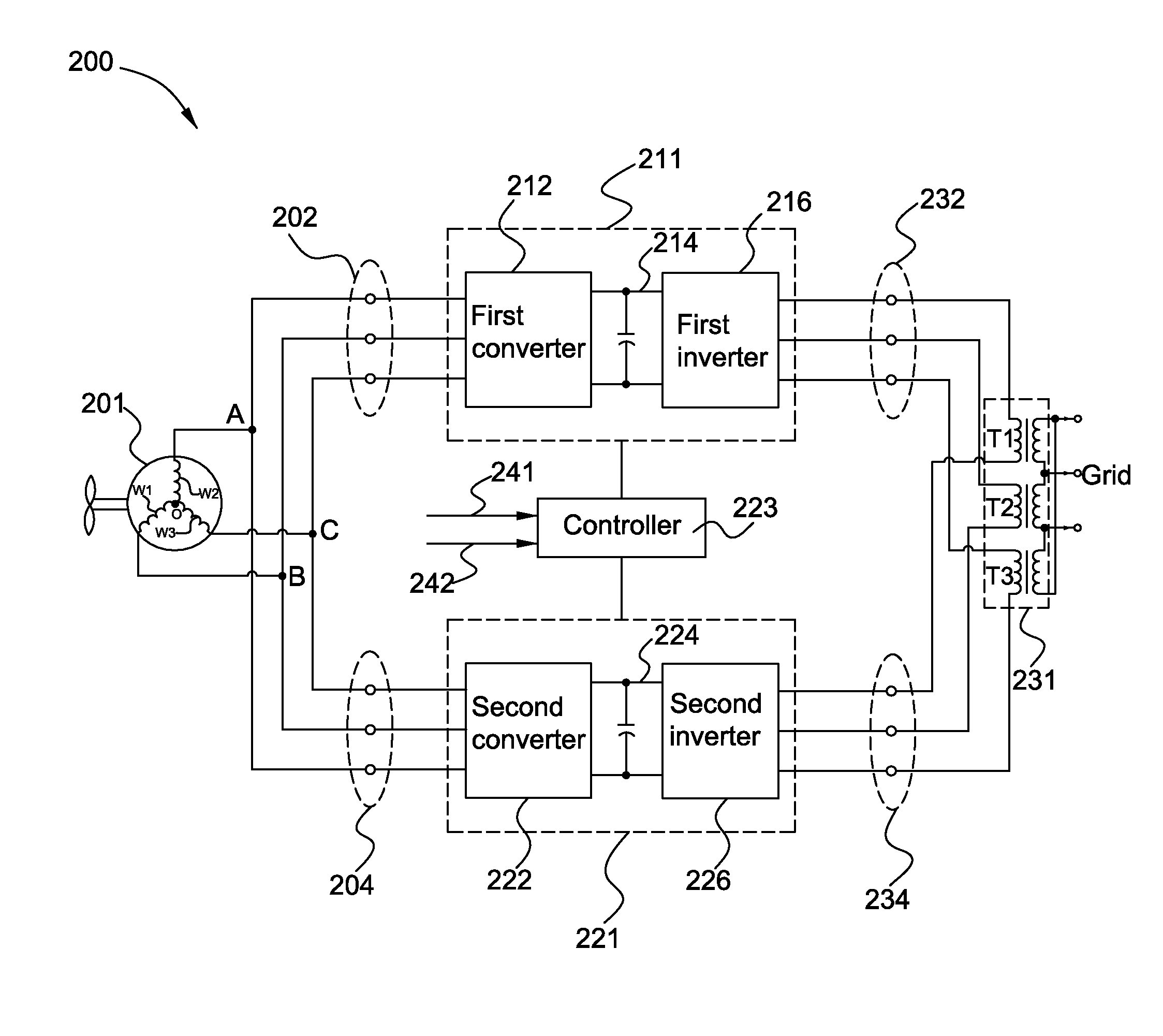

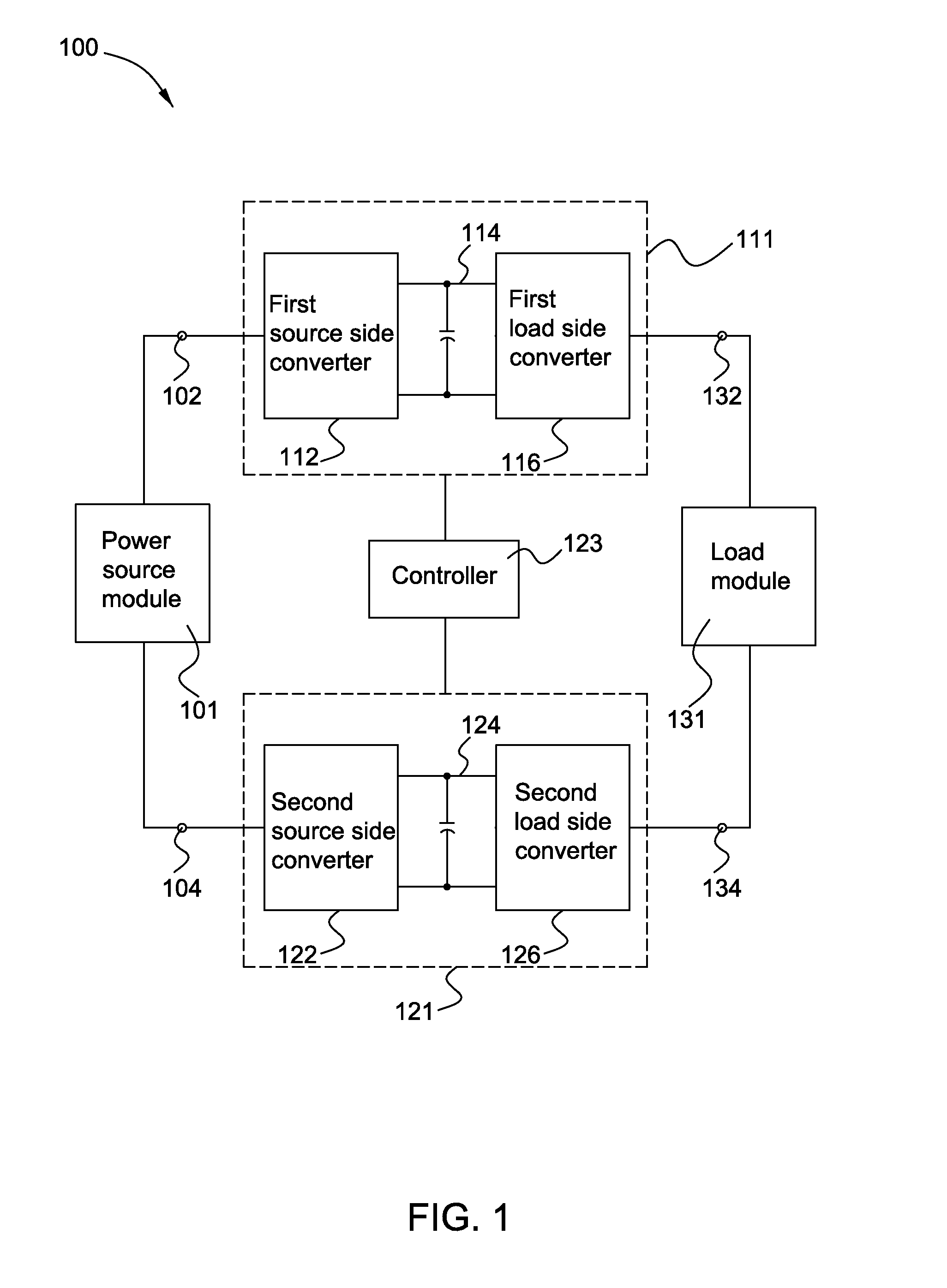

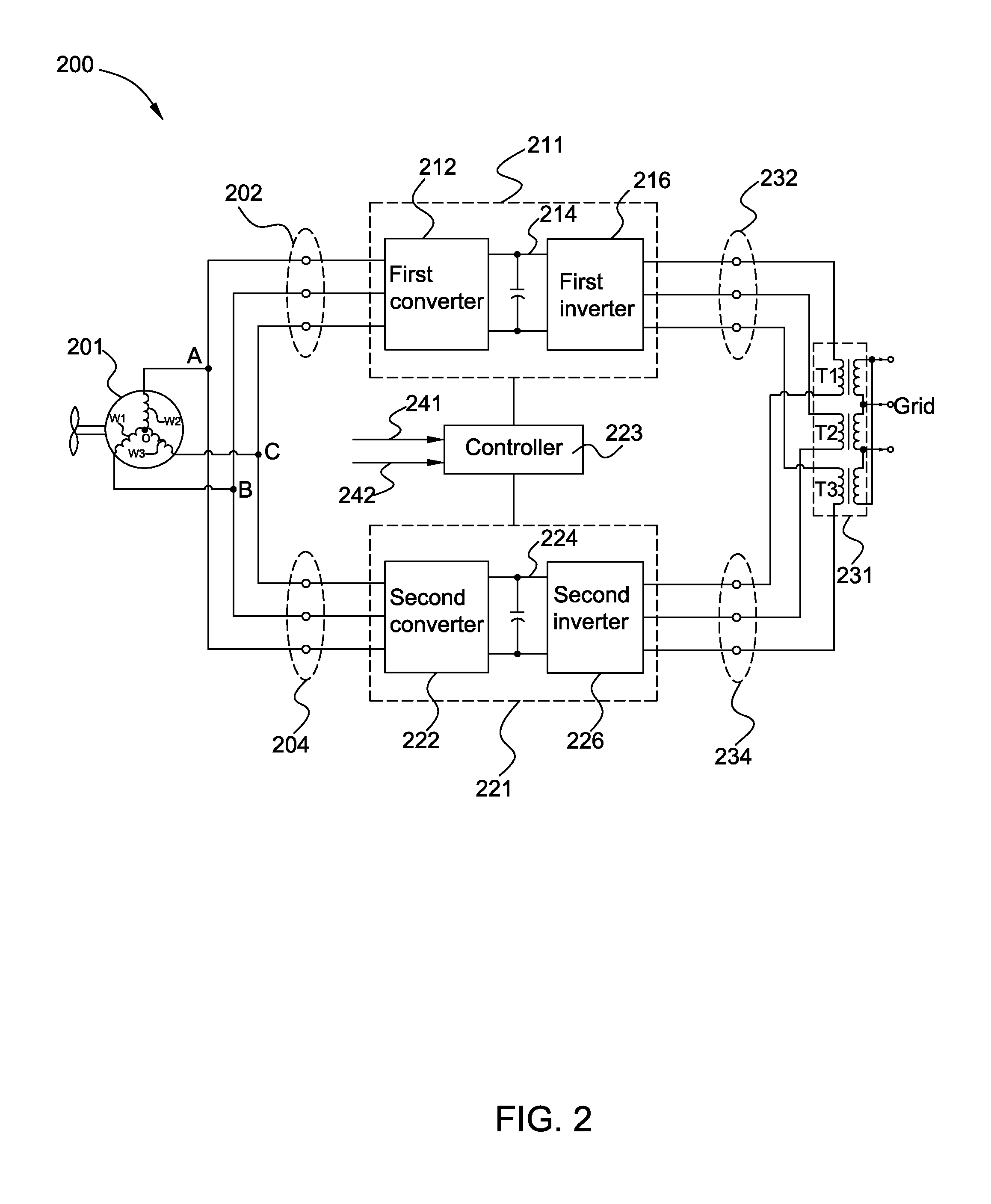

Power conversion system and method

ActiveUS20150035284A1Reduce voltage differenceDc network circuit arrangementsAc-dc conversion without reversalSwitching signalDc link voltage

An exemplary power conversion system includes a first power conversion module, a second power conversion module, and a controller. The first power conversion module includes a first source side converter, a first load side converter, and a first DC link coupled between the first source side converter and the second load side converter. The second power conversion module includes a second source side converter, a second load side converter, and a second DC link coupled between the second source side converter and the second load side converter. The controller is configured to generate a number of switching signals according to a circuit structure of the power source module or a circuit structure of the load module. The switching signals are provided to the first power conversion module and the second power conversion module to balance a first DC link voltage and a second DC link voltage.

Owner:GENERAL ELECTRIC CO