Array substrate and preparation method and display device of array substrate

A technology of array substrate and substrate substrate, which is applied in semiconductor/solid-state device manufacturing, optics, instruments, etc., can solve the problems of reduced pixel aperture ratio, not very obvious, limited, etc., to improve aperture ratio, reduce resistance value, reduce The effect of voltage differences

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

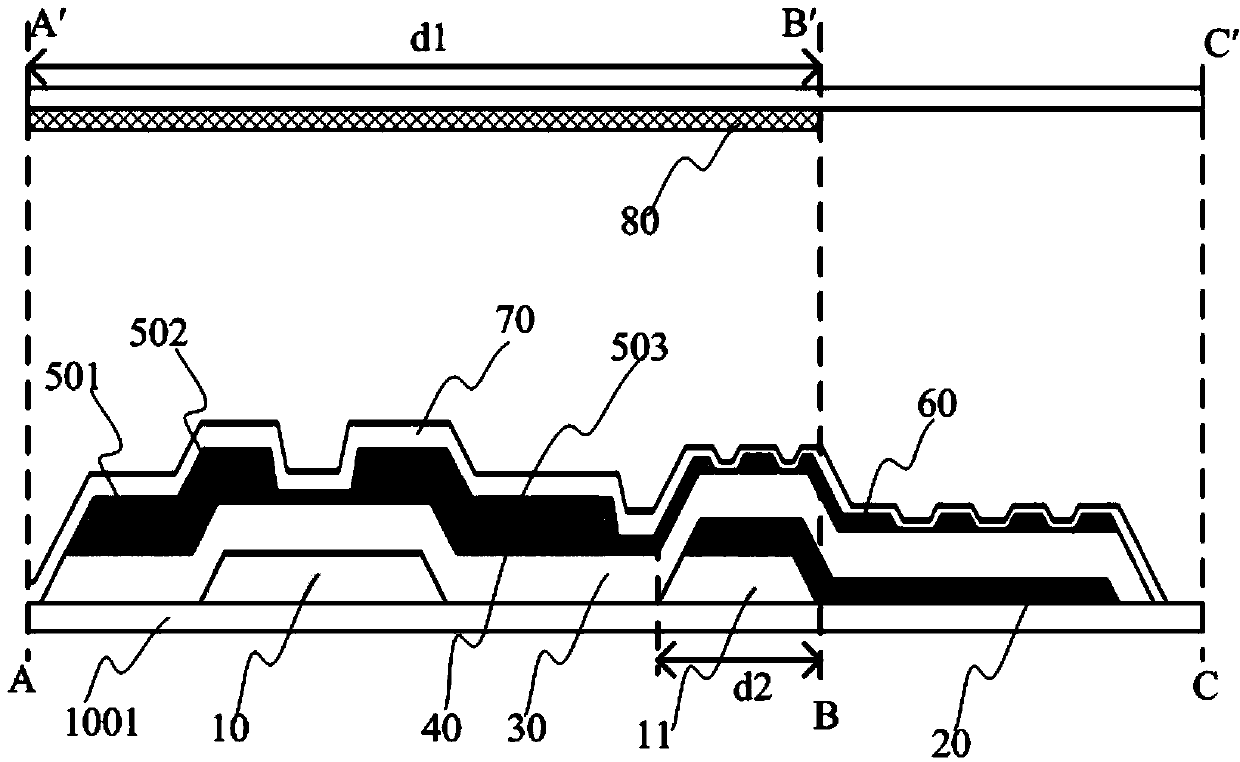

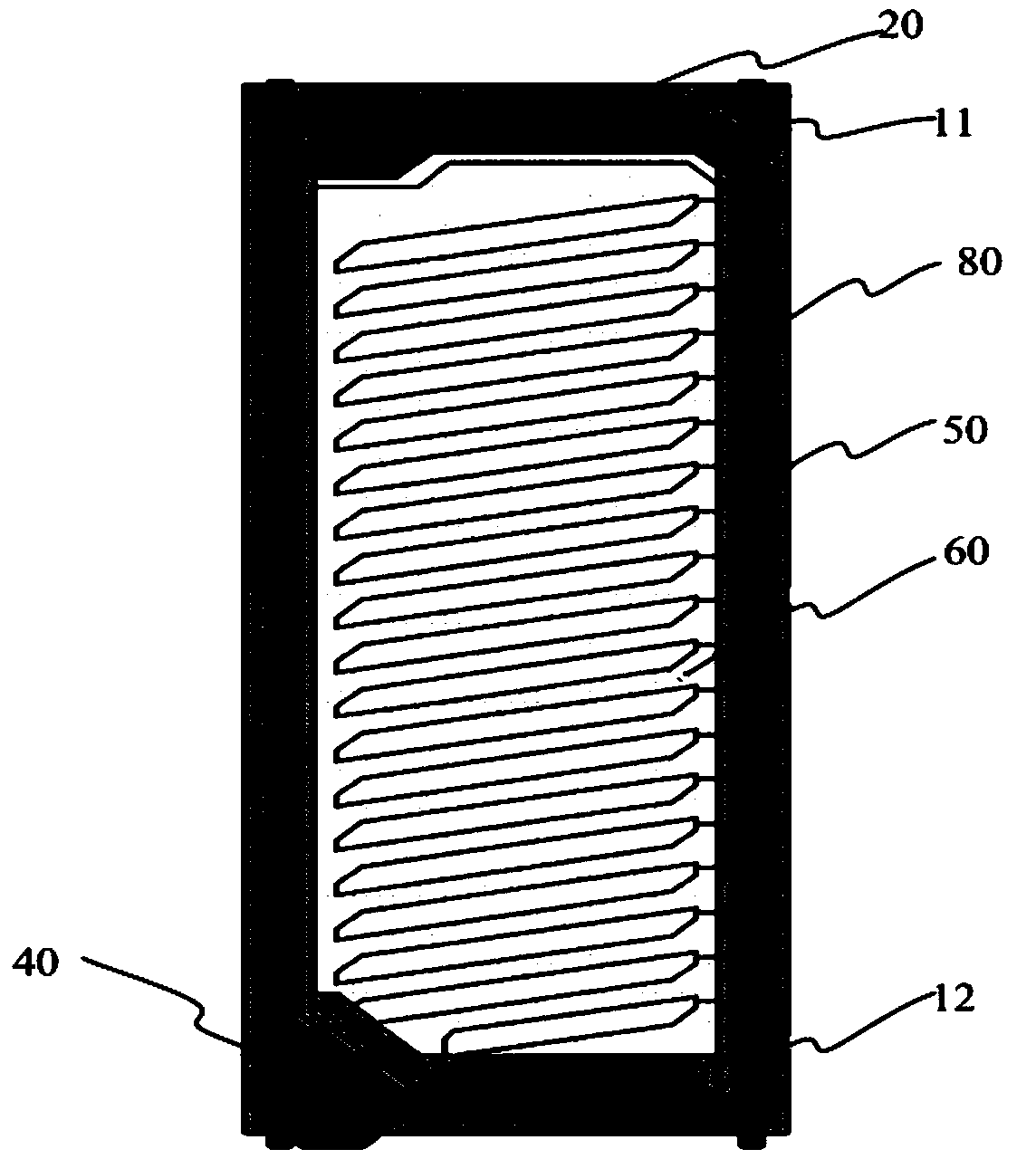

[0094] Embodiment 5 of the present invention provides a method for preparing an array substrate, the method comprising:

[0095] forming a pattern comprising a common electrode layer and a conductive black matrix on the base substrate, the black matrix is electrically connected to the common electrode layer, and the black matrix is arranged in a non-display area of the pixel unit;

[0096] Forming a second insulating layer on the base substrate, the covered area of the second insulating layer overlaps with the covered area of the black matrix and the common electrode layer, and is used to connect the black matrix and the common electrode layer with the thin film transistor insulation;

[0097] Patterns including thin film transistors and pixel electrodes are formed on the base substrate.

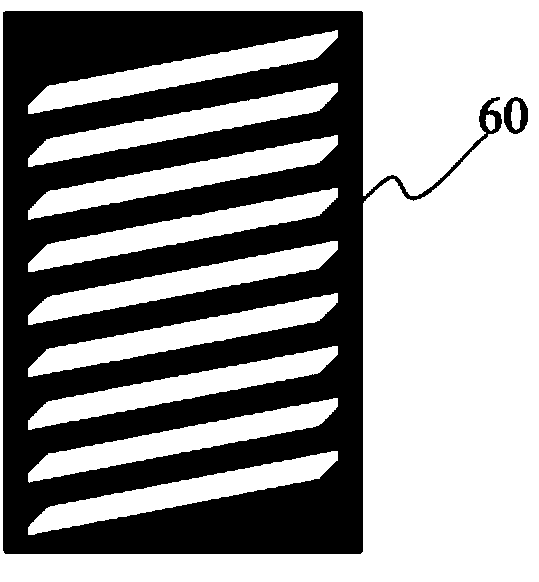

[0098] The array substrate prepared by the method includes a conductive black matrix disposed above the base substrate, the black matrix is electrically connected to the common ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More