Data retention in operational and sleep modes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

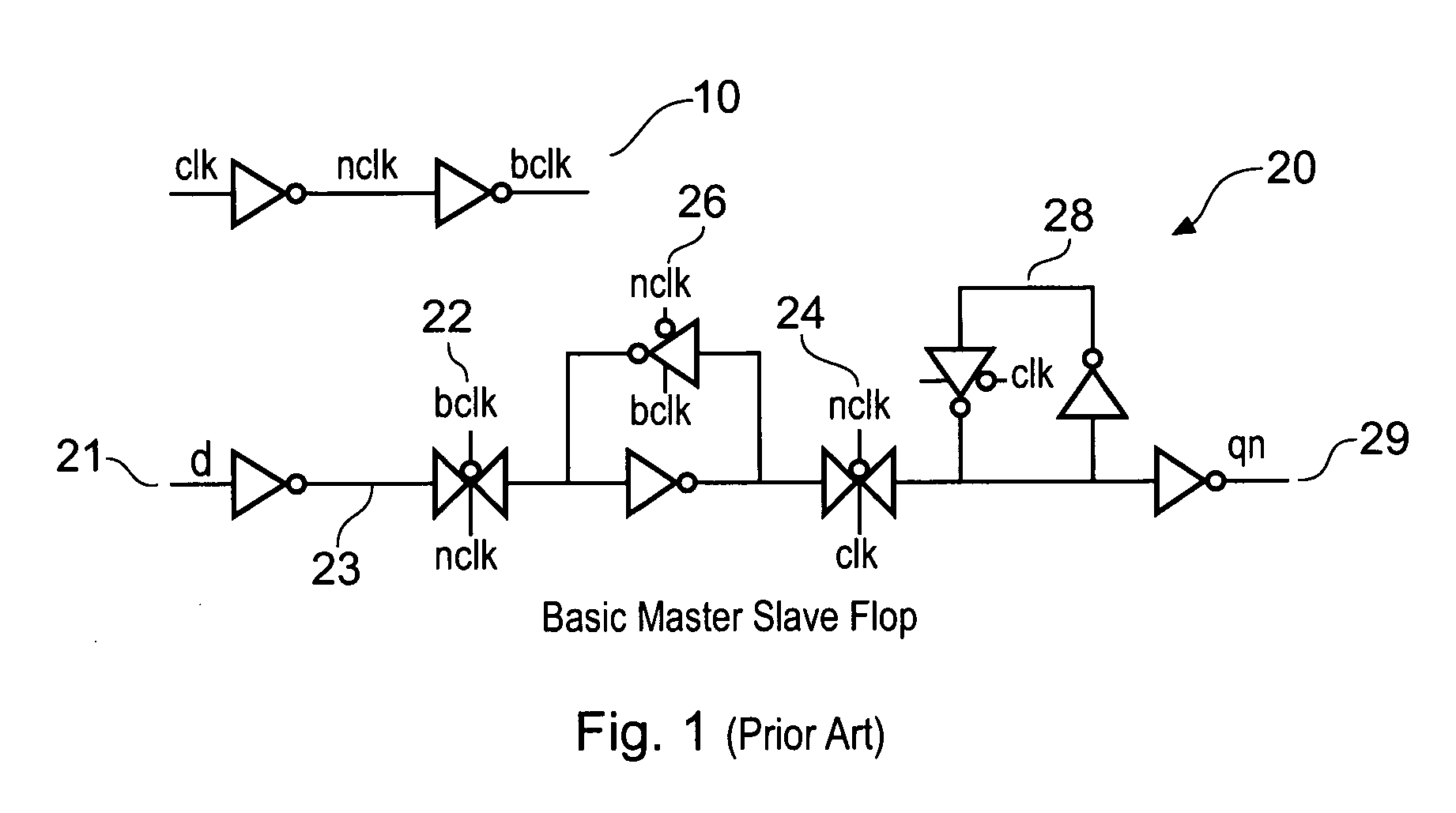

[0062]FIG. 1 shows in schematic form a basic master slave flip flop according to the prior art. This basic master slave flop 20 has a clock distribution means 10 which comprises a plurality of inverters operable to deliver different clock signals, clk, nclk an inverted form of clk, and bclk an inverted form of nclk. The basic master slave flop has a forward data path 23, between data input 21 and data output 29. This forward data path takes data from the input to a master latch 26 via transmission gate 22 and to slave latch 28 via transmission gate 24. Transmission gates 22 and 24 are tristateable devices able to provide a low impedance data path or a high impedance data path depending on the clock values at their inputs. Thus, they act to either isolate the latches or to allow transmission of data to them.

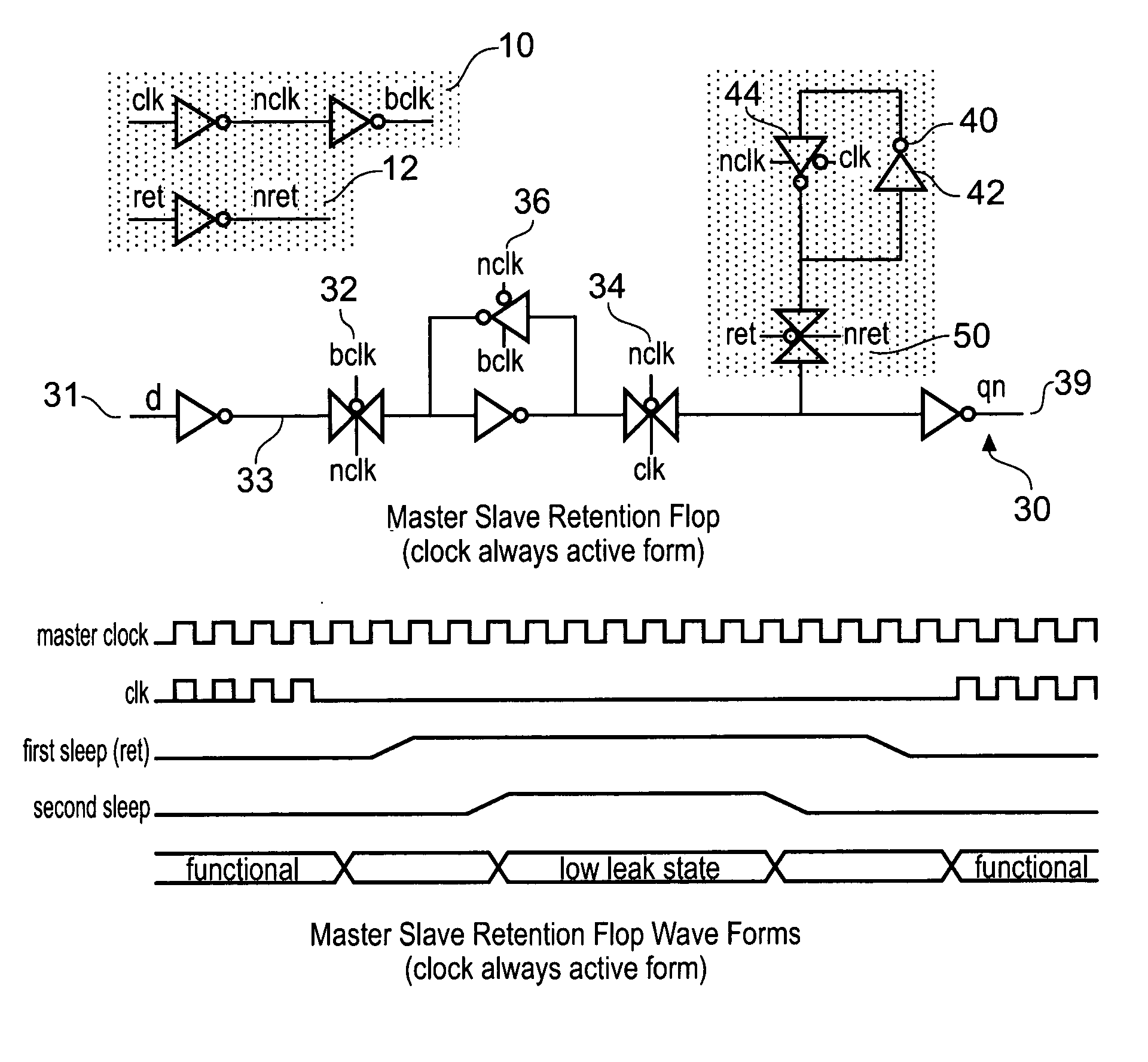

[0063]FIG. 2 shows a master slave retention flop 30 according to an embodiment of the present invention. This is an adaptation of the flop of FIG. 1 and is able to provide data r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More