LDMOS transistor and manufacturing method thereof

A technology of oxide semiconductor and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of unstable device performance, increased photolithography process, and increased cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

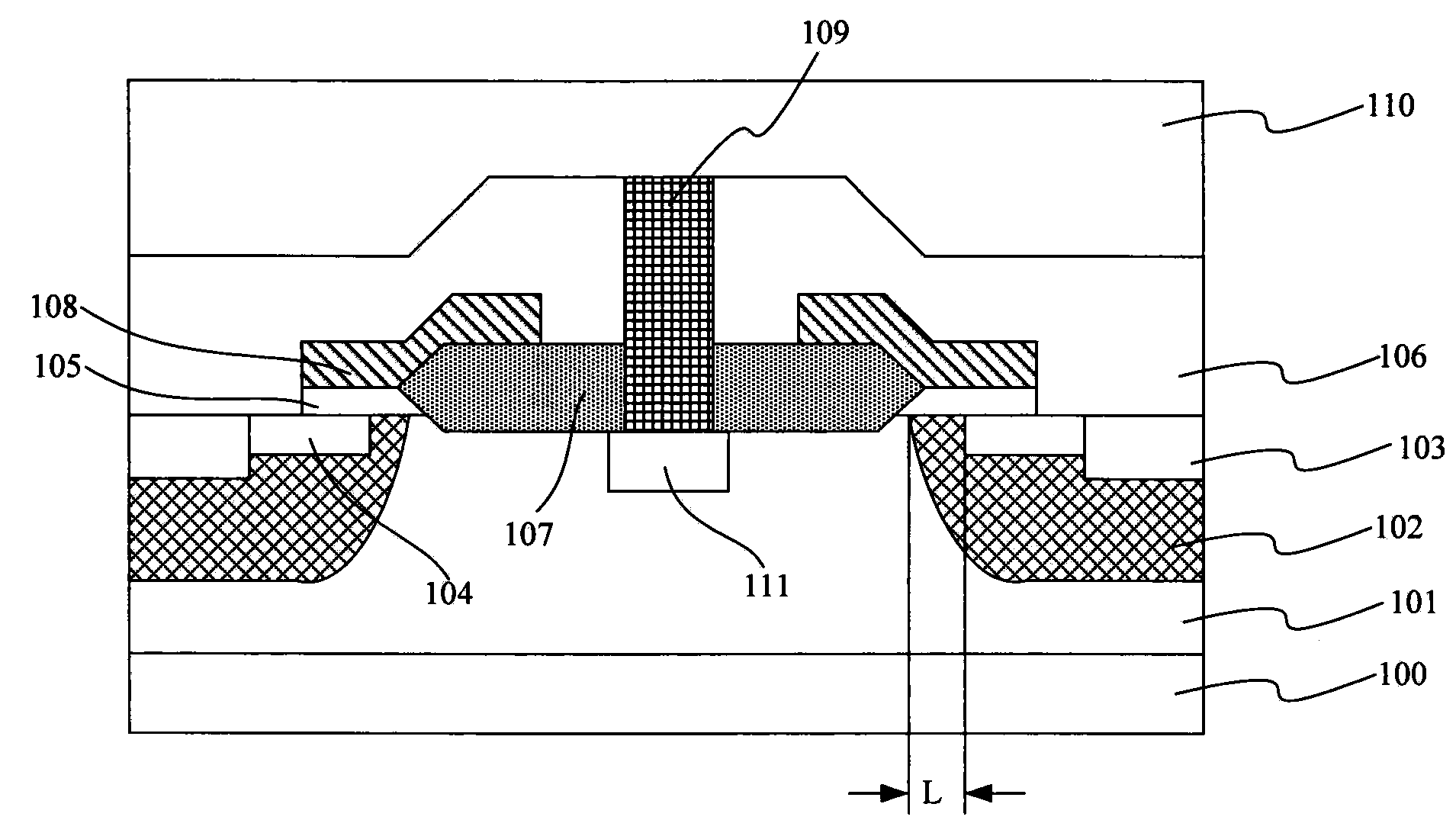

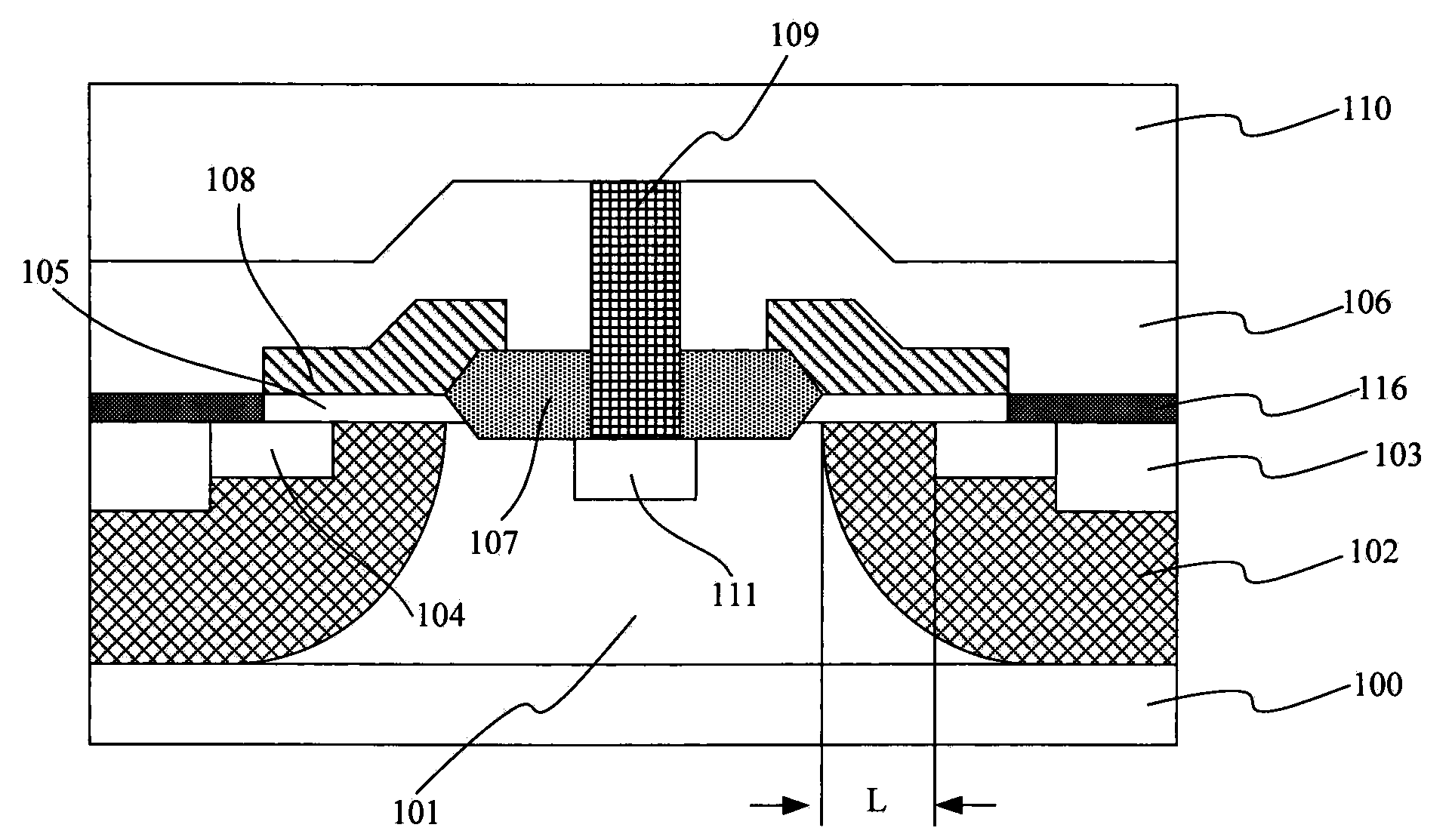

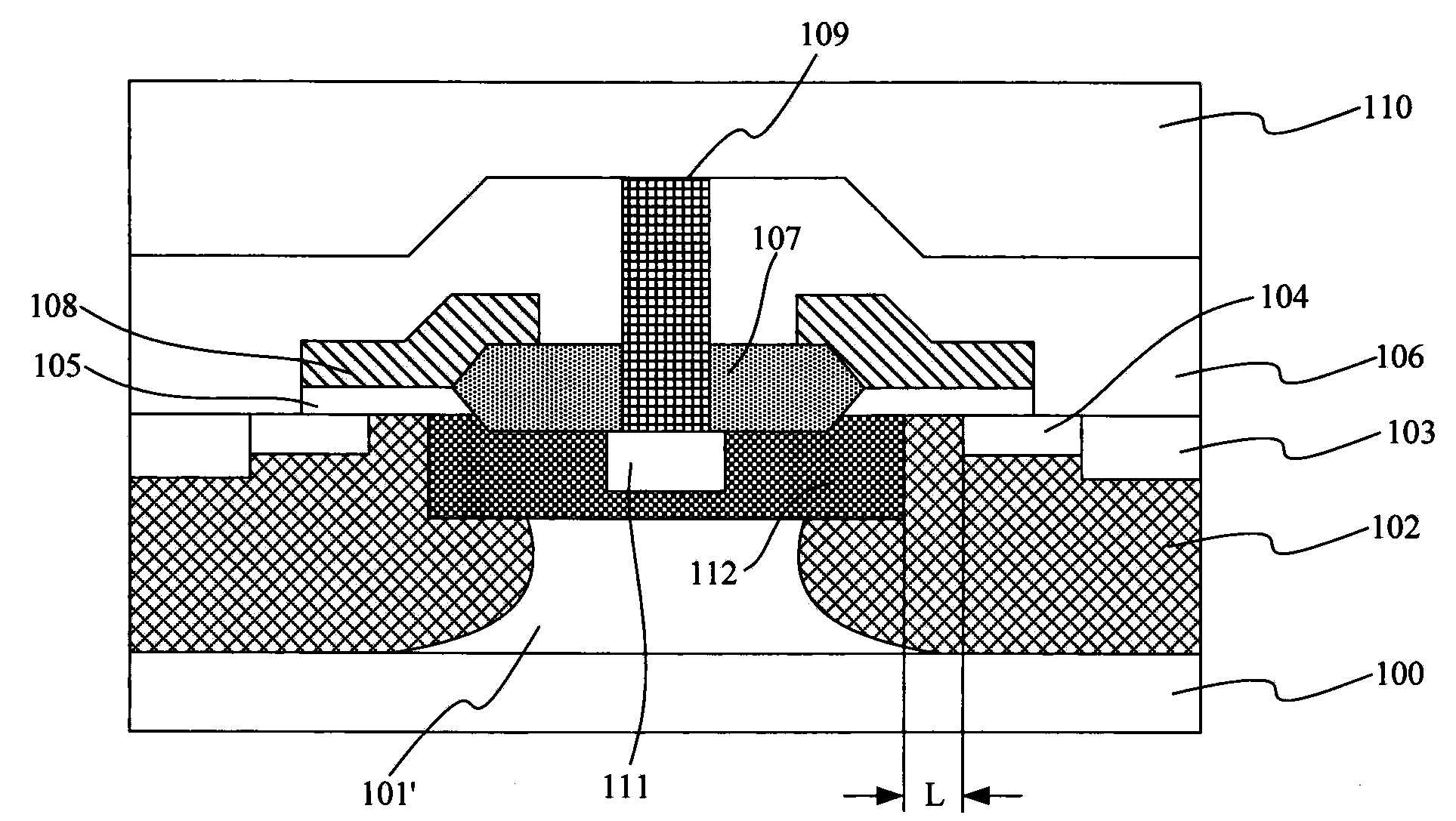

Embodiment 1

[0112] reference Figure 4 First, an N-type epitaxial layer 201 is formed on the surface of a P-type substrate 200 through an epitaxial process. Wherein, the P-type substrate 200 is a high-concentration doped outsourced original silicon wafer, the resistivity of the P-type substrate is 0.001 ohm·cm, the N-type epitaxial layer 201 is formed by an epitaxial process, and the N-type epitaxial layer 201 serves as the drain of the LDMOS, which will withstand higher source and drain voltages. In this embodiment, the N-type epitaxial layer has a resistivity of 0.3 ohm·cm and a thickness of 3 μm. The specific epitaxial growth process conditions are: silane thermal decomposition method is used for vapor phase epitaxy, the reactant is silane, the N-type dopant phosphine, the epitaxy temperature is 1100°C, and the time is 20 minutes. The epitaxial thickness is determined by the LDMOS operating voltage, that is, the source and drain voltages. The higher the voltage, the greater the thicknes...

Embodiment 2

[0138] The principle of embodiment 2 is the same as that of embodiment 1, and the main steps are also the same. The only difference is the selection of the following process parameters:

[0139] The resistivity of the P-type substrate is 0.01 ohm·cm, the resistivity of the N-type epitaxial layer is 1.0 ohm·cm, the thickness is 5 μm, and the epitaxial temperature for forming the N-type epitaxial layer is 1200° C. and the time is 40 minutes.

[0140] The thickness is first grown by thermal oxidation process Lining oxide layer, and then deposit silicon nitride by low pressure chemical vapor deposition process, where the thickness of silicon nitride is The thickness of the field oxide layer 207 grown by the thermal oxidation process is

[0141] The formation condition of the P-type doped region 202 is: the doping dose is 1e14cm -2 The boron ions are accelerated to 200 keV for P-type ion implantation to form a P-type doped region 202 in the N-type epitaxial layer.

[0142] The ion implan...

Embodiment 3

[0154] The principle of embodiment 3 is the same as that of embodiment 1, and the main steps are also the same. The only difference is the selection of the following process parameters:

[0155] The resistivity of the P-type substrate is 0.005 ohm·cm, the resistivity of the N-type epitaxial layer is 0.8 ohm·cm, the thickness is 7 μm, and the epitaxial temperature for forming the N-type epitaxial layer is 1150° C. and the time is 45 minutes.

[0156] The formation condition of the P-type doped region 202 is: the doping dose is 5e14cm -2 The boron ions are accelerated to 150 keV for P-type ion implantation to form a P-type doped region 202 in the N-type epitaxial layer.

[0157] The ion implantation conditions of arsenic ions are: energy: 50keV; doping dose: 5e16cm -2 .

[0158] The thermal propulsion conditions for forming the P trap are: the thermal propulsion temperature is 1050° C., the thermal propulsion time is 100 minutes, and the channel length L is 1.5 μm.

[0159] The thickness ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Upper width | aaaaa | aaaaa |

| Doping concentration | aaaaa | aaaaa |

| Doping concentration | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More