Patents

Literature

32results about How to "Lower pinch-off voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

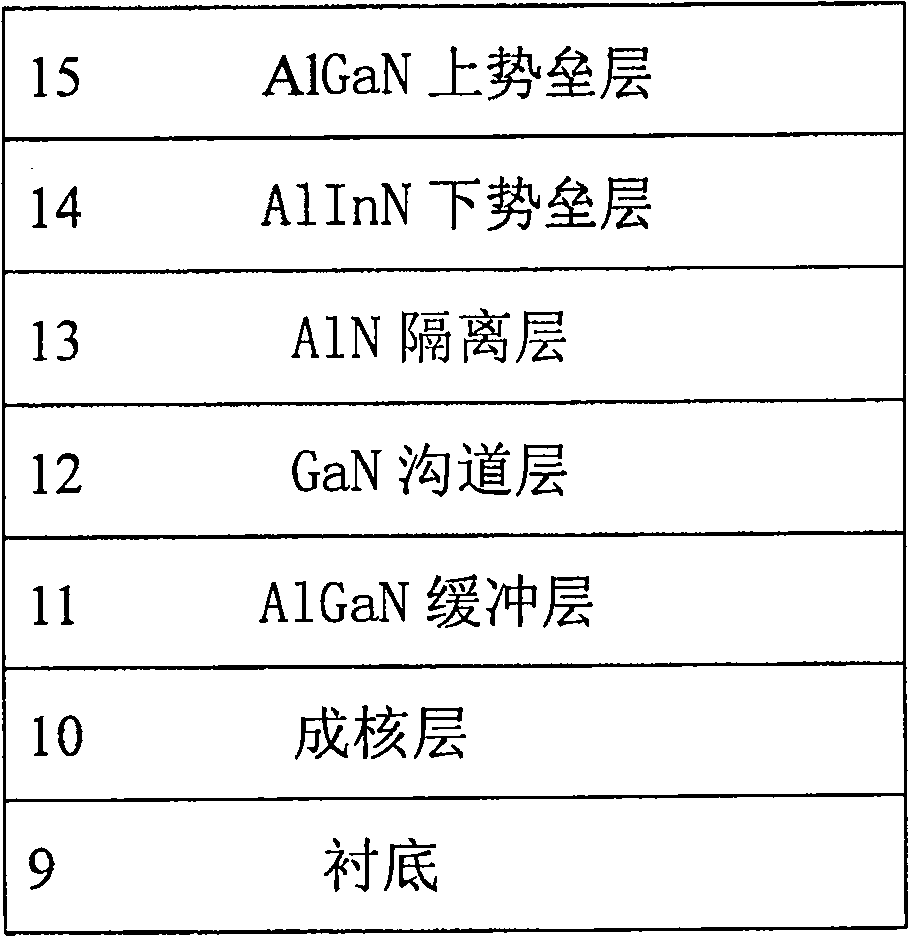

Epitaxial structure of the compound insulation layer nitride high-electronic transfer transistor and its making method

ActiveCN101009326AShorten speedShorten the lengthSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerAlloy

The invention discloses a nitride high electron mobility ratio transistor extension configuration which adopts compound insulated layer and preparation method, by inserting GaN insulated layer between the AlGaN potential barrier layer and the insulated layer of the AlGaN / GaN high electron mobility ratio transistor, it can decrease the ratio that hot electron enters into the AlGaN potential barrier effectively, and decrease the dispersion of alloy, increase the transmission property of electron, so the frequency property of the transistor can be improved, besides it is good for the realization of component ohm contacting craft and decreasing the hardness of craft of producing high property component.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

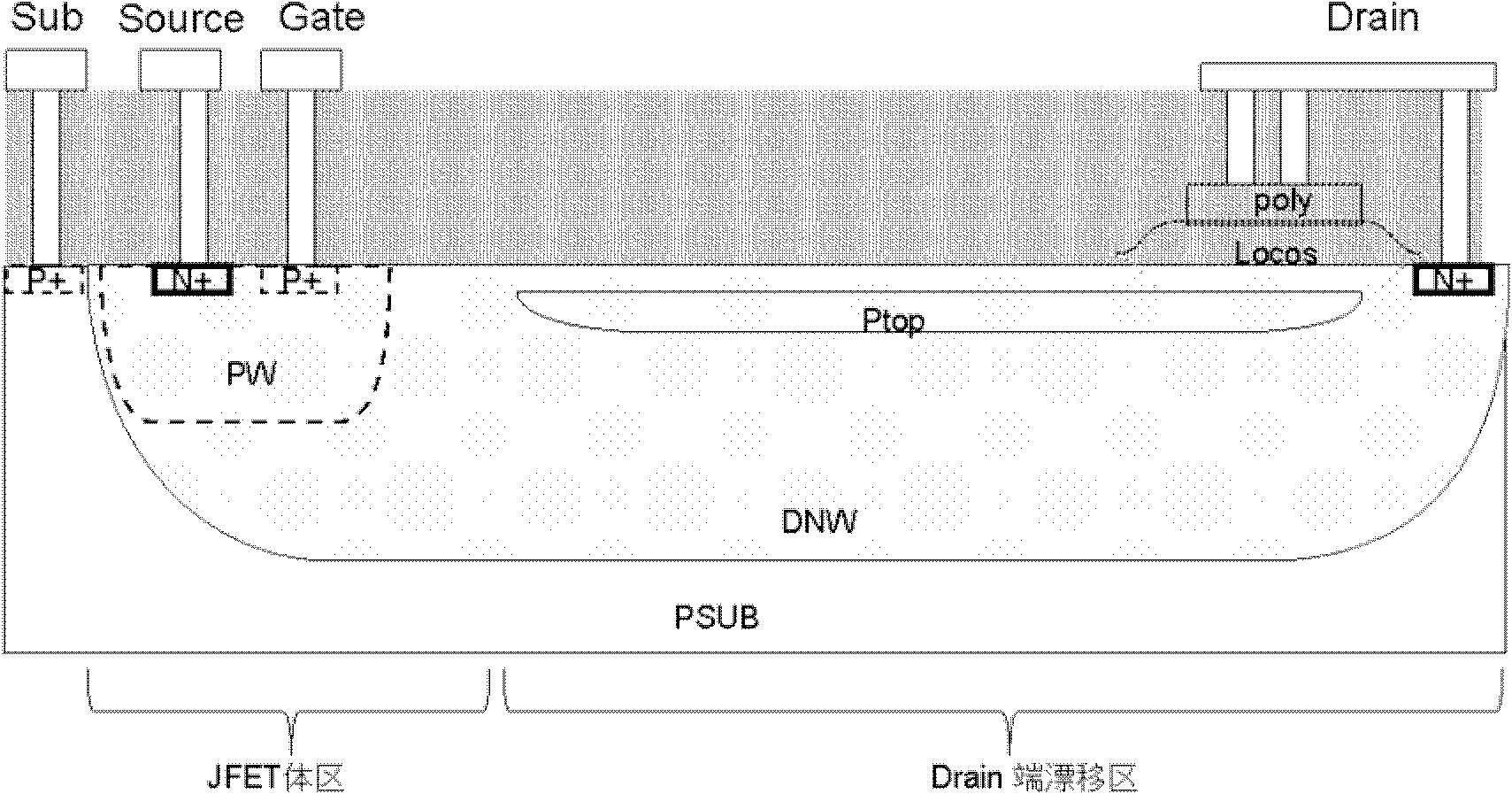

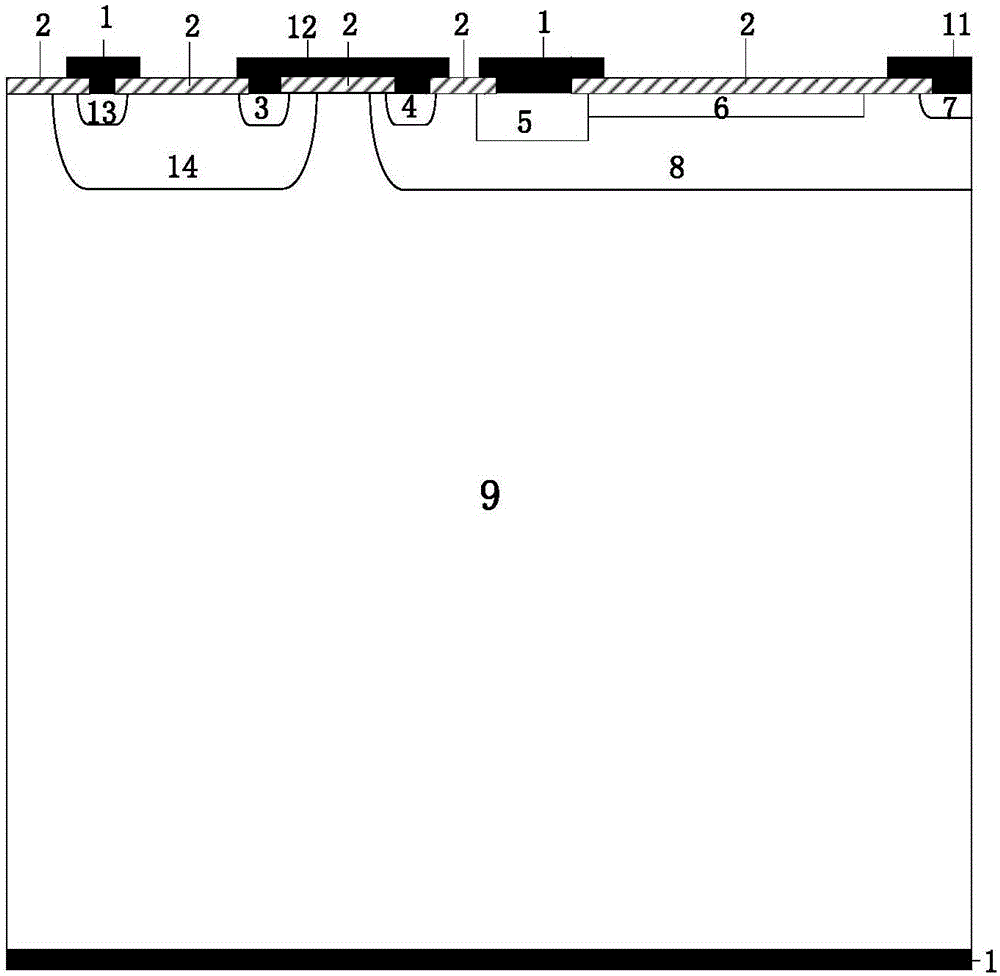

High-voltage junction field effect transistor structure and manufacture method

ActiveCN103178093AReduce impurity concentrationEasy to run outSemiconductor/solid-state device manufacturingSemiconductor devicesJFETBody region

The invention discloses a high-voltage junction field effect transistor structure. An inversion layer is filled into a deep channel of a body region of the structure. The invention further discloses a manufacture method of the high-voltage junction field effect transistor structure (HV JFET) structure. The manufacture method comprises the steps of manufacturing the inversion layer in the deep channel of the body region through a photoetching and ion implantation process while manufacturing a substrate trap of a manufacture body region or the inversion layer of a drain terminal drifting region in the HV JFET conventional manufacture process. By filling one opposite type of impurities into the deep channel of the JFET body region, the impurity concentration of the channel of the JFET body region is reduced on a basis that any photoetching layer is not increased, the channel is easily used up, and accordingly the pinch-off voltage of an HV JFET device is effectively reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

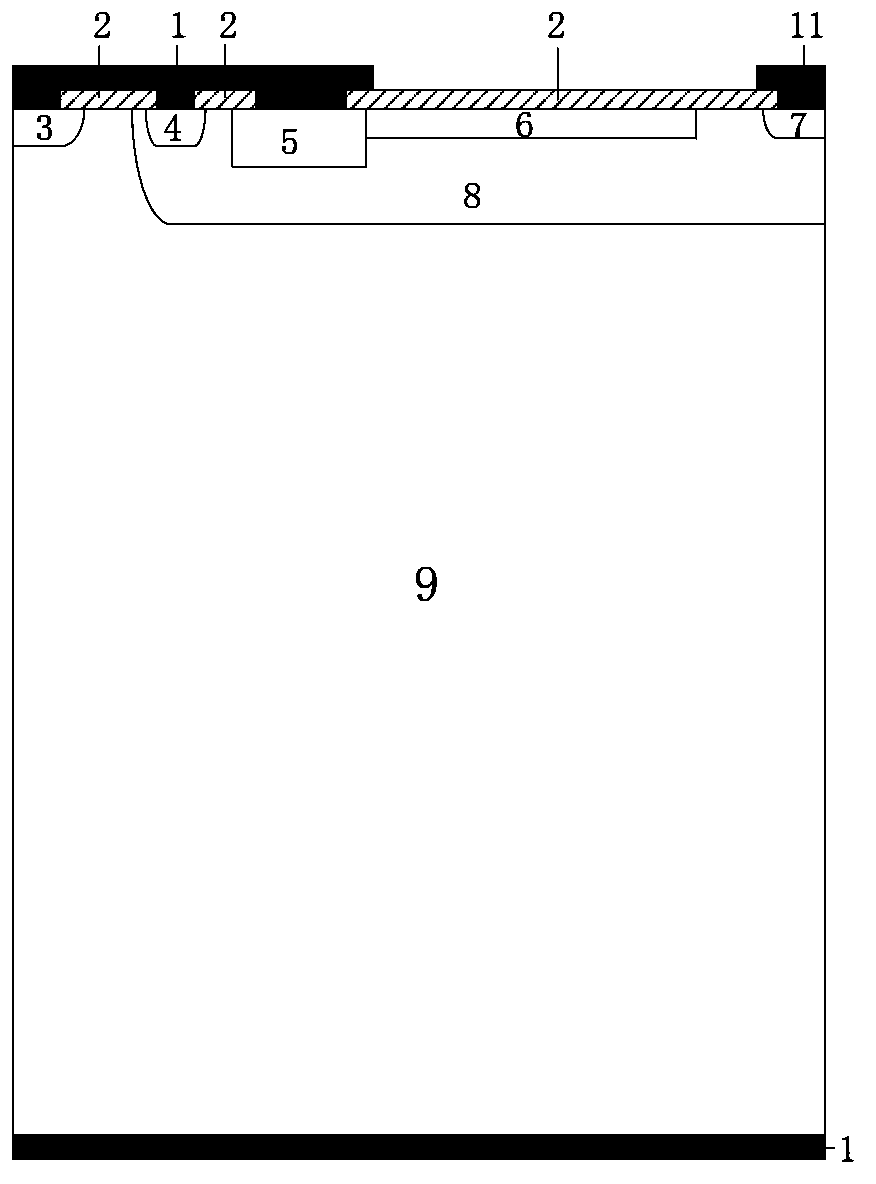

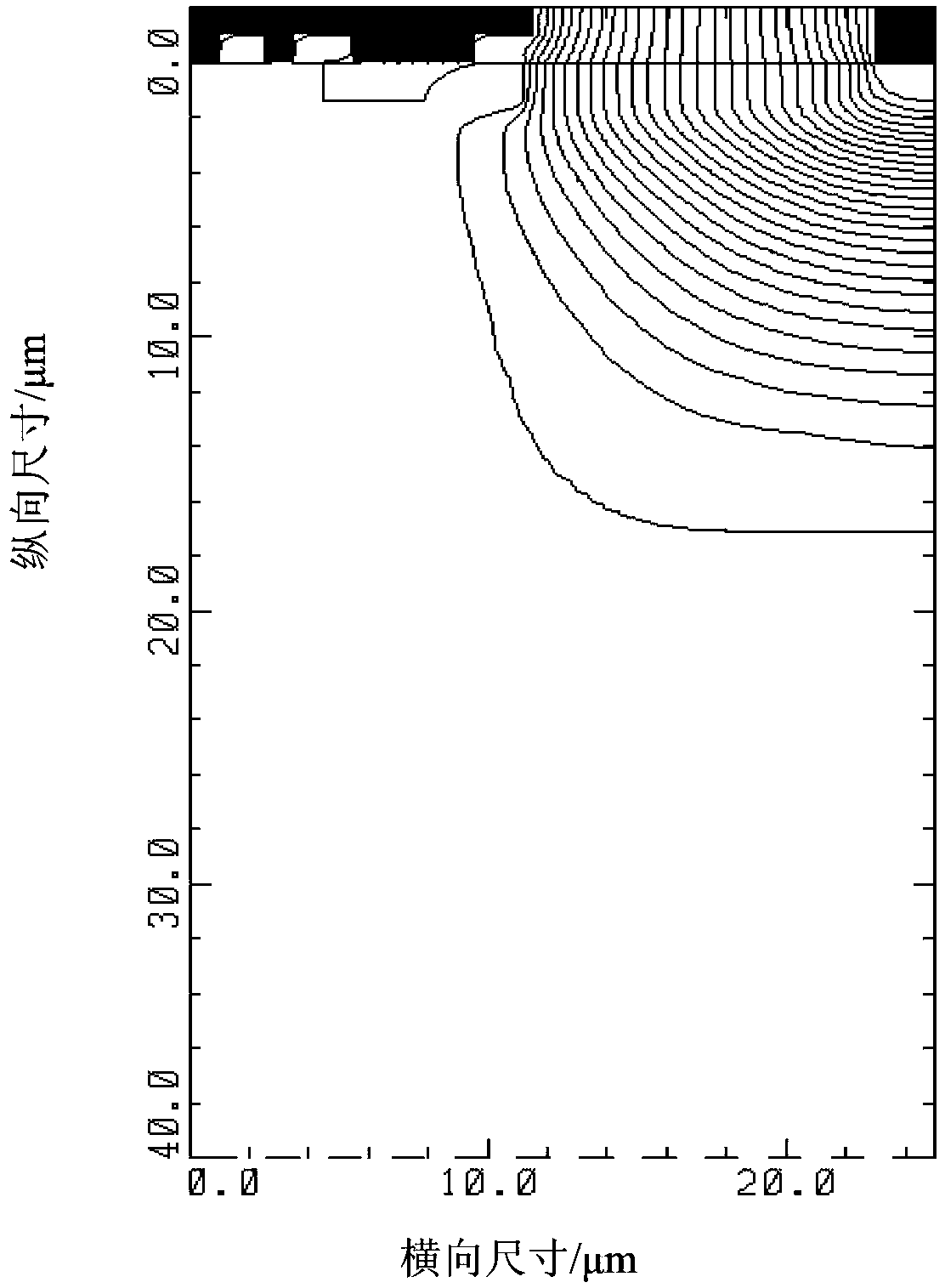

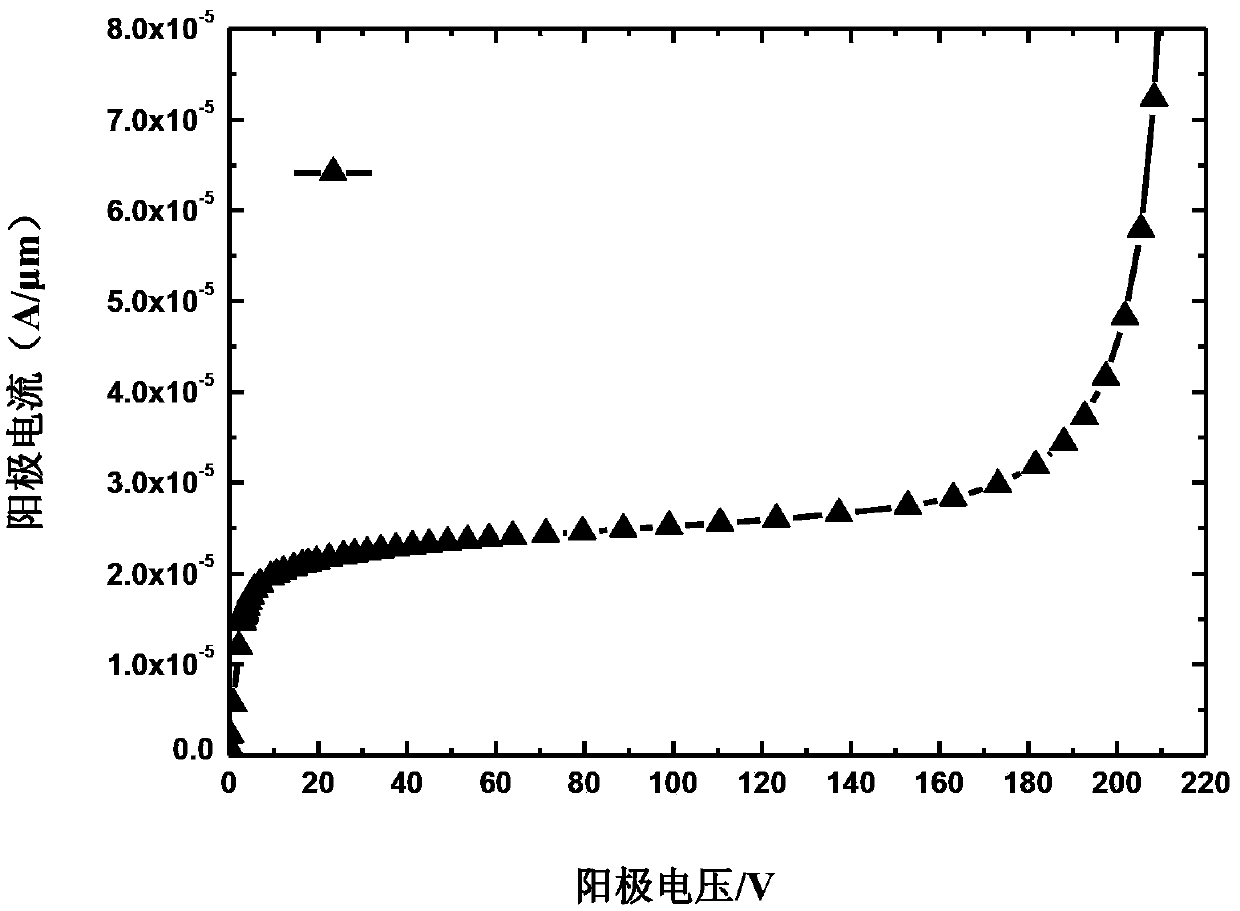

Transverse constant current diode

InactiveCN103400863AIncrease the constant currentEasy to pinch offSemiconductor devicesConstant-current diodeSemiconductor

The invention relates to semiconductor technologies, and particularly relates to a transverse constant current diode. The transverse constant current diode provided by the invention forms a P-type well region through introducing a lightly doped P-type region and a heavily doped P-type region into an N-type well region, thereby modulating a surface electric field, and improving breakdown voltage. Meanwhile, the lightly doped P-type region can assist to exhaust the N-type well region, thereby enabling a channel to be pinched off more easily, coming into a constant current region quickly, enabling the constant current diode to have lower pinch-off voltage, shortening the channel length of the deep heavily doped P-type region, and improving the constant current of the constant current diode. The transverse constant current diode has the beneficial effects that the breakdown voltage of the transverse constant current diode is improved effectively, the channel is enabled to be pinched off more easily at the same time, the constant current region can be entered quickly, the transverse constant current diode is enabled to have lower pinch-off voltage, and the constant current of the transverse constant current diode is effectively improved. The transverse constant current diode provided by the invention is especially applied to transverse constant current diodes.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

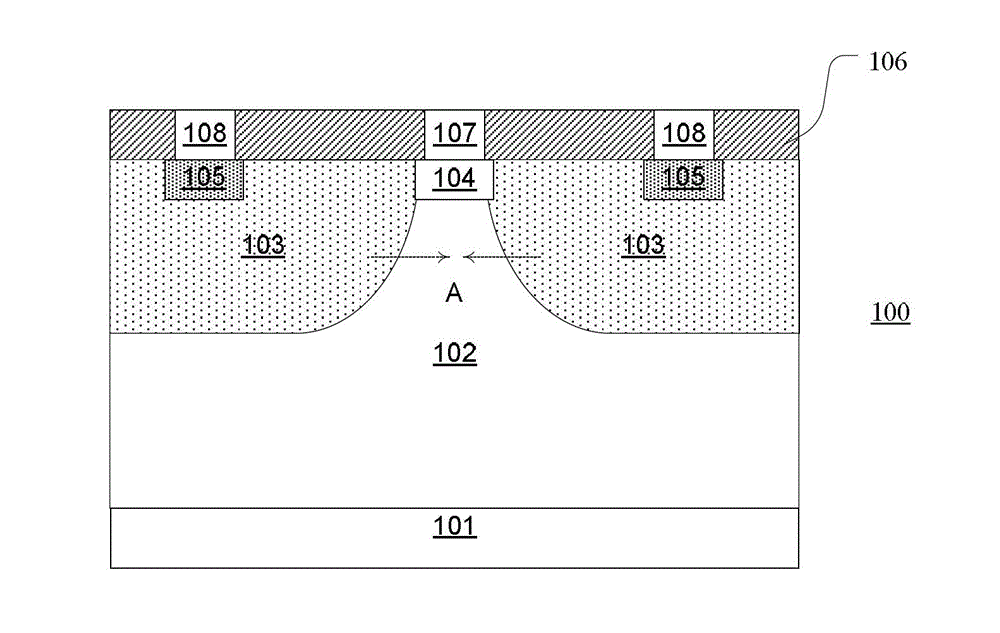

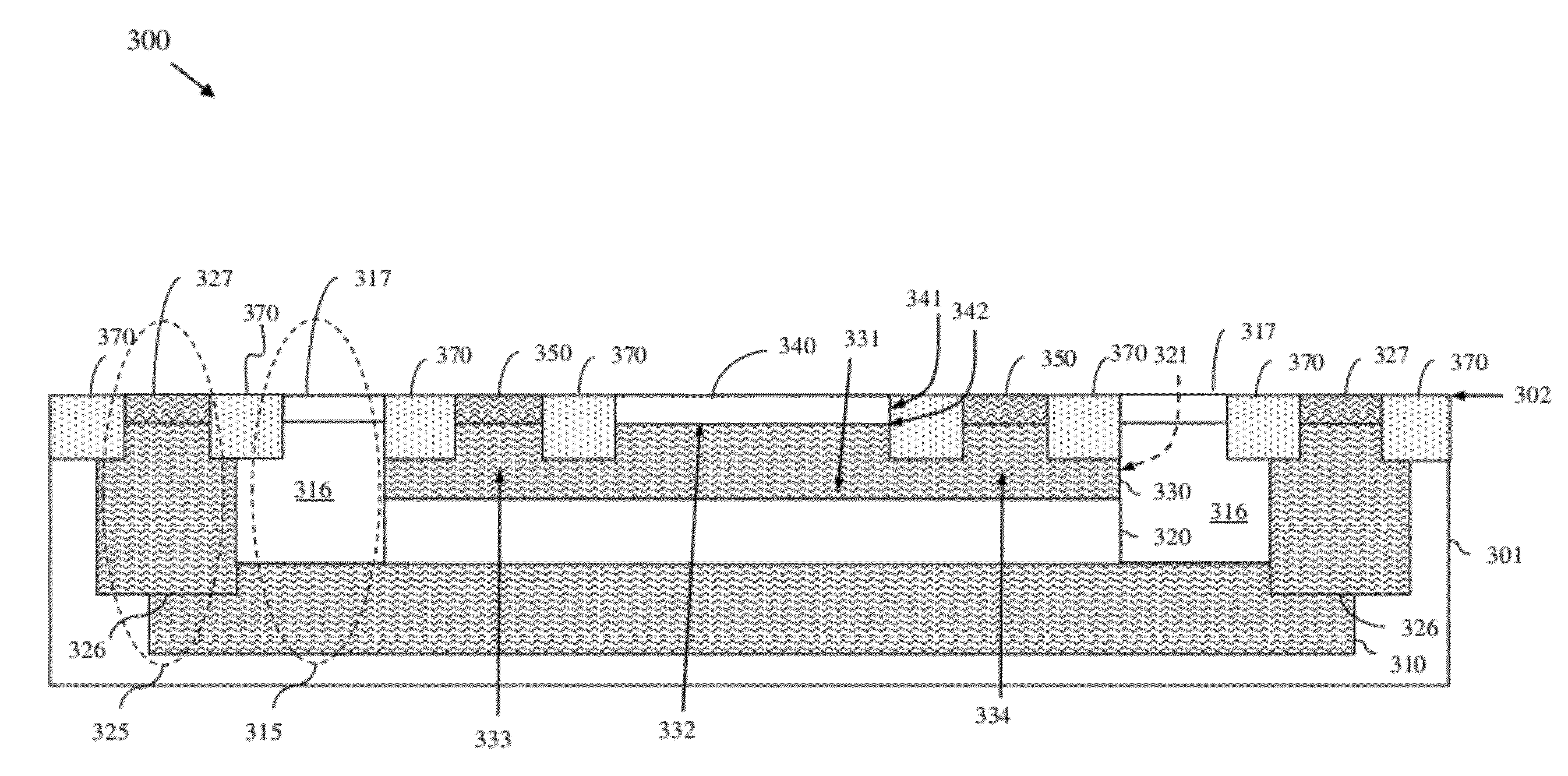

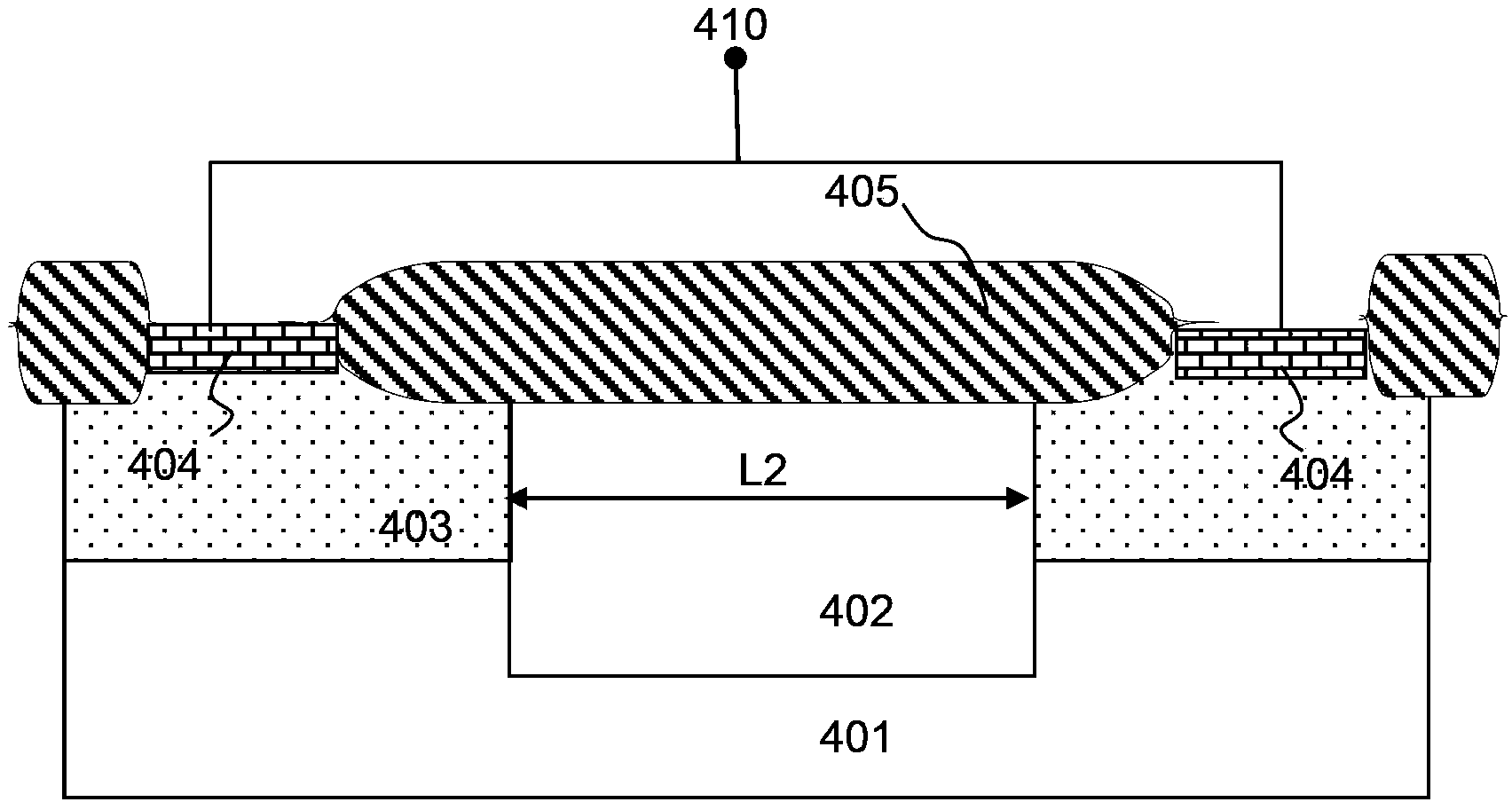

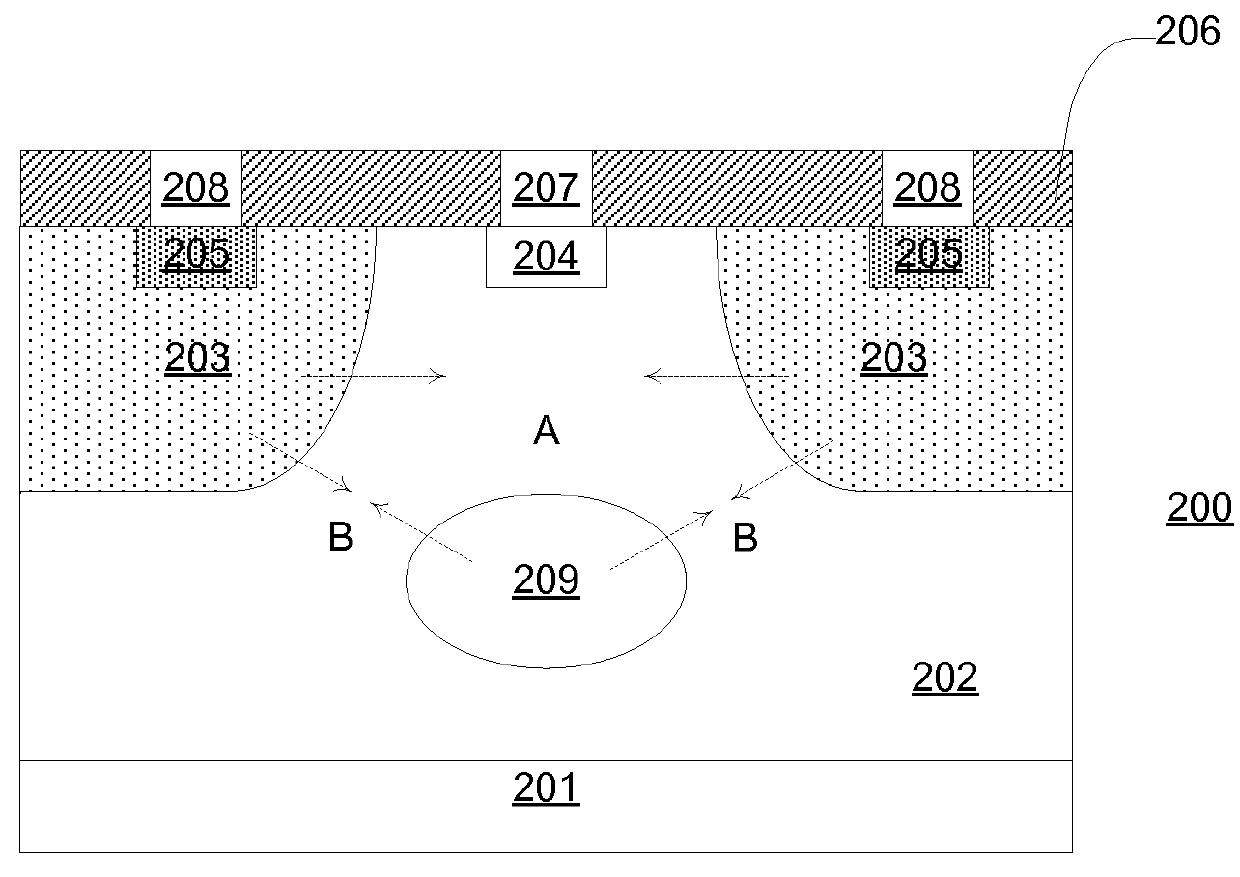

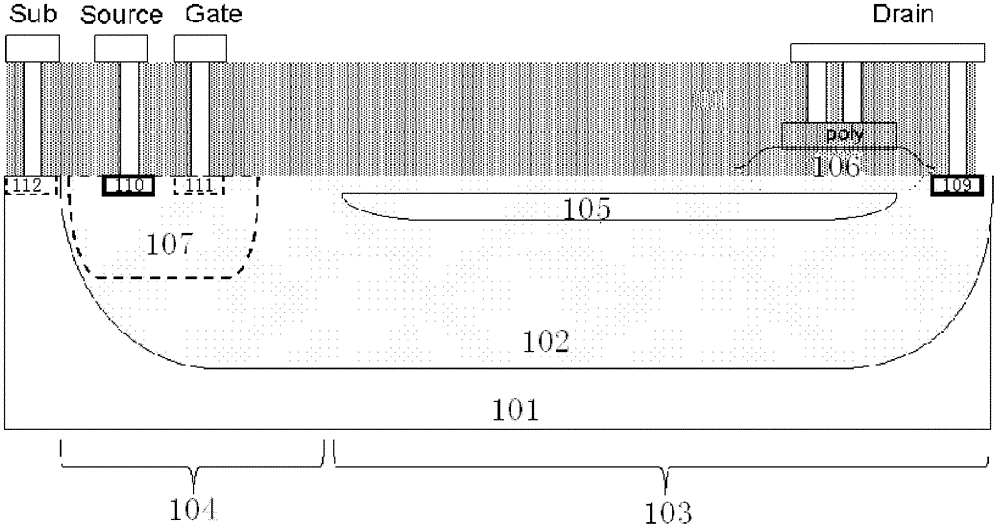

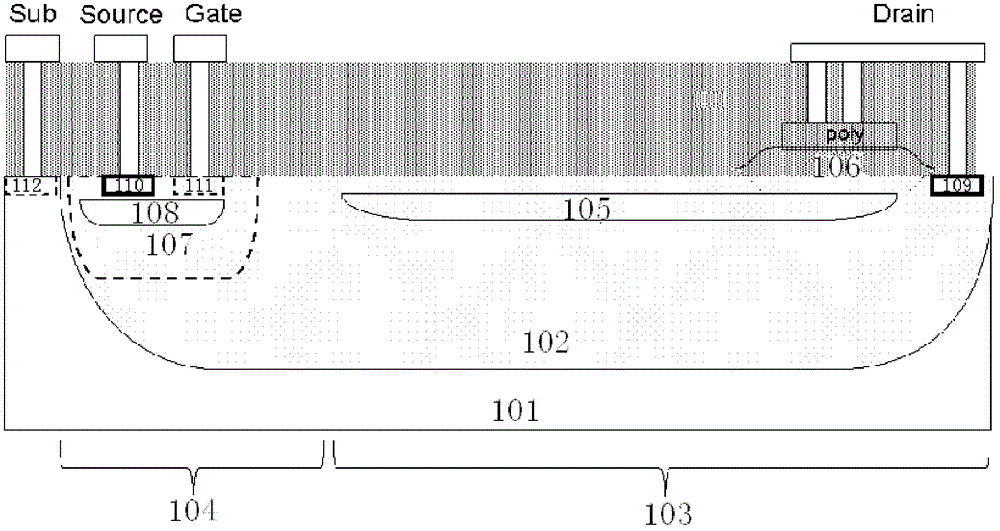

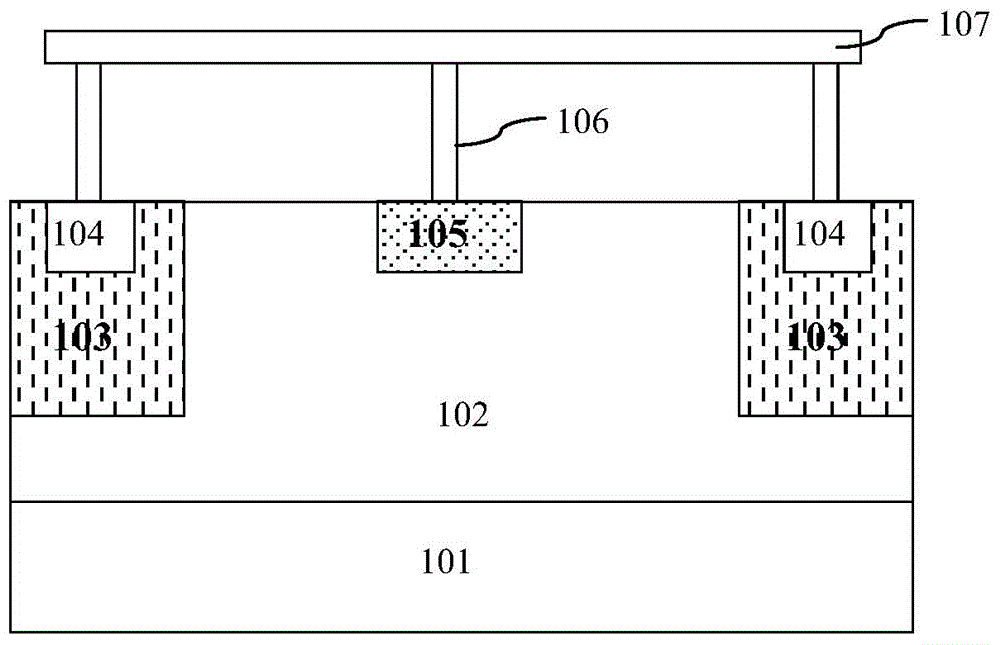

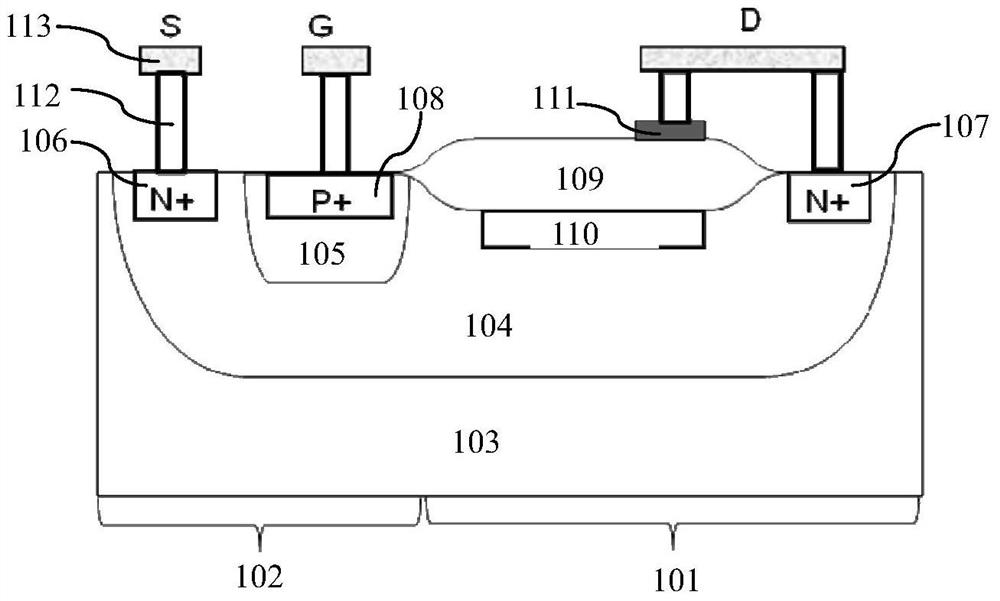

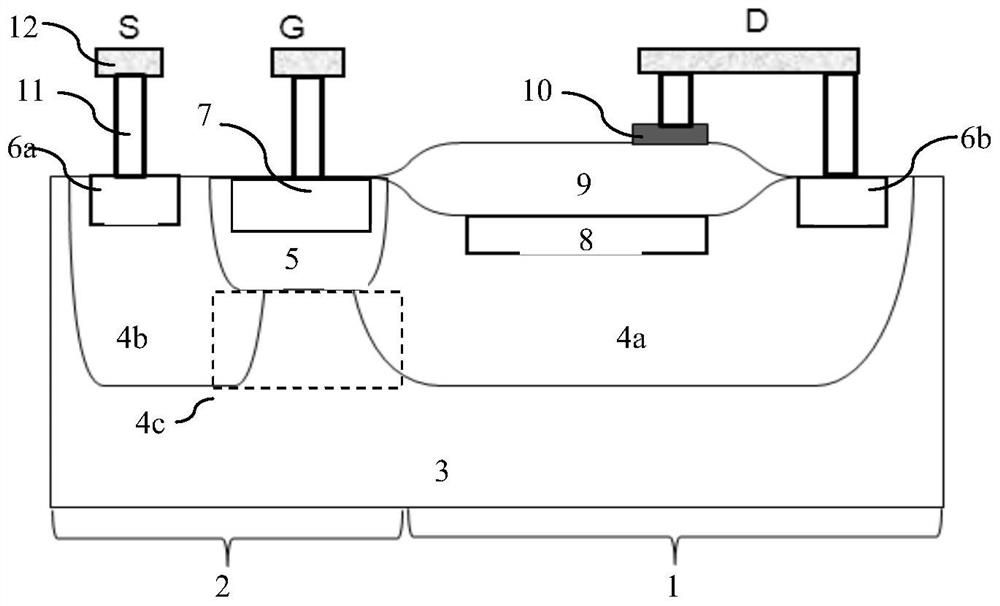

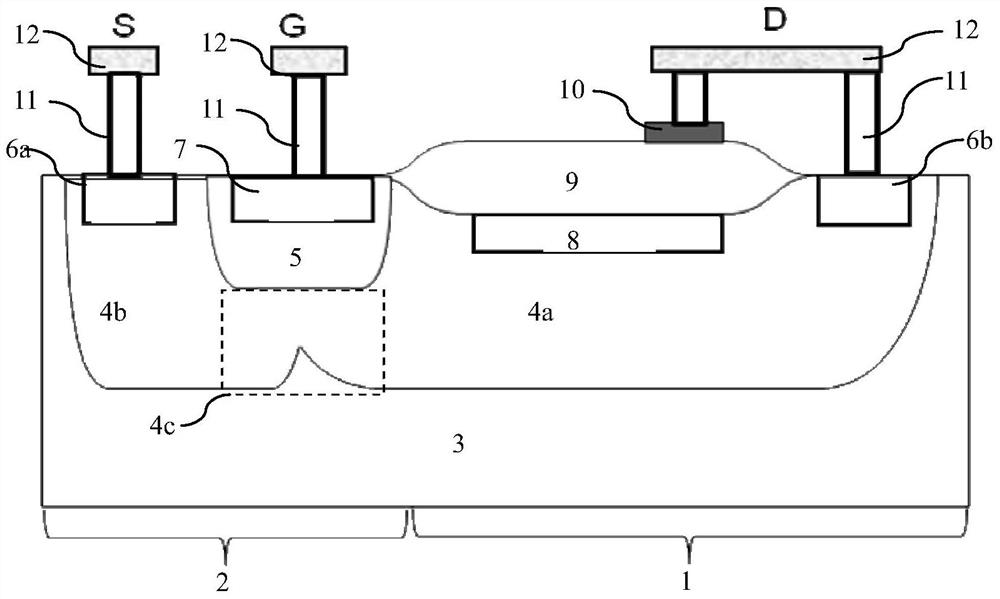

Semiconductor device comprising junction type filed effect transistor and manufacturing method thereof

ActiveCN102916049AEnhanced pinch-off effectLower pinch-off voltageTransistorSolid-state devicesDevice materialEngineering

The invention discloses a semiconductor device comprising a junction type field effect transistor and a manufacturing method thereof. The semiconductor device comprises a junction type field effect transistor, wherein the junction type field effect transistor comprises a semiconductor underlay, an epitaxial layer, a body region, a source electrode region and a grid region, wherein the semiconductor underlay is provided with a first doping type and taken as a drain region of the junction type field effect transistor; the epitaxial layer is located on the semiconductor underlay and provided with a first doping type; the body region is located in the epitaxial layer and provided with a second doping type, and the types of the second doping type and the first doping type are reverse; the source electrode is located in the epitaxial layer and provided with a first doping type; and the grid region is located in the body region and provided with the second doping type, wherein the junction type field effect transistor further comprises a shielding layer, the shielding layer is provided with the second doping type, which is located in the epitaxial layer, and is also located in a conduction path between the source electrode region and the drain region. With the adoption of the shielding layer, a new pinch-off region is generated in the junction type field effect transistor, so as to reduce pinch-off voltage.

Owner:CHENGDU MONOLITHIC POWER SYST

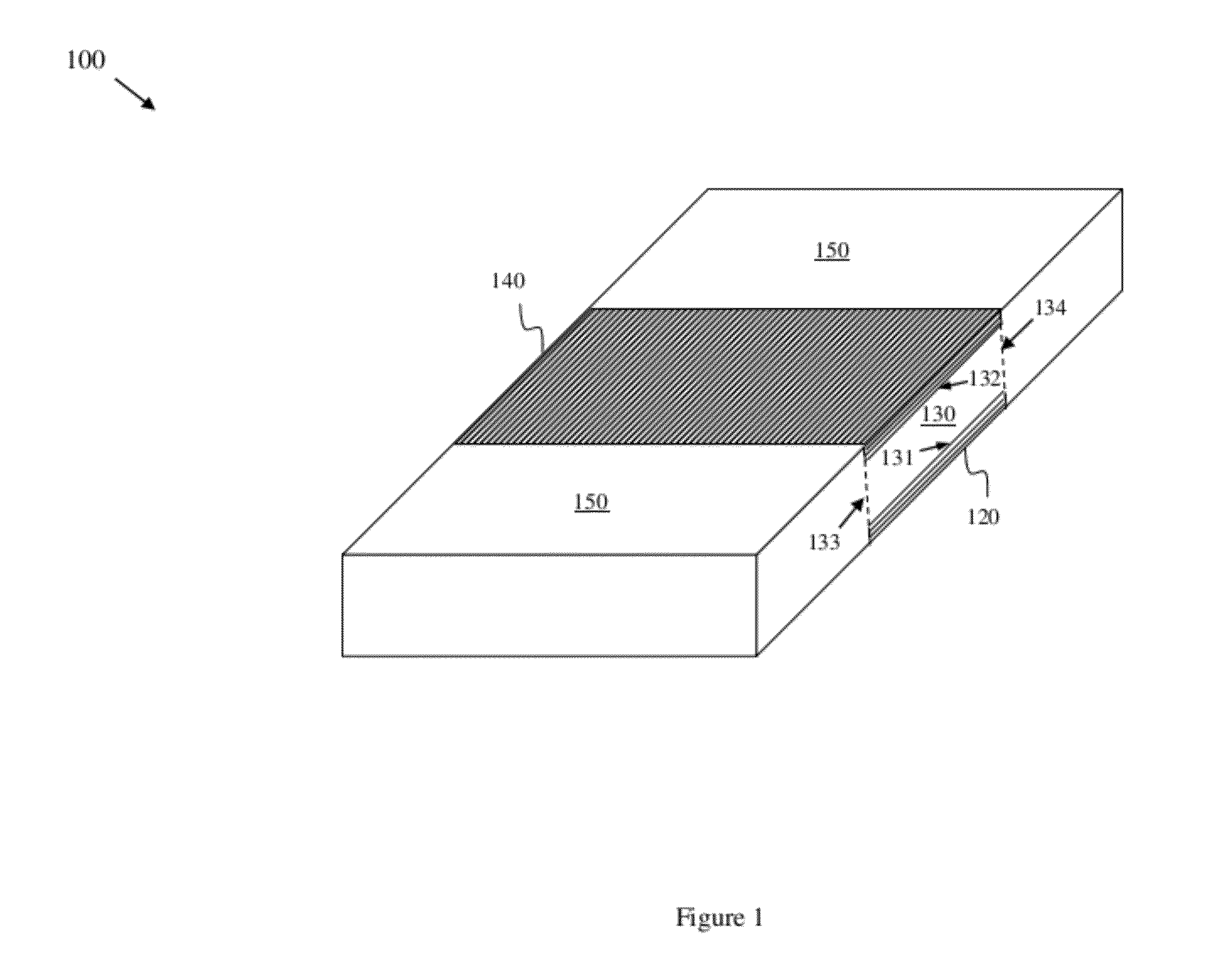

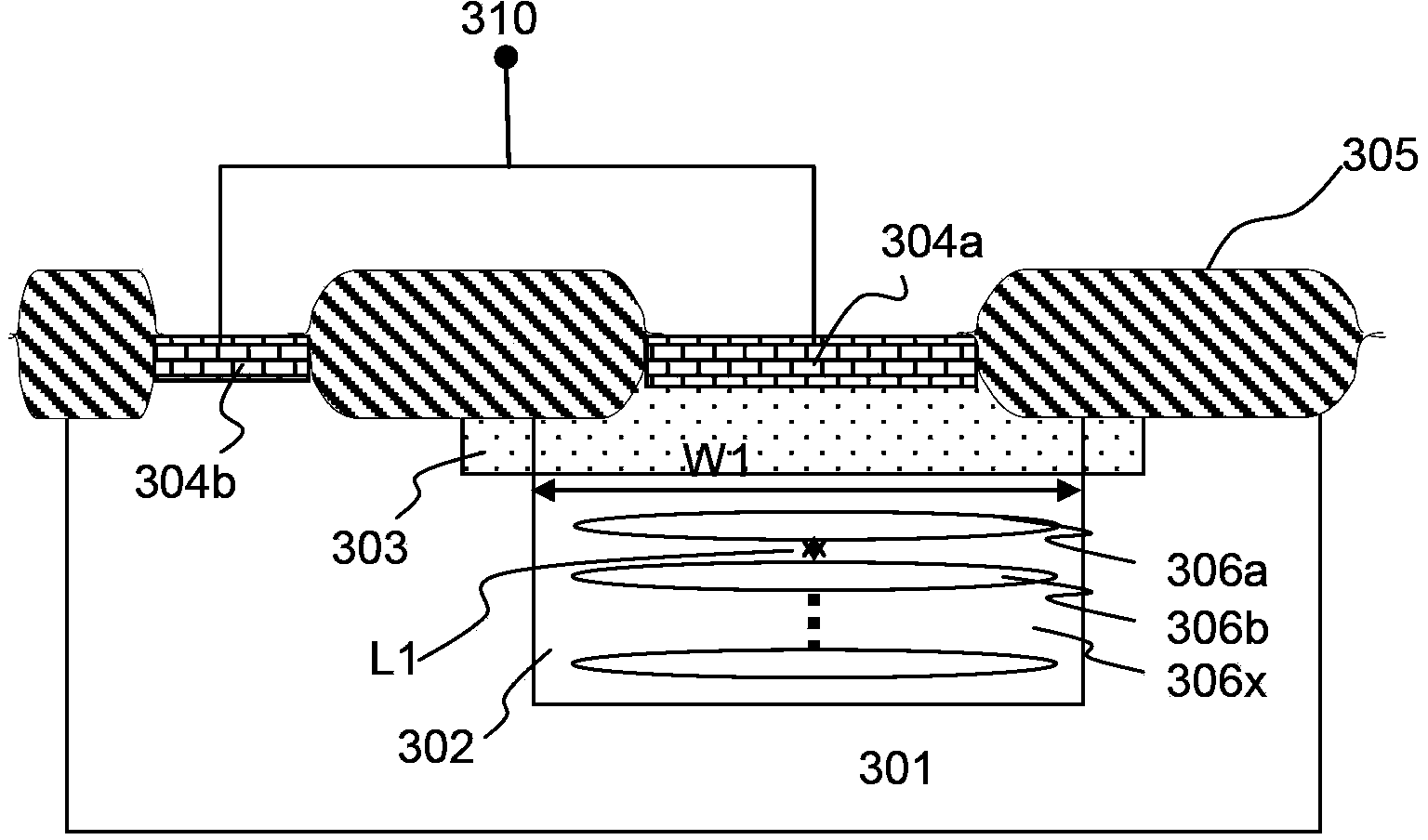

Junction field effect transistor structure with p-type silicon germanium or silicon germanium carbide gate(s) and method of forming the structure

ActiveUS20120168820A1Faster pinchReduce voltageTransistorSemiconductor/solid-state device manufacturingHeterojunctionDopant

Disclosed are embodiments of a junction field effect transistor (JFET) structure with one or more P-type silicon germanium (SiGe) or silicon germanium carbide (SiGeC) gates (i.e., a SiGe or SiGeC based heterojunction JFET). The P-type SiGe or SiGeC gate(s) allow for a lower pinch off voltage (i.e., lower Voff) without increasing the on resistance (Ron). Specifically, SiGe or SiGeC material in a P-type gate limits P-type dopant out diffusion and, thereby ensures that the P-type gate-to-N-type channel region junction is more clearly defined (i.e., abrupt as opposed to graded). By clearly defining this junction, the depletion layer in the N-type channel region is extended. Extending the depletion layer in turn allows for a faster pinch off (i.e., requires lower Voff). P-type SiGe or SiGeC gate(s) can be incorporated into conventional lateral JFET structures and / or vertical JFET structures. Also disclosed herein are embodiments of a method of forming such a JFET structure.

Owner:GLOBALFOUNDRIES US INC

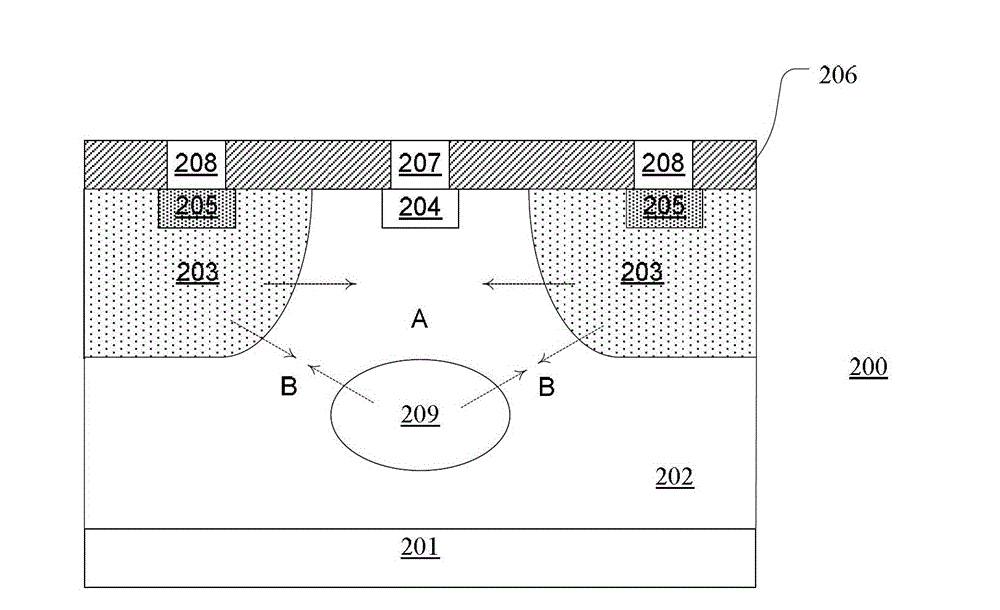

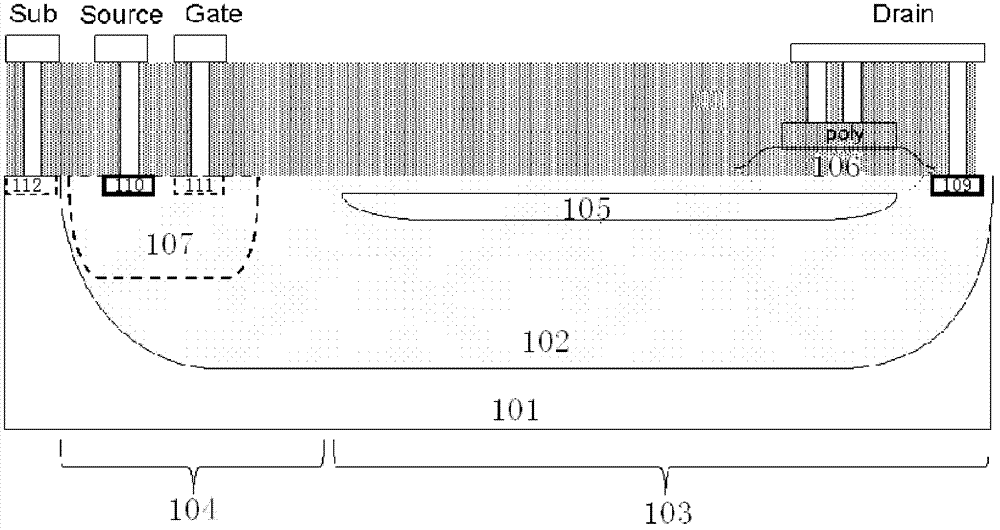

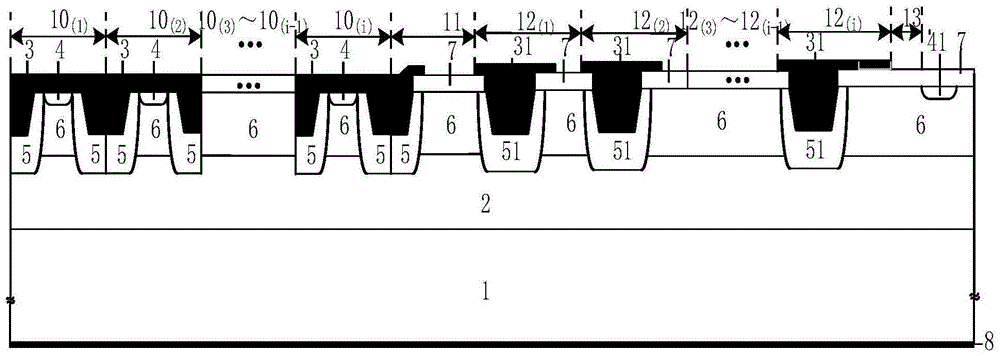

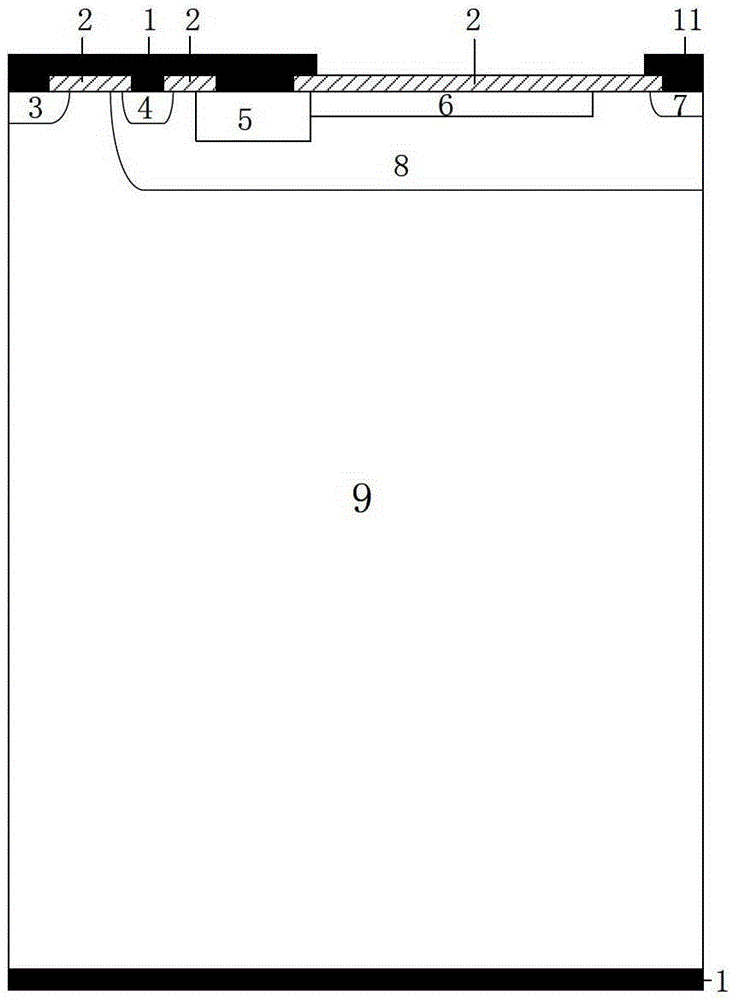

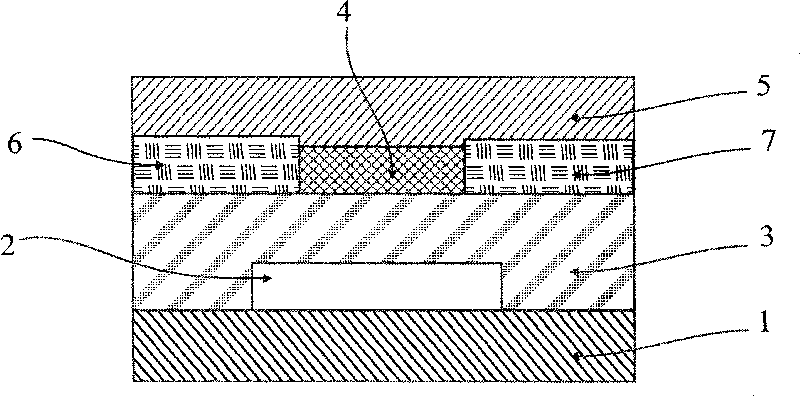

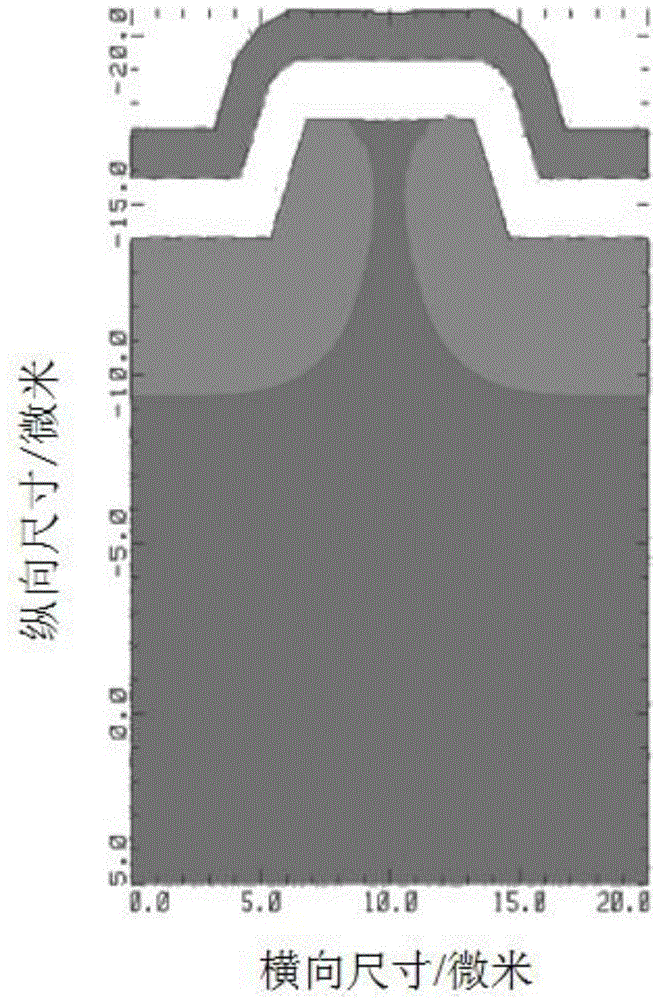

Pinch-off voltage reducing structure of dual-channel high voltage junction field effect transistor (FET) and manufacturing method thereof

ActiveCN103094319AEasy to run outLower pinch-off voltageSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorHigh pressure

The invention discloses a pinch-off voltage reducing structure of a dual-channel high voltage junction field effect transistor (FET) and a manufacturing method of the pinch-off voltage reducing structure of the dual-channel high voltage junction FET. A well region provided with a channel region and a drift region is formed in a silicon substrate, a drift region inversion layer is arranged in the drift region, a gate region is formed on the outer side of the channel region, a channel region inversion layer is arranged in the channel region, the transverse width of the channel region inversion layer is longer than the transverse width of the channel region, and two ends of the channel region inversion layer are connected with the gate region. A drain electrode leading-out terminal is formed in the drift region, a source electrode leading-out terminal is formed in the channel region, a gate electrode leading-out terminal is formed in the gate region, and a substrate leading-out terminal is formed in the substrate region. The drift region, the drain electrode leading-out terminal and the source electrode leading-out terminal are in a second conductivity type, the substrate, the drift region inversion layer, the channel region inversion layer, the gate region, the gate leading-out terminal and the substrate leading-out terminal are in a first conductivity type, and electrodes are led out from the leading-out terminals. According to the pinch-off voltage reducing structure of the dual-channel high voltage junction FET and the manufacturing method of the pinch-off voltage reducing structure of the dual-channel high voltage junction FET, impurities which are opposite in type are implanted inside the channel region to form double channels, namely an upper channel and a lower channel, the opposite impurities are arranged in the channel region at the same time, and therefore each channel can be exhausted more easily, and pinch-off voltage is lowered.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Vertical current regulative diode and manufacturing method thereof

InactiveCN105206682ALower pinch-off voltageGood constant current characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesNegative feedbackVoltage drop

The invention relates to semiconductor technologies, in particular to a vertical current regulative diode and a manufacturing method thereof. The vertical current regulative diode comprises an oxide layer, a highly-doped N-type epitaxial layer, a lightly-doped N-type epitaxial layer, a heavily-doped N+ substrate and a metal anode which are sequentially arranged in a stacked mode. The vertical current regulative diode is characterized in that a resistor is additionally arranged to serve as a negative feedback structure. The vertical current regulative diode has the advantages that because the introduced resistor has a certain voltage drop when a device works, a channel can be pinched off more easily, the vertical current regulative diode can enter a constant current area rapidly, the breakdown voltage of the lateral current regulative diode is effectively increased, the lateral current regulative diode has a low pinch-off voltage, the constant current of the lateral current regulative diode is effectively increased, and the effective operating voltage range of the lateral current regulative diode is effectively widened. The method is especially suitable for the lateral current regulative diode.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

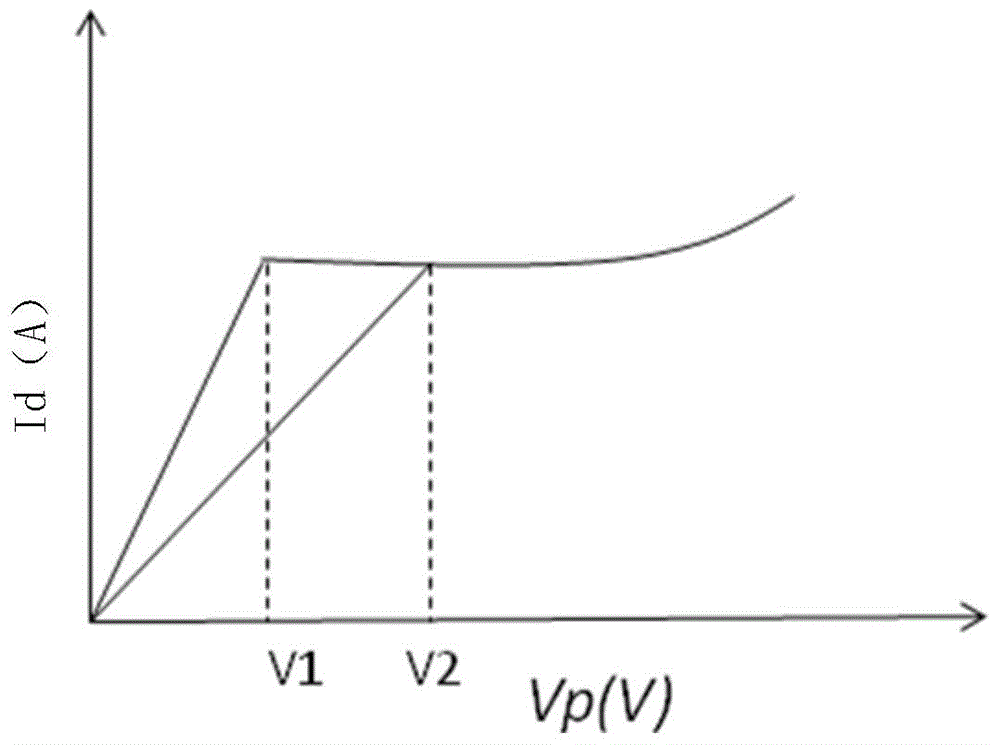

Transverse current regulator diode and manufacturing method thereof

InactiveCN105047724AEasy to pinch offLower pinch-off voltageSemiconductor/solid-state device manufacturingSemiconductor devicesVoltage dropEngineering

The invention belongs to the semiconductor power device technical field and relates to a transverse current regulator diode and a manufacturing method thereof. The transverse current regulator diode is characterized in that a negative feedback resistor is led into the source of an ordinary current regulator diode, so that the performance of the current regulator diode can be higher. The resistor led into the ordinary current regulator diode has a certain voltage drop when working, so that a channel will be pinched off more easily, and the current regulator diode can quickly enter a constant current region, and therefore, the breakdown voltage of the transverse current regulator diode can be effectively improved, and the transverse current regulator diode can have low pinch-off voltage, and the constant current of the transverse current regulator diode can be effectively improved, and the effective operating voltage range of the transverse current regulator diode can be effectively extended. The manufacturing method of the invention is especially suitable for transverse current regulator diodes.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Junction field effect transistor

ActiveCN104518008ALower pinch-off voltageUniform electric field distributionSemiconductor devicesPower flowJFET

The invention belongs to the semiconductor device field and discloses a junction field effect transistor. According to the junction field effect transistor, a back grid is formed between a trench and a P substrate of the JFET (junction type field effect transistor) and is corresponding to the position of a positive grid, and as a result, when negative voltage is applied to the grids, depletion regions of a positive grid PN junction and a negative grid PN junction do not horizontally extend, but vertically extend with the increase of the negative voltage, so that small pinch-off voltage can be obtained; drain-source voltage is mainly borne by horizontal extension of the depletion regions, and P type lightly-doped regions which are adjacent to a source are formed between the trench and the P substrate of the JFET, so that the distribution of an electric field in the trench of the JFET is more uniform, and N type lightly-doped regions which are located below a drain are formed between the trench and the P substrate of the JFET, and thus, breakdown of a PN junction formed by the trench and the P substrate of the JFET, which occurs at the bottom of a drain end, can be avoided, and as a result, high drain-source breakdown voltage can be obtained. With the junction field effect transistor adopted, contradictions among three parameters, namely, the pinch-off voltage, the drain-source breakdown voltage and current conduction capacity, can be alleviated.

Owner:FOUNDER MICROELECTRONICS INT

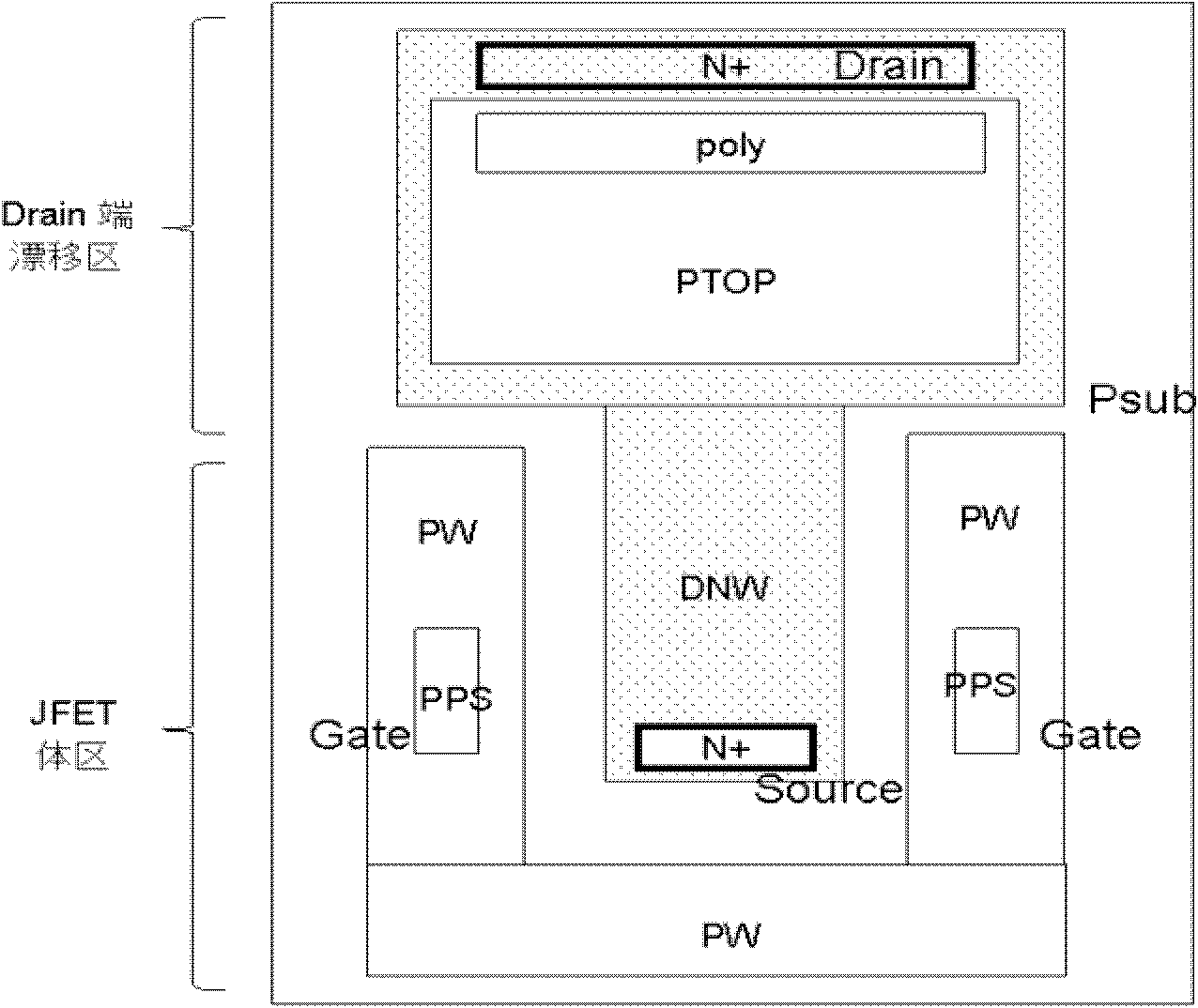

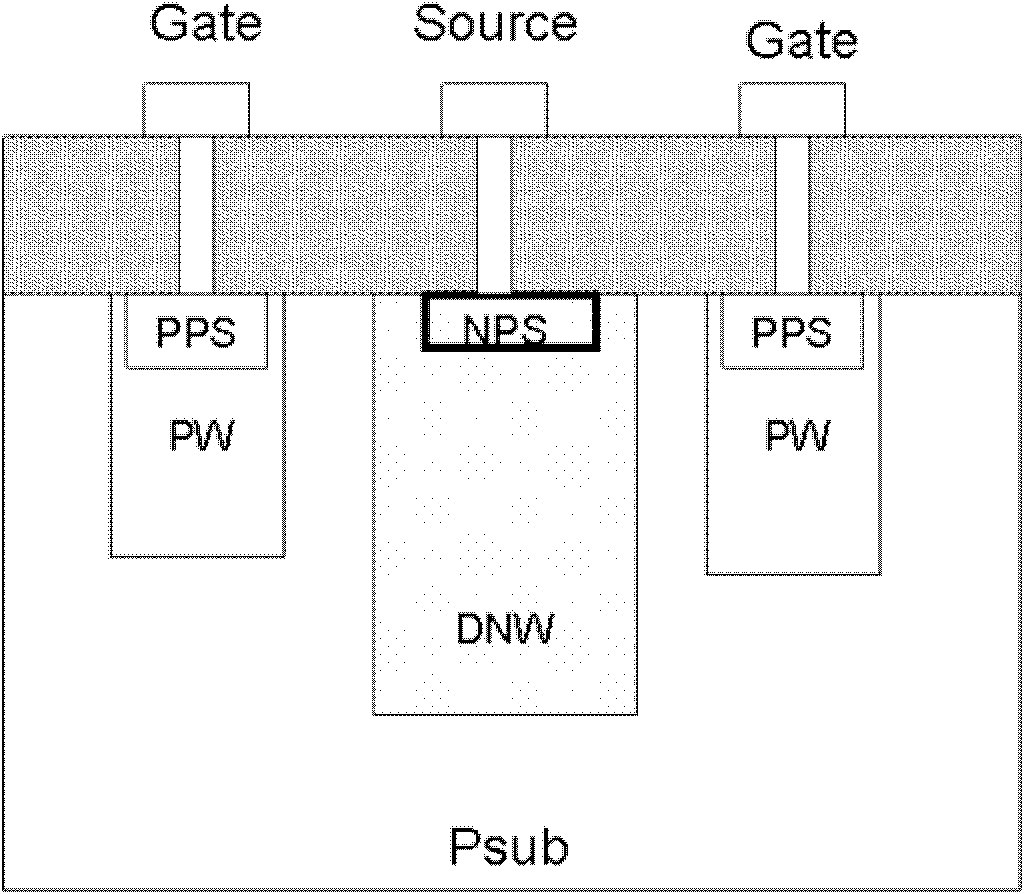

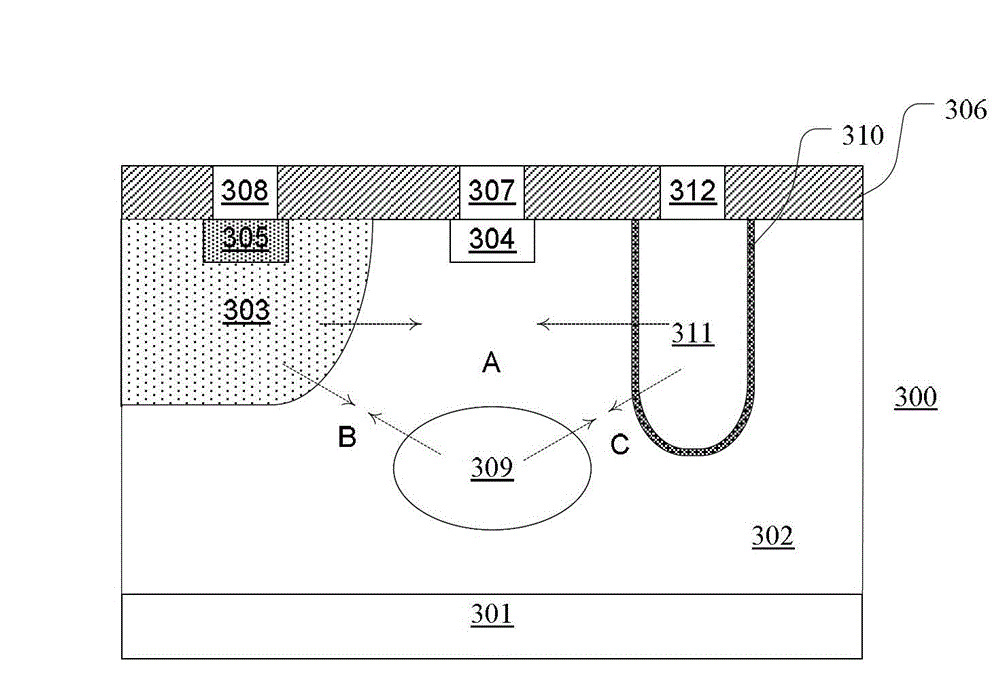

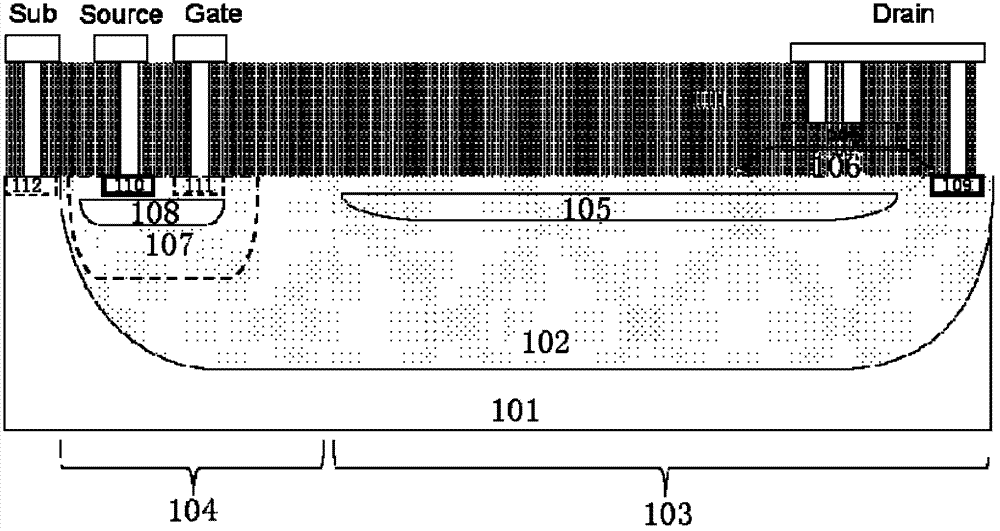

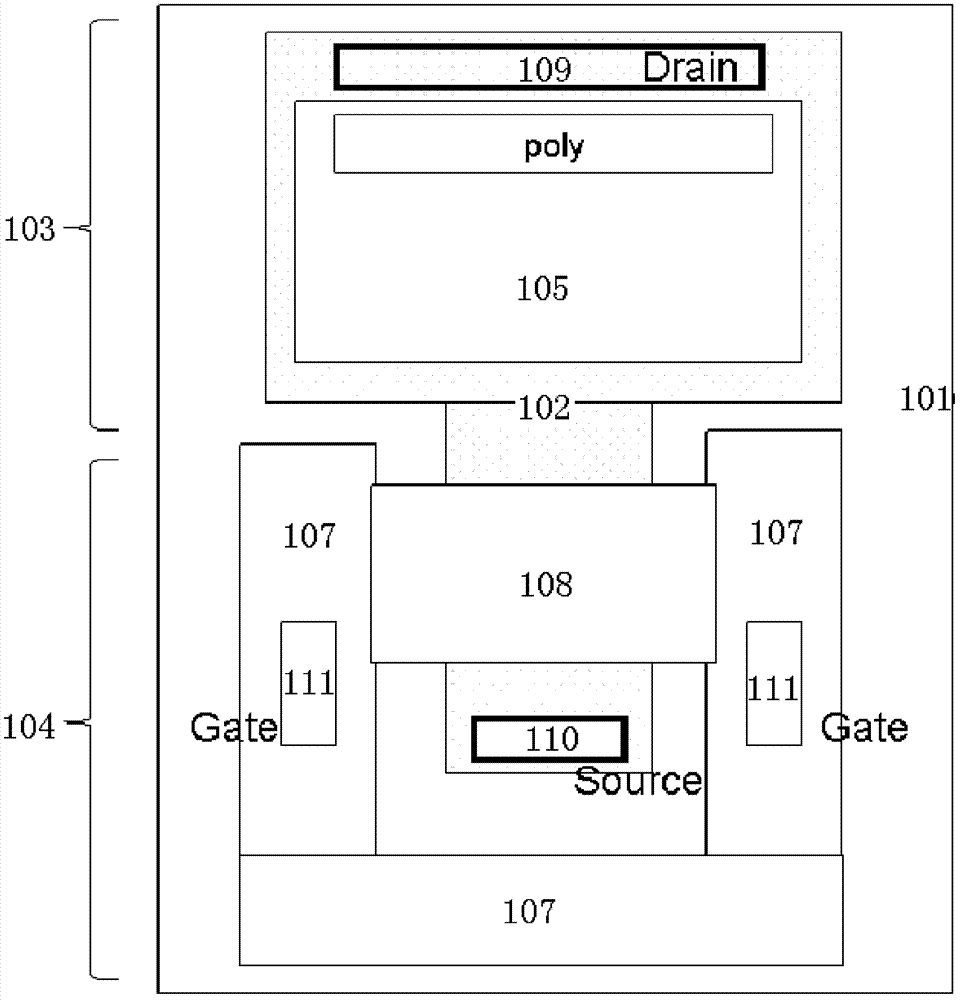

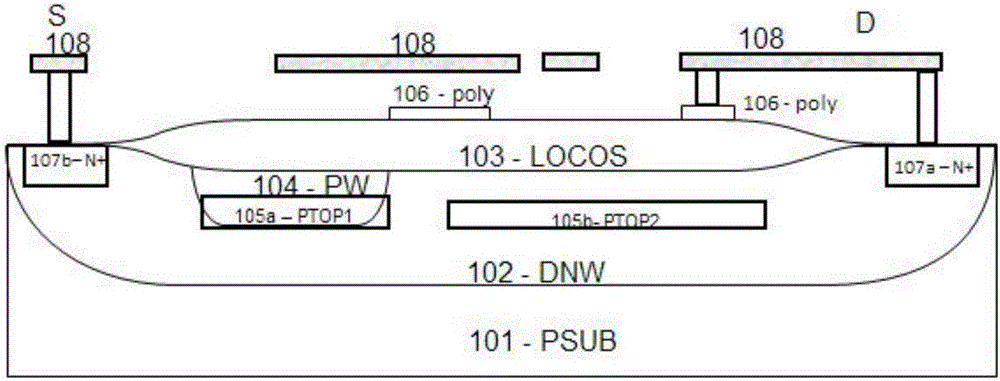

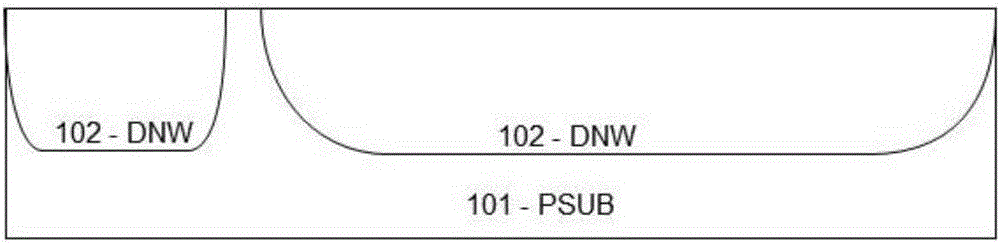

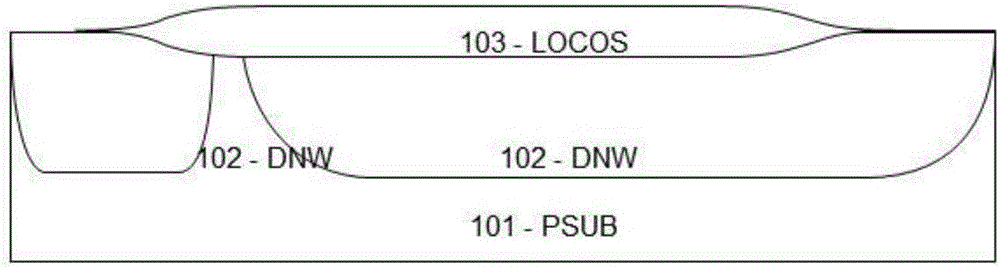

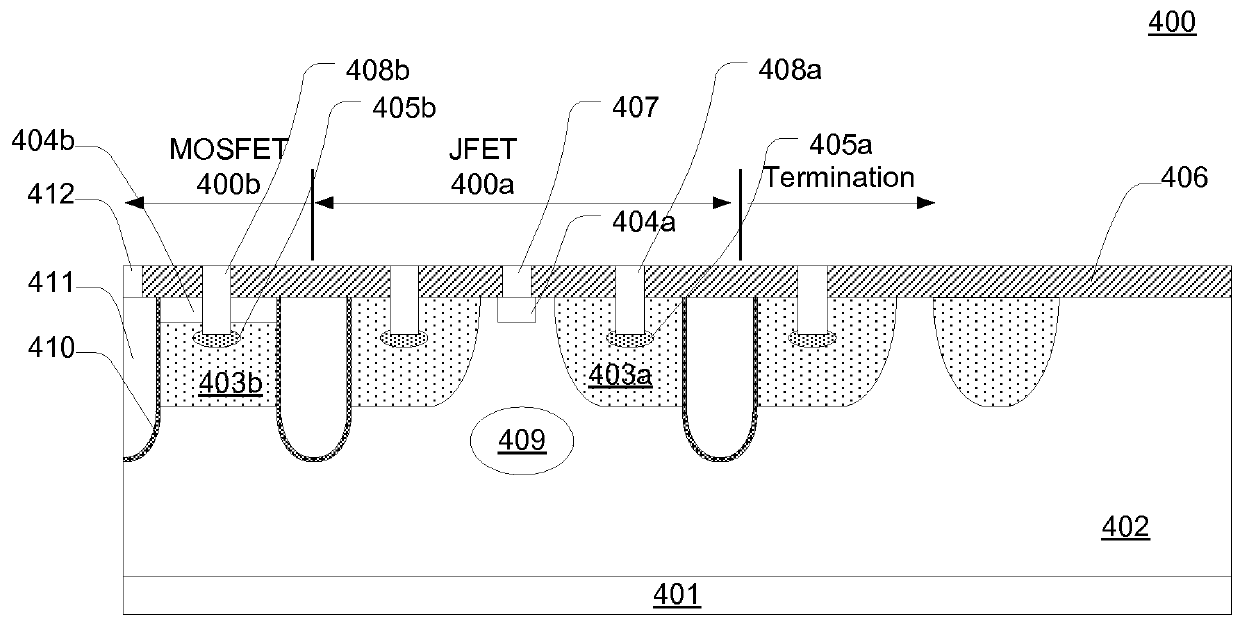

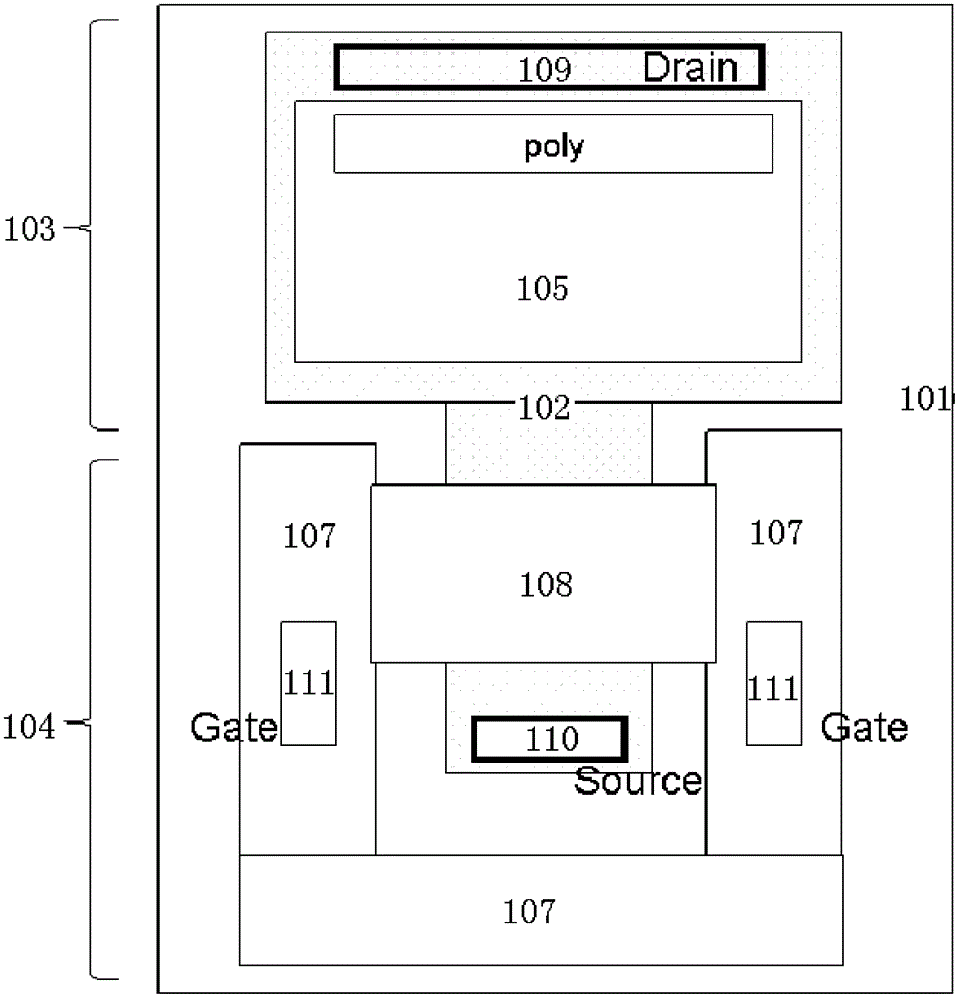

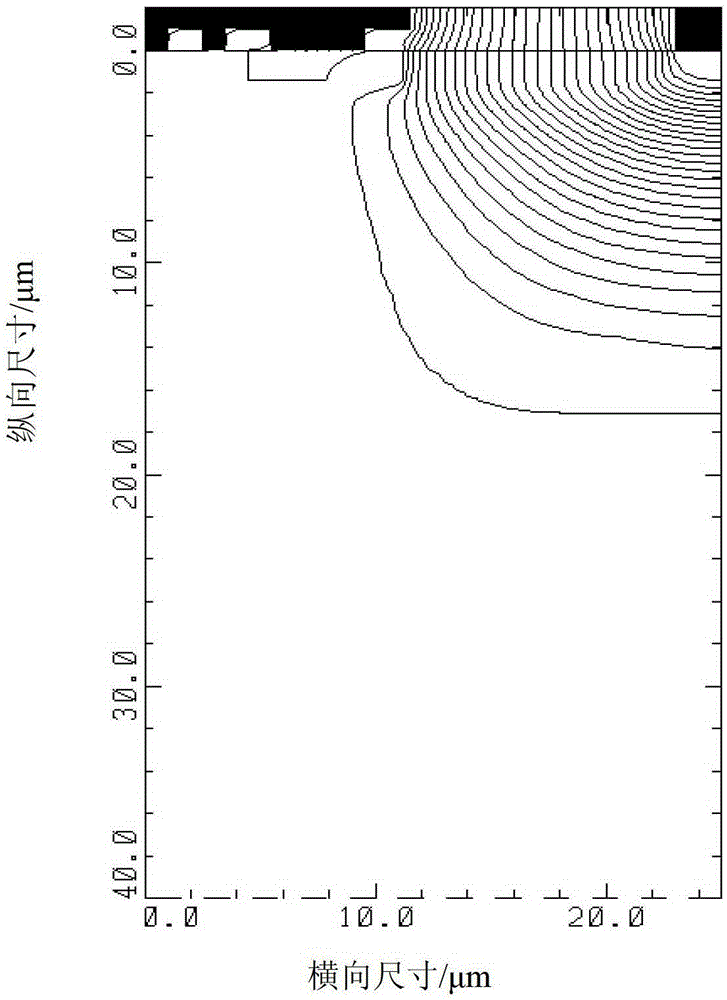

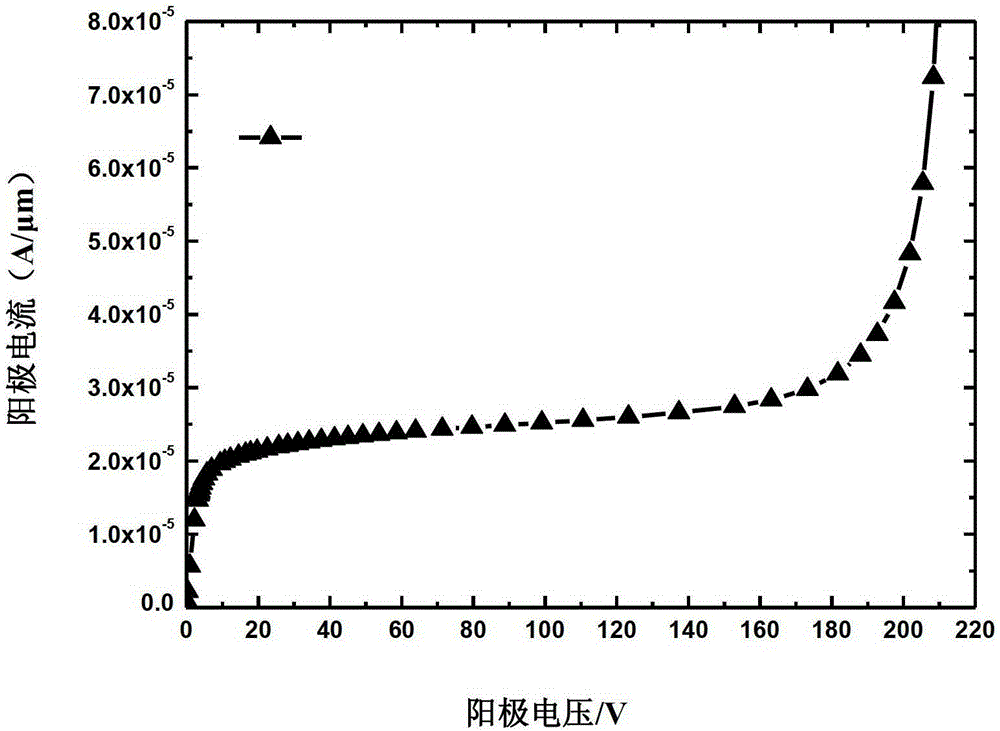

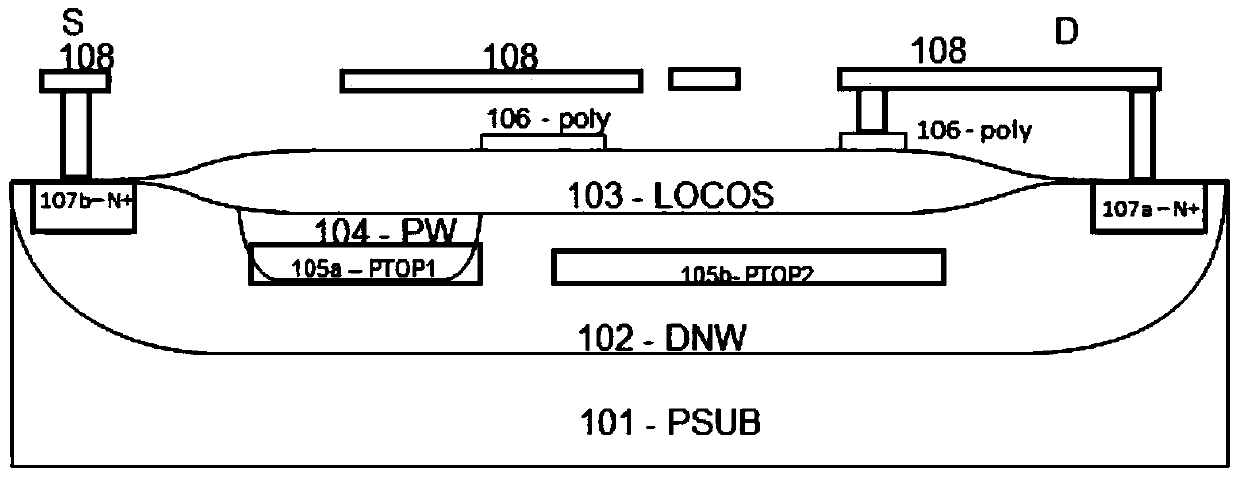

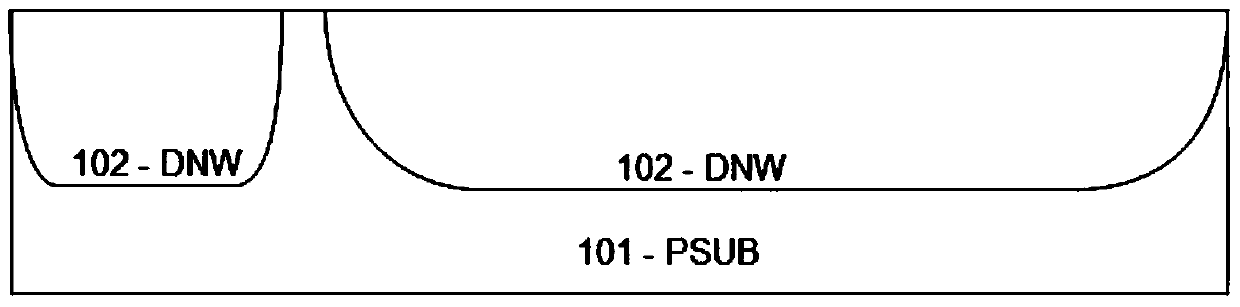

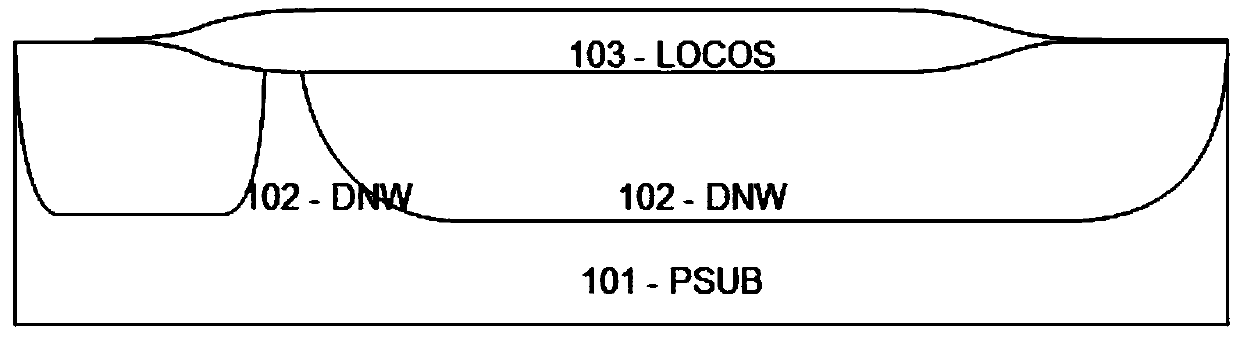

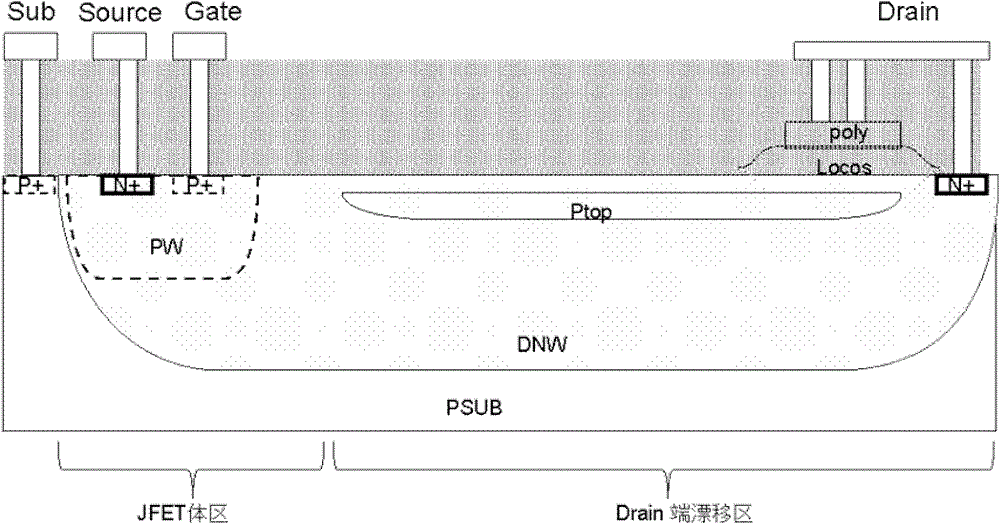

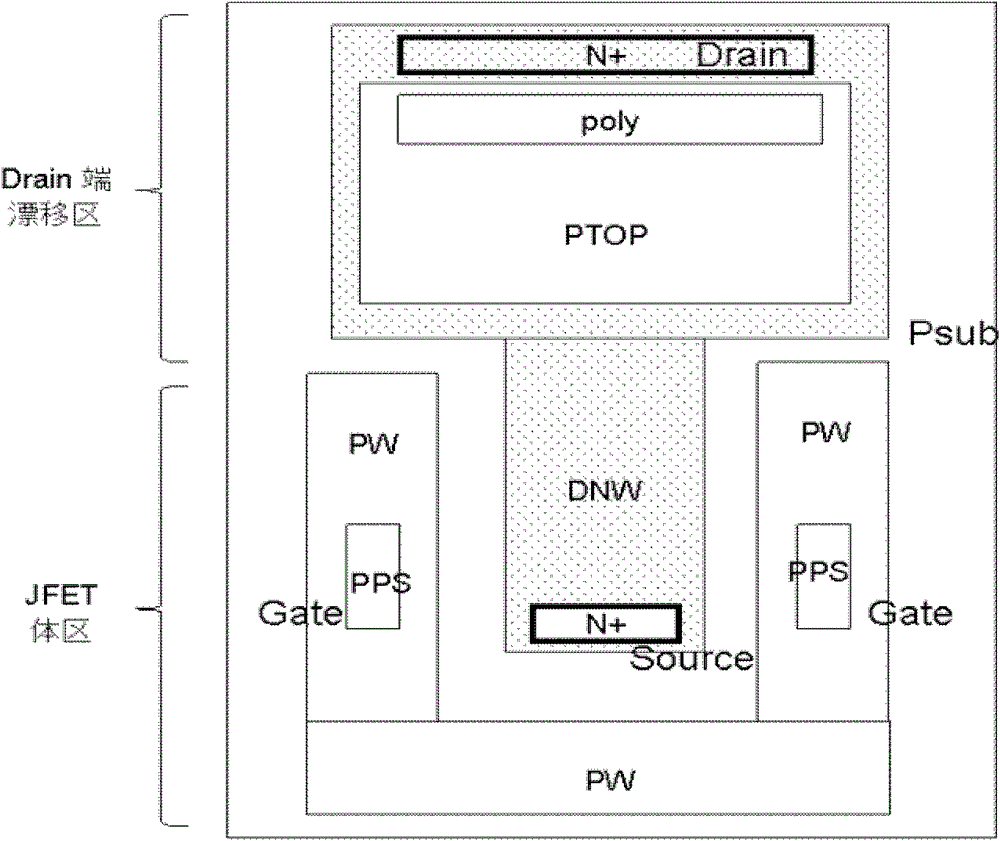

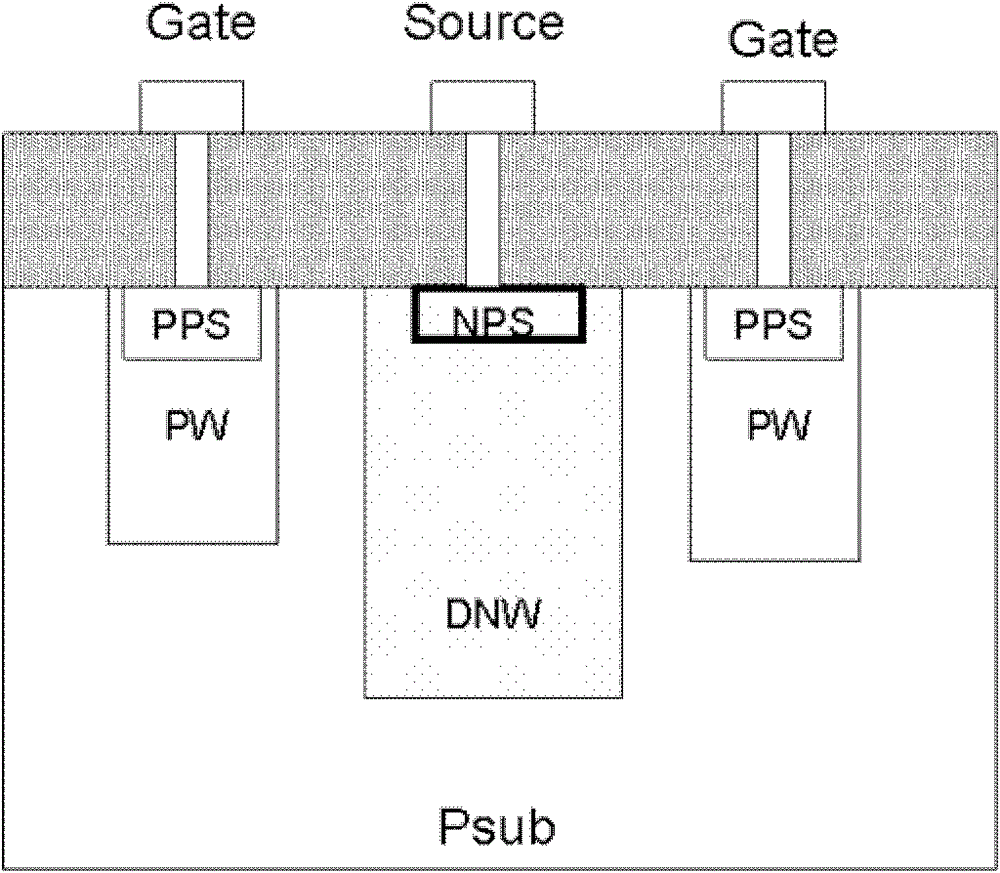

High voltage JFET device and processing method of the same

ActiveCN105914238AImprove breakdown voltageReduce N-type impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSource area

The invention discloses a high voltage JFET device and a processing method of the same. A P substrate is provided with a deep N-well. From a cutaway view angle, a field oxide is on the deep N-well, and the two ends of the field oxide are a JFET source area and a drain area. The field oxide is covered with a poly-silicon field plate. The deep N-well is divided into two sections: a first deep N-well section and a second deep N-well section wherein the first deep N-well section contains the JFET source area and the second deep N-well section contains the JFET drain area and a P injection layer. The first deep N-well section and the second deep N-well section are independent from each other. Between the first deep N-well section and the second deep N-well section is a P-well. The P-well shares the sizes with both the two deep N-well sections. Also between the first deep N-well section and the second deep N-well section is the P injection layer. The P injection layer, right under the P well, also shares sizes with with both the two deep N-well sections. The JFET device provided by the invention is provided with adjustable pinch-off voltage and at the same time, with high breakdown voltage as well. The invention also discloses a processing method for such a high voltage JFET device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

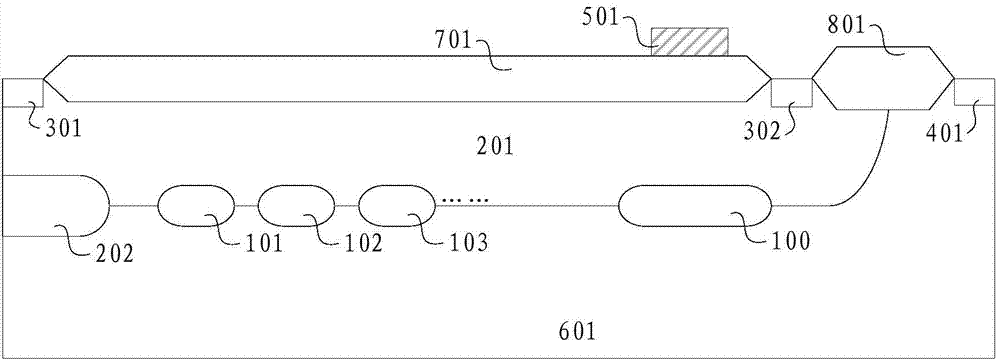

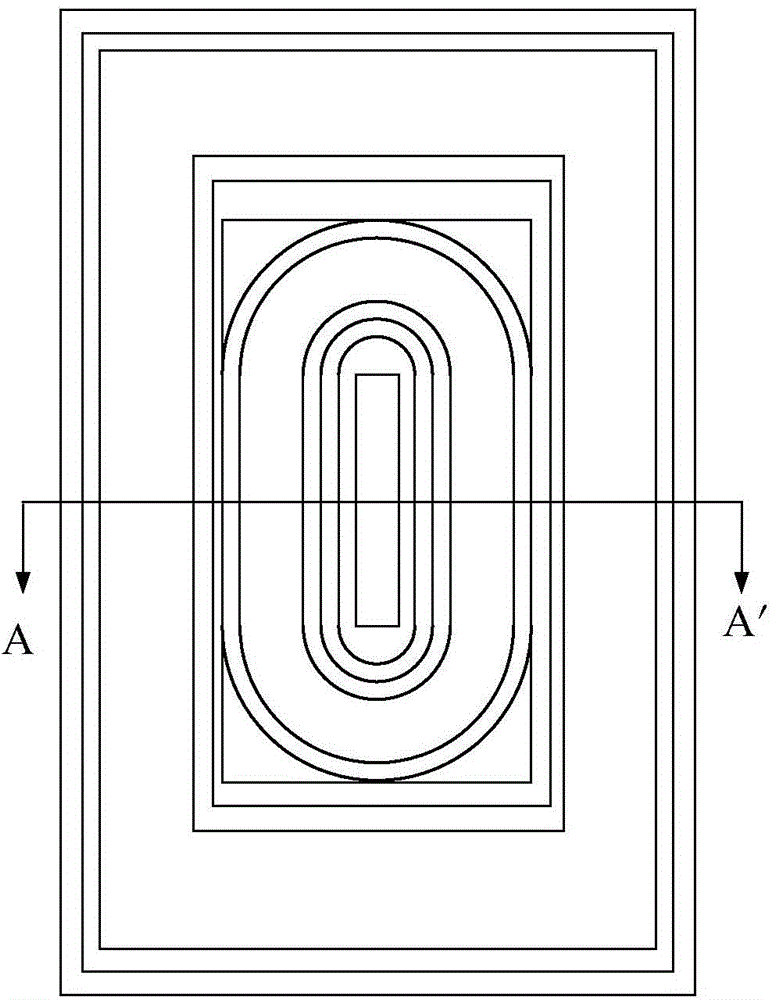

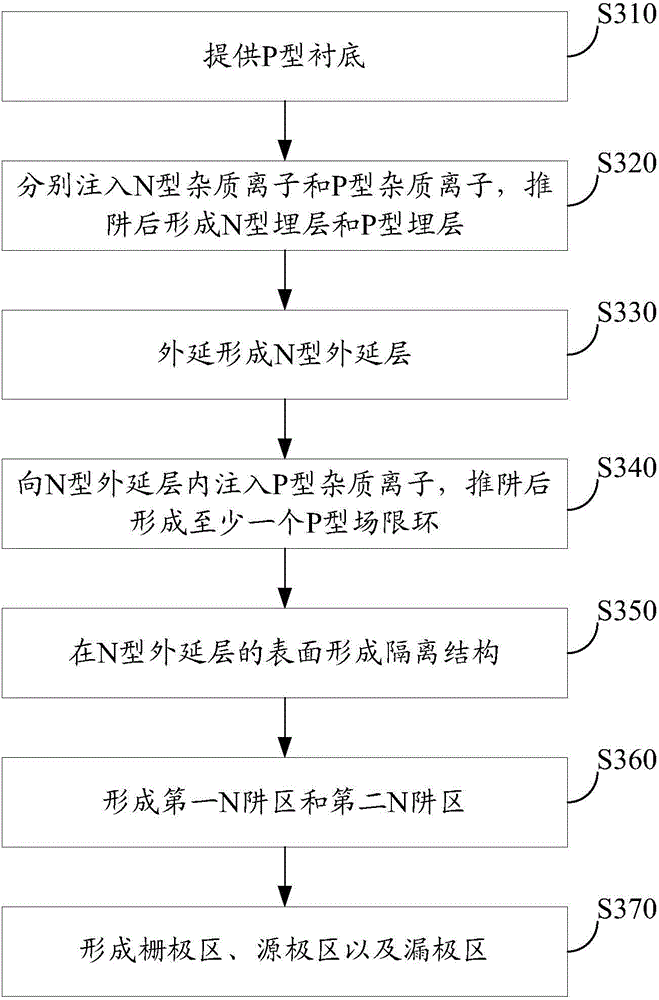

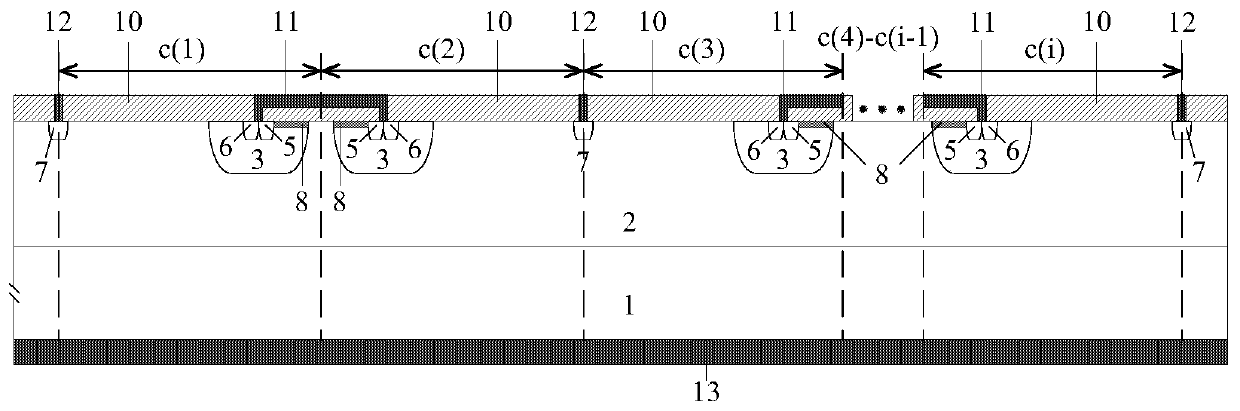

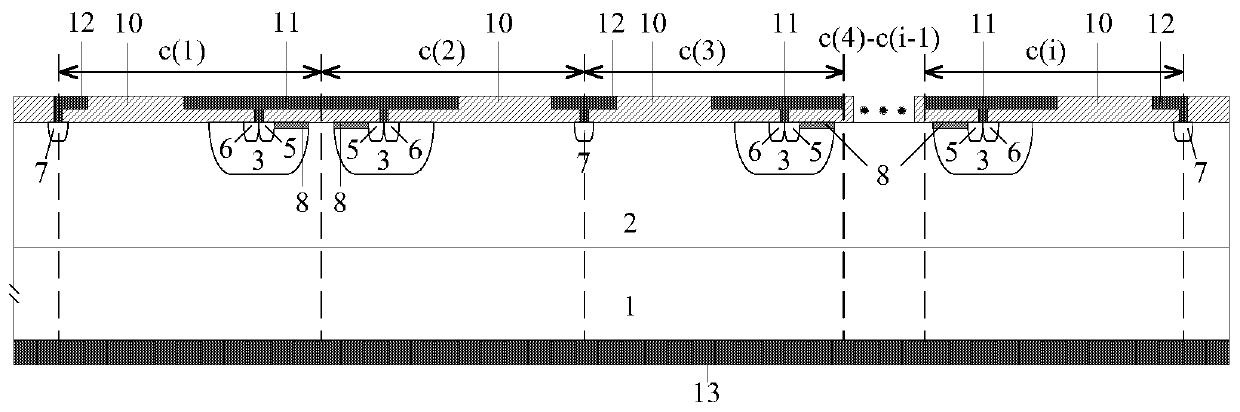

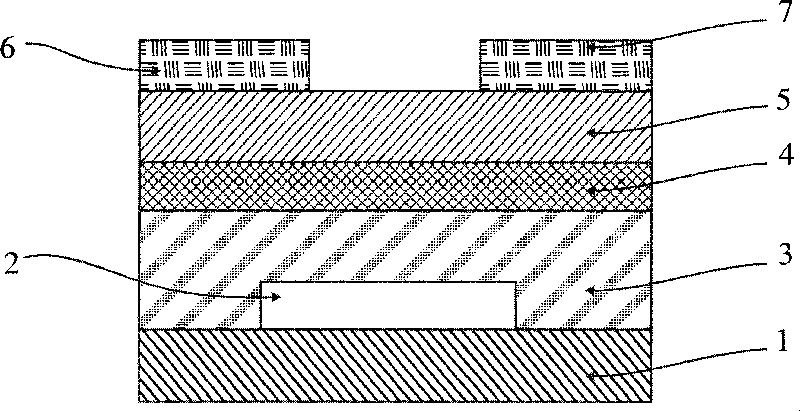

Junction field effect transistor and preparation method thereof

ActiveCN105140303AImprove high voltage blocking abilityLower pinch-off voltageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField-effect transistor

The present invention discloses a junction field effect transistor which comprises a P type substrate, a P type buried layer, N type buried layers arranged at two sides of the P type buried layer, an N type epitaxial layer, a first isolation structure, a second isolation structure, a third isolation structure and a fourth isolation structure which are arranged on the N type epitaxial layer, a source electrode area arranged between the first isolation structure and the second isolation structure, a first N well area arranged under the source electrode area, a gate electrode area arranged between the second isolation structure and the third isolation structure, a drain electrode area arranged between the third isolation structure and the fourth isolation structure, a second well area arranged under the source electrode area, and at least one P type field limit ring which is arranged above the N type epitaxial layer and is between the source electrode area and the drain electrode area. According to the above junction field effect transistor, the effect of Triple RESURF can be realized, the pinch-off voltage can be reduced effectively, and the purpose of low pinch-off voltage is realized. The invention also discloses the preparation method of the junction field effect transistor.

Owner:CSMC TECH FAB2 CO LTD

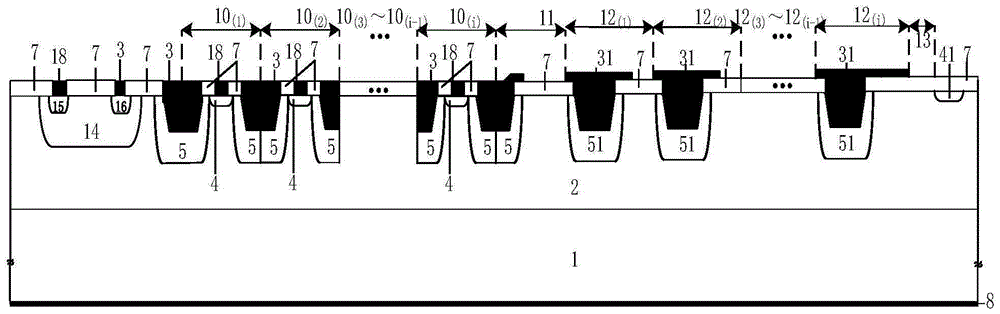

Semiconductor device and manufacturing method thereof

ActiveCN110534581AGood constant current effectIncrease exhaustSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialMetal electrodes

The invention provides a semiconductor device and a manufacturing method thereof, and belongs to the technical field of power semiconductors. The semiconductor device is formed by multiple interdigitally connected cells with the same structure / The cell structure comprises a second conductivity type light doped substrate, a first conductivity type light doped epitaxial layer, a diffusion second conductivity type well region, a first and third heavily doped regions having the first conductivity type, a second heavily doped region having the second conductivity type, a depletion type channel region, an oxide medium layer, a metal cathode, a metal anode and a back metal electrode. The forward withstand voltage and constant current characteristics of the device are optimally designed through the form of a metal field plate and injection of the second conductivity type doped region; the used second conductivity type light doped substrate has the effect of assisting the depletion of the first conductivity type light doped epitaxial layer and the conductive channel so as to improve the withstand voltage of the device and reduce the pinch-off voltage and realize better constant current capability and higher breakdown voltage; and finally the designed withstand voltage of the device is 460V and the pinch-off voltage is below 4V.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

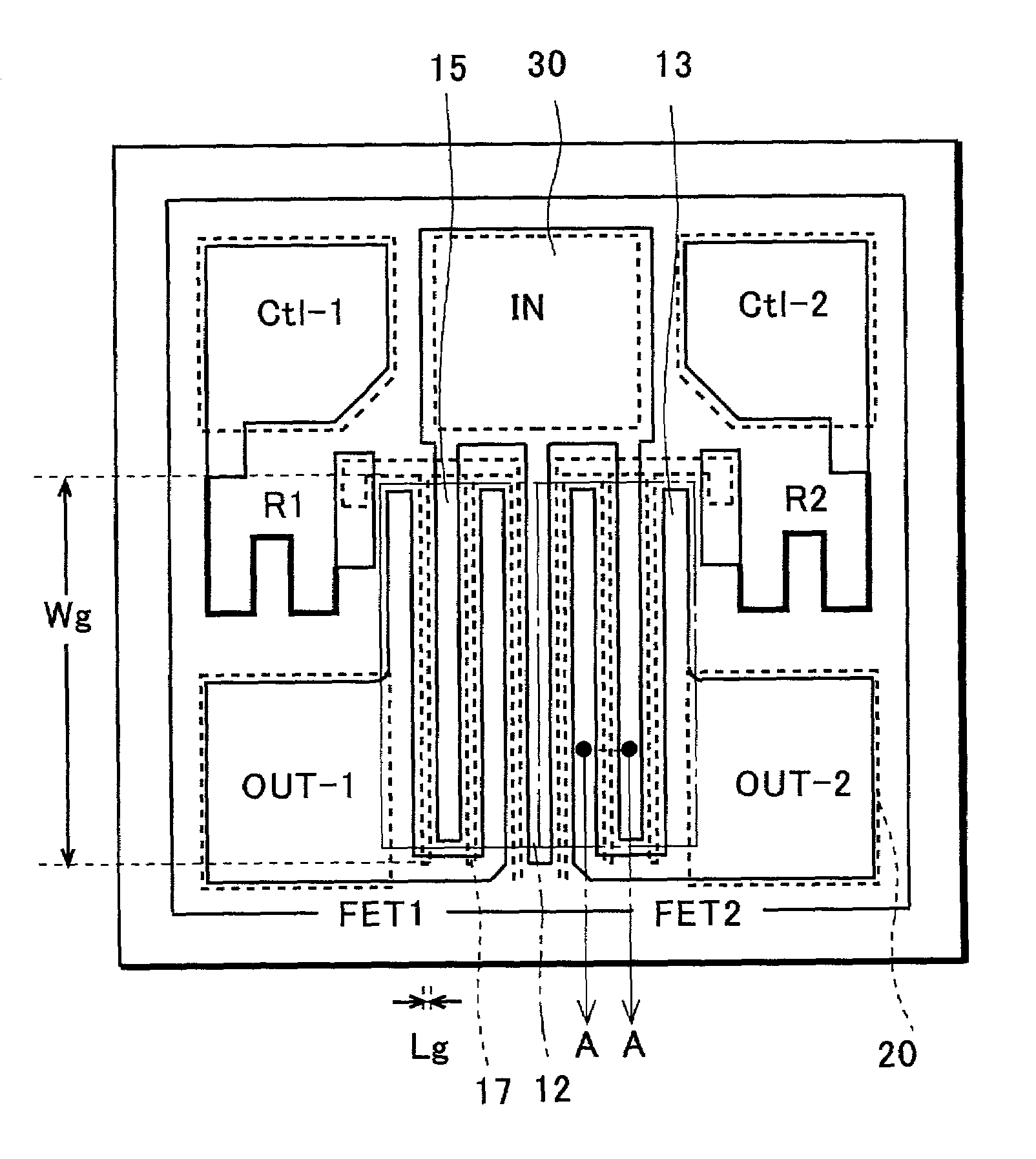

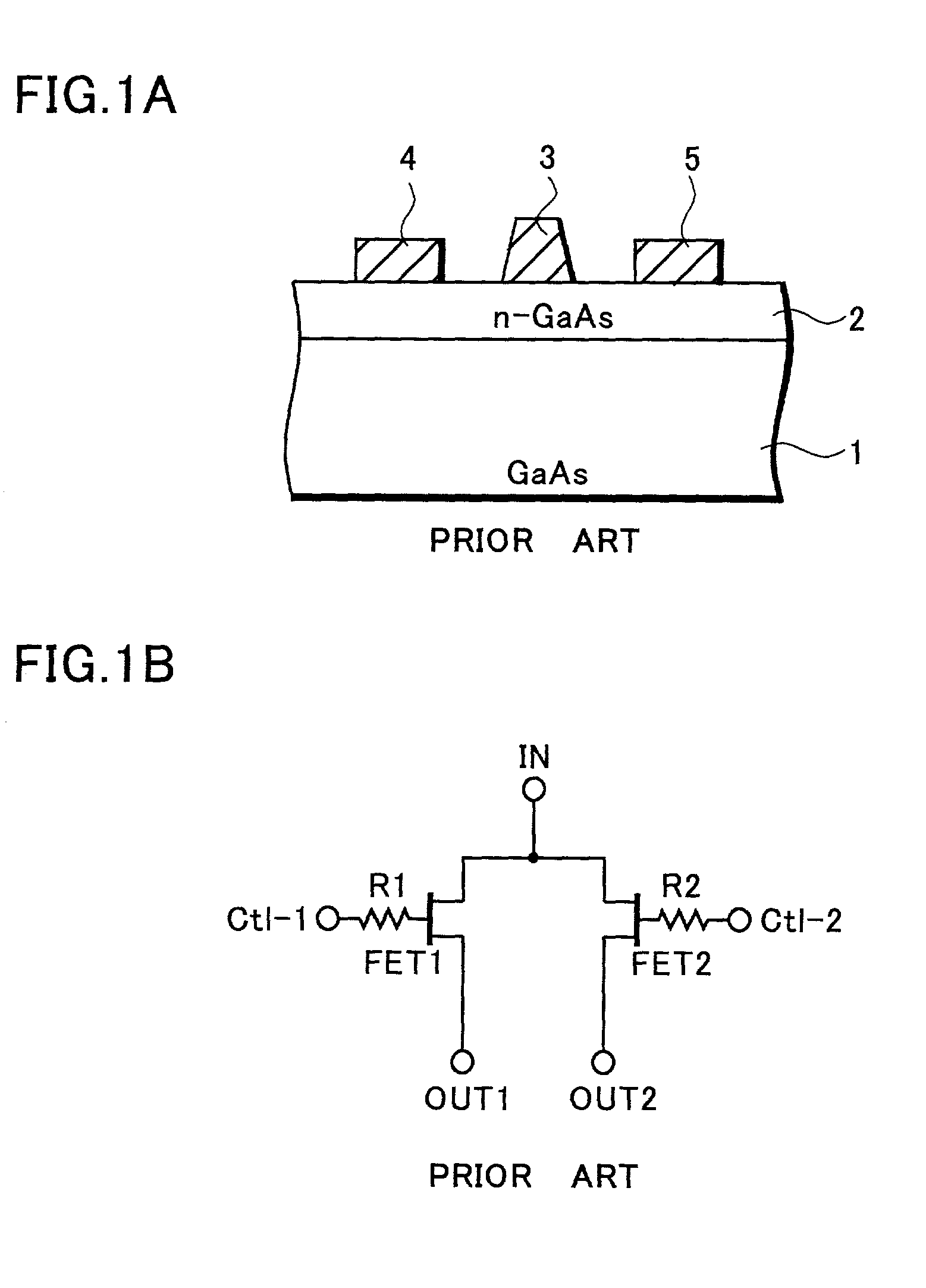

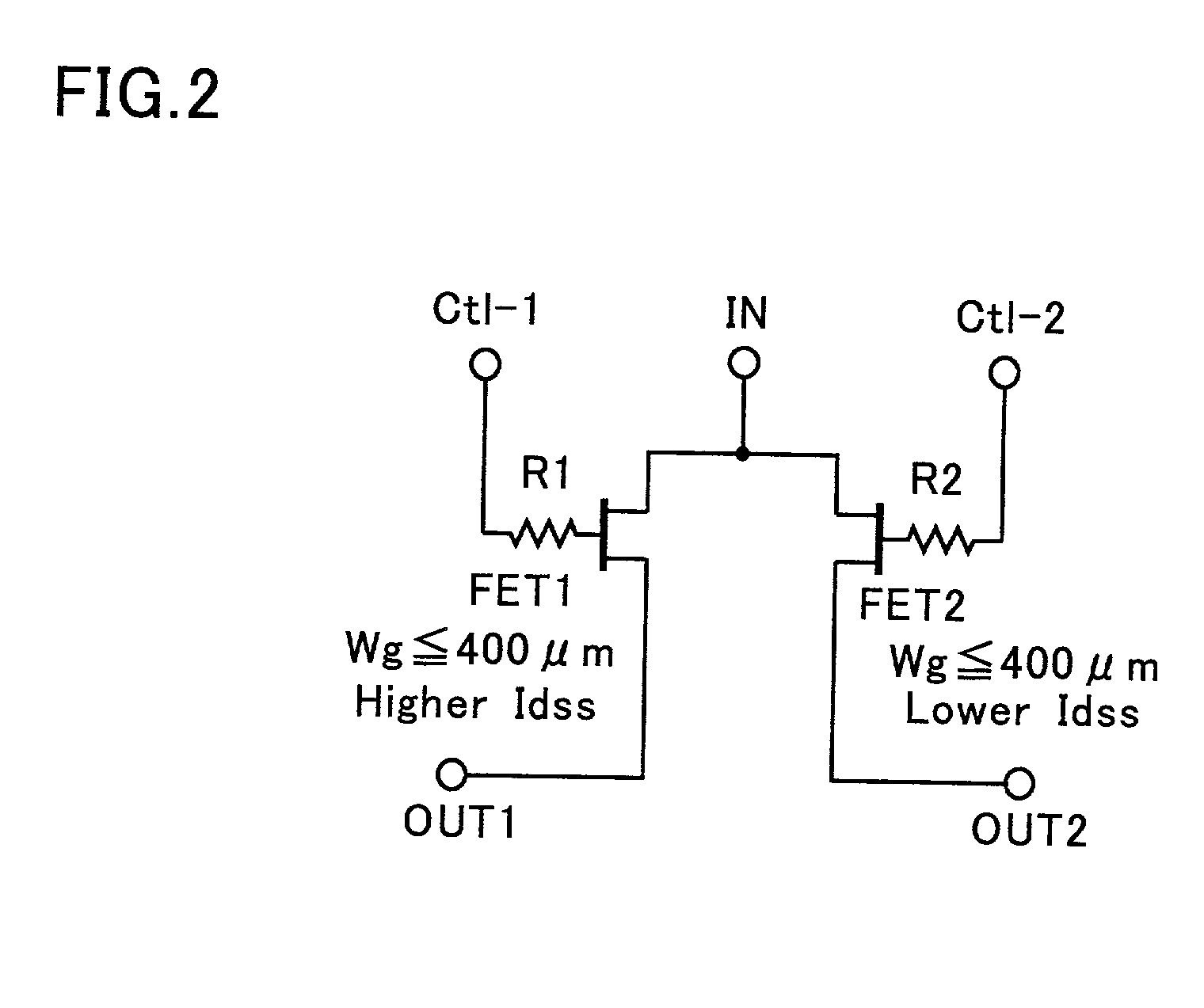

Semiconductor switching device

A semiconductor switching device includes two FETs with different device characteristics, a common input terminal, and two output terminals. The gate width of each FET is about 400 μm, and the maximum power required for the device operation is maintained by a lager conductivity of the channel layer of one FET and by a lower conductivity of the channel layer of another FET. The device operates at frequencies of 2.4 GHz or higher without use of shunt FET.

Owner:SEMICON COMPONENTS IND LLC

Epitaxial structure of the compound insulation layer nitride high-electronic transfer transistor and its making method

ActiveCN100485959CShorten speedShorten the lengthSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerHigh electron

The invention discloses a nitride high electron mobility ratio transistor extension configuration which adopts compound insulated layer and preparation method, by inserting GaN insulated layer between the AlGaN potential barrier layer and the insulated layer of the AlGaN / GaN high electron mobility ratio transistor, it can decrease the ratio that hot electron enters into the AlGaN potential barrier effectively, and decrease the dispersion of alloy, increase the transmission property of electron, so the frequency property of the transistor can be improved, besides it is good for the realization of component ohm contacting craft and decreasing the hardness of craft of producing high property component.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

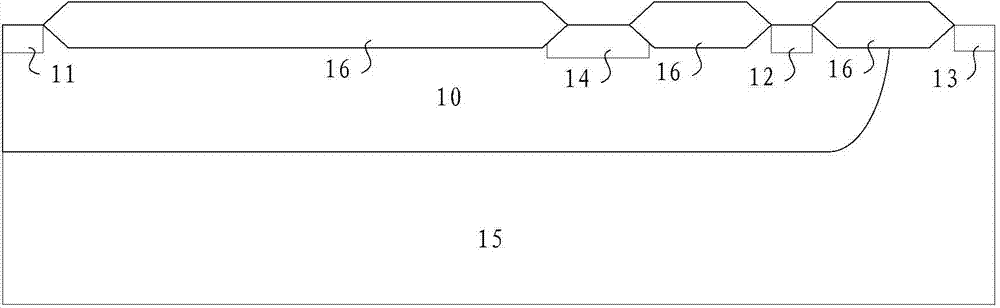

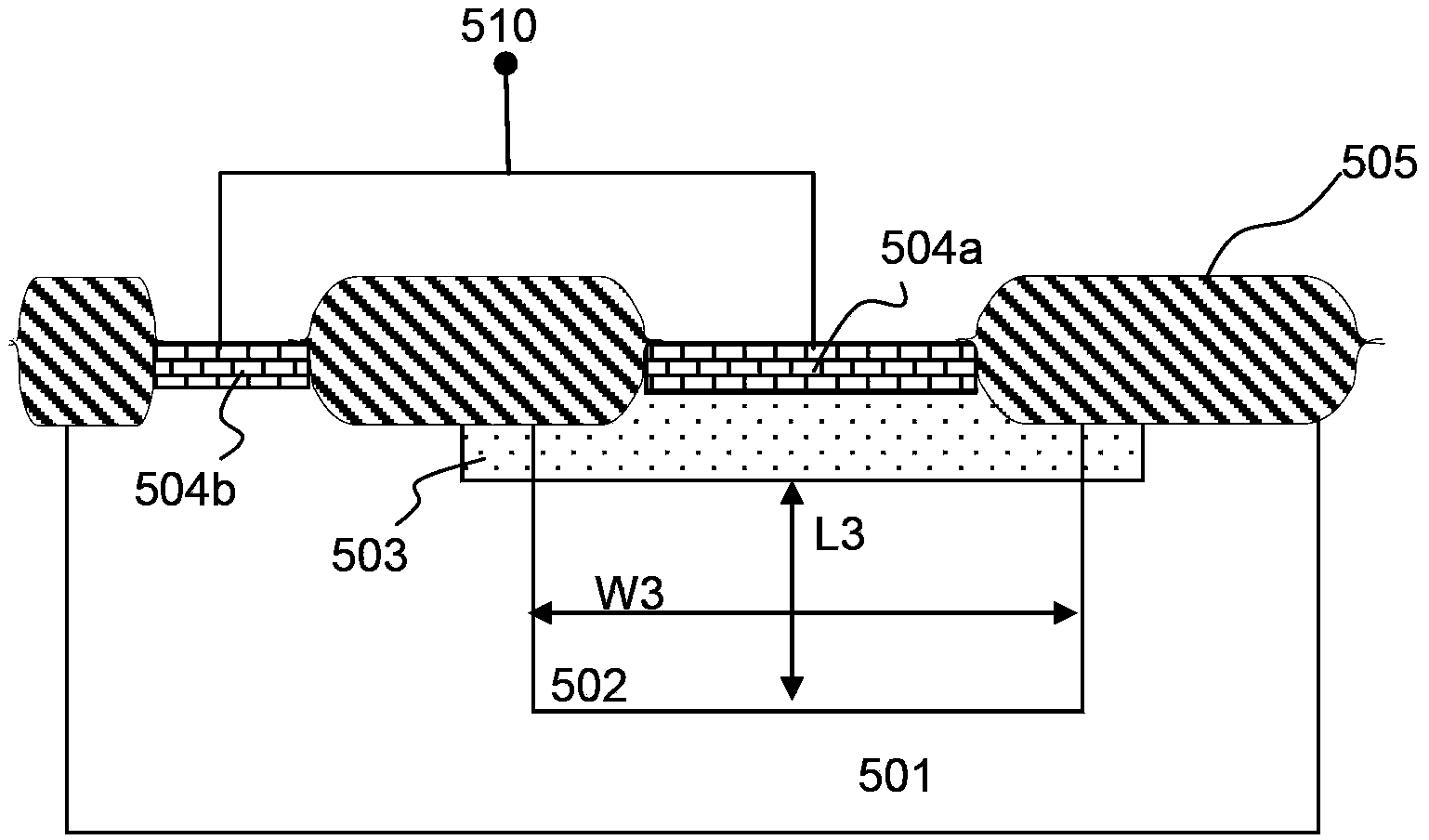

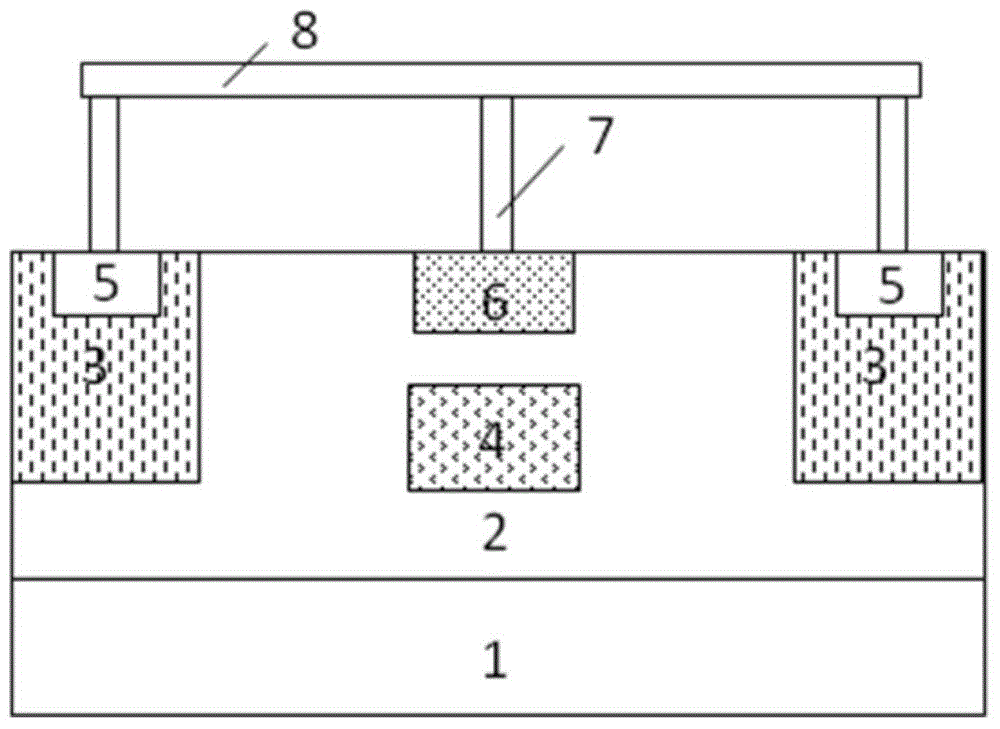

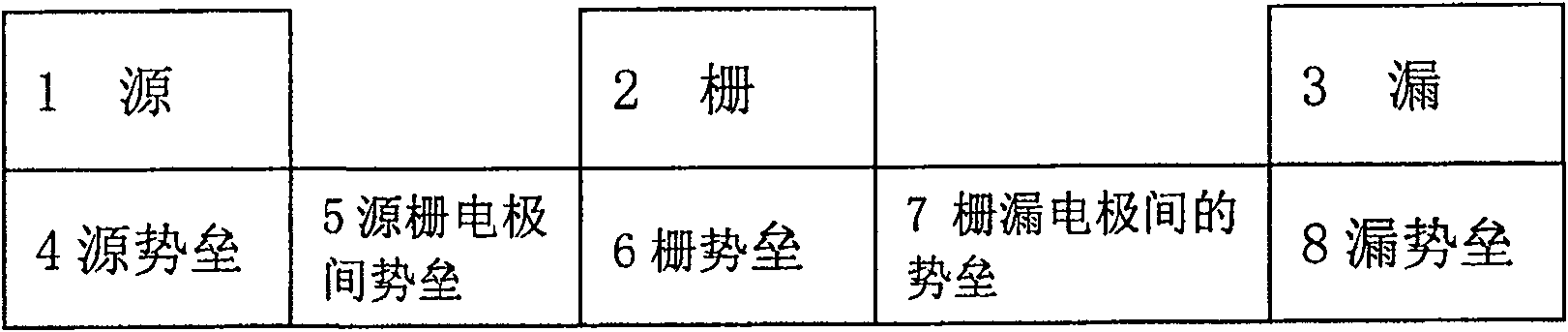

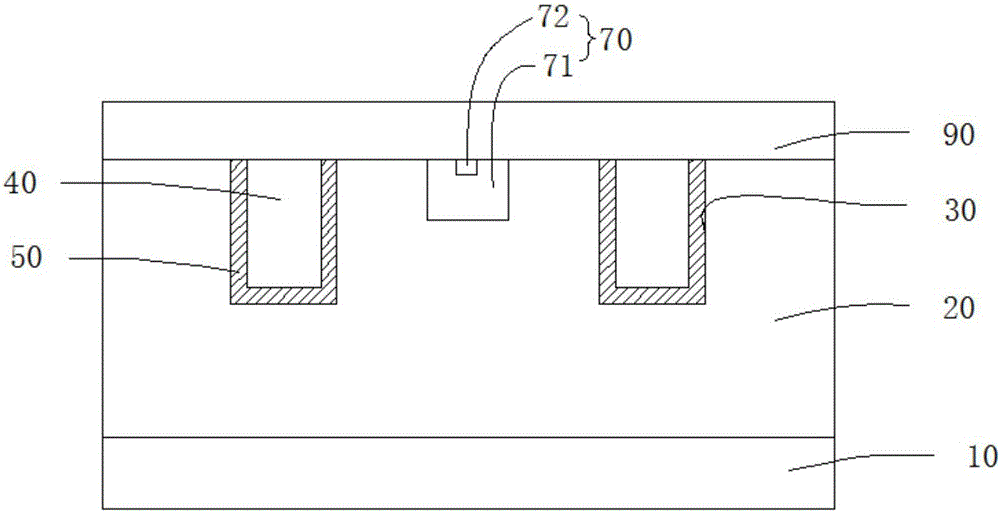

Junction field effect transistor and manufacturing method thereof

InactiveCN103730517AReduce doping concentrationLower pinch-off voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsVoltage

The invention discloses a junction field effect transistor. A channel region is arranged between two adjacent same-doped well regions, the channel region is doped through diffusion of the two adjacent well regions, and well regions with the opposite doping types are arranged above the channel region and used for longitudinal depleting the channel region. According to the junction field effect transistor, the doping concentration of the channel region can be reduced, the pinch-off voltage of the channel region is lowered, and thus the pinch-off voltage of the channel region can be adjusted, a small pinch-off voltage is obtained and extra cost does not need to be added. The width requirement of the channel region can be met just by adjusting the widths of the two adjacent same-doped well regions on the two sides of the channel region, and thus the channel current of the device can be adjusted; moreover, the channel current can be enlarged easily, and thus a large channel current is obtained. The invention further discloses a manufacturing method of the junction field effect transistor.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

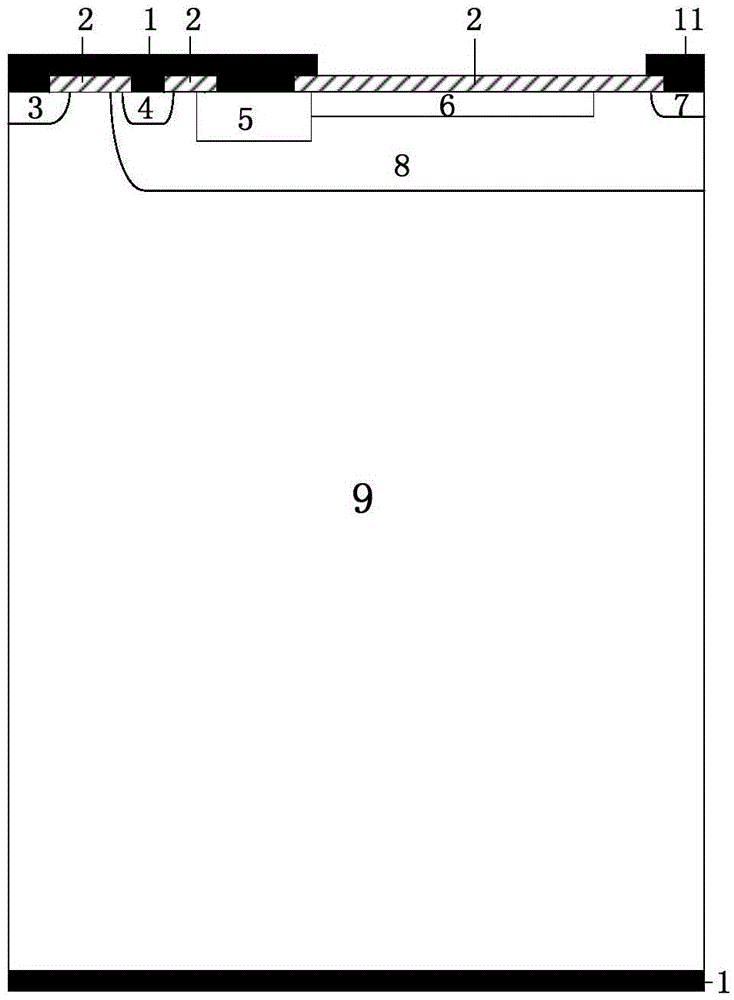

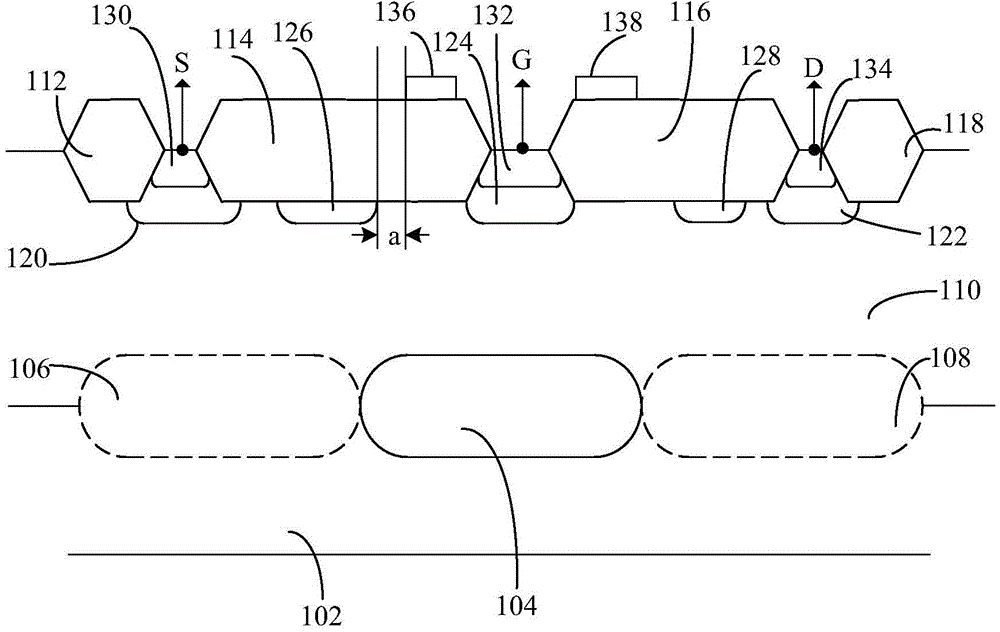

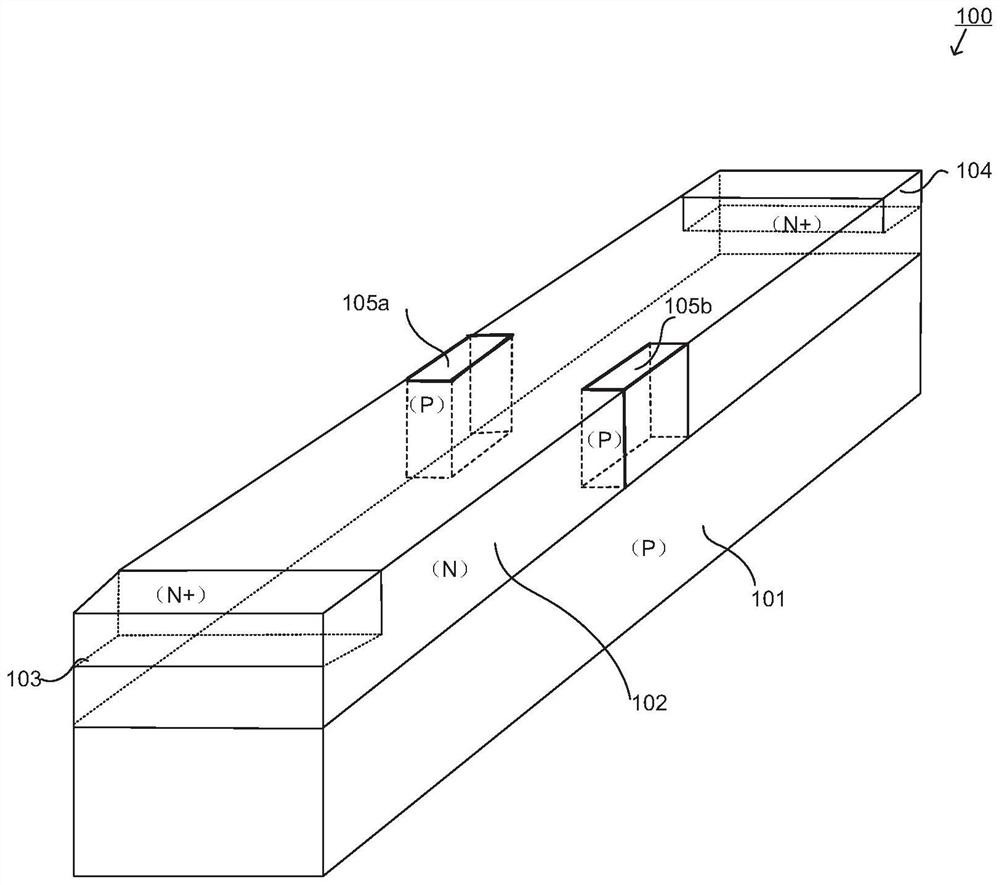

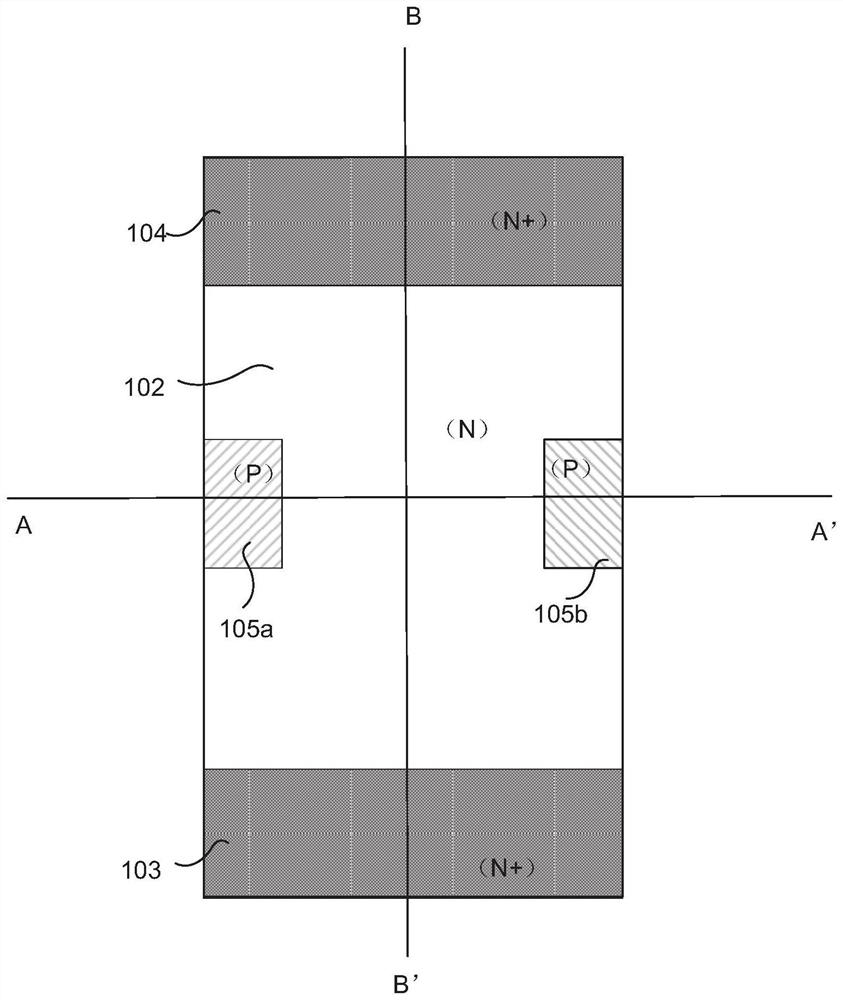

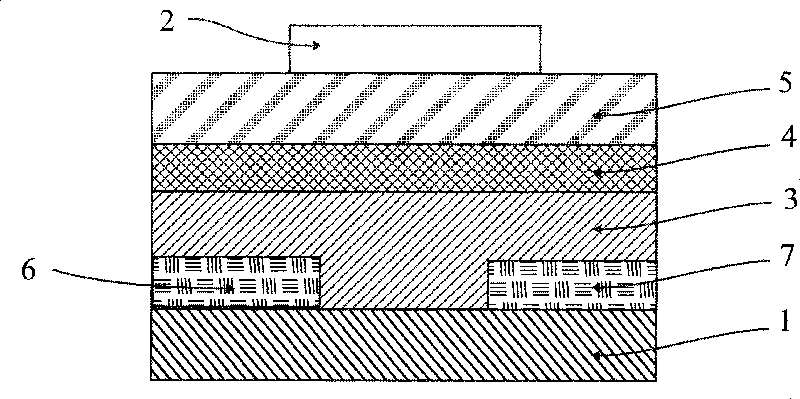

Junction field effect transistor (JFET) with first and second top layer of opposite conductivity type for high driving current and low pinch-off voltage

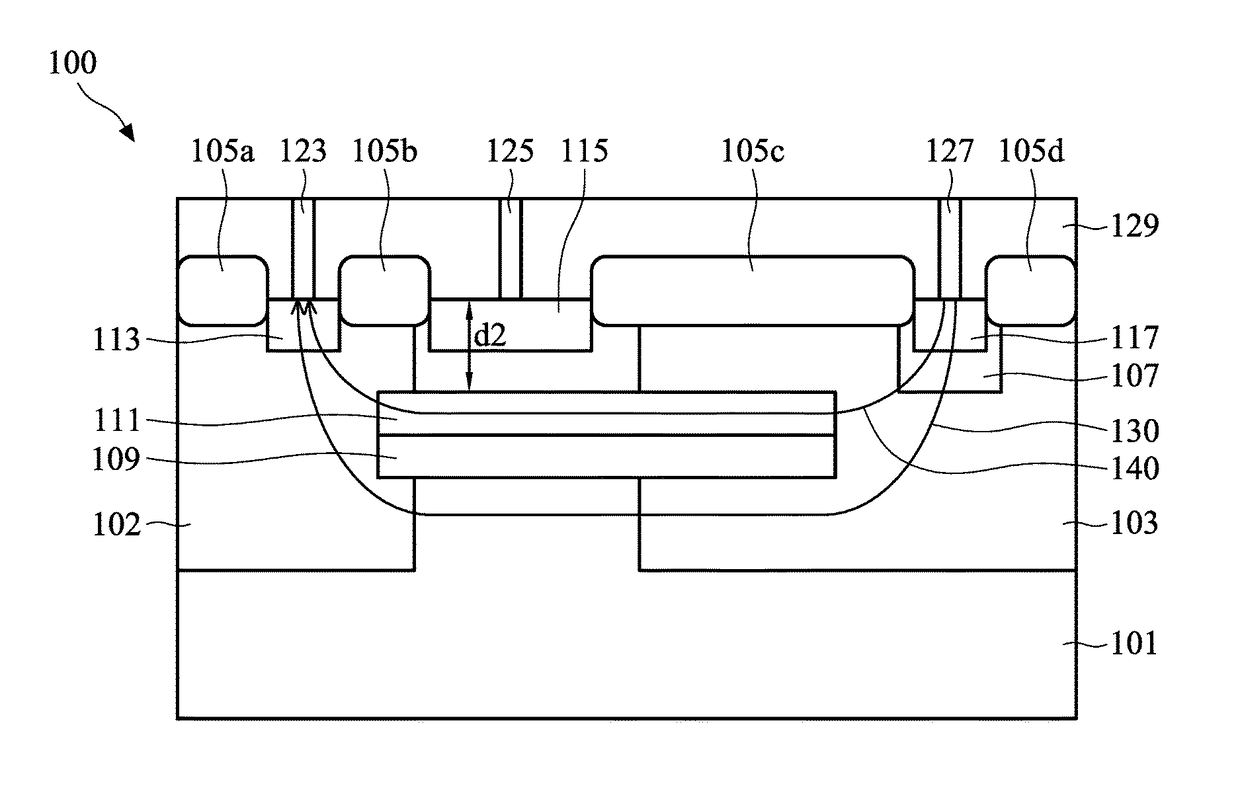

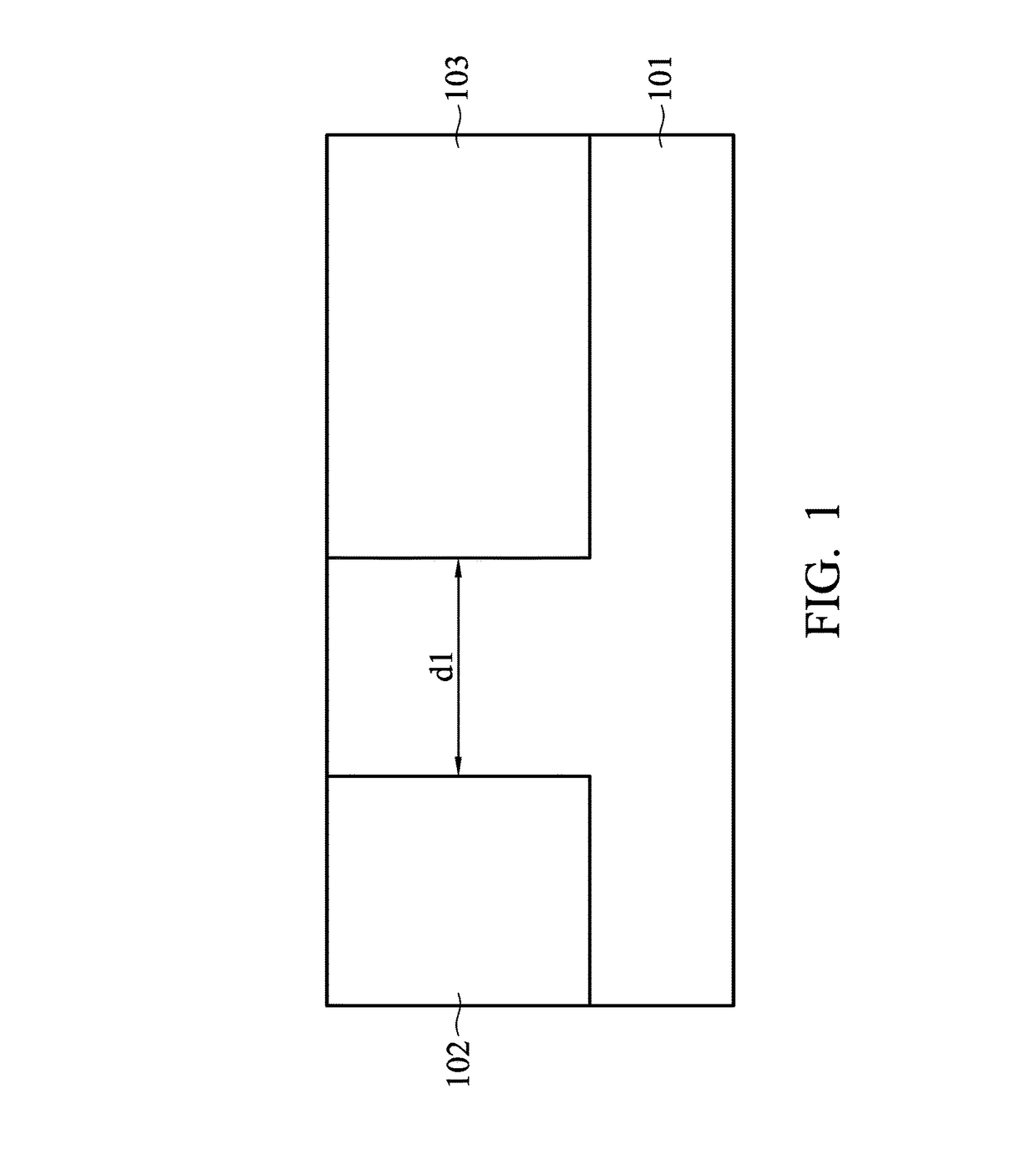

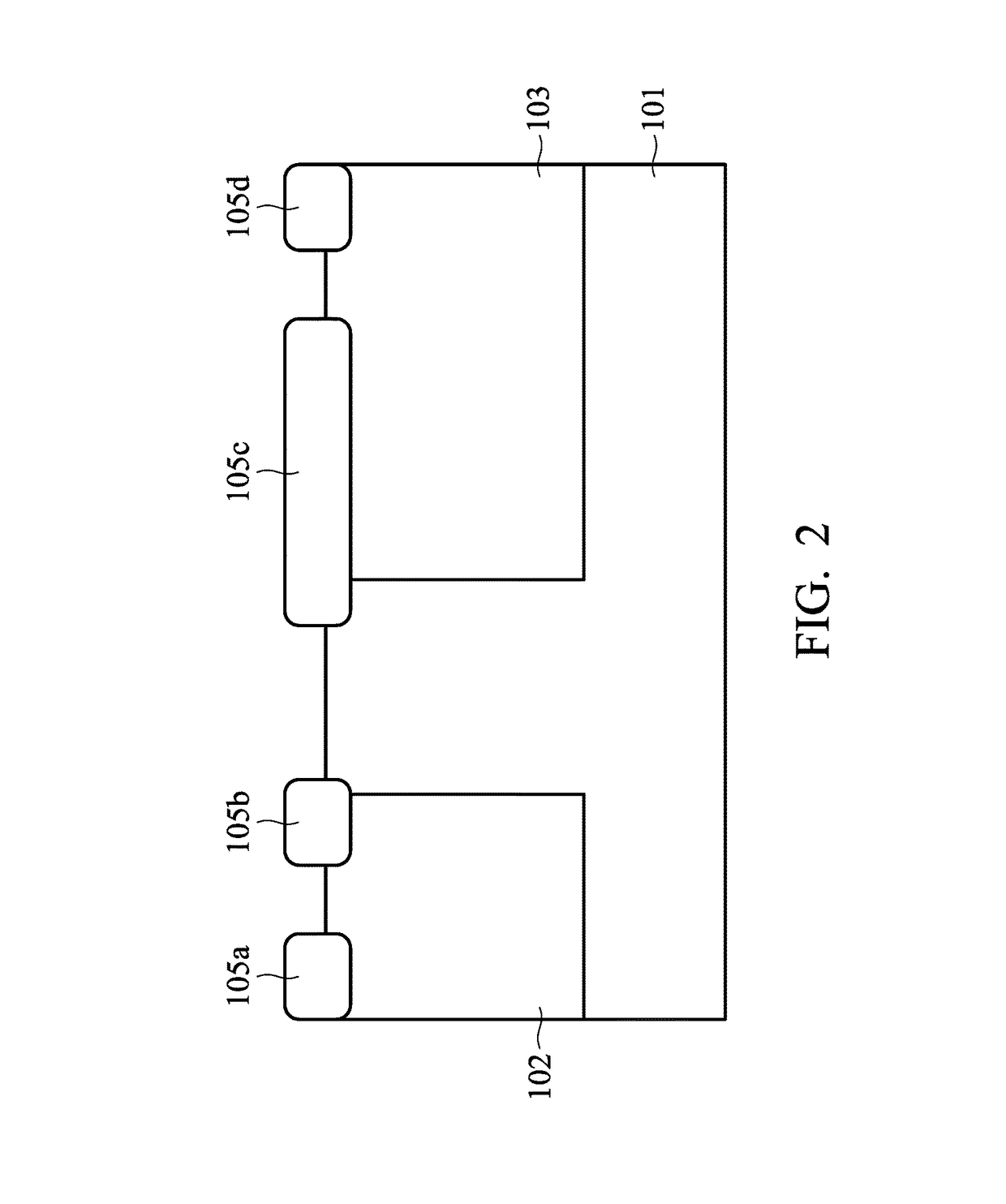

ActiveUS9929283B1Increase drive currentLower pinch-off voltageSemiconductor/solid-state device detailsSolid-state devicesDriving currentJFET

A semiconductor device includes a semiconductor substrate, a first well region, and a second well region. The semiconductor substrate has a first conductivity type. The first and second well regions are disposed in the semiconductor substrate. The first and second well regions have a second conductivity type that is opposite to the first conductivity type. The semiconductor device also includes a first top layer and a second top layer. The first top layer is disposed in the semiconductor substrate. The first top layer extends from the first well region to the second well region. The first top layer has the first conductivity type. The second top layer is disposed in the semiconductor substrate and on the first top layer. The second top layer extends from the first well region to the second well region. The second top layer has the second conductivity type.

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

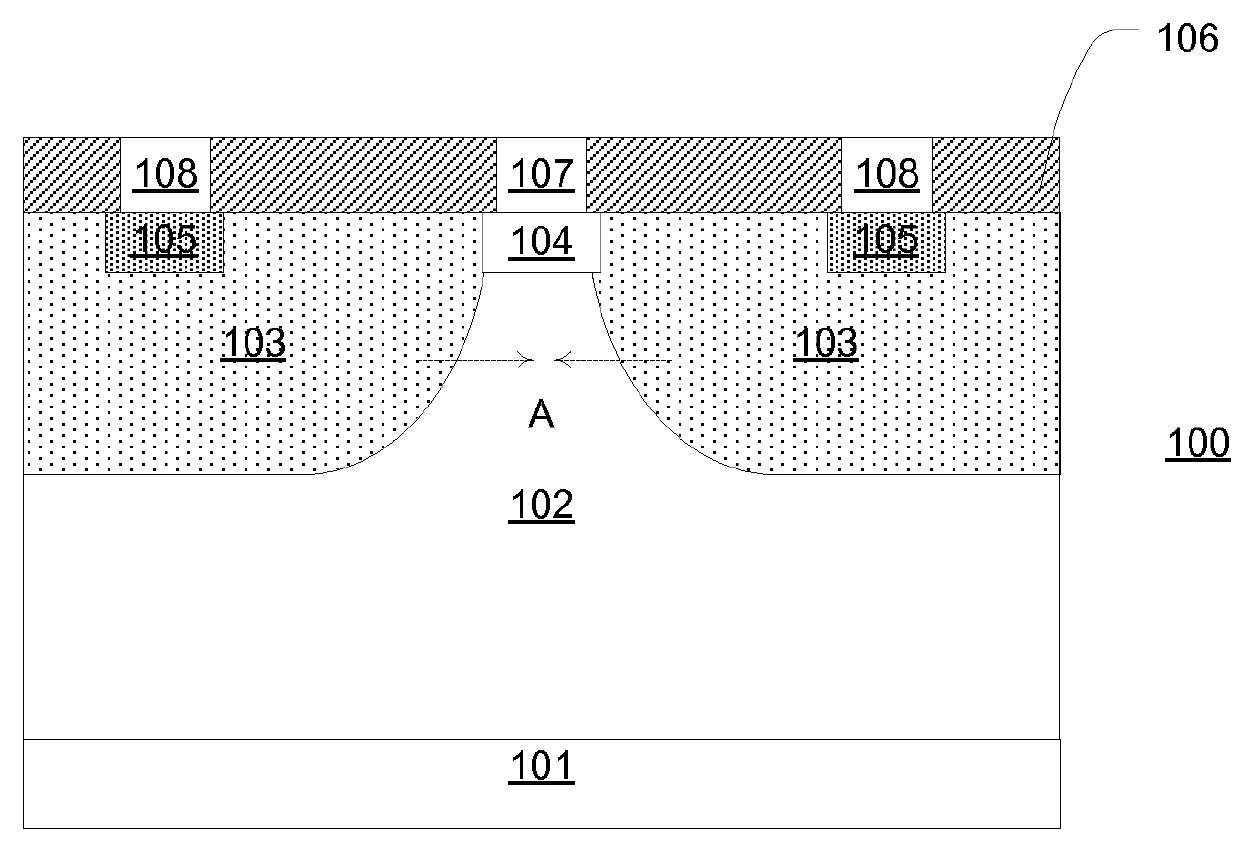

Junction field effect transistors and associated fabrication methods

ActiveUS9230956B2Enhance pinch-off effectHigh gate-source breakdown voltageTransistorSolid-state devicesJFETBody region

A JFET having a semiconductor substrate of a first doping type, an epitaxial layer of the first doping type located on the semiconductor substrate, a body region of a second doping type located in the epitaxial layer, a source region of the first doping type located in the epitaxial layer, a gate region of the second doping type located in the body region, and a shielding layer of the second doping type located in the epitaxial layer, wherein the semiconductor substrate is configured as a drain region, the shielding layer is in a conductive path formed between the source region and the drain region.

Owner:CHENGDU MONOLITHIC POWER SYST

Semiconductor device with low pinch-off voltage

PendingCN114784116ALower pinch-off voltageSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialField effect

Disclosed is a semiconductor device having a low pinch-off voltage. The semiconductor device includes a junction field effect transistor. The junction field effect transistor comprises a semiconductor substrate, a first well region formed in the semiconductor substrate, a first edge gate, a second edge gate, a source electrode and a drain electrode. Wherein the first edge gate and the second edge gate are formed in the first well region, the depth of the first edge gate, the depth of the second edge gate and the depth of the first well region are the same, and the source electrode and the drain electrode are formed in the first well region.

Owner:CHENGDU MONOLITHIC POWER SYST

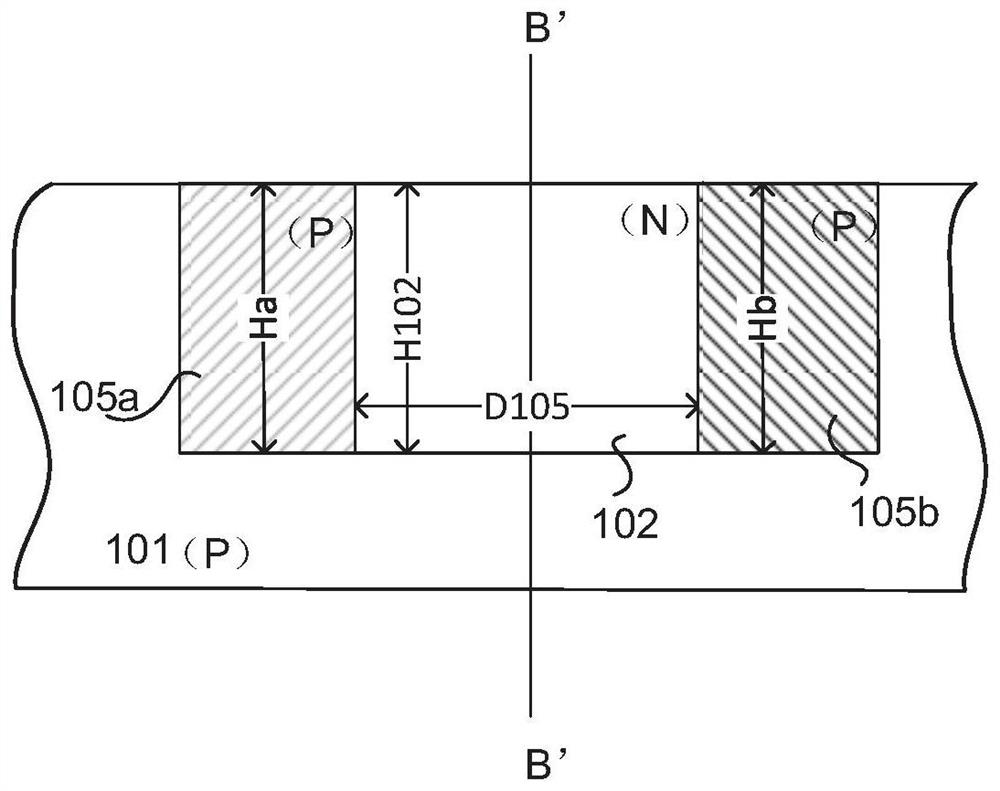

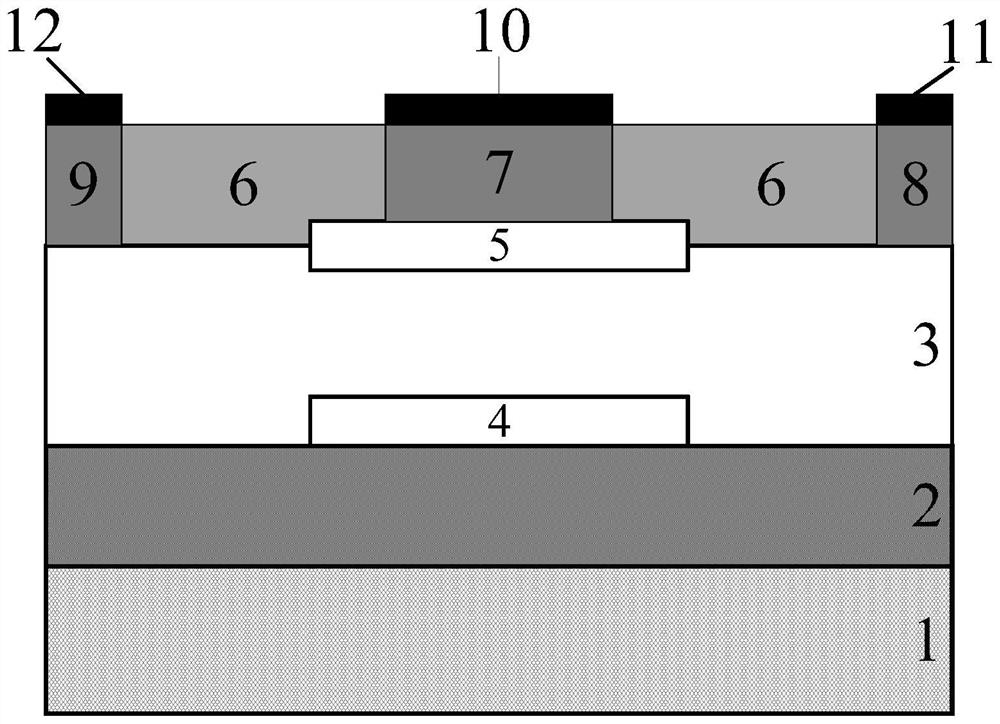

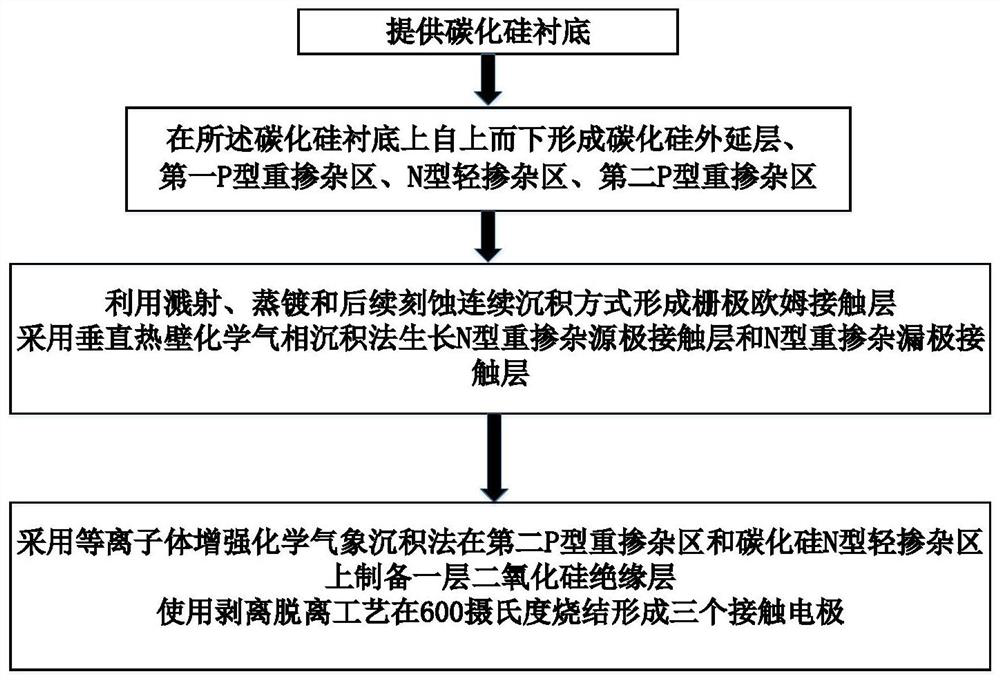

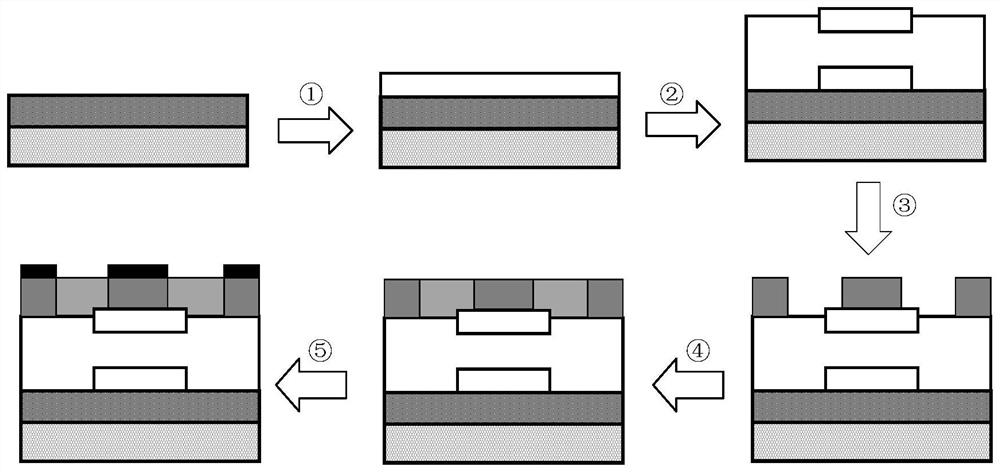

SiC-based junction field effect transistor and manufacturing method thereof

PendingCN114220867ALower on-resistanceReduce switching lossesSemiconductor/solid-state device manufacturingSemiconductor devicesContact layerField-effect transistor

The invention discloses a SiC-based junction field effect transistor and a manufacturing method thereof, and mainly solves the problems of high on resistance, low breakdown voltage and working temperature limitation of the existing device. Comprising a silicon carbide substrate, a silicon carbide epitaxial layer located above the substrate, and an N-type doped region on the upper surface of the epitaxial layer as a channel; a first P-type doped region serving as a back gate is arranged between the N-type doped region and the silicon carbide epitaxial layer, and a second P-type doped region serving as a positive gate is arranged on the upper surface of the N-type doped region; forming a source electrode contact layer and a drain electrode contact layer on the surface of the N-type doped region by adopting a vertical hot wall chemical vapor deposition method, forming an ohmic contact layer on the surface of the second P-type doped region, and arranging a contact electrode on the ohmic contact layer; and electrical isolation is formed among the gate metal electrode, the source metal electrode and the drain metal electrode by using the insulating layer. According to the invention, the current conduction capability and the working voltage range can be improved while a relatively small pinch-off voltage is maintained, and the device is simple in structure and easy to prepare and has the characteristic of high temperature resistance.

Owner:XI'AN UNIVERSITY OF ARCHITECTURE AND TECHNOLOGY

Structure and manufacturing method of dual-channel high-voltage junction field effect transistor for reducing pinch-off voltage

ActiveCN103094319BEasy to run outLower pinch-off voltageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringHigh pressure

The invention discloses a pinch-off voltage reducing structure of a dual-channel high voltage junction field effect transistor (FET) and a manufacturing method of the pinch-off voltage reducing structure of the dual-channel high voltage junction FET. A well region provided with a channel region and a drift region is formed in a silicon substrate, a drift region inversion layer is arranged in the drift region, a gate region is formed on the outer side of the channel region, a channel region inversion layer is arranged in the channel region, the transverse width of the channel region inversion layer is longer than the transverse width of the channel region, and two ends of the channel region inversion layer are connected with the gate region. A drain electrode leading-out terminal is formed in the drift region, a source electrode leading-out terminal is formed in the channel region, a gate electrode leading-out terminal is formed in the gate region, and a substrate leading-out terminal is formed in the substrate region. The drift region, the drain electrode leading-out terminal and the source electrode leading-out terminal are in a second conductivity type, the substrate, the drift region inversion layer, the channel region inversion layer, the gate region, the gate leading-out terminal and the substrate leading-out terminal are in a first conductivity type, and electrodes are led out from the leading-out terminals. According to the pinch-off voltage reducing structure of the dual-channel high voltage junction FET and the manufacturing method of the pinch-off voltage reducing structure of the dual-channel high voltage junction FET, impurities which are opposite in type are implanted inside the channel region to form double channels, namely an upper channel and a lower channel, the opposite impurities are arranged in the channel region at the same time, and therefore each channel can be exhausted more easily, and pinch-off voltage is lowered.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

A lateral constant current diode

InactiveCN103400863BIncrease the constant currentEasy to pinch offSemiconductor devicesConstant-current diodeSemiconductor technology

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

High voltage jfet device and process method

ActiveCN105914238BImprove breakdown voltageReduce N-type impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesSource areaSilicon

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

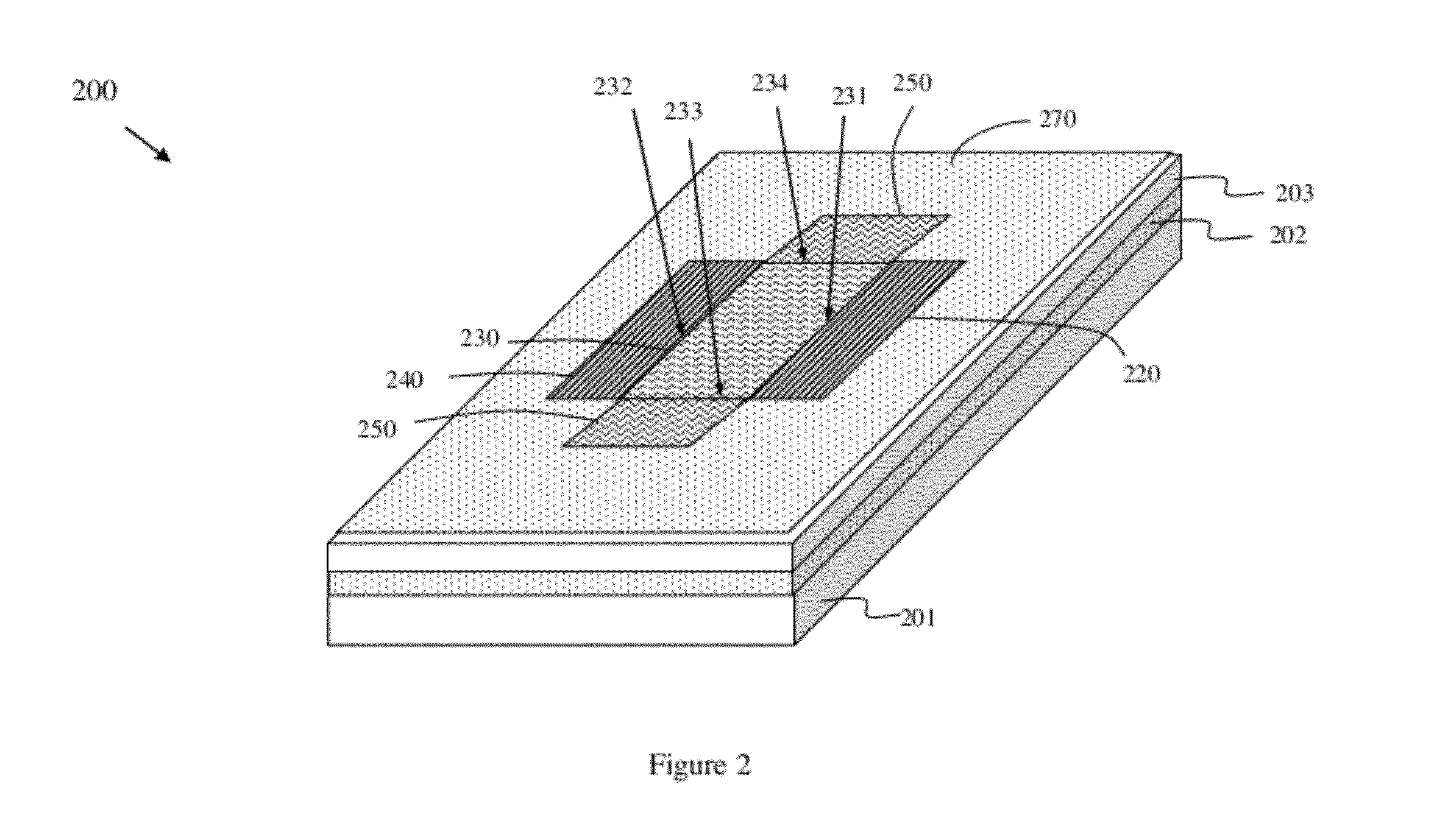

Organic thin-film transistor and manufacturing method thereof

InactiveCN101257093BSimple manufacturing processWide range of choicesSolid-state devicesSemiconductor/solid-state device manufacturingOrganic filmThin membrane

The invention provides an organic thin-film transistor, which includes: a substrate, a gate electrode, an isolation layer, an organic semiconductor layer, a leakage electrode and a source electrode. The organic thin-film transistor has structure that is one of top contact type, bottom contact type and top gate type. The organic thin-film transistor has characteristics in that: also includes a connection layer, said connection layer is composed of one or more of cavity type organic semiconductor material. Aims of the invention is to optimize manufacturing process of the organic thin-film transistor, increase the organic thin-film transistor performance, reduce greatly the organic thin-film transistor cost, and reduce technological requirement and cost for the organic thin-film transistor industrialization.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Current stabilizer tube and manufacturing method thereof

InactiveCN104701367ALower pinch-off voltageIncrease the on-currentSemiconductor/solid-state device manufacturingSemiconductor devicesConduction currentSilicon

The invention discloses a current stabilizer tube comprising a P-type epitaxial layer, two first N-type areas, a longitudinal conduction trench and a third N-type area. The P-type epitaxial layer is formed on the front surface of a P+ silicon substrate. The first N-type areas are formed in the P-type epitaxial layer. The part, between the first N-type areas forms the longitudinal conduction trench. The third N-type area is formed in the P-type epitaxial layer in the bottom area of the longitudinal conduction trench. When a device operates, the third N-type area helps increase the ability to consume the P-type epitaxial layer in the bottom area of the longitudinal conduction trench, pinch-of voltage of the device can be reduced thereby; increase in the width of the longitudinal conduction trench leads to increase in conduction current; by adjusting the pinch-off voltage of the device through the third N-type area, the pinch-off voltage can be kept unchanged or lower while conduction current is increased, and reliability of the device is improved thereby. The invention further discloses a manufacturing method of the current stabilizer tube.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

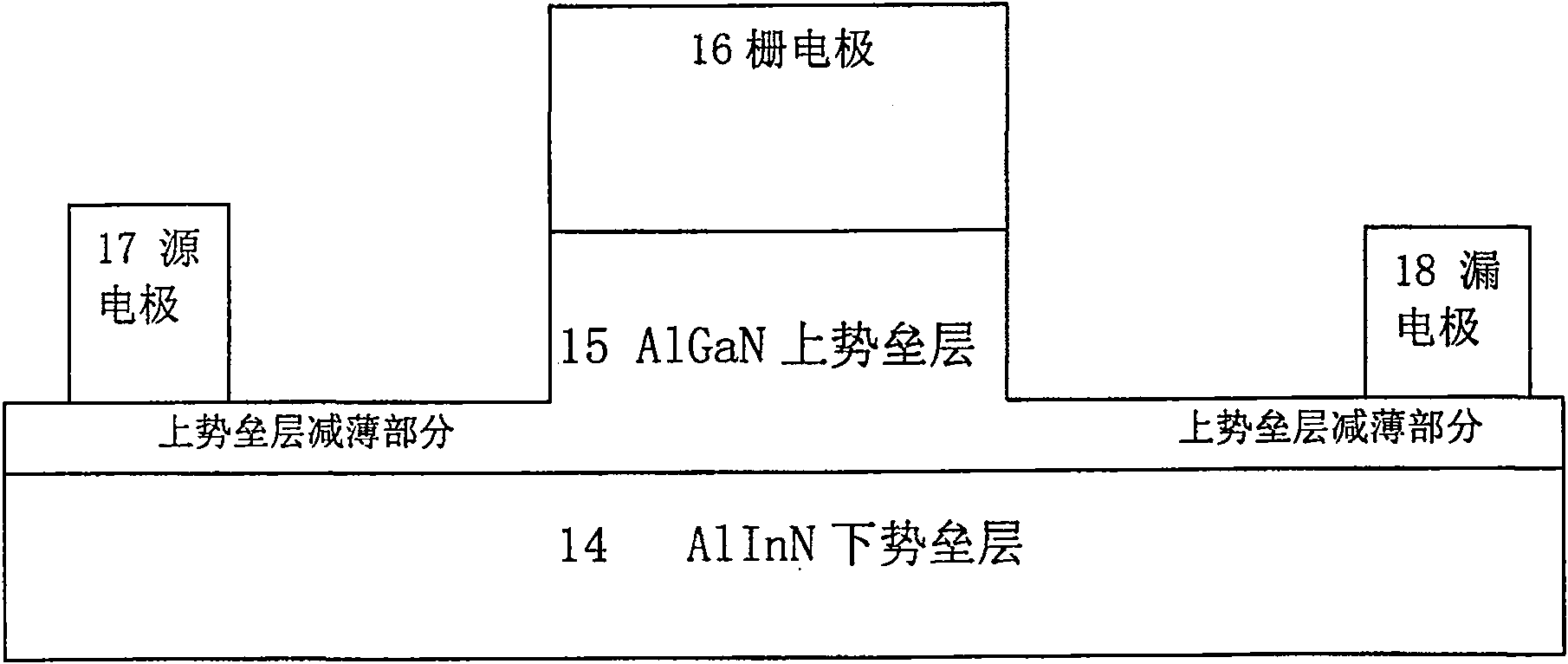

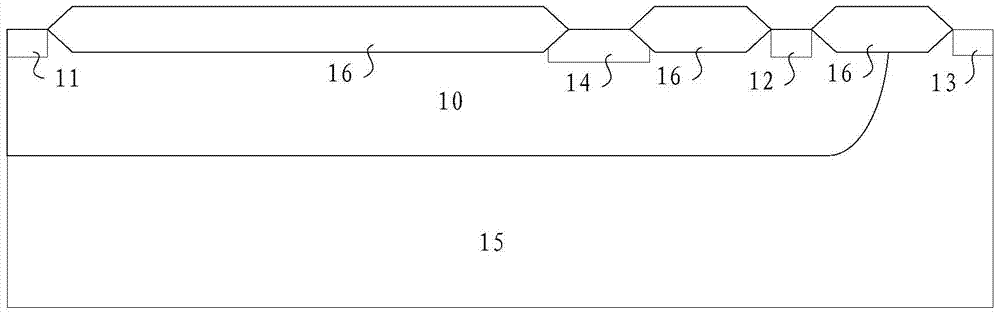

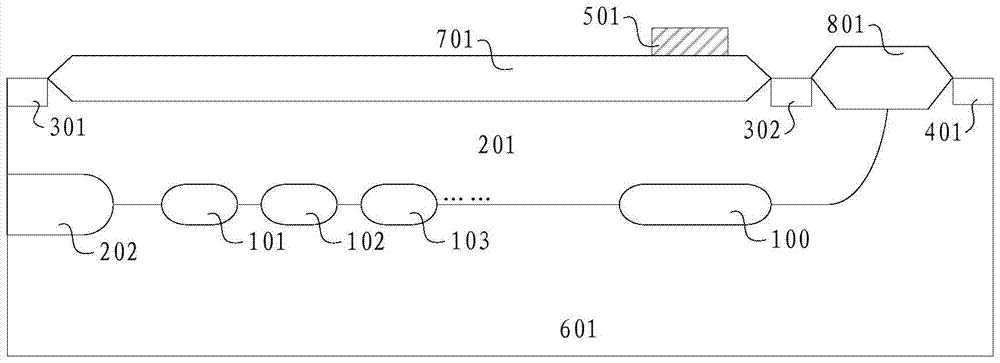

Method for producing AlGaN/AlInN composite potential barrier gallium nitride field effect pipe

InactiveCN100570833CSimple structureEnhanced 2D featuresSemiconductor/solid-state device manufacturingSchottky barrierOhmic contact

The invention is a method for manufacturing AlGaN / AlInN compound barrier gallium nitride field effect transistor. The process steps are divided into sequentially growing a nucleation layer, an AlGaN buffer layer, a GaN channel layer, an AlN isolation layer and an AlInN layer on a substrate. The lower barrier layer; the AlGaN upper barrier layer is covered on the AlInN lower barrier layer to form a composite barrier; the AlGaN upper barrier layer on the AlGaN upper barrier layer is thinned except for the area reserved for gate electrodes by microelectronic technology Layer; making source electrode and drain electrode on the thinned part; making gate electrode on the area reserved for making gate electrode on the AlGaN upper barrier layer. Advantages: broaden and increase the potential barrier, improve the channel well structure, enhance the two-dimensional characteristics of the electron gas, and the strong negative polarized charge on the AlGaN / AlInN heterointerface increases the strength of energy band clipping, and meets the requirements of ohmic contact and Schottky potential different heterostructure requirements throughout the barrier, under-gate trench, and off-gate trench.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

A junction field effect transistor

ActiveCN104518008BLower pinch-off voltageUniform electric field distributionSemiconductor devicesJFETBreakdown voltage

The invention belongs to the semiconductor device field and discloses a junction field effect transistor. According to the junction field effect transistor, a back grid is formed between a trench and a P substrate of the JFET (junction type field effect transistor) and is corresponding to the position of a positive grid, and as a result, when negative voltage is applied to the grids, depletion regions of a positive grid PN junction and a negative grid PN junction do not horizontally extend, but vertically extend with the increase of the negative voltage, so that small pinch-off voltage can be obtained; drain-source voltage is mainly borne by horizontal extension of the depletion regions, and P type lightly-doped regions which are adjacent to a source are formed between the trench and the P substrate of the JFET, so that the distribution of an electric field in the trench of the JFET is more uniform, and N type lightly-doped regions which are located below a drain are formed between the trench and the P substrate of the JFET, and thus, breakdown of a PN junction formed by the trench and the P substrate of the JFET, which occurs at the bottom of a drain end, can be avoided, and as a result, high drain-source breakdown voltage can be obtained. With the junction field effect transistor adopted, contradictions among three parameters, namely, the pinch-off voltage, the drain-source breakdown voltage and current conduction capacity, can be alleviated.

Owner:FOUNDER MICROELECTRONICS INT

Improved groove-type Schottky rectifier device and manufacturing method thereof

InactiveCN106784021AIncrease contact areaIncrease pressure dropSemiconductor devicesSurface layerGate insulator

The invention discloses an improved groove-type Schottky rectifier device and a manufacturing method thereof. The improved groove-type Schottky rectifier device disclosed by the invention comprises a first conduction type substrate, a first conduction type conducting layer, grooves, conducting polycrystalline silicon, a gate insulator layer and a metal electrode layer, wherein a second conduction type area is arranged inside the upper surface layer of the first conduction type conducting layer between every two adjacent grooves; and the metal electrode layer is arranged on the first conduction type conducting layer, the conducting polycrystalline silicon and the second conduction type area. The backward voltage resisting capacity is improved, and meanwhile the problem that the forward voltage drop becomes large caused by small groove distance is solved.

Owner:杭州易正科技有限公司

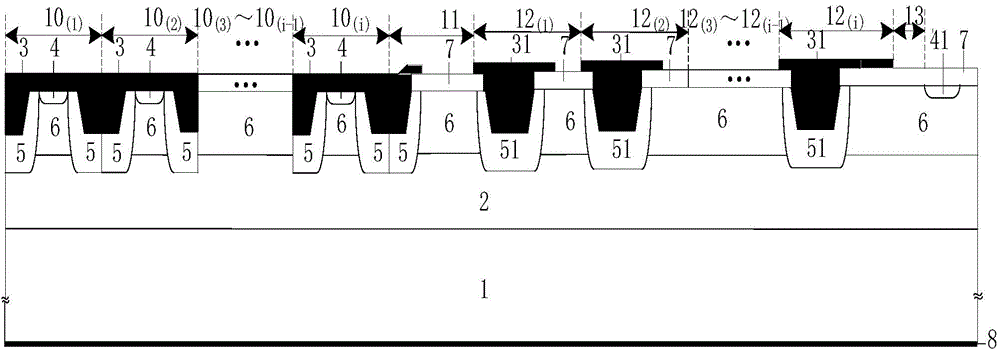

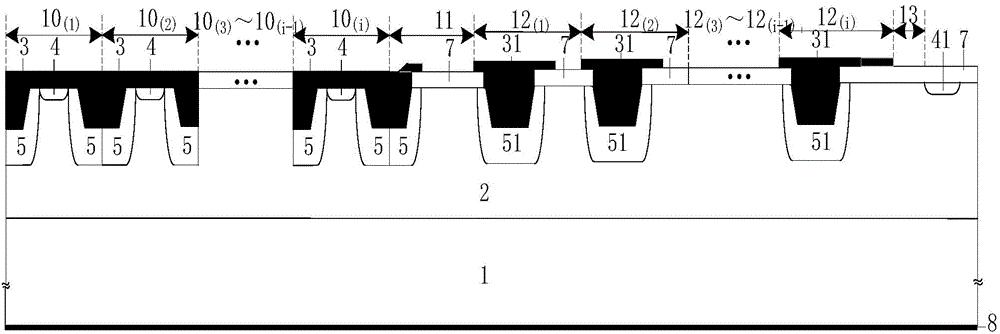

Jfet device and its manufacturing method

ActiveCN104518034BReduce doping concentrationLower pinch-off voltageSemiconductor/solid-state device manufacturingSemiconductor devicesVoltage regulationEngineering

The invention discloses a JFET (junction field-effect transistor) device and a manufacturing method thereof. A drift region is formed by a doped first deep trap region, in a second conduction type, formed on a doped substrate in a first conduction type; a body region comprises a channel region and a doped second deep trap region in the second conduction; the channel region is positioned between the first deep trap region and the second deep trap region and comprises more than two doped third deep trap regions, in the second conduction type, in evenly-spaced arrangement, and doping impurities of a space area between each two adjacent third deep trap regions are formed by diffusion impurities of the adjacent third deep trap region; process conditions of the three deep trap regions are identical. Pinch-off voltage of the JFET device can be adjusted by adjustment of impurity concentration of the deep trap regions, width of each space area and number of the space areas. By the JFET (junction field-effect transistor) device and the manufacturing method thereof, the pinch-off voltage can be lowered, convenience in adjustment of the pinch-off voltage is achieved, and requirements on various different pinch-off voltages can be met.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

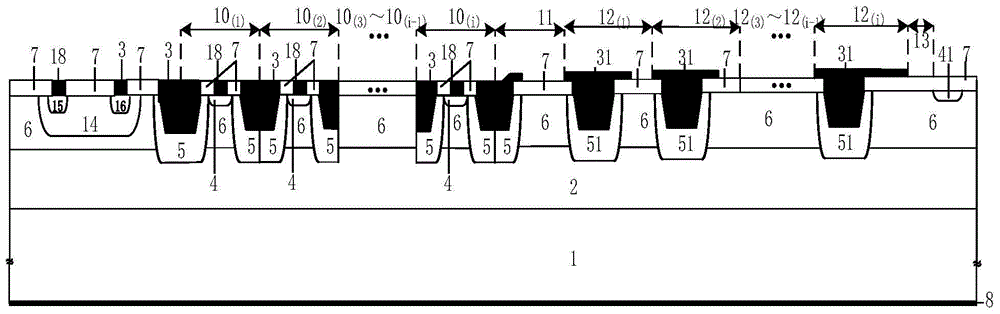

A vertical constant current diode and its manufacturing method

InactiveCN103426936BLower pinch-off voltageGood constant current effectSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringConstant-current diode

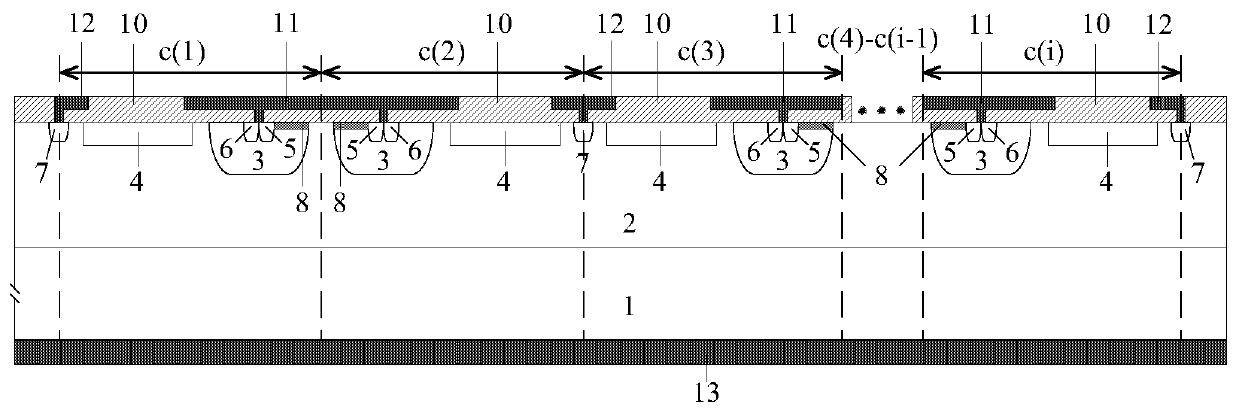

The invention relates to semiconductor technology, in particular to a vertical current regulative diode and a manufacturing method thereof. The vertical current regulative diode comprises an oxide layer, a highly doped N-type epitaxial layer, a lightly doped N-type epitaxial layer, a heavily doped N+ substrate and a metal anode which are sequentially stacked. The vertical current regulative diode is characterized by further comprising a cellular structure, a terminal structure and a cut-off ring which are sequentially connected, the cellular structure comprises a plurality of cells which are the same in structure and are sequentially connected, and the terminal structure comprises a plurality of terminals which are the same in structure and are sequentially connected. The vertical current regulative diode has the advantages that the diode is easily pinched off, pinch-off voltage can be below 5V, a pinch-off point more slowly changes along with increase of the voltage, constant current is more stable, the diode is more flexible in design and more reasonable in structure, an additional photo-etching plate can be omitted, and manufacturing cost is saved. The manufacturing method is particularly applicable to the current regulative diode.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Structure and Fabrication Method of High Voltage Junction Field Effect Transistor

ActiveCN103178093BReduce impurity concentrationEasy to run outSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorBody region

The invention discloses a high-voltage junction field effect transistor structure. An inversion layer is filled into a deep channel of a body region of the structure. The invention further discloses a manufacture method of the high-voltage junction field effect transistor structure (HV JFET) structure. The manufacture method comprises the steps of manufacturing the inversion layer in the deep channel of the body region through a photoetching and ion implantation process while manufacturing a substrate trap of a manufacture body region or the inversion layer of a drain terminal drifting region in the HV JFET conventional manufacture process. By filling one opposite type of impurities into the deep channel of the JFET body region, the impurity concentration of the channel of the JFET body region is reduced on a basis that any photoetching layer is not increased, the channel is easily used up, and accordingly the pinch-off voltage of an HV JFET device is effectively reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com