SiC-based junction field effect transistor and manufacturing method thereof

A technology of field effect transistors and junctions, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as low breakdown voltage, high on-resistance, and operating temperature limitations, and achieve large band gap, Effect of high intrinsic temperature and small pinch-off voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

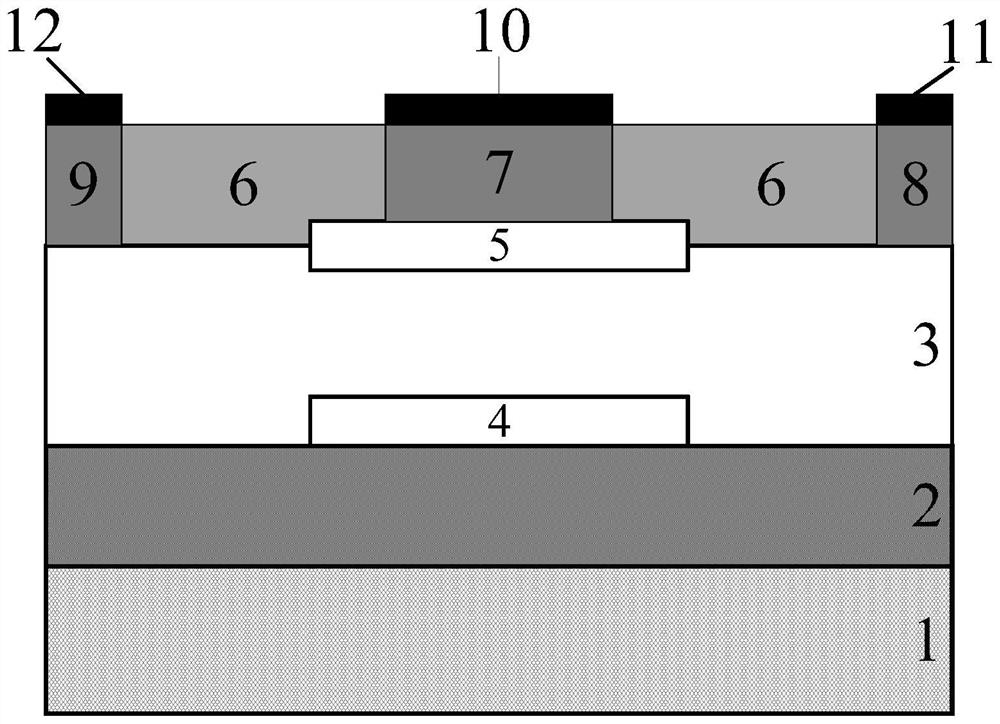

[0029] Example 1: Refer to figure 1 , The SiC-based junction field effect tube proposed by the present invention is discharged from silicon carbide as a substrate, and the silicon carbide substrate 1 is discharged from the silicon carbide epitaxial layer 2, the first P-type doped region 4, the second P-type doped region 5, two p-type doped regions are provided with n-type doped regions 3;

[0030] The intermediate position of the n-type doped region 3 is adjacent to the lower surface and the upper surface, respectively, as a first p-doped region 4 as a back gate, respectively, a second P-type doped region 5 as a normal gate; N-type doped The silica insulating layer 6, the ohmic contact layer 7, the source contact layer 8 and the drain contact layer 9 are formed in the upper surface of the region 3; wherein the silica insulating layer 6 is divided into two parts, and a portion is located in the ohmic contact layer 7 and the source. Between the contact layer 8, the other portion is ...

Embodiment 2

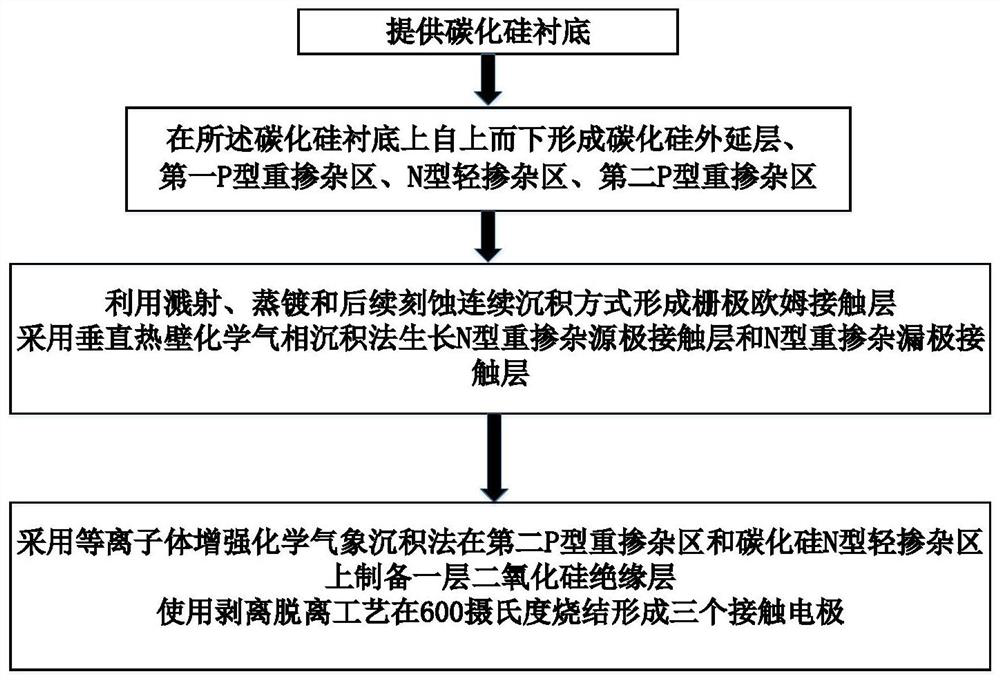

[0036] Example 2: Reference figure 1 and figure 2 , The specific steps are as follows: The specific steps are as follows:

[0037] Step 1) Provide a heavily doped silicon carbide substrate;

[0038] Step 2) Grow the silicon carbide epitaxial layer on the silicon carbide substrate;

[0039] Step 3) Plasma doping in the center portion of the silicon carbide epitaxial layer, forming a first P-type doped region, and its carrier concentration ranges from 1 × 10 18 cm -3~ 1 × 10 19 cm -3 ;

[0040] Step 4) An n-type silicon carbide is prepared on the silicon carbide epitaxial layer and the first P-type doped region, and the desired doped pattern is obtained on the N-shaped silicon carbide; the carrier concentration range of n-type silicon carbide 1.5 × 10 17 cm -3~ 2 × 10 17 cm -3 ;

[0041] Step 5) Plasma doping in the position of the N-type silicon carbide after the photolithography, plasma doping, forming a second P-type doped region, and its carrier concentration ranges from 1 × 10 ...

Embodiment 3

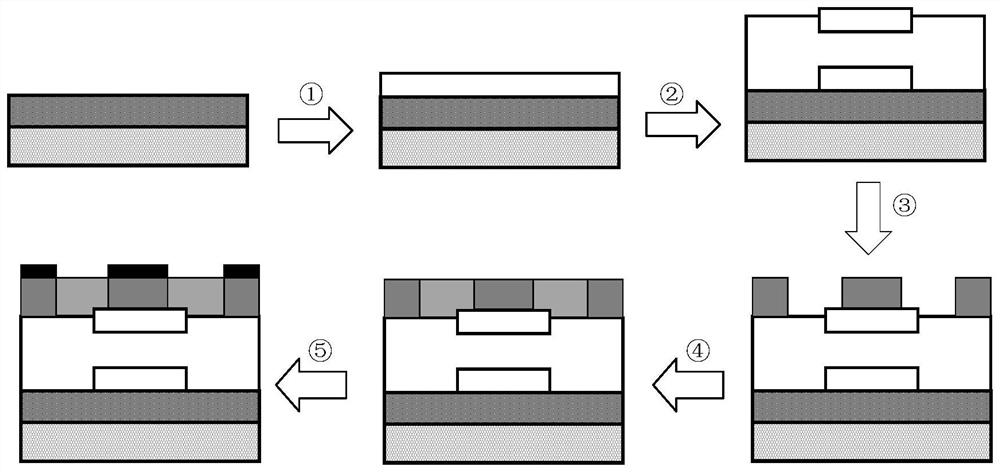

[0045] Example 3: Reference image 3 The overall step of the present embodiment is based on the second embodiment, and gives a specific parameter and process operation further describe the implementation steps of the method of the present invention:

[0046] Step 1: Select the substrate.

[0047] First, 250 nm P-type doped silicon carbide is first used as the initial material, which is used as a substrate.

[0048] Step 2: Grow the epitaxial layer.

[0049] The epitaxial growth technique was used to grow 200 nm P-type silicon carbide epitaxial layer in the substrate in the substrate using a vertical thermal wall chemical vapor deposition method.

[0050] Step 3: Growing silicon carbide first P-type retaining region.

[0051] The chemical vapor deposition method CVD growth of 50 nm of silicon carbide P-type retaining region is grown on silicon carbide epitaxial layer; image 3 The process flow 1 is shown.

[0052] Step 4: Growing silicon carbide n-type lightly doped regions.

[0053]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com