Patents

Literature

89results about How to "Increase the bandgap width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

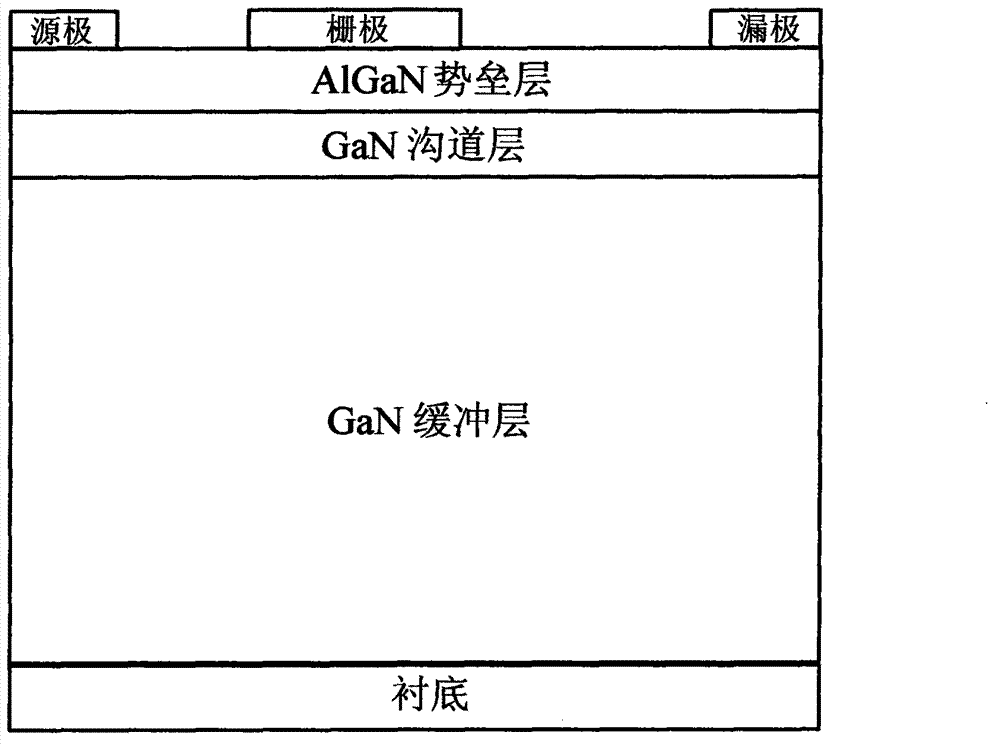

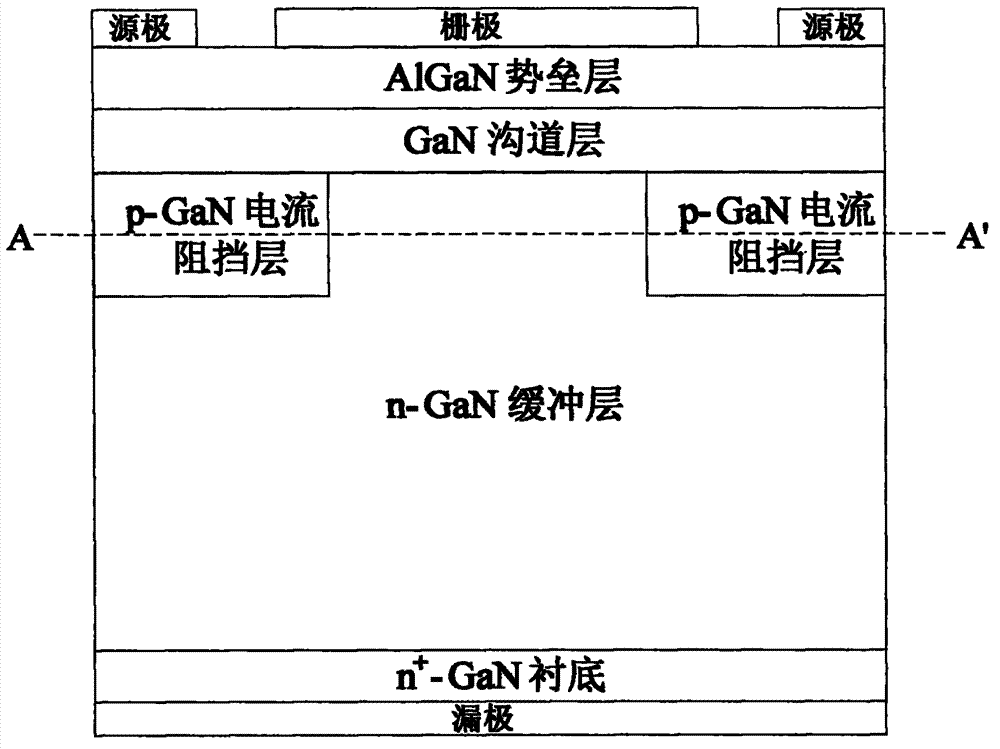

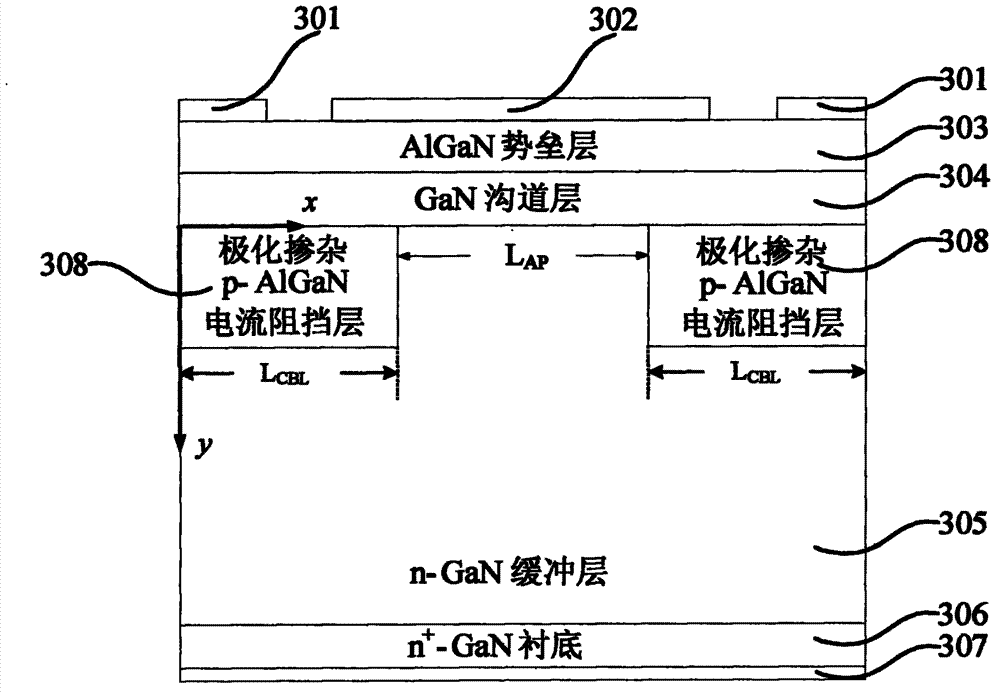

Vertical gallium nitride based nitride heterojunction field effect transistor with polarized doped current barrier layer

InactiveCN103035706AImprove thermal stabilityHigh activation rateSemiconductor devicesOhmic contactGallium nitride

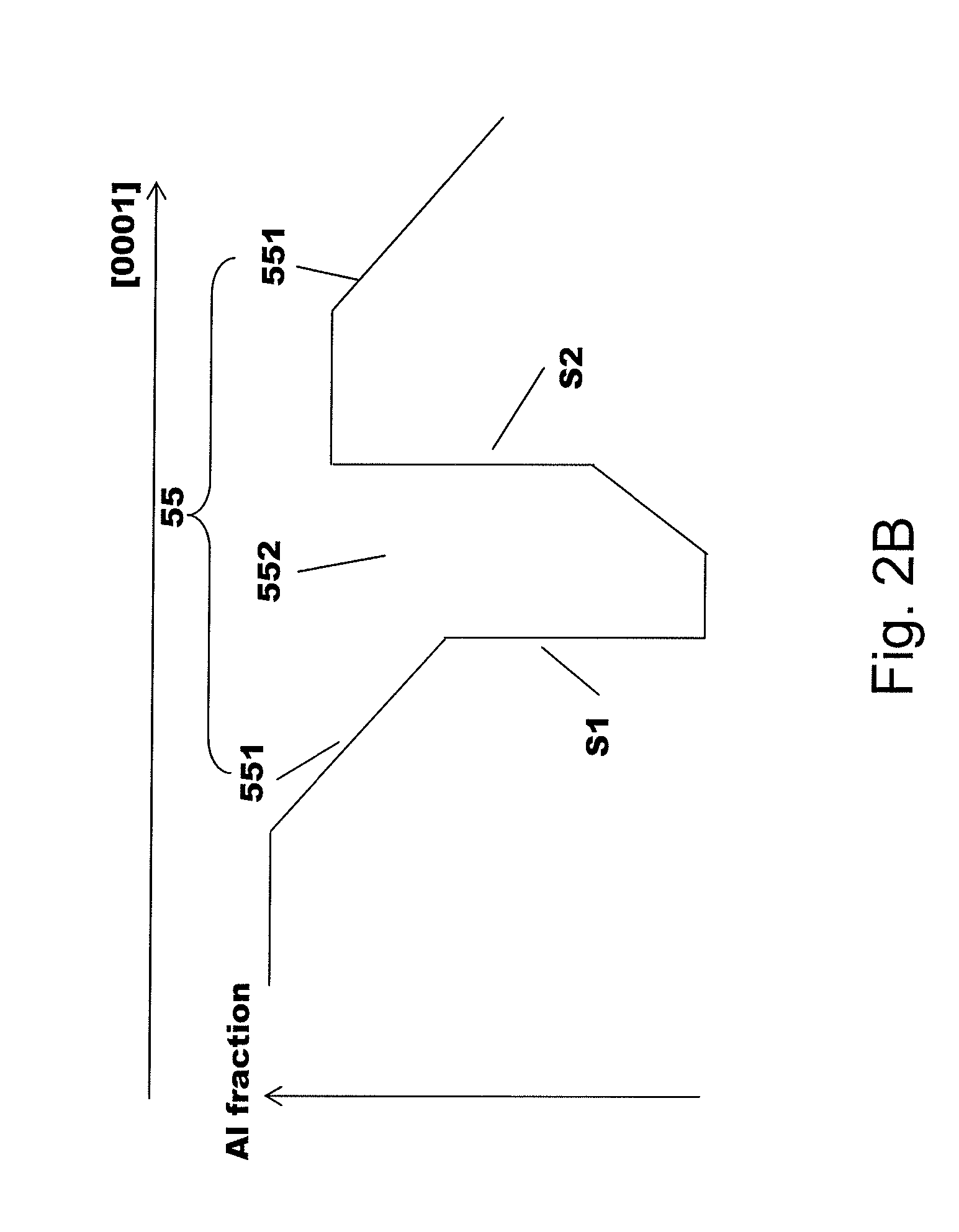

The invention provides a vertical gallium nitride based nitride heterojunction field effect transistor with a polarized doped current barrier layer, which sequentially and mainly comprises a drain electrode, an n<+>-GaN substrate, an n-GaN buffer layer, a GaN channel layer, an AlGaN barrier layer, a source electrode on the AlGaN barrier layer and a grid electrode on the AlGaN barrier layer from bottom to top, wherein the source electrode and the drain electrode are both in ohmic contact, the grid electrode is in Schottky contact, the vertical gallium nitride based nitride heterojunction field effect transistor further comprises the polarized doped p-AlGaN current barrier layer between the n-GaN buffer layer and the GaN channel layer, and an Al component in the current barrier layer increases gradually in the y direction. According to the vertical gallium nitride based nitride heterojunction field effect transistor with the polarized doped current barrier layer, a polarized electric field, produced by the gradual change of the Al component in the current barrier layer, increases the activation rate of p-type impurities and the hole concentration of the current barrier layer, so that the breakdown voltage of an element is increased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

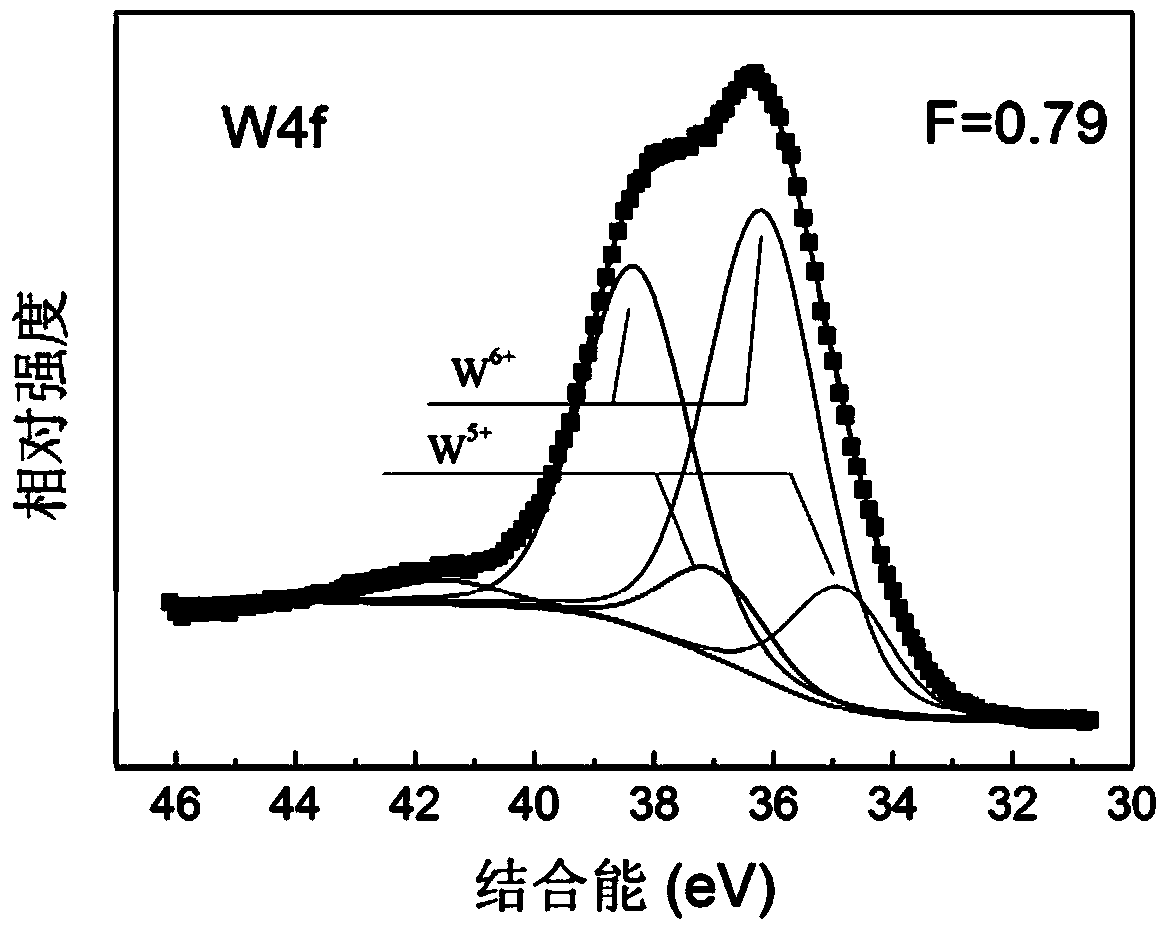

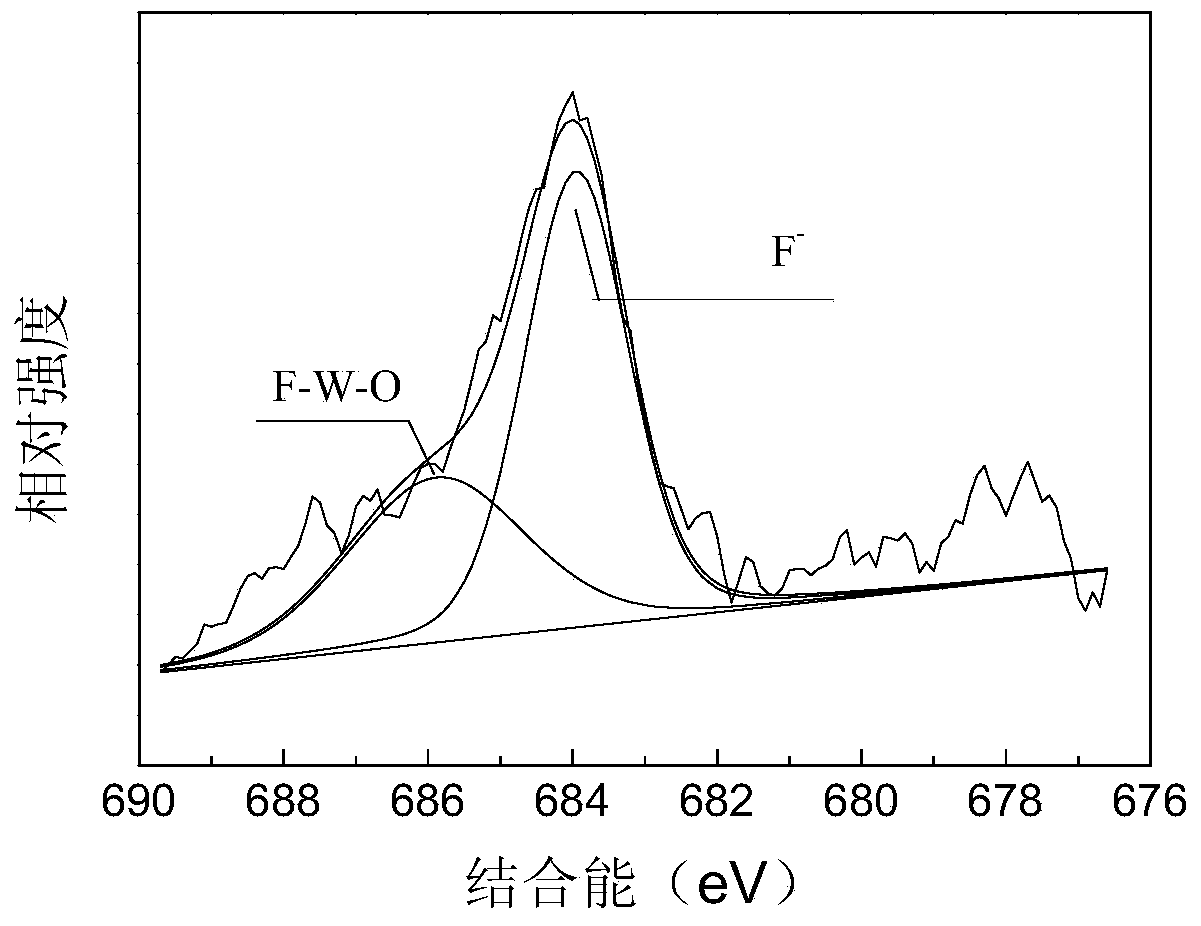

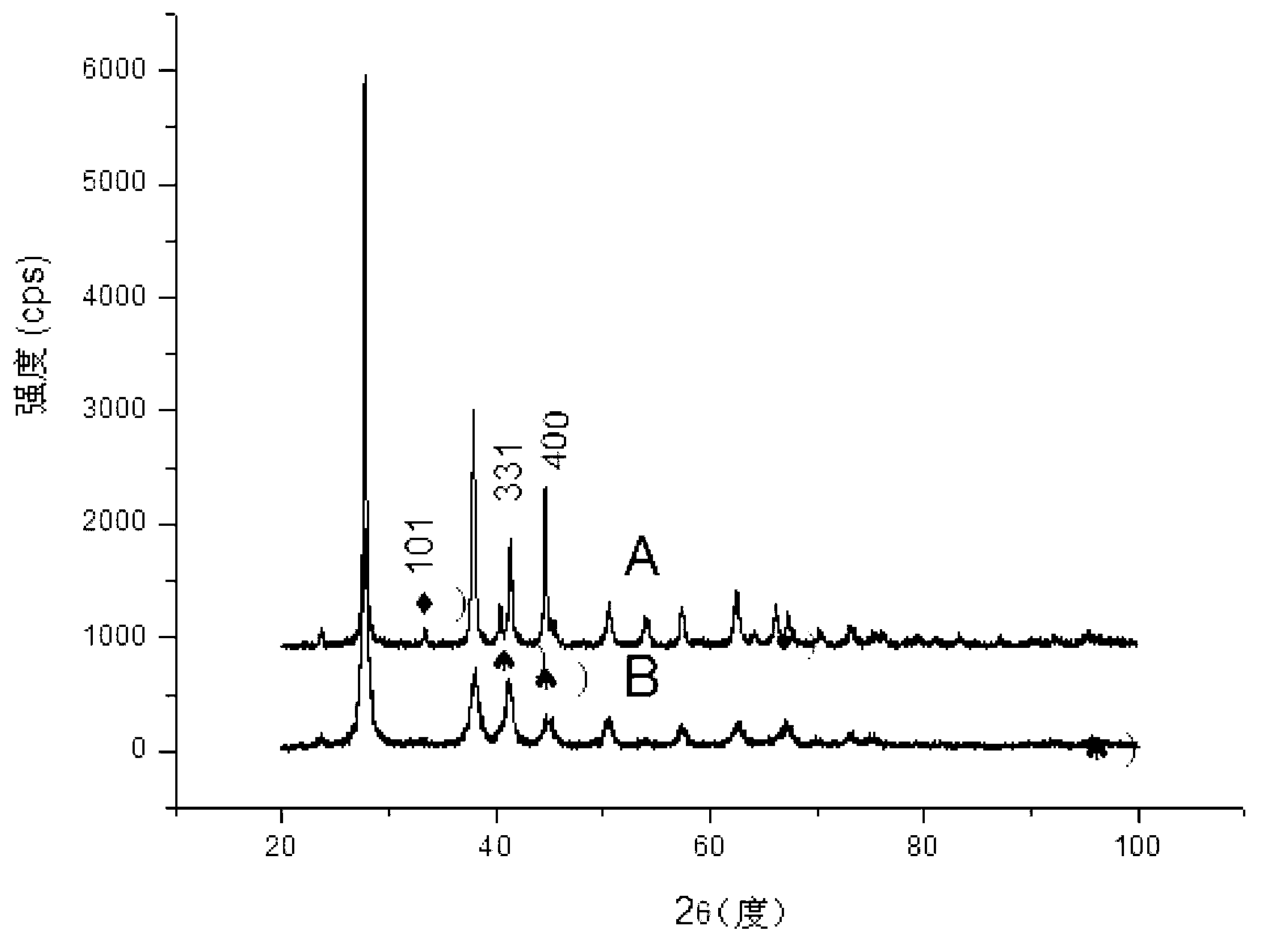

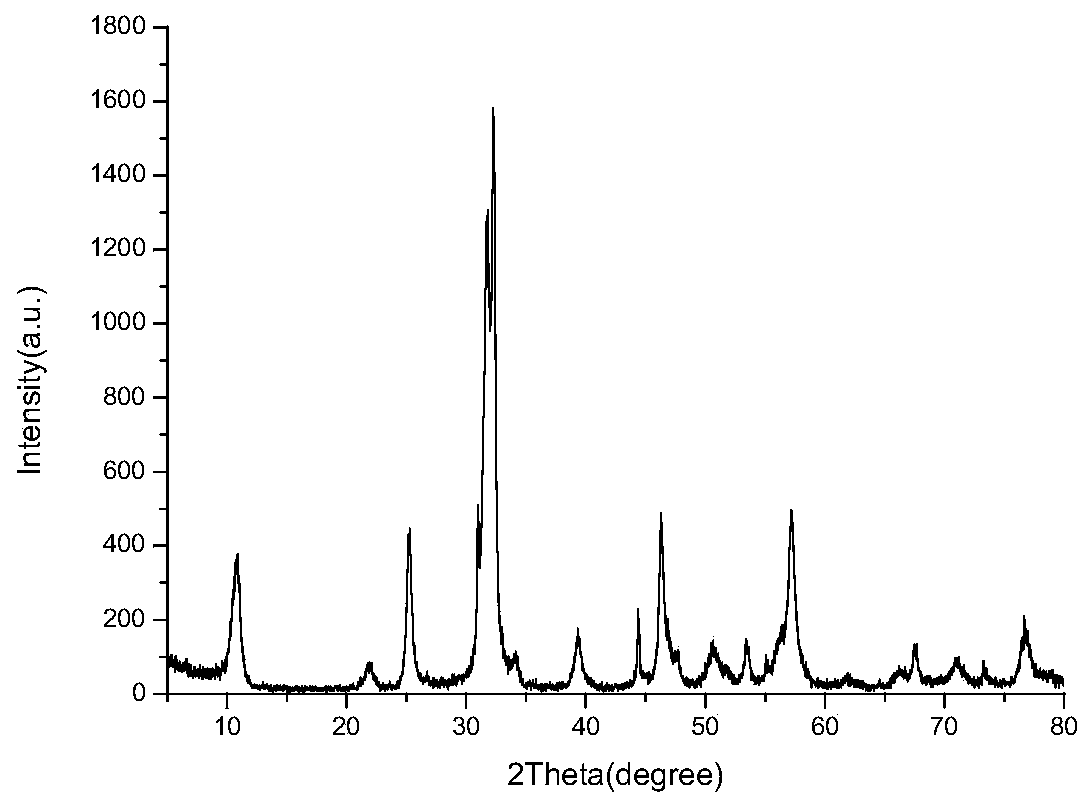

CsxWOyFz powder and preparation method thereof

ActiveCN103708558APreparation method scienceThe preparation method is reasonableRadiation-absorbing paintsTungsten compoundsHigh pressureMaterials science

The invention provides CsxWOyFz powder and a preparation method thereof. The preparation method of the CsxWOyFz powder comprises the following steps: mixing a tungstic acid solution with a fluorine source solution, and adding organic acid to form a WO3-F composite sol; adding a Cs2CO3 solution to the WO3-F composite sol to form a Cs-WO3-F composite sol; putting the Cs-WO3-F composite sol in a high-pressure kettle, and carrying out hydrothermal reaction for 1-3 days at the temperature of 180-200 DEG C; and sequentially carrying out centrifugation, water washing, alcohol washing and drying on the reactant to obtain the CsxWOyFz powder. The preparation method provided by the invention has the advantages of no need for high temperature hydrogen reduction, simple process, low cost, little toxicity and benefit of scale production and practical application. The CsxWOyFz powder prepared by adopting the method has the advantages of excellent visible light transmission performance and near infrared shielding performance and broad application prospect in the aspects of light transmitting and heat insulating of buildings and automobile window glasses.

Owner:DALIAN POLYTECHNIC UNIVERSITY

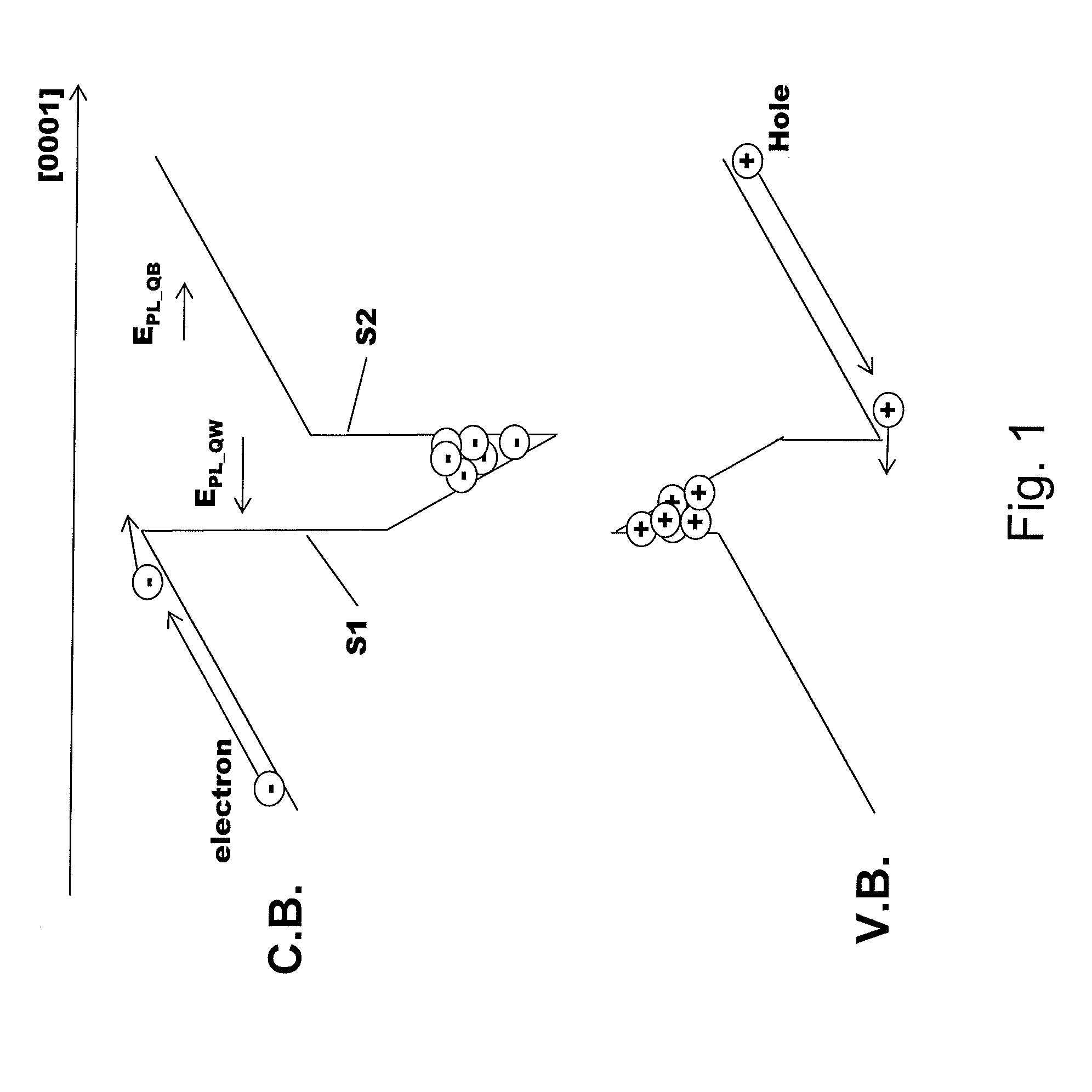

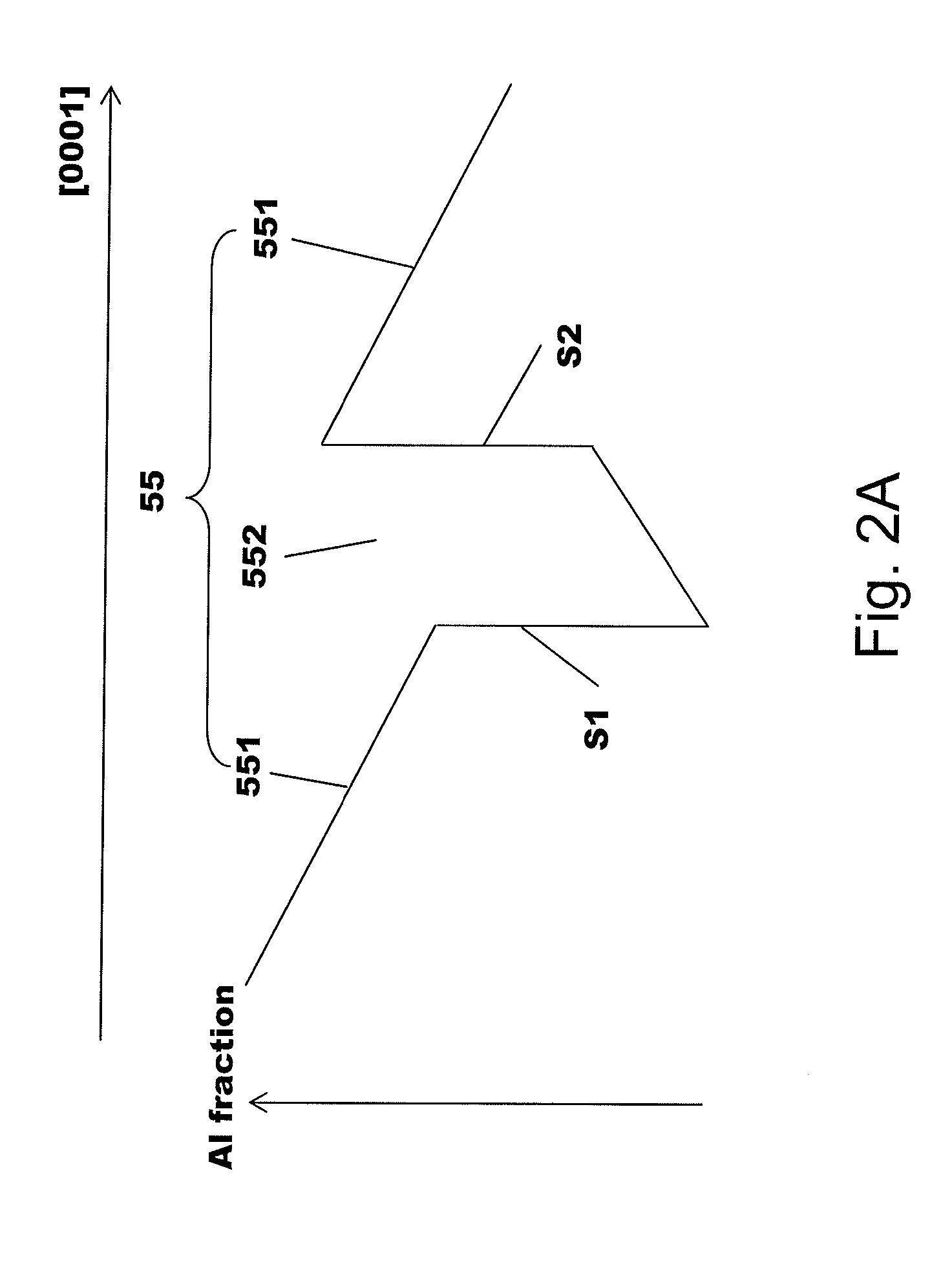

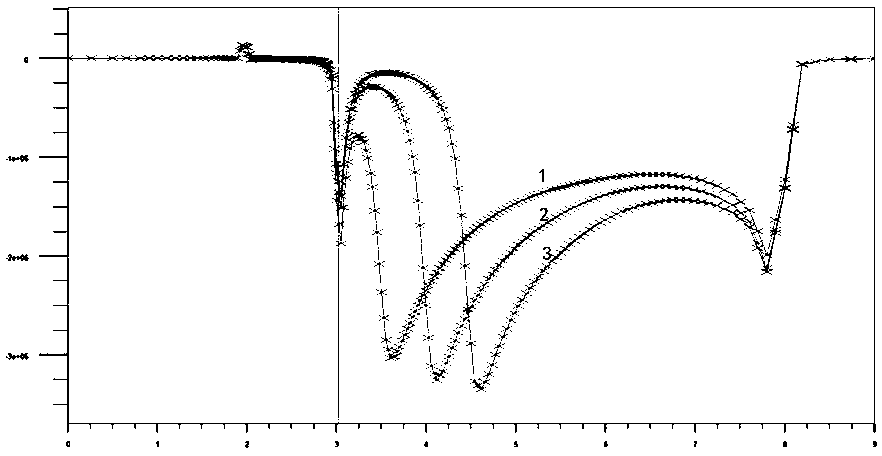

Semiconductor light-emitting device

InactiveUS20140332754A1Mitigate polarization field induced band structure distortionIncrease the bandgap widthSemiconductor devicesQuantum efficiencyLight emitting device

The present invention presents a solid-state semiconductor light emitting device with reduced forward voltage and improved quantum efficiency. The light emitting device is characterized by its multiple-quantum-well active-region with opposite composition grading in the quantum barriers and quantum wells along the device epitaxy direction.

Owner:QINGDAO JASON ELECTRIC

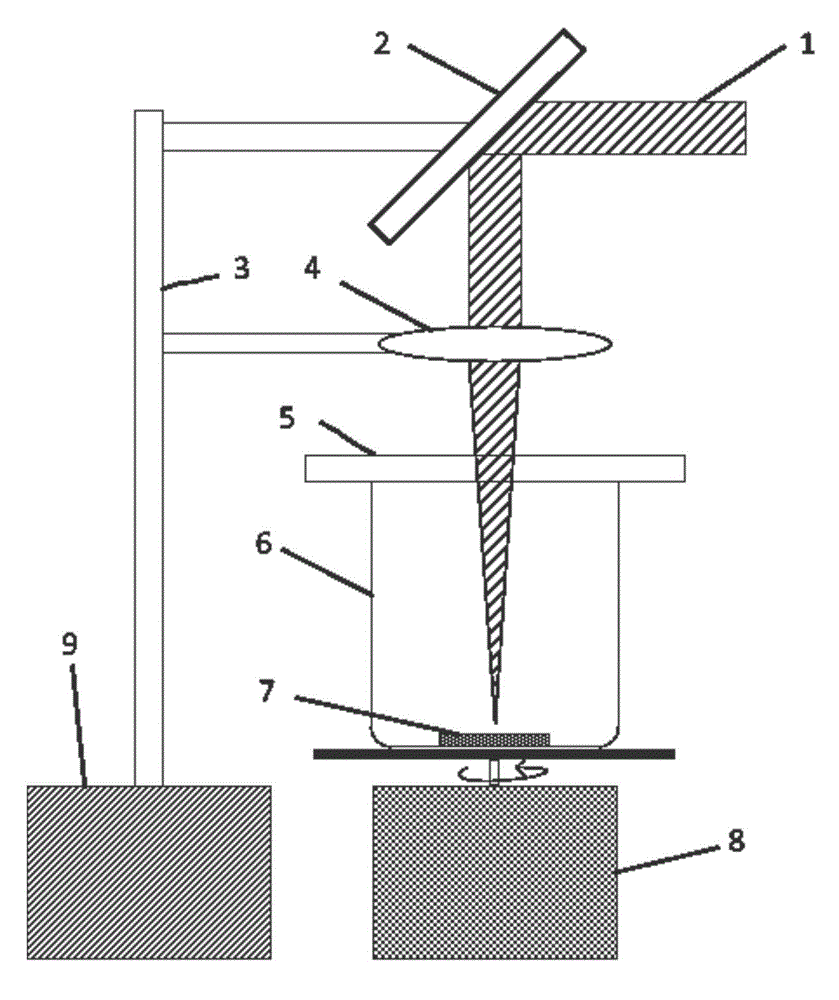

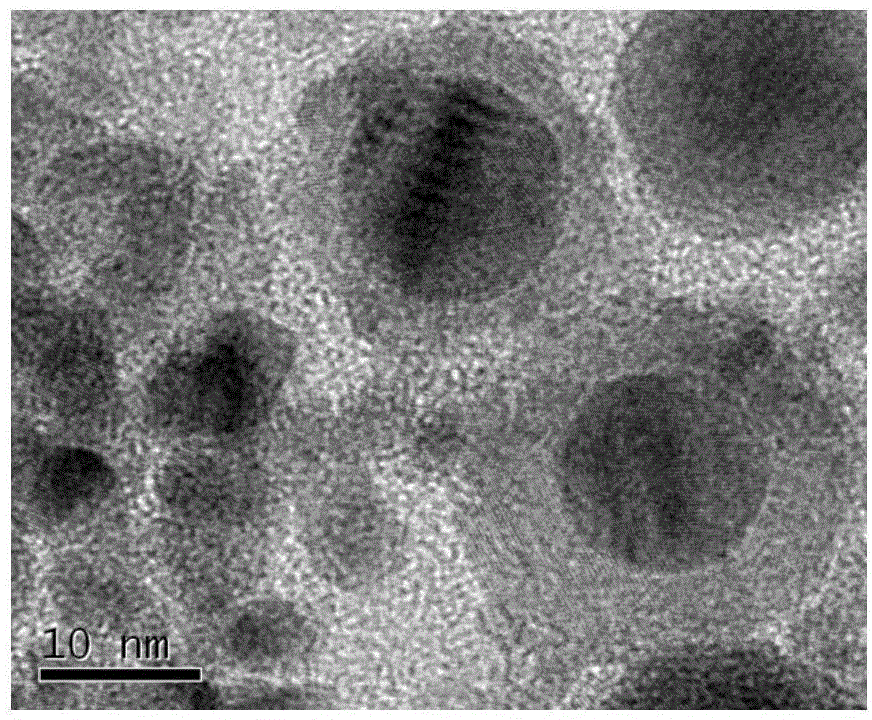

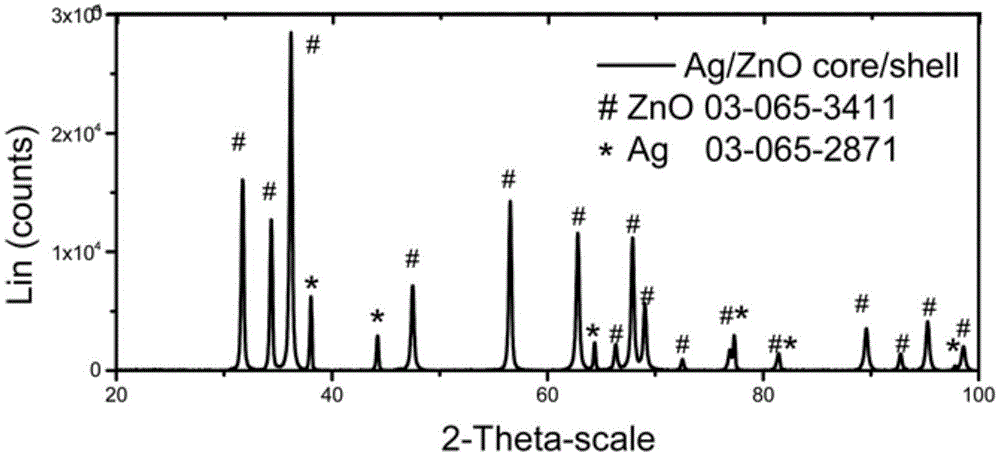

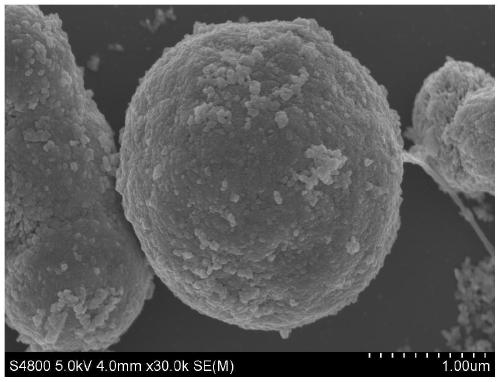

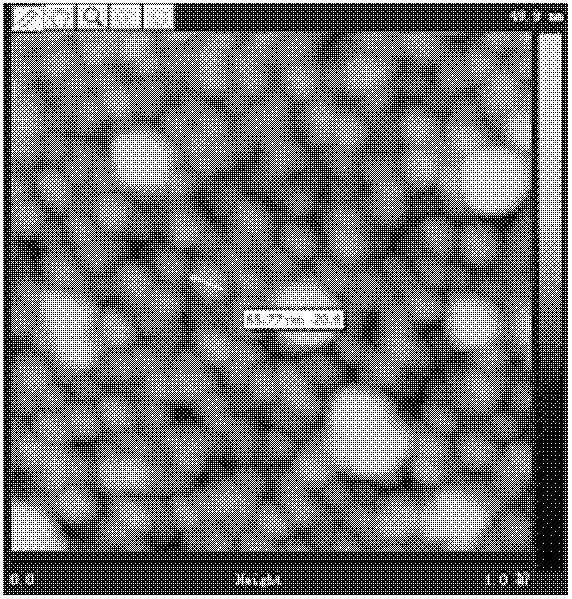

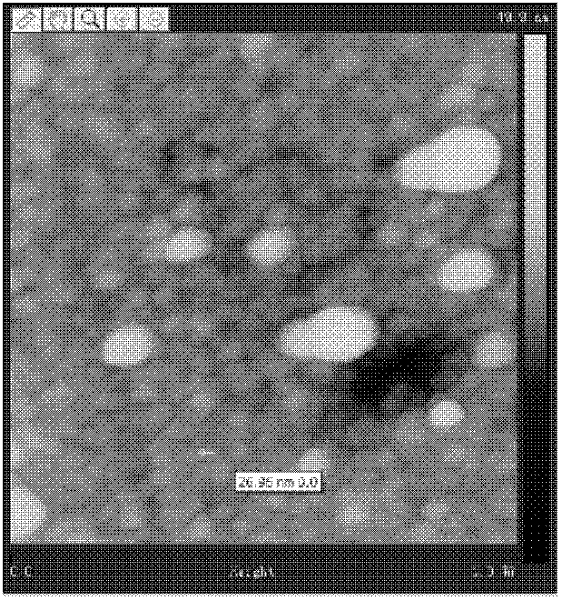

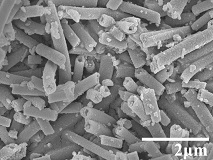

Method for preparing Ag/ZnO core-shell nanostructure by adopting pulse laser liquid ablation

The invention discloses a method for preparing an Ag / ZnO core-shell nanostructure by adopting pulse laser liquid ablation and belongs to the field of material preparation. Two-step pulse laser liquid ablation is adopted, oxide layers of an Ag target and a Zn target are removed by using nitric acid, and ultrasonic cleaning is performed. The method comprises the following steps of ablating the Ag target in deionized water by using excimer laser with the wavelength of 248nm, the single pulse energy of 400mJ and the repetition frequency of 10Hz to obtain Ag colloid; ablating the Zn target in the Ag colloid by using the same laser to obtain the Ag / ZnO core-shell nanostructure. According to the method, preparation equipment is simple, the preparation is quick and safe without pollution, the surface plasma resonance absorption of the prepared Ag / ZnO core-shell nanostructure can be adjusted, and the Ag / ZnO core-shell nanostructure has other excellent photoelectric properties and has a good application prospect in the fields of optics, electrics, catalysis and the like.

Owner:BEIJING UNIV OF TECH

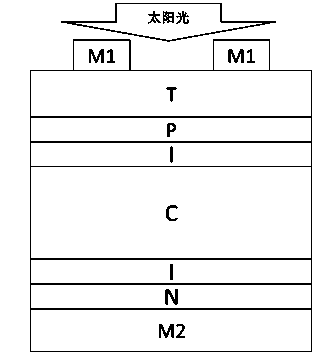

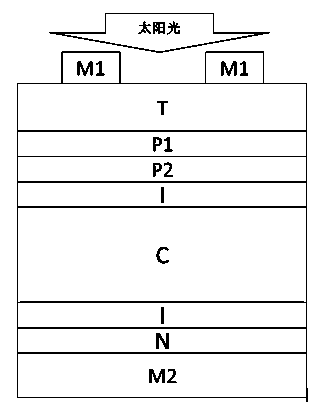

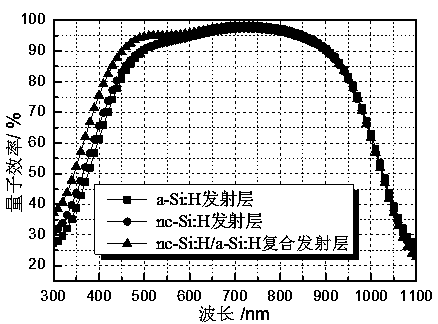

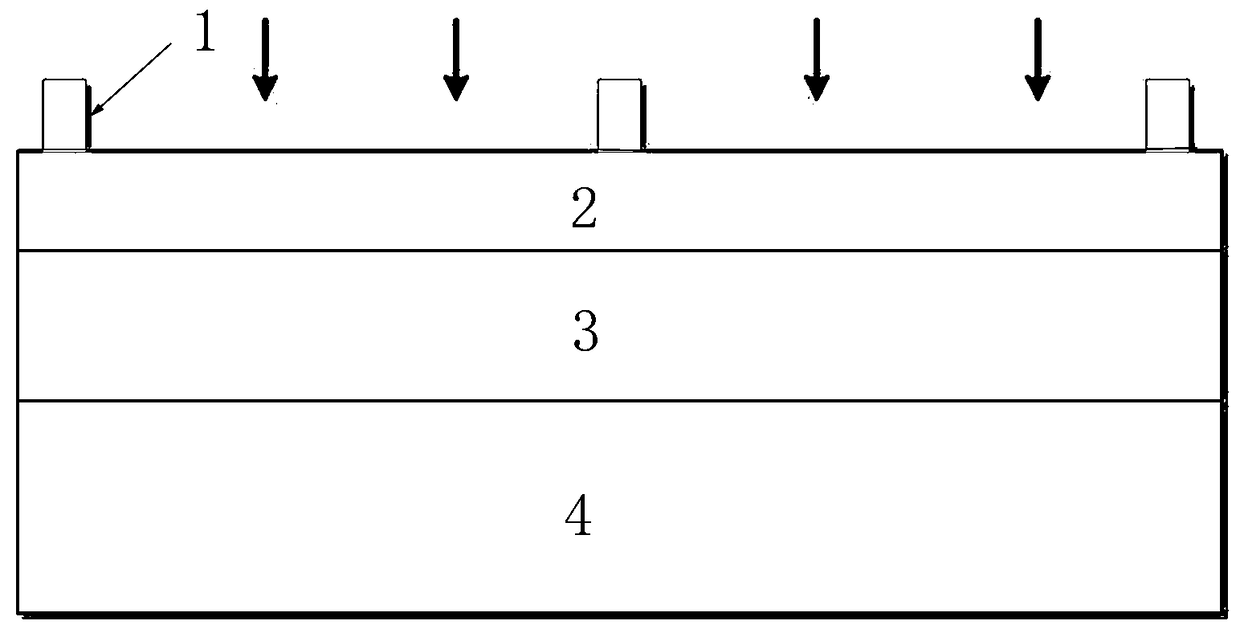

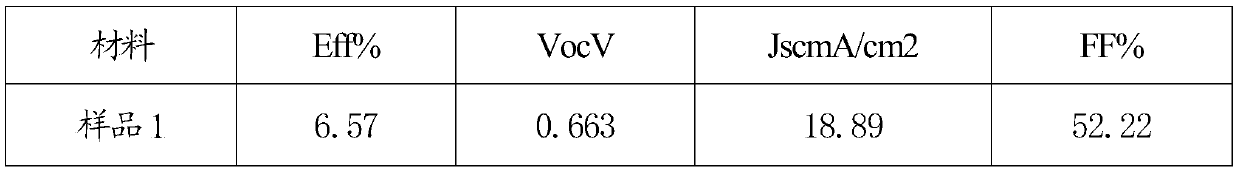

Method for preparing silicon heterojunction solar cell containing composite emission layer

ActiveCN103915523AReduced series resistanceReduce absorptionFinal product manufacturePhotovoltaic energy generationNanocrystalline siliconCrystalline silicon

The invention provides a method for preparing a silicon heterojunction solar cell containing a composite emission layer. The method includes the steps that an amorphous silicon back field N is deposited on one face of a substrate C on which a double-faced intrinsic amorphous silicon passivation layer I is deposited, an amorphous silicon layer P2 with the uniform structure is prepared on the face opposite to the amorphous silicon back field N under the conditions that doping concentration, hydrogen dilution and power density are low, a nanocrystalline silicon layer P1 with the uniform structure is prepared under the conditions that the doping concentration, the hydrogen dilution and the power density are improved, and an amorphous silicon / nanocrystalline silicon composite structure formed by the two silicon films serves as the emission layer of the silicon heterojunction solar cell. Materials have the advantages of being high in transmittance and conductivity through the structure, on the basis, the passivation effect of the surface of crystalline silicon can be improved, short wave response and output characteristics of the cell are improved, and the method for preparing the silicon heterojunction solar cell is simple and easy to carry out.

Owner:捷造科技(宁波)有限公司

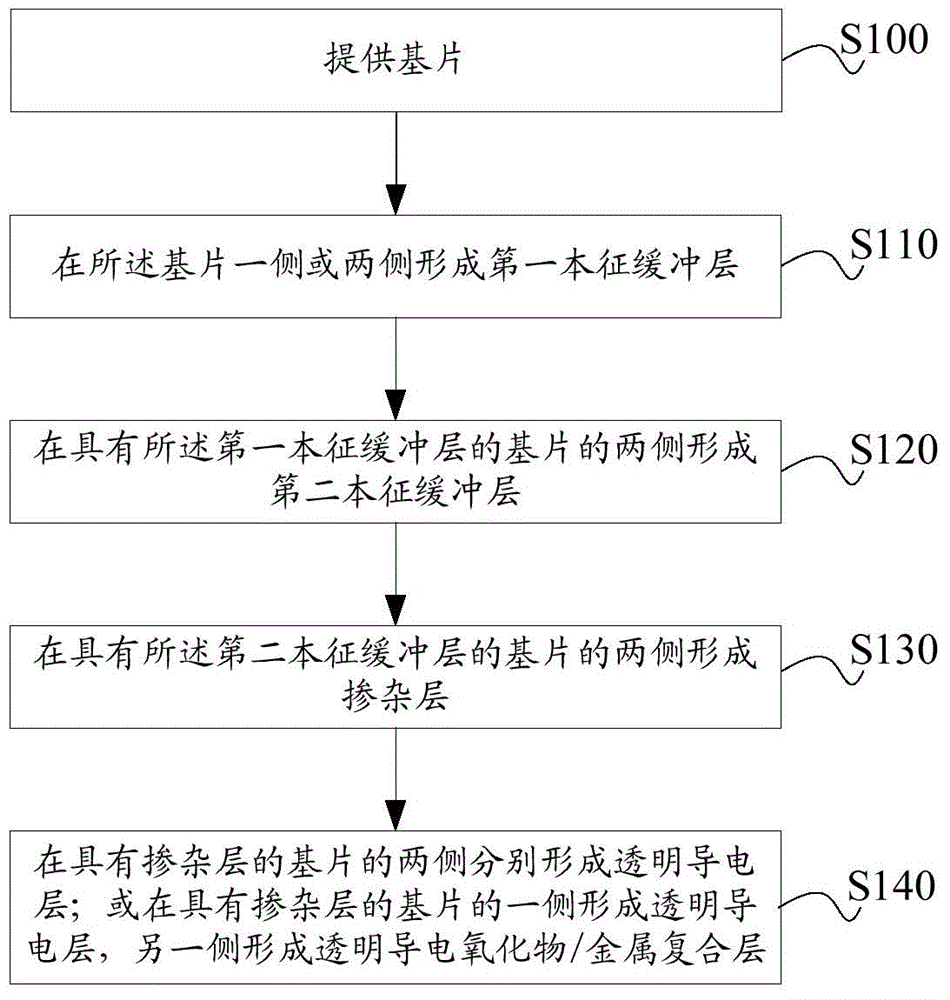

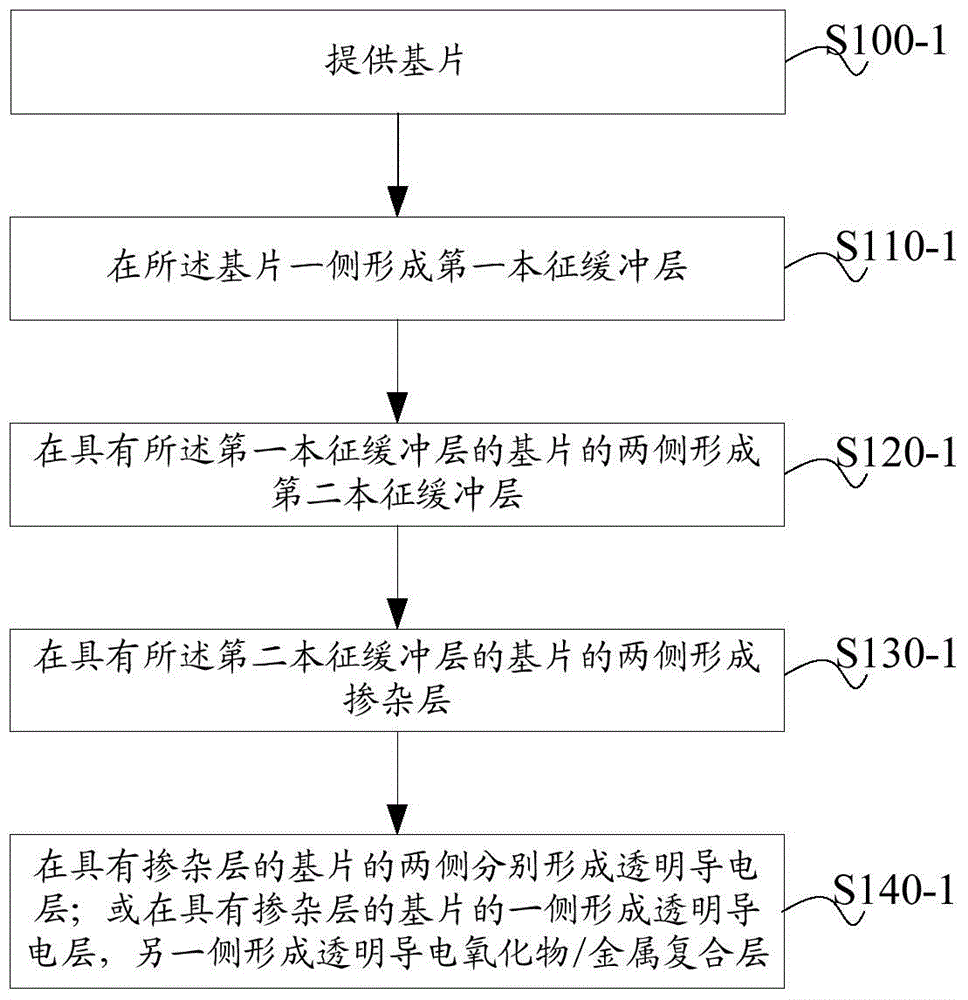

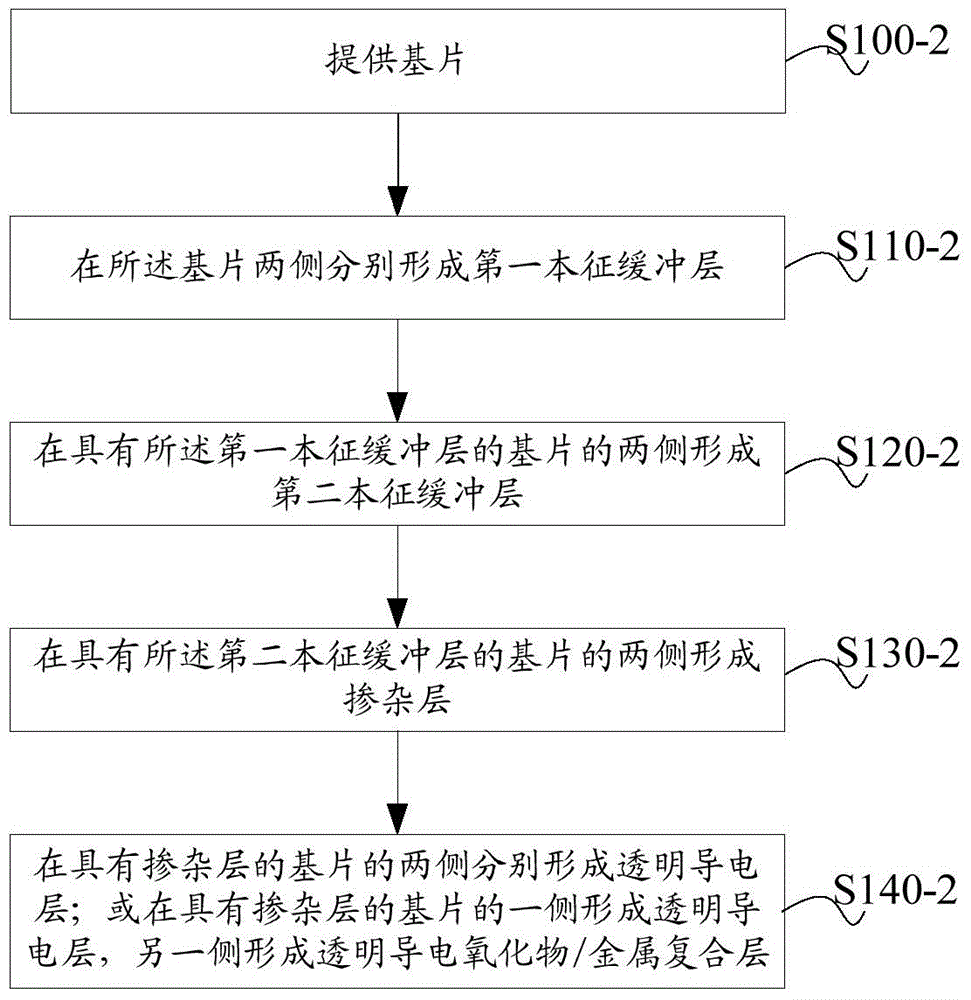

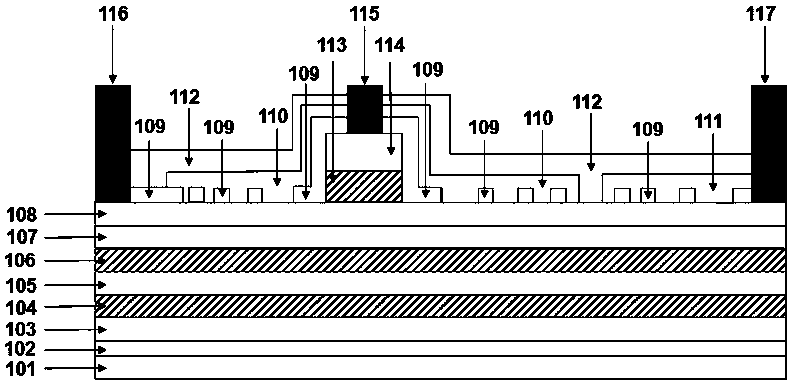

Manufacturing method of hetero-junction solar cell and hetero-junction solar cell

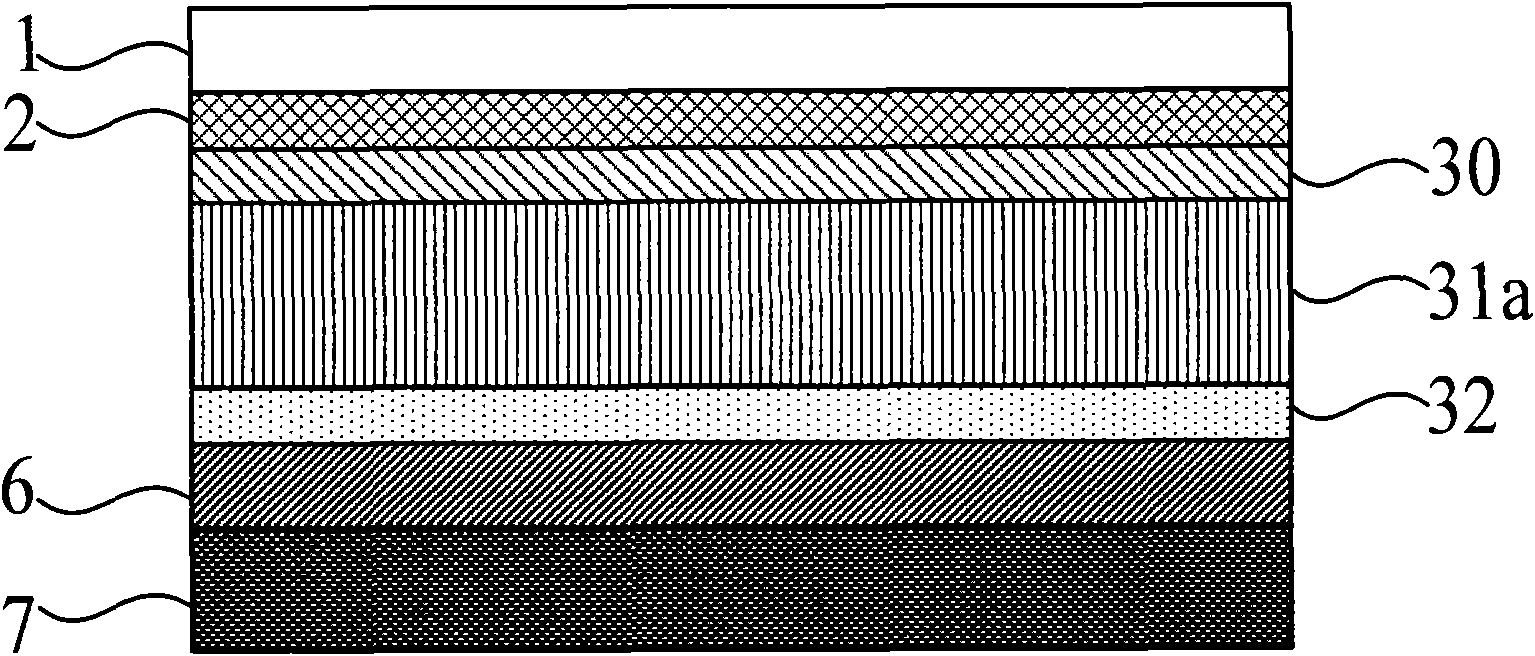

InactiveCN104600157AImprove photoelectric conversion efficiencyImprove battery performanceFinal product manufacturePhotovoltaic energy generationEngineeringConductive oxide

The invention discloses a manufacturing method of a hetero-junction solar cell. The manufacturing method of the hetero-junction solar cell comprises the steps that a substrate is provided; first intrinsic buffer layers are formed on one side or two sides of the substrate; second intrinsic buffer layers are formed on the two sides of the substrate with the first intrinsic buffer layers; doping layers, namely the first doping layer and the second doping layer, are formed on the two sides of the substrate with the second intrinsic buffer layers; transparent conducting layers are formed on the two sides of the substrate with the doping layers; or a transparent conducting layer is formed on one side of the substrate with the doping layers, and a transparent conducting oxide / metal composite layer is formed on the other side of the substrate with the doping layers. Therefore, the photoelectric conversion efficiency of the hetero-junction solar cell is improved. In addition, the invention provides the hetero-junction solar cell.

Owner:APOLLO PRECISION (FUJIAN) LIMITED

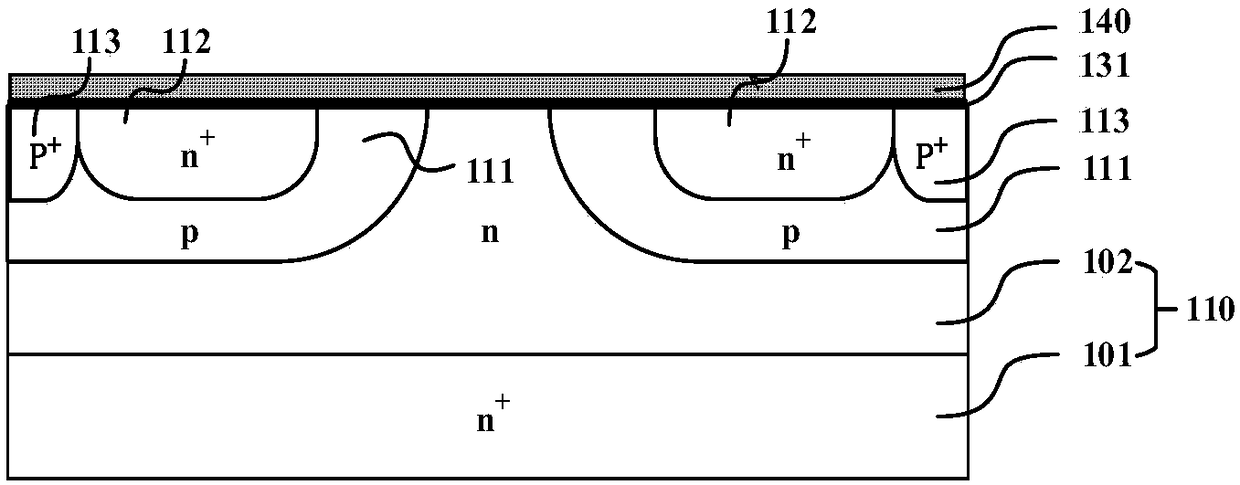

Gallium nitride power device with multi-field plate structure, and preparation method thereof

ActiveCN111370483AImprove pressure resistanceImprove breakdown resistanceEfficient power electronics conversionSemiconductor/solid-state device manufacturingElectrode insertionEngineering

The invention discloses a gallium nitride power device with a multi-field plate structure. The gallium nitride power device is sequentially provided with a substrate, a nucleating layer, a buffer layer, a first insertion layer, a first GaN layer, a second insertion layer, a second GaN layer, an AlGaN barrier layer, a passivation layer, a grid electrode field plate, a drain electrode field plate, aprotective layer, a grid electrode insertion layer, a p-type GaN grid electrode, a grid electrode metal, a source electrode metal and a drain electrode metal from bottom to top, wherein the passivation layer located on the surface of the AlGaN barrier layer is in a strip shape arranged at intervals, the grid electrode field plate and the drain electrode field plate respectively cover part of thepassivation layer, and the surfaces of the grid electrode field plate and the drain electrode field plate and the space between the grid electrode field plate and the drain electrode field plate are covered with the protective layer. According to the invention, the electric field distribution is uniform, the voltage endurance capability of the device is enhanced, the stability of grid electrode turn-on voltage and grid electrode voltage of the device is effectively improved, and the electric leakage of the device under the action of large current is effectively reduced. The preparation methodis completely compatible with a traditional process, and the preparation difficulty is low.

Owner:CHANGSHU INSTITUTE OF TECHNOLOGY

Film solar battery based on crystalline silicon and formation method thereof

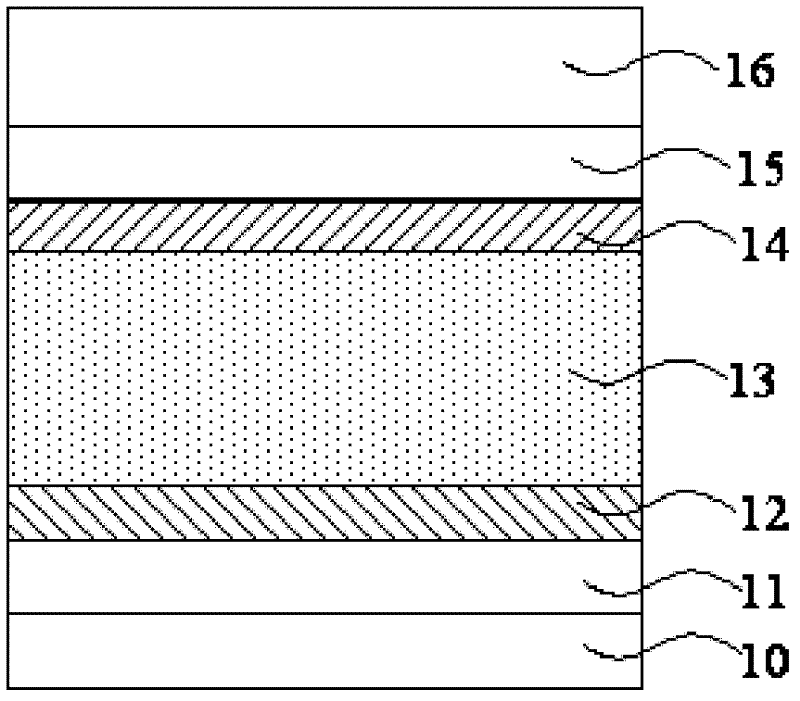

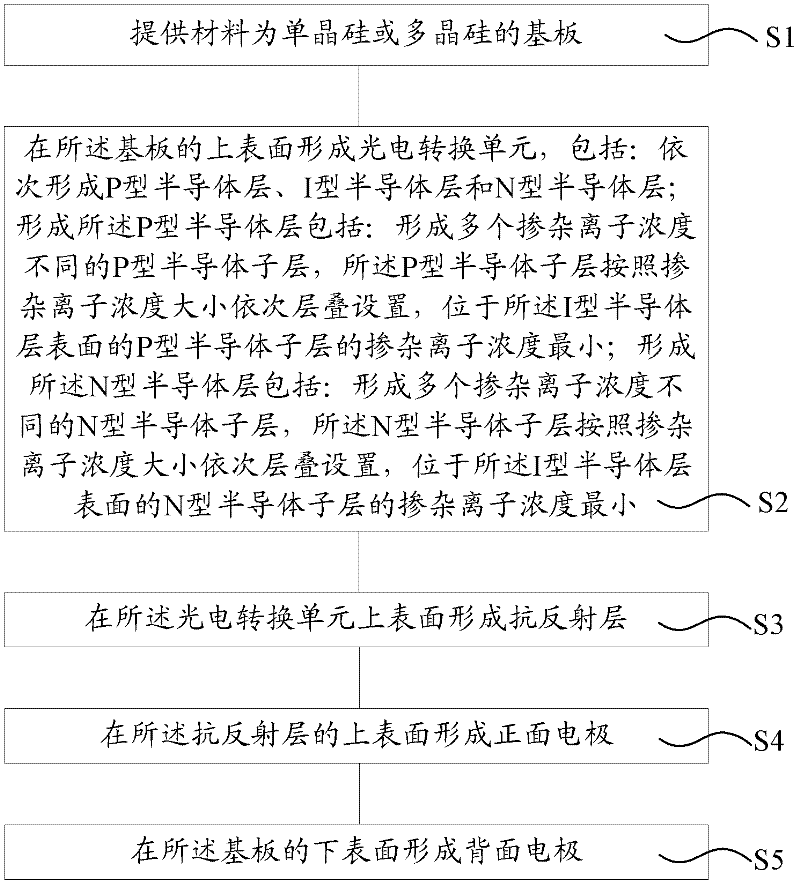

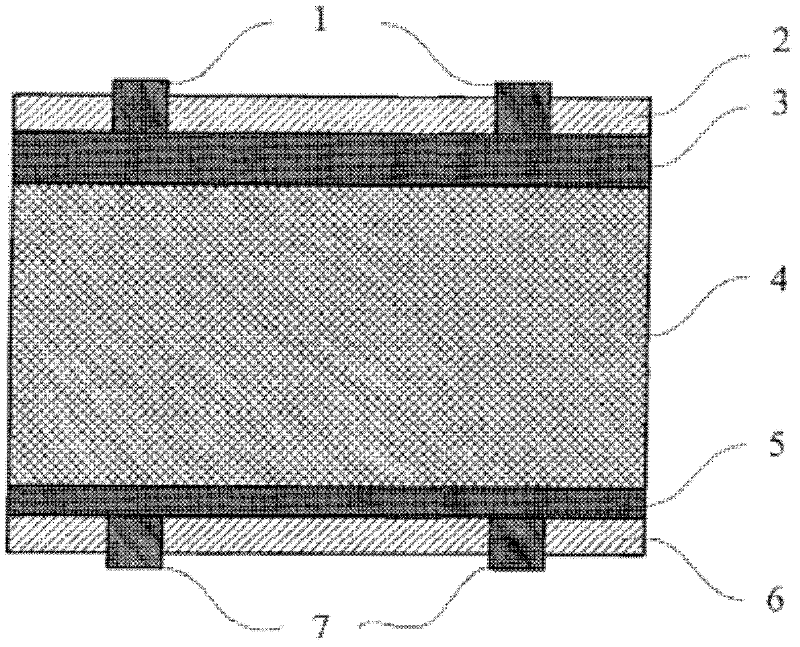

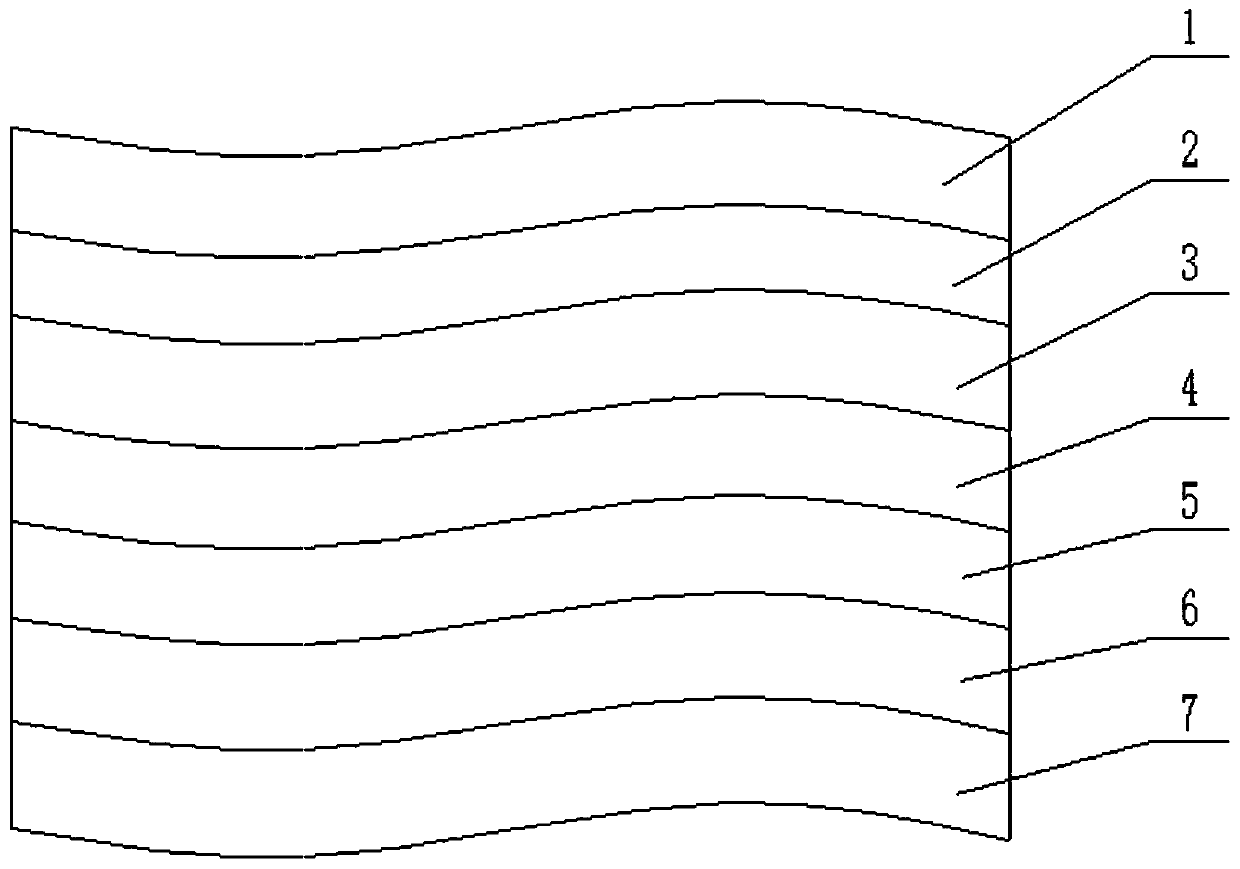

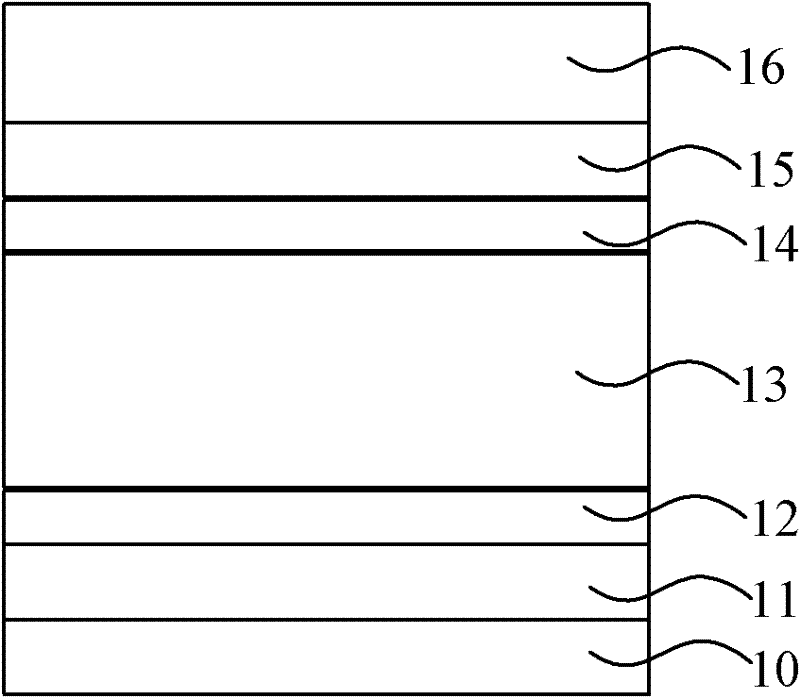

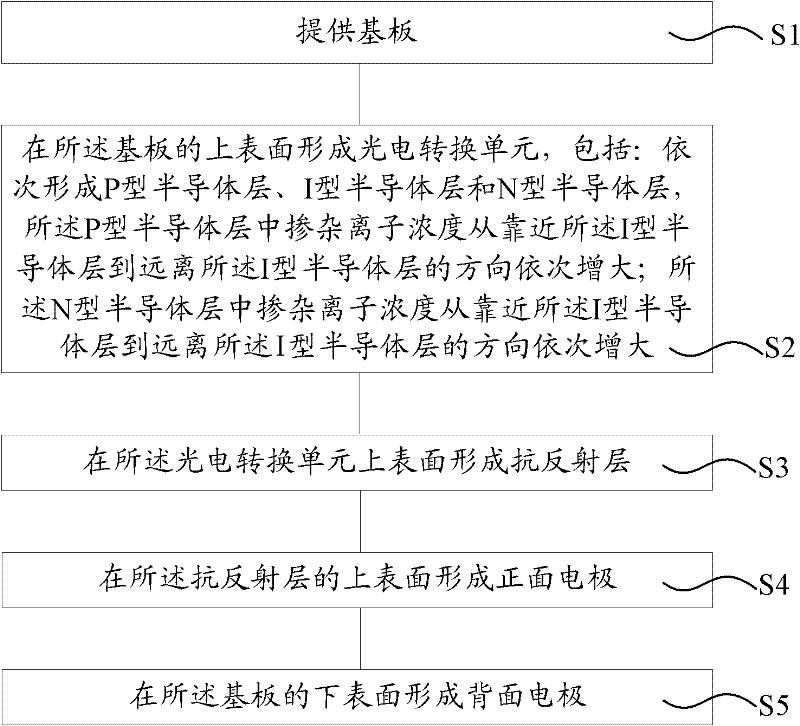

InactiveCN102446990ADoping ion concentration is smallReduce pollutionFinal product manufacturePhotovoltaic energy generationEngineeringPhotoelectric conversion

The invention relates to a film solar battery based on crystalline silicon and a formation method thereof. The battery comprises a baseplate made of monocrystalline silicon or polysilicon, a photoelectric conversion unit positioned on the upper surface of the baseplate, an antireflection layer, a front electrode and a back electrode, wherein the photoelectric conversion unit successively comprises a P-type semiconductor layer, an I-type semiconductor layer and an N-type semiconductor layer,; the P-type semiconductor layer comprises multiple P-type semiconductor sublayers with different doped ion concentrations, and the P-type semiconductor sublayers are successively arranged in a stacking manner according to the doped ion concentrations; the N-type semiconductor layer comprises multiple N-type semiconductor sublayers with different doped ion concentrations, and the N-type semiconductor sublayers are successively arranged in a stacking manner according to the doped ion concentrations; the doped ion concentrations of the P-type semiconductor sublayer and the N-type semiconductor sublayer which are positioned on the surface of the I-type semiconductor layer are minimal; and the antireflection layer is positioned on the upper surface of the photoelectric conversion unit, the front electrode is positioned on the upper surface of the antireflection layer, and the back electrode is positioned on the lower surface of the baseplate. According to the invention, the photoelectric conversion efficiency can be improved.

Owner:SILEVO CHINA

Method of preparing n-type counterfeit ternary erbium-doped thermoelectric material by utilizing mechanical alloying cold pressing sintering method

InactiveCN102925729AAchieve compoundImprove mechanical propertiesThermoelectric device manufacture/treatmentRare-earth elementThermoelectric materials

The invention discloses a method of preparing an n-type counterfeit ternary erbium-doped thermoelectric material by utilizing a mechanical alloying cold pressing sintering method, and relates to a method of preparing a thermoelectric material. The invention solves the technical problems of easiness in separation, poor mechanical property and high material cost of the conventional thermoelectric material. The method comprises the following steps of: 1, mixing a simple substance Bi, a simple substance Sb, a simple substance Te and a simple substance Se, adding a rare earth element Er, and ball-milling to obtain alloy powder; 2, cold-pressing the alloy powder to a block at room temperature; 3, placing the cold-pressing block obtained in the step 2 into a high-temperature-resistant glass tube, sintering, and cooling to room temperature along with a furnace so as to obtain the n-type counterfeit ternary erbium-doped thermoelectric material. The material, prepared by the method in the invention, has a thermoelectromotive force rate close to an oriented crystal, according to the national departmental standard, the Seebeck coefficient of the material is tested to reach 200 muVK<-1>, the conductivity is 55 omega<-1>cm<-1>, and a power factor is close to 2 muWcm<-1>K<-2>.

Owner:HARBIN NORMAL UNIVERSITY

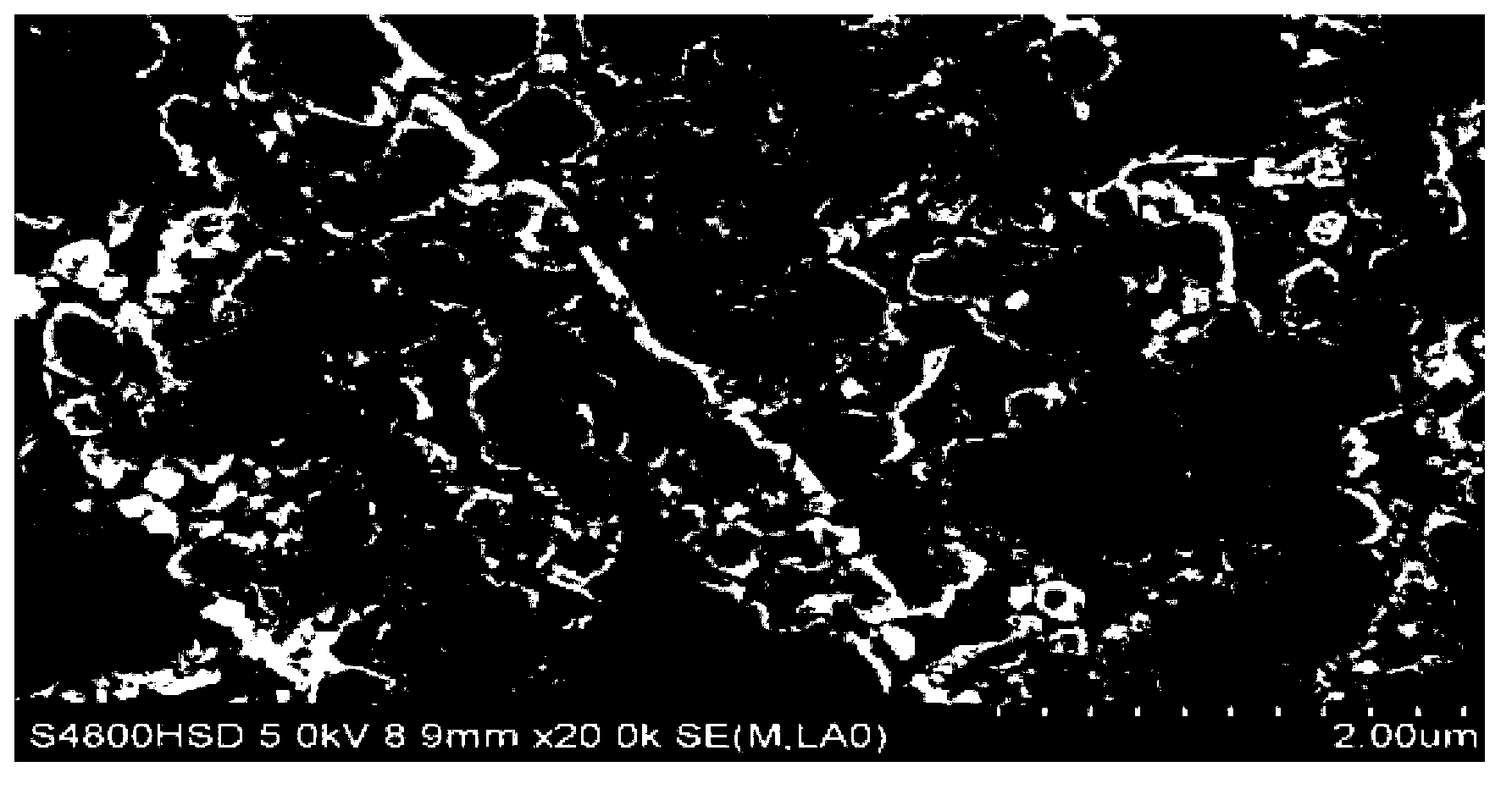

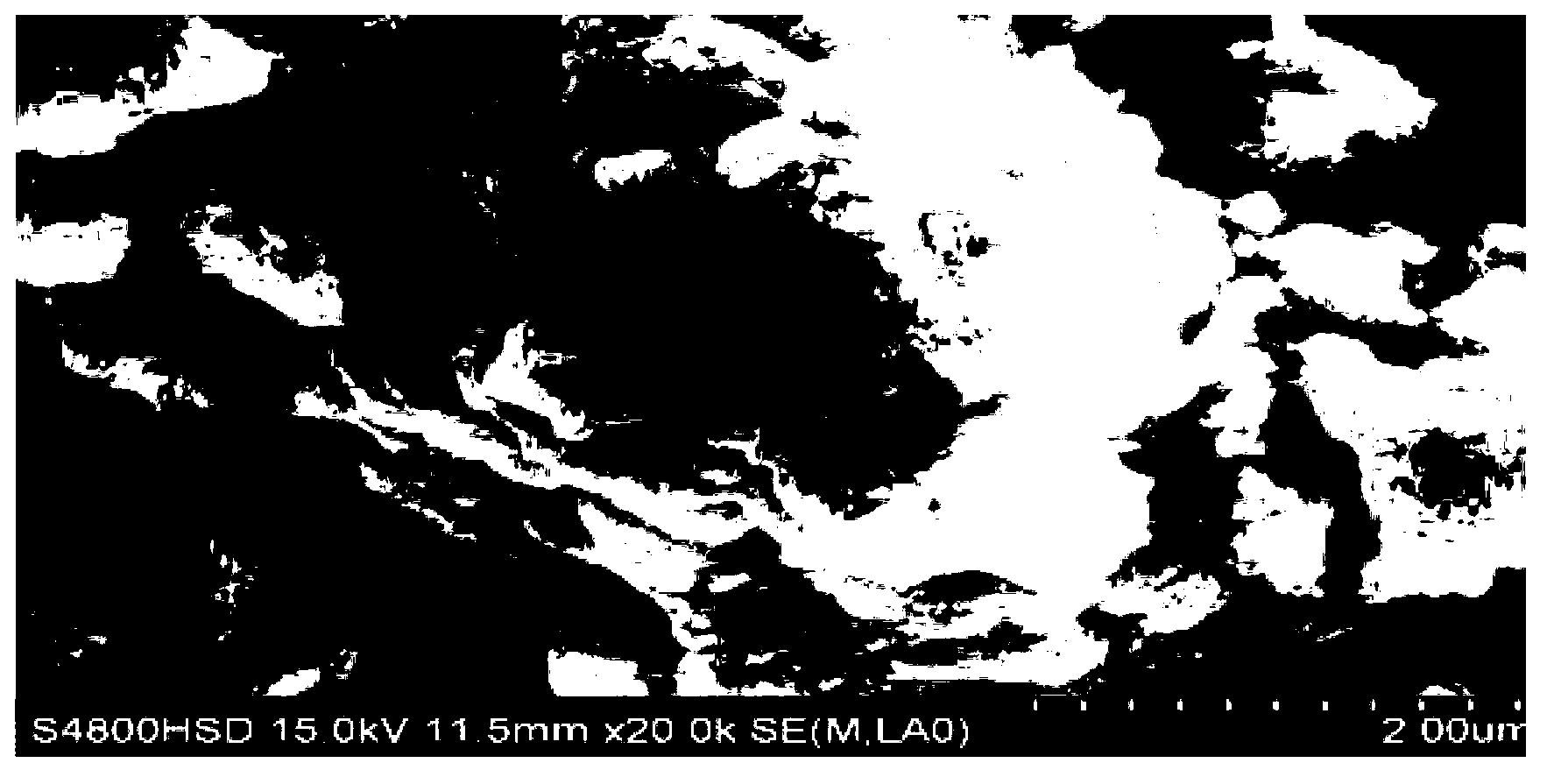

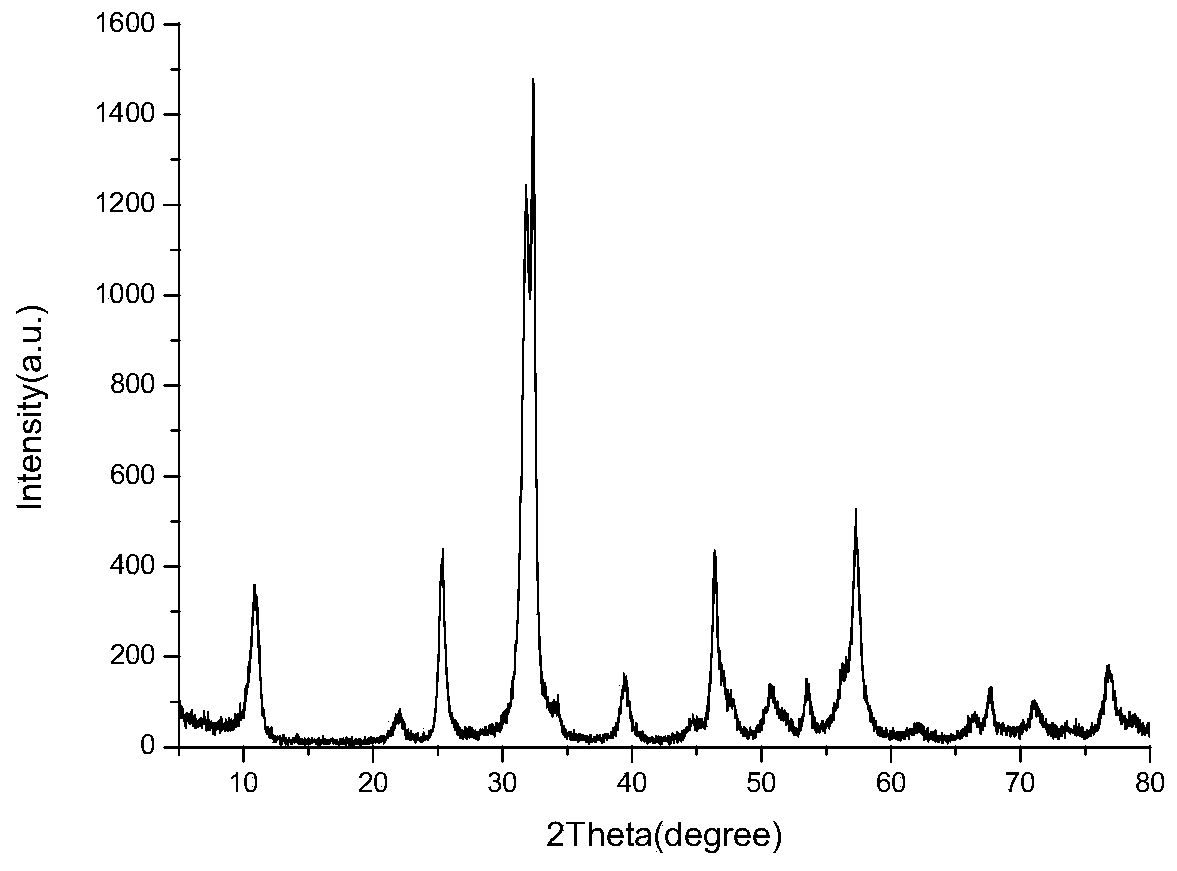

Bismuth oxybromide ternary heterostructure photocatalyst as well as preparation method and application thereof

ActiveCN109759122AIncrease the bandgap widthReduced band gapPhysical/chemical process catalystsWater/sewage treatment by irradiationGraphiteSilver bromide

The invention discloses a preparation method of a bismuth oxybromide ternary heterostructure photocatalyst. The method uses bismuth nitrate pentahydrate, potassium bromide, graphite phase carbon nitride and silver nitrate as raw materials; the prepared graphite phase carbon nitride and silver bromide are compounded with bismuth oxybromide so as to realize modification; the bismuth oxybromide ternary heterostructure photocatalyst is prepared by using a one-step solvothermal method. The modified bismuth oxybromide prepared by the method is purer, has a smaller forbidden band width and a higher visible light absorbing effect. The smaller forbidden band width reduces the transmission distance of photogenerated electron holes, improves the separation efficiency of the photogenerated electron holes, and reduces the recombination rate; the higher light absorption effect improves photon utilization rate, increases the yield of the electron hole pairs, and greatly improves the photocatalytic activity under the visible light. The method has the advantages of being low in cost and convenient to operate; the bismuth oxybromide ternary heterostructure photocatalyst can be used for degrading organic pollutants under the visible light, thus having an important practical value in environmental purification.

Owner:LIAONING UNIVERSITY

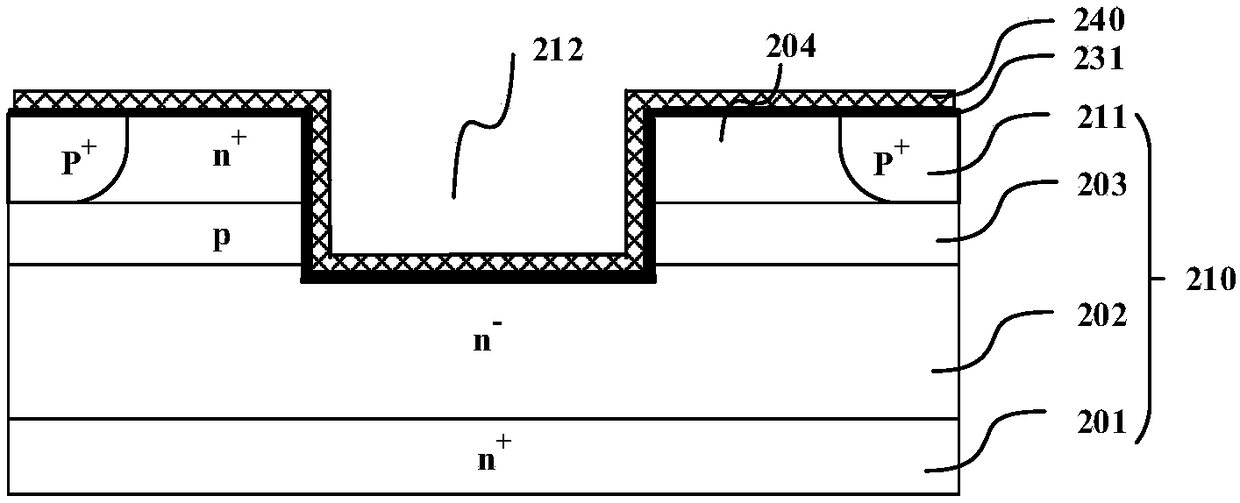

Preparation method of high k-gate dielectric layer and silicon carbide MOS power device

ActiveCN108257855AImprove pressure resistanceEliminate lattice damageSemiconductor/solid-state device manufacturingSemiconductor devicesLattice defectsGate dielectric

The present invention provides a preparation method of a high k-gate dielectric layer and a silicon carbide MOS power device. The preparation method comprises the steps of: performing high-temperaturesacrificial oxidation of a silicon carbide epitaxial wafer with a first conductive type, and forming a sacrificial oxidation layer at the upper surface of the epitaxial layer of the silicon carbide epitaxial wafer; performing corrosion of the sacrificial oxidation layer until the sacrificial oxidation layer on the epitaxial layer is completely removed; performing high-temperature surfacing processing of the upper surface of the epitaxial layer after removal of the sacrificial oxidation layer, and forming a smooth passivated surface; and depositing an Al2O3 dielectric coating layer, a LaAlO3 dielectric layer and an Al2O3 dielectric coating layer at the smooth passivated surface in order, performing annealing of a laminated structure formed by the Al2O3 dielectric coating layer, the LaAlO3dielectric layer and the Al2O3 dielectric coating layer, and forming a high k-gate dielectric layer. Compared to the prior art, the preparation method of the high k-gate dielectric layer and the silicon carbide MOS power device can reduce the interface defects caused by impurities and / or surface lattice defects at a SiC / SiO2 interface so as to improve the voltage endurance capability of the gate dielectric layer.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

Thin film solar battery and manufacturing method thereof

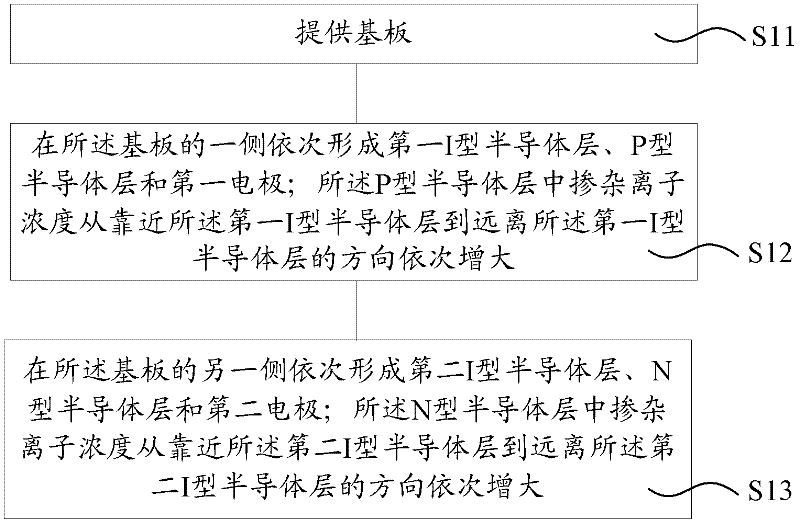

InactiveCN102446992AReduce pollutionIncreased bandgap widthFinal product manufacturePhotovoltaic energy generationIonBand gap

The invention relates to a thin film solar battery and a manufacturing method thereof. The thin film solar battery comprises a substrate, a first I-type semiconductor layer, a P-type semiconductor layer and a first electrode, a second I-type semiconductor layer, an N-type semiconductor layer and a second electrode, wherein the first I-type semiconductor layer, the P-type semiconductor layer and the first electrode are positioned at one side of the substrate in sequence, and the concentration of ions doped in the P-type semiconductor layer successively increases from the direction adjacent to the first I-type semiconductor layer to the direction far away from the first I-type semiconductor layer; the second I-type semiconductor layer, the N-type semiconductor layer and the second electrode are positioned at the other side of the substrate in sequence, and the concentration of ions doped in the N-type semiconductor layer successively increases from the direction adjacent to the second I-type semiconductor layer to the direction far away from the second I-type semiconductor layer. The invention has the beneficial effect that not only can the pollution of the P-type semiconductor layers or the N-type semiconductor layers to the I-type semiconductor layers be reduced, but also the larger band gap width can be obtained, and therefore, the photoelectric conversion efficiency is high.

Owner:SILEVO CHINA

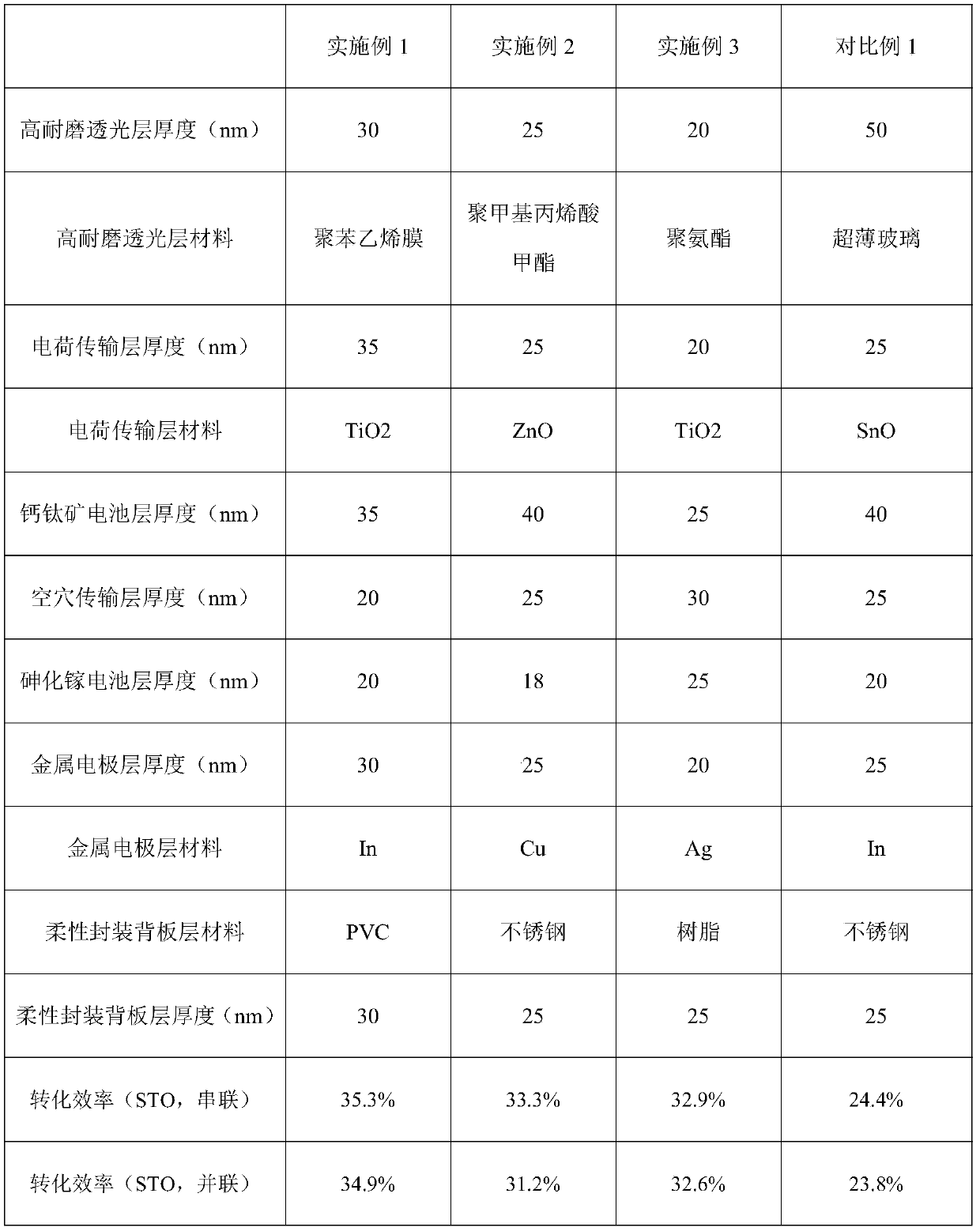

Flexible composite laminated solar cell and preparation method thereof

InactiveCN111490120AIncrease the bandgap widthImprove the combined synergistic effectFinal product manufacturePhotovoltaic energy generationCell layerElectrical battery

The invention discloses a flexible composite laminated solar cell and a preparation method thereof. The composite laminated solar cell sequentially comprises a high-wear-resistance light-transmittinglayer, a charge transmission layer, a perovskite cell layer, a hole transmission layer, a gallium arsenide cell layer, a metal electrode layer and a flexible packaging backboard layer from a light receiving surface to a backlight surface. The structure is a thin-layer flexible structure and can be bent, curled and folded; according to the invention, the problems of gallium arsenide energy loss andlattice mismatch are solved, the energy gap is large, the overall conversion efficiency is improved, and the service life is prolonged. According to the invention, the charge transport layer is prepared by adopting a spraying method, the hole transmission layer is prepared by adopting a spray pyrolysis method, the metal electrode layer is prepared by adopting a coating method, and the flexible packaging backboard layer is prepared by adopting a thermal bonding method; the preparation difficulty is reduced while the thin layer preparation requirement is met, industrial popularization is facilitated, layer-to-layer combination is facilitated through selection of the preparation method, and then the conversion efficiency is improved.

Owner:兴储世纪科技股份有限公司

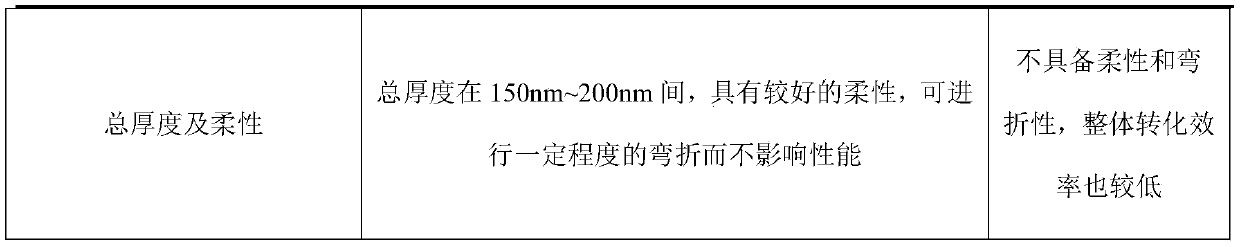

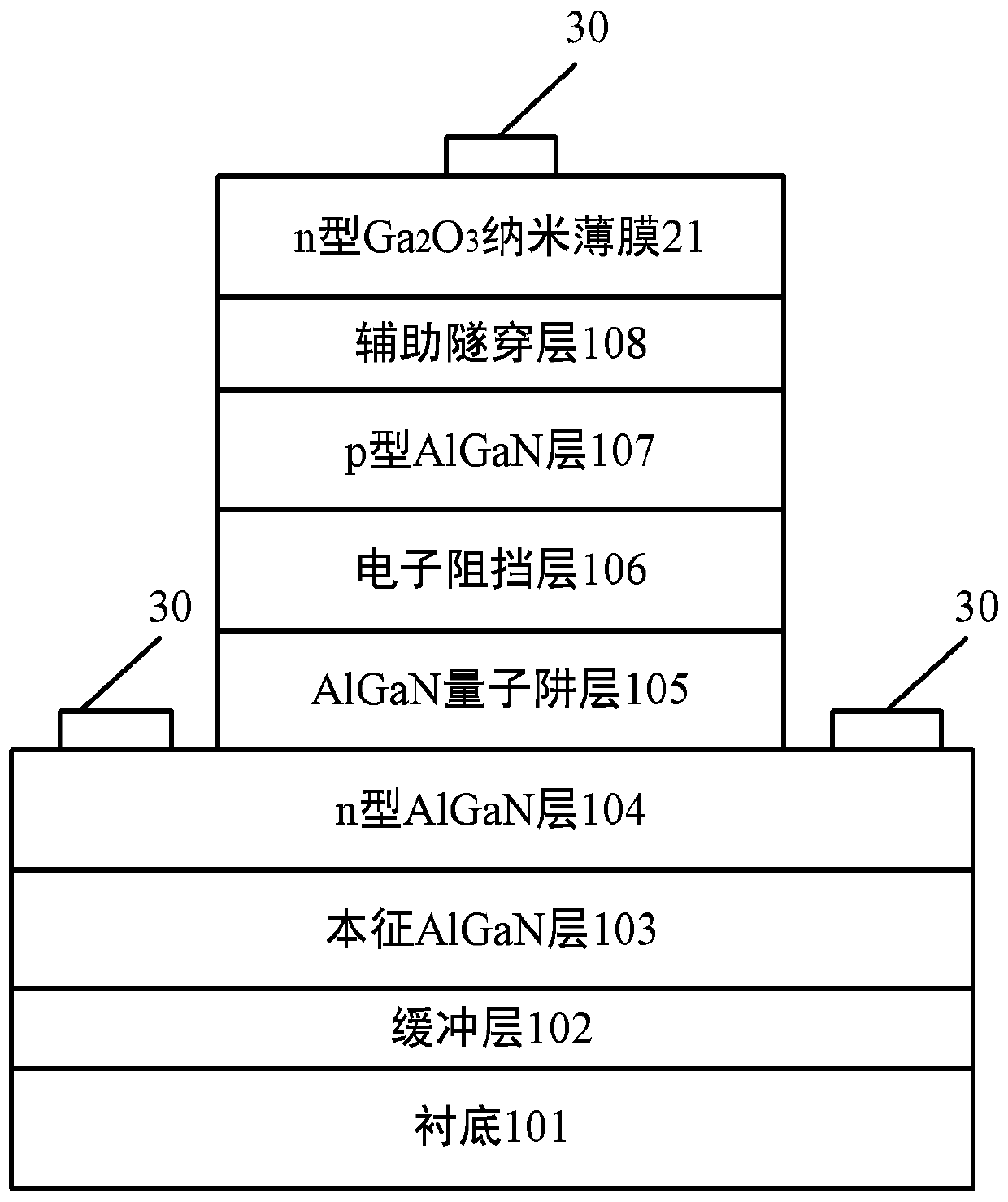

Deep ultraviolet LED structure and manufacturing method thereof

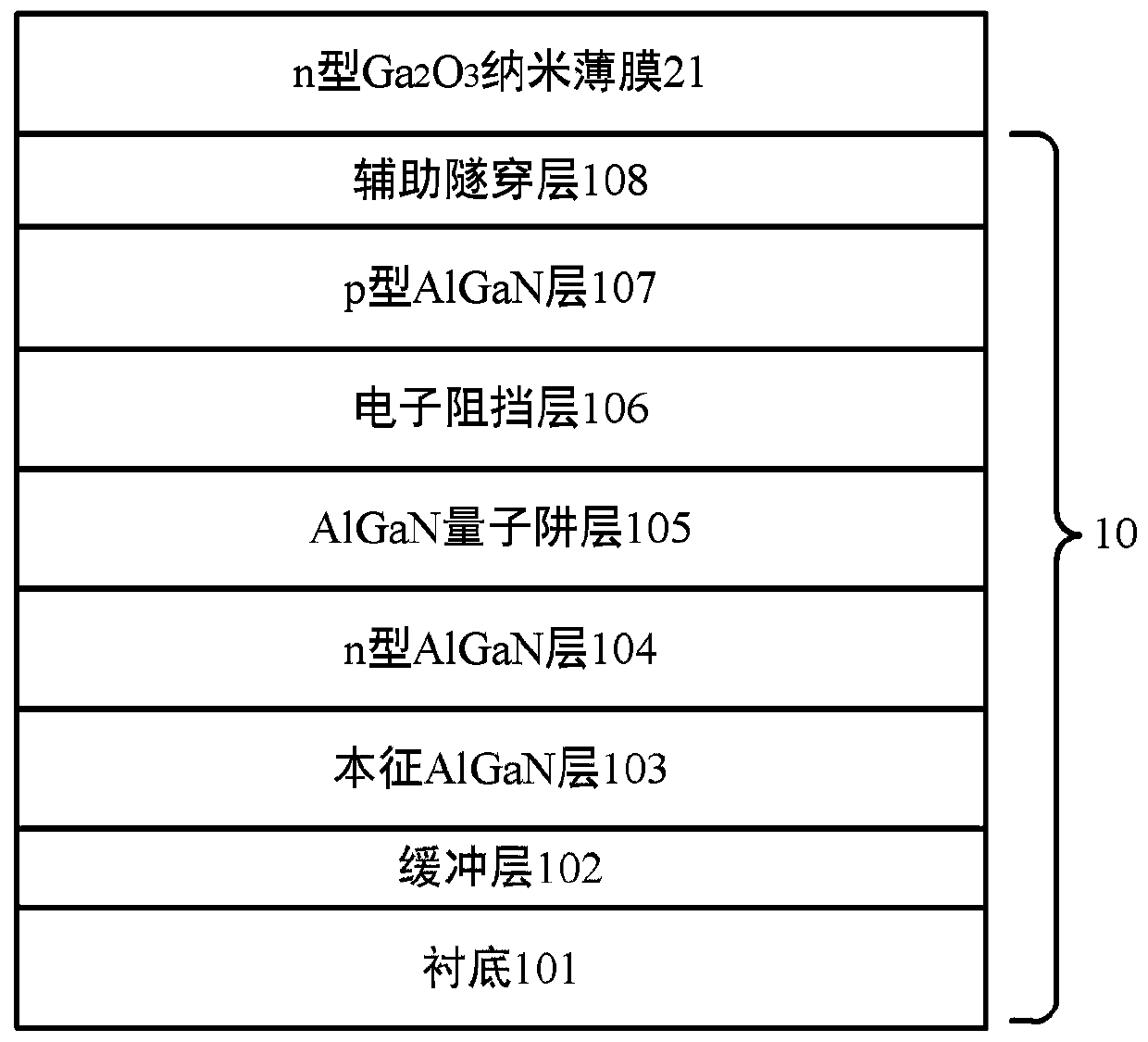

ActiveCN110808320ASolve the doping concentrationSolve the problem of low injection efficiencySemiconductor devicesQuantum efficiencyOhmic contact

The invention discloses a deep ultraviolet LED structure and a manufacturing method thereof. The deep ultraviolet LED structure comprises a deep ultraviolet AlGaN epitaxial structure and an n-type Ga2O3 nano thin film, wherein the deep ultraviolet AlGaN epitaxial structure comprises a p-type AlGaN layer; the n-type Ga2O3 nano thin film is positioned on the upper surface of the deep ultraviolet AlGaN epitaxial structure; the n-type Ga2O3 nano thin film and the p-type AlGaN layer form a tunnel junction, and the tunnel junction is used as a surface electrode contact layer and a hole supply layer.The tunnel junction is formed by using the n-type Ga2O3 nano thin film and the p-type AlGaN layer, on one hand, the tunnel junction is used as a hole supply layer to improve the hole concentration, and on the other hand, the tunnel junction is used as a surface electrode contact layer and forms good ohmic contact with the surface electrode, so that the external quantum efficiency of the deep ultraviolet LED is improved, and meanwhile, the n-type Ga2O3 nano thin film has relatively high transmittance for light in a deep ultraviolet band and does not absorb light generated by the LED.

Owner:TSINGHUA UNIV

Al-doped gallium oxide X-ray detector and preparation method thereof

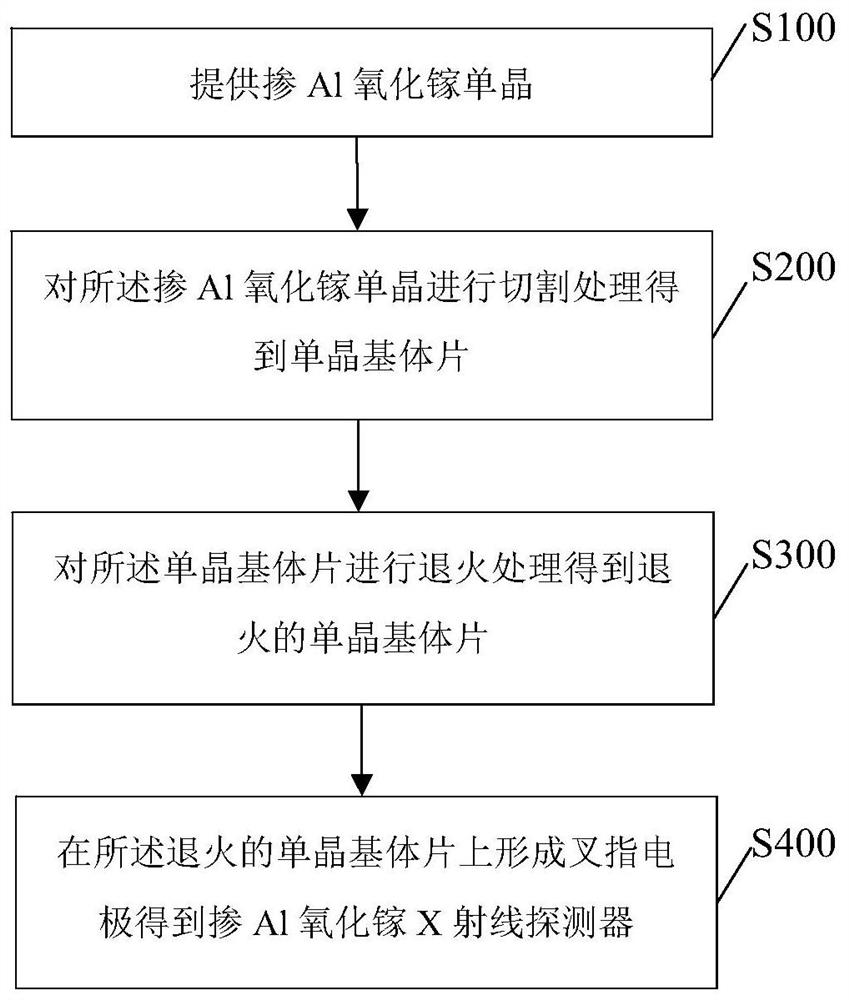

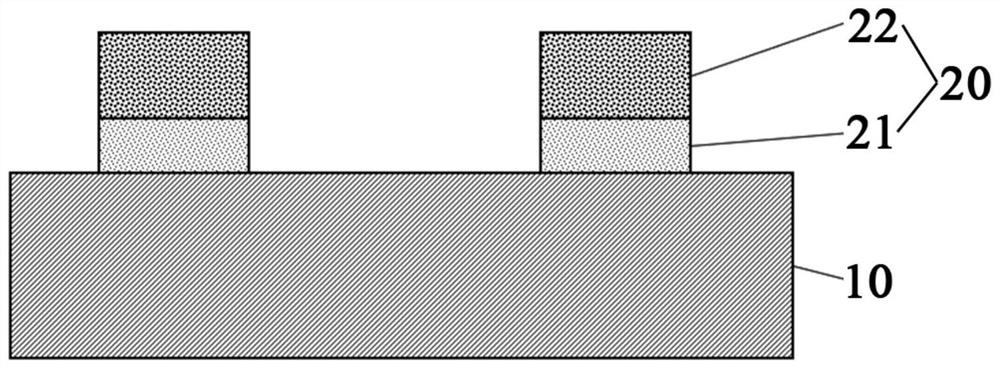

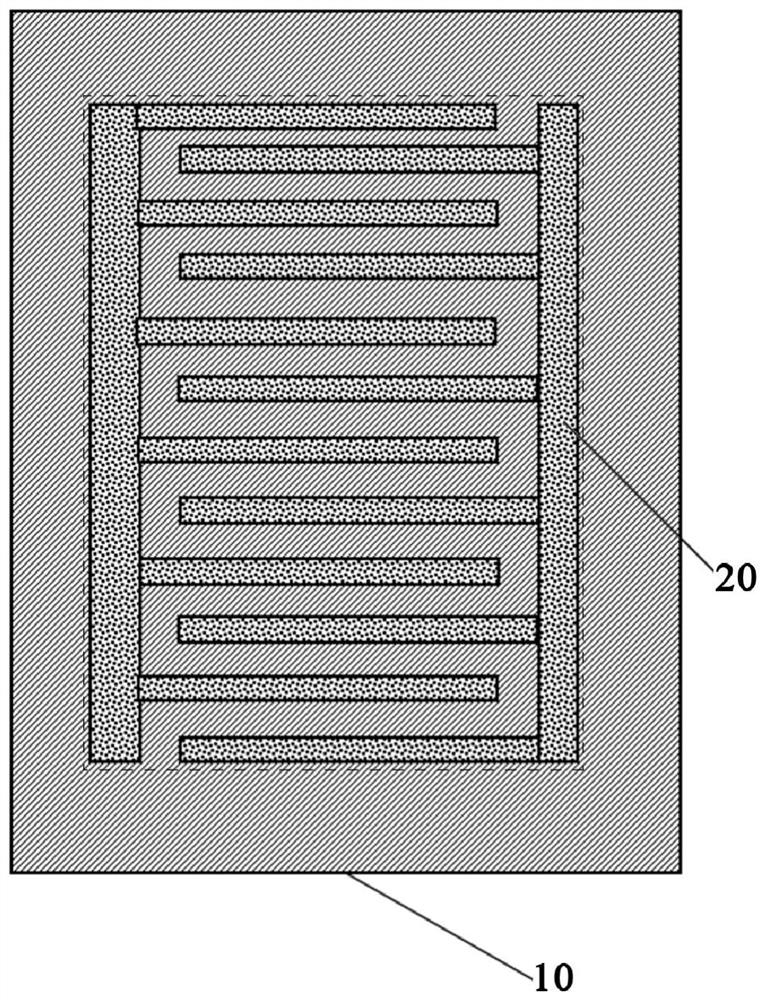

PendingCN113035999AReduce the concentration of free electronsHigh sensitivityFinal product manufactureSemiconductor devicesSingle crystal substrateSingle crystal

The invention discloses an Al-doped gallium oxide X-ray detector and a preparation method thereof. The preparation method of the Al-doped gallium oxide X-ray detector comprises the following steps of: providing an Al-doped gallium oxide single crystal; cutting the Al-doped gallium oxide single crystal to obtain a single crystal substrate sheet; carrying out annealing treatment on the single crystal substrate sheet to obtain an annealed single crystal substrate sheet; and forming an interdigital electrode on the annealed single crystal substrate sheet to obtain the Al-doped gallium oxide X-ray detector. According to the method, the Al-doped gallium oxide single crystal is adopted, the resistivity of the detector is improved by doping Al in gallium oxide, the single crystal substrate sheet is obtained after the Al-doped gallium oxide single crystal is cut, the single crystal substrate sheet is subjected to annealing treatment, and the concentration of free electrons in the Al-doped gallium oxide single crystal is reduced through annealing treatment, so that the sensitivity of the detector is improved.

Owner:HANGZHOU FUJIA GALLIUM TECH CO LTD

Thin film solar cell and formation method thereof

InactiveCN102447000AReduce pollutionImprove photoelectric conversion efficiencyFinal product manufacturePhotovoltaic energy generationPhotoelectric conversionSemiconductor

The invention relates to a thin film solar cell and a formation method thereof. The thin film solar cell comprises a substrate, a photoelectric conversion unit, an anti-reflective layer, a positive electrode, and a backplate. The photoelectric conversion unit, which is arranged on the upper surface of the substrate, includes a P type semiconductor layer, an I type semiconductor layer, and an N type semiconductor layer; doped ion concentration in the P type semiconductor layer is successively increased along a direction from a position close to the I type semiconductor layer to a position far from the I type semiconductor layer; and doped ion concentration in the N type semiconductor layer is successively increased along a direction from a position close to the I type semiconductor layer to a position far from the I type semiconductor layer. Besides, the anti-reflective layer is arranged on the upper surface of the photoelectric conversion unit; the positive electrode is arranged on the upper surface of the anti-reflective layer; and the backplate is arranged on the lower surface of the substrate. According to the invention, pollution on an I type semiconductor layer by a P type semiconductor layer or an N type semiconductor layer can be reduced; and a broad band gap can be realized; therefore, photoelectric conversion efficiency is high.

Owner:SILEVO CHINA

Three-laminated-layer thin film solar cell and preparation method thereof

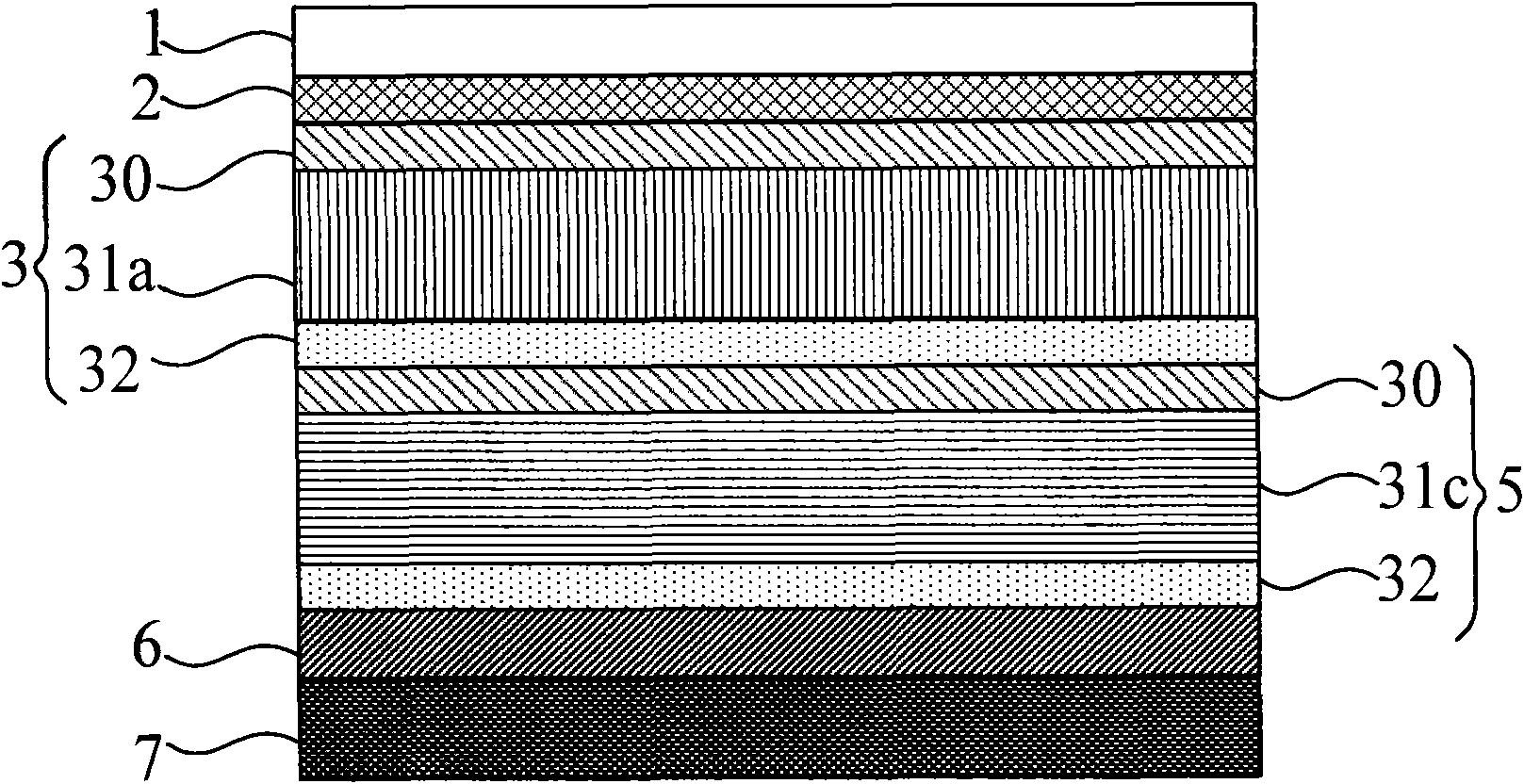

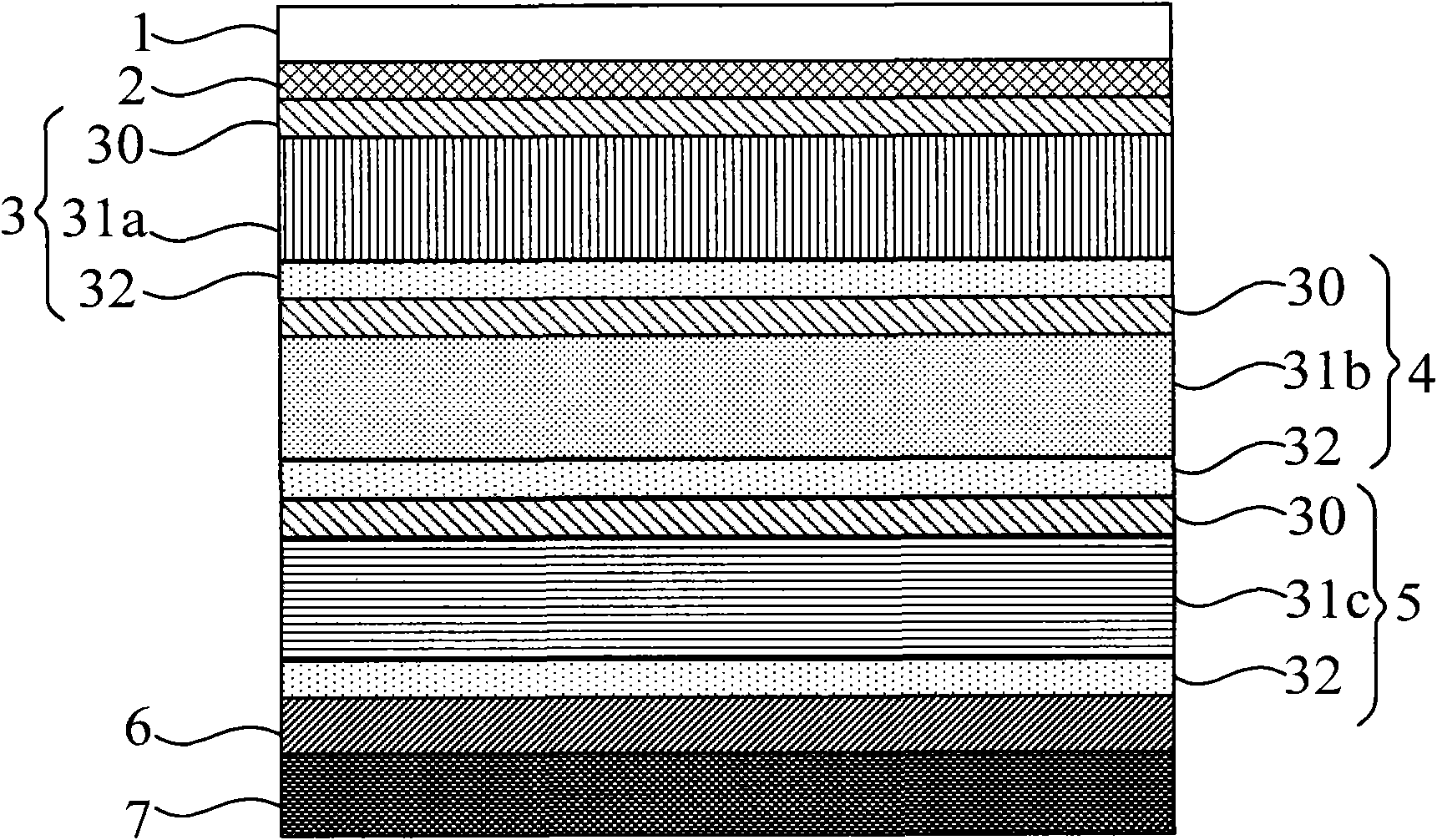

ActiveCN102117860AIncrease the bandgap widthBroaden the spectral absorption rangeFinal product manufacturePhotovoltaic energy generationCarbon layerSilanes

The invention relates to a three-laminated-layer thin film solar cell and a preparation method thereof, wherein the three-laminated-layer thin film solar cell comprises a top cell, a middle cell and a bottom cell, wherein each cell comprises a P-type doping layer, an intrinsic layer and an N-type doping layer, and the intrinsic layer of the top cell is an intrinsic nano-silicon film, wherein the crystallite dimension is 2 to 10 nanometers and the crystallization rate is 10 to 20 percent. In the preparation method of the three-laminated-layer thin film solar cell, the intrinsic nano-silicon film is deposited on a boron-doped amorphous silicon carbon layer with a silane-hydrogen mixed gas under the deposition gas pressure of 1.0 to 1.5 Torr at the deposition temperature of 180 to 220 DEG C with the glow power of 15 to 30 watts when the intrinsic layer of the top cell is formed, wherein the silane concentration of the silane is 1 to 5 percent. The three-laminated-layer thin film solar cell and the preparation method thereof can improve the band gap width of the top cell, enlarge the spectrum absorption range of the thin film solar cell, and overcome S-W effect, thus improving the photoelectric conversion efficiency.

Owner:BOE TECH GRP CO LTD +1

Nitrogen-doped nickel oxide and zinc oxide near ultraviolet detector

InactiveCN109301026AIncrease the carrier concentrationHigh sensitivitySemiconductor devicesPhysicsElectric field

The invention discloses a nitrogen-doped nickel oxide and zinc oxide near ultraviolet detector of the following structure of Ag / NiO:N / ZnO / FTO conductive glass, and FTO represents fluorine doped indiumoxide. According to the detector, the carrier concentration in NiO is improved, the conductivity is increased, a built-in electric field is enhanced, the forbidden band is narrower, absorption wavelength moves towards the long wave direction, and the detector is highly sensitive to weak UVA near ultraviolet.

Owner:ZHEJIANG NORMAL UNIVERSITY

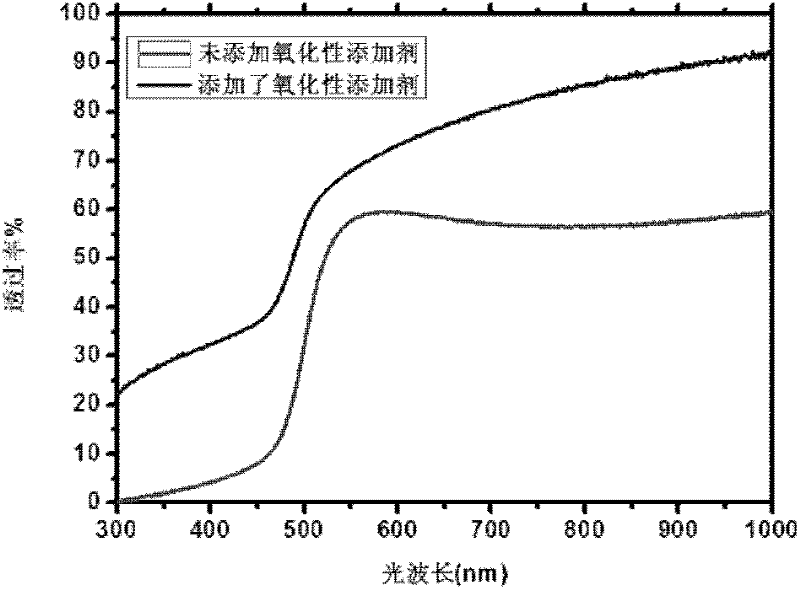

Method for preparing wide bandgap nanometer cadmium sulfide thin film

The invention relates to a method for preparing a wide bandgap nanometer cadmium sulfide thin film, which comprises the following steps that: indium tin oxide (ITO) glass using as substrates is placed in a reaction container after organic solvent soaking, ultrasonic cleaning and drying, and oxidbillity additives are added into reaction solution; in the reaction solution preparation stage, cadmiumsalt and the same acid radical ammonium salt are added into the container, de-ionized water is then added, when the temperature is heated to 40 to 70 DEG C, the proper amount of weak base aqueous solution (ammonia solution) is added for producing cadmium complex compounds, and the reaction solution in the first step is formed; and the weak base solution is added, simultaneously, the oxidbillity additives are added, the additives are organic peroxide (ROOH), organic peroxyacetic acid (RCOOOH) and 2 percent to 30 percent of oxyful, and the addition quantity of the oxidbillity additives is 1 percent to 10 percent of the mol number of the cadmium salt. At the time, thiourea is then added, the light transmittance and the energy gap of the wide bandgap nanometer cadmium sulfide thin film are obviously improved, and window materials of copper indium gallium selenium batteries or cadmium telluride batteries can be more favorably manufactured.

Owner:NANJING UNIV

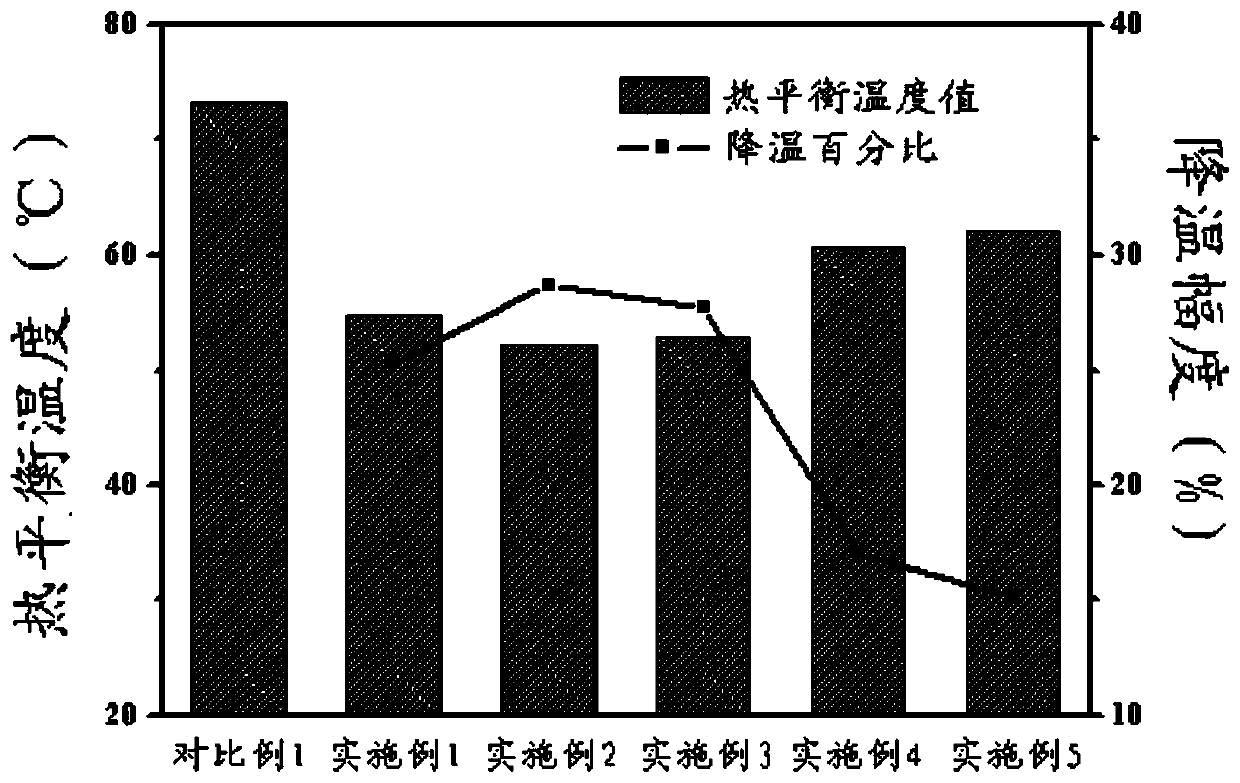

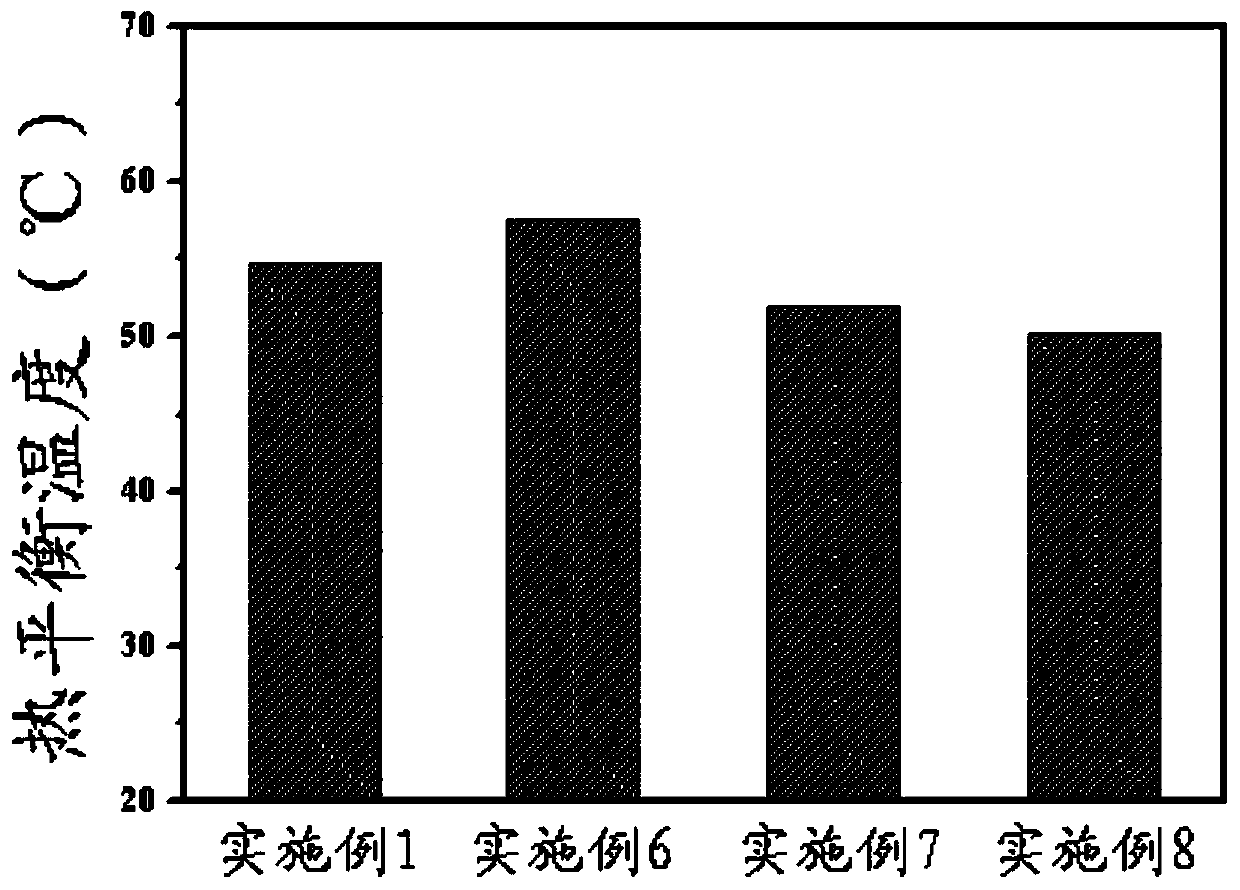

Low-temperature type artificial lawn filling rubber-plastic particles and preparation method thereof

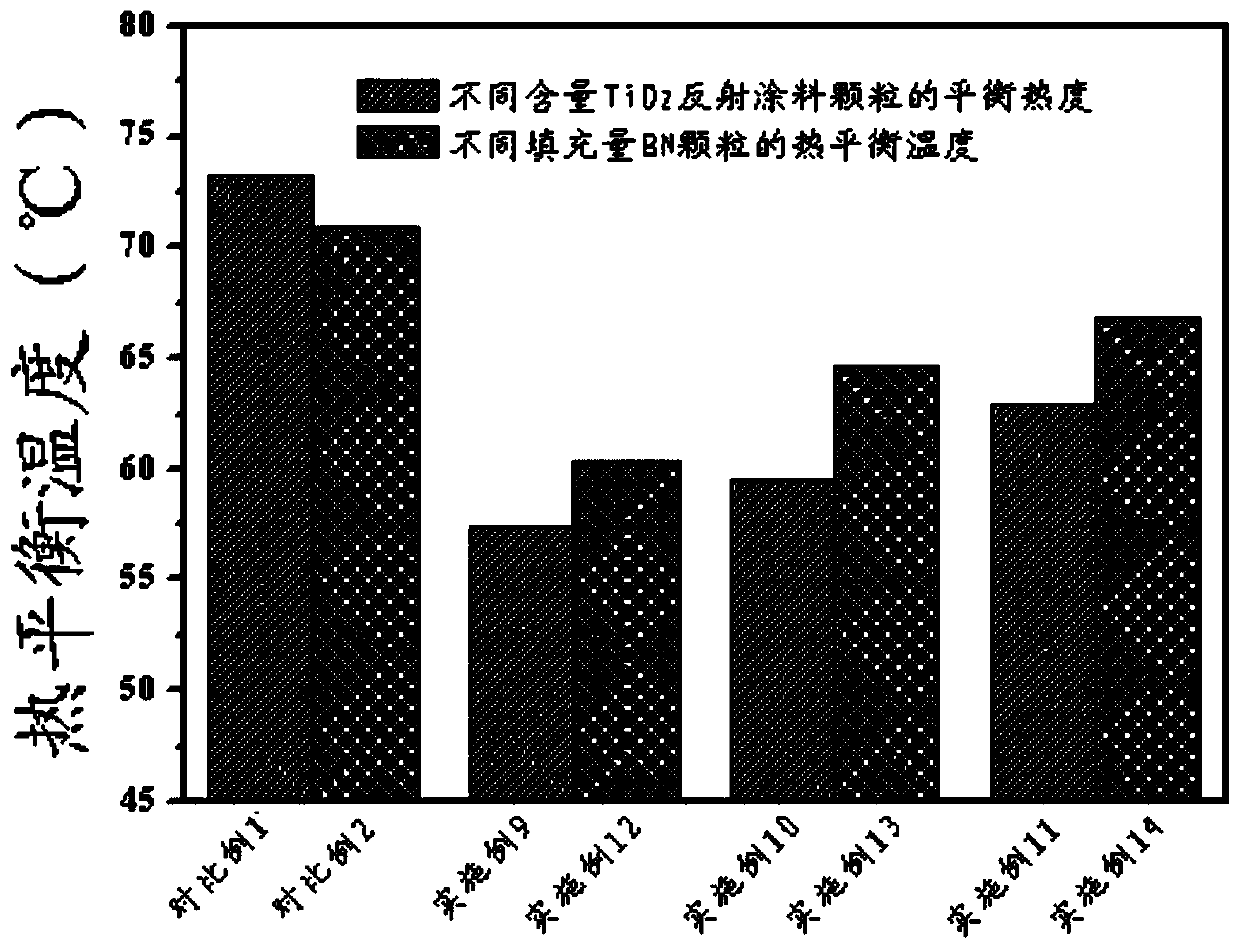

InactiveCN110078965AImprove reflectivityReduce maintenance costsFireproof paintsGround pavingsYarnThermoplastic

The invention discloses low-temperature type artificial lawn filling rubber-plastic particles and a preparation method thereof. The particles are positioned at the upper end of a quartz sand filling layer and uniformly dispersed among artificial grass yarns. The filling particles are prepared by blending and extruding a rubber base material and a light / heat reflection functional filler, coating the surfaces of the particles with a light / heat reflection coating layer or a composite technology thereof. The rubber-plastic particle base material consists of thermoplastic plastics, rubber or blendsthereof, color masterbatches, auxiliaries, filling oil and inorganic fillers. On the basis that various mechanical performance requirements are met, the rubber-plastic particles have lower using temperature compared with similar products in a solar illumination environment, the defect that an existing artificial lawn filling rubber-plastic particles are not resistant to high temperature is overcome, the service life of an artificial lawn system is prolonged, product replacement in a short period is avoided, and the maintenance cost of the lawn is reduced.

Owner:COCREATION GRASS CO LTD

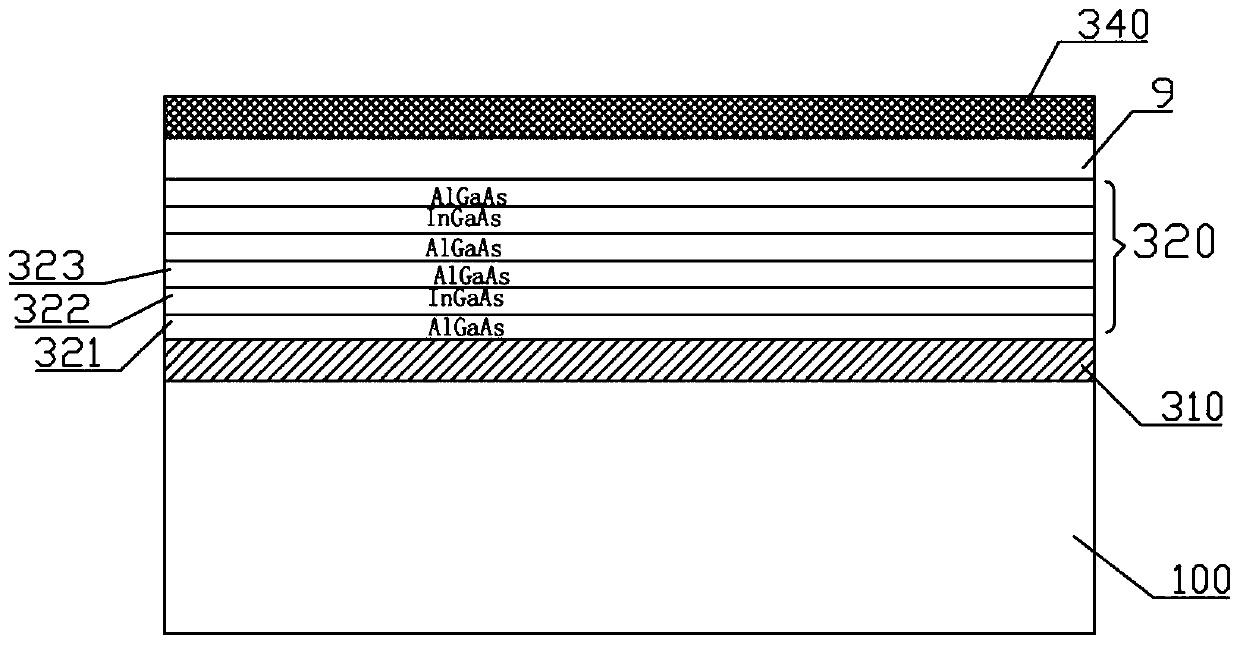

Mid-far infrared avalanche photodetector

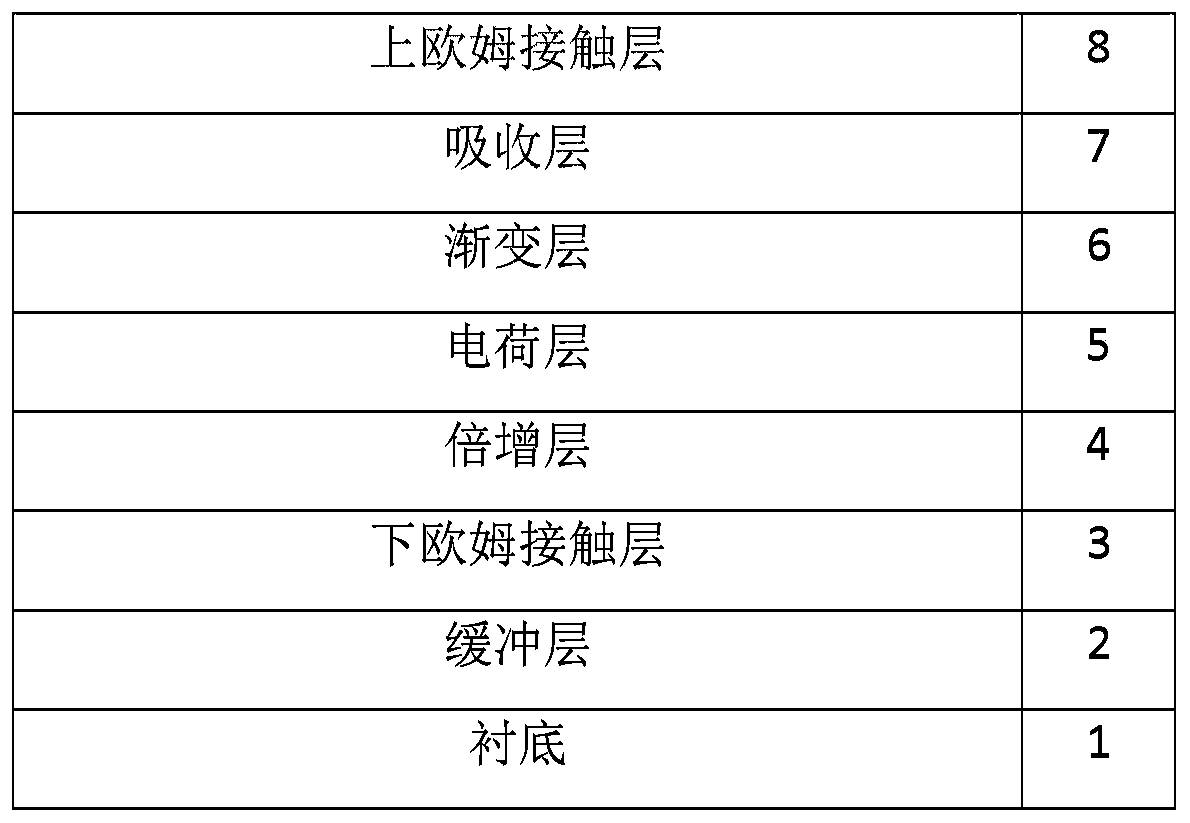

InactiveCN111540797AMature technologyImprove compatibilitySemiconductor devicesPhotovoltaic detectorsFar-red

The invention discloses a mid-far infrared avalanche photodetector which comprises a substrate, a buffer layer, a lower ohmic contact layer, a multiplication layer, a charge layer, a gradient layer, an absorption layer and an upper ohmic contact layer which are sequentially connected from bottom to top, and the doping type of the substrate and the buffer layer is n type. Or the mid-far infrared avalanche photodetector comprises the substrate, the buffer layer, a second ohmic contact layer, the absorption layer, the gradient layer, the charge layer, the multiplication layer and a first ohmic contact layer which are sequentially connected from bottom to top, and the doping type of the substrate and the buffer layer is p type, wherein the multiplication layer is made of an AlAsxSb1-x material, x is greater than or equal to 0.12 and less than or equal to 0.18, the gradient layer is of a plurality of (InAs)m / (AlAs0.15Sb0.85)n quantum well structures or an InyAl1-yAszSb1-z material, and thedetection wavelength of the absorption layer is a middle and far infrared band. The mid-far infrared avalanche photodetector provided by the invention can block dark current and reduce noise, does notneed a cooling device, improves the working temperature of the device, reduces the cost, and is convenient to use.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Laminated solar cell top cell and preparation method thereof

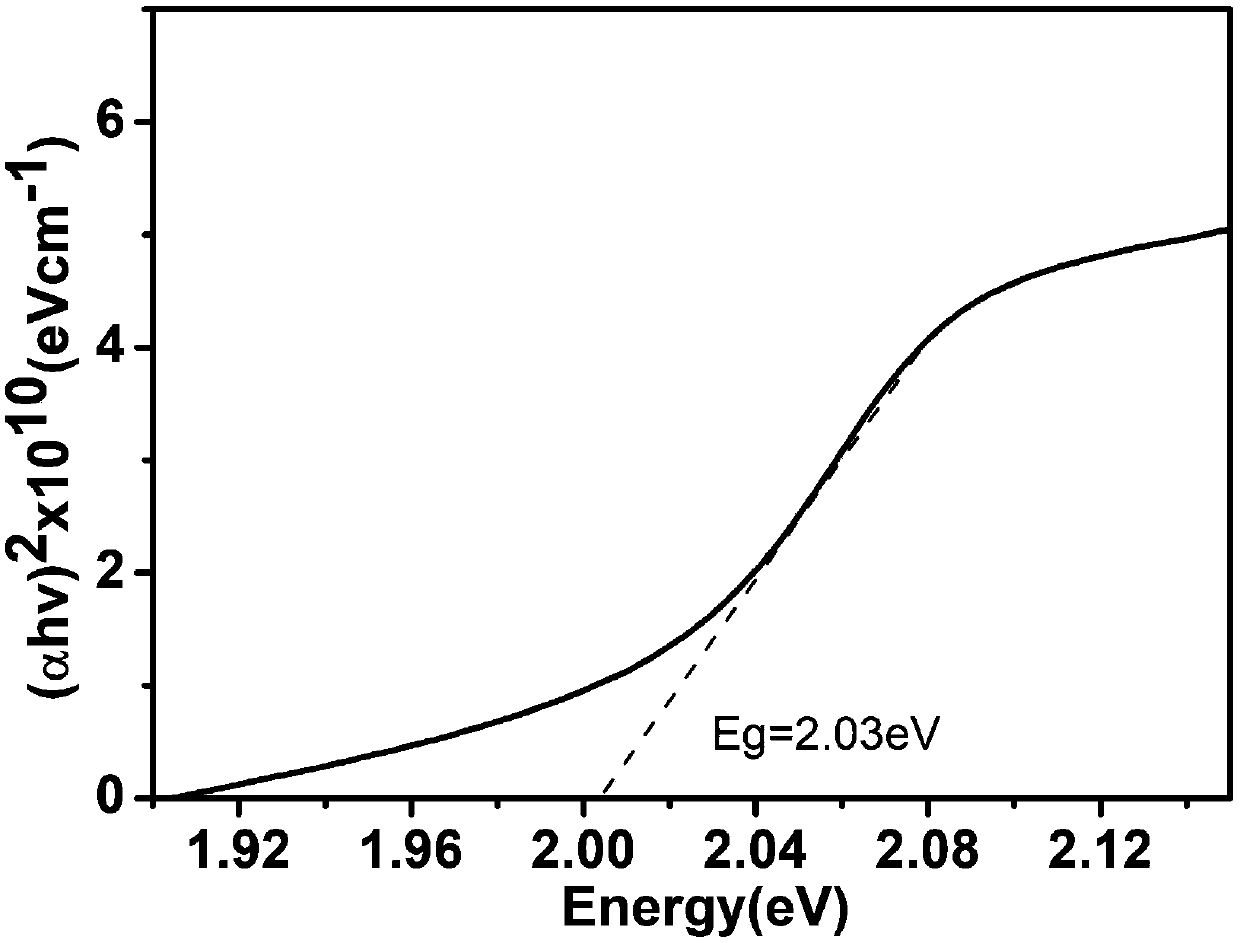

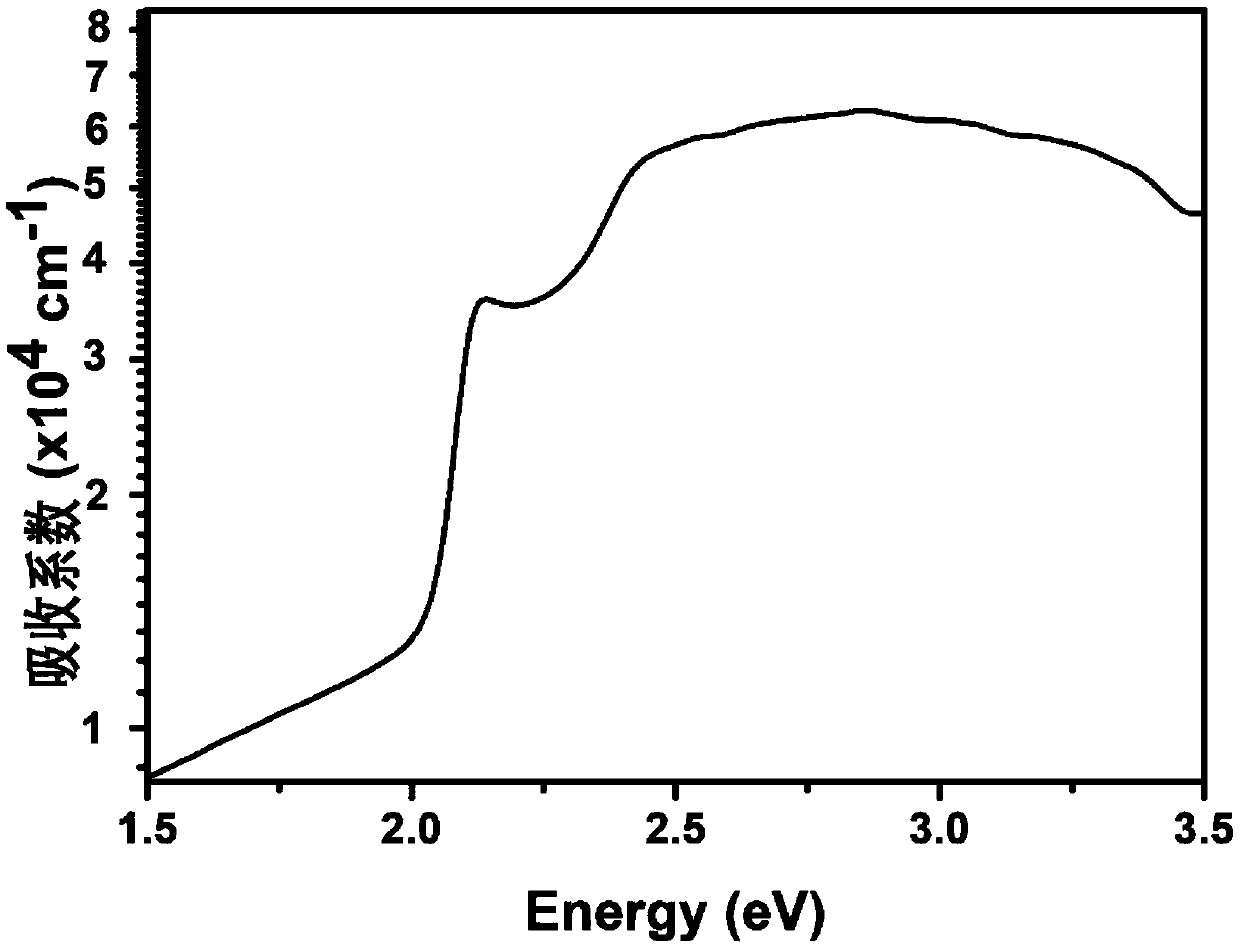

InactiveCN109671786AIncrease the bandgap widthHigh light absorption coefficientFinal product manufacturePhotovoltaic energy generationCZTSElectron

The invention discloses a laminated solar cell top cell and a preparation method thereof. The laminated solar cell top cell comprises a transparent conductive glass substrate, an electron transmissionlayer, a Cu2BaSnS4 or Cu2SrSnS4 light absorption layer and a transparent top electrode in sequential laminated arrangement. The forbidden bandwidth of the Cu2BaSnS4 or Cu2SrSnS4 material is high; thelight absorption coefficient is high. Compared with conventional CZTS, lower inverse defect density is realized; higher open circuit voltage can be obtained; the material is very suitable to be usedas light absorption layer materials of the laminated solar cell top cell. The laminated solar cell top cell has the advantages that the structure is simple; the composition elements are nontoxic and harmless; the stability is high, and the preparation method is simple and easy.

Owner:CENT SOUTH UNIV

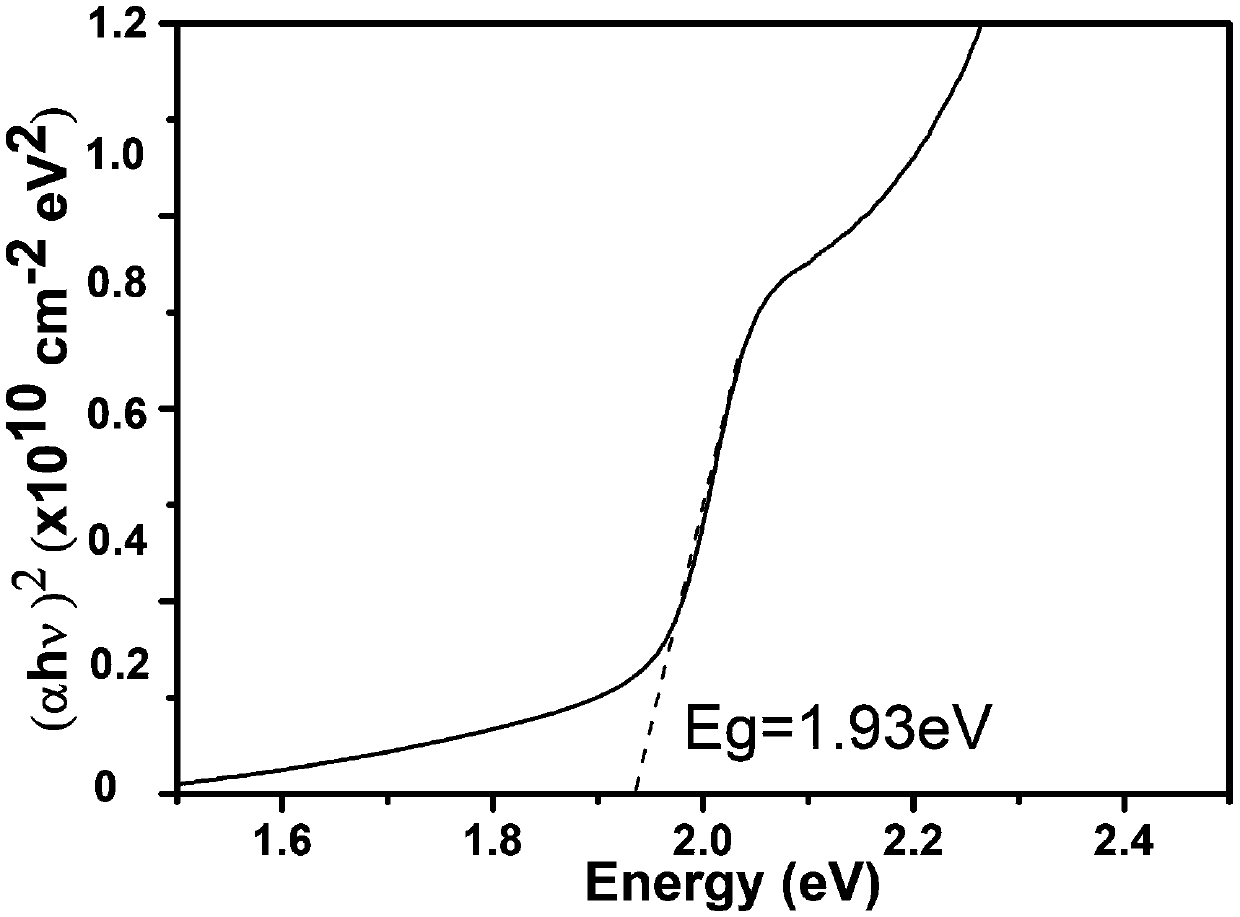

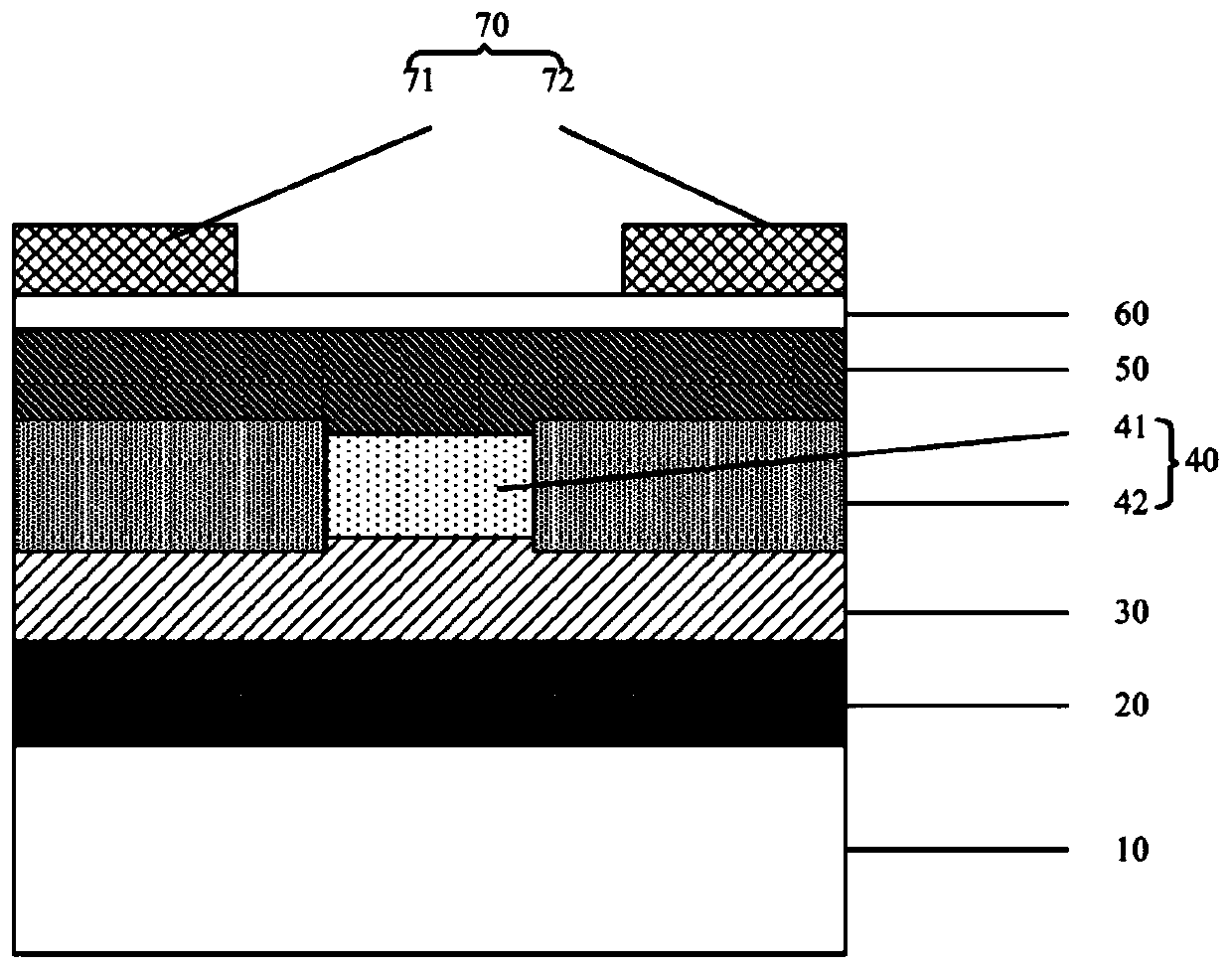

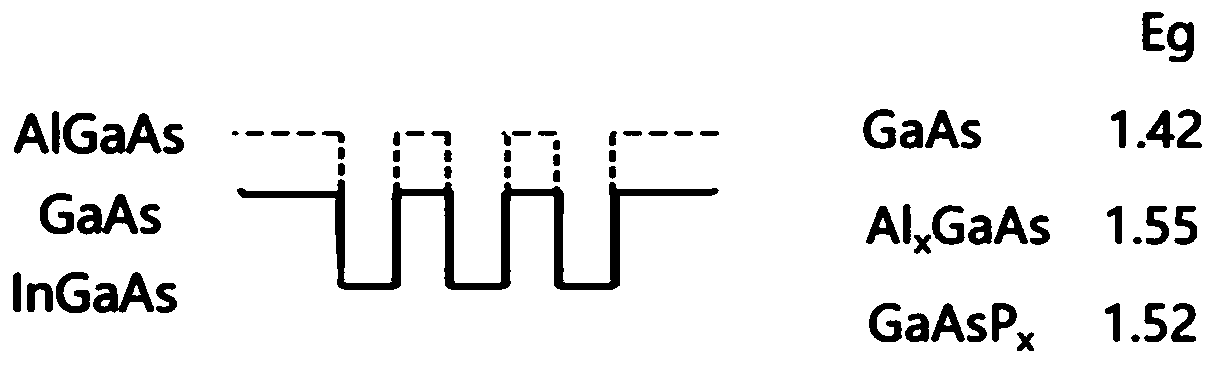

VCSEL chip with high recombination efficiency and manufacturing method thereof

PendingCN110197993AIncrease the bandgap widthImprove compound efficiencyLaser detailsLaser active region structureQuantum wellOptoelectronics

The invention relates to the technical field of laser chips, in particular to a VCSEL chip with high recombination efficiency and a manufacturing method thereof. The VCSEL chip comprises a substrate,an epitaxial layer and an N-contact, the epitaxial layer comprises an N-DBR, a quantum well, an oxide layer and a P-DBR, the P-DBR, the oxide layer and the quantum well are etched to the surface of the N-DBR to form a table top, the quantum well comprises a plurality of pairs of quantum well composite layers, each quantum well composite layer comprises AlxGaAs potential barriers, InGaAs potentialwells and AlxGaAs potential barriers which are grown in an overlapping mode, the P-DBR is divided into a central area, a middle area and an edge area, the central area is a light outlet hole, a firstSiNx layer grows on the P-DBR at the position corresponding to the central area, a P-contact is evaporated on the P-DBR at the position corresponding to the middle area, and a second SiNx layer growson the P-DBR at the position corresponding to the edge area. The potential barrier in the quantum well in the VCSEL chip has high forbidden bandwidth, lattice matching is easy to achieve, more electrons are intensively bound in the quantum well, excitation probability is increased, composite efficiency is improved, and therefore, stimulated radiation with higher efficiency is achieved.

Owner:威科赛乐微电子股份有限公司

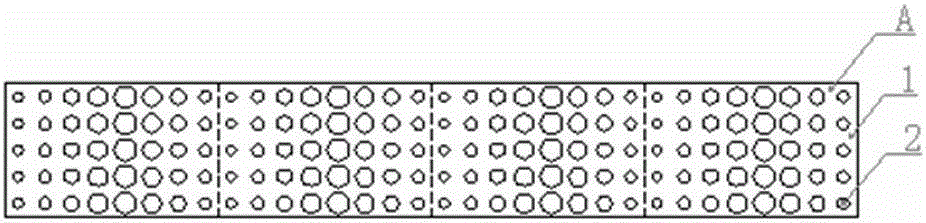

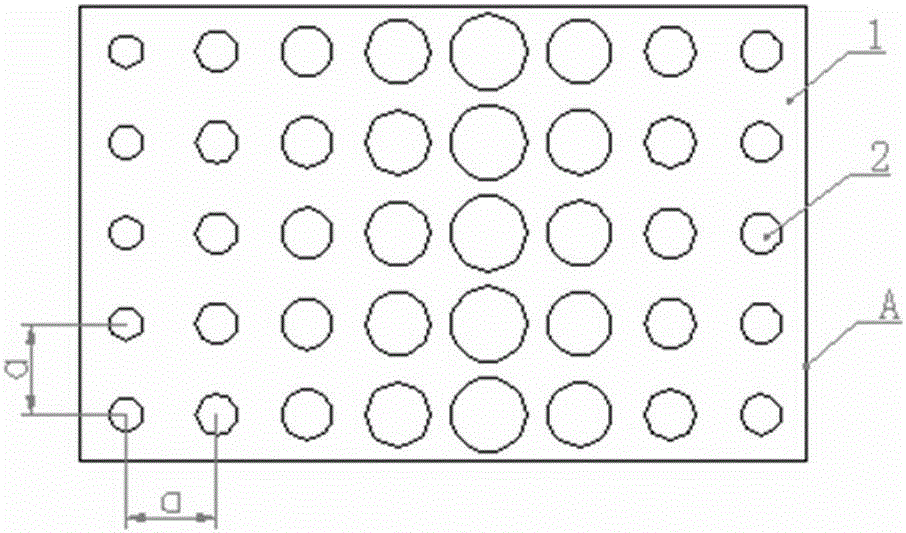

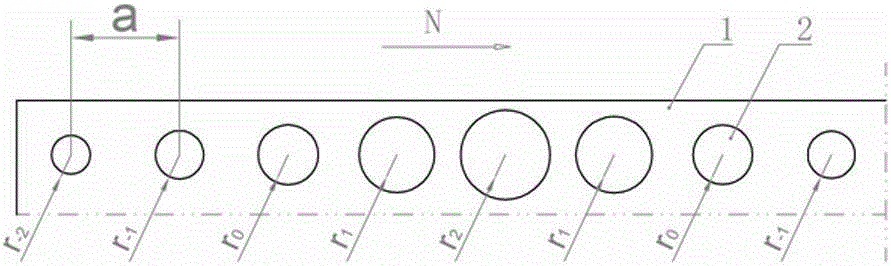

Two-dimensional photonic crystal of linear gradually-changed structure

InactiveCN105204116AIncrease the bandgap widthIncrease band gapOptical light guidesPhotonic crystalLattice constant

A two-dimensional photonic crystal of a linear gradually-changed structure comprises a matrix made of a low-dielectric-constant material, and high-dielectric-constant material columns are embedded into the material of the matrix and distributed in a square in space periodically. The radiuses of the columns are linearly and gradually increased or reduced in the wave propagation direction at a certain step length, the radiuses of the columns are not changed in the direction perpendicular to the wave propagation direction, and the center distances of the columns in the two directions are lattice constants. By optimizing structural parameters, under the condition that the dielectric ratio is relatively low, the relative band gap width is nearly 200% that of a standard square structure; under the condition that the dielectric ratio is higher, the band gap width is 2-5 times that of the standard structure. Compared with a traditional structure, the band gap rate is greatly increased. Compared with other complex structures, design is simple, a user can select a required forbidden band range according to materials needing to be adjusted and the structural parameters, and important value is provided for design, manufacturing and application of the two-dimensional photonic crystal.

Owner:XIDIAN UNIV

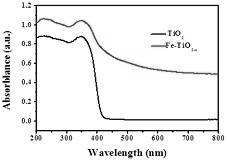

Electrostatically spun defect-state TiO2/Fe3O4 composite nanofiber material and preparation method thereof

PendingCN113546625AEfficient compositeNo shedding problemMaterial nanotechnologyWater/sewage treatment by irradiationFiberSpinning

The invention relates to a defect-state TiO2 / Fe3O4 composite nanofiber material and a preparation method thereof, and belongs to the technical field of materials. The preparation method of the material comprises the following steps: firstly, dispersing a titanium source, an iron source and a high-molecular polymer in a solvent to prepare a stable and uniform solution; then preparing the solution into a nanofiber membrane through an electrostatic spinning technology; and calcining the nanofiber membrane, grinding the calcined material and sodium borohydride, and reducing in a nitrogen atmosphere to obtain the defect-state TiO2 / Fe3O4 composite nanofiber material. The method is simple to operate, easy to control, environment-friendly and capable of realizing continuous production, and the obtained defect-state TiO2 / Fe3O4 composite nanofiber material has good crystallinity and photoresponsiveness and has excellent degradation performance on organic pollutants in a water environment.

Owner:INST OF URBAN ENVIRONMENT CHINESE ACAD OF SCI

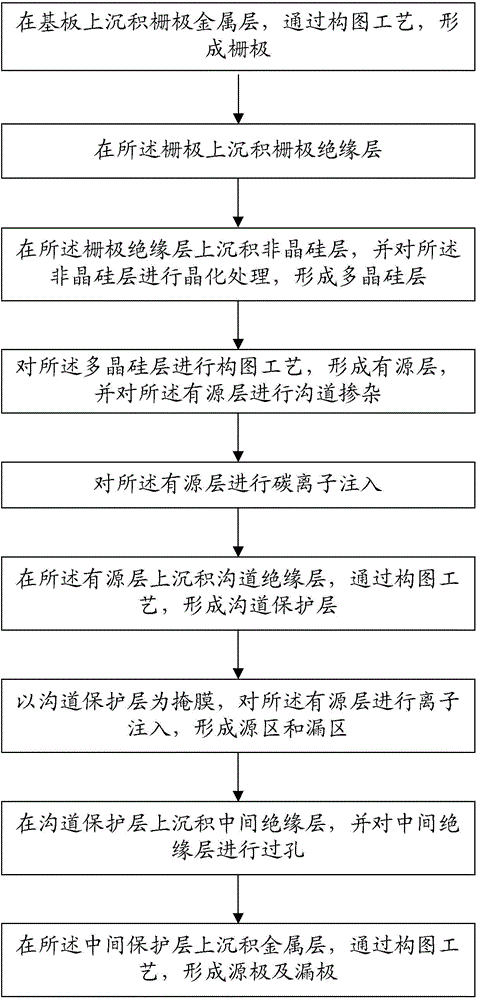

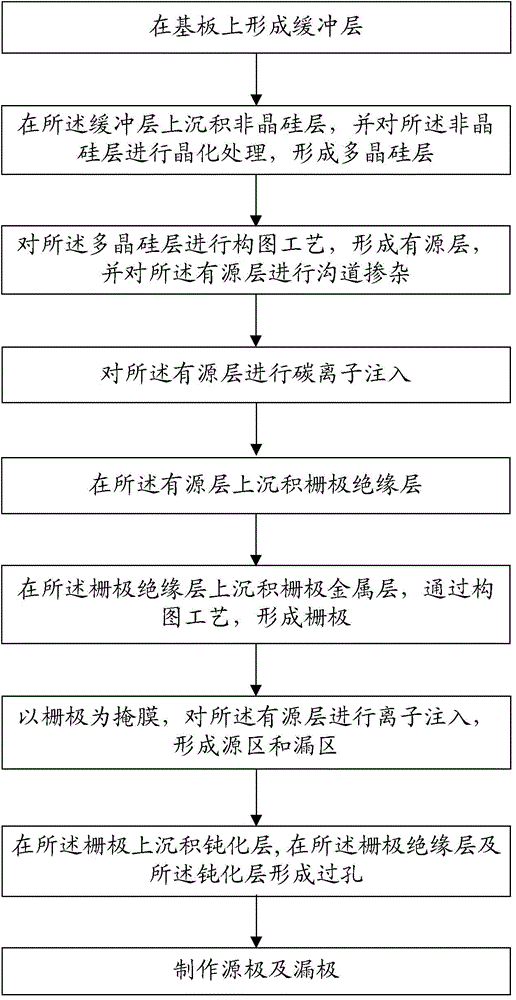

Thin-film transistor and manufacturing method thereof, array substrate and display device

InactiveCN104867833AReduce leakage currentIncrease the bandgap widthTransistorSolid-state devicesProduction lineDisplay device

The invention provides a manufacturing method of a thin-film transistor. The method comprises a step of deposition of an amorphous silicon layer; a step of formation of a polycrystalline silicon layer through crystallizing treatment; a step of formation of an active layer; a step of formation of channel doping; a step of carbon ion injection; a step of formation of via holes; a step of formation of a gate electrode insulating layer and a gate electrode; and a step of formation of a source electrode and a drain electrode. According to the manufacturing method of the thin-film transistor, forbidden bandwidth of the active layer can be enhanced and thus leakage current of a low-temperature polycrystalline silicon thin-film transistor can be reduced. Besides, visible light absorption coefficient of low-temperature polycrystalline silicon can also be reduced, and light-induced leakage current generated by a backlight source can be reduced. Furthermore, the manufacturing method of the thin-film transistor is suitable for existing polycrystalline silicon thin-film transistor production lines without additional number of times of photo-masking or modification of production equipment, and thus the operation method is easy and convenient. The invention also provides the thin-film transistor, an array substrate and a display device.

Owner:TRULY HUIZHOU SMART DISPLAY

Cadmium telluride thin film solar battery and preparation method thereof

ActiveCN109801980AIncrease the bandgap widthImprove initial performanceFinal product manufacturePhotovoltaic energy generationMercury cadmium tellurideOhmic contact

The invention discloses a cadmium telluride thin film solar battery. The cadmium telluride thin film solar battery comprises a substrate layer, a light absorbing layer, a back contact layer and a backelectrode layer which are arranged sequentially from bottom to top; the light absorbing layer is a cadmium telluride film layer; and the back contact layer is composed of an antimony telluride and copper selenide composite material. According to the cadmium telluride thin film solar battery of the invention, the back contact layer made of the antimony telluride and copper selenide composite material can form good ohmic contact with the cadmium telluride light absorbing layer, and therefore, potential barriers are lowered, and doped copper selenide can effectively eliminate the defects of thecadmium telluride light absorbing layer, and after selenium diffuses to a cadmium telluride interface, the forbidden band width of the cadmium telluride can be effectively increased, and presents deep-V type gradient change; and the initial performance and long-term stability of the battery are excellent, and the conversion efficiency of the battery is high.

Owner:CNBM CHENGDU OPTOELECTRONICS MATERIAL

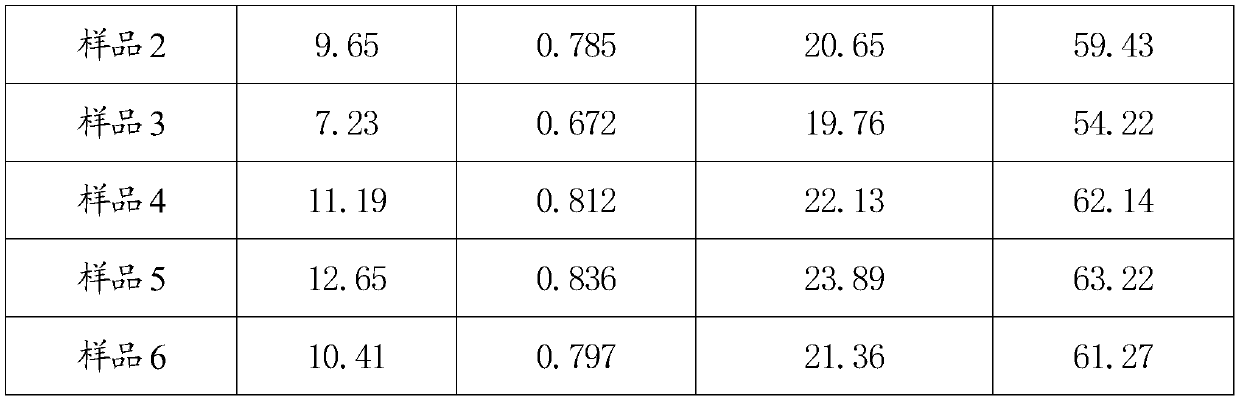

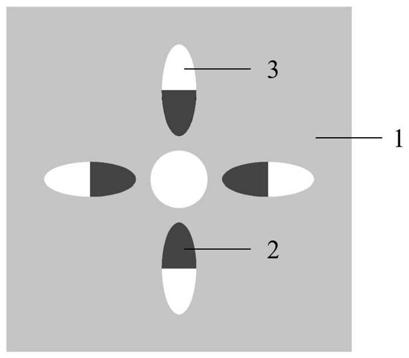

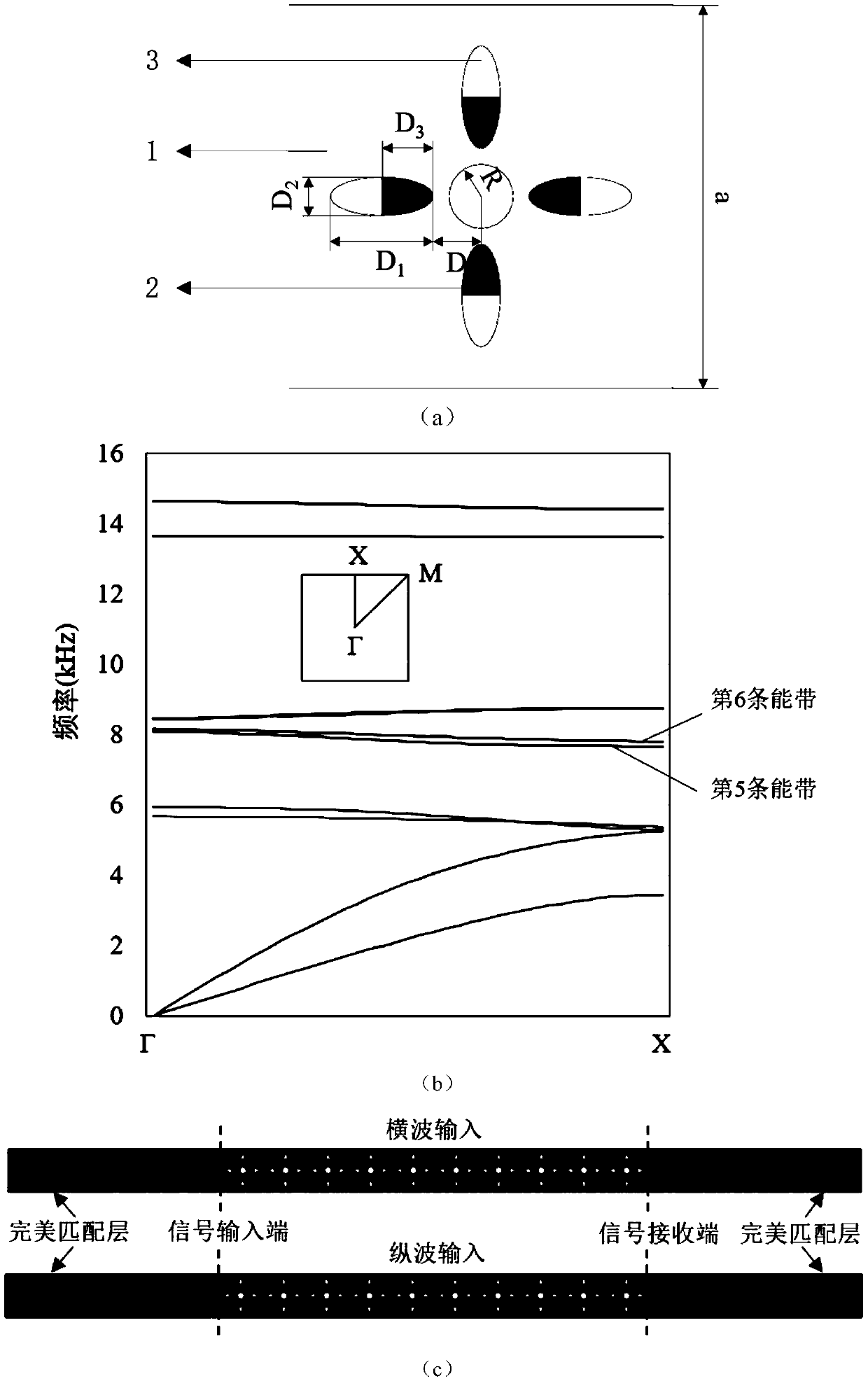

Three-negative elastic wave metamaterial with wide forbidden band

PendingCN111120551ARegulating the transmission pathElastic bandgapSprings/dampers functional characteristicsMultiple spring combinationsShear modulusNegative refraction

The invention discloses a three-negative elastic wave metamaterial with a wide forbidden band. The three-negative elastic wave metamaterial comprises N unit cells, wherein each unit cell is of a two-dimensional structure and is square; a base material is foam; a round hole is formed in the center of the base material; four elliptical holes are formed around the round hole; the four elliptical holes are filled with scatterer metal tungsten, but the elliptical holes cannot be filled with scatterers; and the whole unit cell is of a central symmetry structure. The elastic wave metamaterial can simultaneously achieve equivalent negative mass density, equivalent negative volume modulus and equivalent negative shear modulus within the same frequency range, so that negative refraction of transverse waves and longitudinal waves of elastic waves is achieved within the same frequency range; and meanwhile, the elastic wave metamaterial also has the relatively wide forbidden band. The material canbe used for designing functional devices and gradient materials for regulating and controlling the elastic waves, and can also be used for vibration isolation and sound insulation of mechanical equipment and building structures.

Owner:SOUTHEAST UNIV

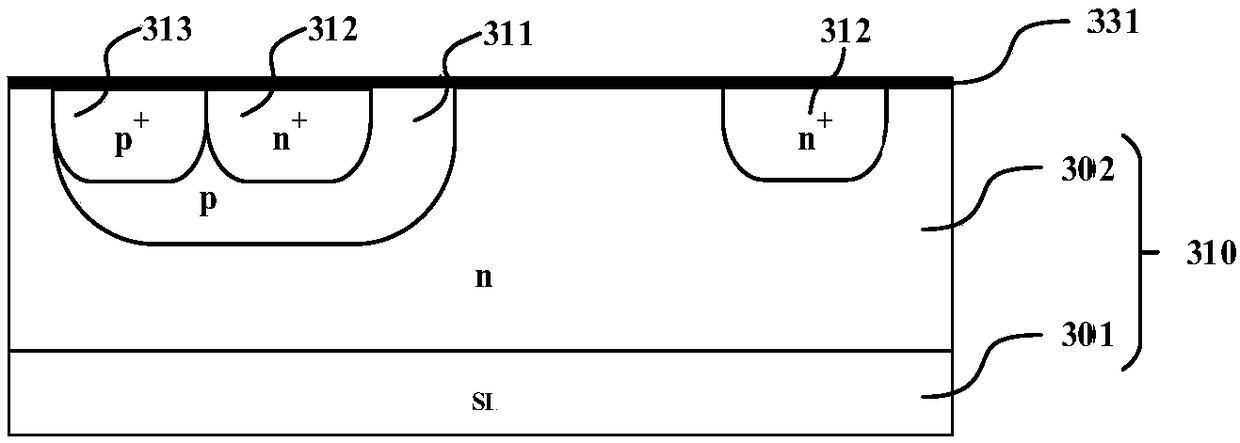

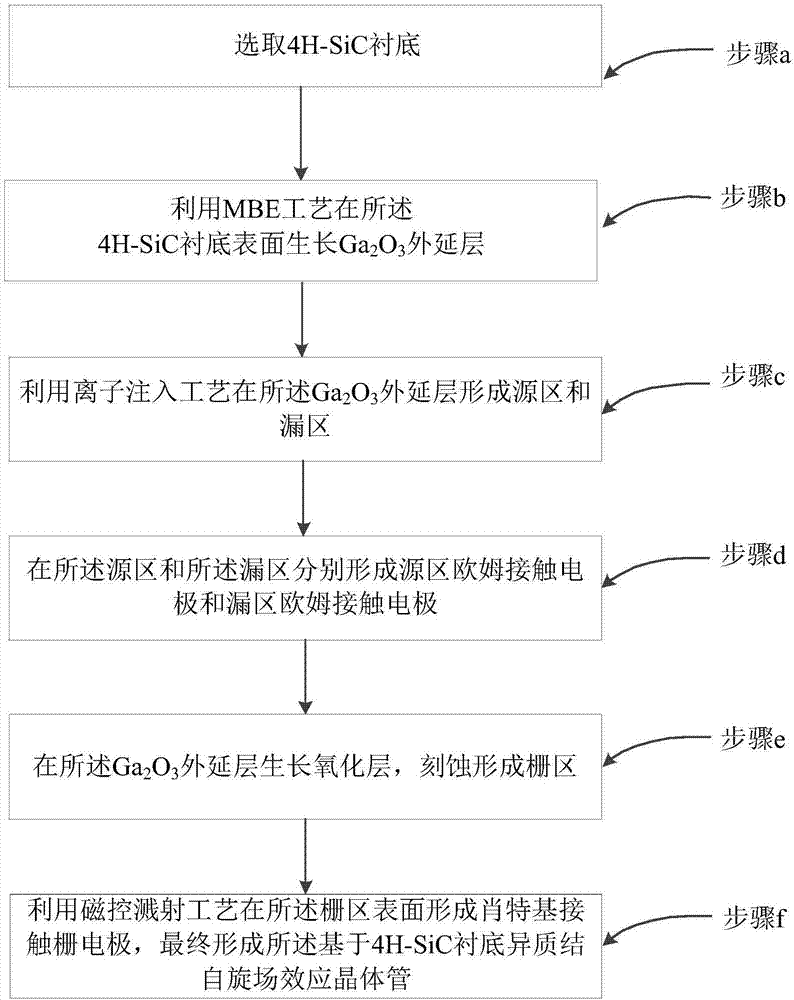

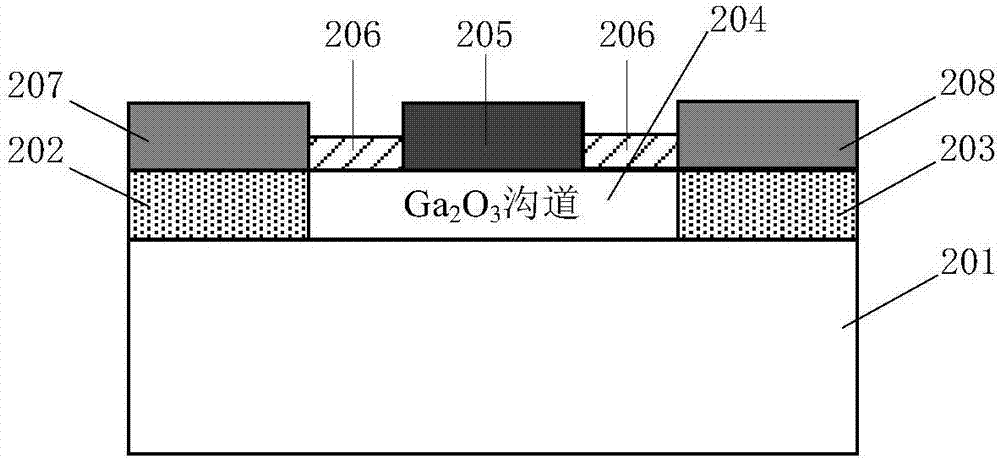

Heterojunction spinning field effect transistor based on 4H-SiC substrate, and manufacturing method for heterojunction spinning field effect transistor

ActiveCN107369707AOptimizing spin polarizabilityHigh saturation magnetizationSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSputtering

The invention relates to a heterojunction spinning field effect transistor based on a 4H-SiC substrate, and a manufacturing method for the heterojunction spinning field effect transistor. The method comprises the following steps: selecting the 4H-SiC substrate; growing a Ga2O3 epitaxial layer on the surface of the 4H-SiC substrate through employing the MBE technology; forming a source region and a drain region on the Ga2O3 epitaxial layer through the ion implantation technology; respectively forming a source region ohmic contact electrode and a drain region ohmic contact electrode in the resource region and the drain region; growing an oxidation layer on the Ga2O3 epitaxial layer, and carrying out the etching to form a grid region; forming a Schottky contact grid electrode on the surface of the grid region through the technology of magnetron sputtering, and finally forming the heterojunction spinning field effect transistor based on the4H-SiC substrate. According to the invention, the source and drain regions are formed in a mode of selecting regions and carrying out the implantation of Fe ions. The method is compatible with the conventional technology, is simple in manufacturing, is small in surface effect, and can improve the spinning injection and receiving efficiency.

Owner:XIDIAN UNIV

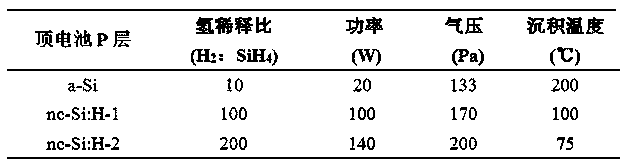

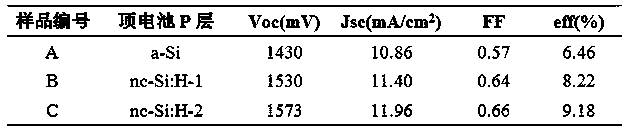

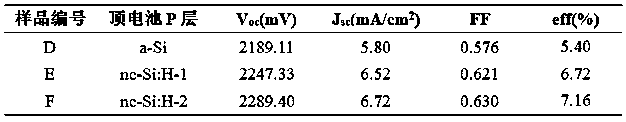

Preparation method and purpose of top cell P type layer of amorphous silicon germanium thin-film solar cell

ActiveCN104393120AIncrease the open circuit voltageExcellent current valueFinal product manufactureSemiconductor/solid-state device manufacturingElectrical batteryEngineering

The invention discloses a preparation method and purpose of a top cell P type layer of an amorphous silicon germanium thin-film solar cell. According to the method, a P type layer of a top cell is prepared by a radio frequency plasma enhanced chemical vapor deposition (RF-PECVD) method; and reactant gas includes hydrogen, silane, and borane. During deposition, gas flow volume proportion of the hydrogen to silane to borane is maintained to be 150 to 200 : 1 : 3 to 8; the borane is borane- hydrogen mixed gas, wherein the borane volume concentration is 0.5%; the air pressure is 160 to 220 Pa; the preparation temperature is within 100 DEG C; the power density inside the cavity is over 300mW / cm<2>; and the band gap width of the P type layer is over 2.0 eV. With the P type layer, the top cell can obtain the high open-circuit voltage and the short-circuit current density can be reduced properly and thus the short-circuit currents generated by the top cells in all sub cells of dual-junction and three-junction cells are the lowest ones, thereby forming a top cell current limitation effect. Therefore, current matching among all sub cells and the fill factors of the integrated cells can be effectively improved, thereby improving the photoelectric conversion efficiency of the dual-junction and three-junction amorphous silicon germanium thin-film solar cells.

Owner:SHANGHAI INST OF SPACE POWER SOURCES