Heterojunction spinning field effect transistor based on 4H-SiC substrate, and manufacturing method for heterojunction spinning field effect transistor

A field-effect transistor and heterojunction technology, which is applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, electrical components, etc., can solve the problem that the efficiency of spin injection is only a few percent, and achieve the optimization of spin polarizability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

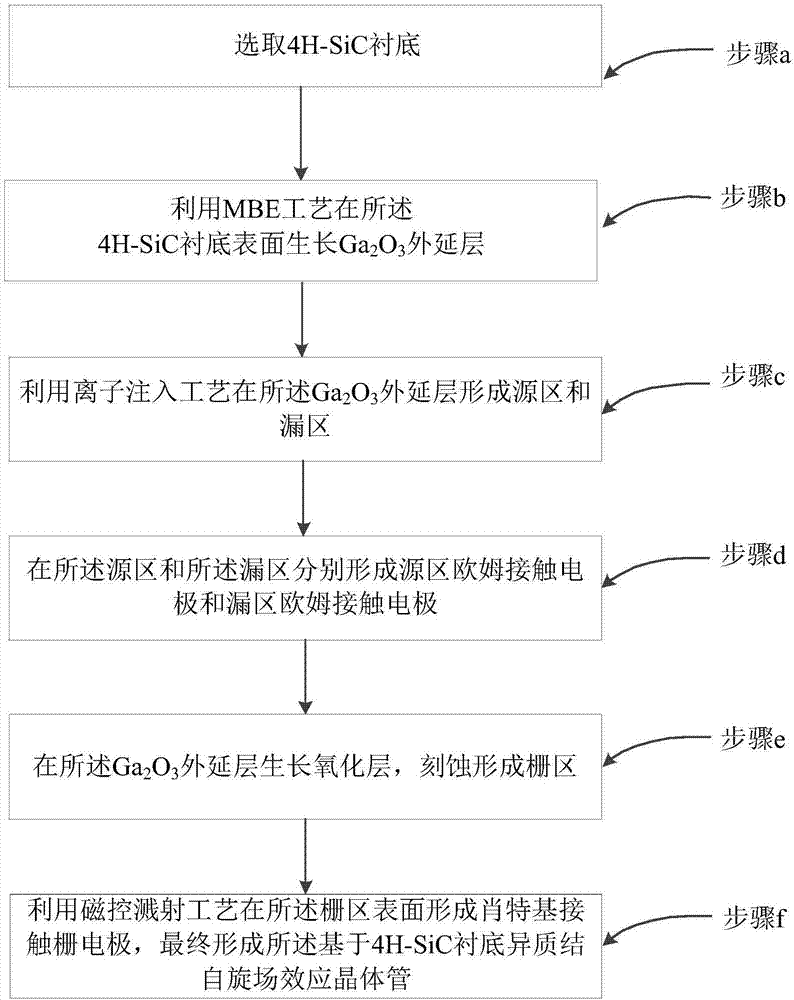

[0047] See figure 1 , figure 1A schematic diagram of a heterojunction spin field effect transistor based on a 4H-SiC substrate and a manufacturing method thereof provided by an embodiment of the present invention. The method comprises the steps of:

[0048] Step a, select 4H-SiC substrate;

[0049] Step b, using the MBE process to grow Ga on the surface of the 4H-SiC substrate 2 o 3 epitaxial layer;

[0050] Step c, using an ion implantation process on the Ga 2 o 3 The epitaxial layer forms source and drain regions;

[0051] Step d, forming a source region ohmic contact electrode and a drain region ohmic contact electrode in the source region and the drain region respectively;

[0052] Step e, in the Ga 2 o 3 The oxide layer is grown on the epitaxial layer, and the gate area is formed by etching;

[0053] Step f, using a magnetron sputtering process to form a Schottky contact gate electrode on the surface of the gate region, and finally forming the heterojunction sp...

Embodiment 2

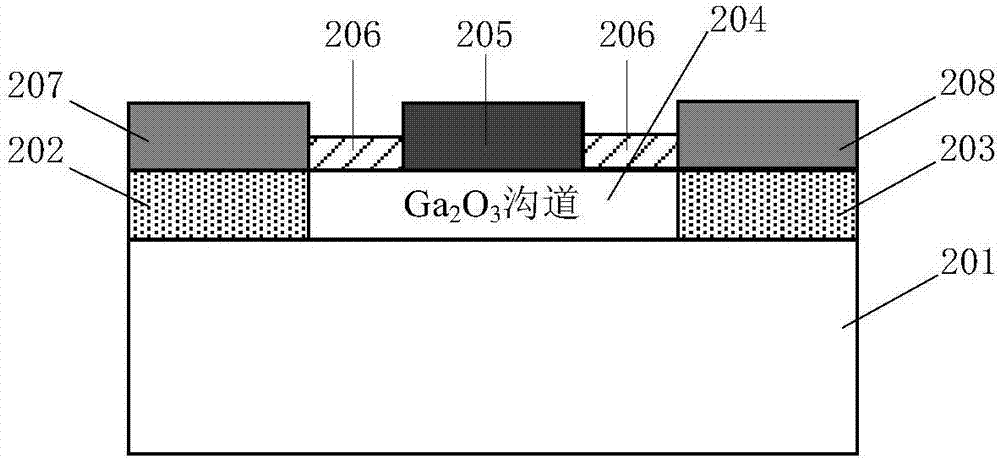

[0076] See figure 2 , figure 2 A device schematic diagram of a heterojunction spin field effect transistor based on a 4H-SiC substrate provided by an embodiment of the present invention. The heterojunction spin field effect transistor based on 4H-SiC substrate includes: 4H-SiC substrate 201, Fe-doped Ga 2 o 3 Source region 202, Fe-doped Ga 2 o 3 Drain region 203, Ga 2 o 3 Channel region 204, Schottky contact gate electrode 205, SiO 2 The isolation layer 206, the ohmic contact source 207, and the ohmic contact drain 208, the heterojunction spin field effect transistor based on the 4H-SiC substrate is prepared and formed by the method described in the above-mentioned embodiments.

[0077] The machine manufacturing method of the heterojunction high electron mobility spin field effect transistor of the present invention, because the same material is used for the channel and the source and drain regions, epitaxial growth can be directly performed on the substrate, and at t...

Embodiment 3

[0079] See Figure 3a-Figure 3g A process schematic diagram of a heterojunction spin field effect transistor based on a 4H-SiC substrate provided by an embodiment of the present invention. On the basis of the above embodiments, this embodiment will introduce the process flow of the present invention in more detail. The method includes:

[0080] Step 301, select the 4H-SiC substrate 301, and use acetone, absolute ethanol and deionized water to perform ultrasonic cleaning on the 4H-SiC substrate, such as Figure 3a shown;

[0081] Step 302, at a temperature of 940°C, the power of the radio frequency source is 300W, and the pressure is 1.5×10 -5 Torr, the evaporation source materials Ga and Sn, the mass fractions are 99.99999% and 99.999% respectively, and the thickness is 0.4-0.6 μm grown on the surface of 4H-SiC substrate 301 by MBE process, and the doping concentration is 1×10 14 -1×10 16 cm -3 Ga 2 o 3 Epitaxial layer 302, such as Figure 3b shown;

[0082] Preferab...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More