Preparation method of high k-gate dielectric layer and silicon carbide MOS power device

A gate dielectric layer and power device technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as uneven oxide layer thickness, high electric field strength, etc., to improve channel mobility, improve resistance Compression ability, effect of reducing impurity content

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0074] Step S201: Prepare silicon carbide epitaxial wafer

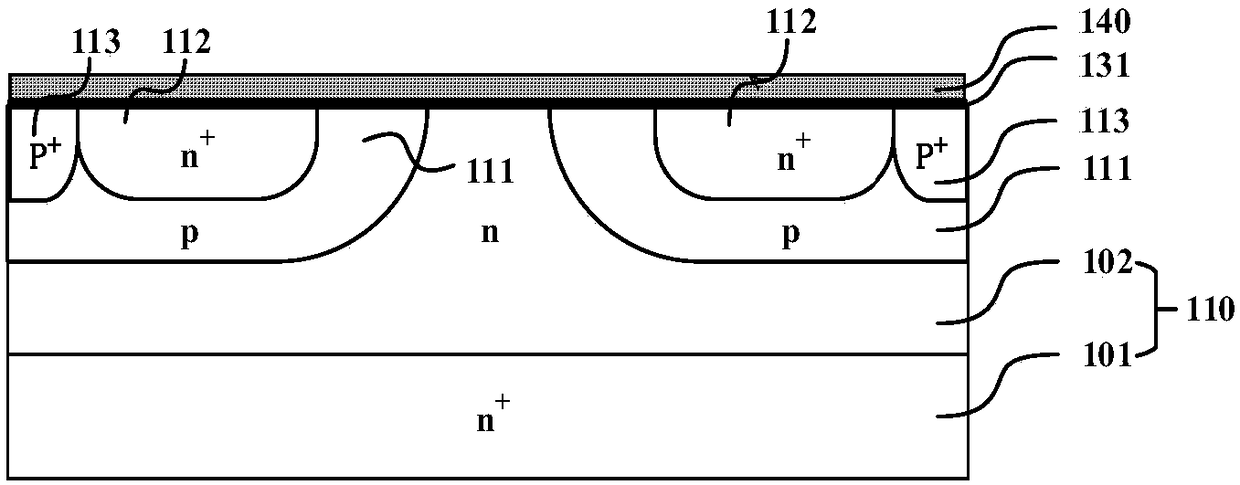

[0075] figure 2 It is a schematic structural diagram of a silicon carbide epitaxial wafer in an embodiment of the present invention. As shown in the figure, a silicon carbide epitaxial wafer 110 in this embodiment includes an n-type silicon carbide substrate 101 and an n-type silicon carbide epitaxial layer 102 .

[0076] Step S202: Prepare well region, source contact region and base contact region

[0077] image 3 It is a schematic diagram of the well region, the source contact region and the base contact region of a silicon carbide epitaxial wafer in an embodiment of the present invention. The p-type well region 111 is doped with p-type ions and n-type ions respectively to form an n-type base contact region 112 and a p-type source contact region 113 .

[0078] Step S203: preparing a sacrificial oxide layer

[0079] Figure 4 It is a schematic diagram of a sacrificial oxide layer of a silicon carbide epitaxial...

Embodiment 2

[0087] Step S301: Prepare silicon carbide epitaxial wafer

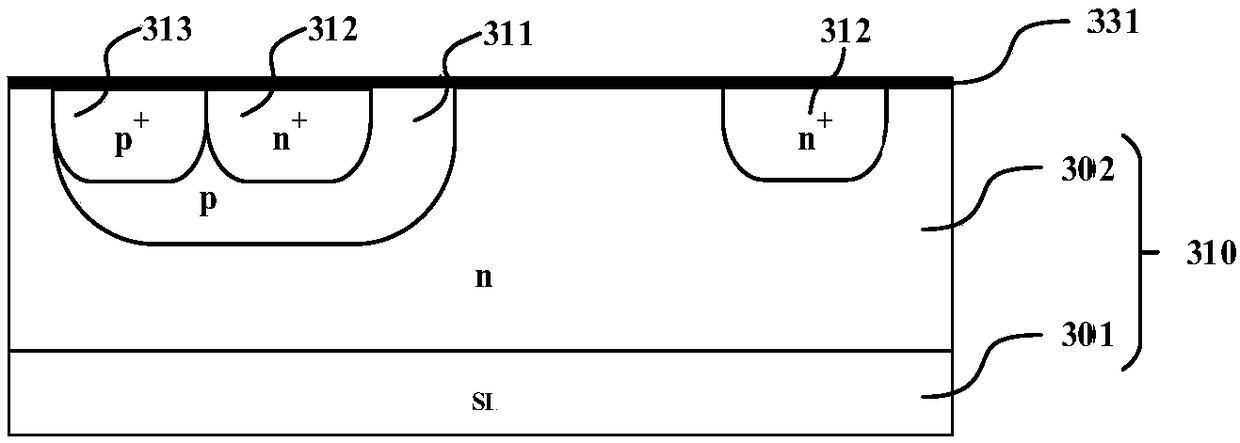

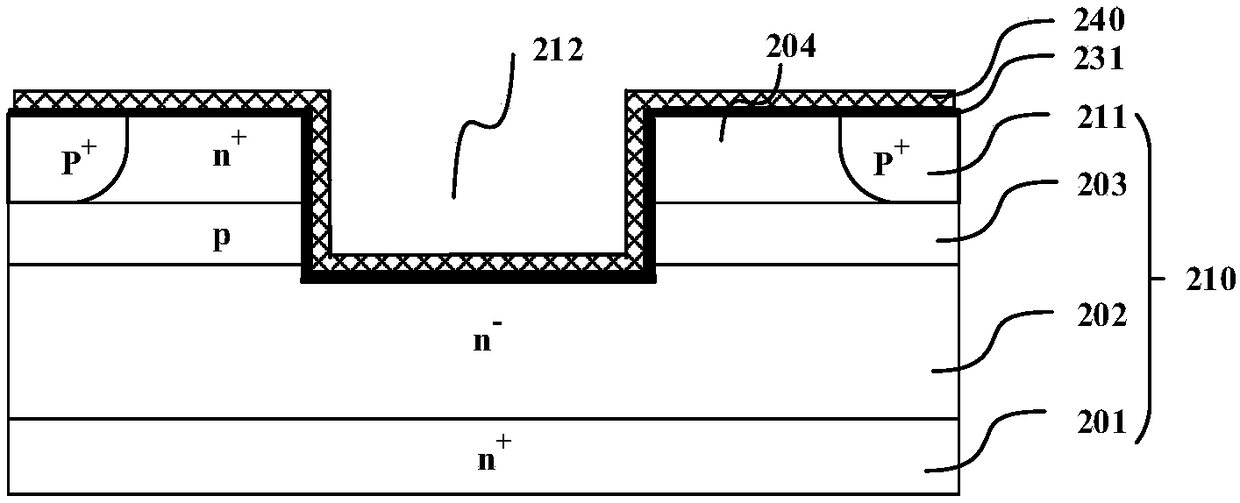

[0088] Figure 9 It is a schematic structural diagram of another silicon carbide epitaxial wafer in the embodiment of the present invention. As shown in the figure, the silicon carbide epitaxial wafer 210 in this embodiment includes an n-type silicon carbide substrate 201, an n-type silicon carbide epitaxial layer 202, and a p-type silicon carbide epitaxial layer 202. SiC epitaxial layer 203 and n-type SiC epitaxial layer 204 .

[0089] Step S302: Prepare base contact region and trench region

[0090] Figure 10 It is a schematic diagram of the base contact region and trench region of another silicon carbide epitaxial wafer in the embodiment of the present invention. As shown in the figure, in this embodiment, the n-type silicon carbide epitaxial layer 204 is doped with p-type ions to form the base contact In the region 211 , the n-type silicon carbide epitaxial layer 202 , the p-type silicon carbide epitaxial laye...

Embodiment 3

[0100] Step S401: Prepare silicon carbide epitaxial wafer

[0101] Figure 16 It is a schematic structural diagram of another silicon carbide epitaxial wafer in the embodiment of the present invention. As shown in the figure, the silicon carbide epitaxial wafer 310 in this embodiment includes an n-type silicon carbide substrate 301 and a semi-insulating silicon carbide substrate 302 .

[0102] Step S402: Prepare well region, source contact region and base contact region

[0103] Figure 17 It is a schematic diagram of the well region, the source contact region and the base contact region of another silicon carbide epitaxial wafer in the embodiment of the present invention. As shown in the figure, the n-type silicon carbide epitaxial layer 302 is doped with p-type ions in this embodiment A p-type well region 311 is formed, and p-type ions and n-type ions are respectively doped in the p-type well region 311 to form an n-type base contact region 312 and a p-type source contact ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More