Patents

Literature

2211results about How to "Eliminate damage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and apparatus for controlling a patient's body temperature by in situ blood temperature modifications

InactiveUS6110168AQuickly felt throughout the patient's bodyEliminate damageStentsBalloon catheterHypothermia inducedHigh body temperature

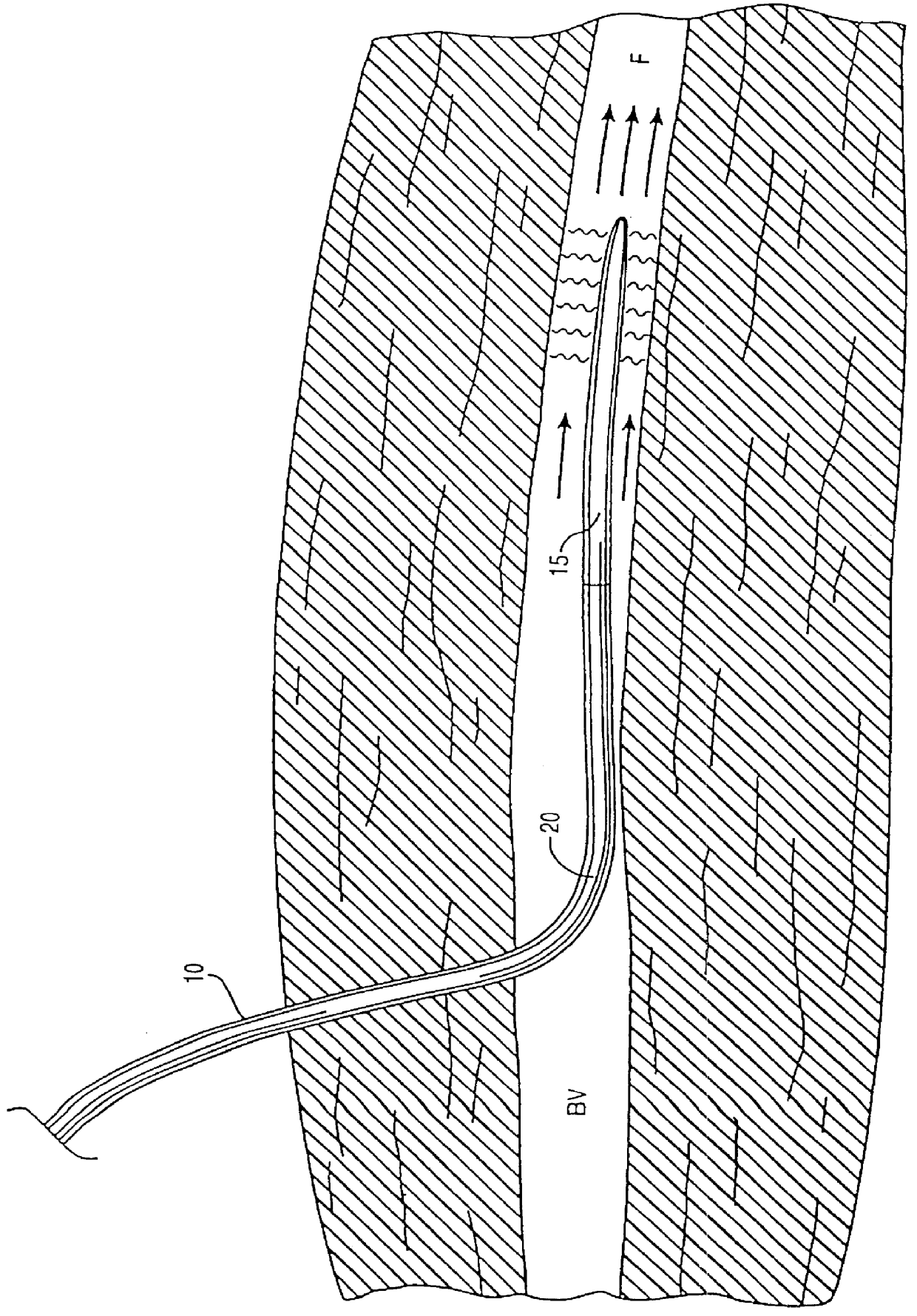

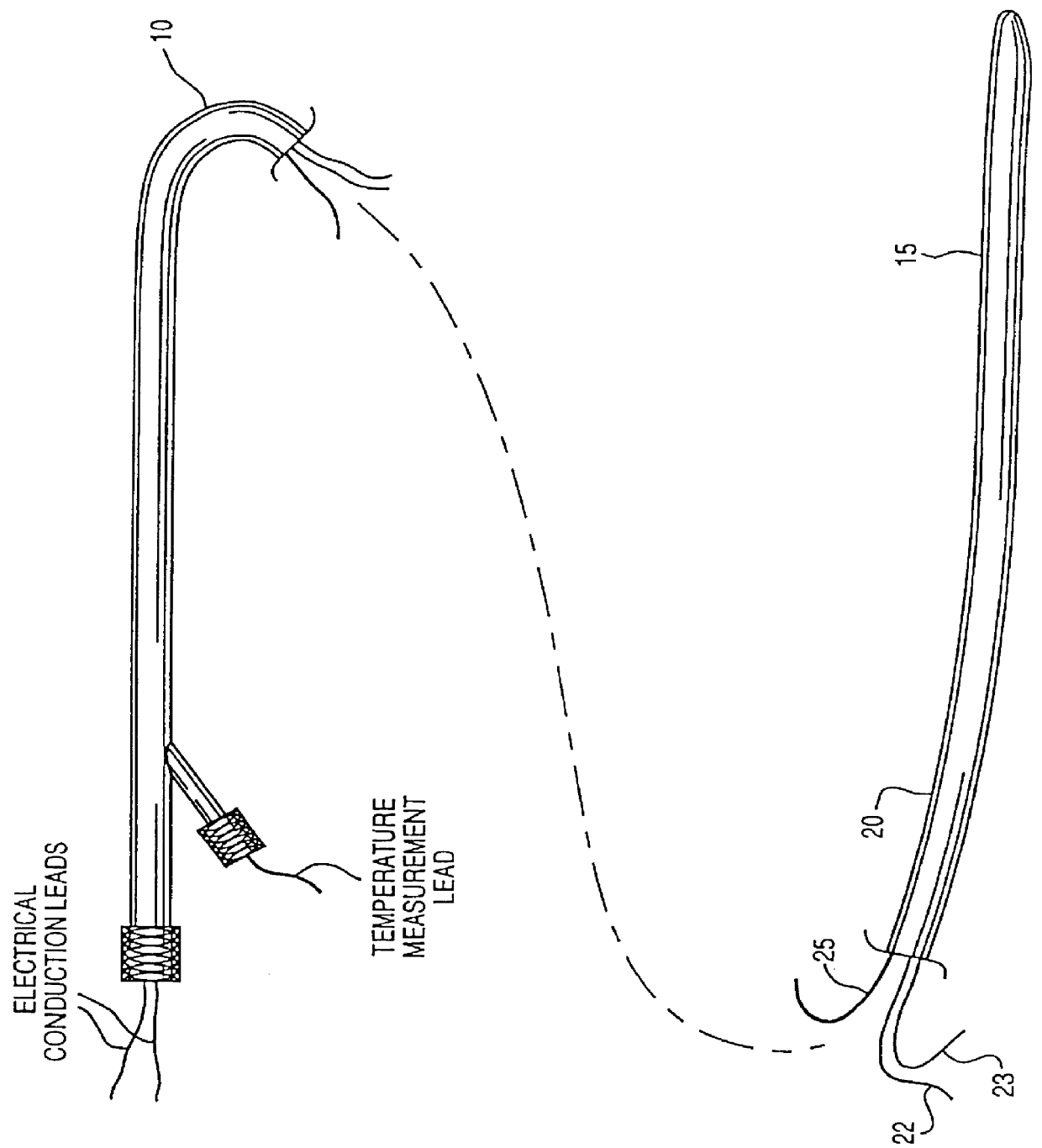

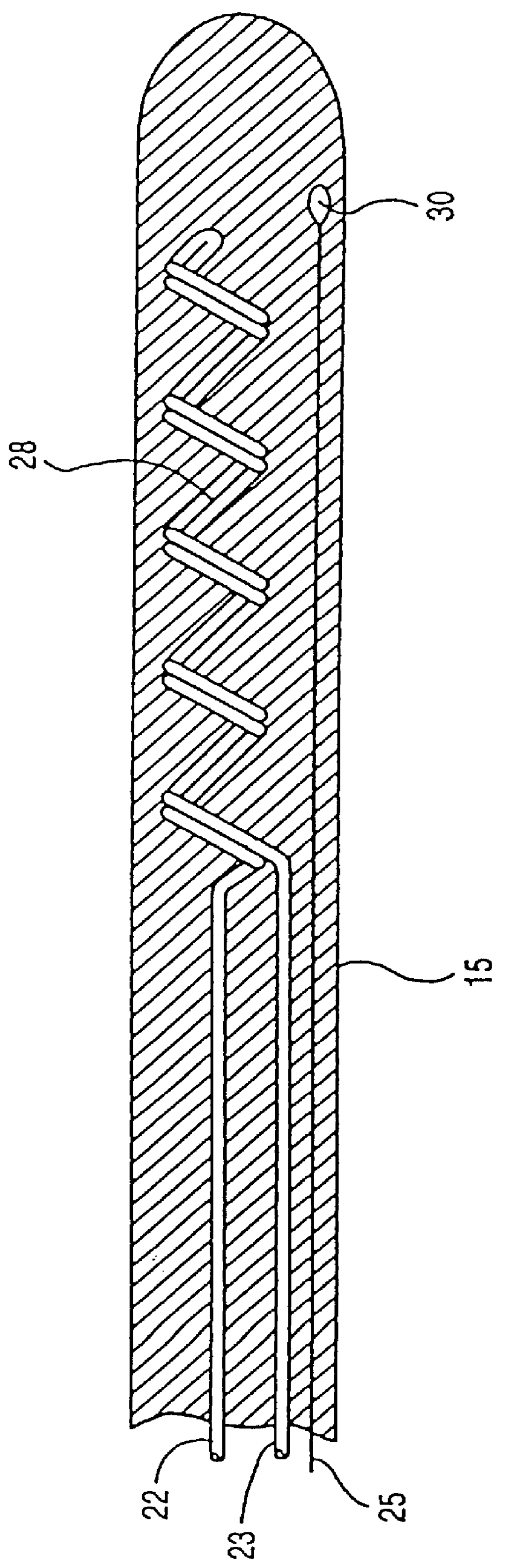

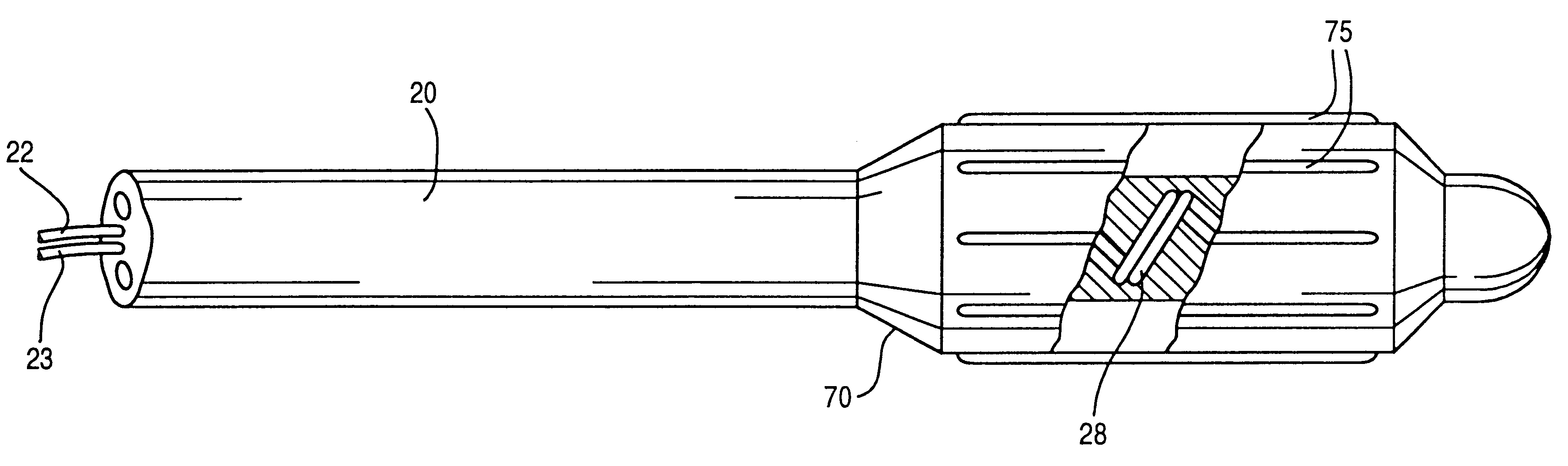

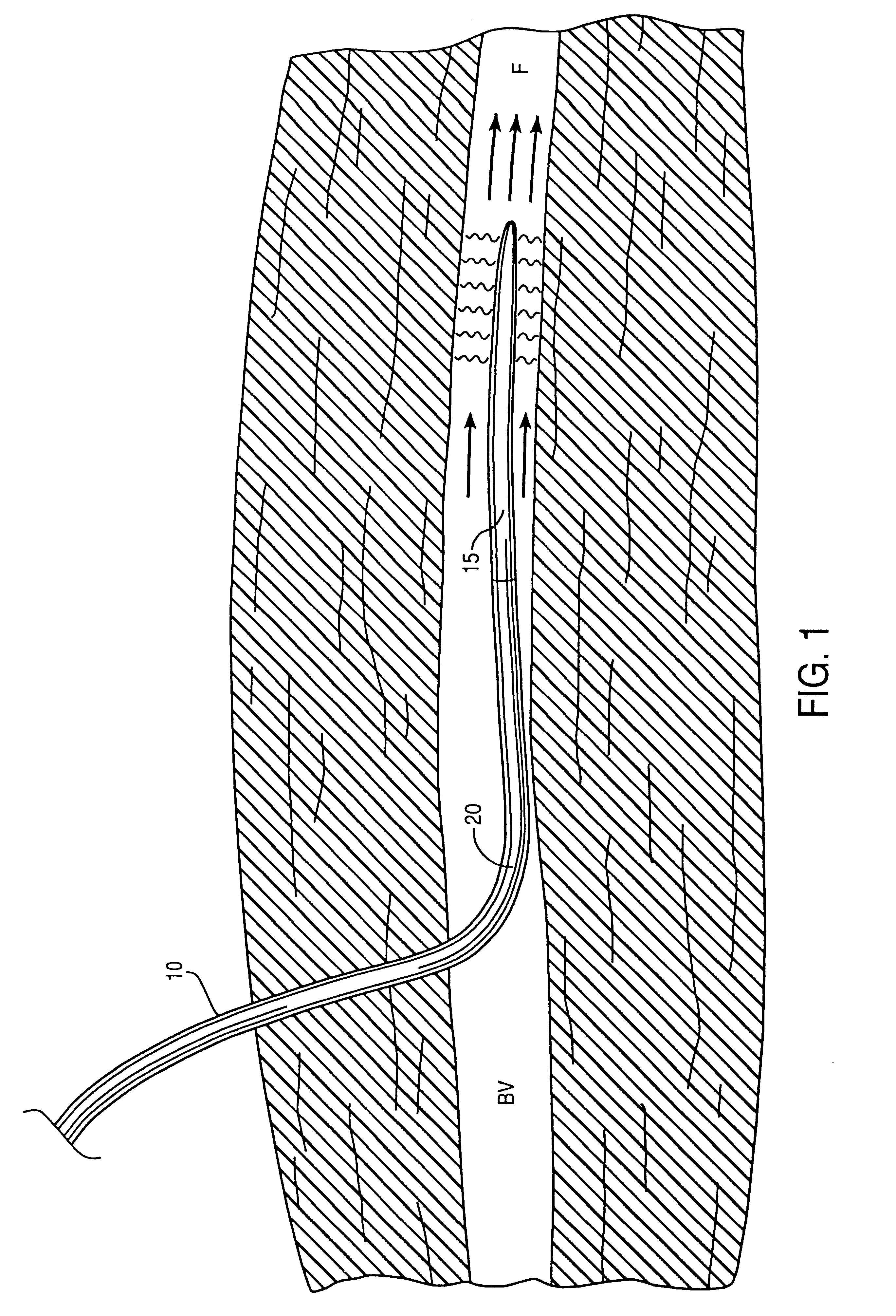

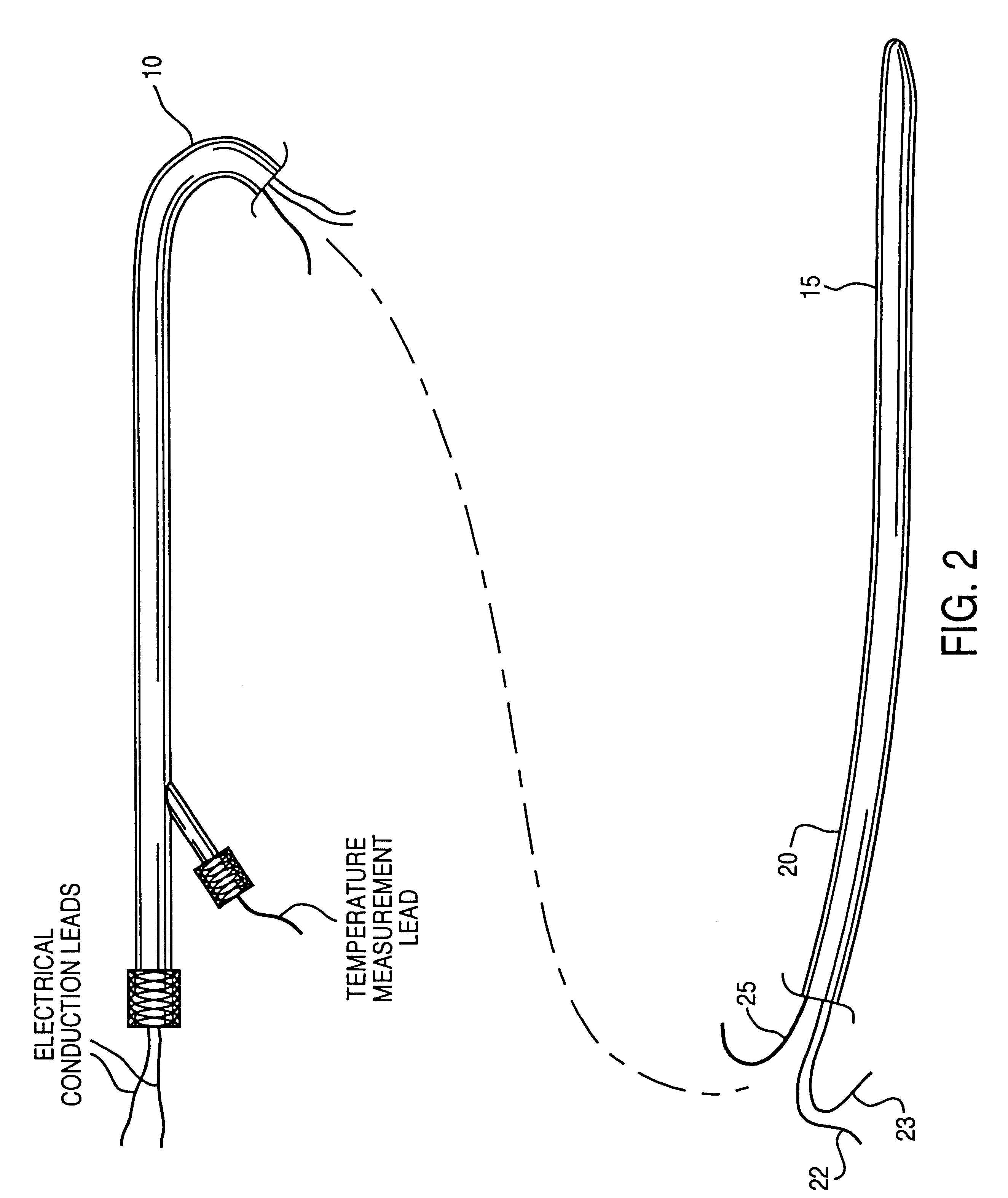

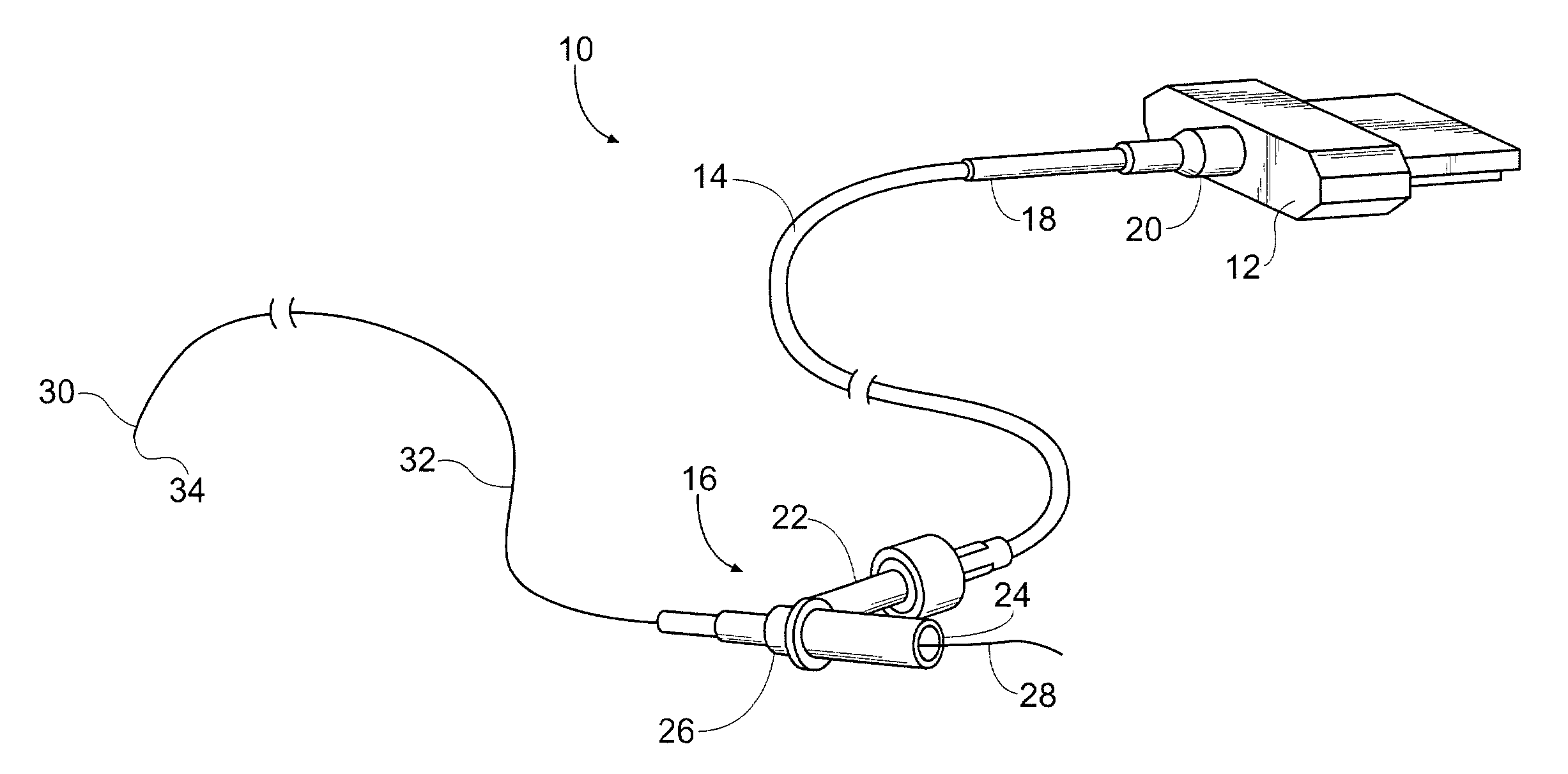

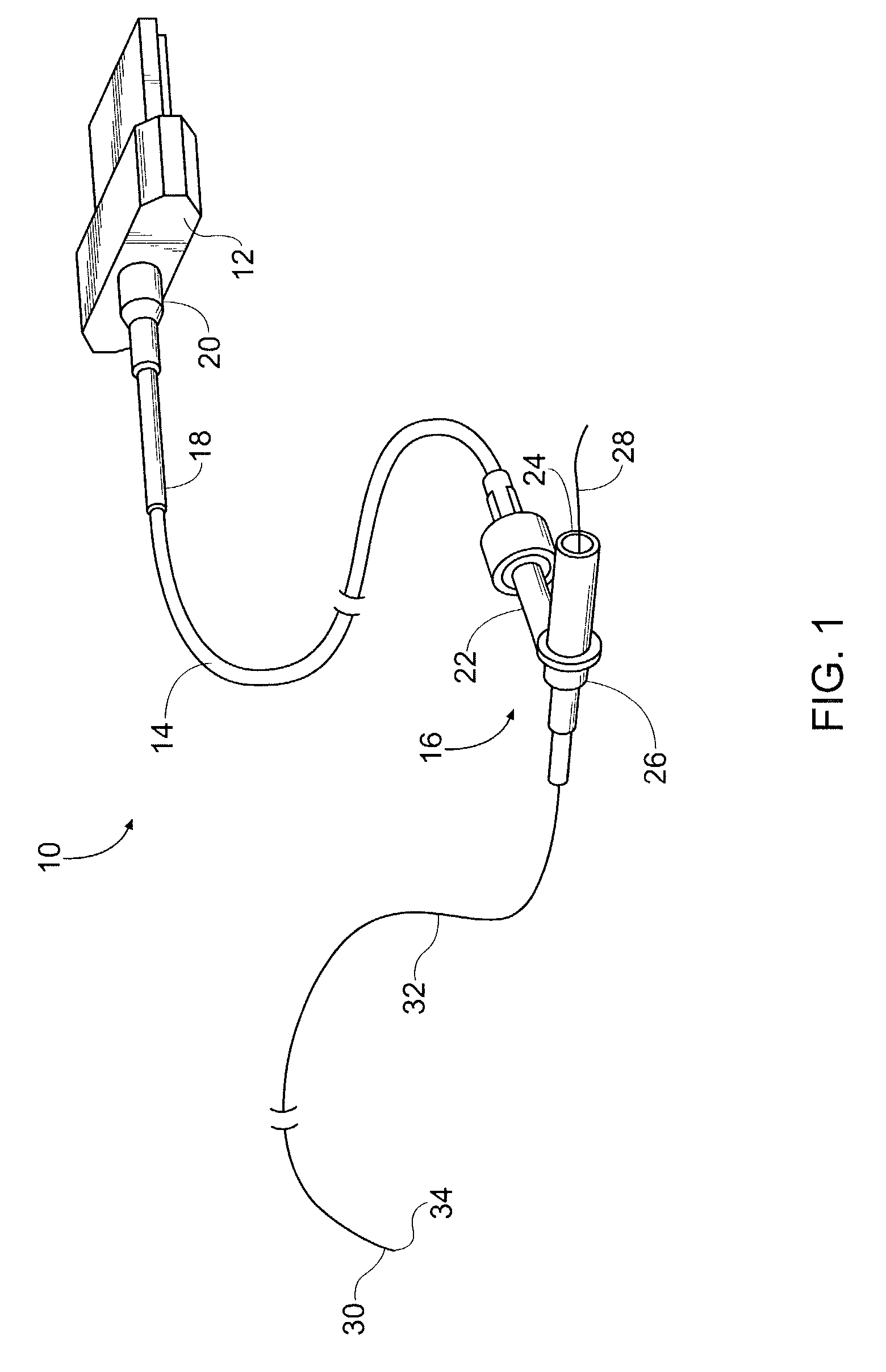

The present invention provides a method and apparatus for controlling the internal body temperature of a patient. According to the present invention, a catheter is inserted through an incision into a large blood vessel of a patient. By selectively heating or cooling a portion of the catheter lying within the blood vessel, heat may be transferred to or from blood flowing within the vessel and the patient's body temperature may thereby be increased or decreased as desired. The invention will find use in treating undesirable conditions of hypothermia and hyperthermia, or for inducing a condition of artificial hypothermia when desired.

Owner:ZOLL CIRCULATION

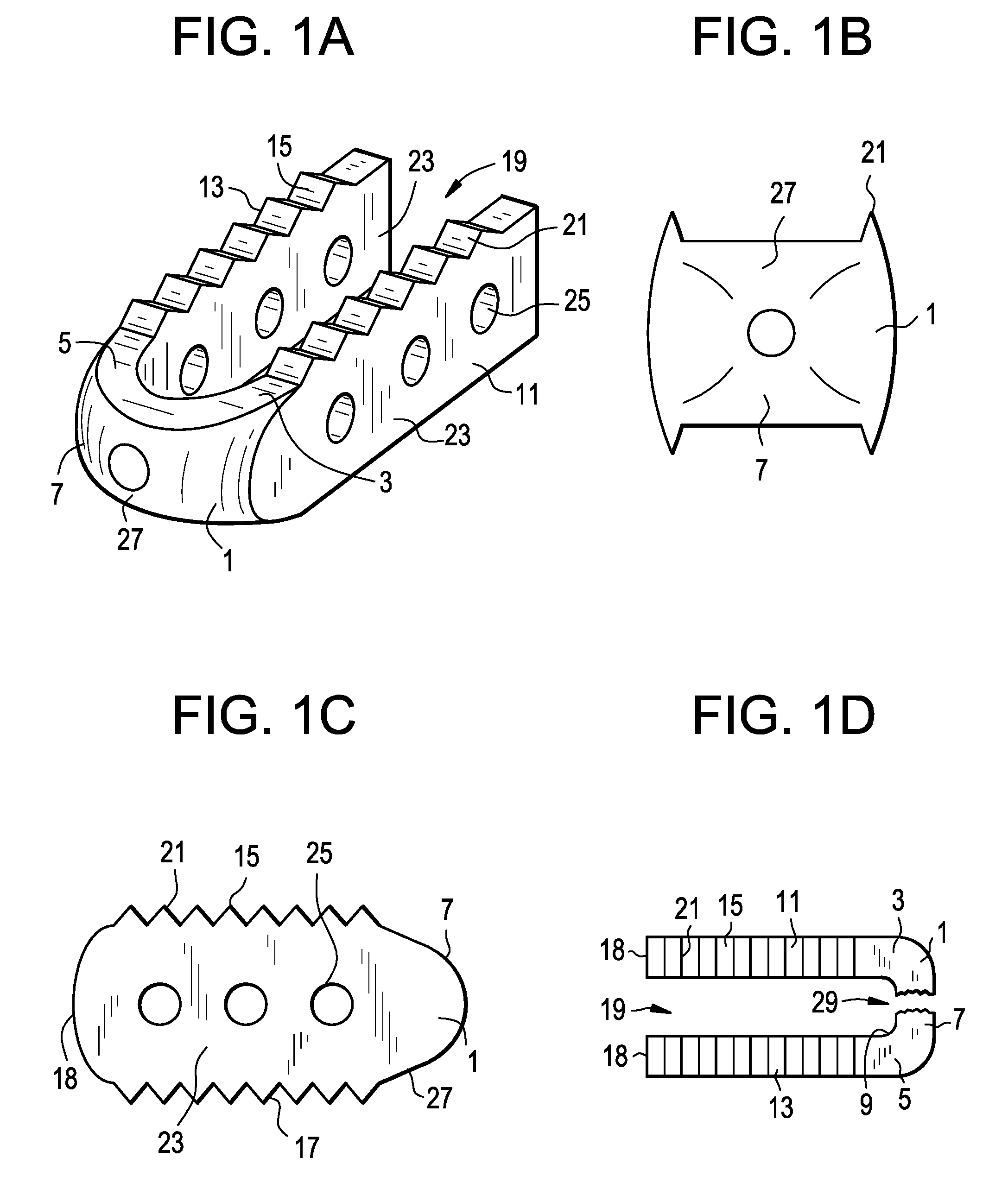

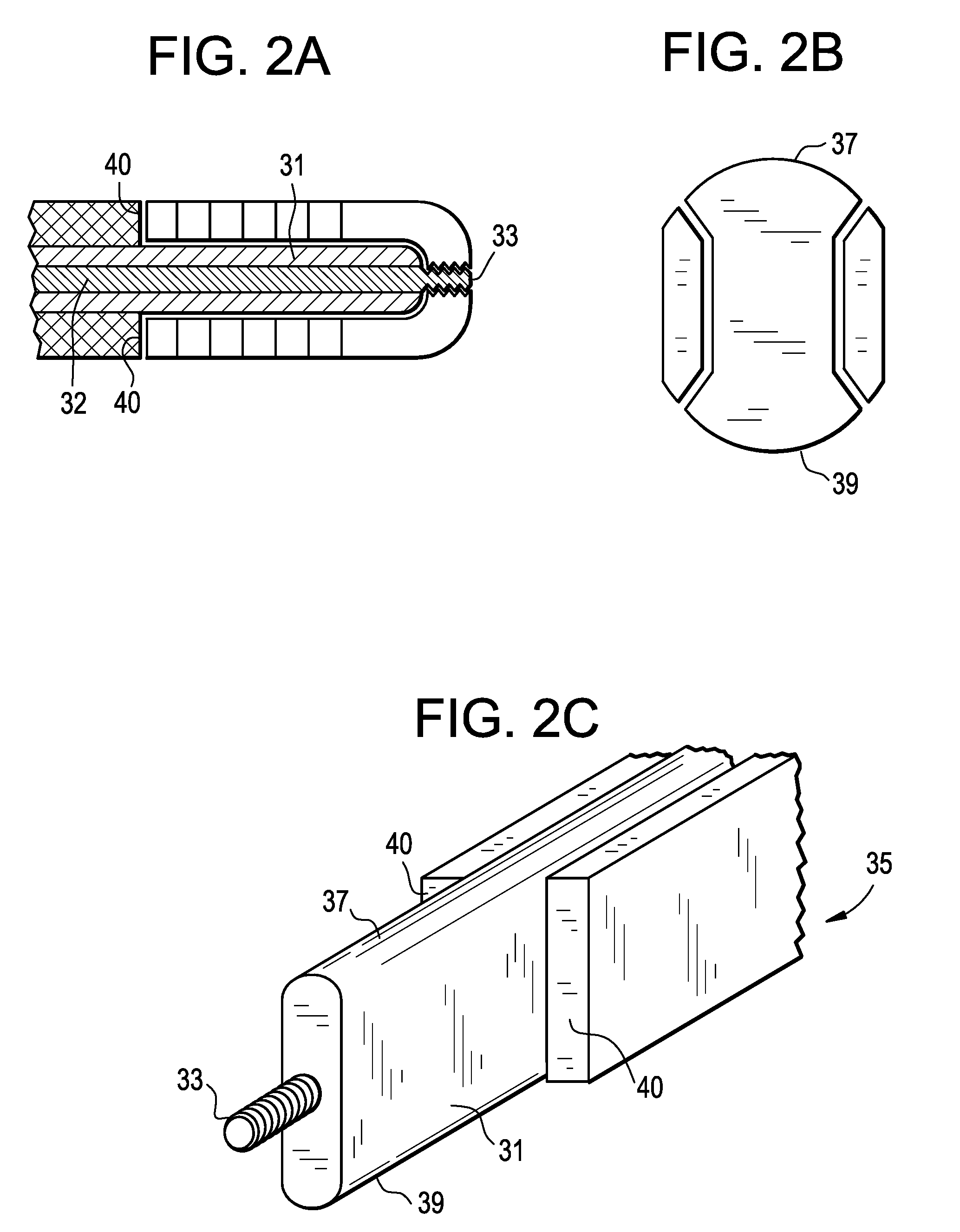

Composite vertebral spacers and instrument

ActiveUS20080154377A1Minimally invasiveEntry delayInternal osteosythesisBone implantMedicineIntervertebral fusion

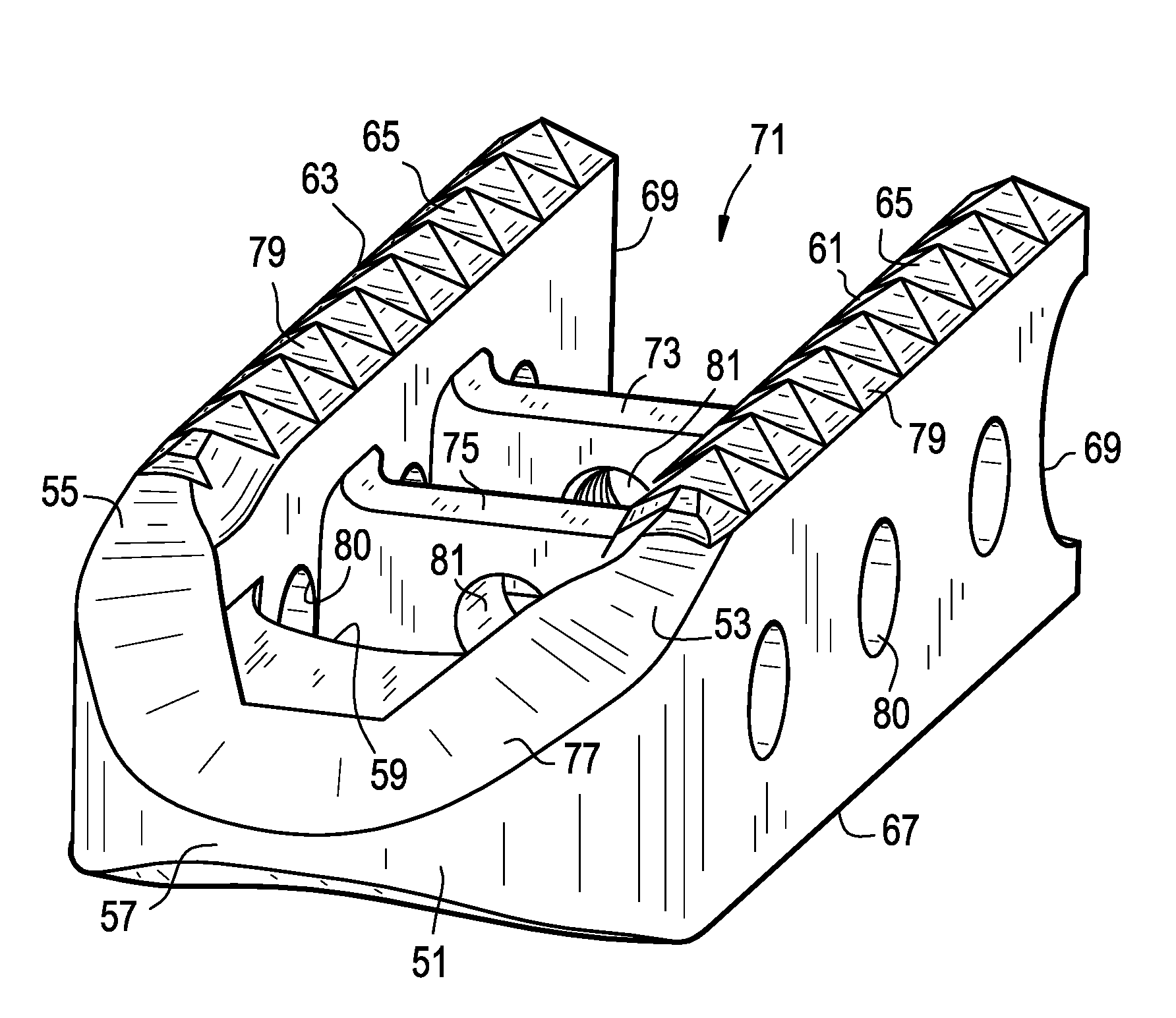

An intervertebral fusion cage that is adapted to contain an inserter within its inner volume during insertion of the cage.

Owner:MEDOS INT SARL

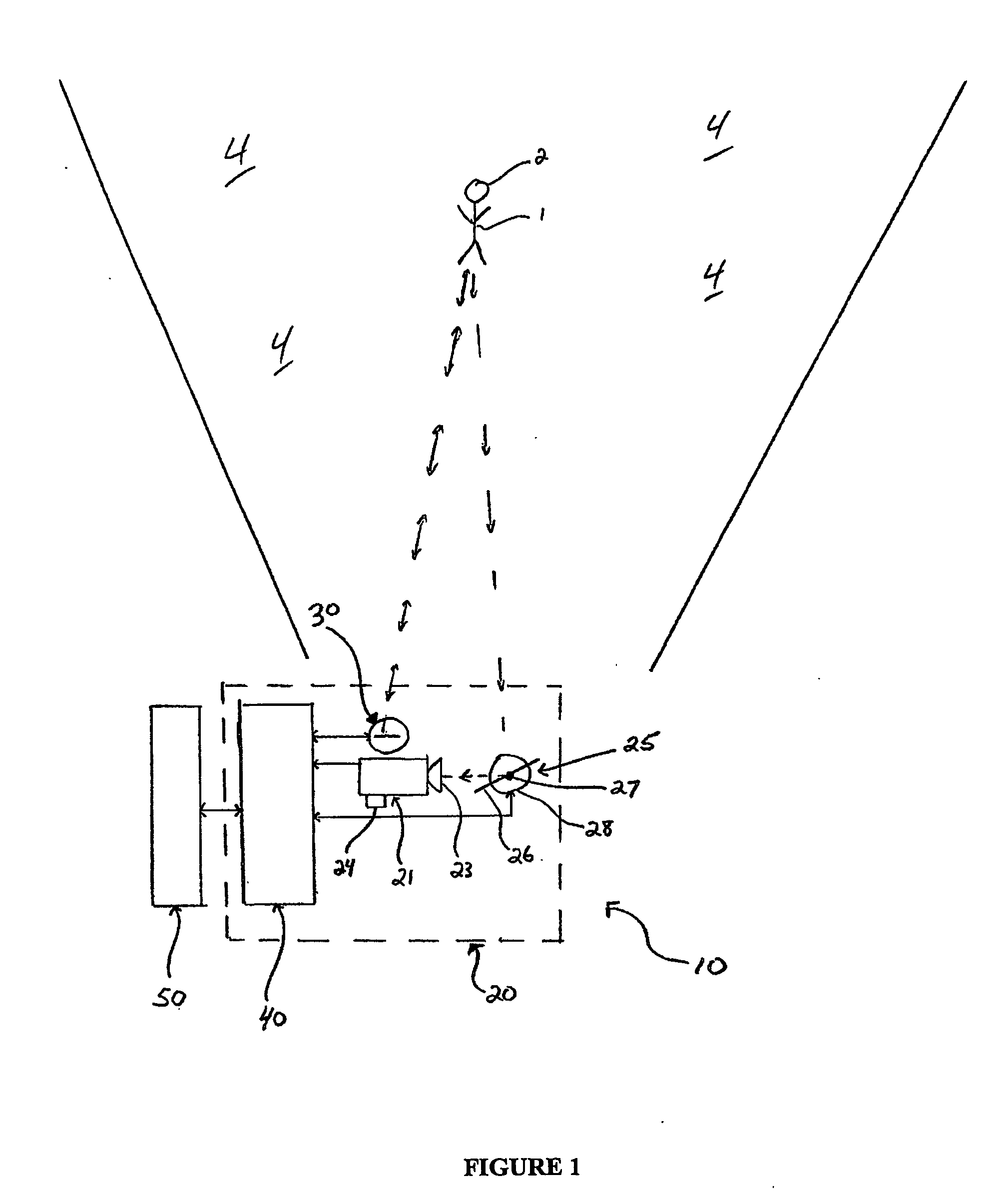

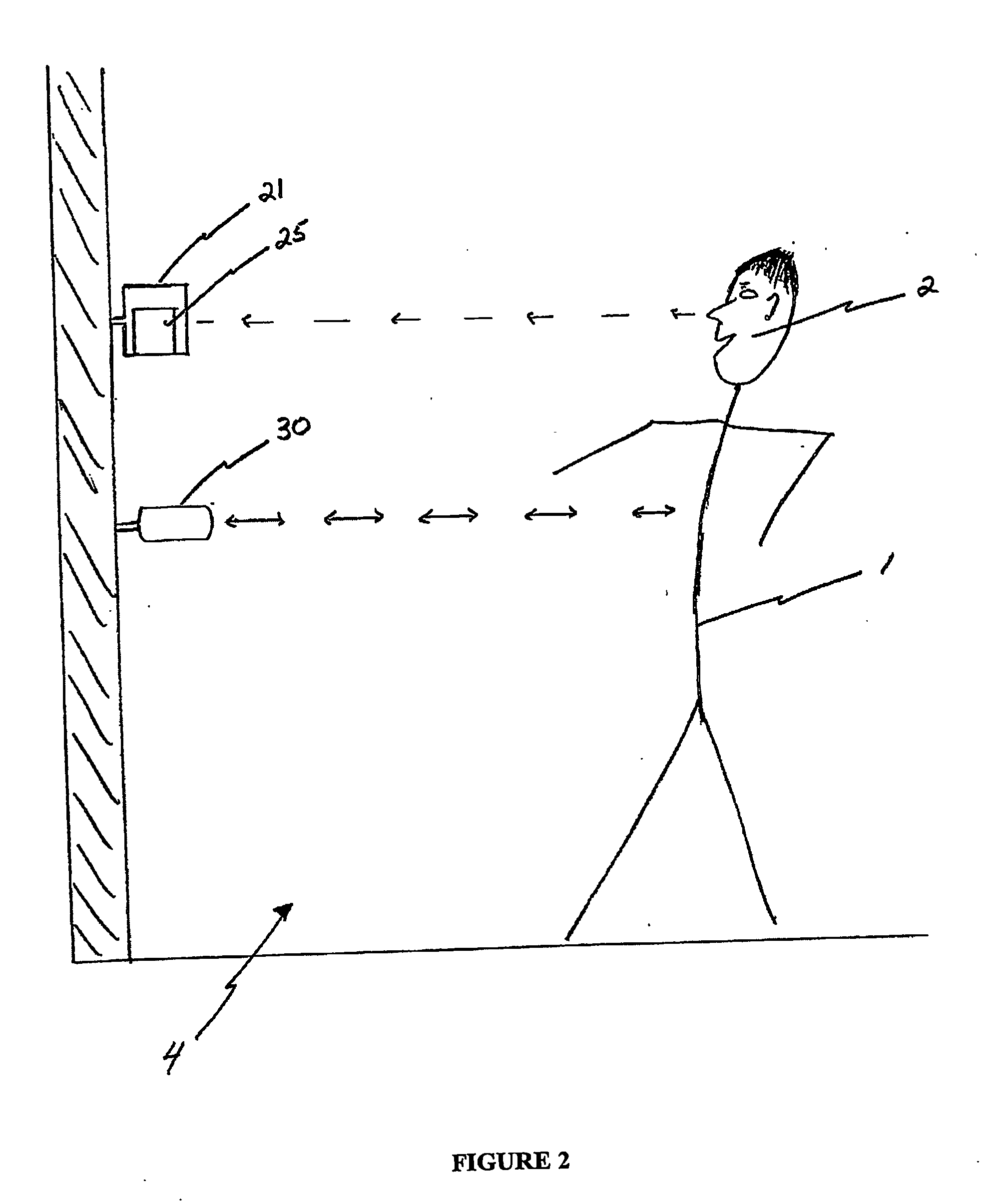

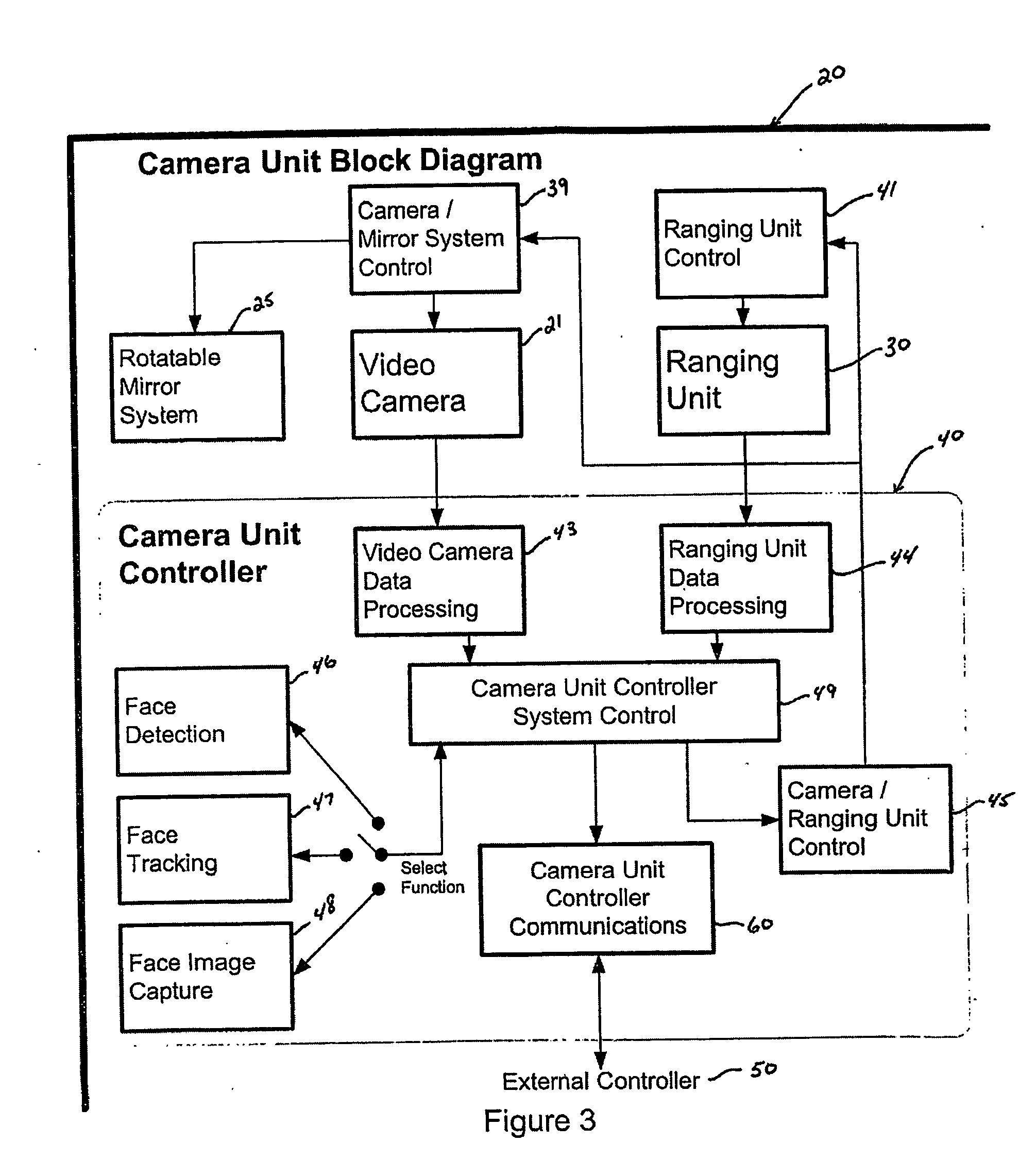

Face imaging system for recordal and automated identity confirmation

InactiveUS20050063566A1Quick checkQuality improvementDiagnostics using lightCharacter and pattern recognitionFace detectionCommunications system

A face imaging system for recordal and / or automated identity confirmation, including a camera unit and a camera unit controller. The camera unit includes a video camera, a rotatable mirror system for directing images of the security area into the video camera, and a ranging unit for detecting the presence of a target and for providing target range data, comprising distance, angle and width information, to the camera unit controller. The camera unit controller includes software for detecting face images of the target, tracking of detected face images, and capture of high quality face images. A communication system is provided for sending the captured face images to an external controller for face verification, face recognition and database searching. Face detection and face tracking is performed using the combination of video images and range data and the captured face images are recorded and / or made available for face recognition and searching.

Owner:BIODENTITY SYST CORP

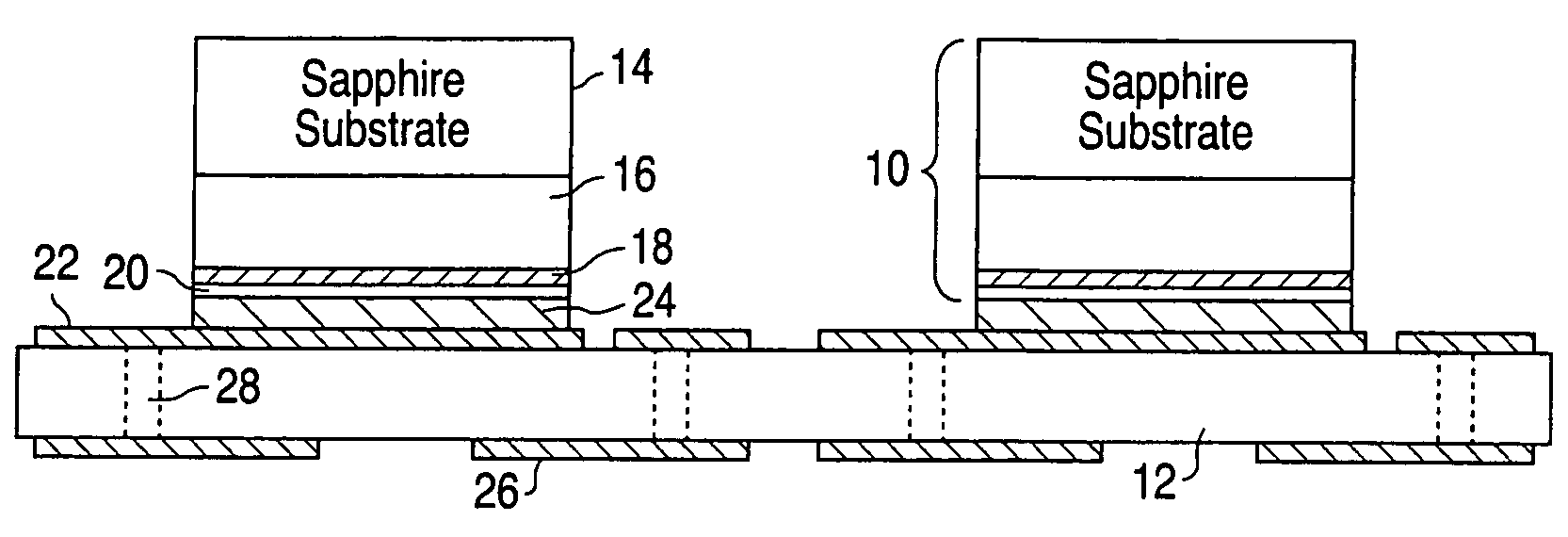

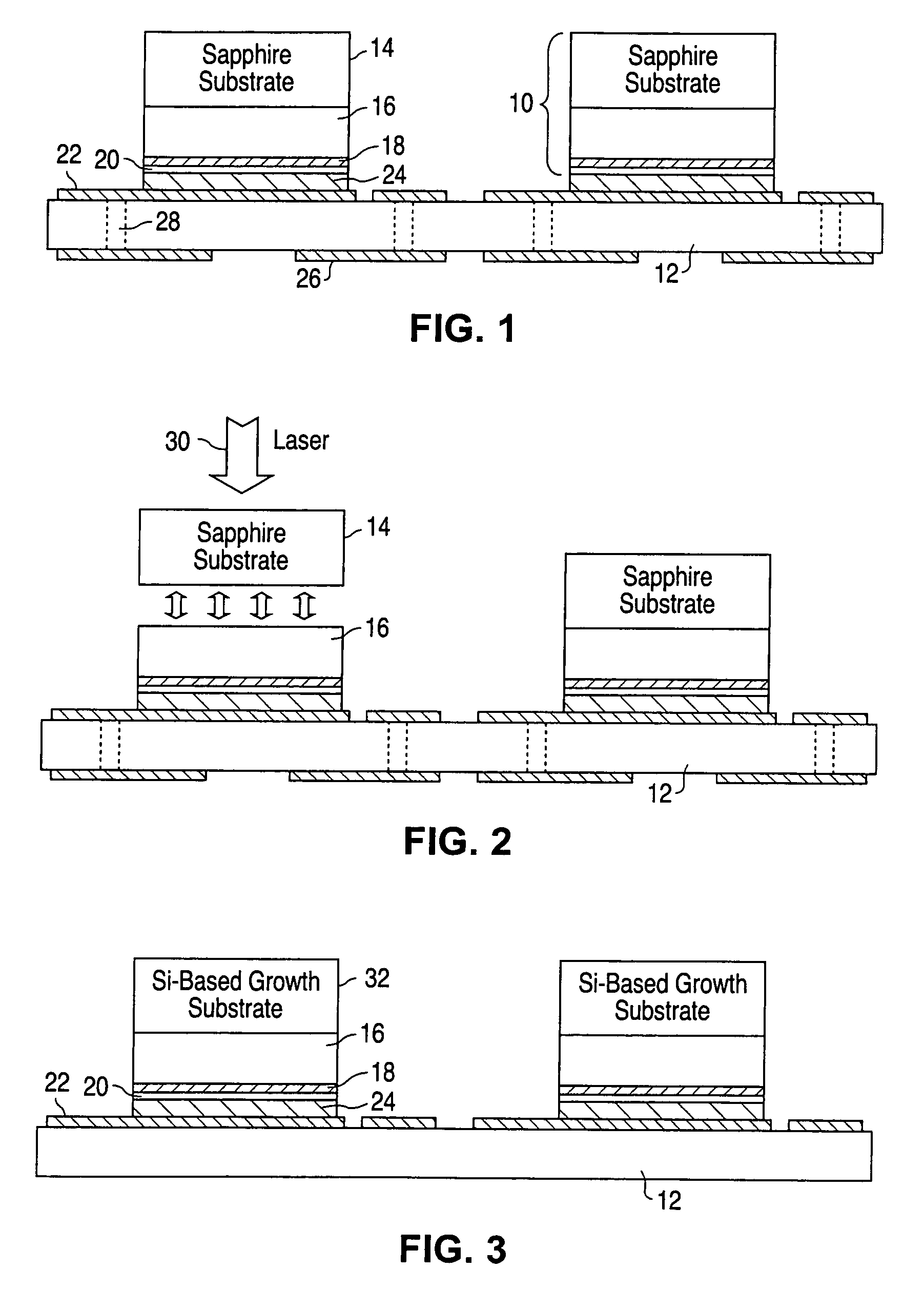

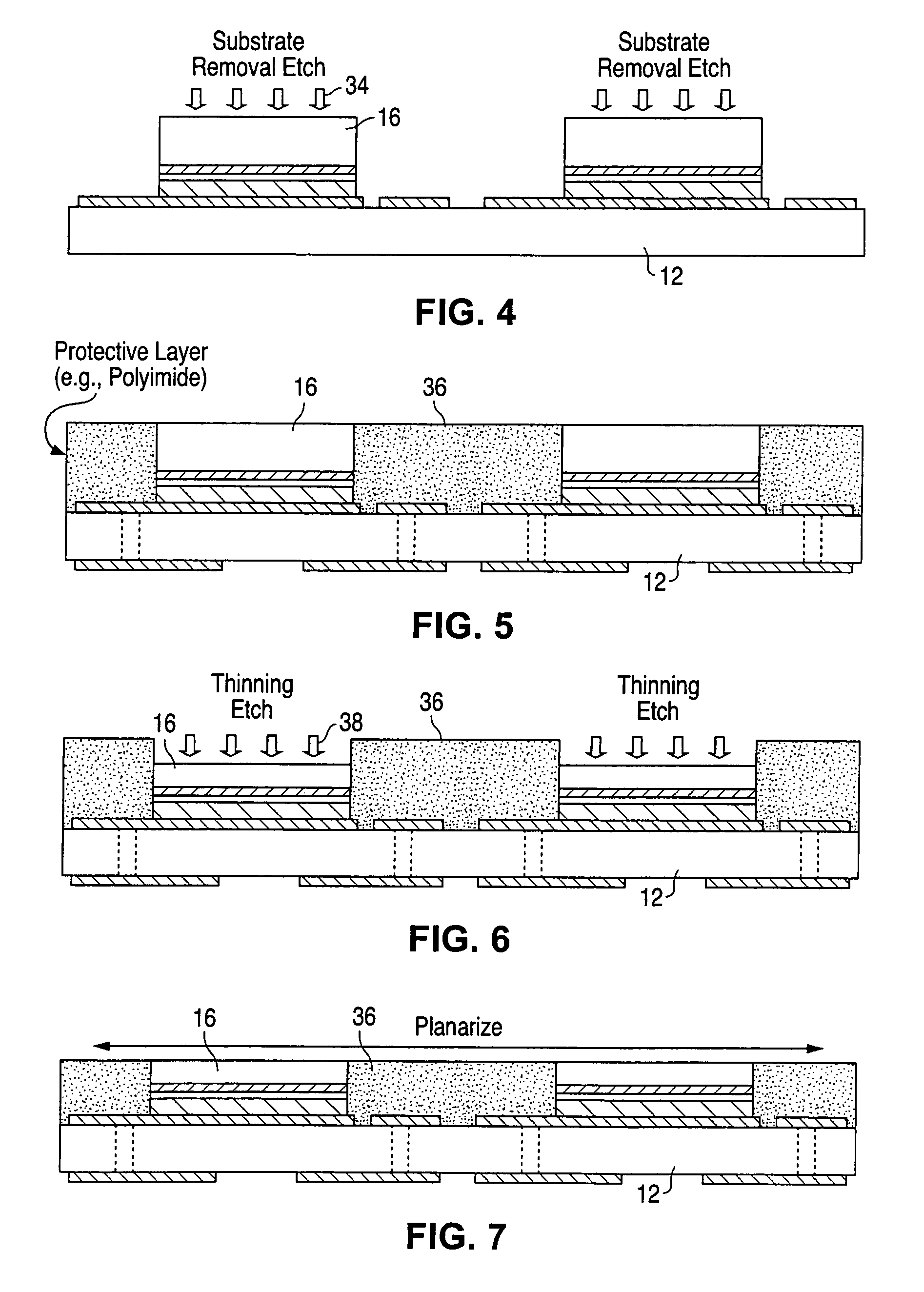

Package-integrated thin film LED

ActiveUS7256483B2Little absorption of lightHigh thermal conductivitySemiconductor/solid-state device detailsSolid-state devicesThermal conductivityEngineering

LED epitaxial layers (n-type, p-type, and active layers) are grown on a substrate. For each die, the n and p layers are electrically bonded to a package substrate that extends beyond the boundaries of the LED die such that the LED layers are between the package substrate and the growth substrate. The package substrate provides electrical contacts and conductors leading to solderable package connections. The growth substrate is then removed. Because the delicate LED layers were bonded to the package substrate while attached to the growth substrate, no intermediate support substrate for the LED layers is needed. The relatively thick LED epitaxial layer that was adjacent the removed growth substrate is then thinned and its top surface processed to incorporate light extraction features. There is very little absorption of light by the thinned epitaxial layer, there is high thermal conductivity to the package because the LED layers are directly bonded to the package substrate without any support substrate therebetween, and there is little electrical resistance between the package and the LED layers so efficiency (light output vs. power input) is high. The light extraction features of the LED layer further improves efficiency.

Owner:LUMILEDS

Catheter system for controlling a patient's body temperature by in situ blood temperature modification

InactiveUS6306161B1Quickly felt throughout the patient's bodyEliminate damageStentsBalloon catheterMedicineHigh body temperature

Owner:ZOLL CIRCULATION

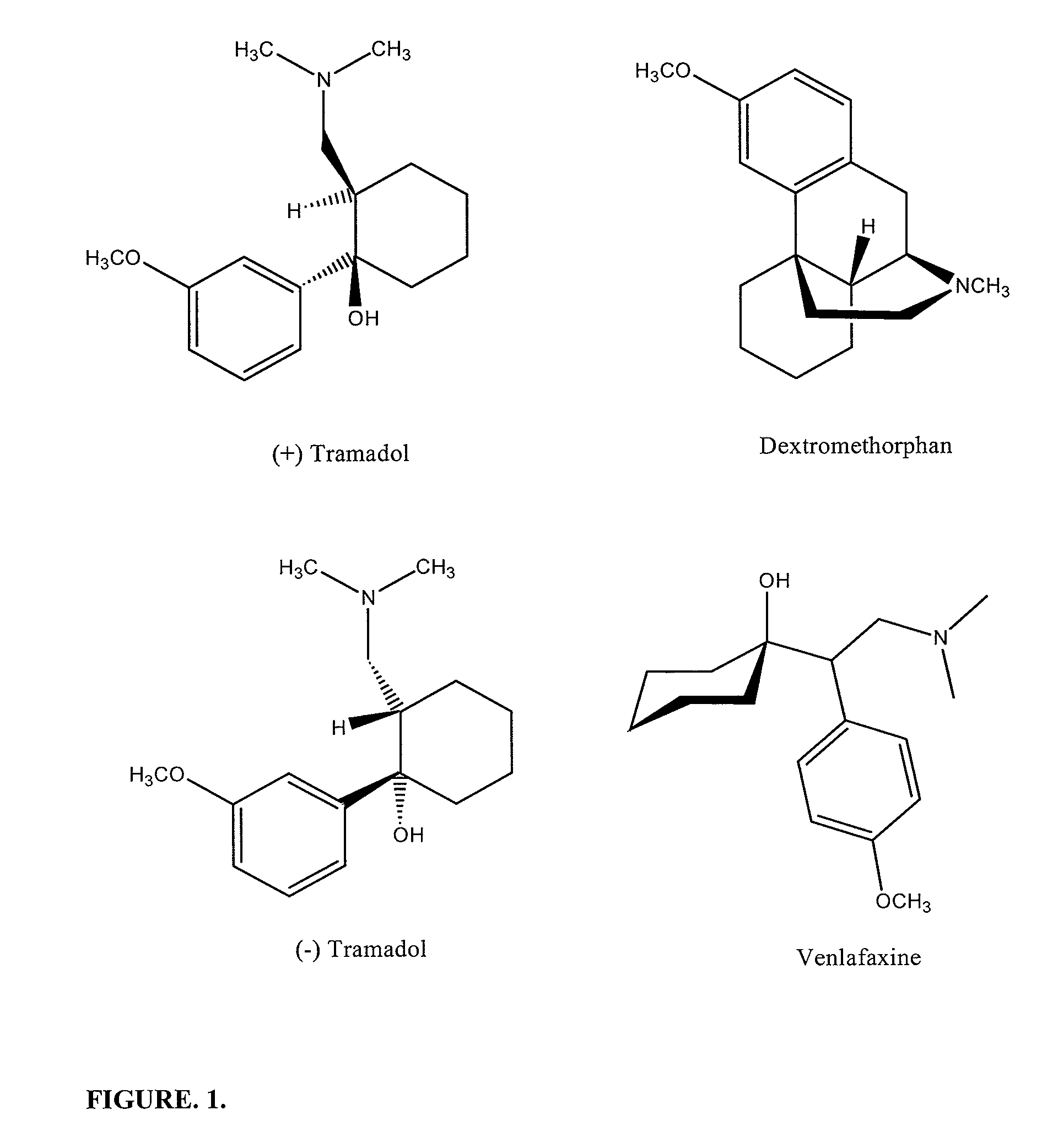

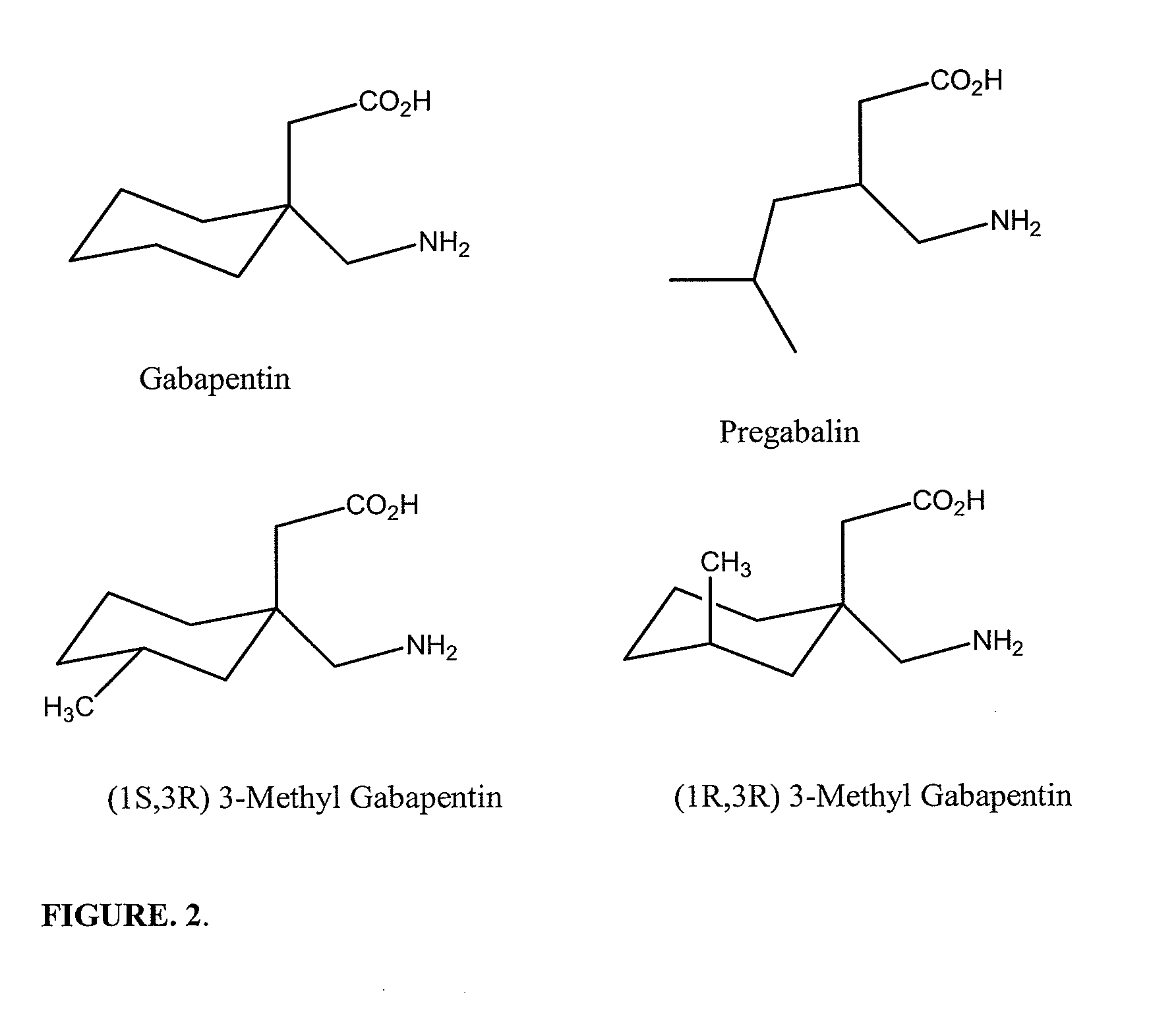

Pharamaceutical compositions for treating chronic pain and pain associated with neuropathy

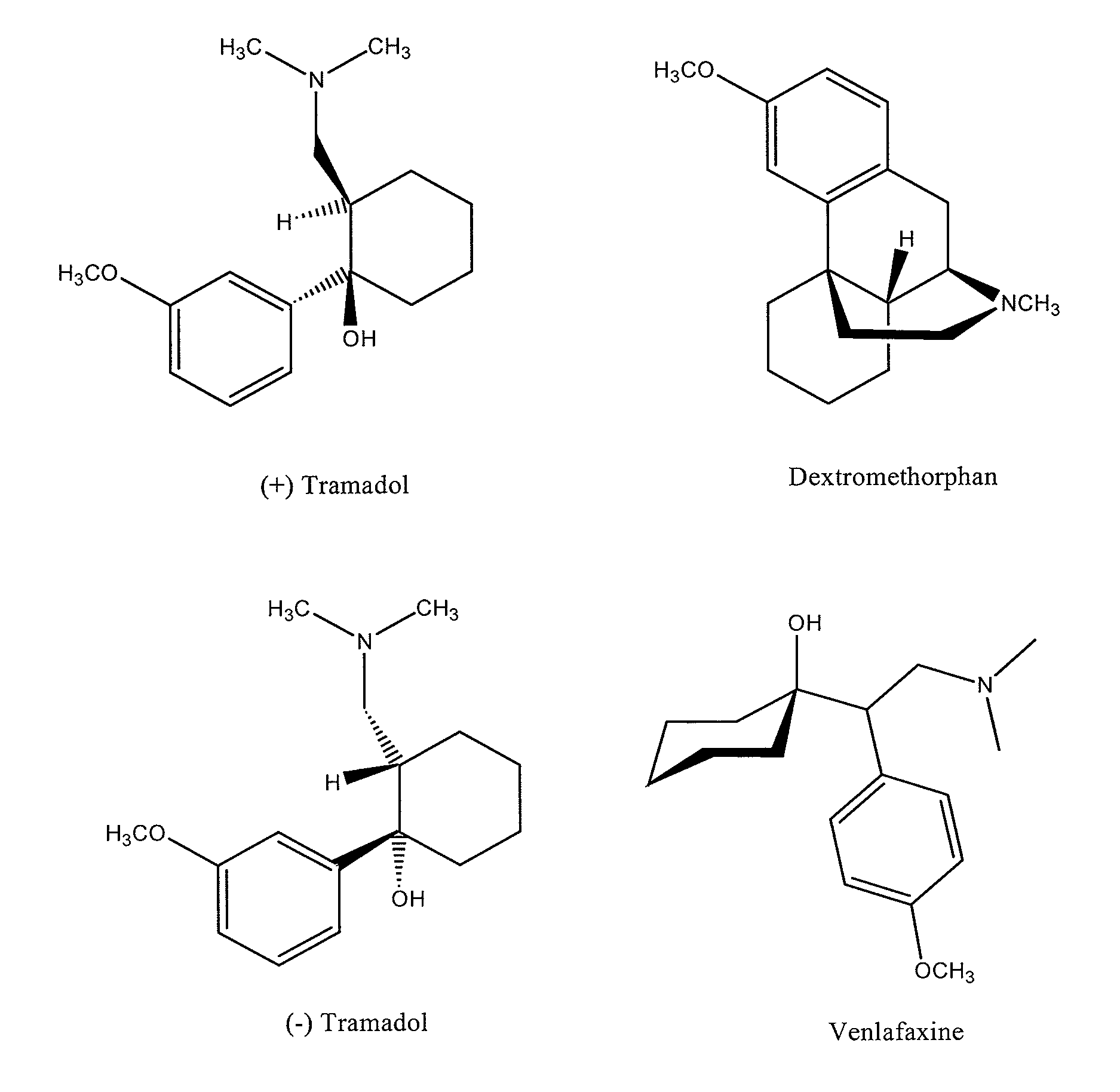

ActiveUS20110039875A1Clear synergyEliminate majorityBiocideNervous disorderGabapentinN-Methyl-D-aspartic acid

The present invention provides methods and compositions for the treatment of neuropathic pain. In certain embodiments, compositions comprising an dextromethorphan (or other N-methyl-D-aspartate receptor antagonist), tramadol, and gabapentin can synergistically act to reduce pain in a human patient. Pharmaceutical compositions may also comprise a capsaicinoid, an esterified capsaicinoid, and / or a tricyclic antidepressant.

Owner:LUMINUS BIOSCIENCES INC

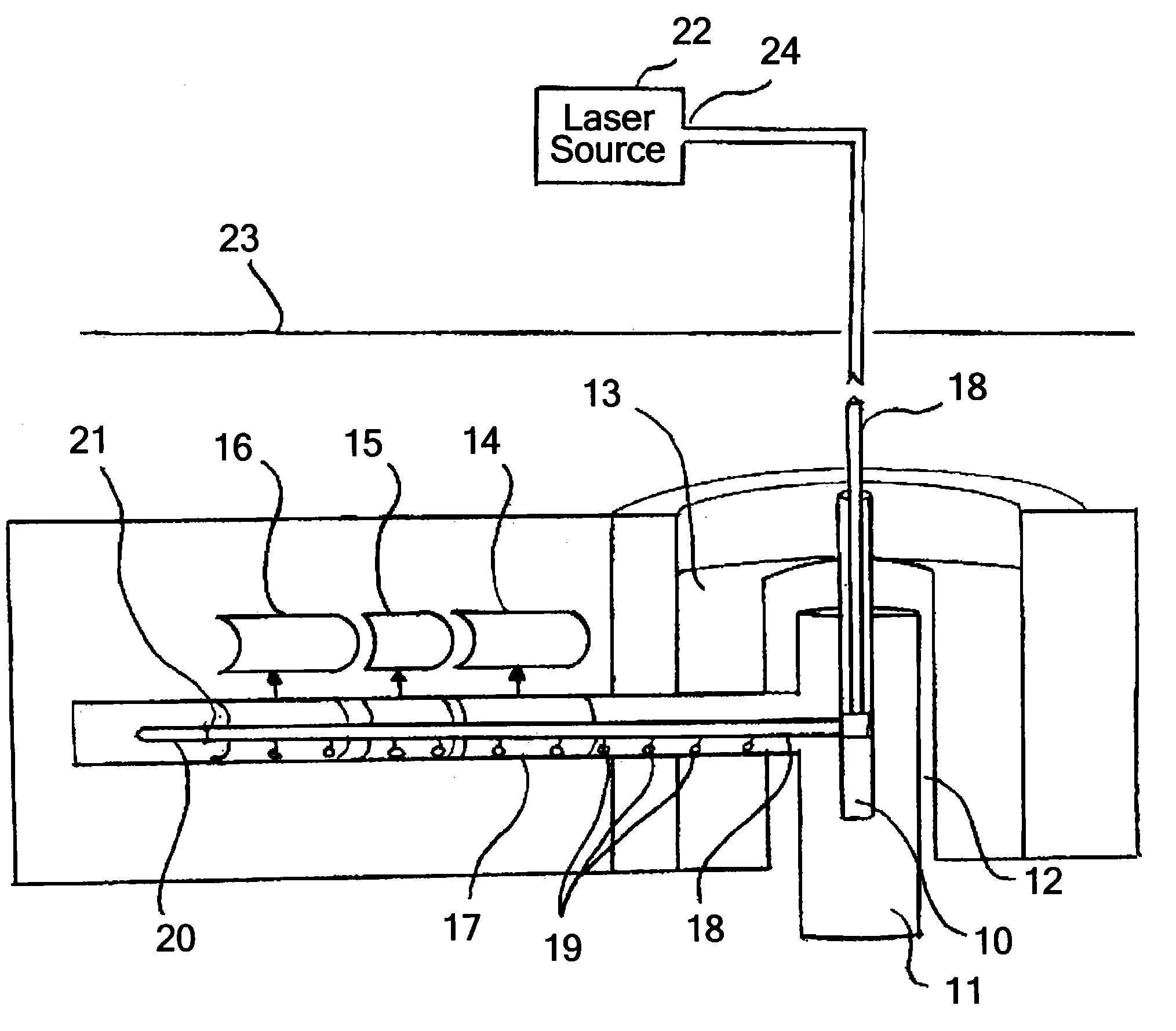

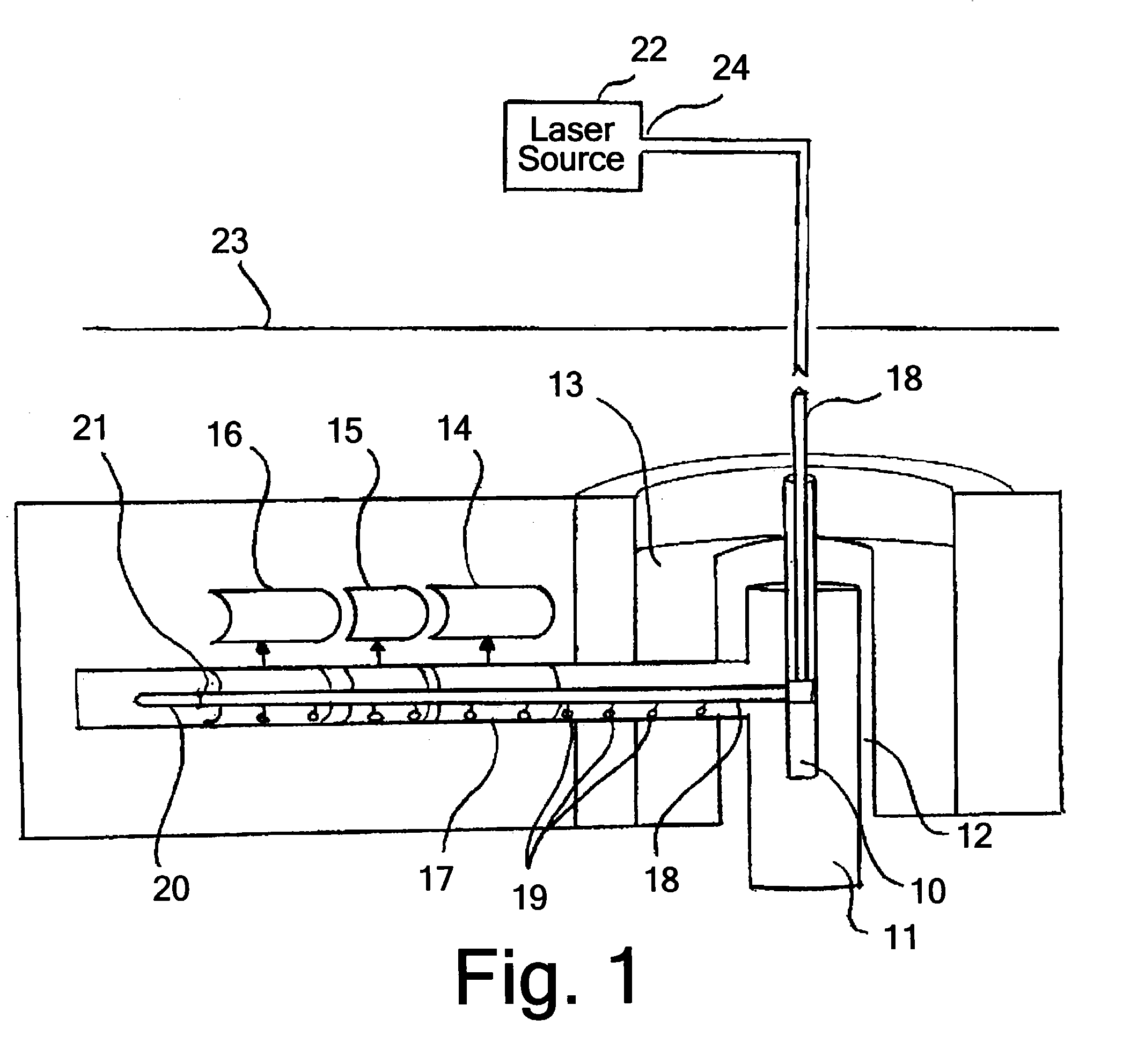

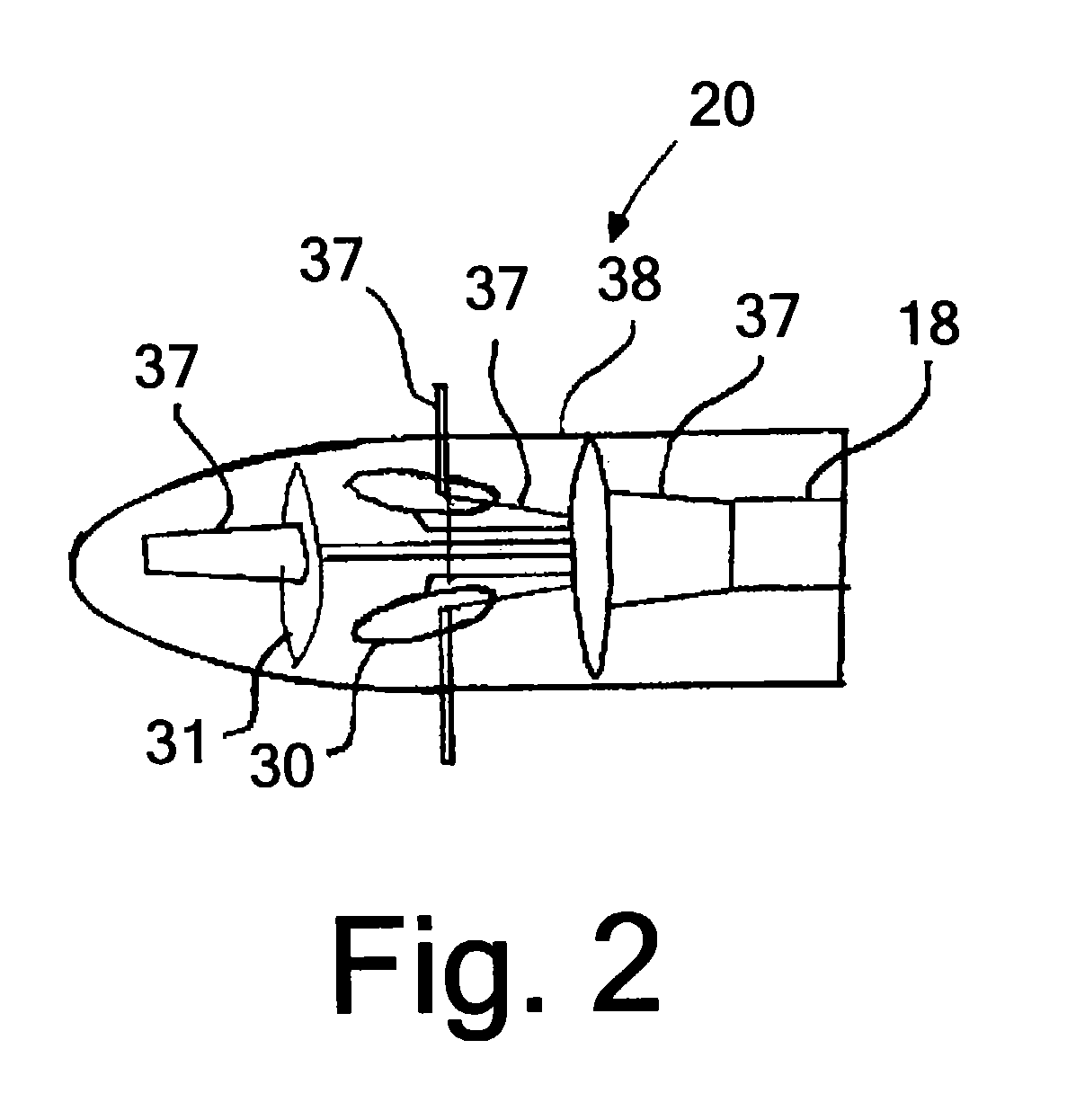

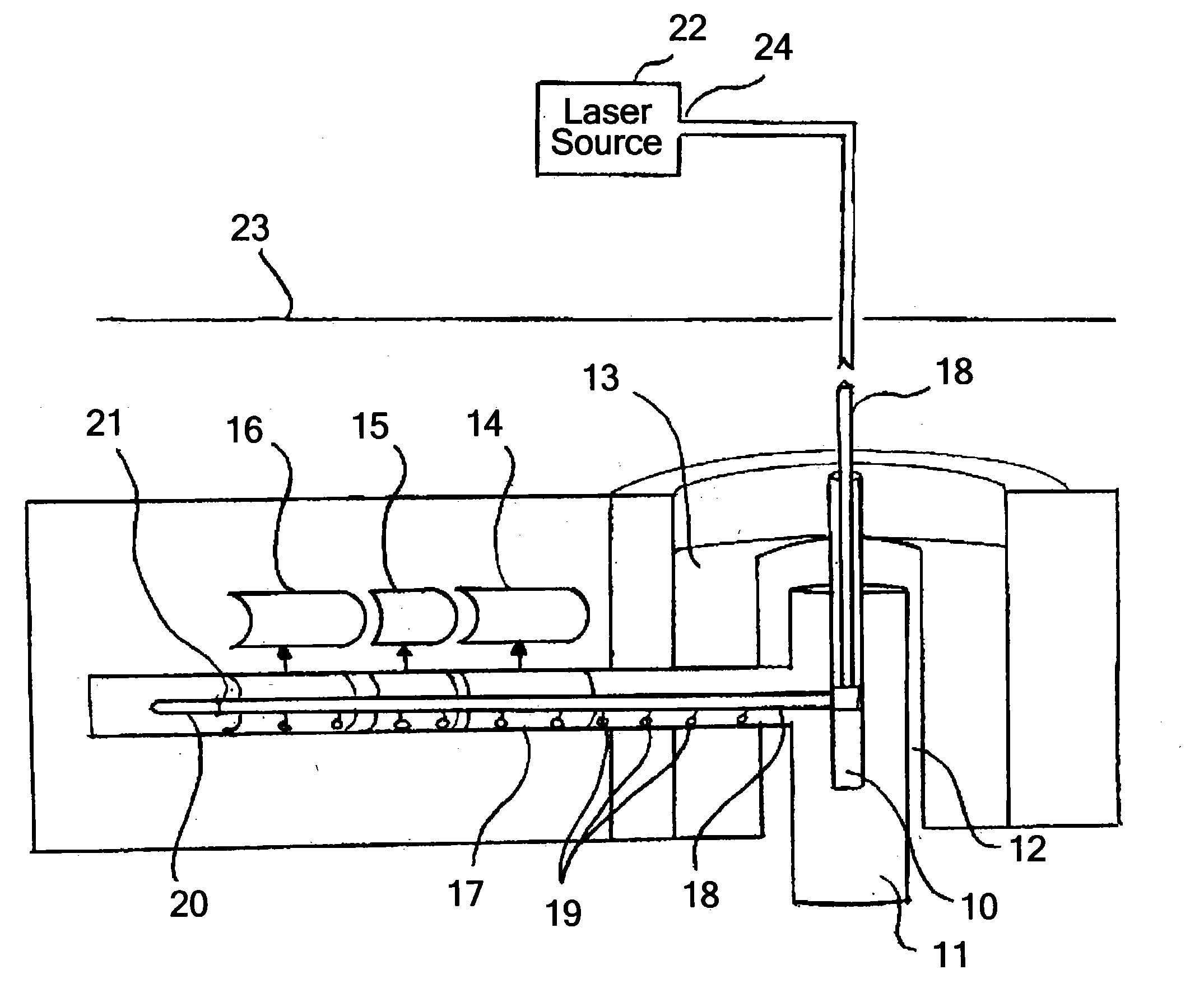

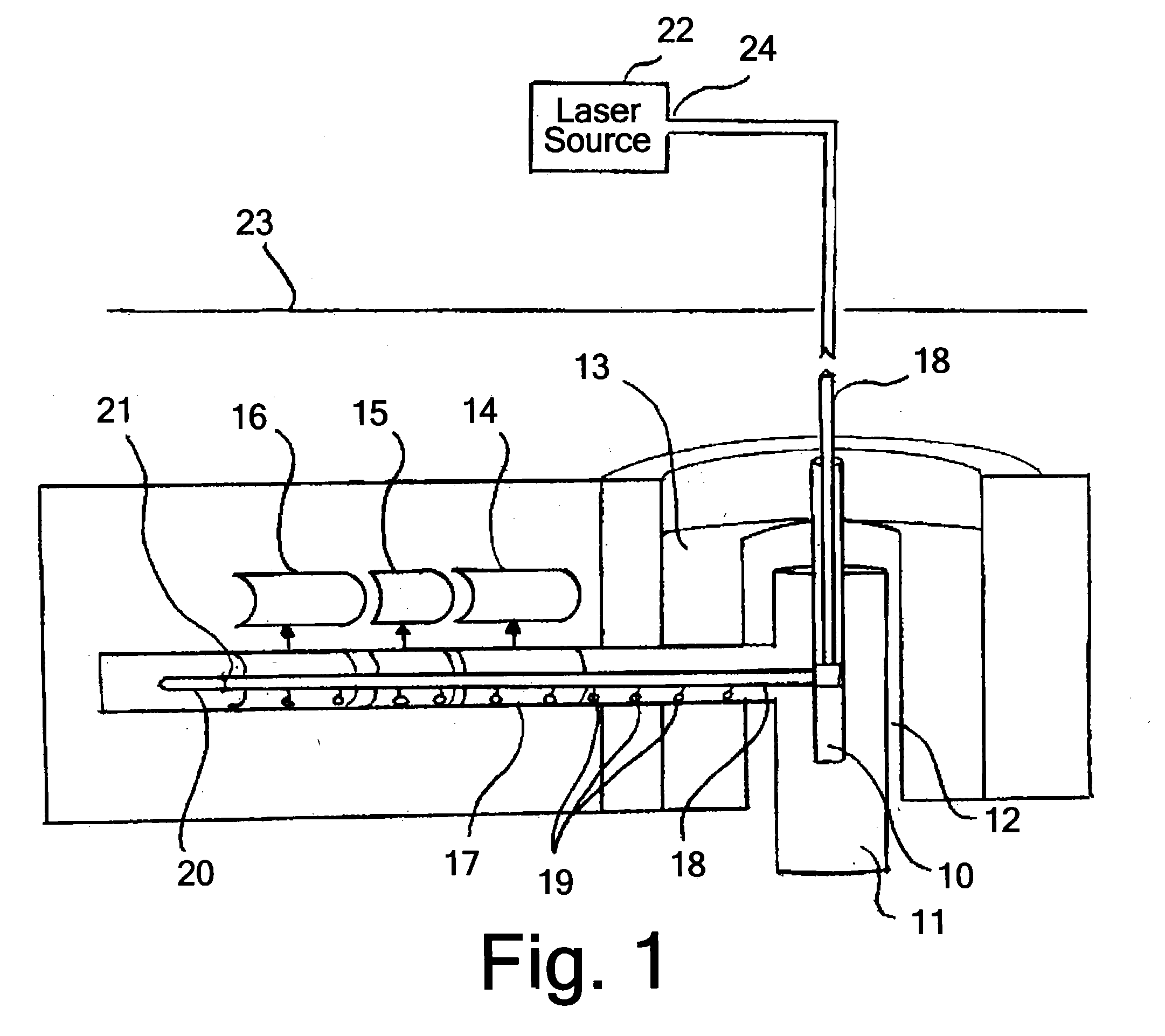

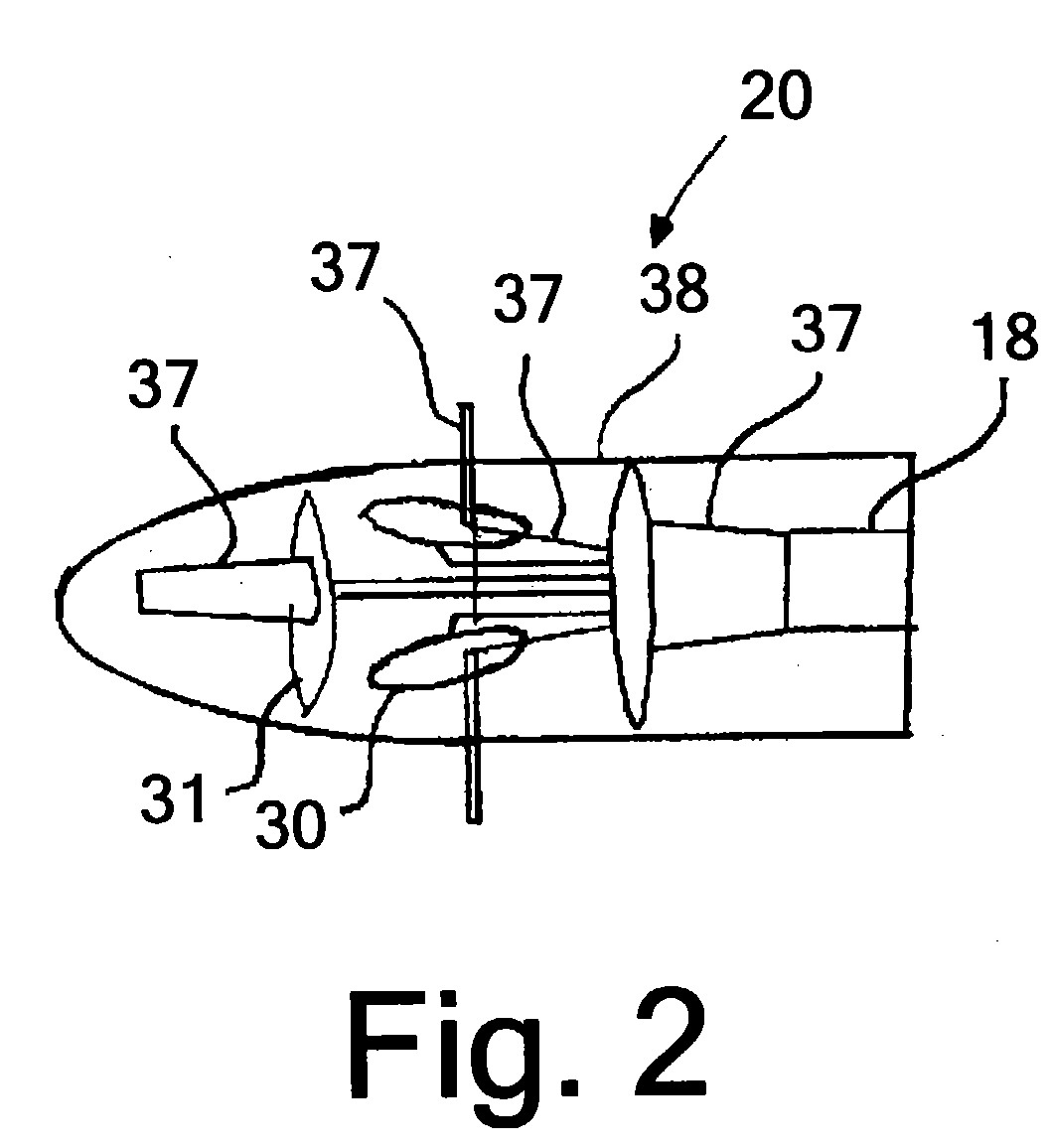

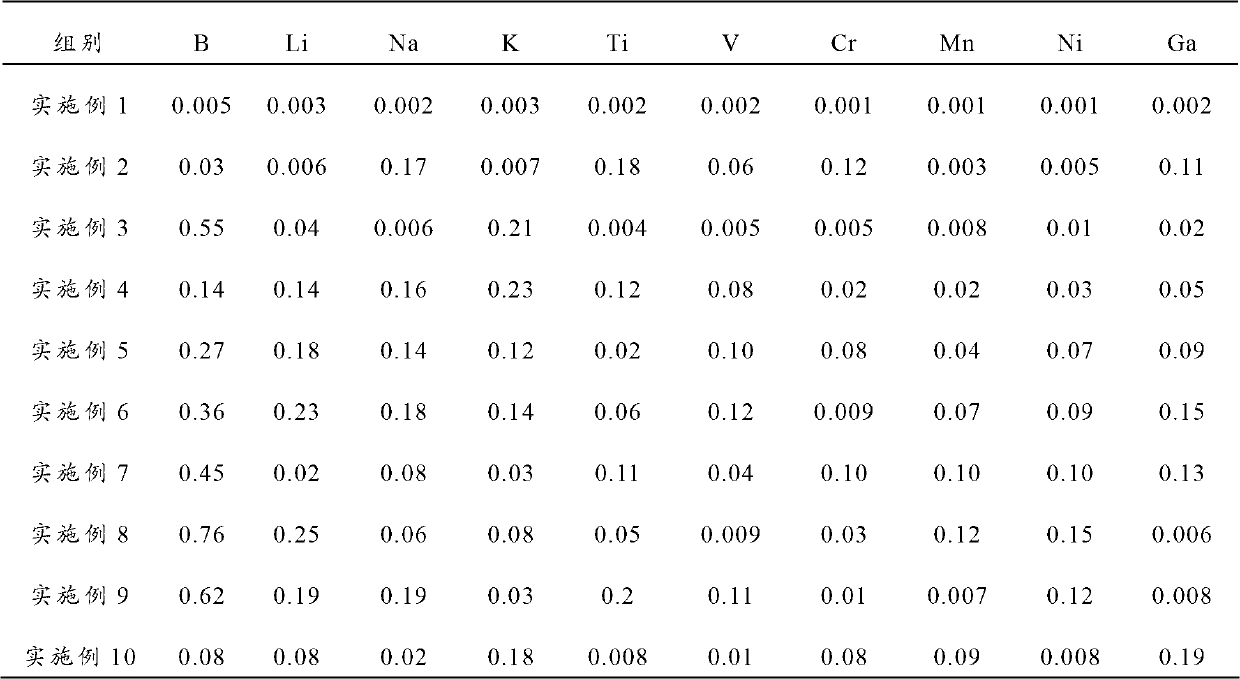

Fiber optics laser perforation tool

InactiveUS6888097B2Eliminate damageReduce productionDisloding machinesThermal drillingFiberOptoelectronics

Owner:GAS TECH INST

Substrate tester location clamping, sensing, and contacting method and apparatus

InactiveUS6043667AEliminate damageDigital variable displayElectronic circuit testingContact methodCam

A substrate tester and method of testing are disclosed in which the tester moves a substrate to be tested into a precise location within the tester prior to making contact with fragile tester pins. The substrate is then clamped in a precise X-Y location relative to the tester contact pins, also without making contact with the tester pins. Next the substrate top surface is moved quickly to a precise Z-axis location, whereupon the tester contact pins are finally applied to the substrate using Z-axis motion only. In addition, a mechanism is included that features a cam-pivot arm micro-switch combination to sense when a product is not properly positioned in or missing from the test station.

Owner:IBM CORP

Fiber optics laser perforation tool

InactiveUS20040256103A1Eliminate damageReduce productionDisloding machinesThermal drillingFiberOptoelectronics

An apparatus for perforation of wellbore walls, which apparatus includes a fiber optic cable having a laser input end and a laser output end. A laser source is operably connected to the laser input end and a laser head is connected to the laser output end. The laser head includes a laser control components for controlling at least one laser beam characteristic. Laser head control elements for controlling the motion and location of the laser head are operably connected to the fiber optic cable. The laser head is enclosed in a protective housing, which protects the fiber optic cable and elements, such as reflectors and lenses for controlling the laser beam emitted by the fiber optic cable disposed therein, from the harsh environments encountered in downhole operations.

Owner:GAS TECH INST

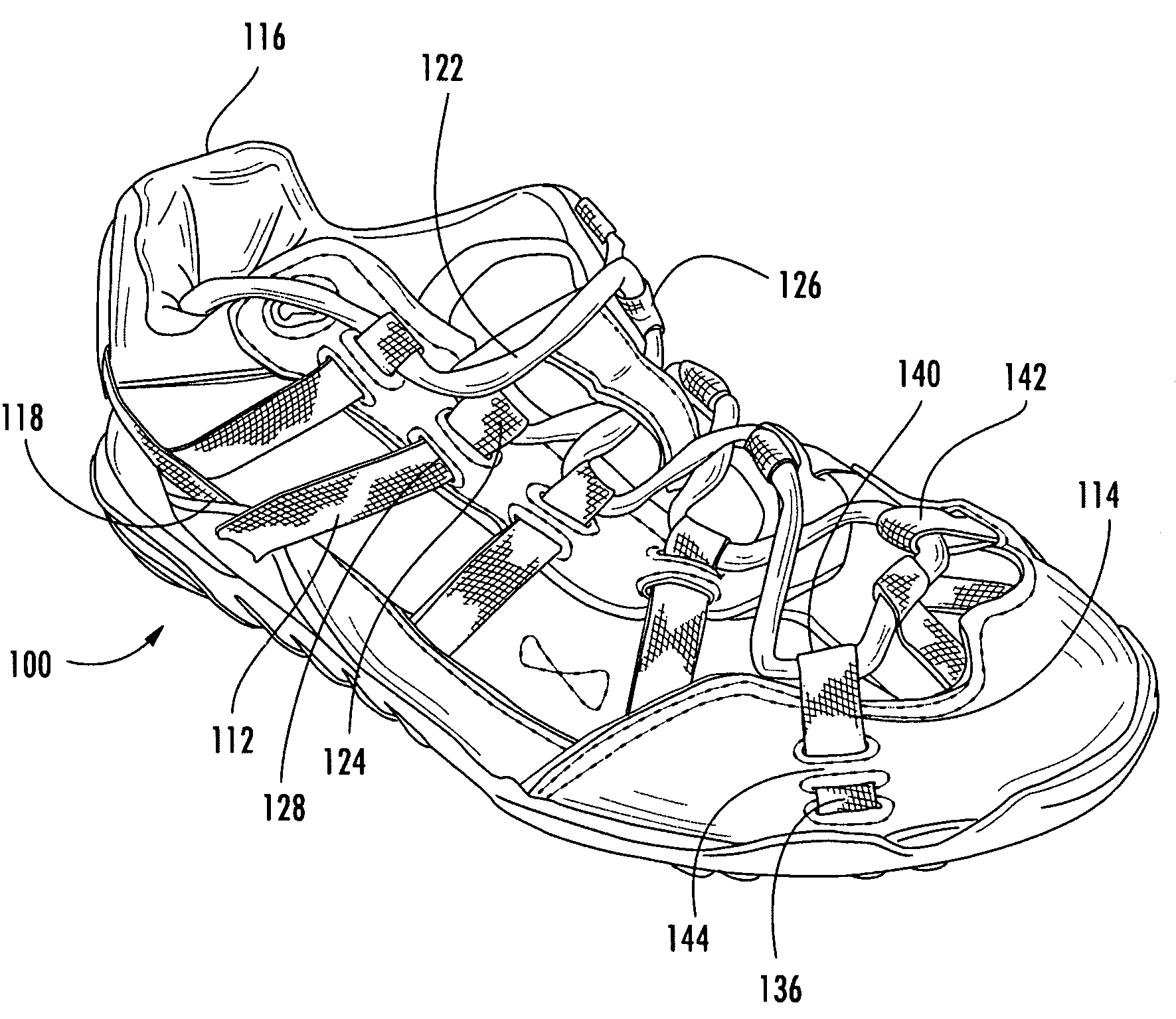

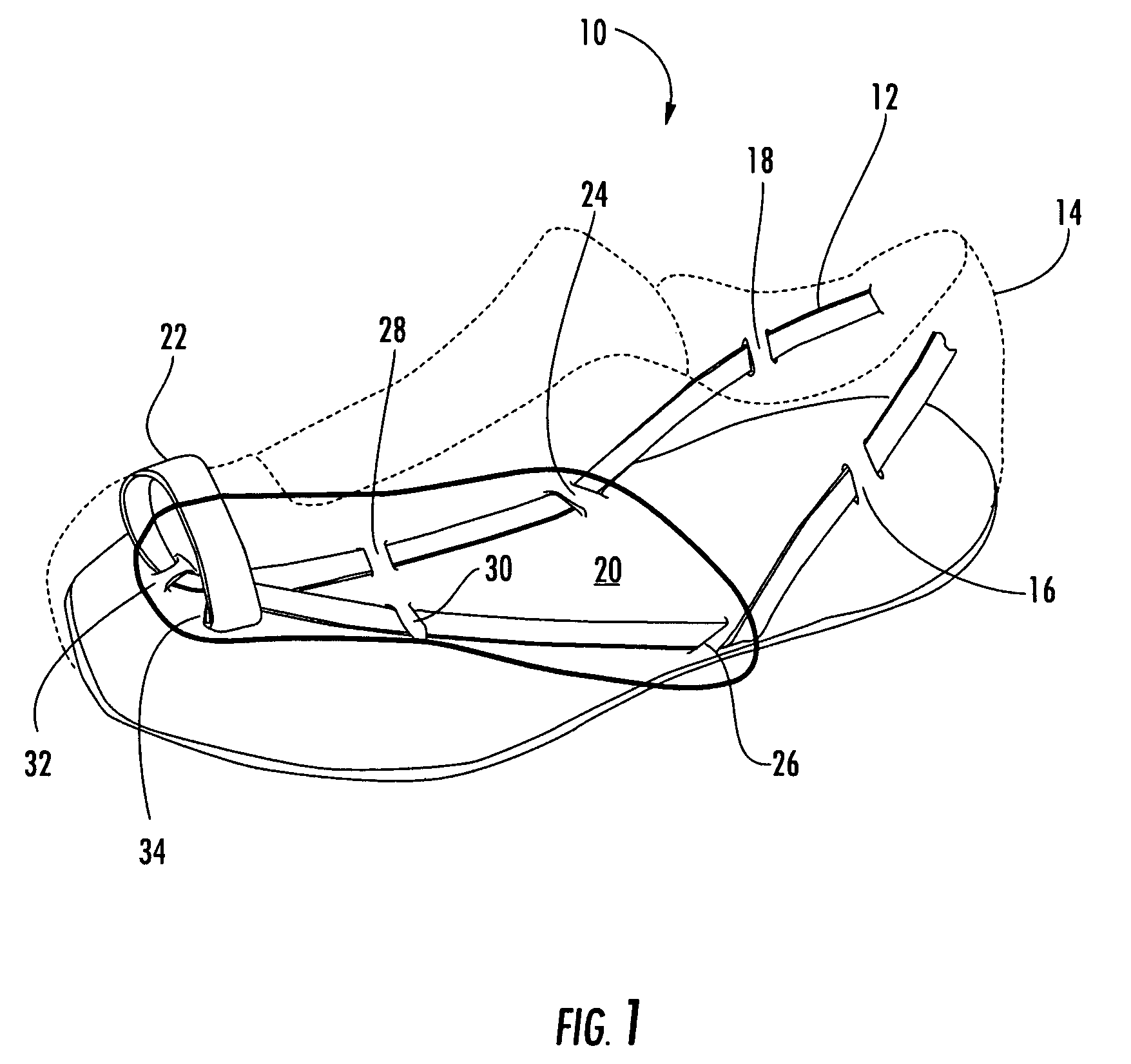

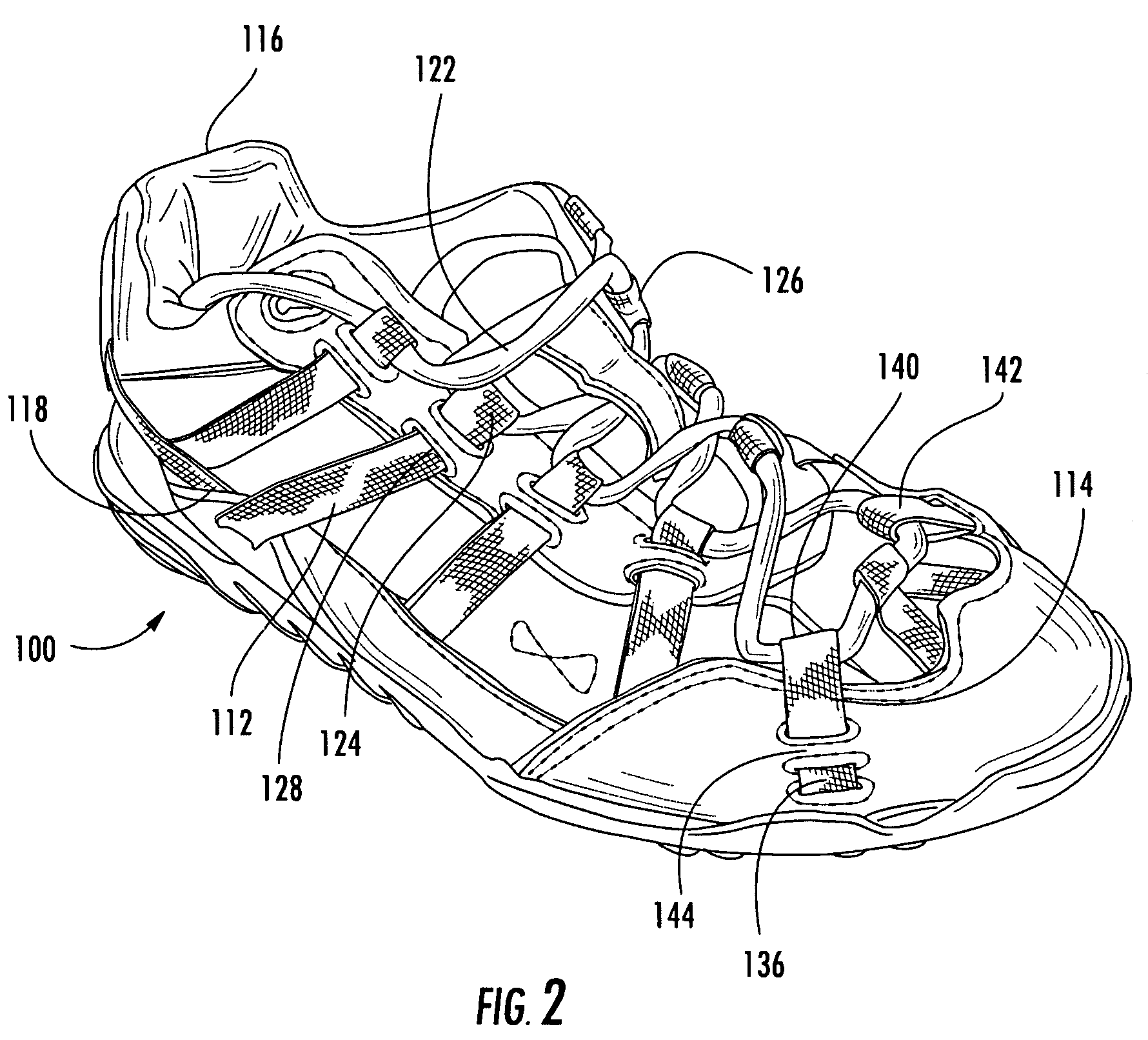

Footwear having an interactive strapping system

The first illustrative embodiment includes a lace or strap which runs behind the heel down the sides of the foot, under the sole of the foot, crosses to opposite sides of the foot, comes up over the toes ending in a cinch. Loops and slots are provided in the shoe to accommodate the additional strap. The second illustrative embodiment includes a heel strap which runs behind the heel, down the sides of the foot where it engages a loop near the bottom of the foot and loops over to the top of the foot where it engages opposite sides of a conventional lace. Tightening of the conventional lace causes a tightening of this heel strap. The second embodiment also includes a toe strap which is attached to opposite sides of the sole, crosses over the sole to opposite sides of the toes, loops over the toes and engages the bottom of a conventional lace. Tightening of the conventional lace causes a tightening of the toe strap.

Owner:NFINITY IP

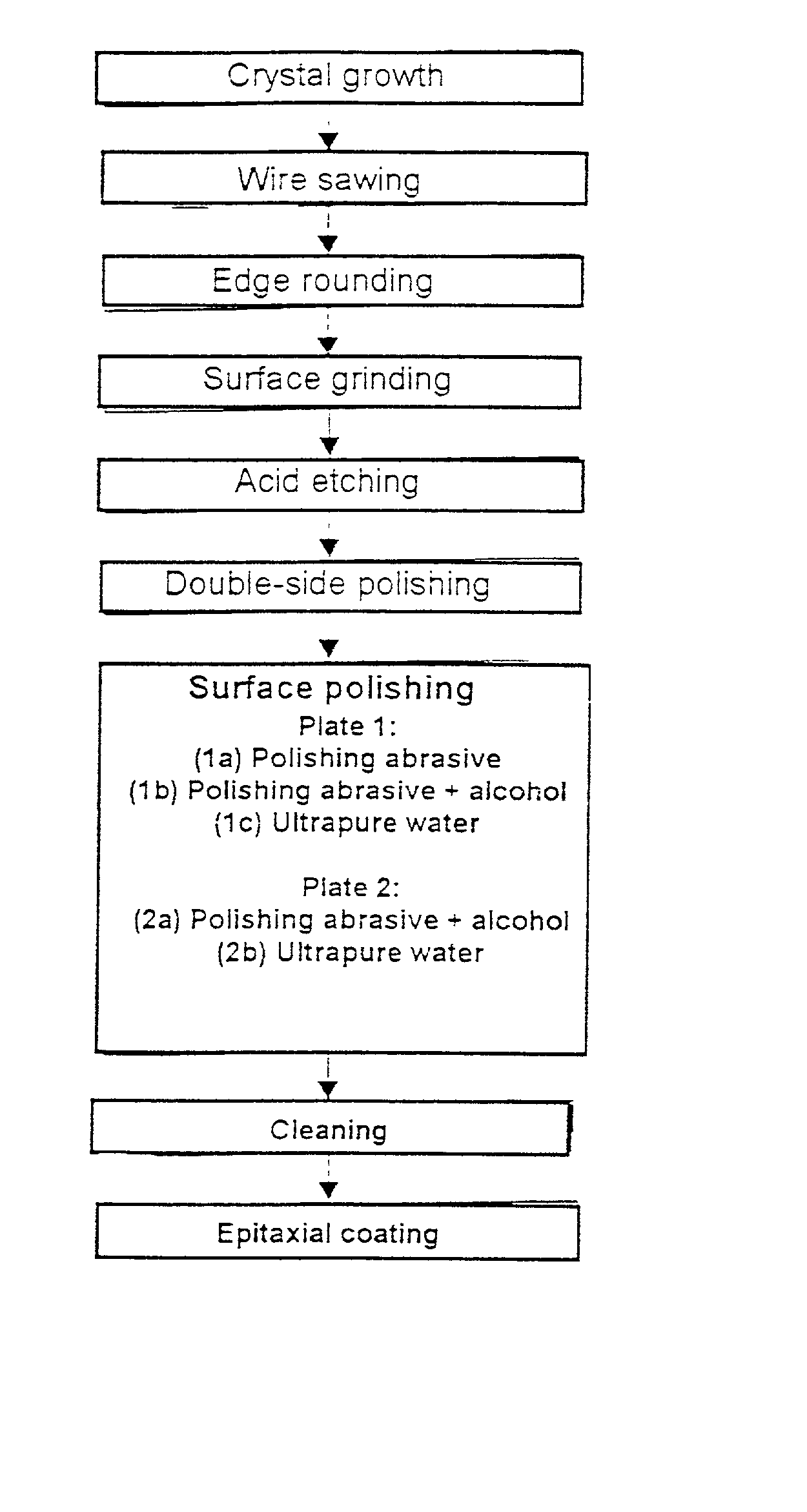

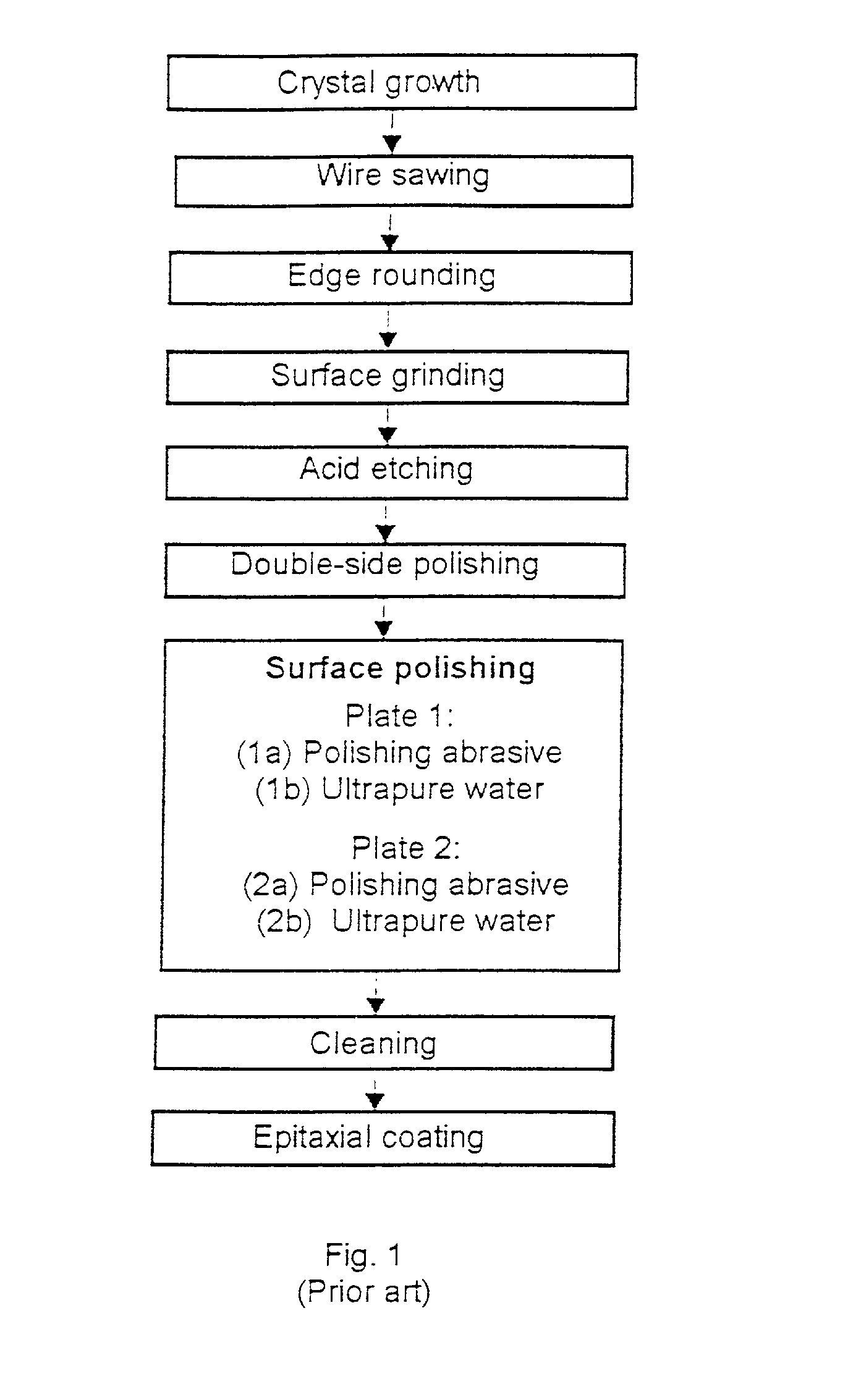

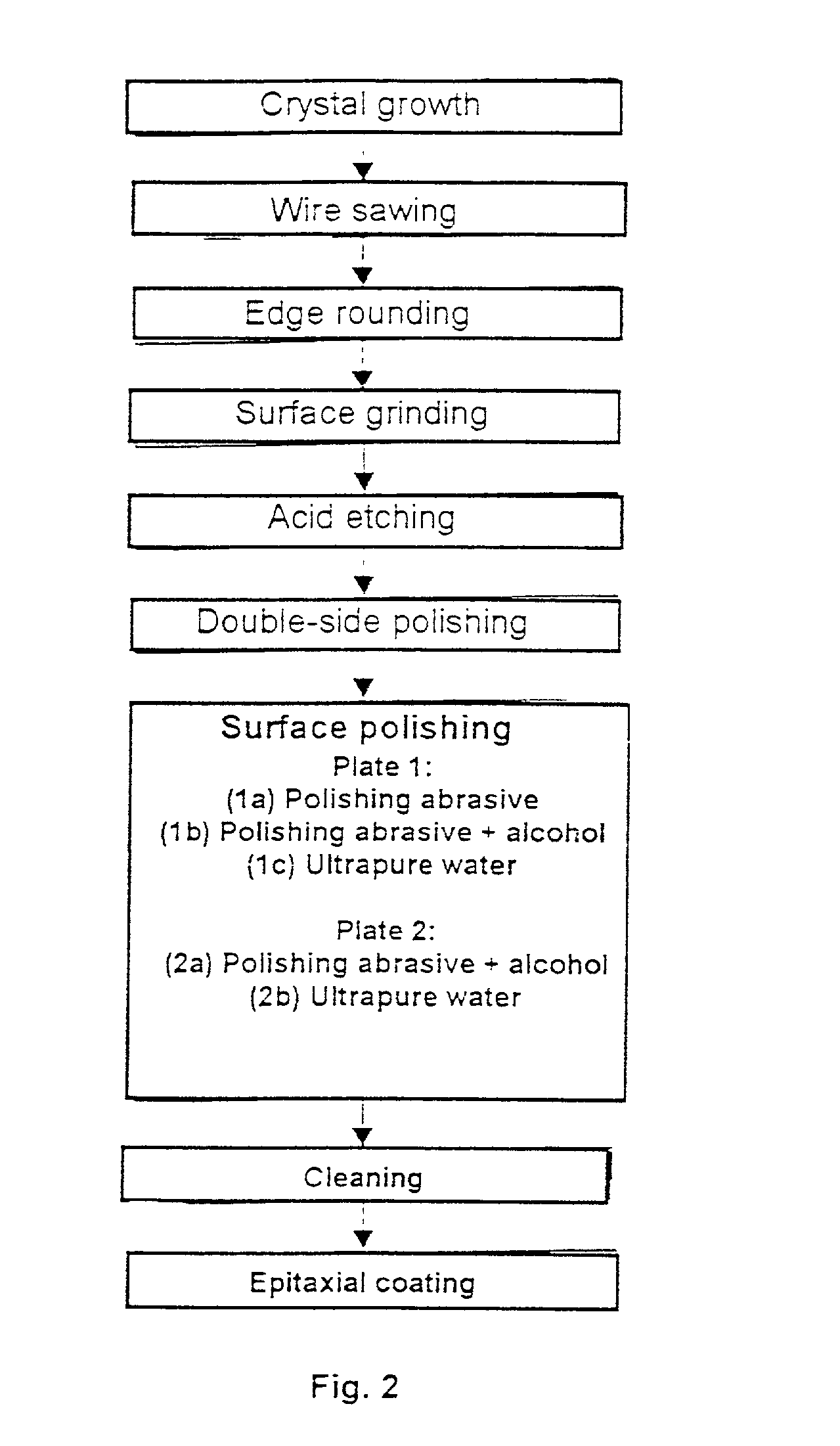

Process for the surface polishing of silicon wafers

InactiveUS20020077039A1High yieldLow costPigmenting treatmentPolishing machinesUltrapure waterAlcohol

A process for the surface polishing of a silicon wafer, includes the successive polishing of the silicon wafer on at least two different polishing plates covered with polishing cloth, with a continuous supply of alkaline polishing abrasive with SiO2 constituents, an amount of silicon removed during the polishing on a first polishing plate being significantly higher than on a second polishing plate, with the overall amount of silicon removed not exceeding 1.5 mum. A polishing abrasive (1a), then a mixture of a polishing abrasive (1b) and at least one alcohol, and finally ultrapure water (1c) are added to the first polishing plate, and a mixture of a polishing abrasive (2a) and at least one alcohol and then ultrapure water (2b) are added to the second plate.

Owner:SILTRONIC AG

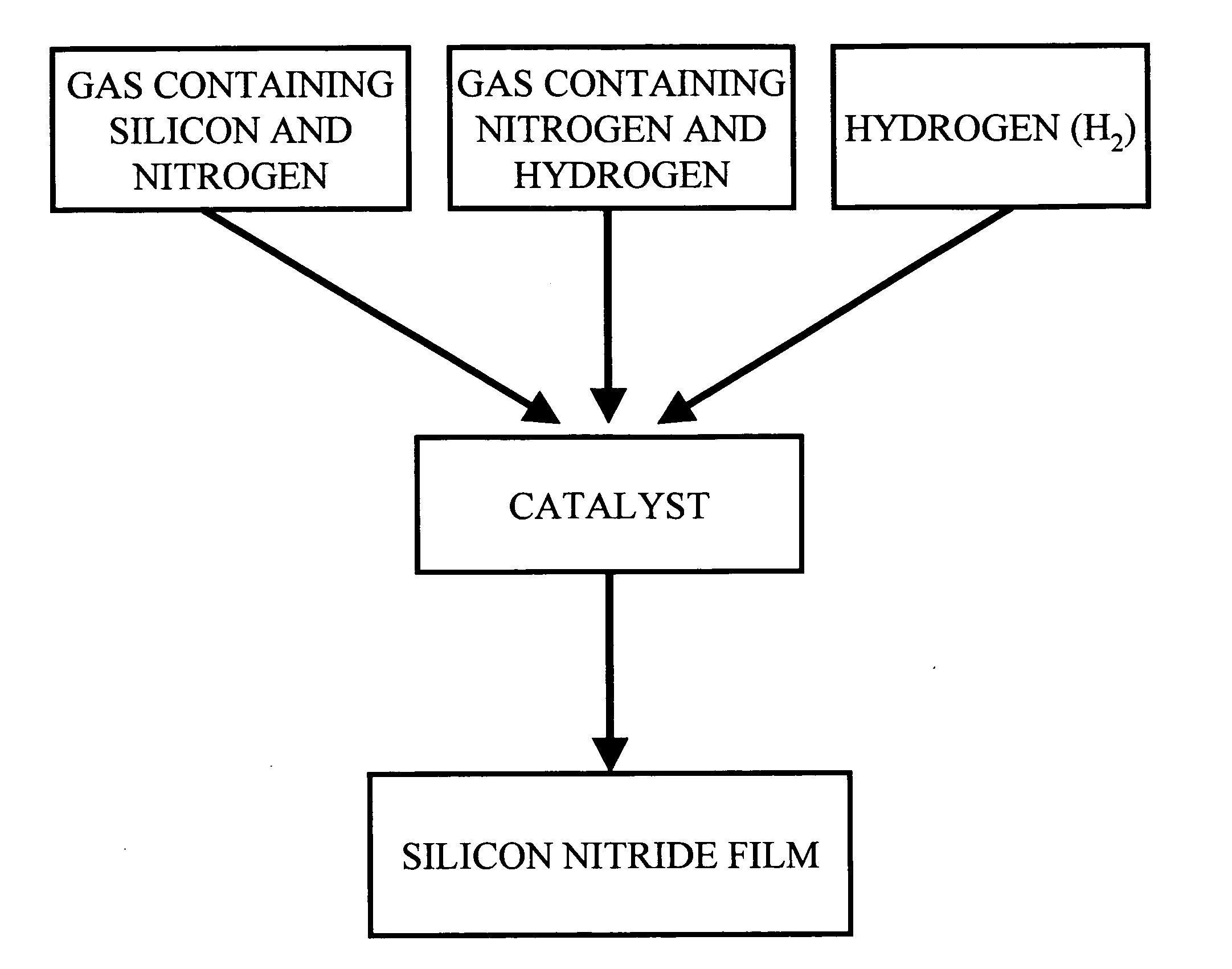

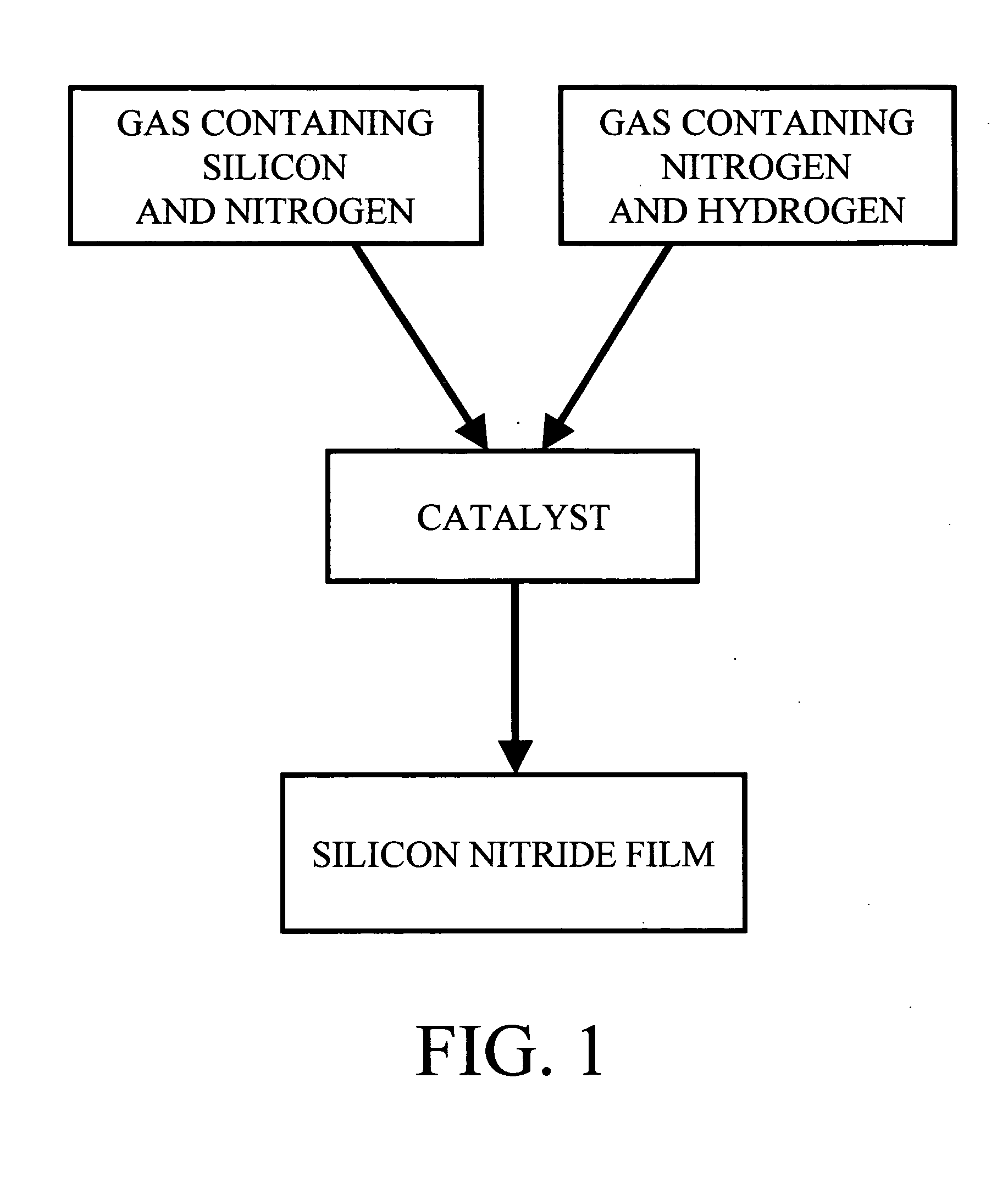

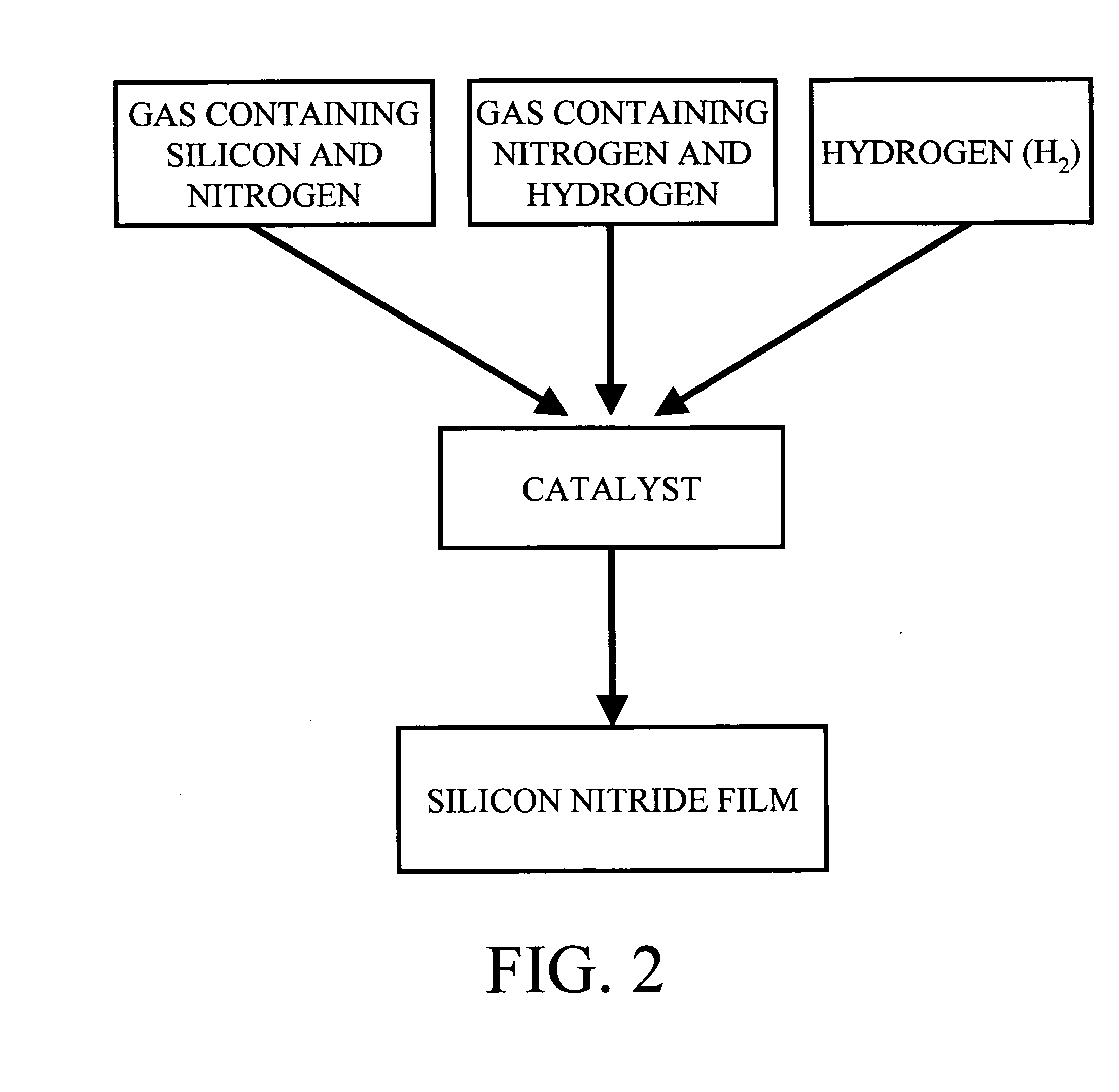

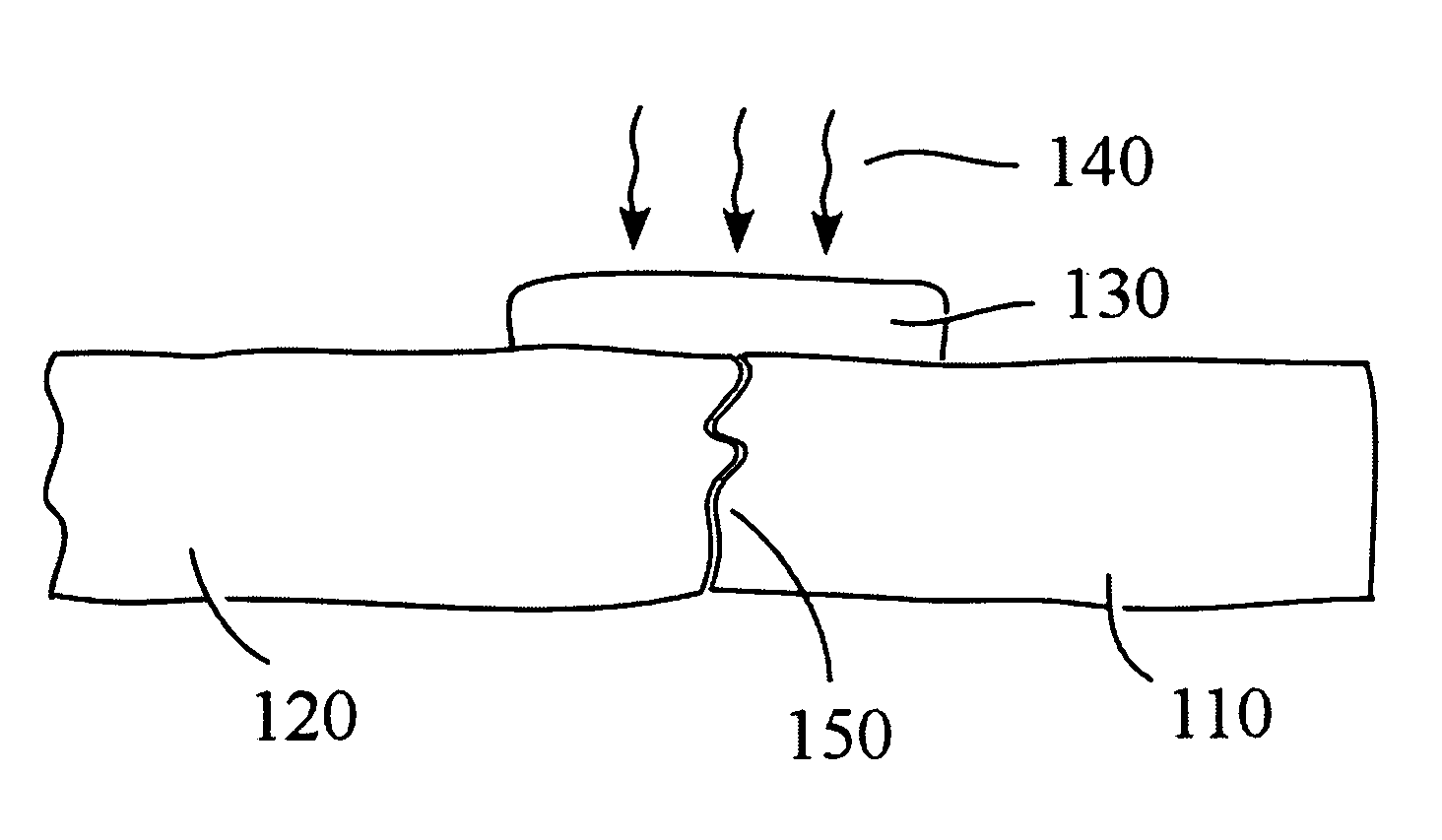

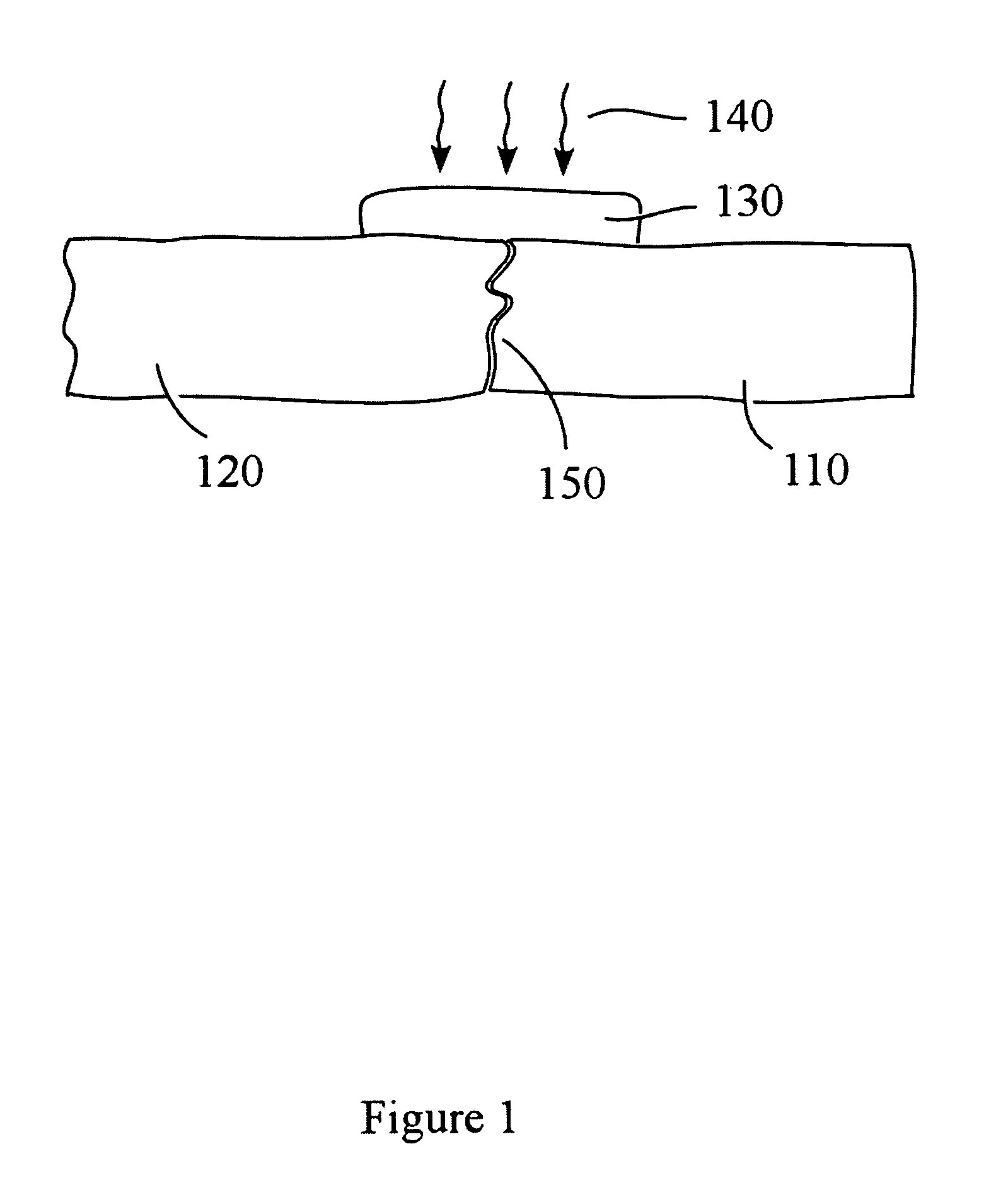

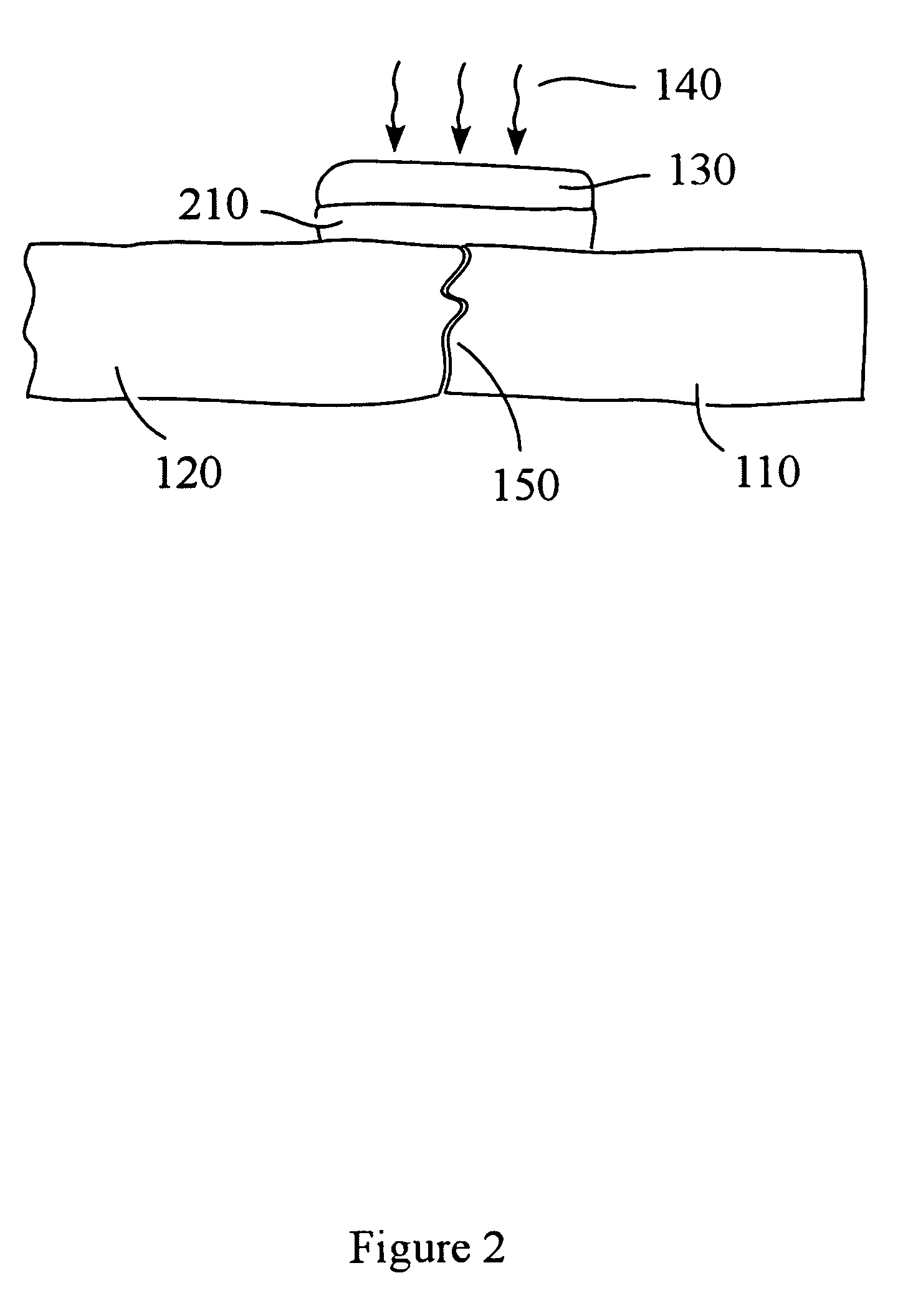

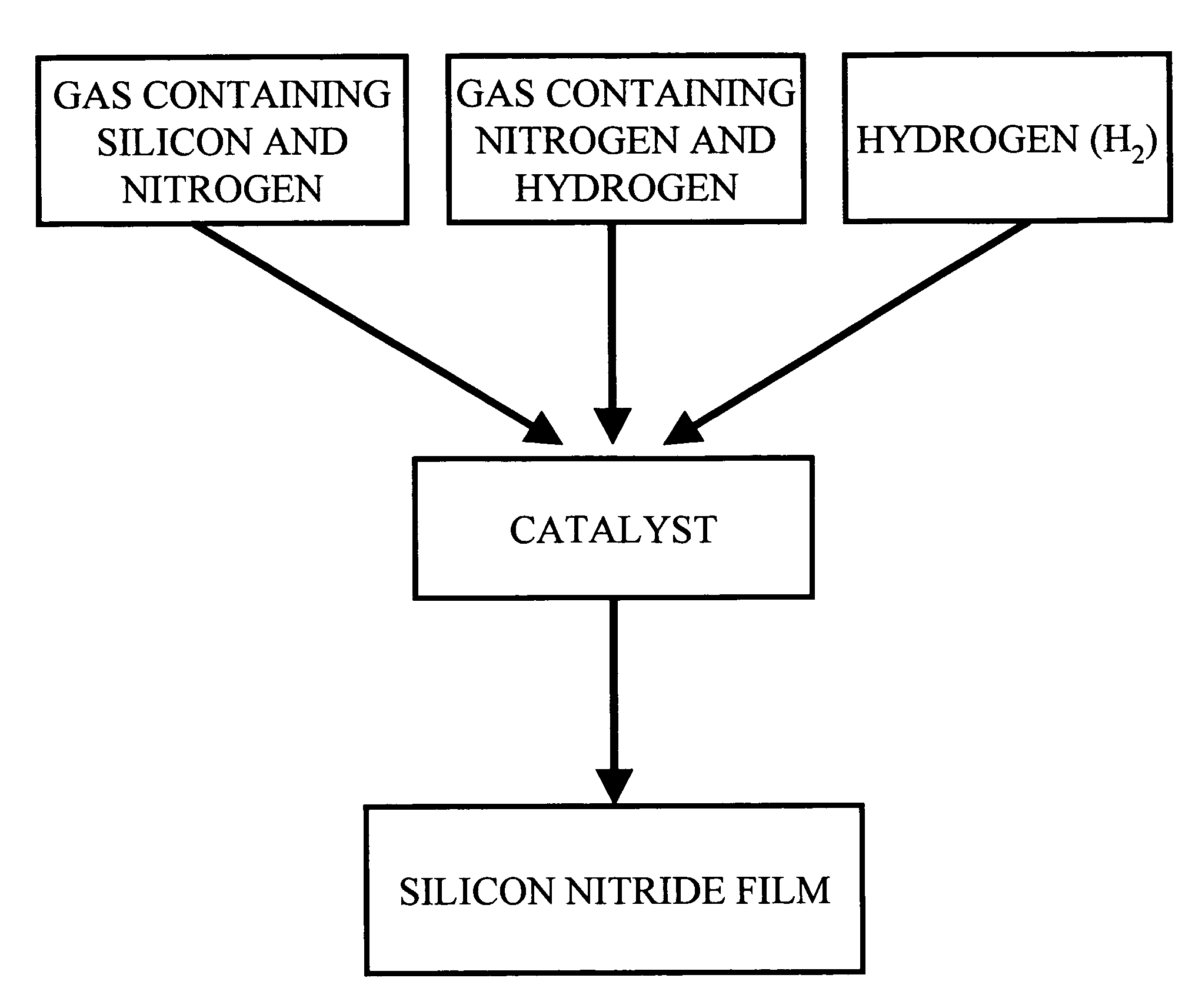

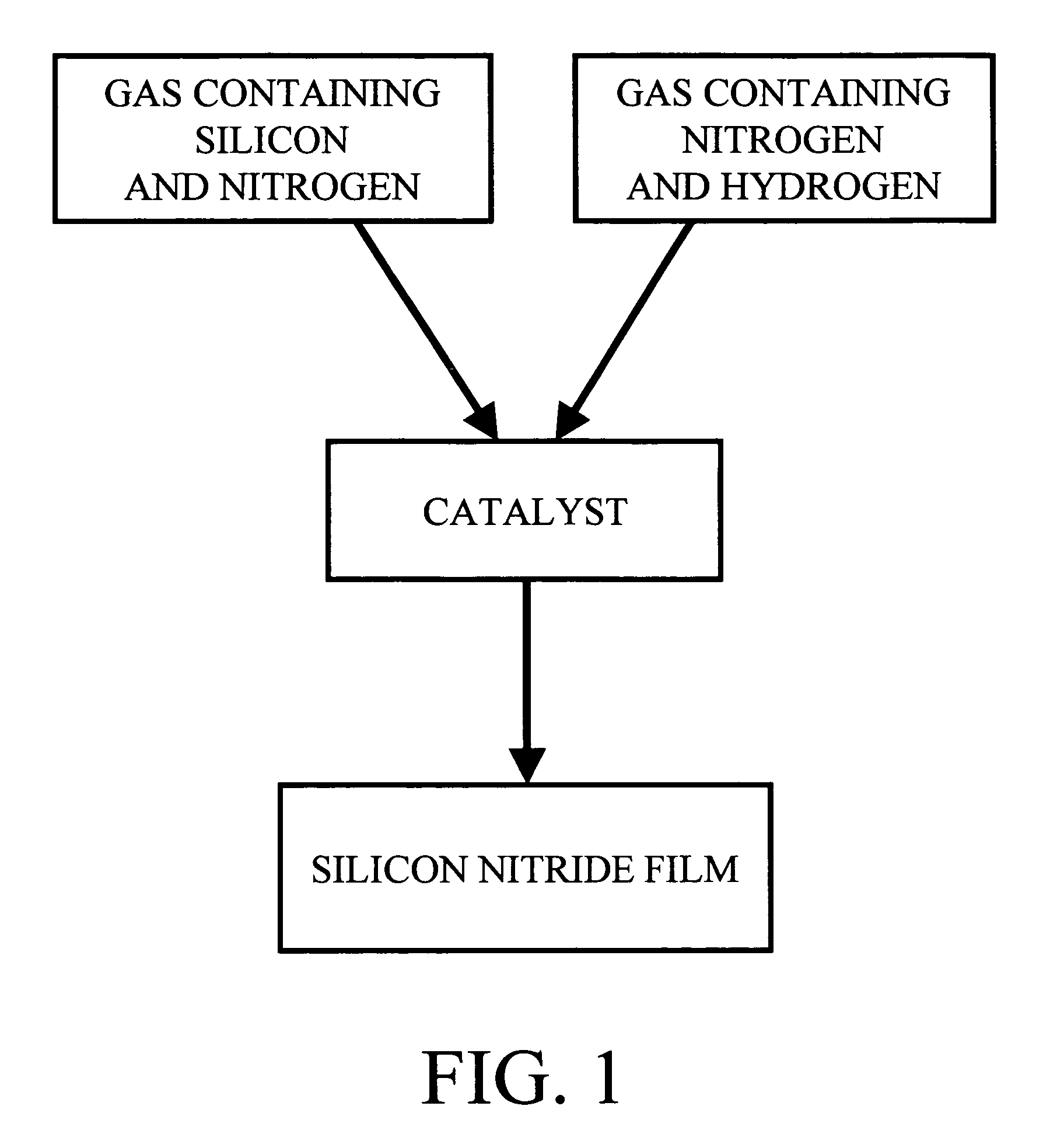

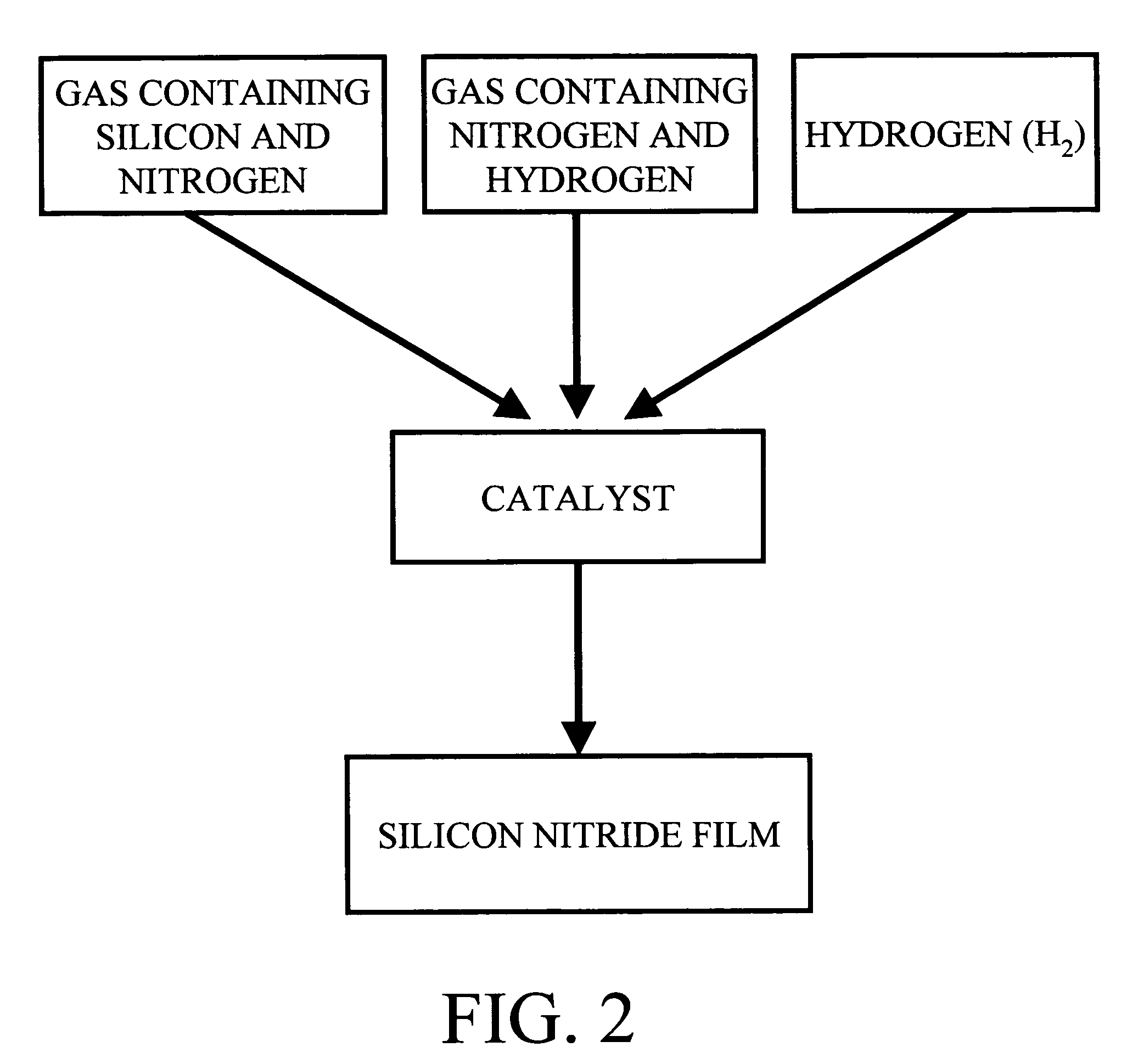

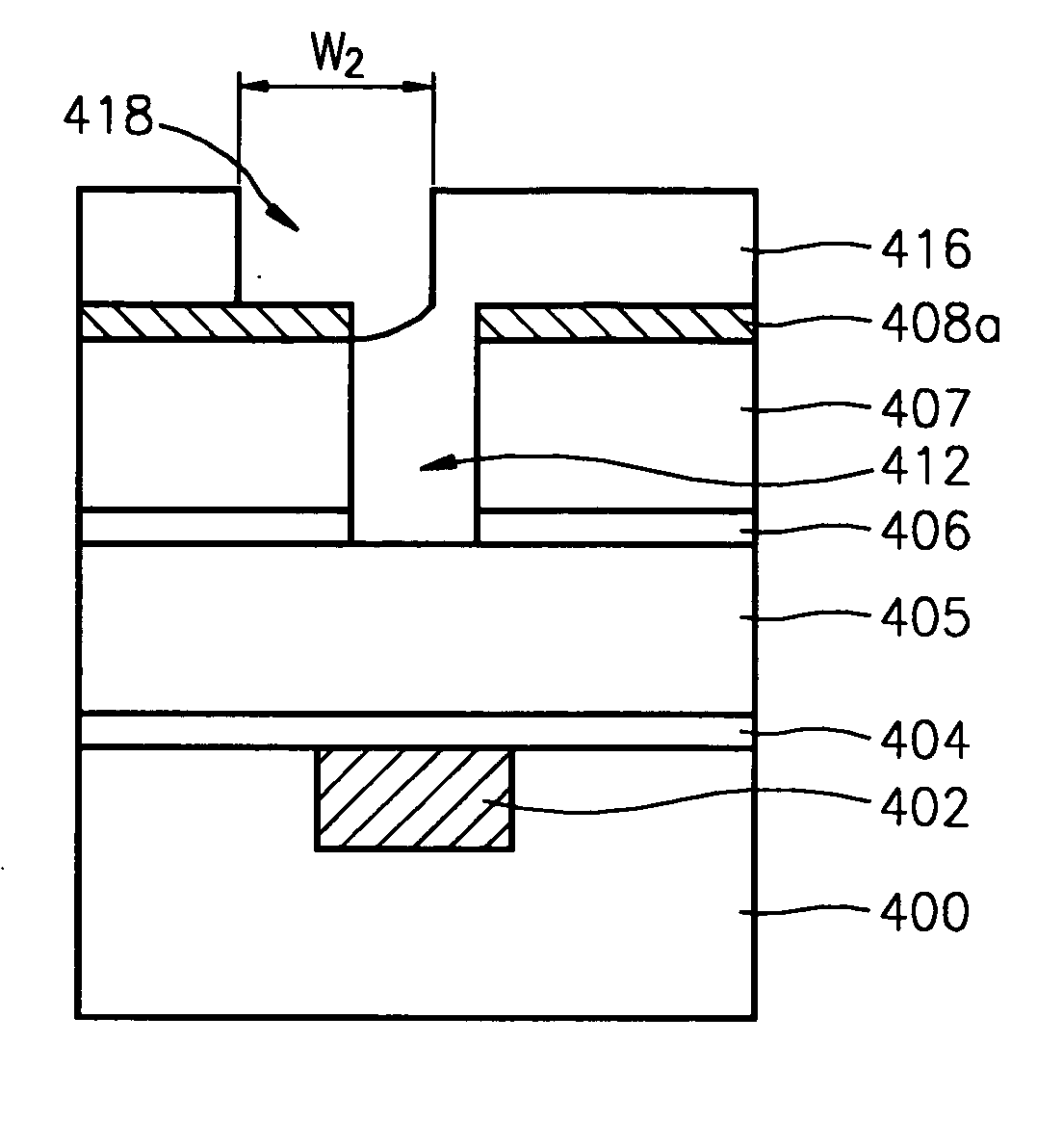

Method of forming silicon nitride film and method of manufacturing semiconductor device

ActiveUS20050196977A1Good step coverageIdeal balanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingInsulation layerHydrogen

A method of forming a silicon nitride film comprises: forming a silicon nitride film by applying first gas containing silicon and nitrogen and second gas containing nitrogen and hydrogen to catalyst heated in a reduced pressure atmosphere. A method of manufacturing a semiconductor device comprising the steps of: forming a silicon nitride film by the method as claimed in claim 1 on a substrate having the semiconductor layer, a gate insulation film selectively provided on a principal surface of the semiconductor layer, and a gate electrode provided on the gate insulation film; and removing the silicon nitride film on the semiconductor layer and the gate electrode and leaving a sidewall comprising the silicon nitride film on a side surface of the gate insulation film and the gate electrode by etching the silicon nitride film in a direction generally normal to the principal surface of the semiconductor layer. A method of manufacturing a semiconductor device comprising the steps of: forming a silicon nitride film by the method as claimed in claim 1 on a substrate including a semiconductor layer; forming an interlayer insulation layer on the silicon nitride film; forming a layer having an opening on the interlayer insulation layer; and etching the interlayer insulation layer via the opening in a condition where an etching rate for the silicon nitride film is greater than an etching rate for the interlayer insulation layer.

Owner:ULVAC INC

Composite tissue adhesive

InactiveUS6939364B1Precise temperature controlShorten treatment timeSurgical instrument detailsSurgical veterinaryThermal energyHigh concentration

Consistent with the present invention, tissue adhesive compositions and an associated laser exposure system are provided for bonding or sealing biological tissues. The compositions are comprised of chemically derivatized soluble collagen which is formulated to concentrations ranging from 300 mg / ml (30%) to 800 mg / ml (80%) collagen protein. In particular, Type I collagen, for example, is first prepared by extraction from bovine or porcine hide and purified. The collagen preparations are then chemically derivatized with sulfhydryl reagents to improve cohesive strength and with secondary derivatizing agents, such as carboxyl groups, to improve the adhesive strength of the solder to the tissue. The compositions are then formed into viscous solutions, gels or solid films, which when exposed to energy generated from an infrared laser, for example, undergo thermally induced phase transitions. Solid or semi-solid protein compositions become less viscous enabling the high concentration protein to penetrate the interstices of treated biological tissue or to fill voids in tissue. As thermal energy is released into the surrounding environment, the protein compositions again become solid or semi-solid, adhering to the treated tissue or tissue space.

Owner:CONVERSION ENERGY ENTERPRISES

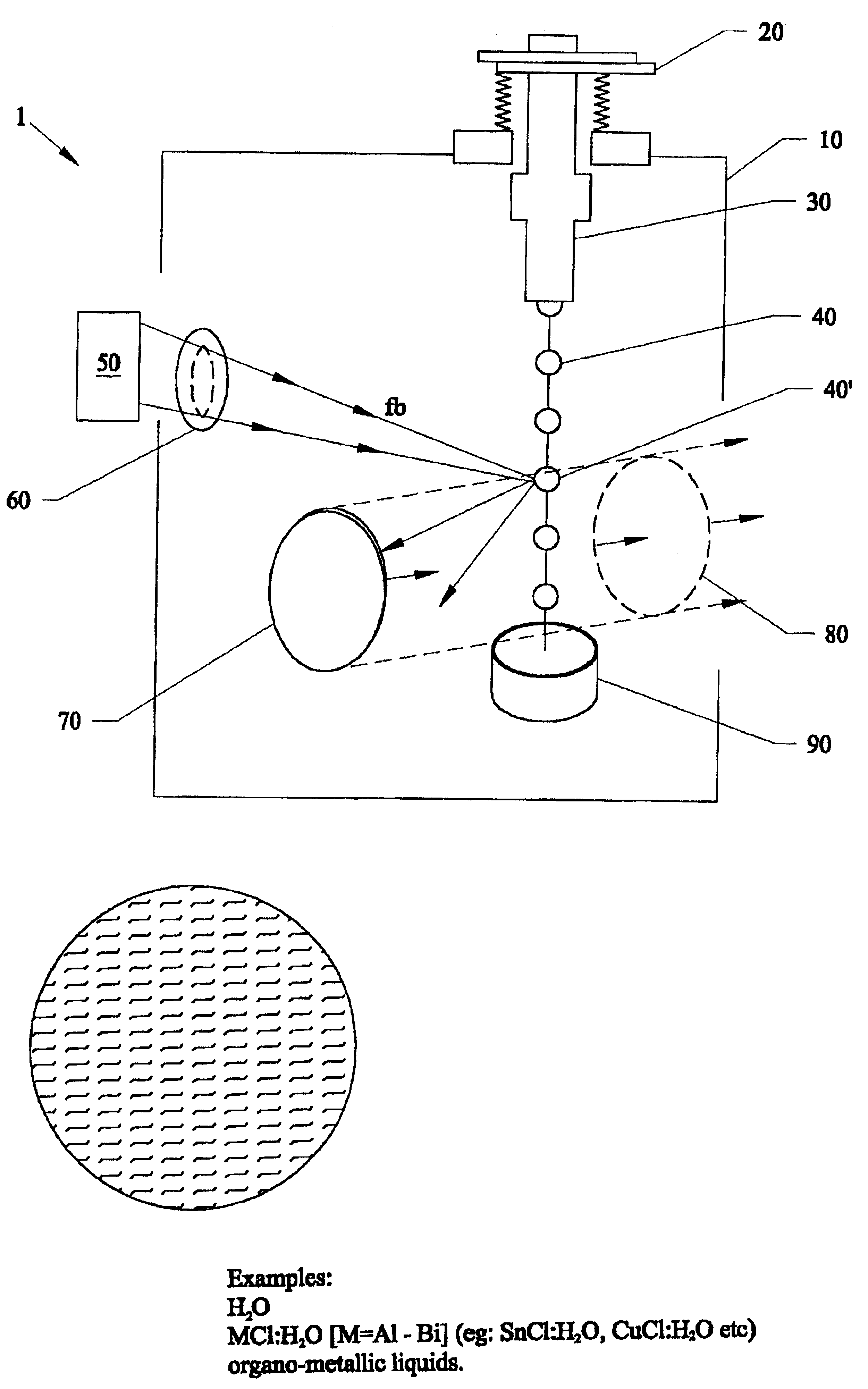

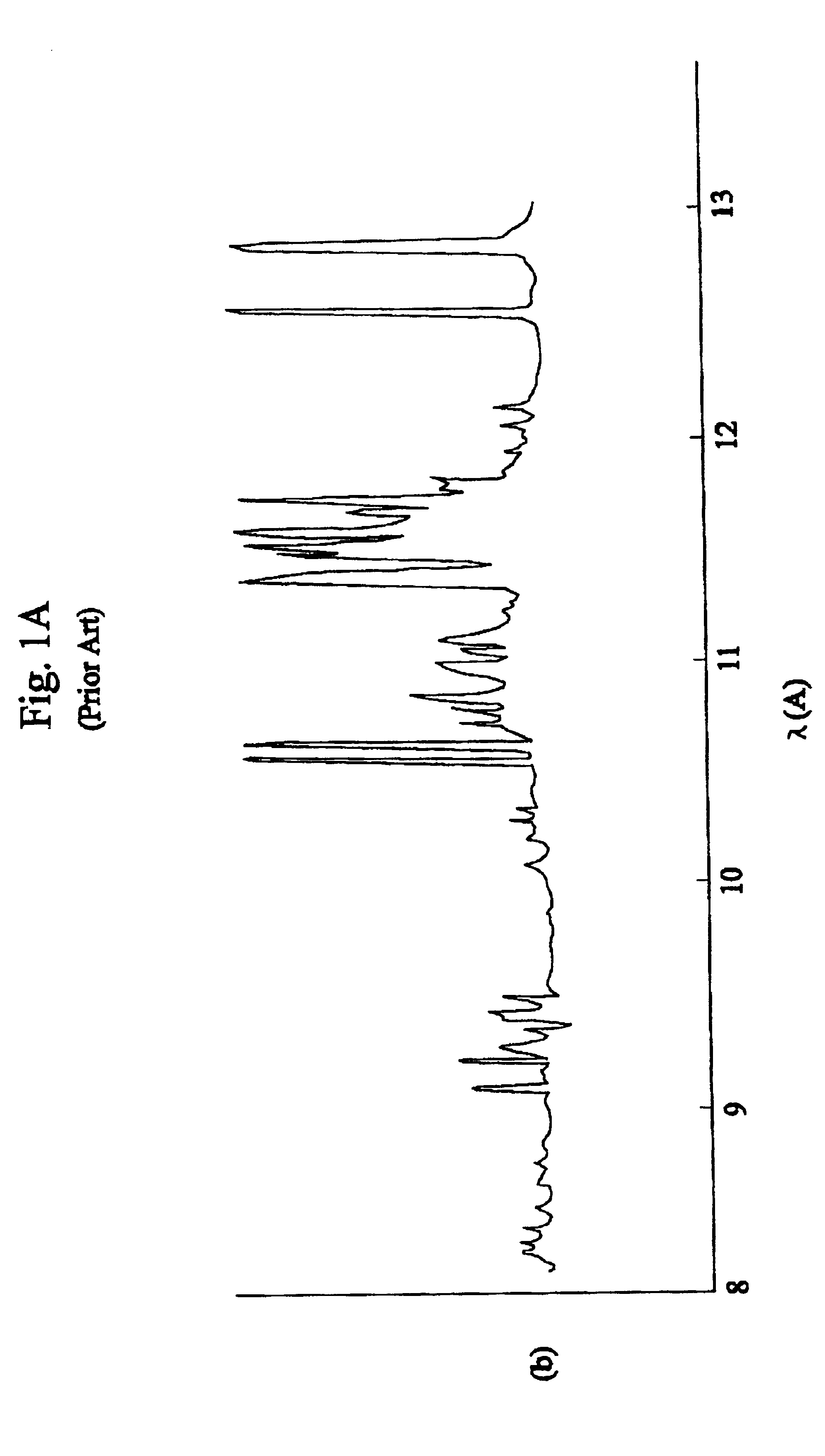

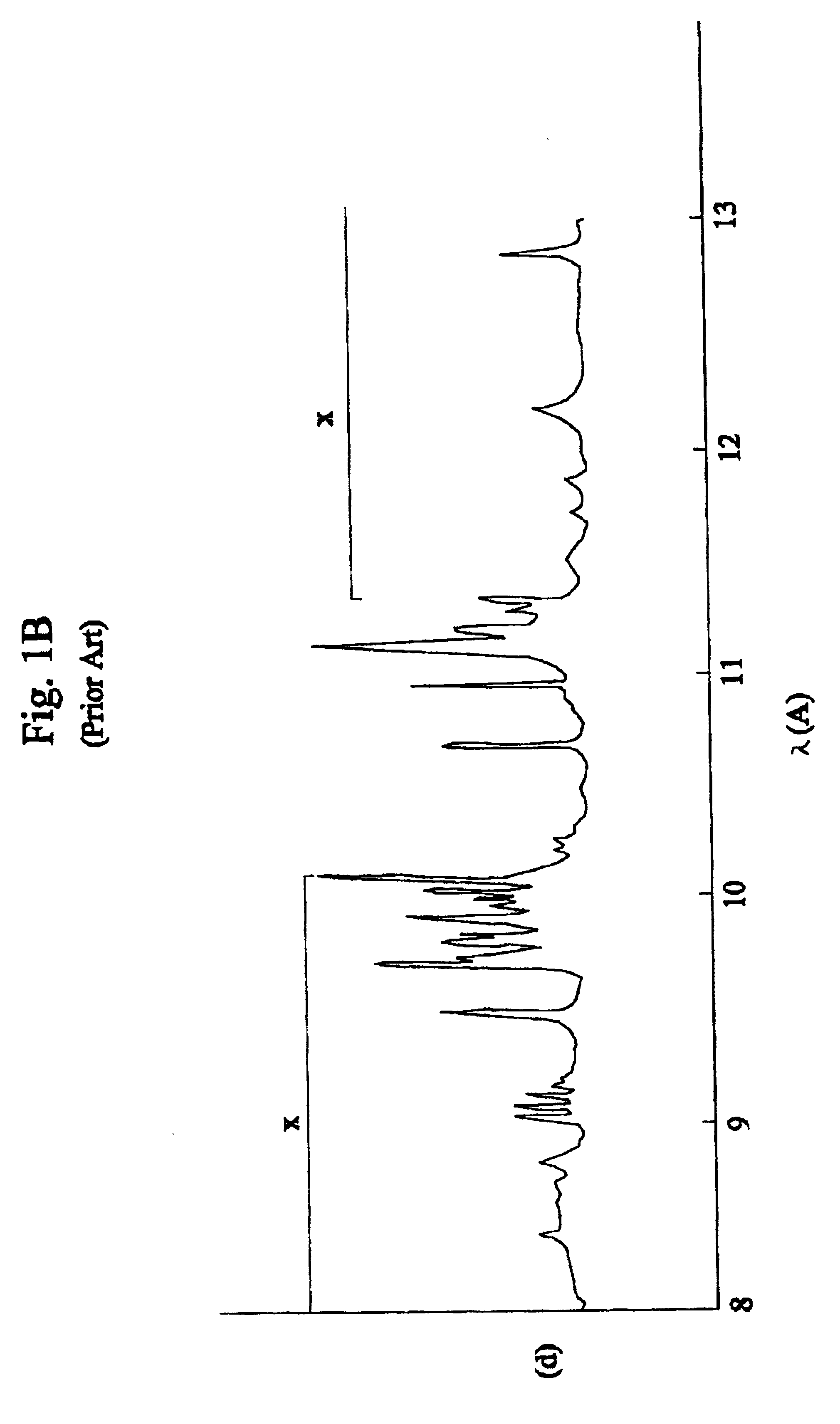

EUV, XUV, and X-ray wavelength sources created from laser plasma produced from liquid metal solutions, and nano-size particles in solutions

InactiveUS6865255B2Efficient and inexpensiveEliminate damageX-ray tube electrodesSemiconductor/solid-state device manufacturingHigh power lasersUltraviolet

Special liquid droplet targets that are irradiated by a high power laser and are plasmarized to form a point source EUV, XUV and x-ray source. Various types of liquid droplet targets include metallic solutions, and nano-sized particles in solutions having a melting temperature lower than the melting temperature of some or all of the constituent metals, used a laser point source target droplets. The solutions have no damaging debris and can produce plasma emissions in the X-rays, XUV, and EUV(extreme ultra violet) spectral ranges of approximately 0.1 nm to approximately 100 nm, approximately 11.7 nm and 13 nm, approximately 0.5 nm to approximately 1.5 nm, and approximately 2.3 nm to approximately 4.5 nm. The second type of target consists of various types of liquids which contain as a miscible fluid various nano-size particles of different types of metals and non-metal materials.

Owner:CENT FLORIDA UNIV OF

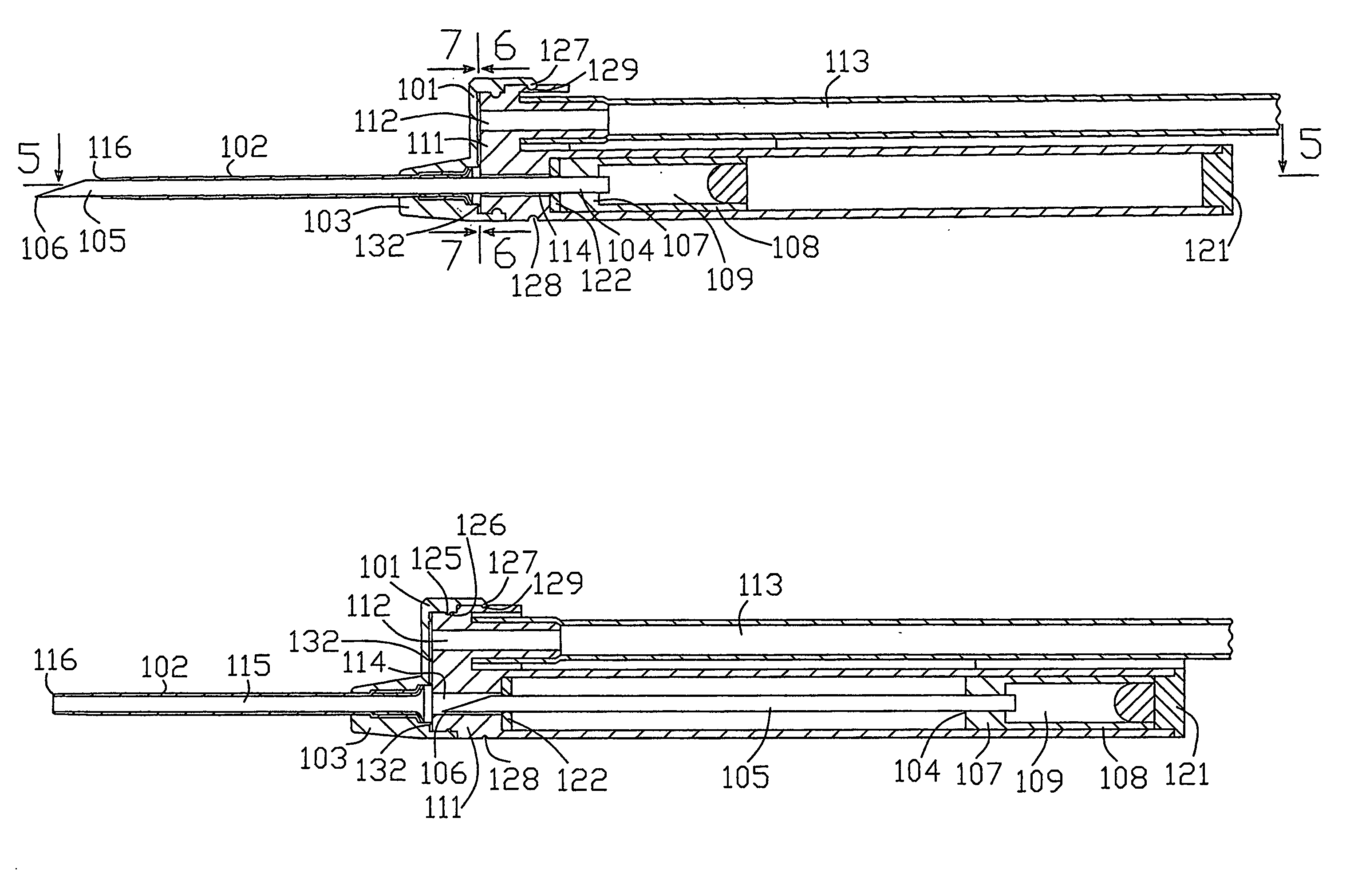

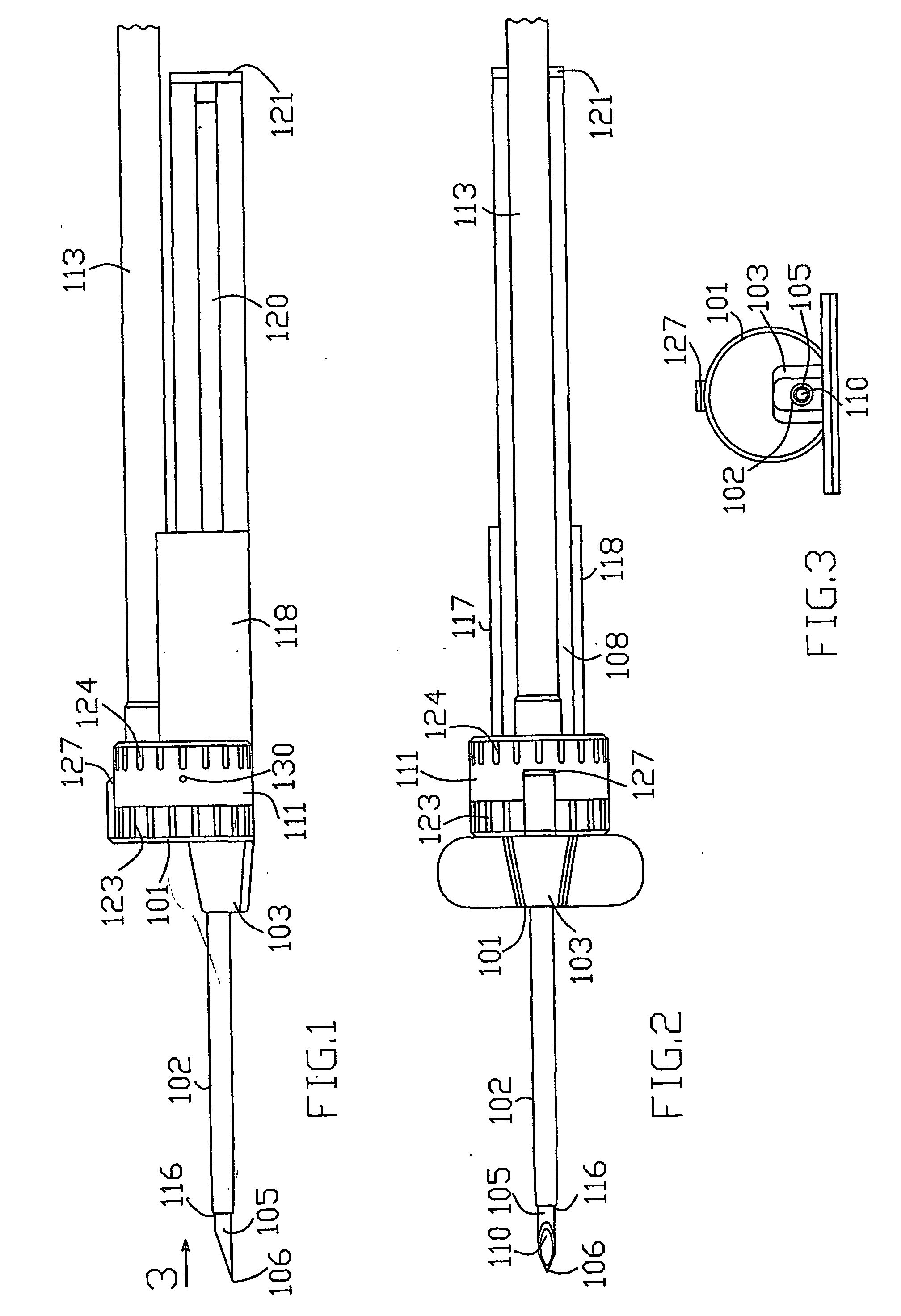

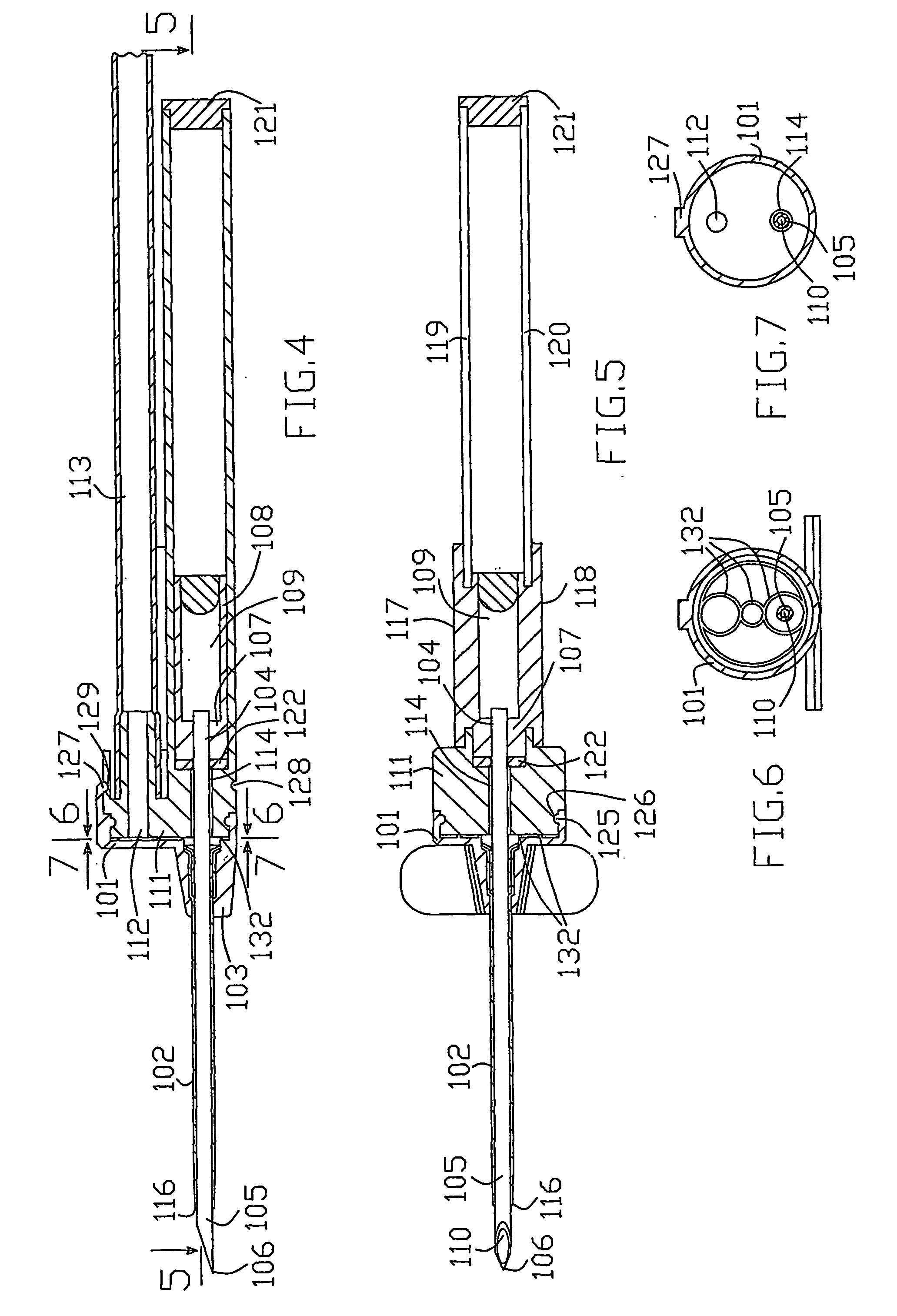

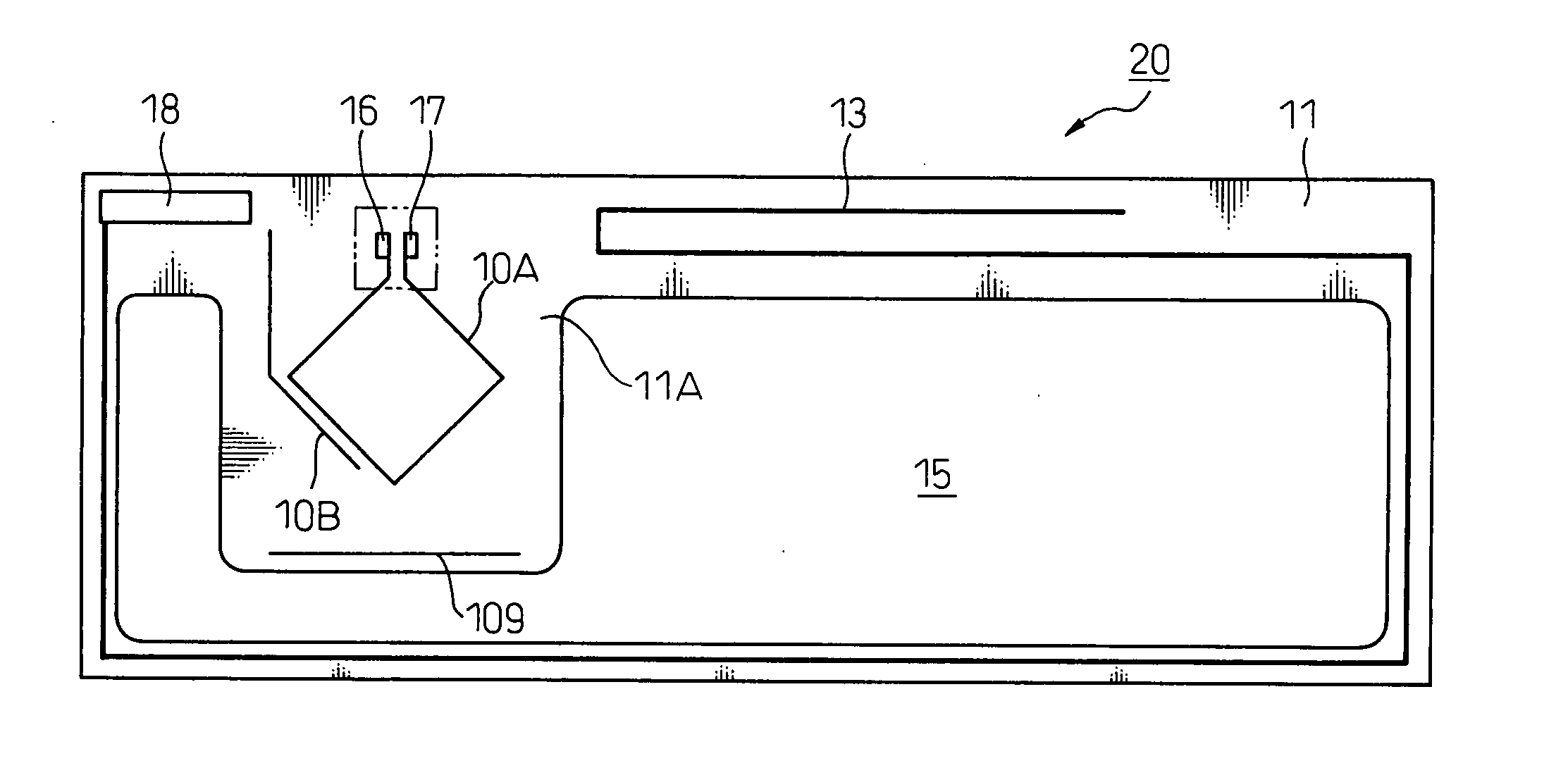

Safety catheter device

InactiveUS20060155244A1Elimination of blood leakageImprove reliabilityGuide needlesMedical devicesHemodialysisVein

A safety catheter device for hemodialysis and donor collection (see FIG. 9) comprises a catheter unit (101), a needle (105) guided by a needle port (114) into the catheter unit to introduce it into patient's vein, an indication channel for blood supply into an indication cavity (109) during catheter emplacement, a blood stream channel for blood supply to hemodialysis or collection set through a blood stream port (112). The minimal cross-sectional area of the blood stream channel is substantially more than one of the indication channel. Forming the blood stream channel is accomplished by retracting the needle and, in version embodiment, by rotating a port unit (111) including the needle and blood stream ports relative to the catheter unit. There are means preventing blood leakage and personnel infecting.

Owner:POPOV

Method of forming silicon nitride film and method of manufacturing semiconductor device

ActiveUS7510984B2Good step coverageIdeal balanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHydrogenInsulation layer

Owner:ULVAC INC

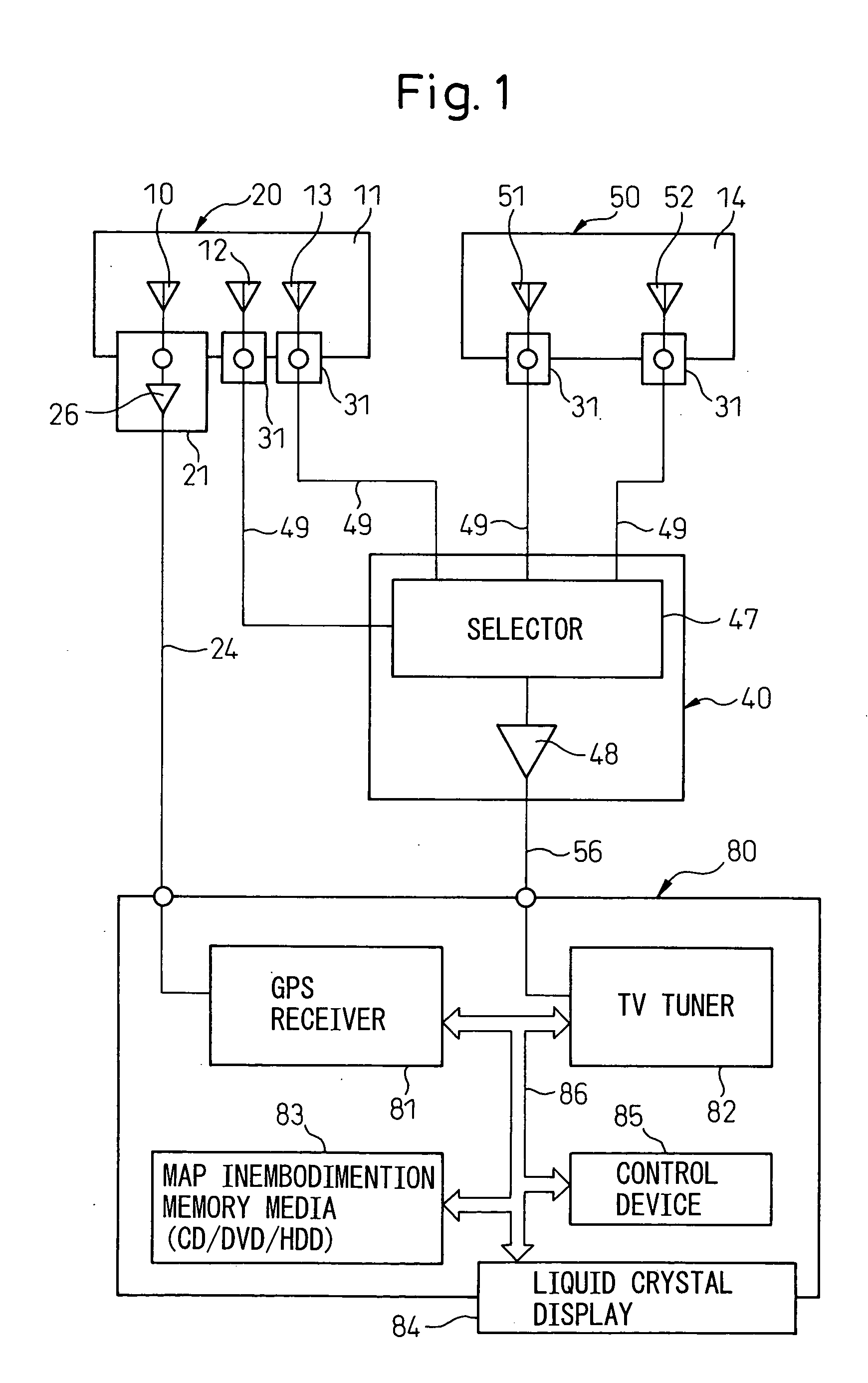

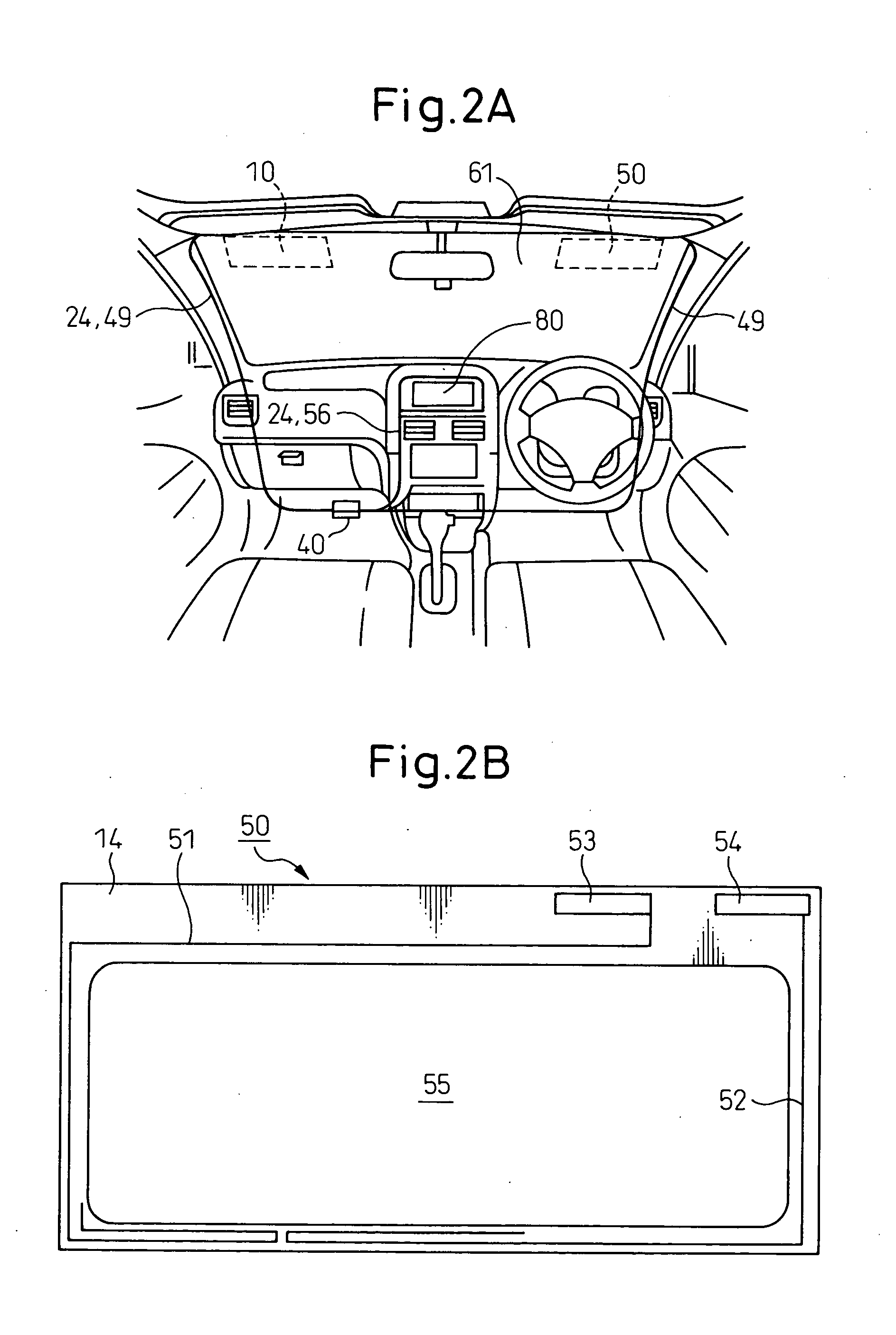

Circular polarization antenna and composite antenna including this antenna

InactiveUS20050052334A1Simple power feed structureReduce spacingResonant long antennasAntenna supports/mountingsElectrical conductorCircularly polarized antenna

When configuring a film antenna for receiving a circular polarized wave, at least one loop antenna is formed on a transparent plastic film and, at the same time, a non-powered element constituted by a wire-shaped conductor independent from the antenna conductor configuring the loop is arranged near this loop antenna. The non-powered element arranged on the side of the loop antenna is configured by a first part and a second part. The first part is made close to the loop antenna in a substantially parallel state. When a monopole antenna is used in place of the loop antenna, by combining this with a wire-shaped conductor orthogonal to this, it becomes possible to receive a circular polarized wave by a configuration providing a power transfer part between the two. It is also possible to configure a composite antenna by mounting another antenna on the transparent plastic film. This antenna can be used as an antenna of a navigation system.

Owner:FUJITSU GENERAL LTD

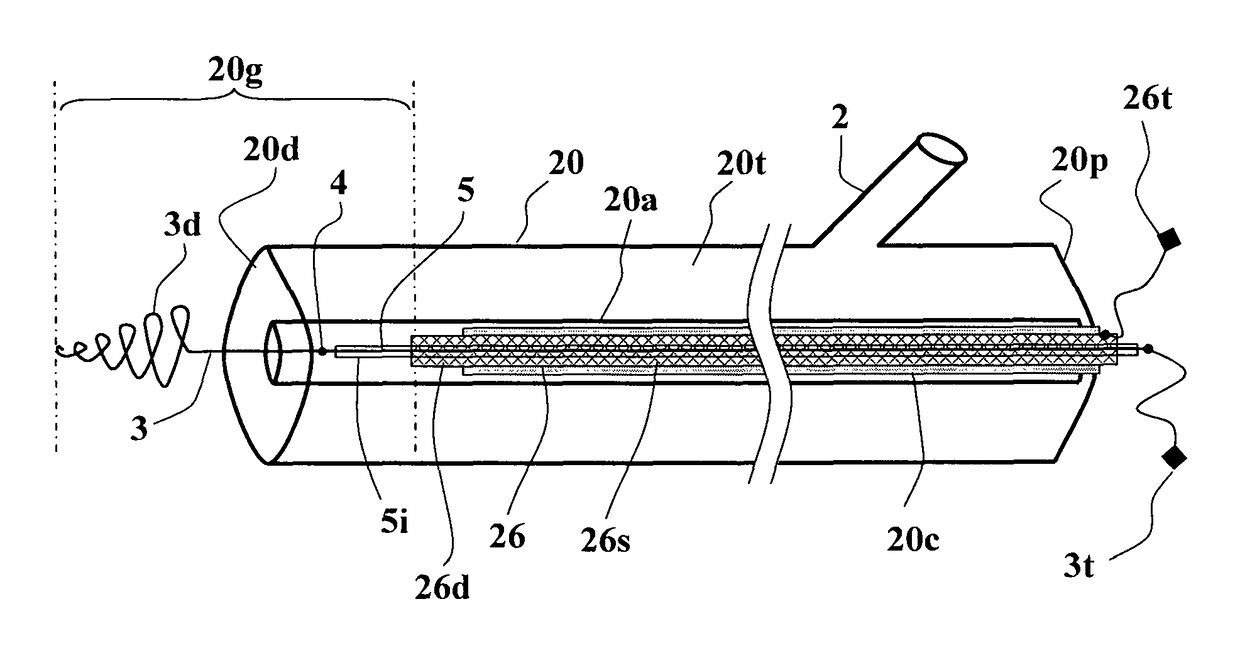

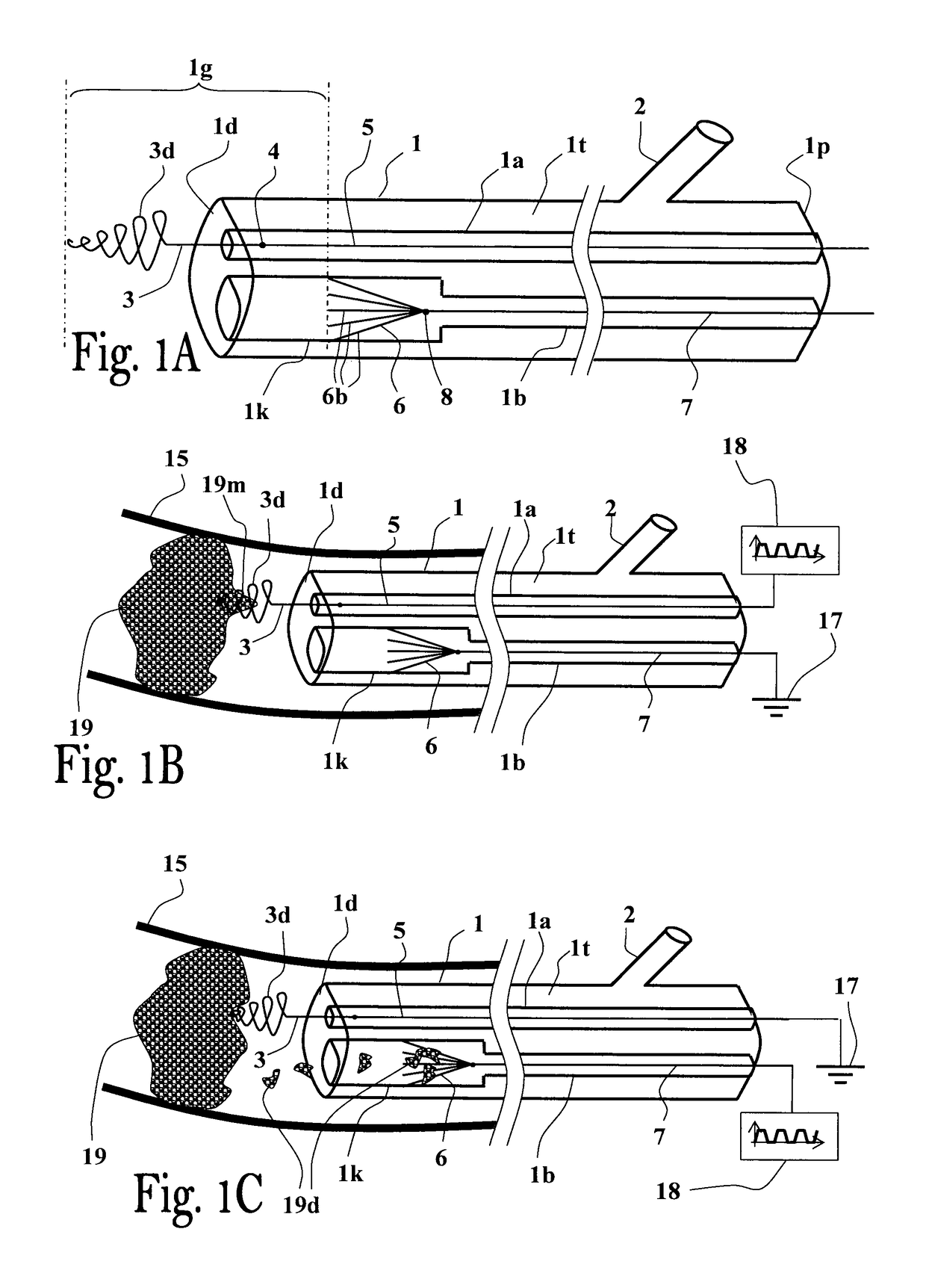

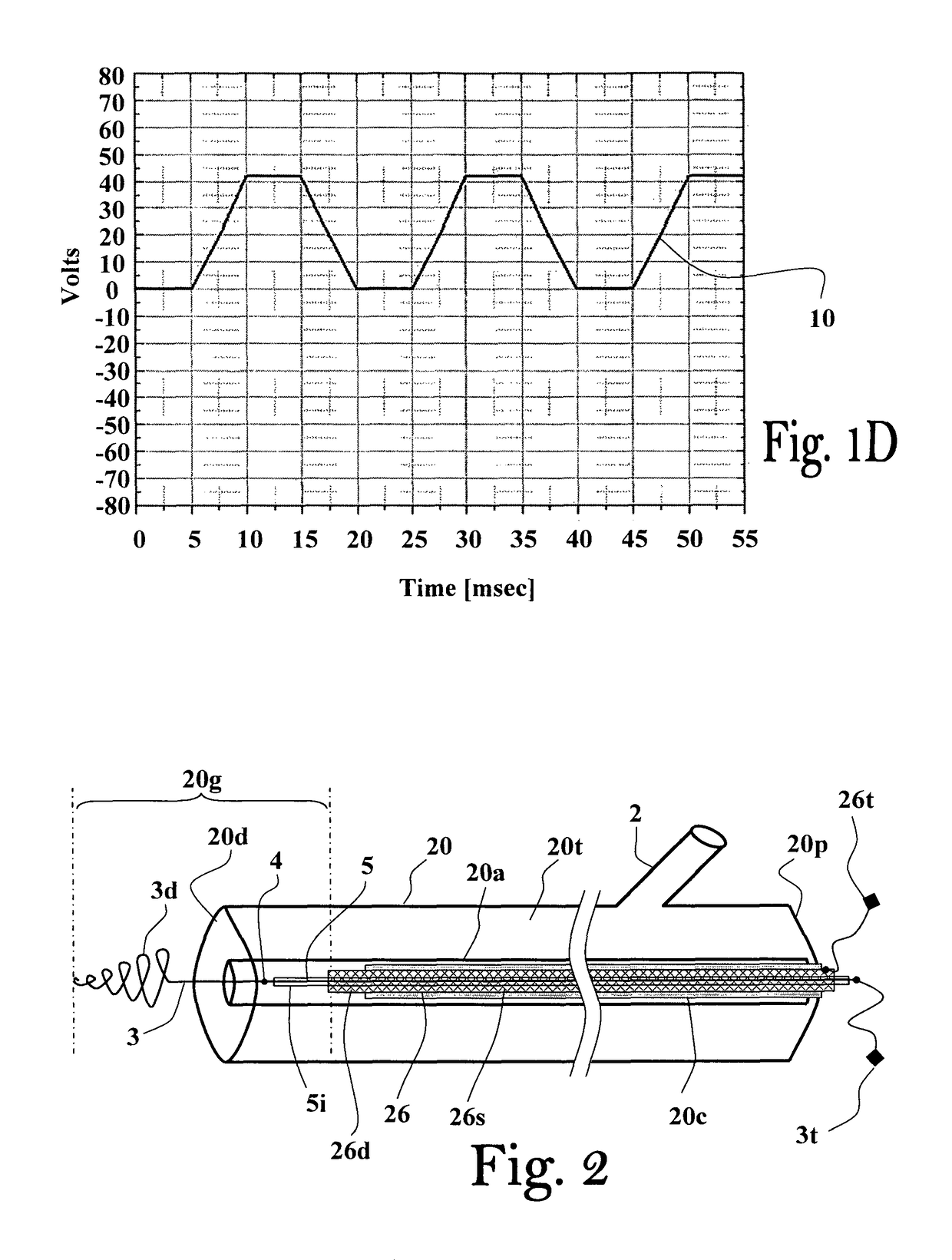

Method and apparatus for thrombus dissolution/thrombectomy by an electrode catheter device

Owner:MAGNETO THROMBECTOMY SOLUTIONS LTD

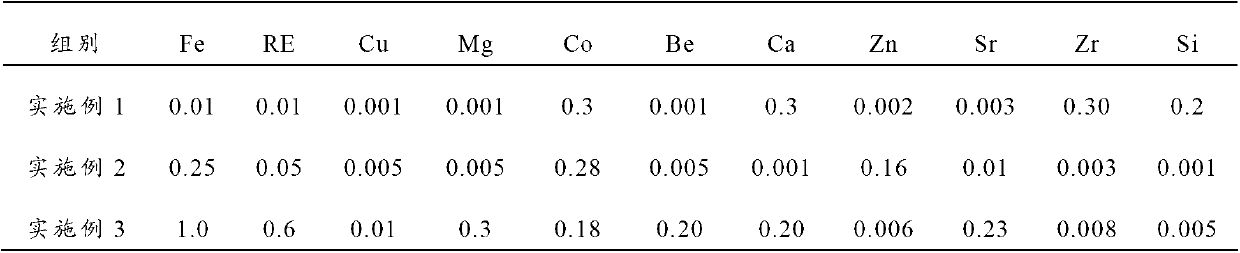

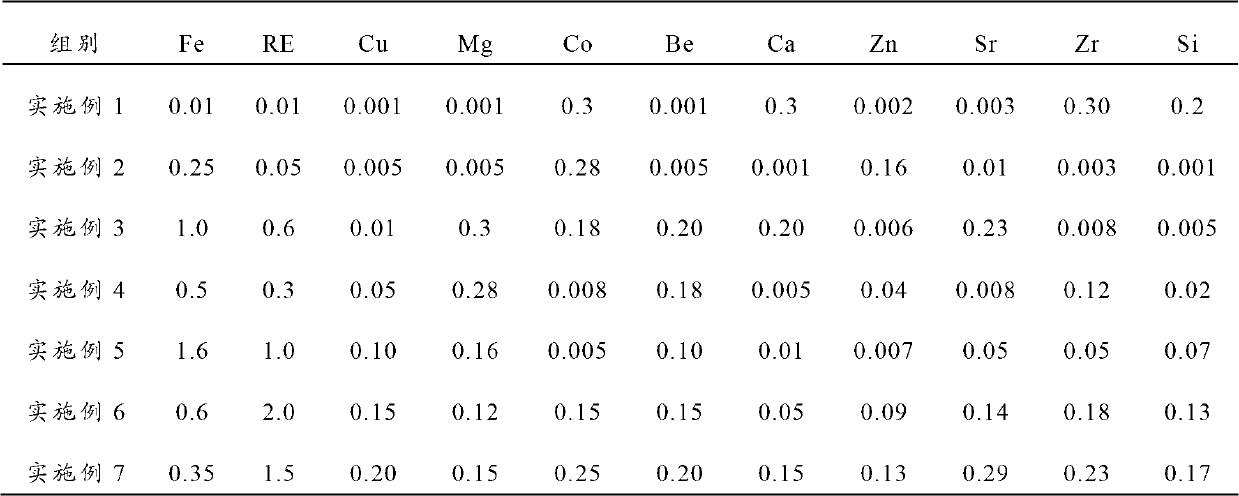

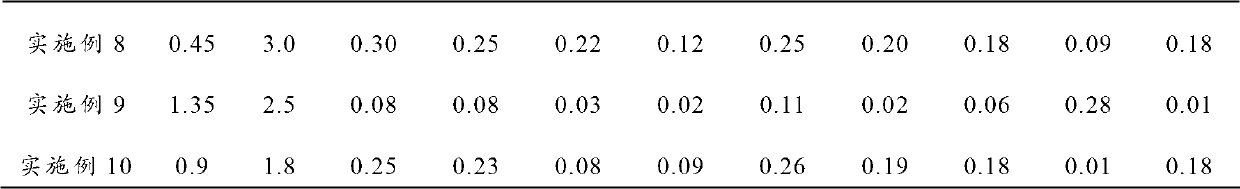

Al-Fe-C-RE aluminium alloy, preparation method thereof and power cable

ActiveCN103103387AEvenly heatedEliminate damagePower cablesMetal/alloy conductorsPower cableMetallurgy

The invention provides an Al-Fe-C-RE aluminium alloy and a preparation method thereof. The preparation method comprises the following steps of: a) casting an aluminium alloy cast ingot; b) homogenizing the aluminium alloy cast ingot and rolling the homogenized aluminium alloy cast ingot to obtain an aluminium alloy rod material; c) intermittently annealing the aluminium alloy rod material obtained in the step b); and d) aging the aluminium alloy rod material obtained in the step c), thus obtaining the aluminium alloy. The invention also provides a power cable. The aluminium alloy has better overall performances by selecting and controlling the added elements and adopting a reasonable preparation process.

Owner:ANHUI JOY SENSE CABLE

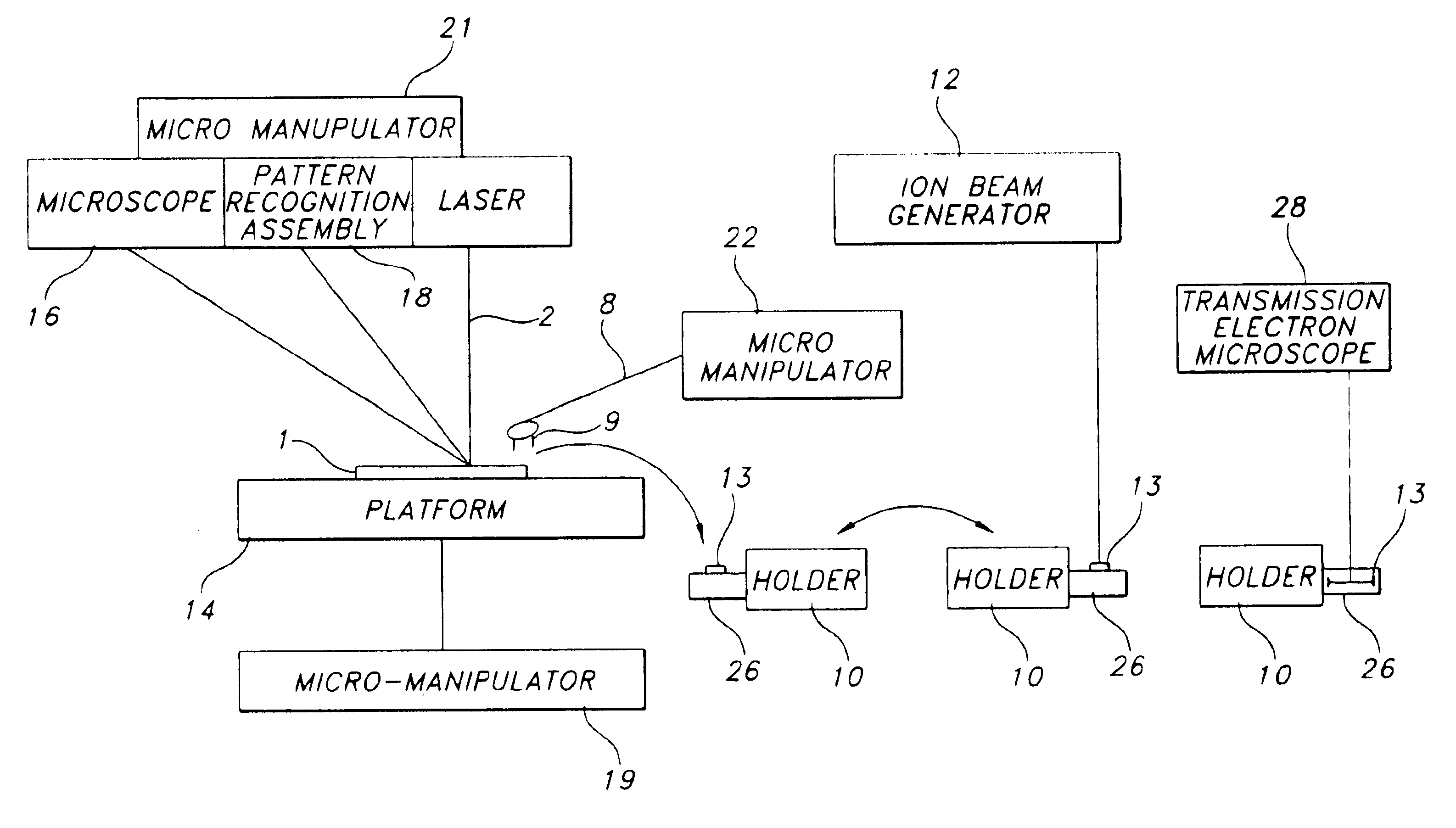

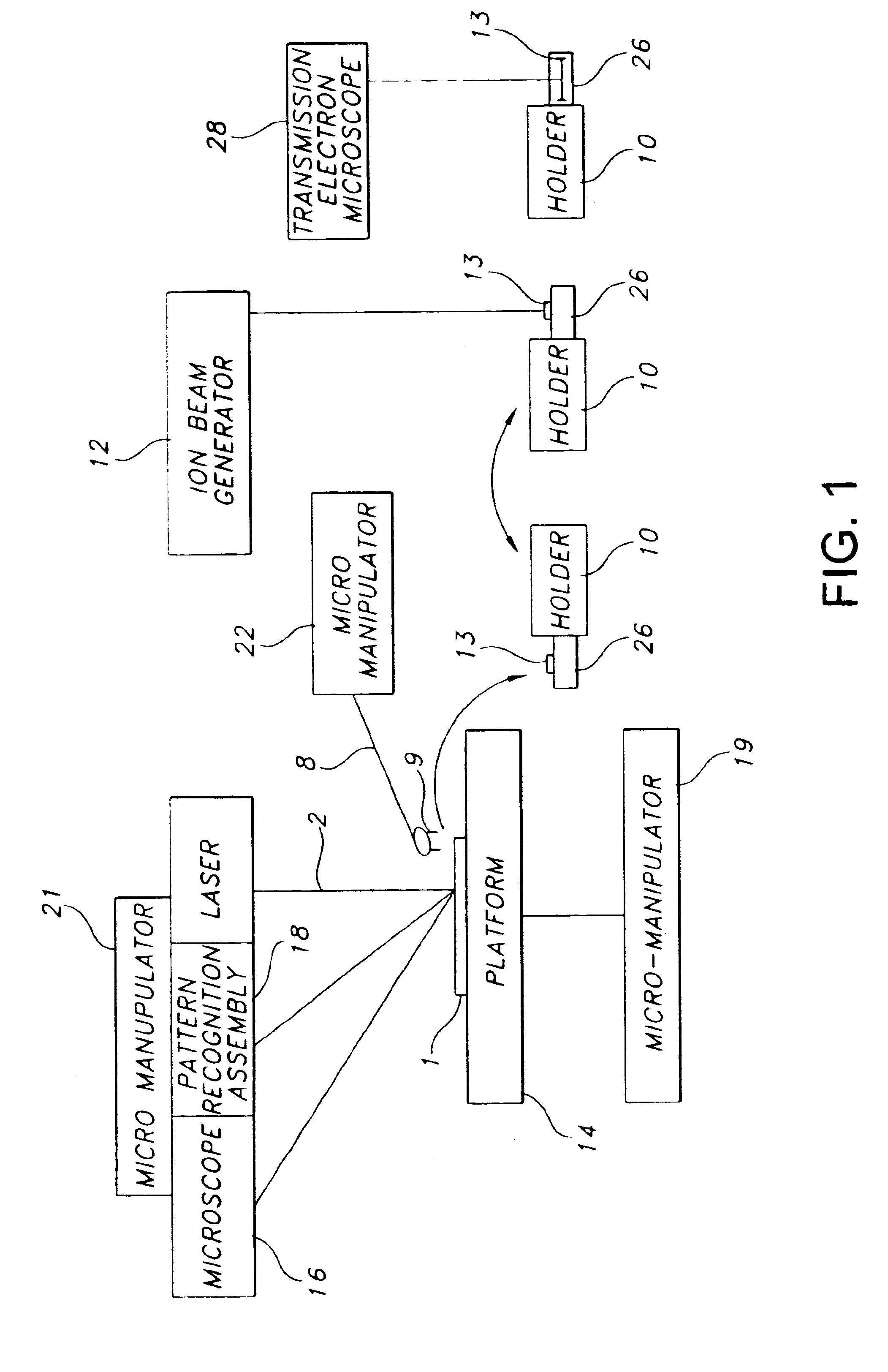

Transmission electron microscope sample preparation

InactiveUS6841788B1Easy to useProvide protectionElectric discharge tubesPreparing sample for investigationElectron microscopeThinning

Sample preparation apparatus and method includes a wafer stage platform with an optical microscope and integrated pattern recognition to automatically address specific locations on the wafer sample of interest. A laser attaches to the optical microscope to mill a set pattern around the area of interest. A precision micro-manipulator engages the sample support structure, extracts the structure, and places the structure in a TEM holder or holder tip. The holder or holder tip can then be placed inside a FIB for final thinning, followed by direct transfer into the TEM.

Owner:OXFORD INSTR AMERICA

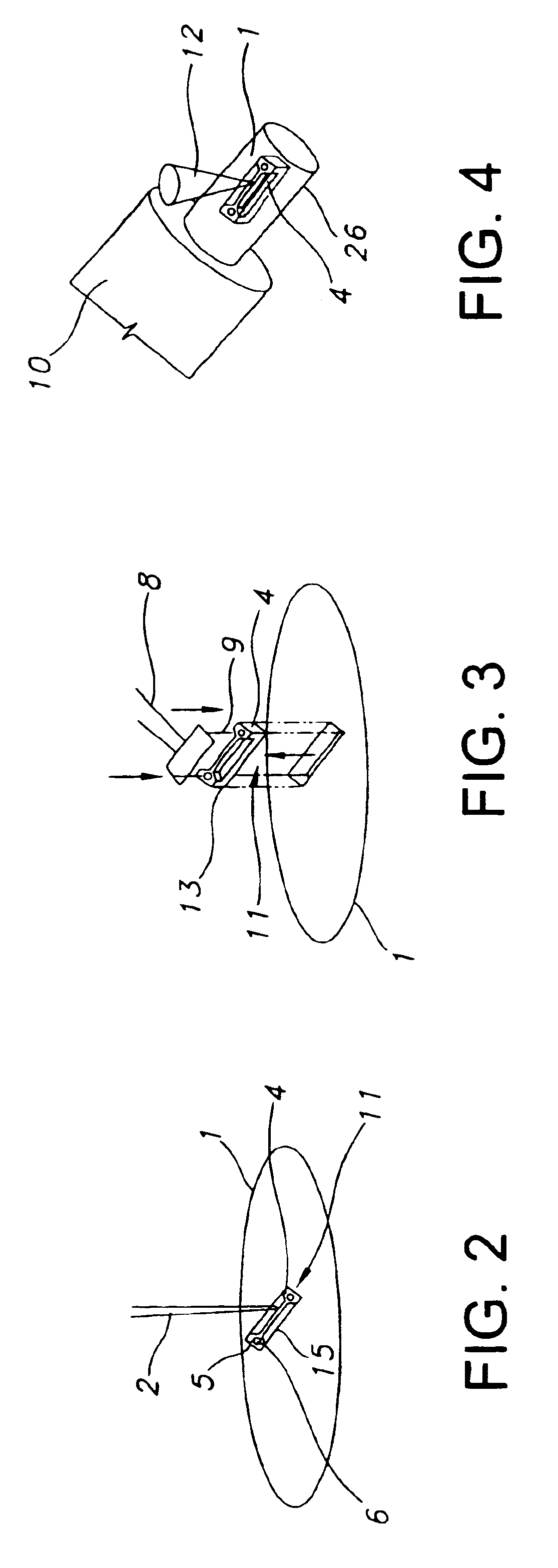

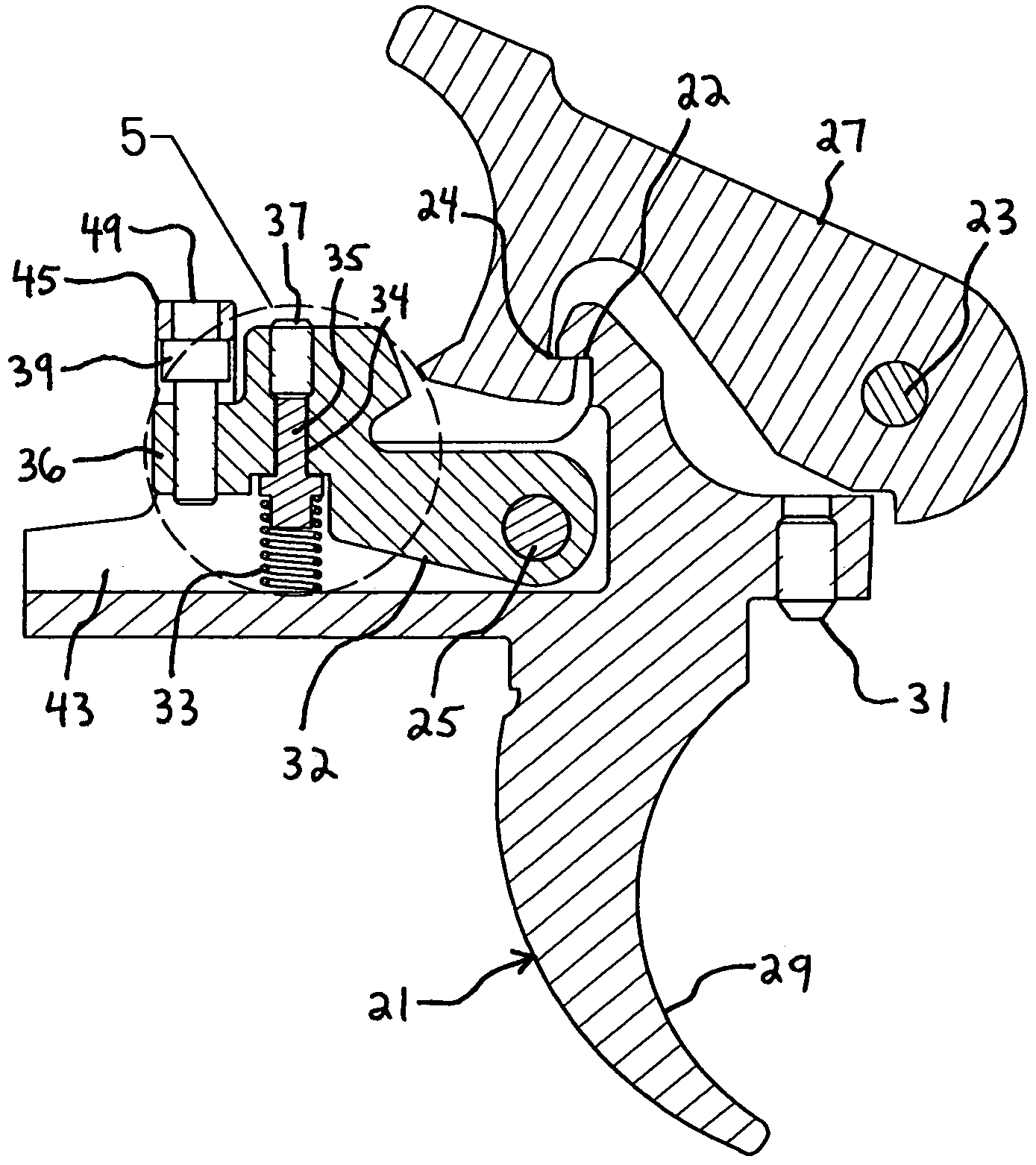

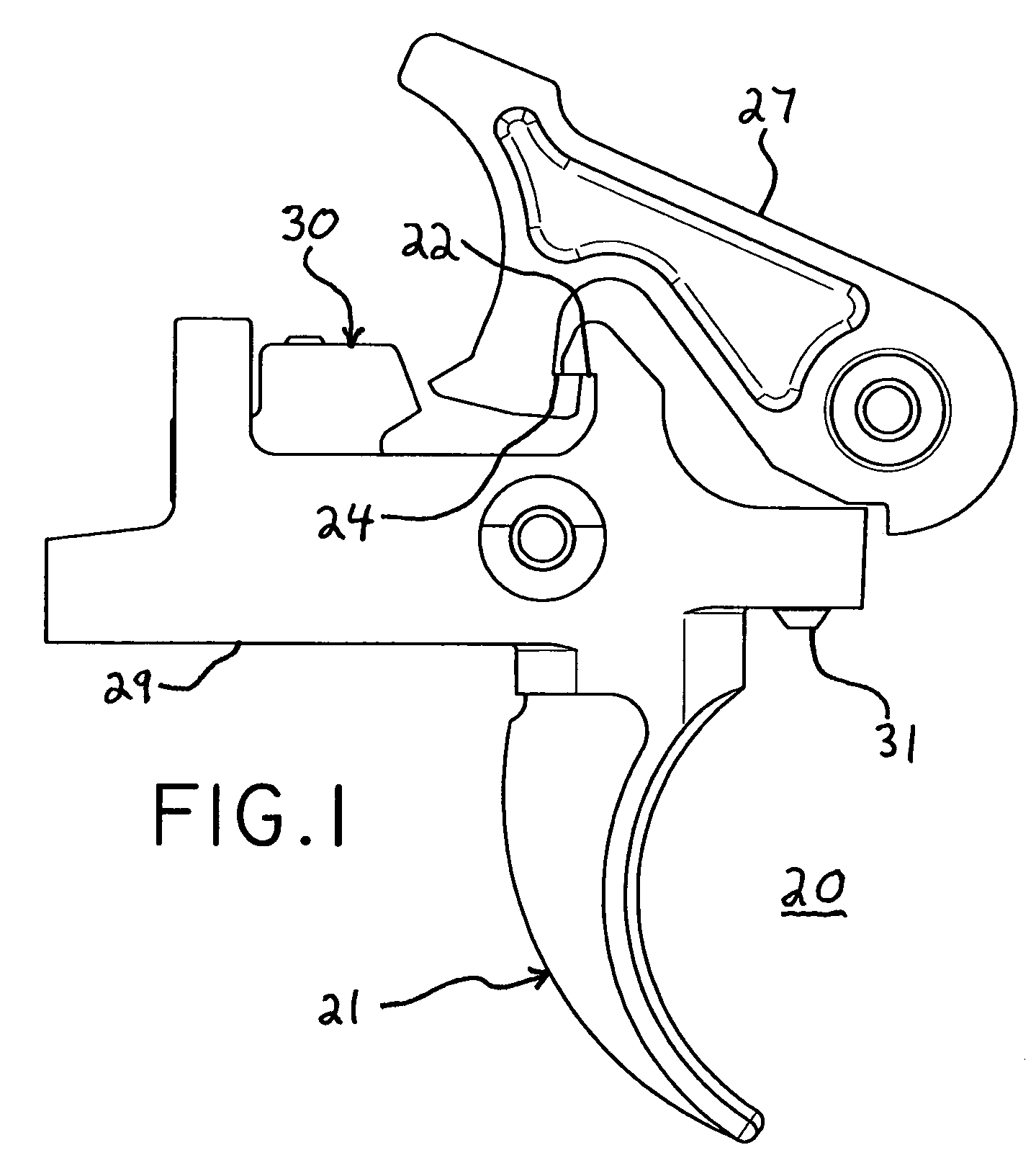

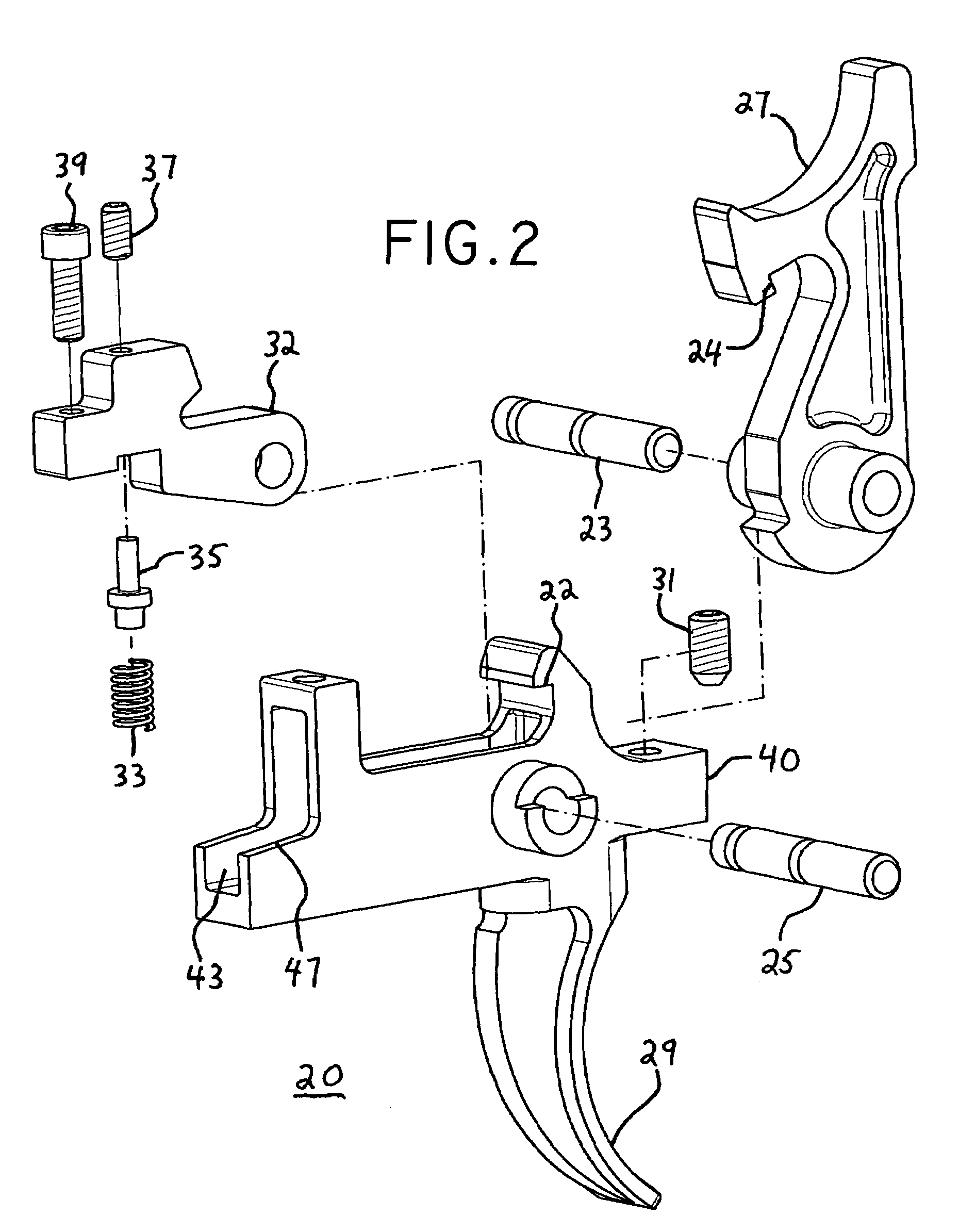

Adjustable dual stage trigger mechanism for semi-automatic weapons

ActiveUS7331136B2Eliminate damageIncrease the areaFiring/trigger mechanismsBreech mechanismsDual stageSemi automatic

A dual stage trigger assembly for a firearm. The trigger assembly comprises a spring loaded lightweight hammer, a spring loaded trigger, a spring loaded disconnector, a spring follower for the disconnector spring and two adjustment screws that allow the user the ability to adjust the sear face of the trigger that is engaged with the hammer in the cocked position and adjust the force imparted to the disconnector by the disconnector spring.

Owner:WHG PROPERTIES

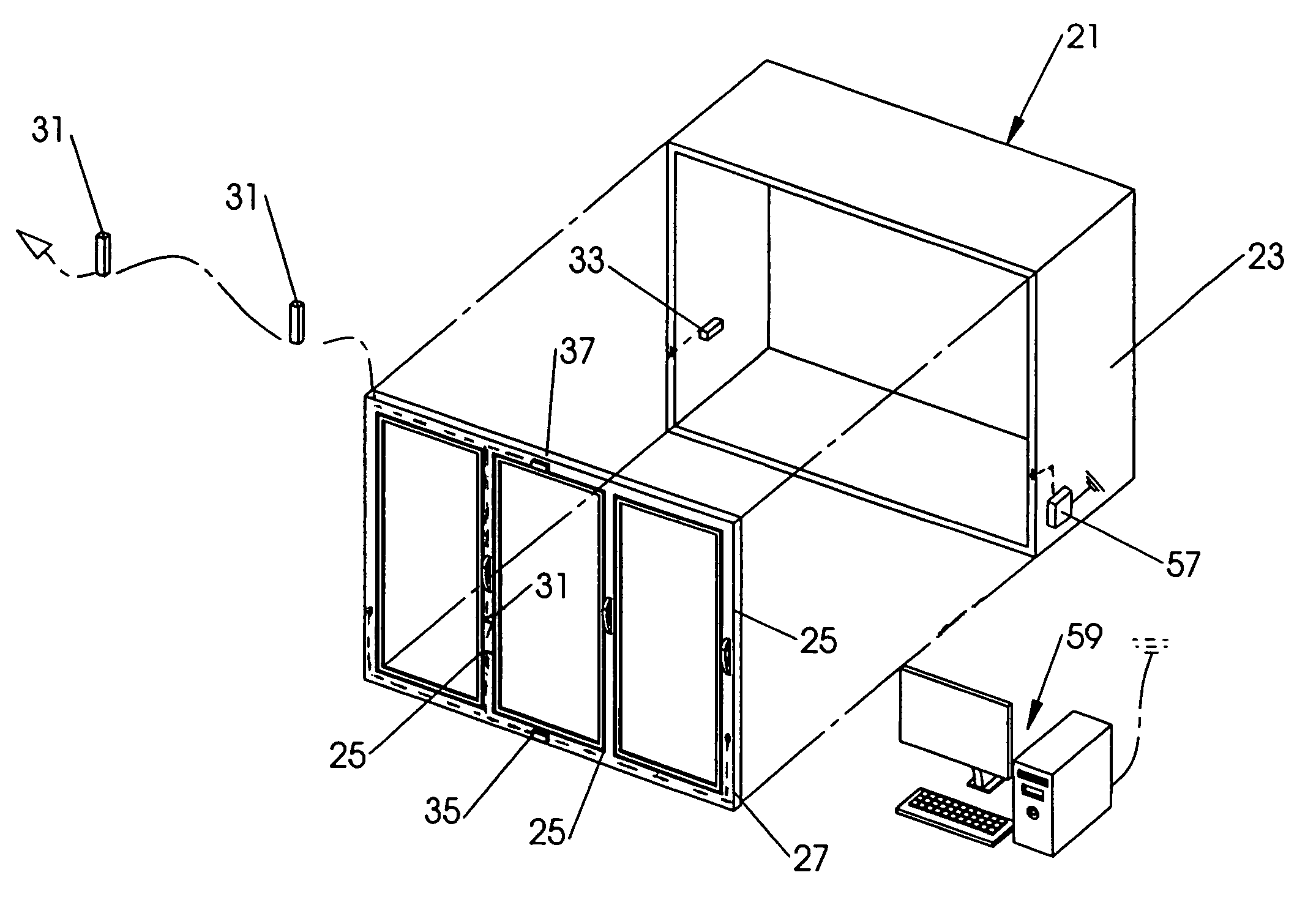

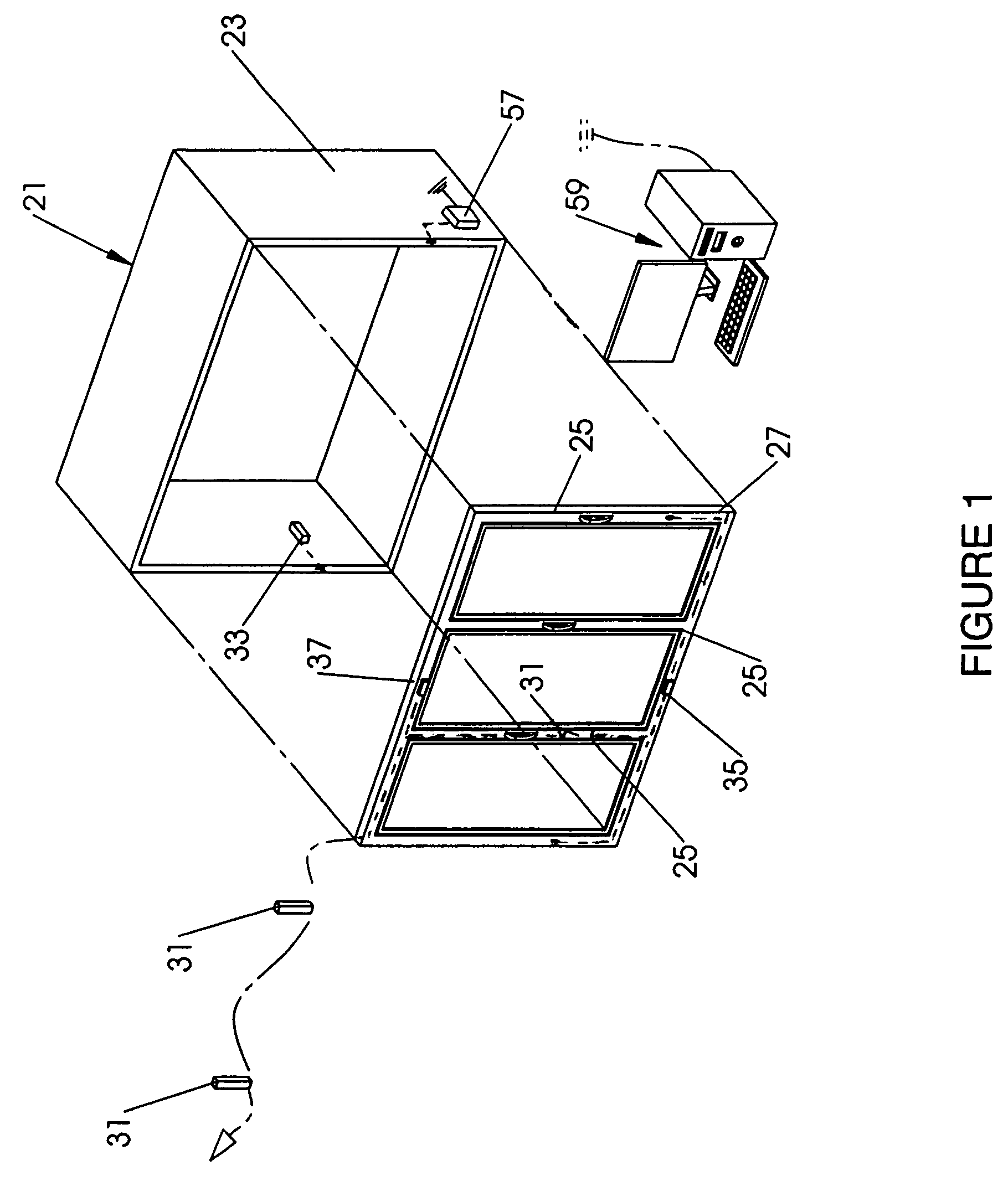

Refrigeration unit condensation prevention

ActiveUS7207181B2Highly accurate sensingEliminate condensationShow cabinetsRefrigeration safety arrangementSensor arrayEngineering

Apparatus, systems and methods are disclosed for efficient elimination of door and frame condensation at widely utilized commercial freezer / refrigeration display cases. The apparatus includes a local controller unit connected with an array of case sensors including an internal case temperature sensor, an external case frame temperature sensor and a dew point sensor. The case frame temperature sensor and dew point sensor are housed to thermally isolate sensing elements thereof from effects of frame temperature changes and ambient air temperature in the vicinity of a sensing element, and to limit heat transfer by the housing to the sensing elements thereby improving sensing accuracy and apparatus performance.

Owner:GEUKE BRADLEY W

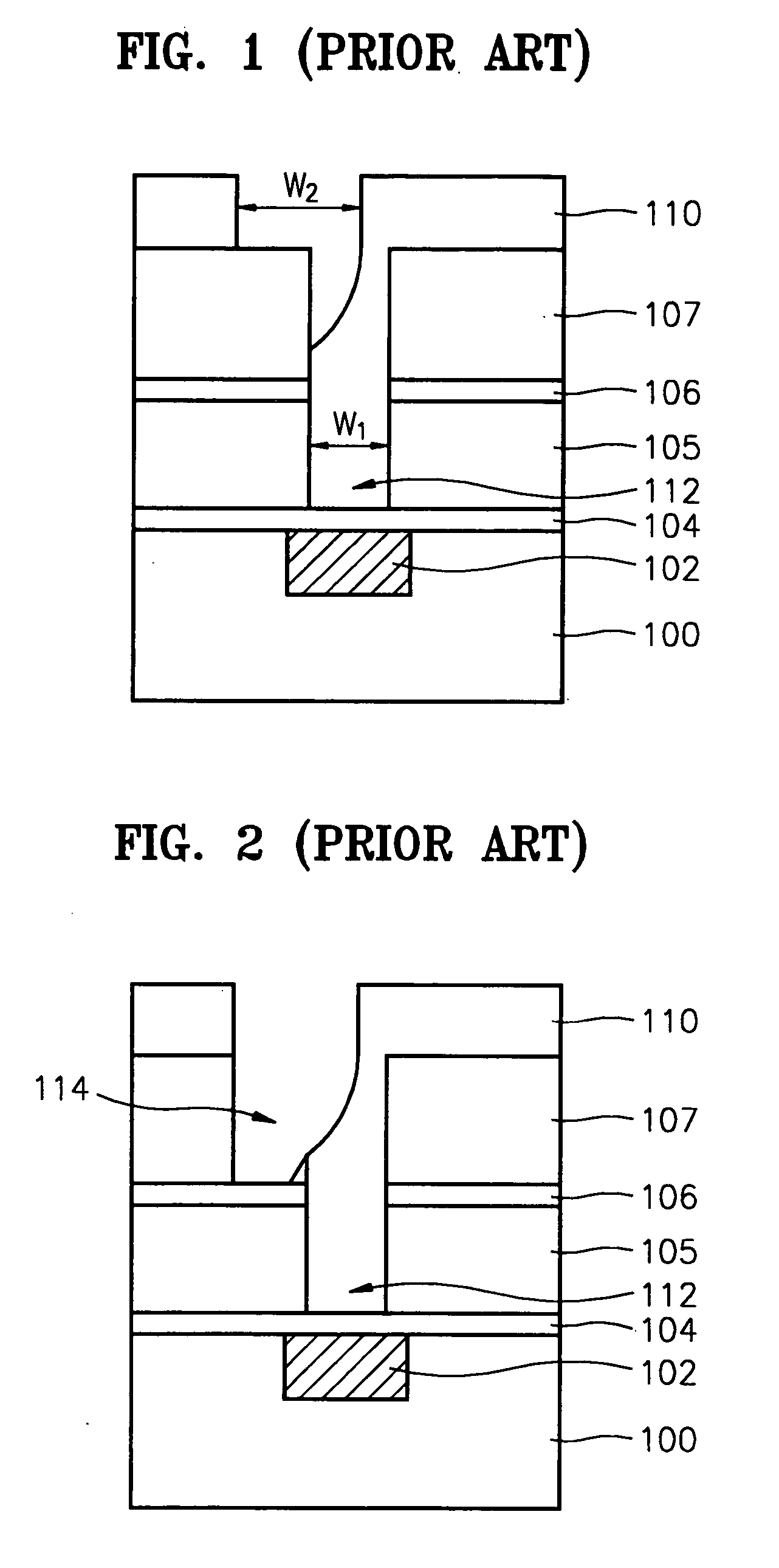

Method of forming metal interconnection layer of semiconductor device

InactiveUS20050037605A1Eliminate disadvantagesEliminate the problemSemiconductor/solid-state device manufacturingMetal interconnectDevice material

Various methods are provided for forming metal interconnection layers of semiconductor devices. One exemplary method for forming a metal interconnection layer of a semiconductor device includes forming an interlayer dielectric layer on a substrate, forming a hard mask layer on the interlayer dielectric layer, wherein the hard mask layer serves as an anti-reflection layer, depositing and patterning a first photoresist layer to form a first photoresist pattern on the hard mask layer, forming a partial via hole in the interlayer dielectric layer by etching the hard mask layer and the interlayer dielectric layer using the first photoresist pattern as an etching mask, removing the first photoresist pattern, depositing a second photoresist layer to fill the partial via hole with photoresist material and patterning the second photoresist layer to form a second photoresist pattern that defines a trench interconnection area which overlaps at least portion of the partial via hole, etching the hard mask layer using the second photoresist pattern as an etching mask to form a hard mask pattern, completely removing the second photoresist pattern and the photoresist material in the partial via hole, etching the interlayer dielectric layer using the hard mask pattern as an etching mask to form the trench interconnection area and to extend the partial via hole to form a full via hole, and filling the full via hole and the trench interconnection area with a conductive material.

Owner:SAMSUNG ELECTRONICS CO LTD

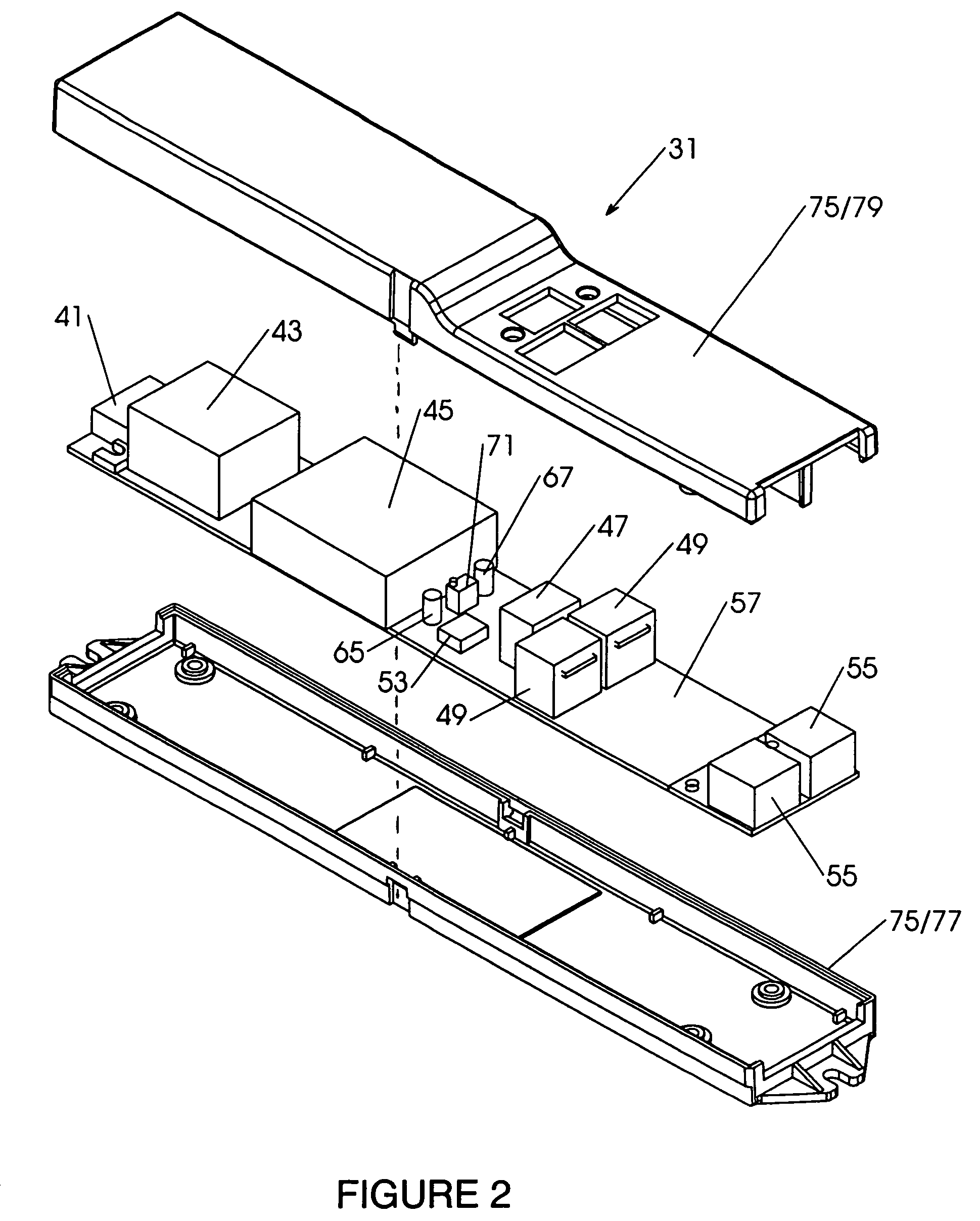

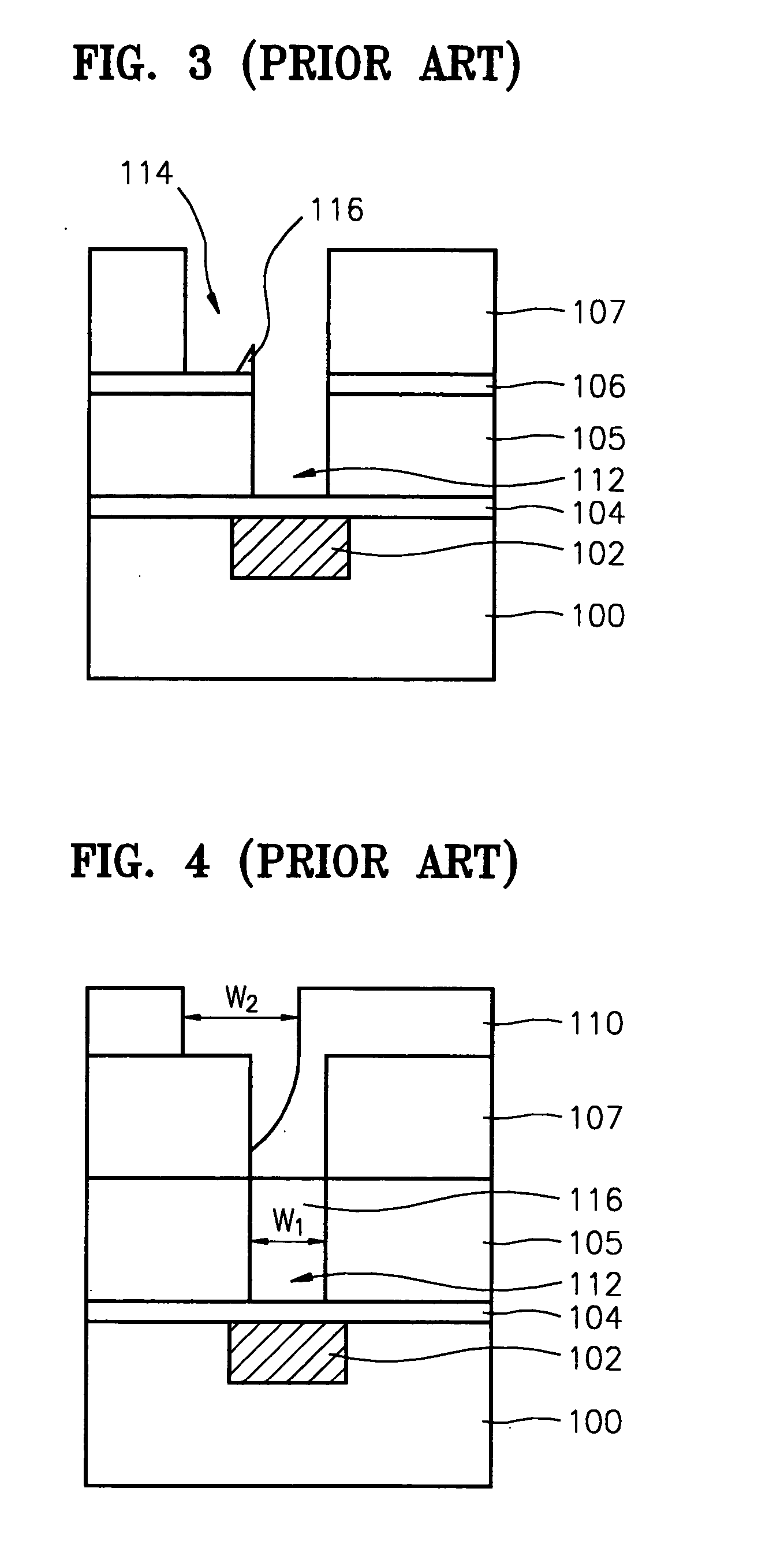

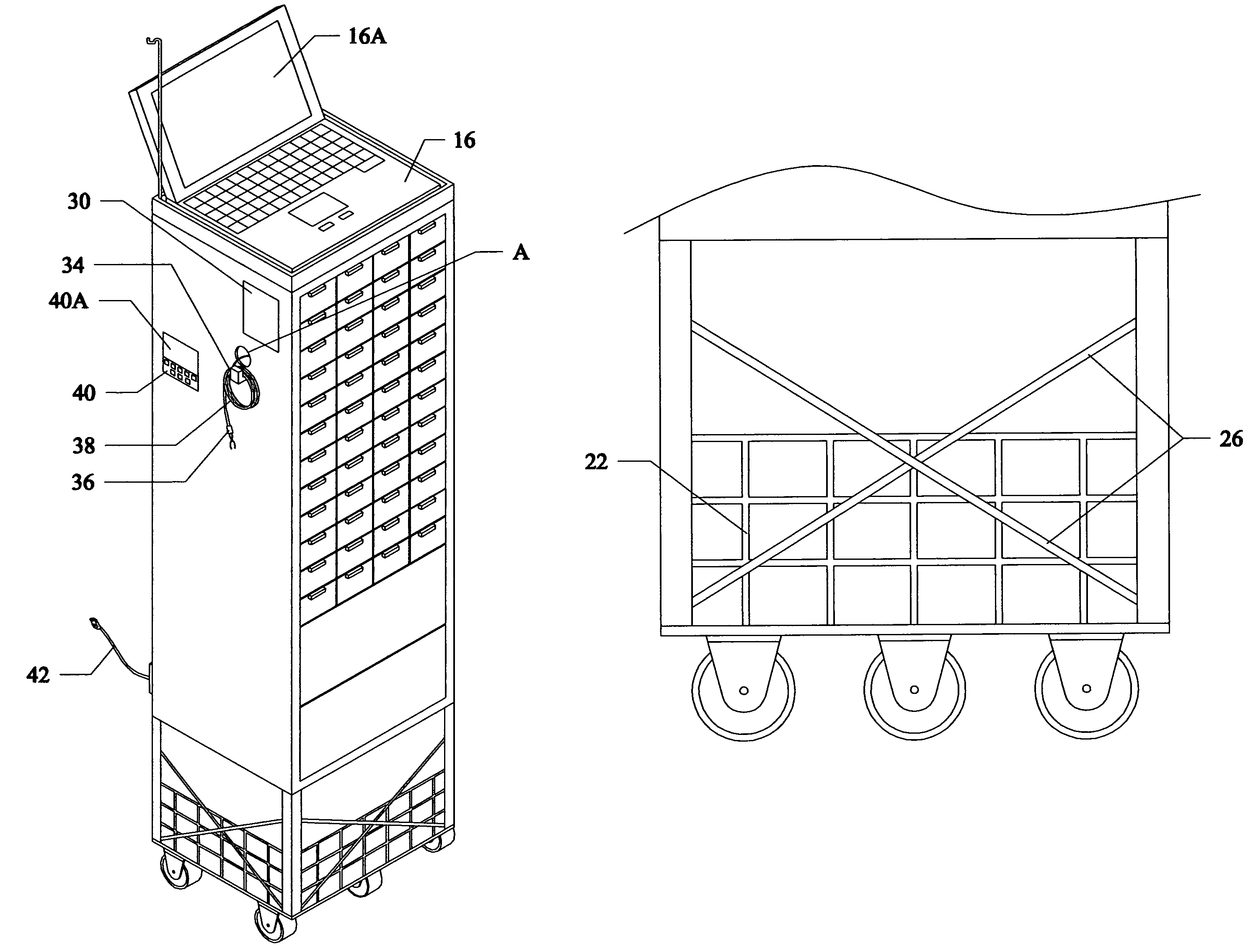

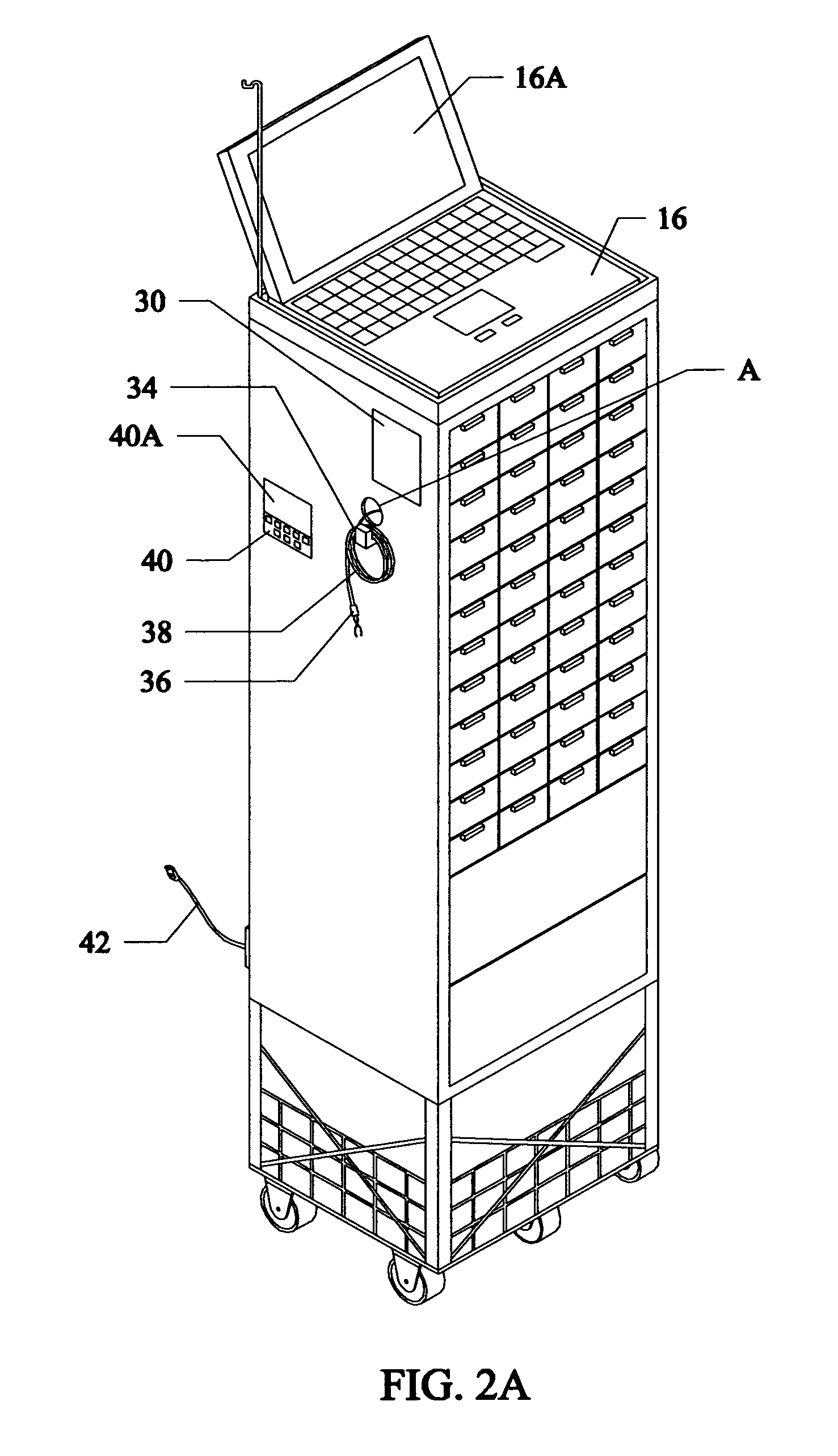

Automated system and device for management and dispensation of respiratory therapy medications

InactiveUS7654261B1Eliminates kneeEliminates back injurySurgical furnitureDrug and medicationsPulse oximetersDisplay device

A computerized, mobile respiratory therapy medication dispensing device, apparatus, system, and method having a mobile housing having a plurality of different size drawers for storing and transporting respiratory therapy medication, devices, and supplies. The housing mounted on a plurality of wheels has a biometric sensor, such as a magnetic badge reader for security, a pulse oximeter mounted in the cabinet for patient monitoring, a computer system mounted on the cabinet including a central processing unit, a transmitter and receiver system responsive to the central processing unit for transmitting and receiving data, the transmitter and receiver system capable of transmitting and receiving data through radio frequency signals, a display responsive to the central processing unit for displaying data, and an input device for inputting data into the computer system, and a rechargeable energy source.

Owner:ROCKHOLD ANN MAREE

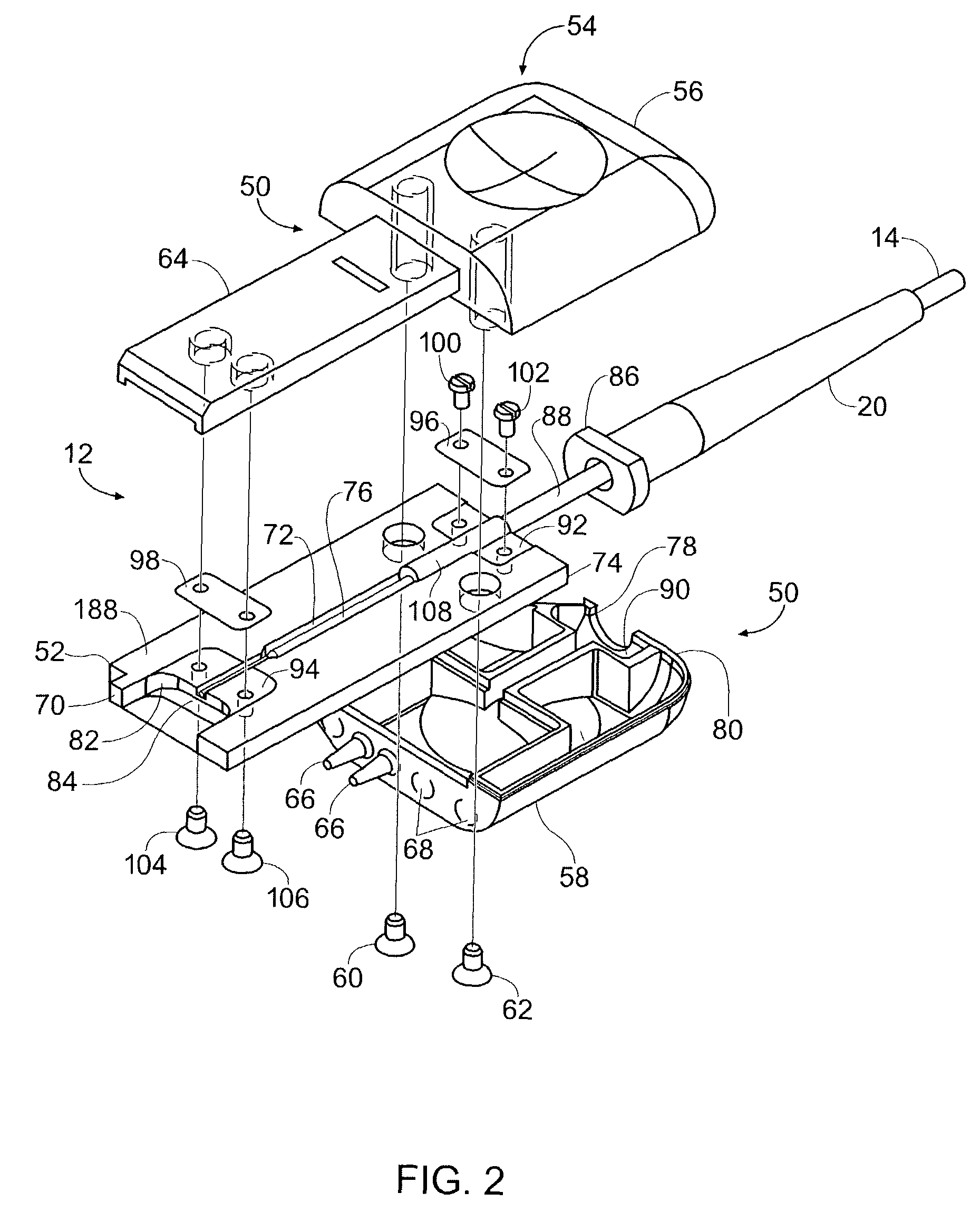

Proximal coupler for optical fibers

InactiveUS7050692B2Eliminate damageMore consistent fiber packingSurgical instrument detailsSensorsFiberAdhesive

A coupler for interfacing a light source, such as a laser, and a fiber optic cable is disclosed. The coupler includes a slide mount having a channel that is adapted to receive optical fibers. The channel extends from a proximal end of the slide mount to a distal end of the slide mount. The proximal end of the slide mount is adapted to fit into an aperture of the light source and the distal end of the slide mount is adapted to transmit light to the fiber optic cable. The coupler also includes a clamp that is mounted on the slide mount adjacent to its proximal end. The clamp covers at least a portion of the channel, thereby securing the optical fibers within the channel without the use of an adhesive.

Owner:SPECTRANETICS

Al-Fe-Sb-RE aluminum alloy, and preparation method and power cable thereof

ActiveCN102978449AEvenly heatedEliminate damagePower cables with screens/conductive layersMetal/alloy conductorsPower cableMetallurgy

The invention provides an Al-Fe-Sb-RE aluminum alloy, and a preparation method of the Al-Fe-Sb-RE aluminum alloy. The method comprises the steps that: (a) an aluminum alloy ingot is cast; (b) the aluminum alloy ingot is subjected to a homogenization treatment; and the obtained aluminum alloy ingot is rolled, such that an aluminum alloy rod material is obtained; (c) the aluminum alloy rod material obtained in the step (b) is subjected to a batch-type annealing treatment; and (d) the aluminum alloy rod material obtained in the step (c) is subjected to an aging treatment, such that aluminum alloy is obtained. The invention also provides a power cable. According to the invention, through the selection and control over added elements and the adoption of a reasonable preparation process, the obtained aluminum alloy is provided with good comprehensive performance.

Owner:ANHUI JOY SENSE CABLE

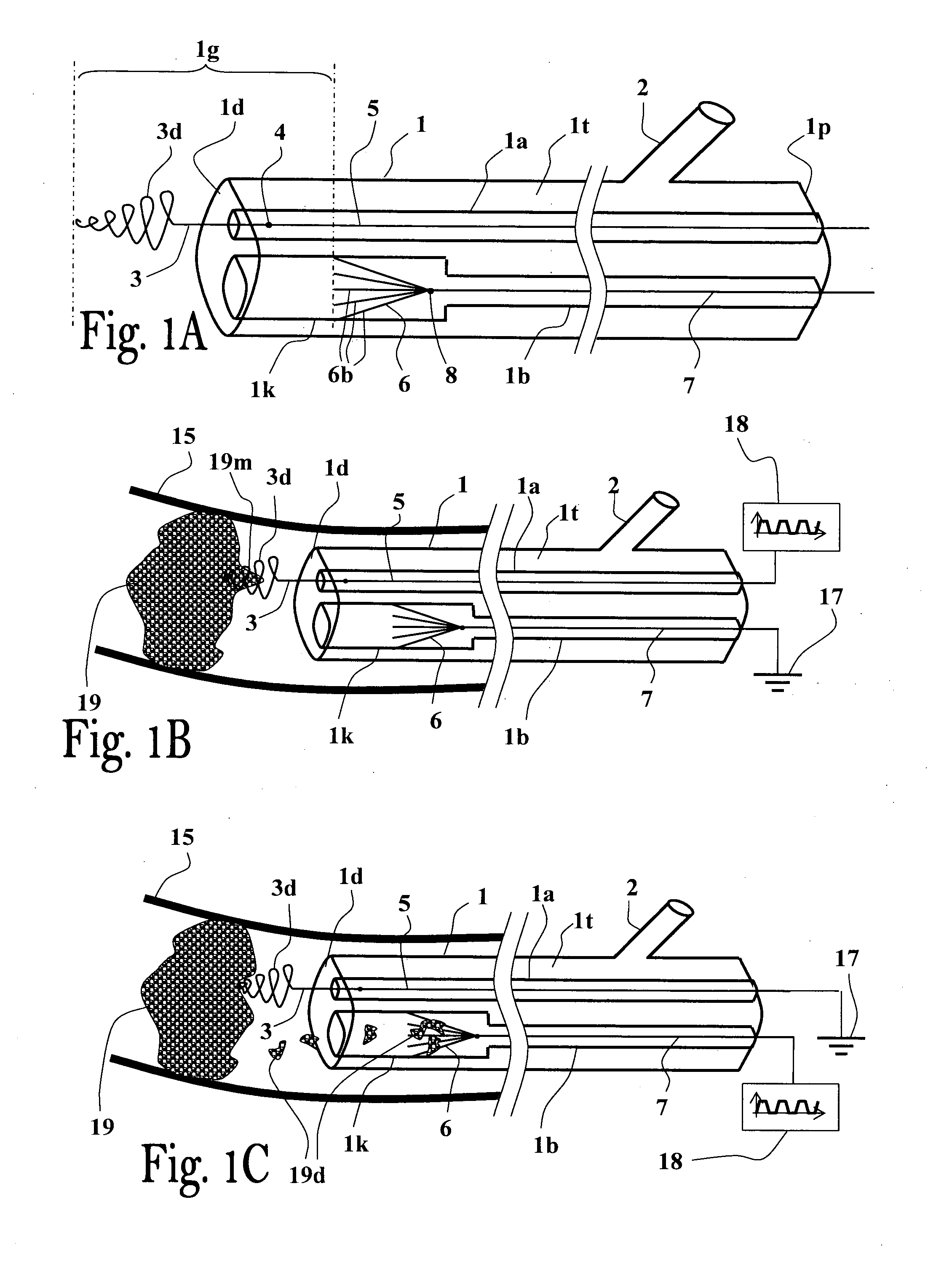

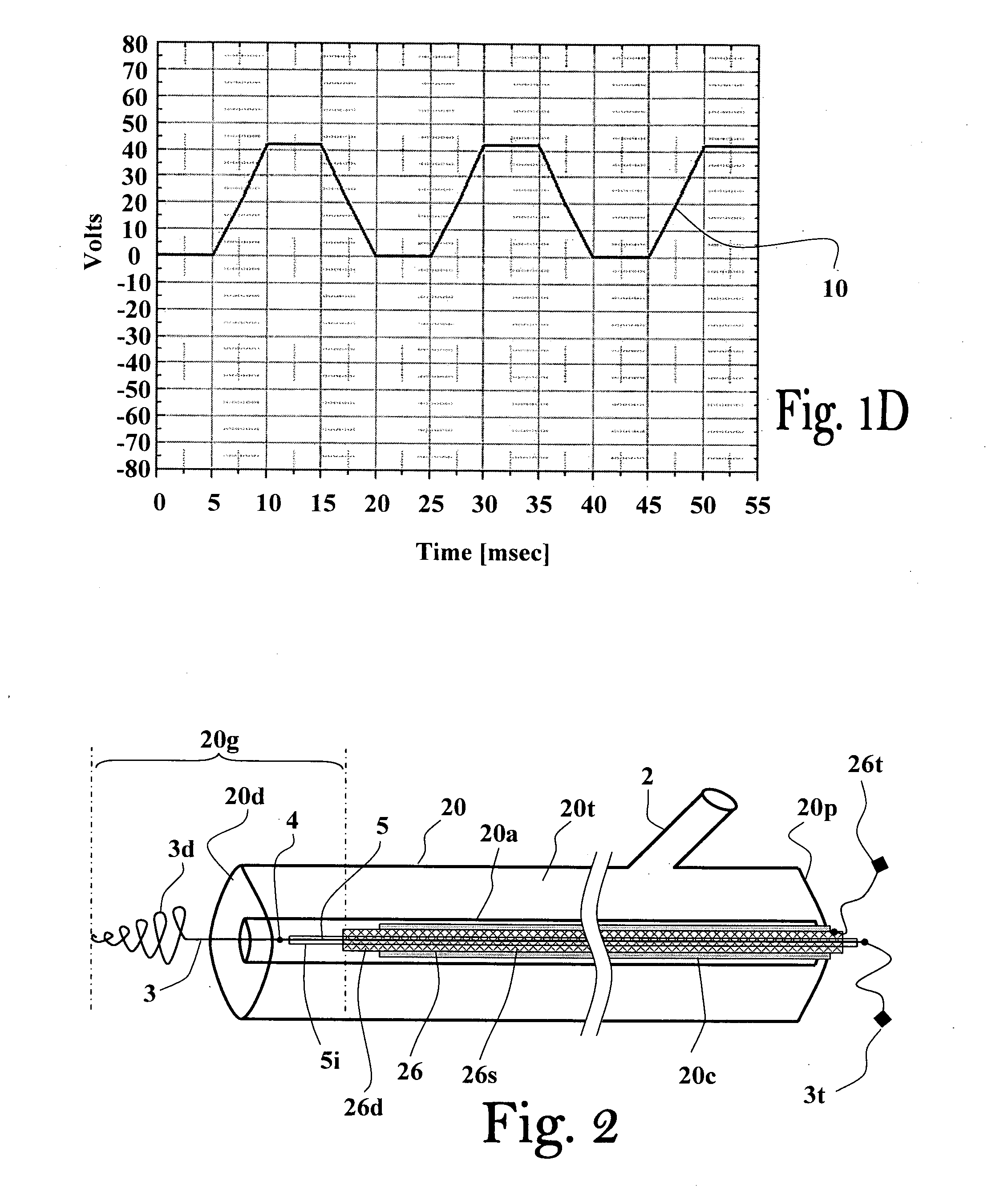

Method and apparatus for thrombus dissolution/thrombectomy by an electrode catheter device

ActiveUS20110301594A1Eliminate damageEasy to useCatheterSurgical instrument detailsElectricityThrombus

The present invention generally relates to a flexible catheter device capable of being introduced into body passages, withdraw fluids therefrom or introduce fluids thereinto, and which includes electrodes configured to apply electrical signals in the body passage for carrying out thrombus dissolution and / or thrombectomy, wherein one of said electrodes is designed to contact the thrombus material and remove it or dissolve it, and wherein the electrical voltage signals are a unipolar pulsatile voltage signal.

Owner:MAGNETO THROMBECTOMY SOLUTIONS LTD

Overhead rotary valve for engines

InactiveUS6308677B1Simple sealing deviceImprove sealingMachines/enginesRotary slide valveCombustion chamberExhaust valve

An overhead rotary valve fitted into a cylinder head with diametrical polygonal openings formed therein for use in combination with an internal combustion engine, driven to bring intake and exhaust ports into and out of alignment with passages leading to and from the combustion chamber. Sleeve bearings are fitted in the cylinder head that provide surface sealing, and annular sealing members prevent the air / fuel mixture or exhaust gases from flowing into regions intermediate ports and individual cylinders. Utilizing this overhead rotary valve and associated seals and bearings increases the efficiency and performance of an internal combustion engine. The overhead rotary valve rotating, at one quarter the speed of the crankshaft, minimizes wear and noise levels, self cleans the ports, allows the engine to operate at higher rpm and imparts proper opening and closing of passages at the proper sequence of valve timing without concern of valve float. The instant invention removes the need for reciprocating intake and exhaust valves, camshafts, rocker arms, lifters, push rods, valve guides and retainers, and other related hardware for actuation, significantly increasing the reliability and effectiveness of the internal combustion engine, while reducing overall manufacturing costs.

Owner:BOHACH WILLIAM LOUIS +1

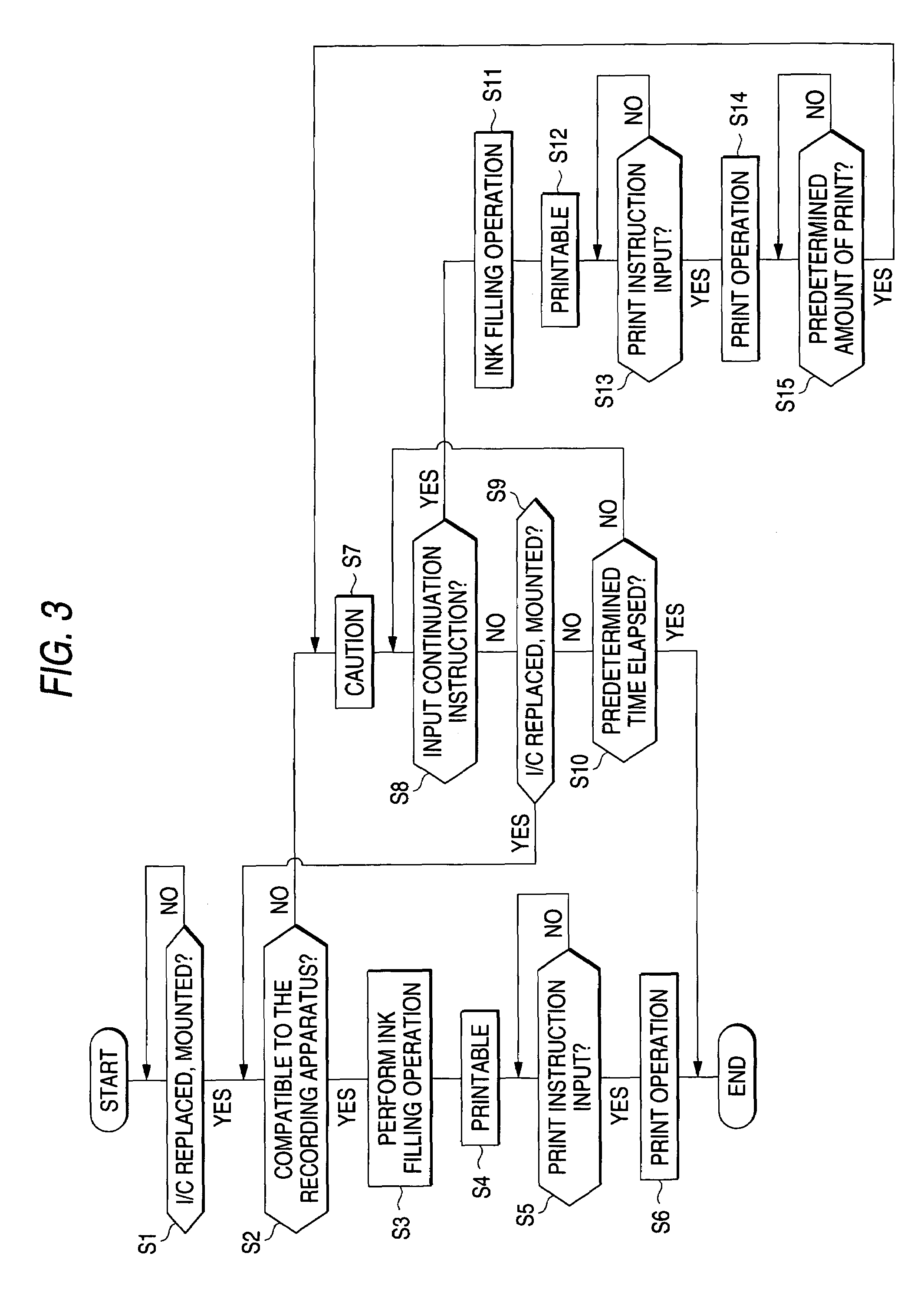

Ink jet recording apparatus

InactiveUS6971732B1Quality improvementEliminate damageOther printing apparatusEngineeringMechanical engineering

In an ink jet recording apparatus comprising an ink jet recording head 3 for receiving supply of ink from an ink cartridge 4 provided with a storage device 7 storing data for determining compatibility to a recording apparatus, and a print controller 10 for determining compatibility of ink based on the data in the storage device 7 and executing the print operation, when an ink cartridge 4 is mounted, if compatibility to the ink cartridge 4 cannot be confirmed, a caution is given and the recording apparatus awaits an input of a continuation instruction by a user to execute a subsequent operation. Even if a cartridge whose compatibility cannot be confirmed is mounted, printing is enabled as much as possible without incurring damage to the recording apparatus.

Owner:SEIKO EPSON CORP

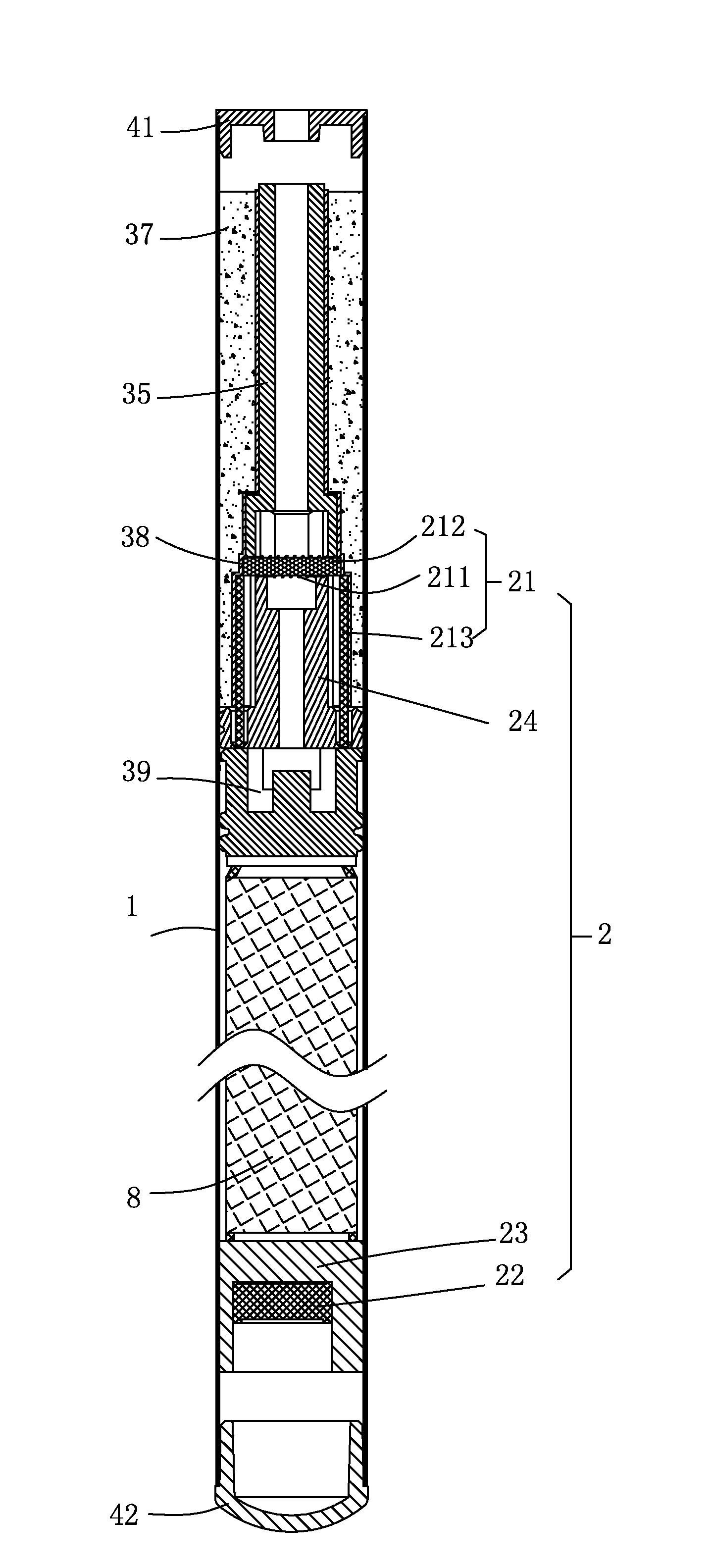

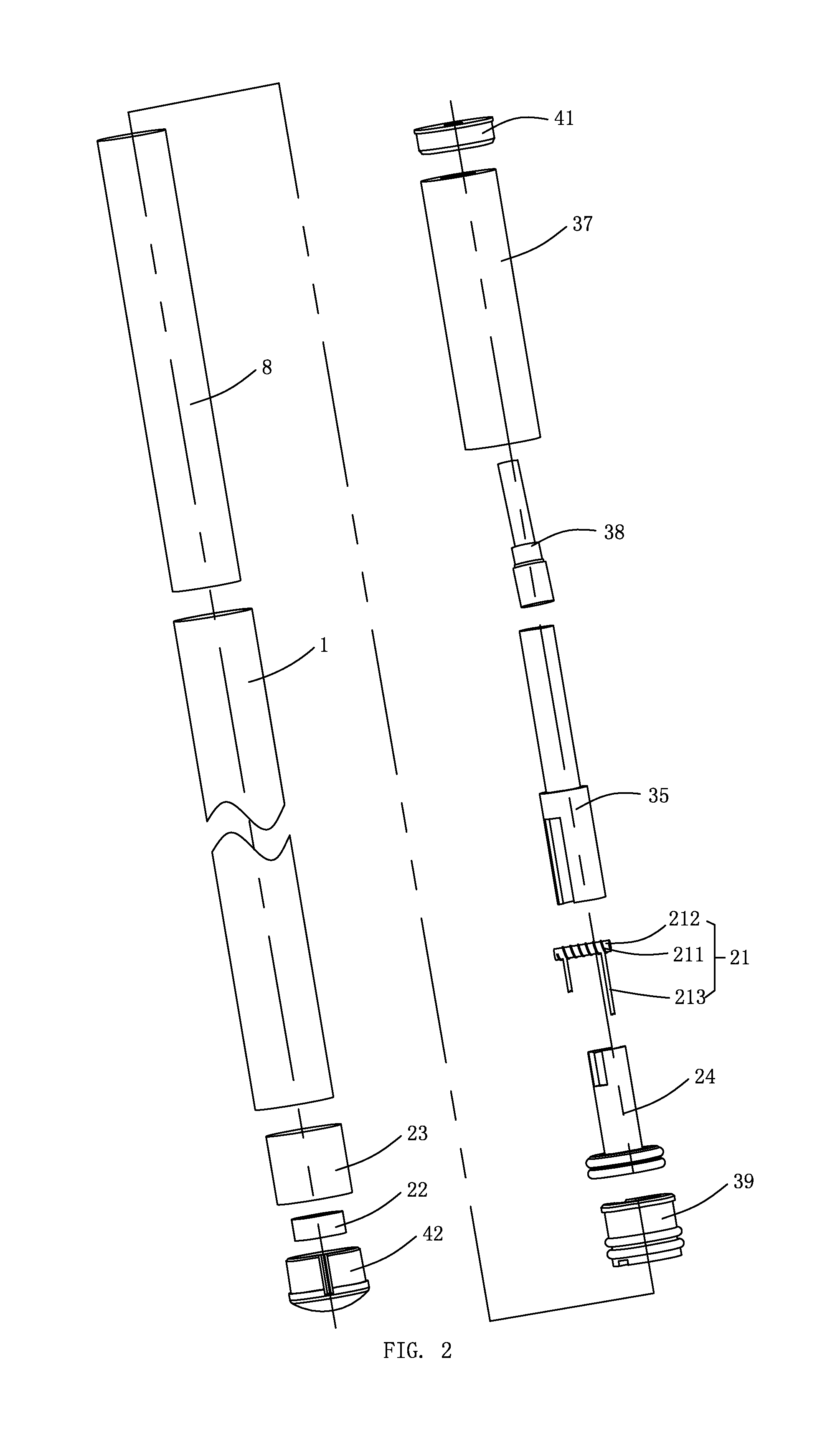

Organic cotton electronic cigarette

InactiveUS20140338684A1Stable internal structureLow costTobacco pipesTobacco devicesGlass fiberElectricity

An organic cotton electronic cigarette includes a liquid storage component and an atomization device. The atomization device includes a hollow spiral tubular electric heater coil and a liquid guiding member passing through the electric heater coil. The liquid guiding member is made from organic cotton free of glass fiber material. The atomization device further includes a smoke guiding tube passing through the liquid storage component for supporting the same and working as a smoke path. The smoke guiding tube includes an external casing and an internal casing one of which is inserted into another one so as to hold the liquid guiding member between the two. The two ends of liquid guiding member extend out of the smoke guiding tube and are tightly pressed against an inner wall of the liquid storage component. This kind of electronic cigarette is safe to human body and has stable internal construction.

Owner:HUIZHOU KIMREE TECH