Junction field effect transistor and manufacturing method thereof

A technology of field effect transistors and surface junctions, applied in the manufacture of surface junction field effect transistors, in the field of surface junction field effect transistors, can solve problems such as increased process costs, achieve reduced doping concentration, small pinch-off voltage, and large The effect of channel current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

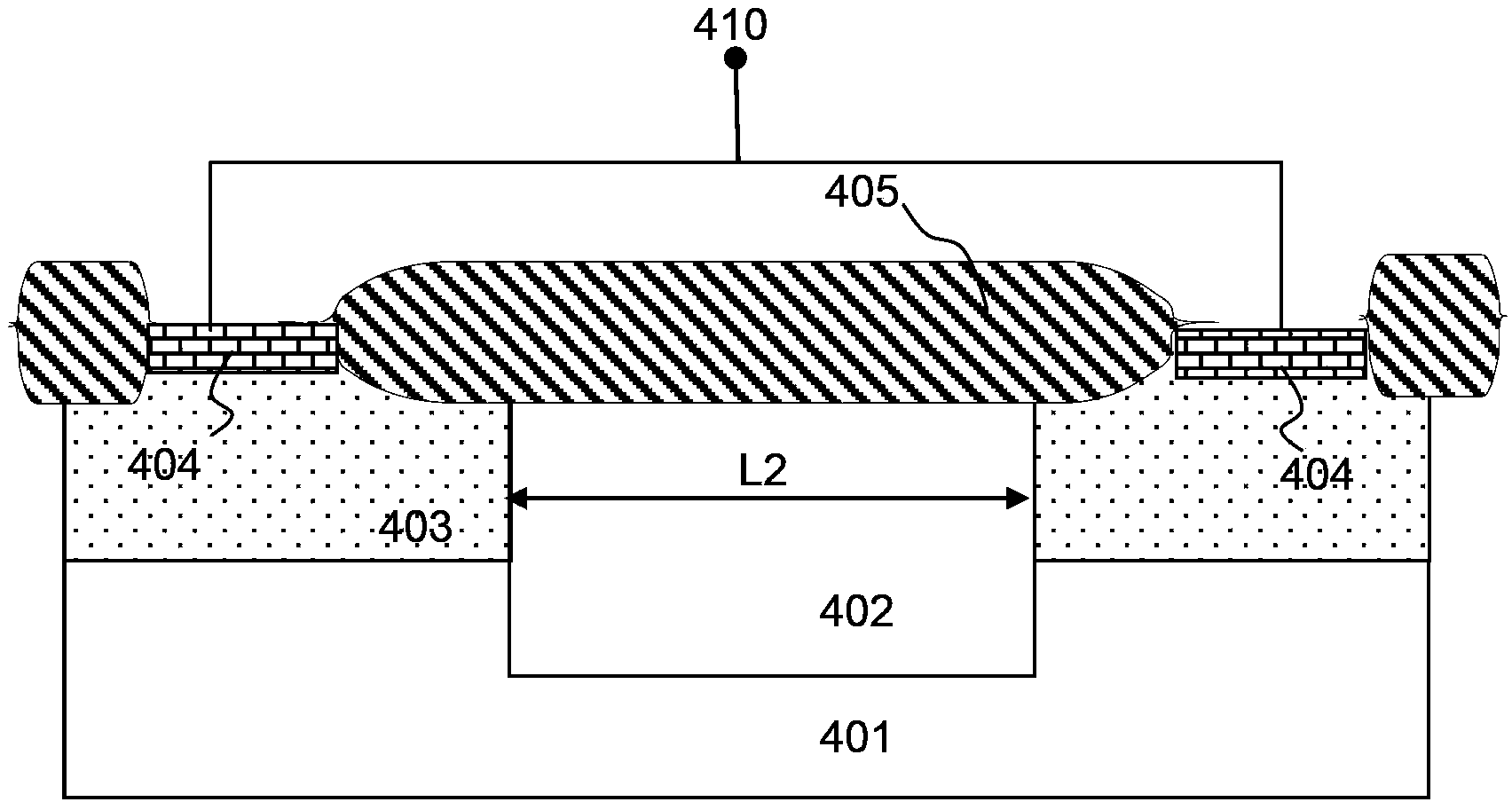

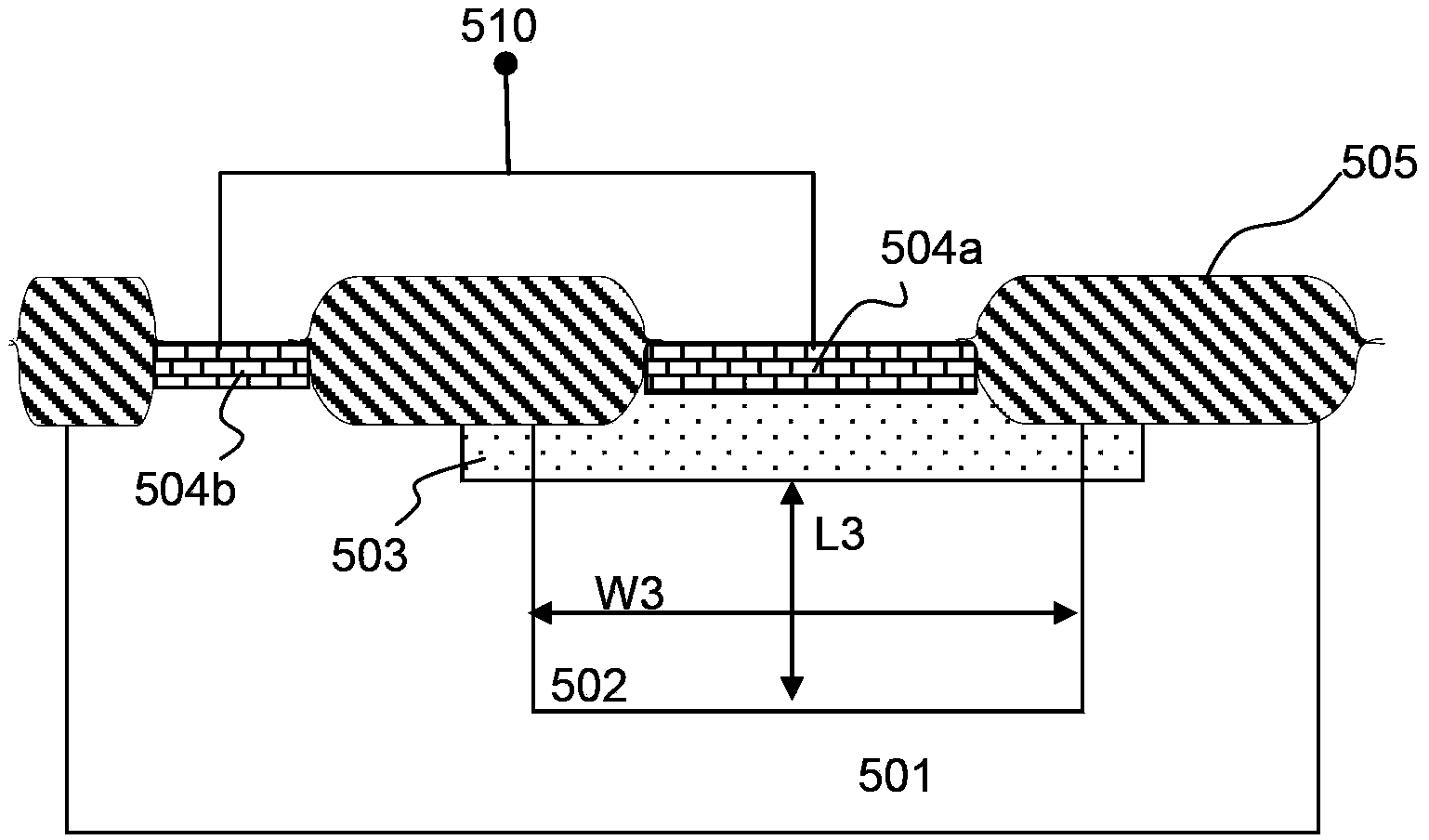

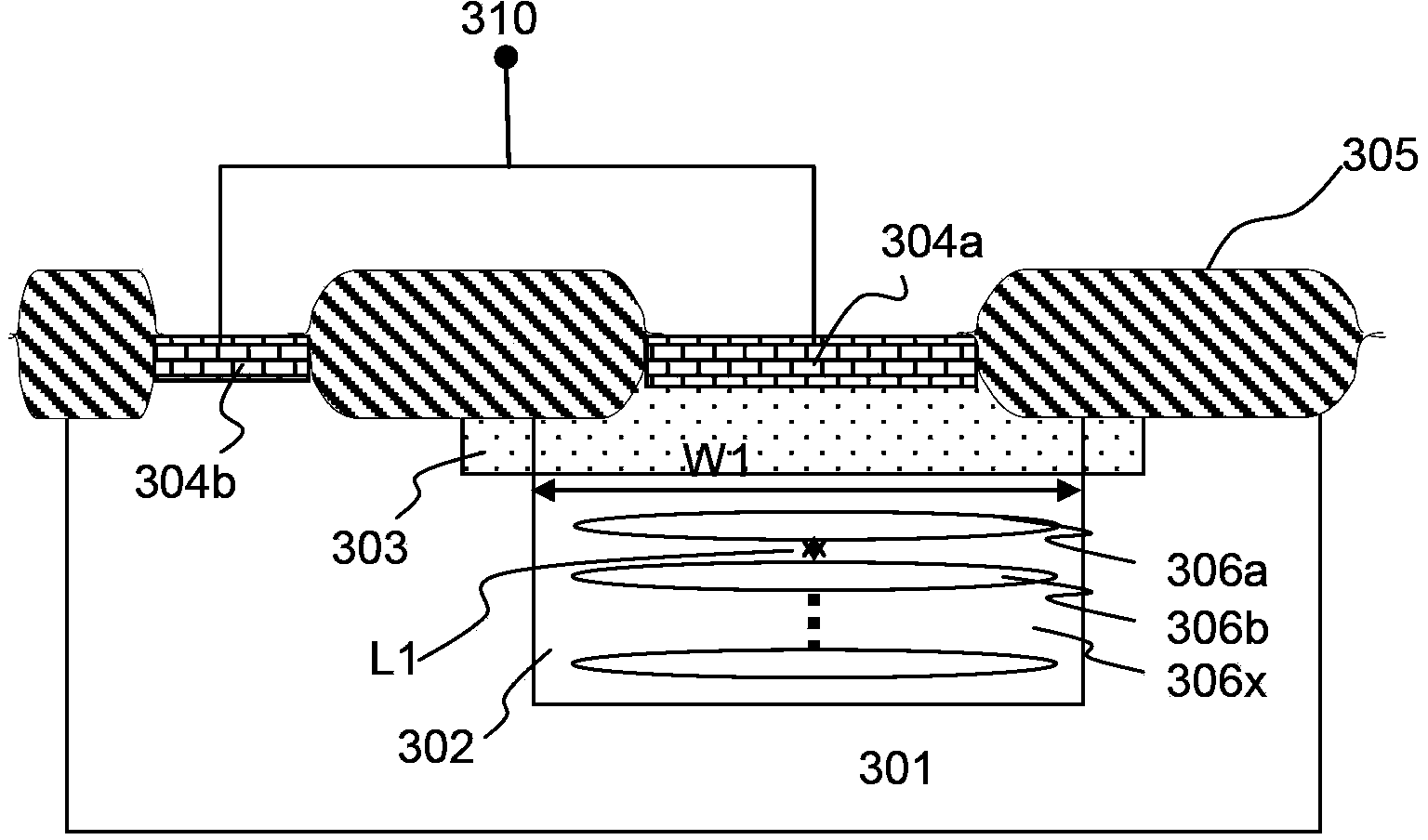

[0049] Such as Figure 4A Shown is a schematic diagram of a top view of a junction field effect transistor according to an embodiment of the present invention; Figure 4B shown, is Figure 4A Schematic diagram of the section along the AA line; Figure 4C shown, is Figure 4A A schematic cross-sectional view along line BB. In the embodiment of the present invention, the junction field effect transistor takes a device whose channel conductivity type is N-type carriers as an example, and the JFET in the embodiment of the present invention includes:

[0050] Two N-type wells 102a and 102b are formed on a P-type semiconductor substrate such as silicon substrate 101 . Such as Figure 4A As shown, the two N-type wells are rectangular, the adjacent width sides of the two N-type wells 102a and 102b are the same size, that is, both have a width W1, and the two N-type wells 102a and 102b are adjacent Both ends of the width sides are aligned and separated by the distance S1.

[005...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More