Metal-insulator-semiconductor transistors with gate-dielectric/semiconductor interfacial protection layer

A gate dielectric layer and interface protection technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve the threshold voltage stability gate dielectric reliability hinders the commercialization of gate E-mode III-NMIS-FET , small safe operating range and other issues, to achieve the effects of high stability, small hysteresis, and high threshold voltage stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

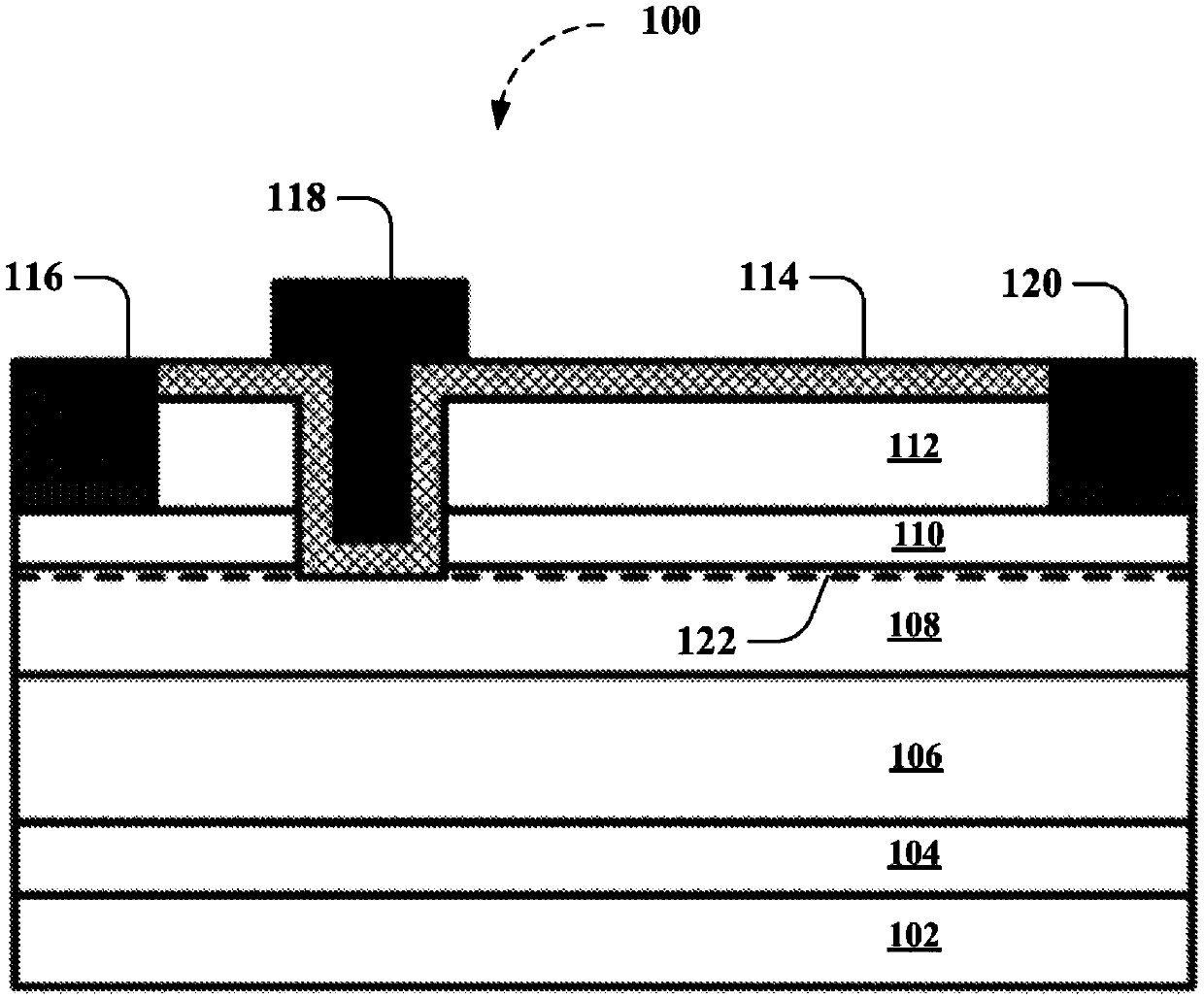

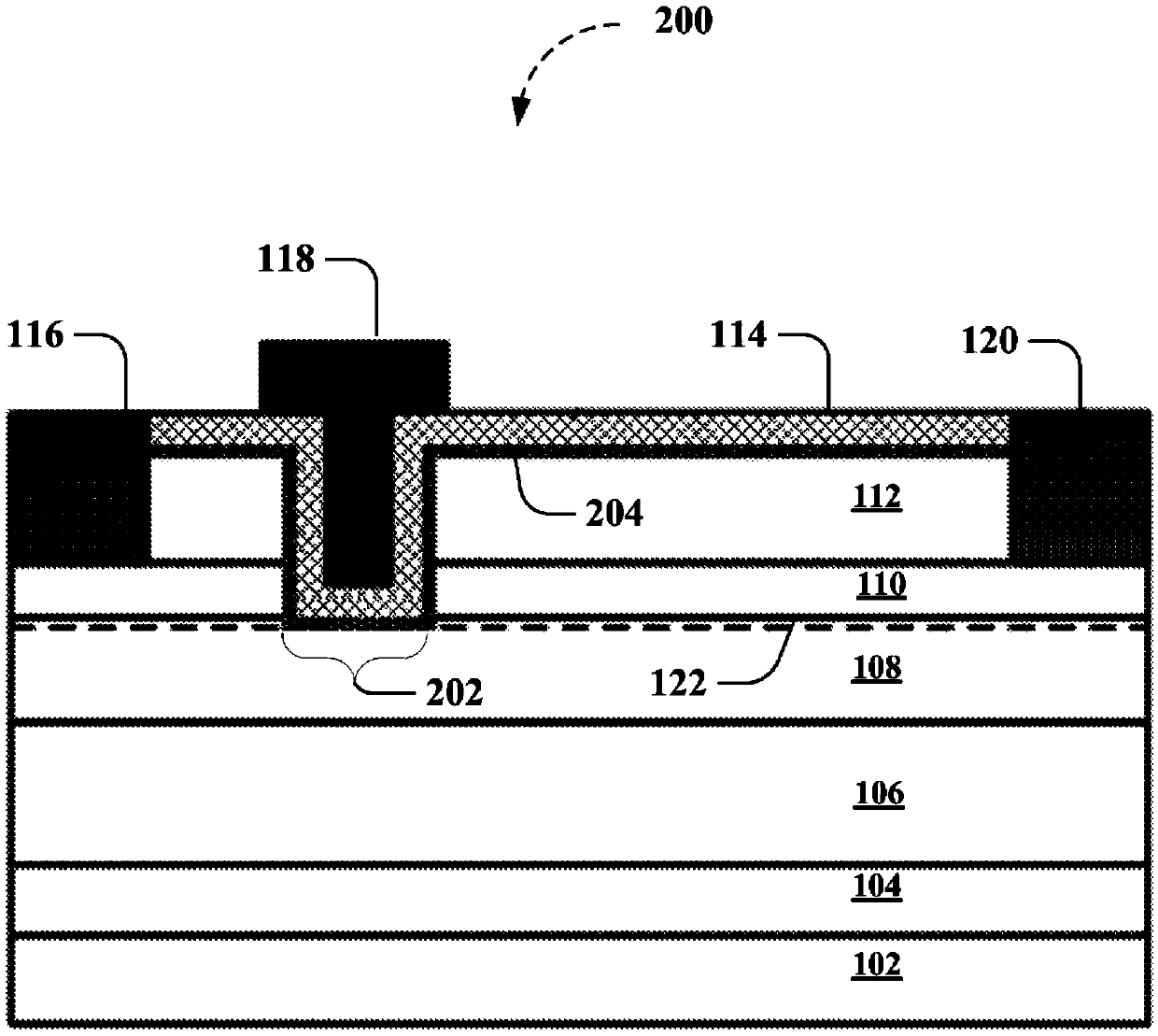

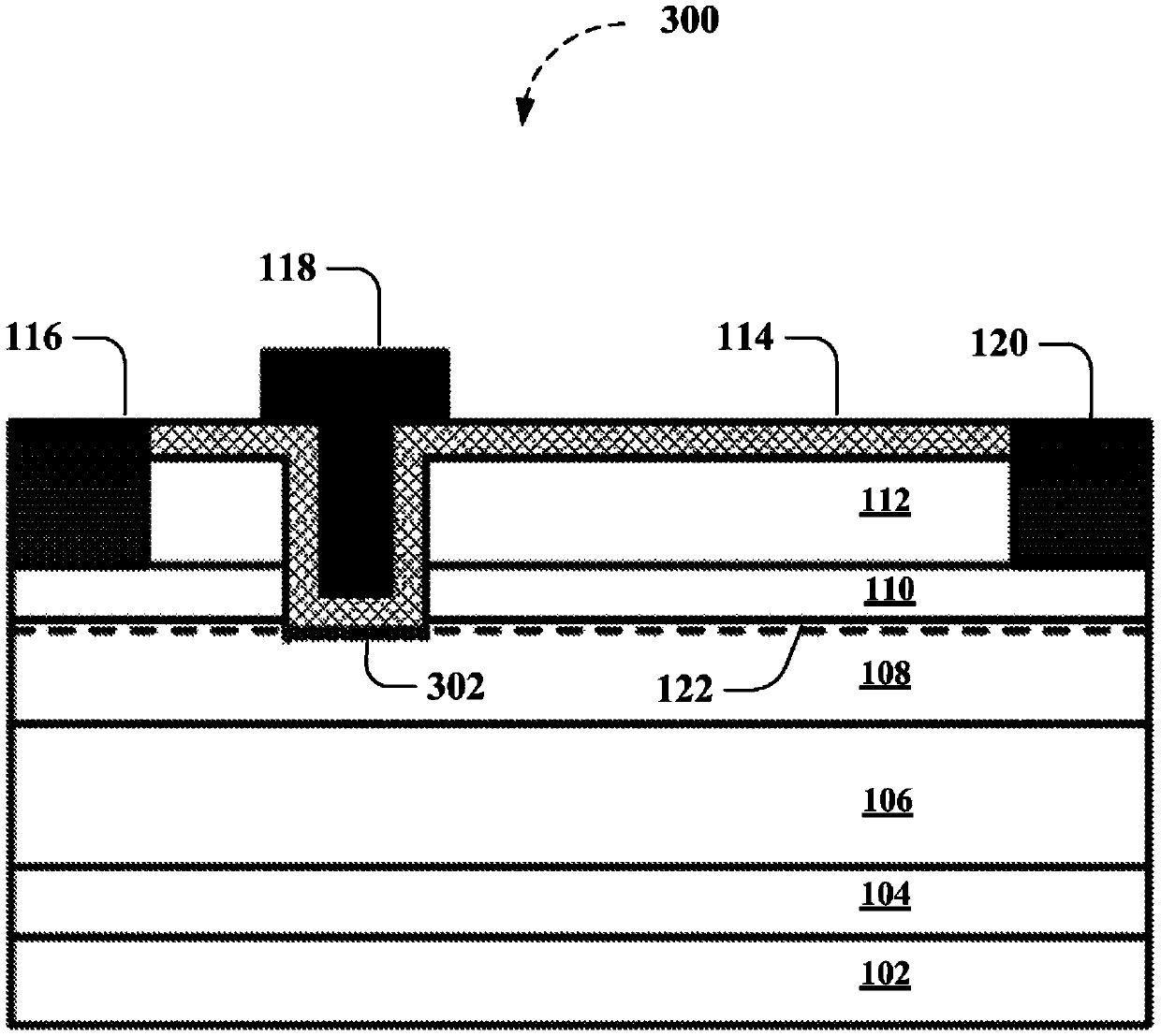

[0073] figure 2 Depicting non-limiting LPCVD-SiN according to various non-limiting aspects described herein x An exemplary cross-sectional schematic of a MIS-FET 200 including an exemplary first embodiment of a gate interfacial protective layer having an exemplary 2 nanometer (nm) plasma-enhanced chemical vapor deposition (PECVD)— SiN x Gate interface protection layer. According to various non-limiting aspects, an exemplary device 200 as described herein can include a substrate 102, a nucleation layer 104, a buffer layer 106, a semiconductor or channel layer 108, a barrier layer 110, a passivation layer 112, a gate interface protection layer 204 and gate dielectric 114 .

[0074] In a further non-limiting aspect, exemplary substrate 102 can include silicon, sapphire, diamond, SiC, AlN, GaN, and the like. Additionally, exemplary nucleation layer 104 can include AlN, GaN, InN, and / or alloys thereof, among others. In a further non-limiting aspect, the exemplary buffer laye...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More