Gate structure and forming method thereof, semiconductor structure and forming method thereof

A gate structure and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as increased leakage current of MOS transistors, reduced reliability of gate oxide layers, and damage to gate oxide layers and polysilicon gates. , to reduce the gate leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

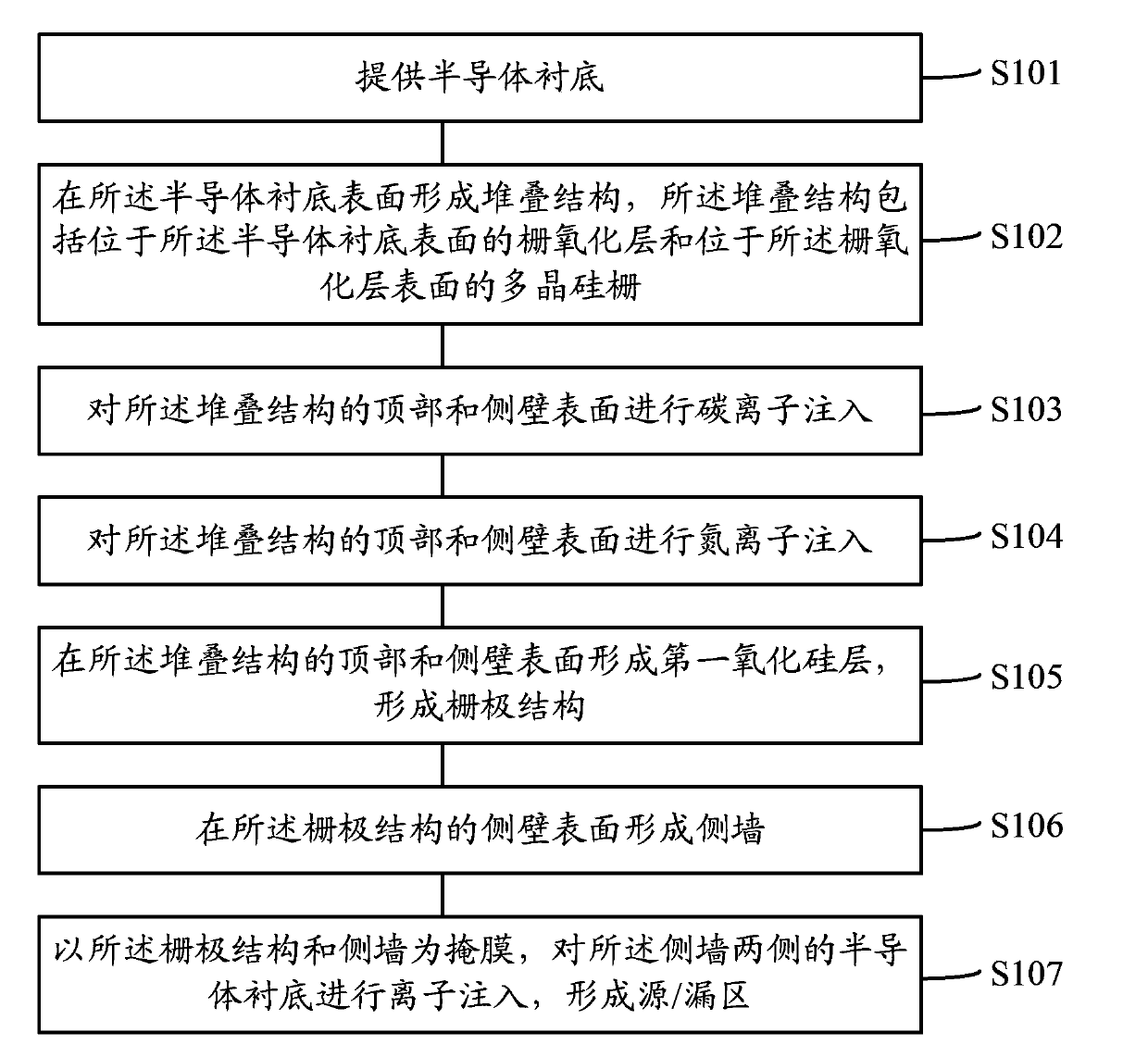

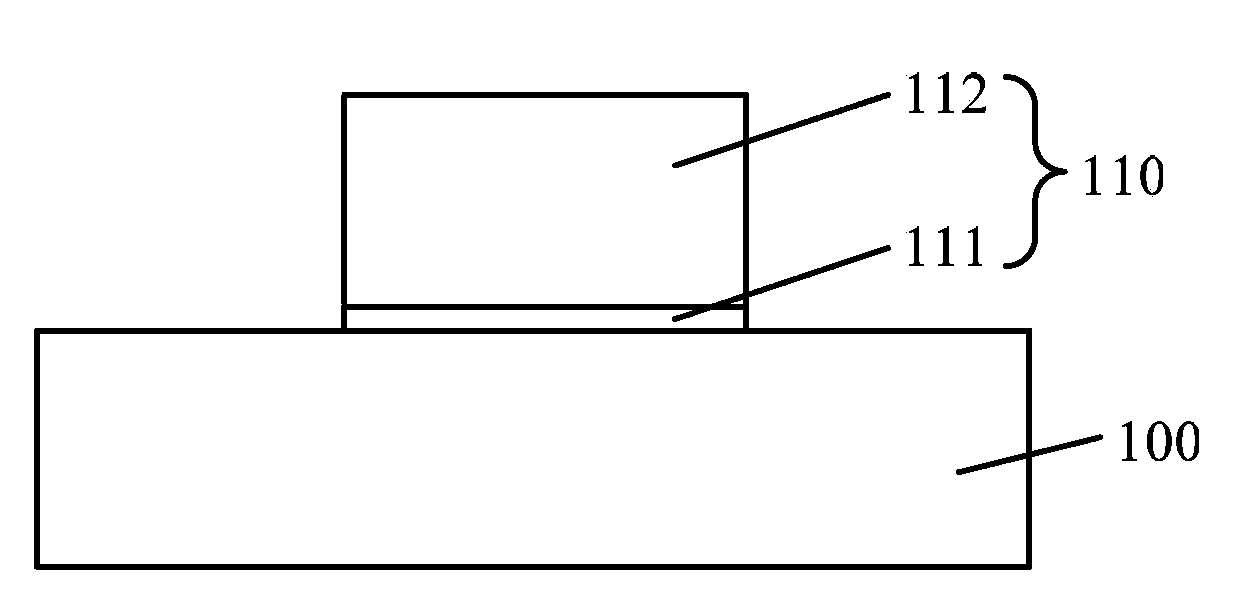

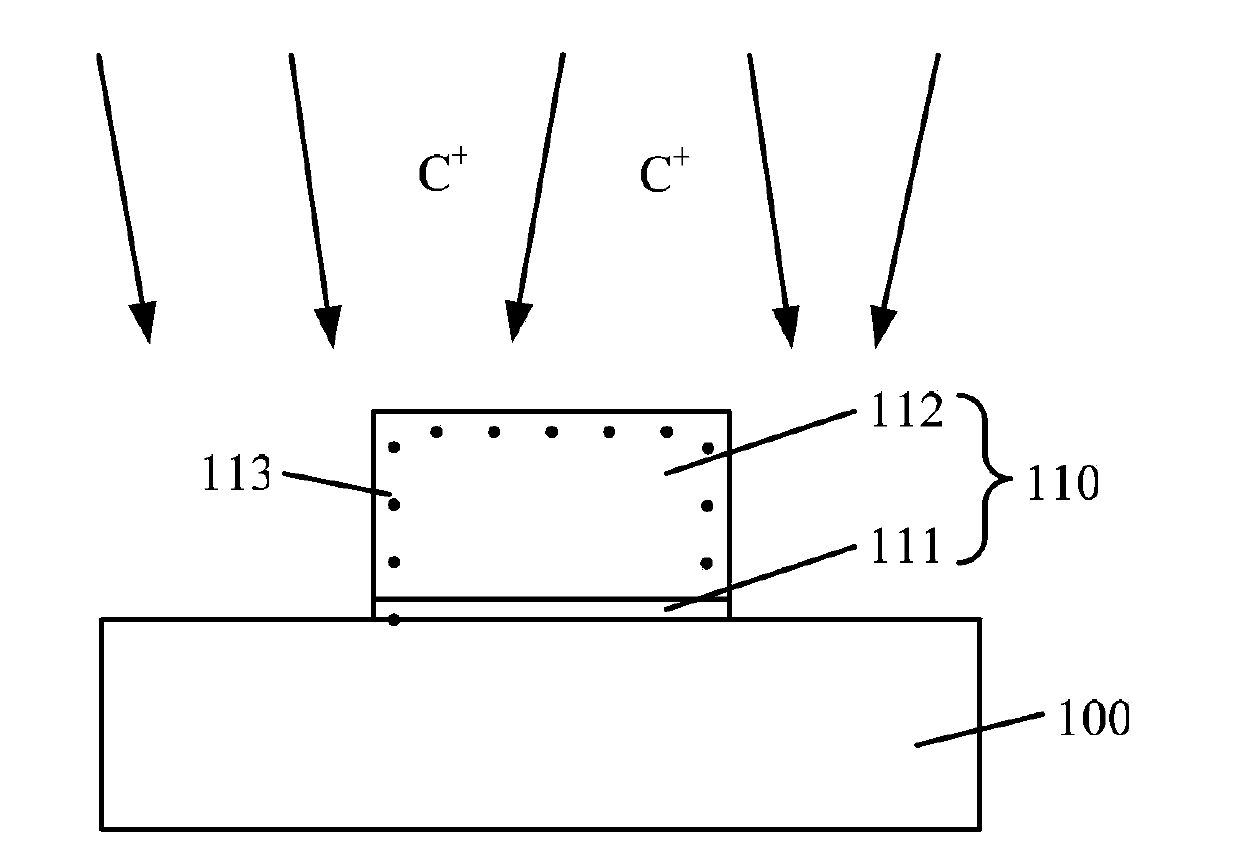

[0061] The inventor has found through research that in the prior art, as the operating frequency requirements of semiconductor devices are getting faster and the power consumption requirements are getting lower and lower, the polysilicon gates are usually doped with impurity ions, and the impurity ions are usually Boron ions or phosphorus ions are used to increase the mobility of carriers and reduce the resistance of the polysilicon gate. However, when the re-oxidation process forms a silicon oxide layer on the top and sidewall surfaces of the polysilicon gate structure, due to the strong mobility of boron ions or phosphorous ions, oxidation-enhanced diffusion (Oxidation Enhanced Diffusion, OED) Under the action of the boron ions or phosphorous ions, it is easy to diffuse to the silicon oxide layer and the gate oxide layer, so that the boron ions or phosphorous ions in the polysilicon gate near the silicon oxide layer and the gate oxide layer diffuse toward the oxide layer Dif...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More