Method for manufacturing transistor

A manufacturing method and transistor technology, which are applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of slow device response speed and high device power consumption of MOS transistors, reduce gate resistance, and improve response. The effect of speed and power consumption reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The response speed of the transistor manufactured by the existing method is relatively slow, and the power consumption of the device is large. After research by the inventors, it is found that because the gate resistance of the transistor manufactured in the prior art is too large, the response speed of the transistor is relatively slow, and the power consumption of the device is small.

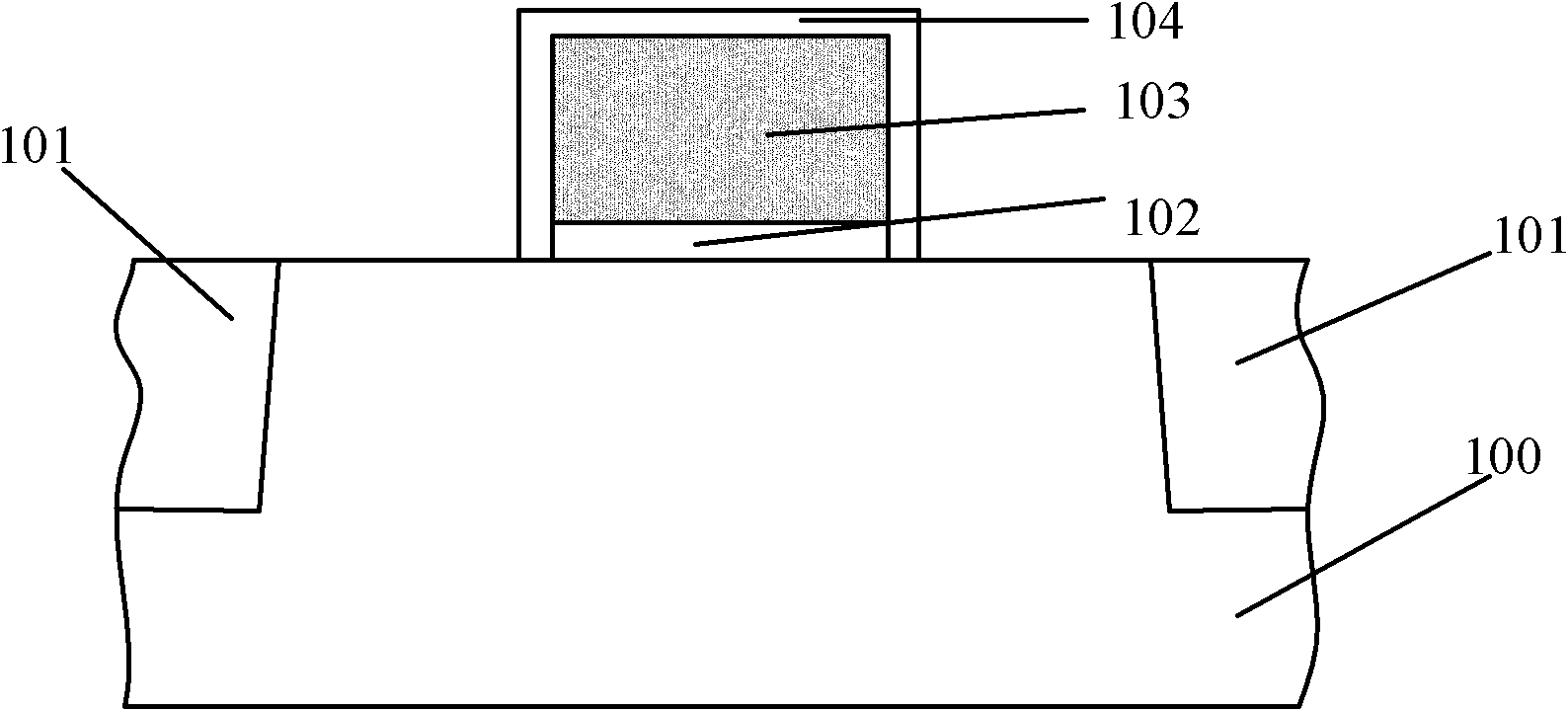

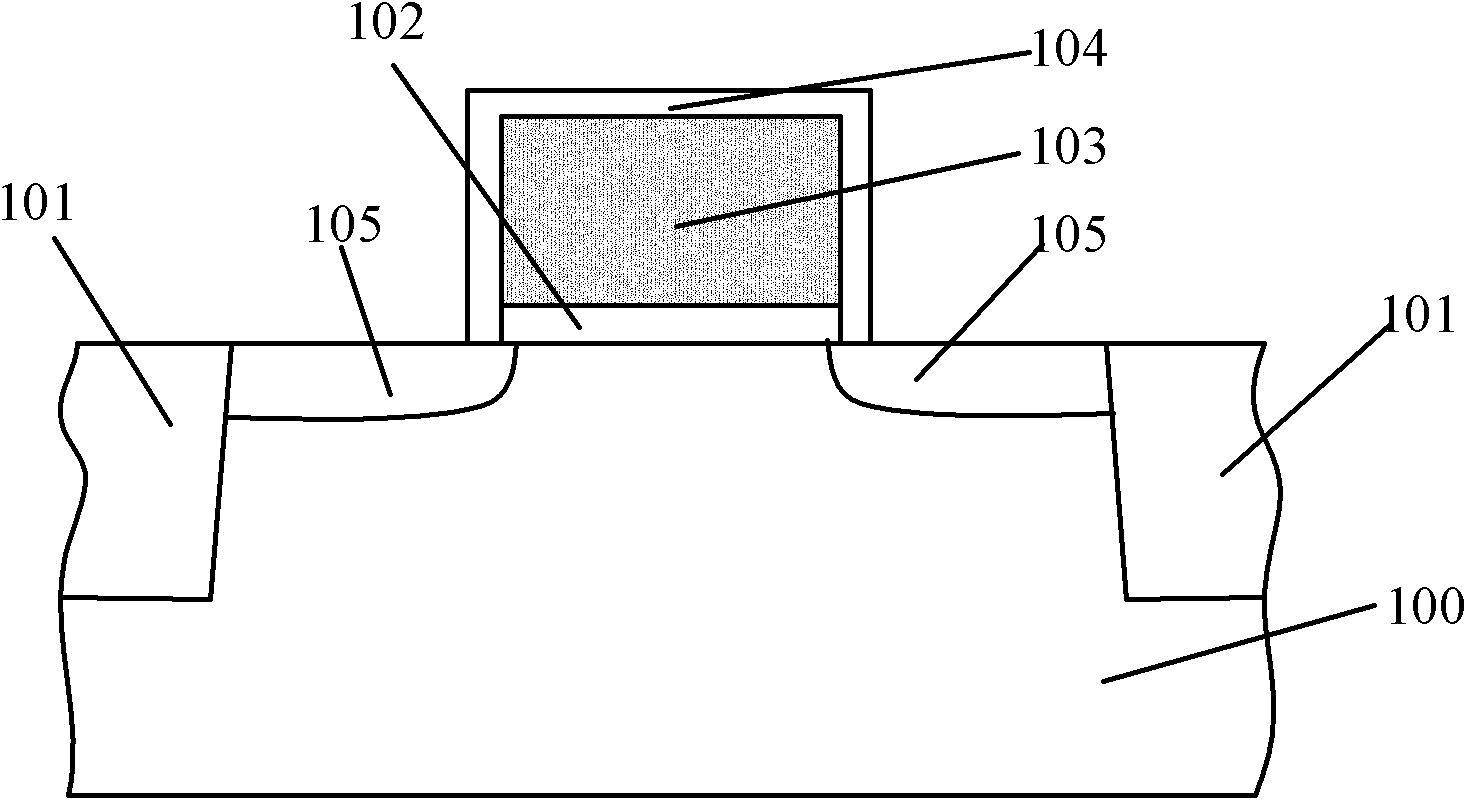

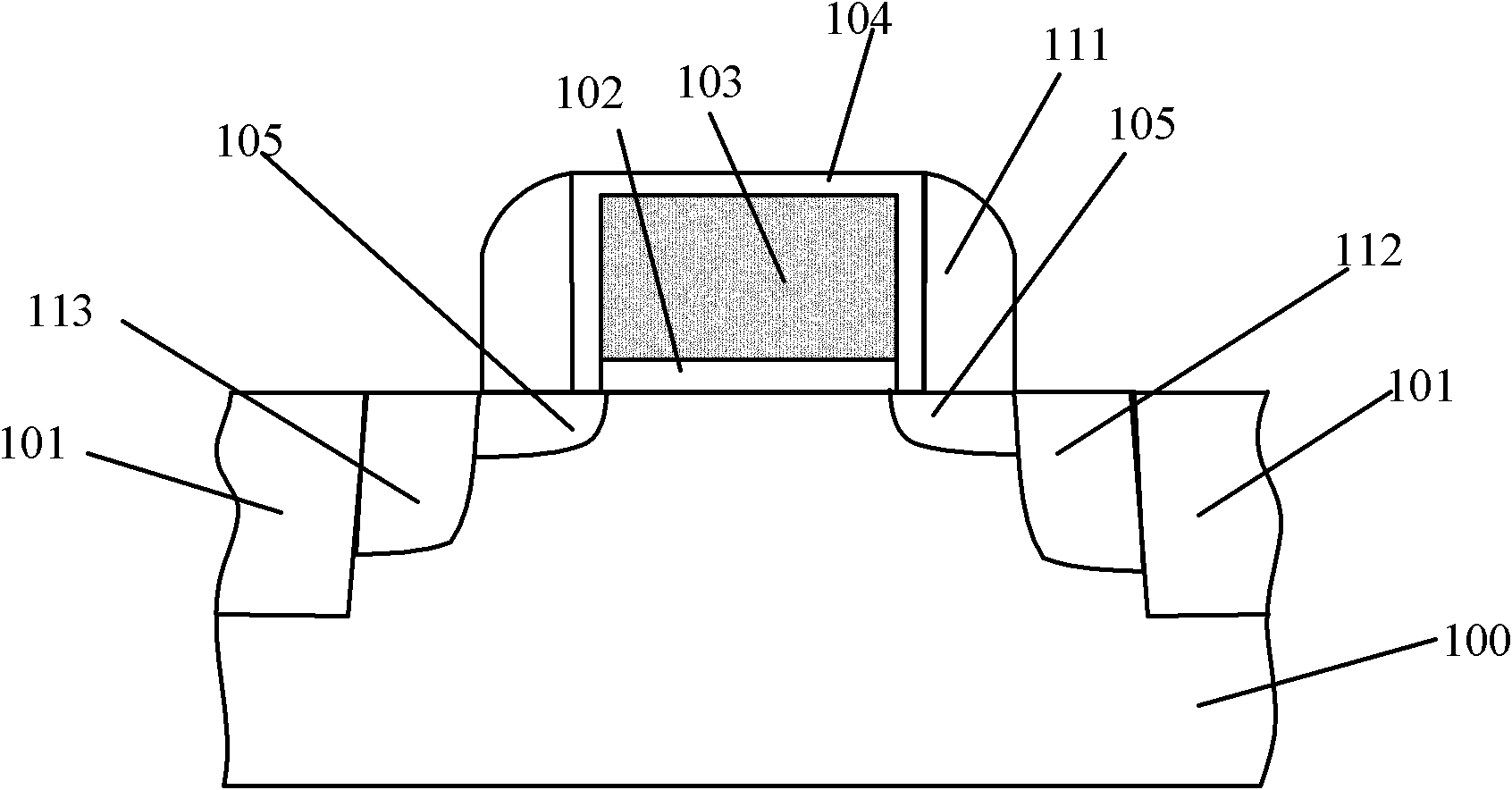

[0046] Specifically, refer to image 3 In the prior art, when ion implantation is performed to form the source region 112 and the drain region 113, ion implantation is also performed on the gate 103 to reduce the resistance of the gate 103, but the dose of the ion implantation is insufficient To reduce the resistance of the gate, it is necessary to adjust the parameters of dopant ion implantation in the gate 103 .

[0047]The inventors have also found that, as the size of the transistor decreases, the source region 112 and the drain region 113 are fabricated using an ultra-shallow jun...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More