JFET and manufacturing method thereof

A manufacturing method and deep well technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as increased leakage current, unadjustable structure, JFET burning, etc., to suppress gate leakage current and reduce current Density, the effect of increasing the process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment J

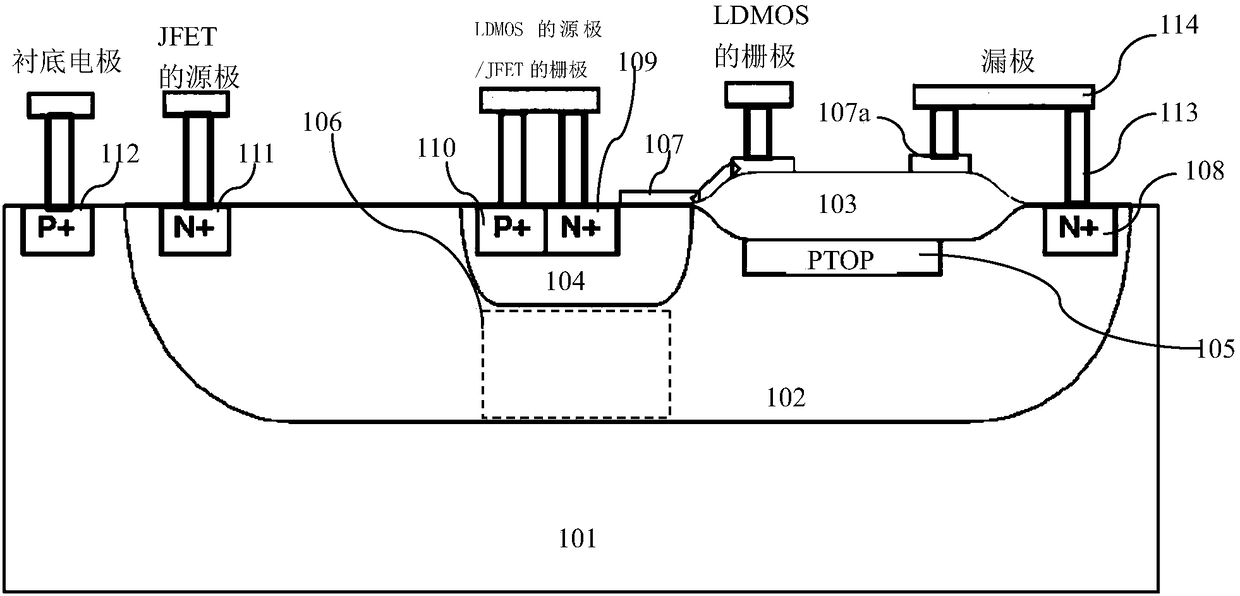

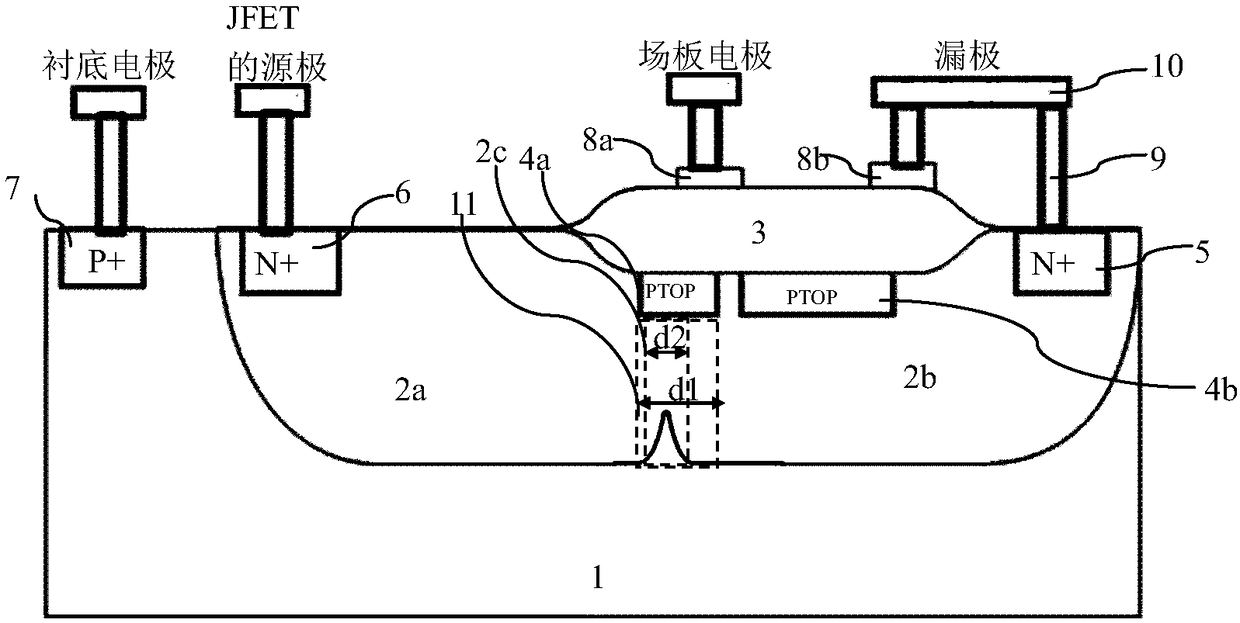

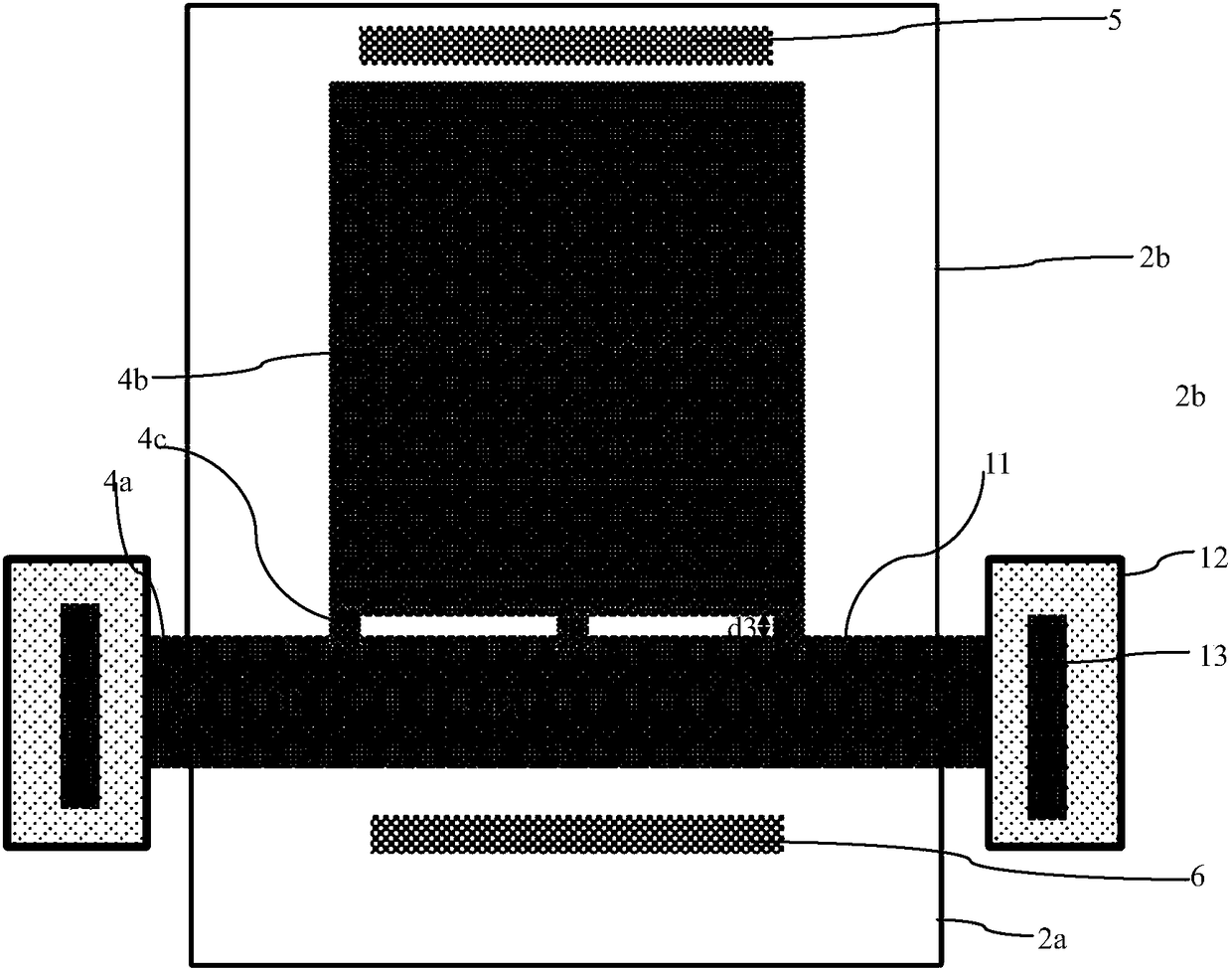

[0064] Such as Figure 2A Shown is the sectional view of JFET of the embodiment of the present invention; Figure 2B Shown is the layout of the JFET of the embodiment of the present invention; the JFET of the embodiment of the present invention includes:

[0065] An N-type deep well is formed on a P-type doped semiconductor substrate 1. The N-type deep well is formed by laterally splicing a first deep well segment 2a and a second deep well segment 2b. The first deep well segment 2a There is a gap with the implanted region of the second deep well segment 2b and is formed simultaneously by the same process, and the implanted gap regions of the first deep well segment 2a and the second deep well segment 2b form the channel resistance of the JFET Regulation area 2c.

[0066] A drift region field oxygen 3 is formed in the surface region of the N-type deep well, and a P-type top layer structure is formed on the surface of the N-type deep well at the bottom of the drift region fiel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More