Ferroelectric field effect transistor based on alumina material with embedded nanocrystalline and preparation method thereof

An electric field effect, alumina technology, applied in the field of large-scale integrated circuits and field effect transistors, can solve the problems of unstable device operation, cross-contamination between ferroelectric thin films and silicon integrated circuits, etc., to improve device performance, avoid cross-contamination, The effect of reducing gate leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

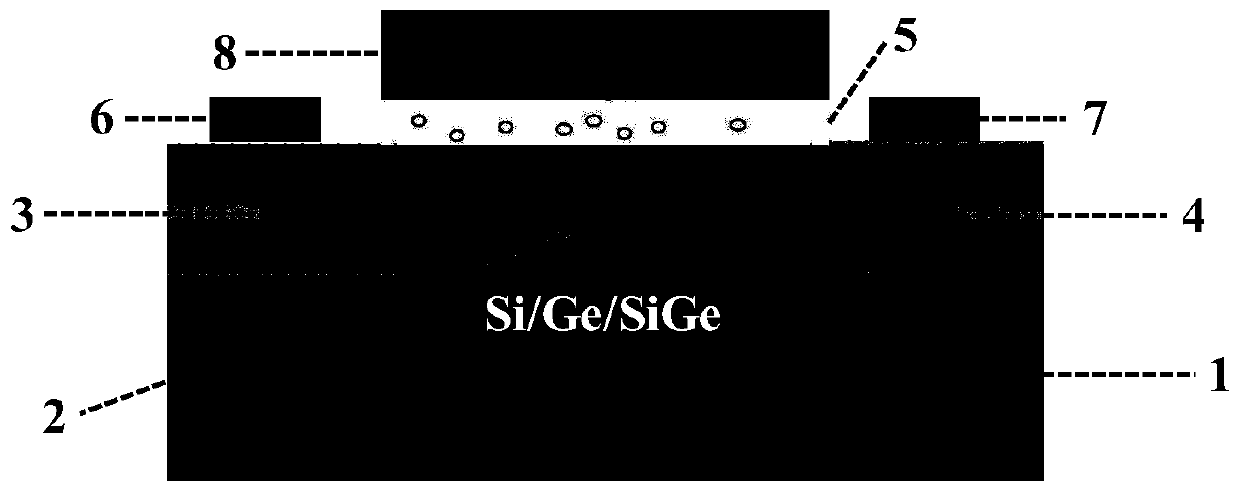

[0030] Embodiment 1: A p-type ferroelectric field effect transistor based on aluminum oxide material embedded with nanocrystals is prepared on a Ge substrate.

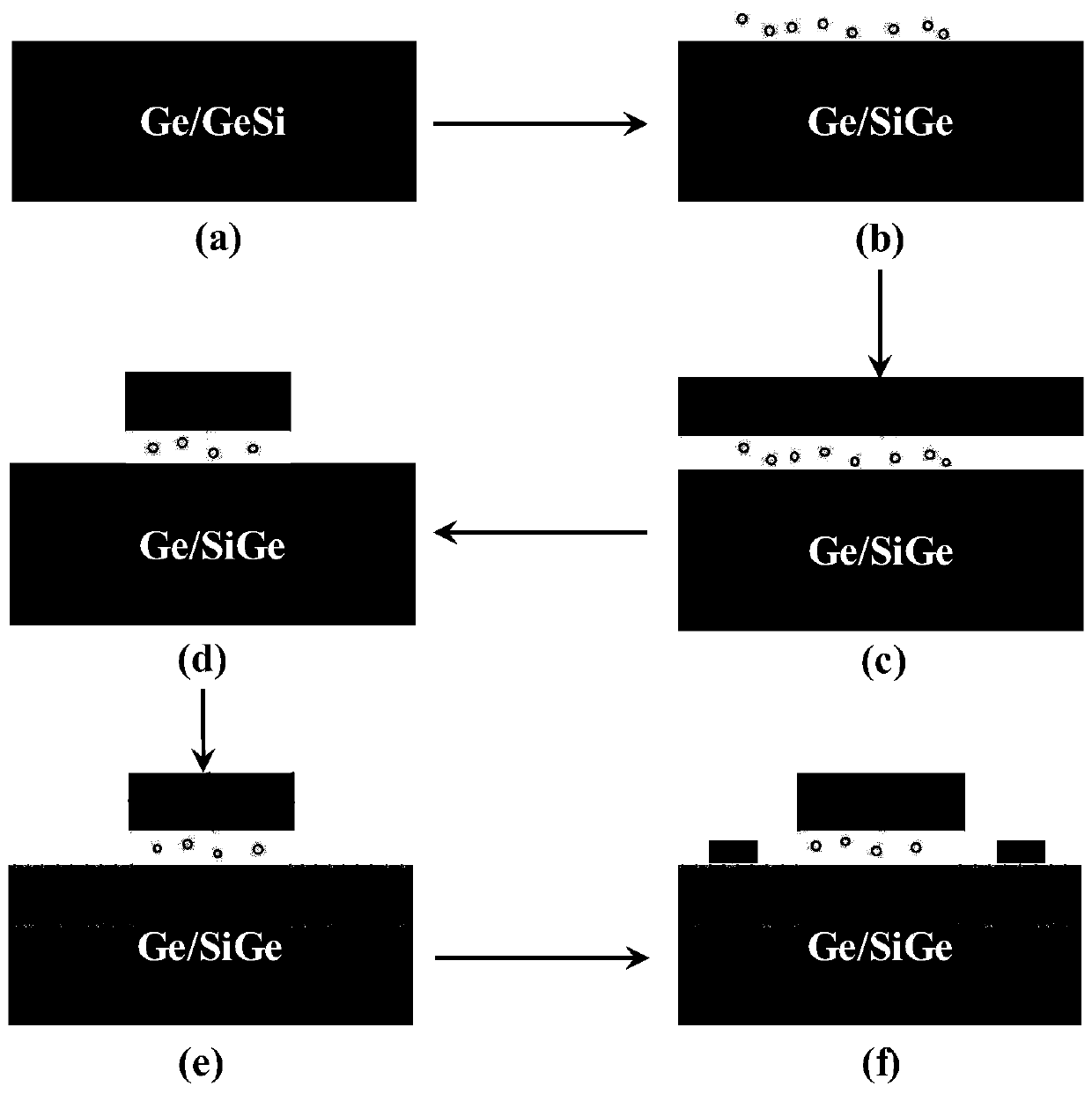

[0031] refer to figure 2 , the implementation steps of this example are as follows:

[0032] Step A: forming an aluminum oxide material embedded nanocrystalline ferroelectric thin film gate dielectric layer, such as figure 2 b.

[0033] A1) Standard cleaning of Ge substrates:

[0034] a1) Put the substrate into acetone, isopropanol and deionized water in sequence, and sonicate for 10 minutes each;

[0035] a2) Soak the substrate after ultrasonication in a mixed solution of hydrofluoric acid and water at a ratio of 1:50 for 1 min, and then rinse with deionized water for 2 min to complete the standard cleaning of the Ge substrate;

[0036] A2) Deposit aluminum oxide material with embedded nanocrystalline ferroelectric thin film gate dielectric layer:

[0037] Using atomic layer deposition technology, solid tetraki...

Embodiment 2

[0051] Example 2: On Si 0.55 Ge 0.45 A p-type ferroelectric field effect transistor embedded with nanocrystals in alumina material is prepared on a substrate.

[0052] refer to figure 2 , the specific implementation of this example is as follows:

[0053] Step 1: Forming an aluminum oxide material embedded nanocrystalline ferroelectric thin film gate dielectric layer, such as figure 2 b.

[0054] 1.1) Standard cleaning Si 0.55 Ge 0.45 Substrate:

[0055] 1.1.1) The specific realization of this step is the same as a1) in step A of embodiment 1;

[0056] 1.1.2) Soak the substrate after ultrasonication in a mixed solution of concentrated sulfuric acid and hydrogen peroxide at a ratio of 3:1 for 20 minutes;

[0057] 1.1.3) The specific realization of this step is the same as a2) in step A of embodiment 1;

[0058] 1.2) Deposit alumina material with embedded nanocrystalline ferroelectric thin film gate dielectric layer:

[0059] Using atomic layer deposition technology,...

Embodiment 3

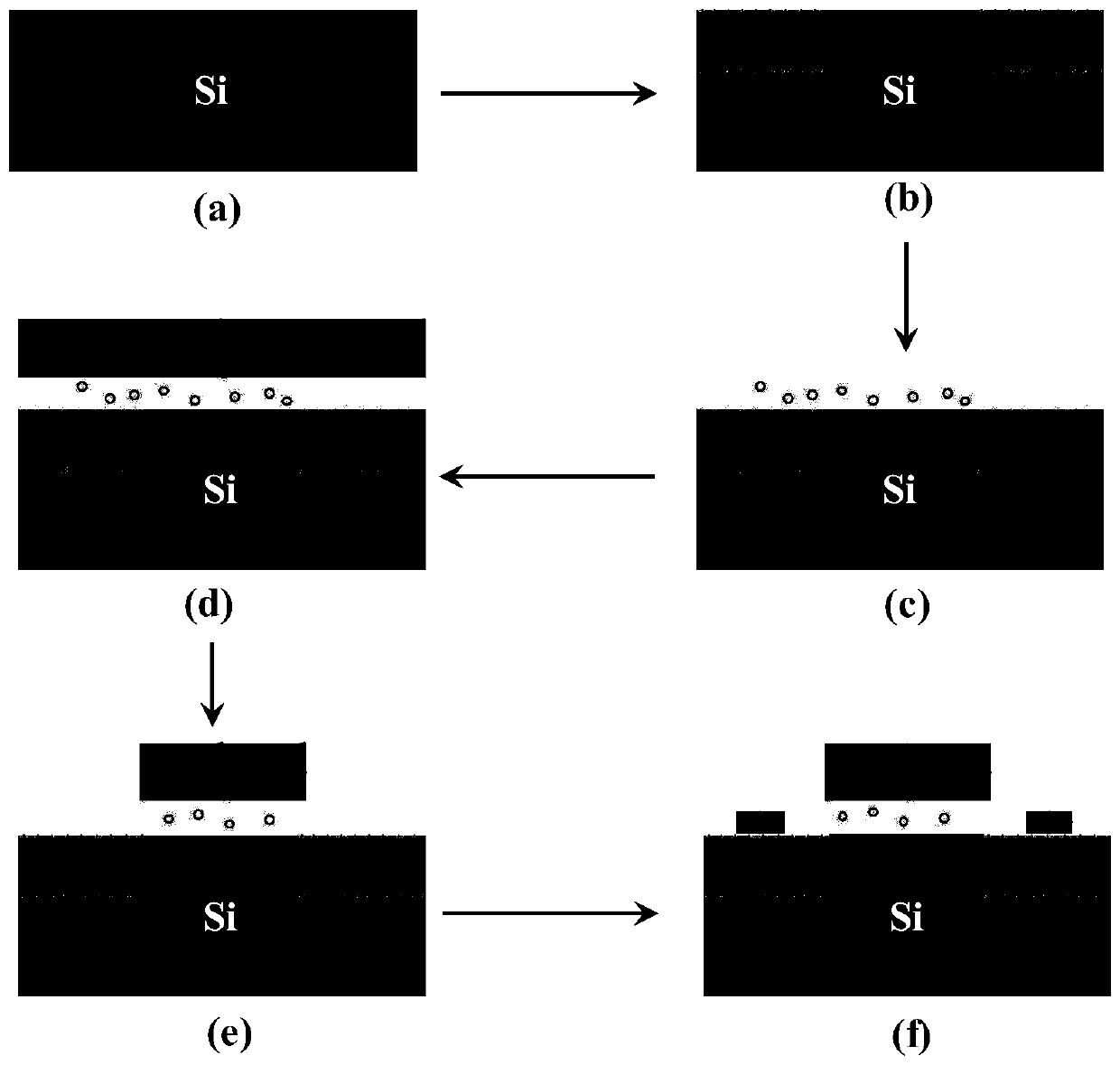

[0072] Embodiment 3: An n-type ferroelectric field effect transistor based on aluminum oxide material embedded with nanocrystals is prepared on a Si substrate.

[0073] refer to image 3 , the implementation steps of this embodiment are as follows:

[0074] Step 1: standard cleaning of the Si substrate, the specific implementation of this step is the same as that of step 1.1) of Embodiment 2.

[0075] The second step: mark the substrate area on the Si substrate.

[0076] Using 365nm I-line photolithography process, mark the source region, gate region, and drain region on the Si substrate, where the gate region is located in the center of the Si substrate, and the source region and drain region are respectively located at the center of the gate region. sides.

[0077] Step 3: Forming source and drain regions, such as image 3 b.

[0078] Under the masking effect of photoresist, ion implantation is performed on the source region and drain region after photolithography:

[...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More