Semiconductor device and formation method thereof

A semiconductor and device technology, applied in the field of semiconductor devices and their formation, can solve problems such as poor performance of MOS transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] As the feature size is further reduced, the performance of semiconductor devices formed in the prior art is poor.

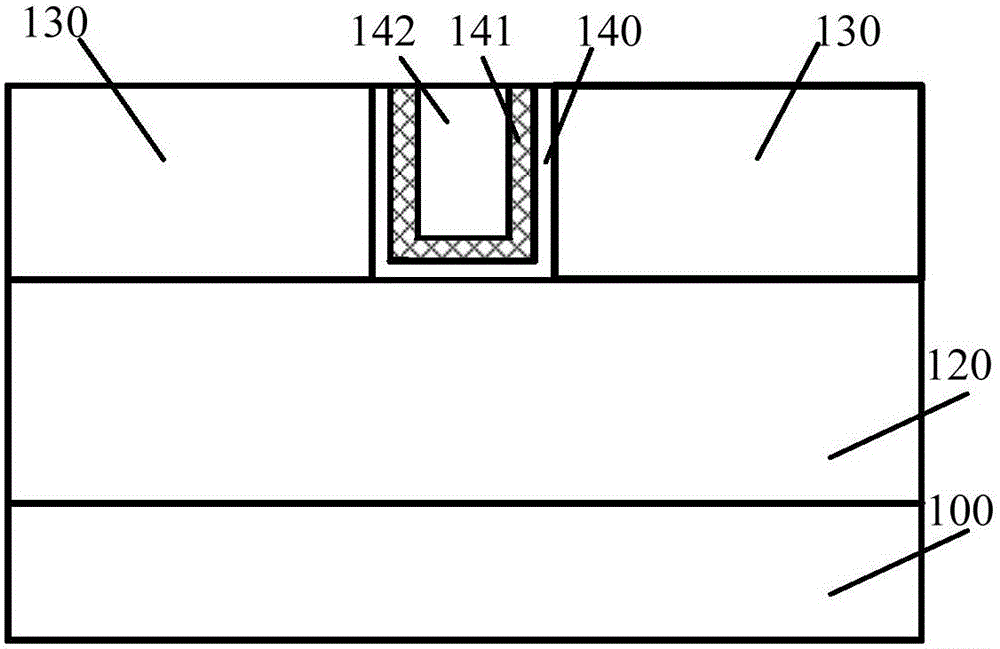

[0036] Figure 1 to Figure 3 It is a structural schematic diagram of the formation process of a semiconductor device in an embodiment of the present invention.

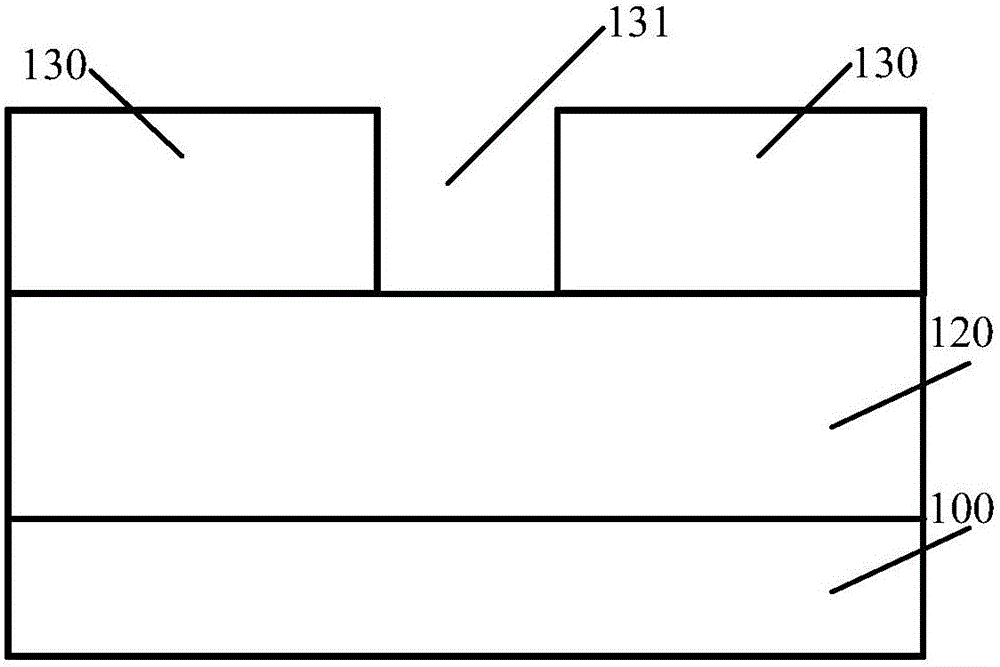

[0037] refer to figure 1 , providing a base, the base includes a substrate 100 and a fin 120 located on the surface of the substrate 100; an interlayer dielectric layer 130 is formed on the surface of the base, and a groove 131 is formed in the interlayer dielectric layer 130, so The groove 131 exposes the top surface and the sidewall of the fin 120 .

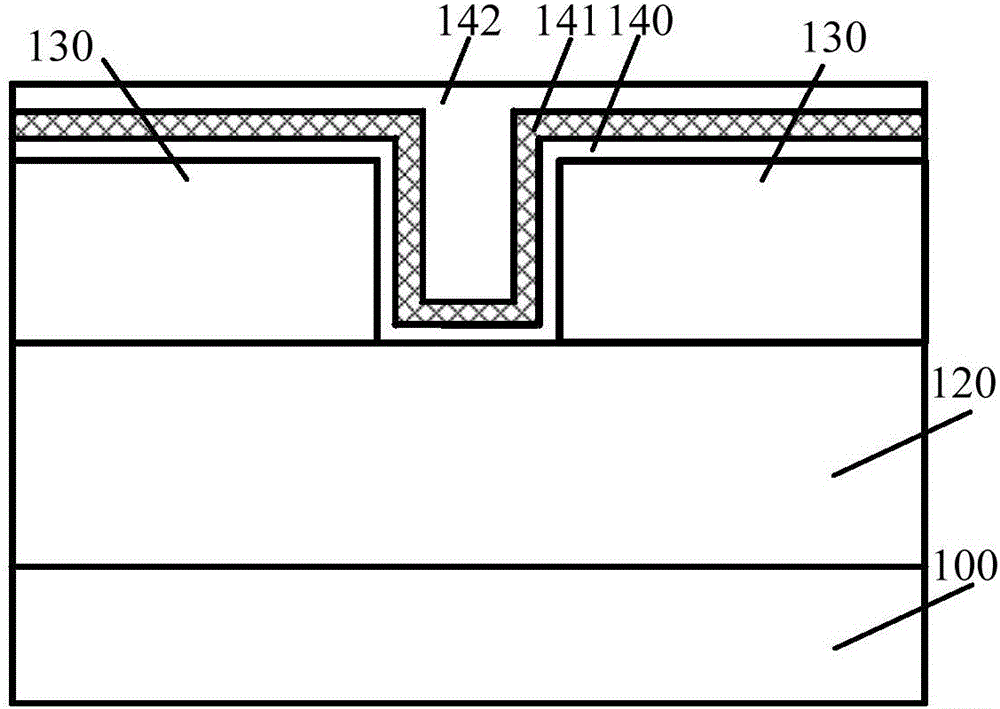

[0038] refer to figure 2 , formed to cover the groove 131 (refer to figure 1 ) a gate dielectric layer 140 at the bottom and sidewalls; forming a barrier layer 141 covering the gate dielectric layer 140; forming a metal layer 142 covering the barrier layer 141, the entire surface of the metal layer 142 being higher than the interlayer dielect...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More