Adjusting device and method for flash memory array after erasion

A flash memory array and adjustment device technology, applied in information storage, static memory, read-only memory, etc., can solve problems affecting the reliability of storage unit A, abnormal critical voltage offset, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

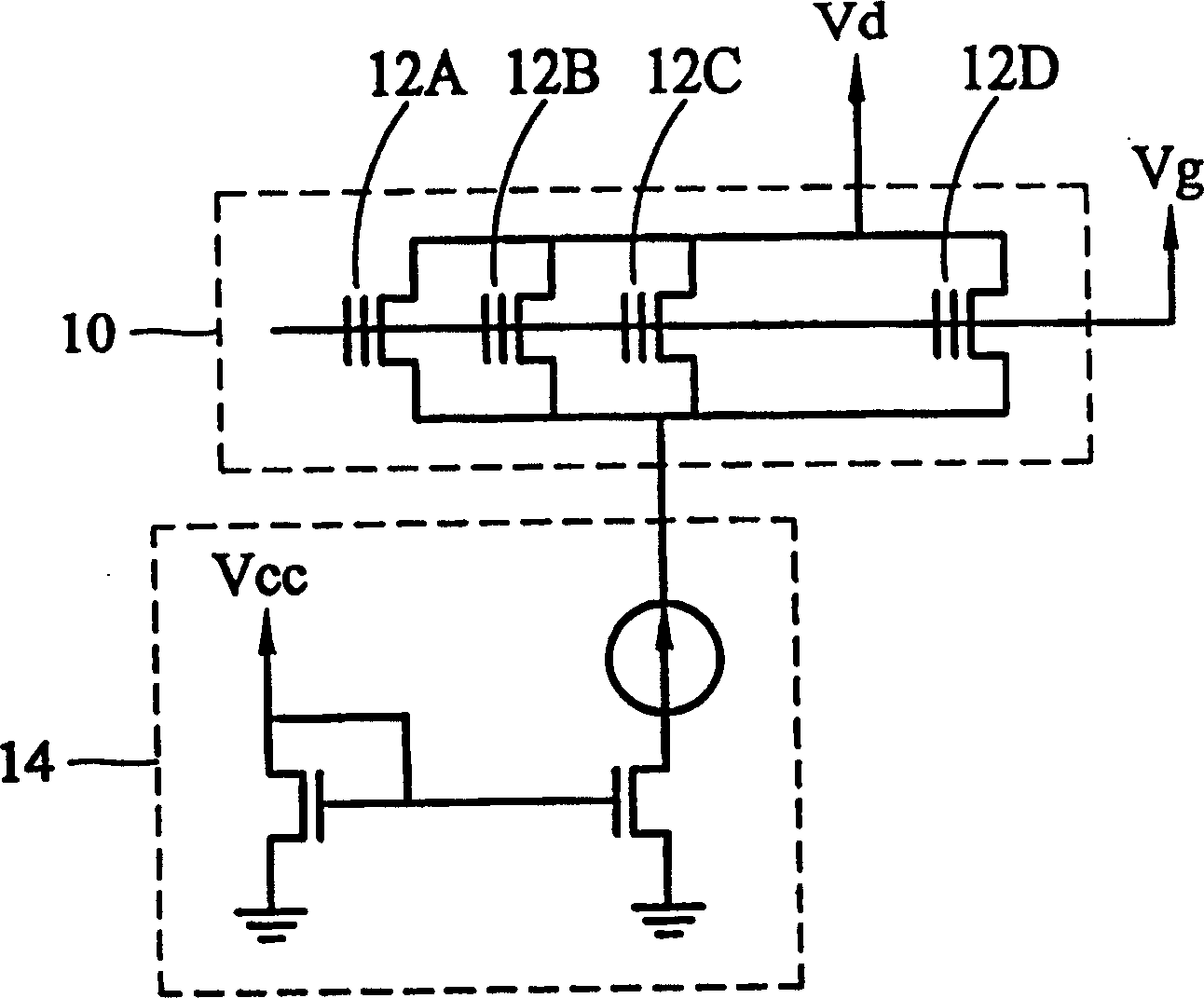

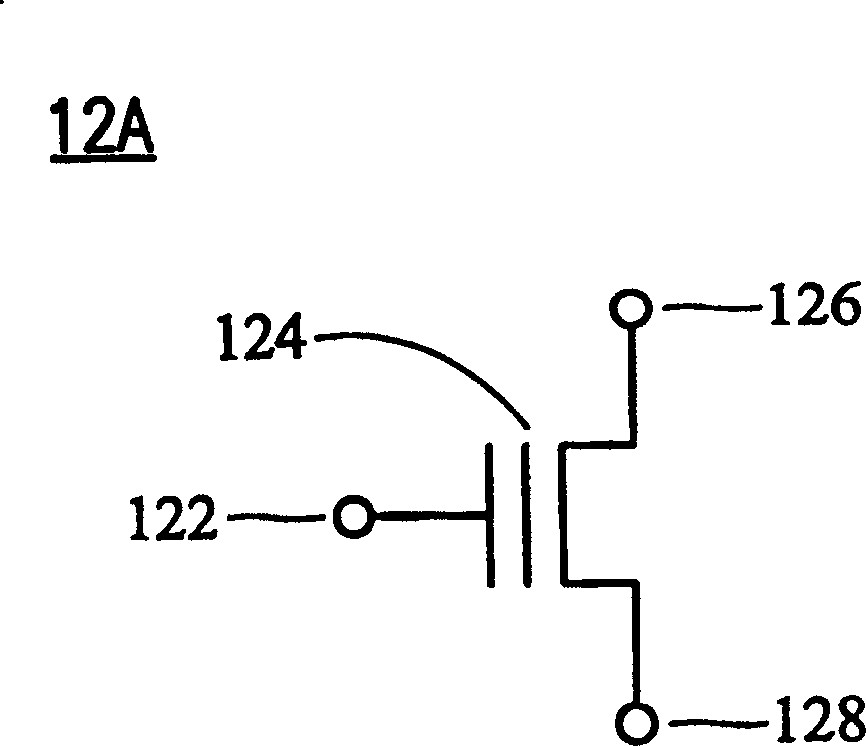

[0022] Figure 5 It is a schematic circuit diagram of post-erasing processing of a flash memory array according to an embodiment of the present invention. Wherein, the storage array 20 has a plurality of storage units 22A, 22B, 22C, and 22D, where a flash memory unit is taken as an example. The structure and structure represented by each part of the flash memory unit 22A, 22B, 22C, 22D in the circuit symbol figure 2 are the same and will not be repeated here. The flash memory cell 22A has a control gate 122 , a floating gate 124 , a drain 126 and a source 128 .

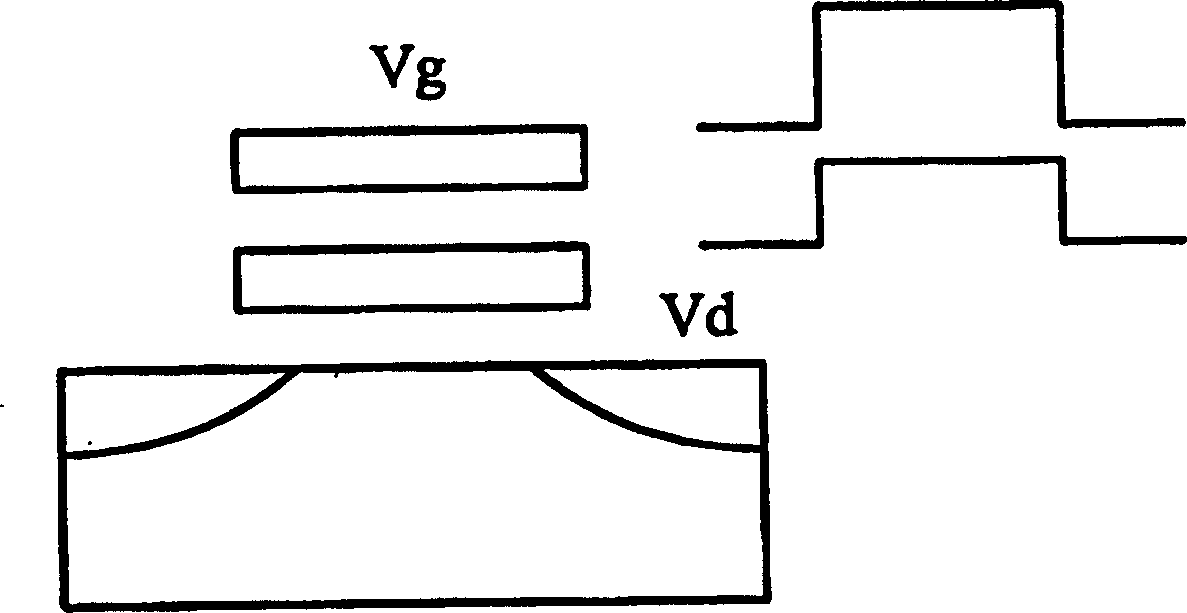

[0023] The drain voltage supplied by the drain power supply device 24 to the flash memory units 22A, 22B, 22C, and 22D ranges from 2.5V to 5V, and the source is coupled to a constant current supplier 26 for receiving a current of about 100uA to 2mA. , the current intensity depends on different post-erase processing requirements. In addition, the control gate of the flash memory unit according to the embodiment of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More