Semiconductor structure and formation method thereof

A semiconductor and patterning technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as the inability to control the threshold voltage of fin field effect transistors, and achieve improved short-channel effects and increased channel lengths , the effect of high channel length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] As mentioned in the background, the multi-gate transistor formed in the prior art cannot adjust the threshold voltage of the transistor by applying a bias voltage.

[0035] In the embodiment of the present invention, while forming a transistor with a multi-gate structure, a back gate is formed on the other side of the channel layer, so that a bias voltage can be applied to the channel layer through the back gate, thereby adjusting the threshold voltage of the transistor .

[0036] In order to make the above objects, features and advantages of the present invention more comprehensible, specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

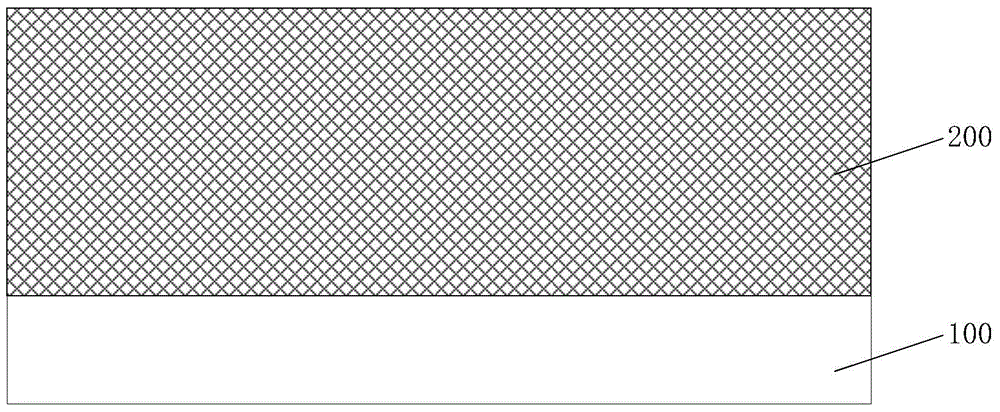

[0037] Please refer to image 3 1. A substrate 100 is provided, and a gate material layer 200 is formed on the surface of the substrate 100 .

[0038] The material of the substrate 100 includes semiconductor materials such as silicon, germanium, silicon germani...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More