Patents

Literature

49results about How to "Drain current increases" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

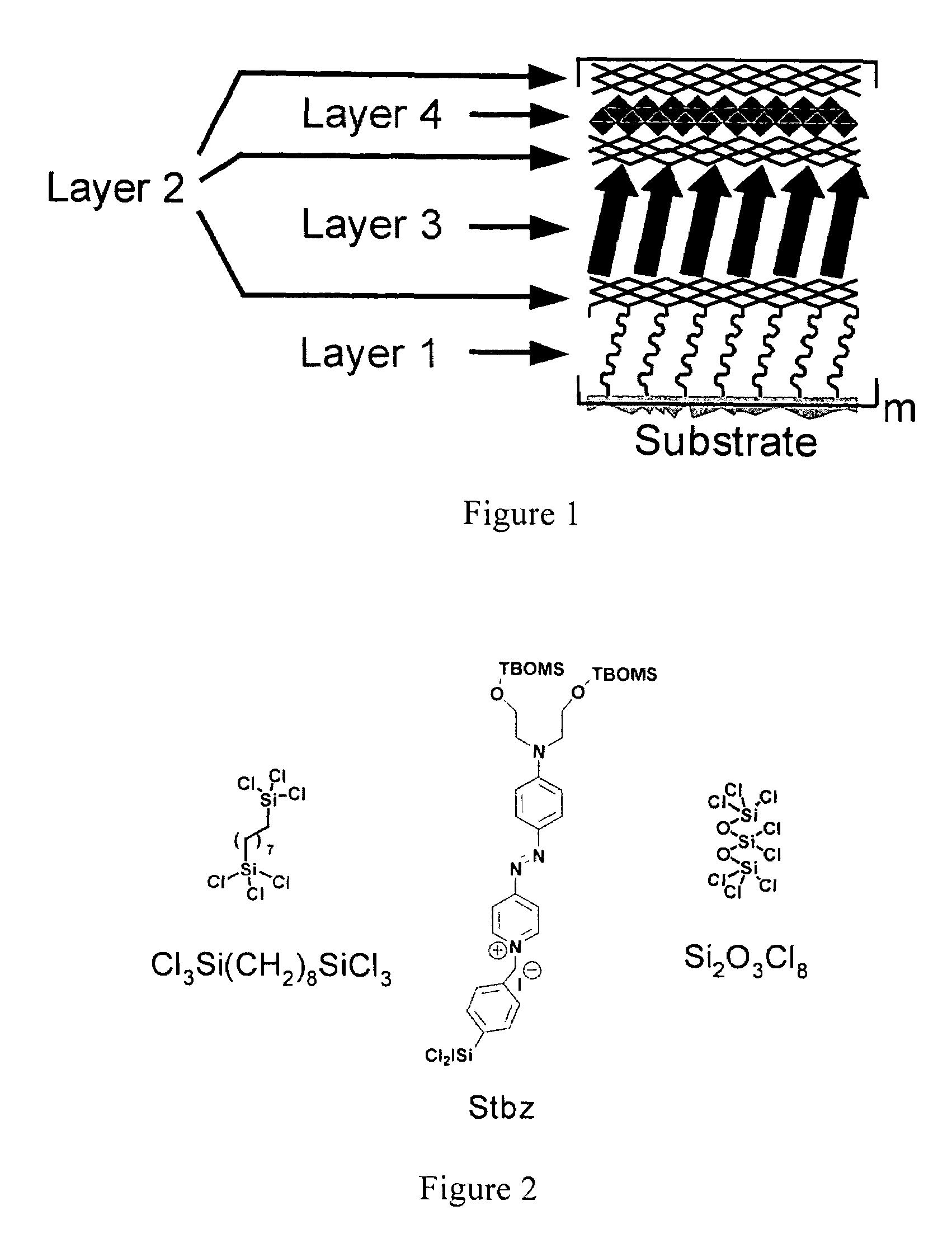

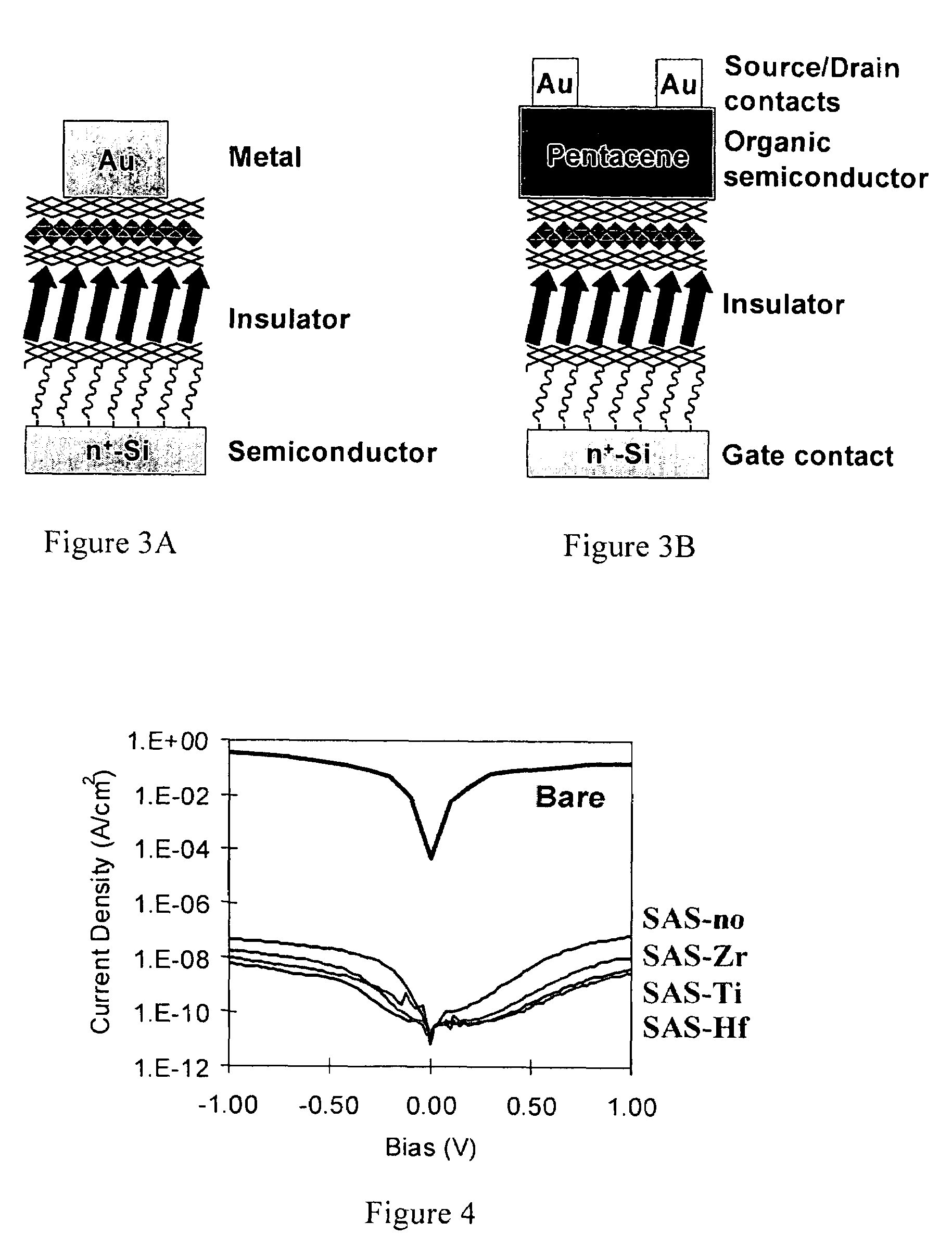

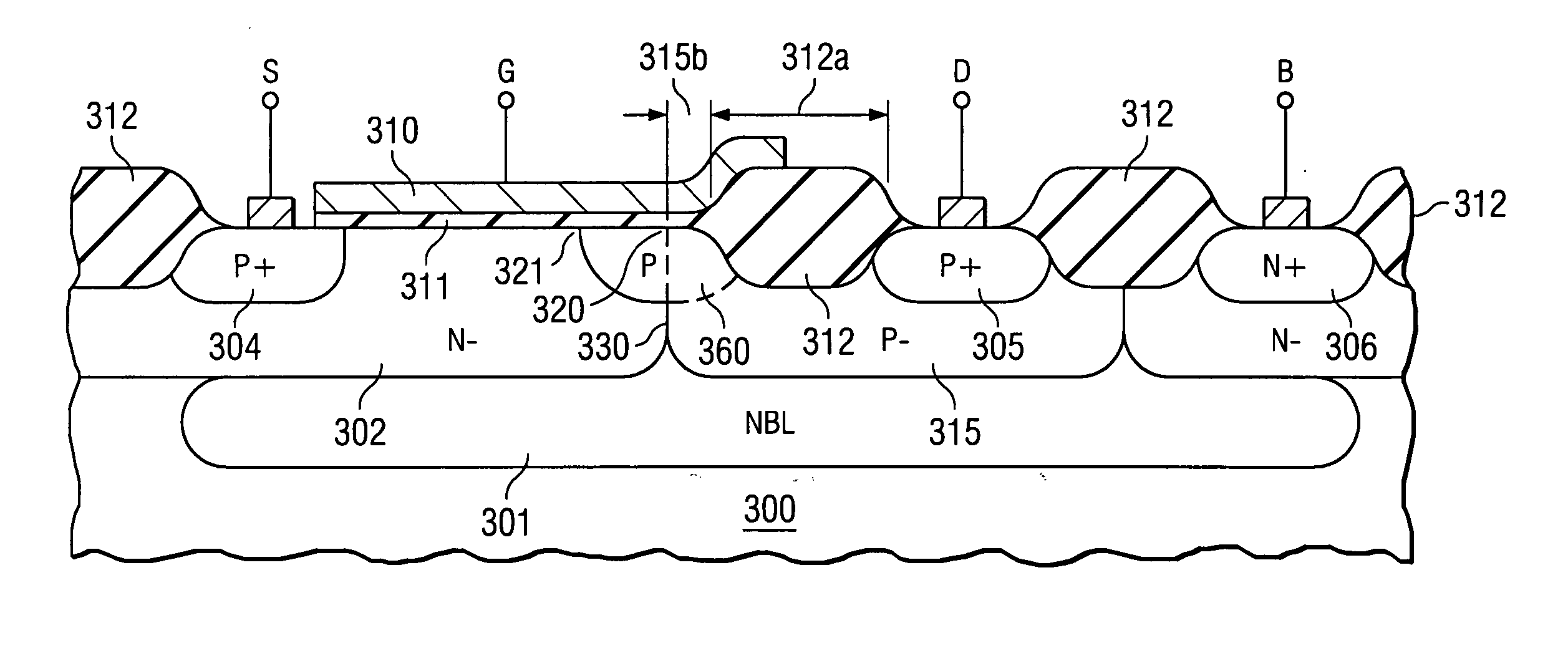

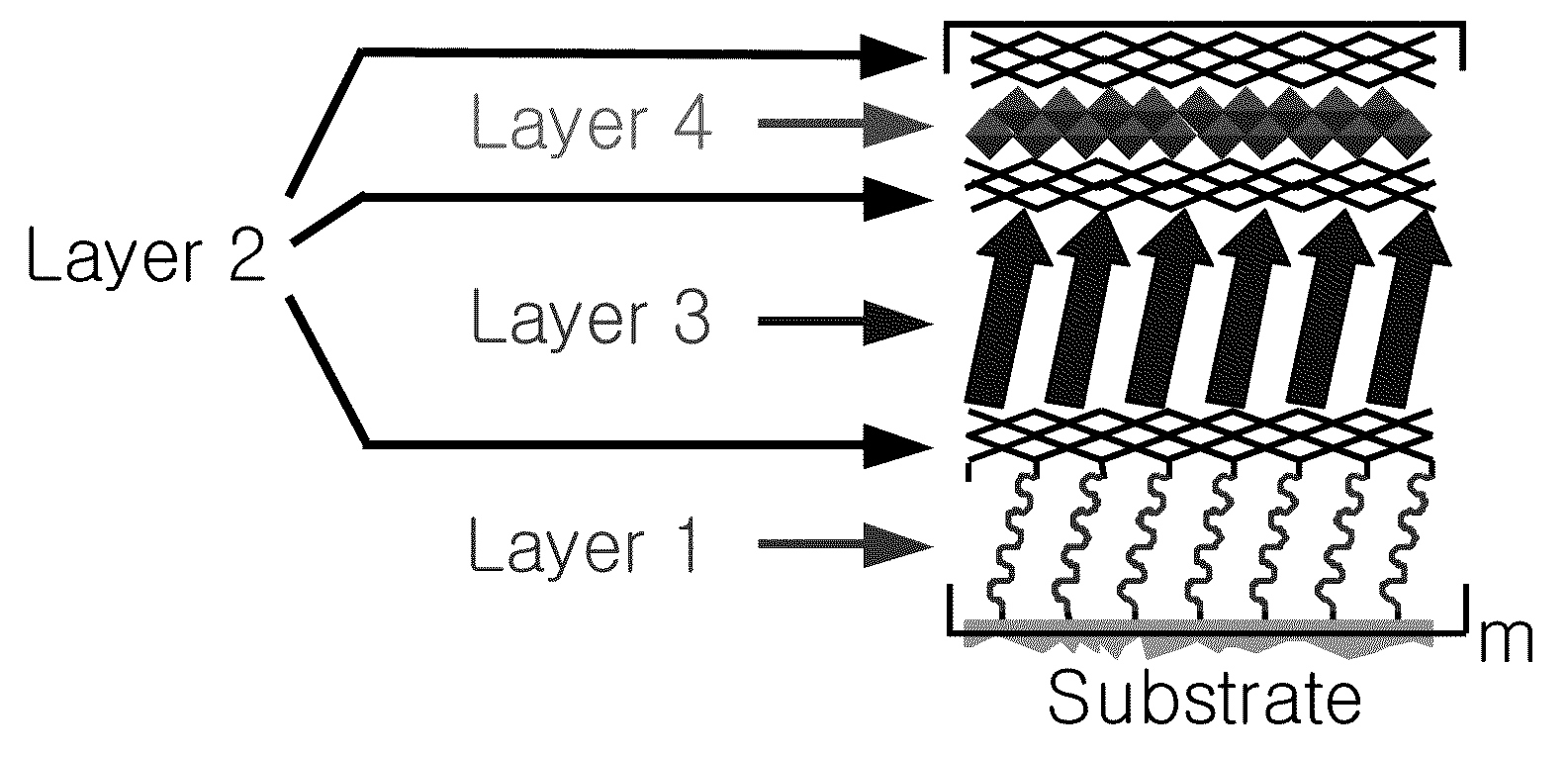

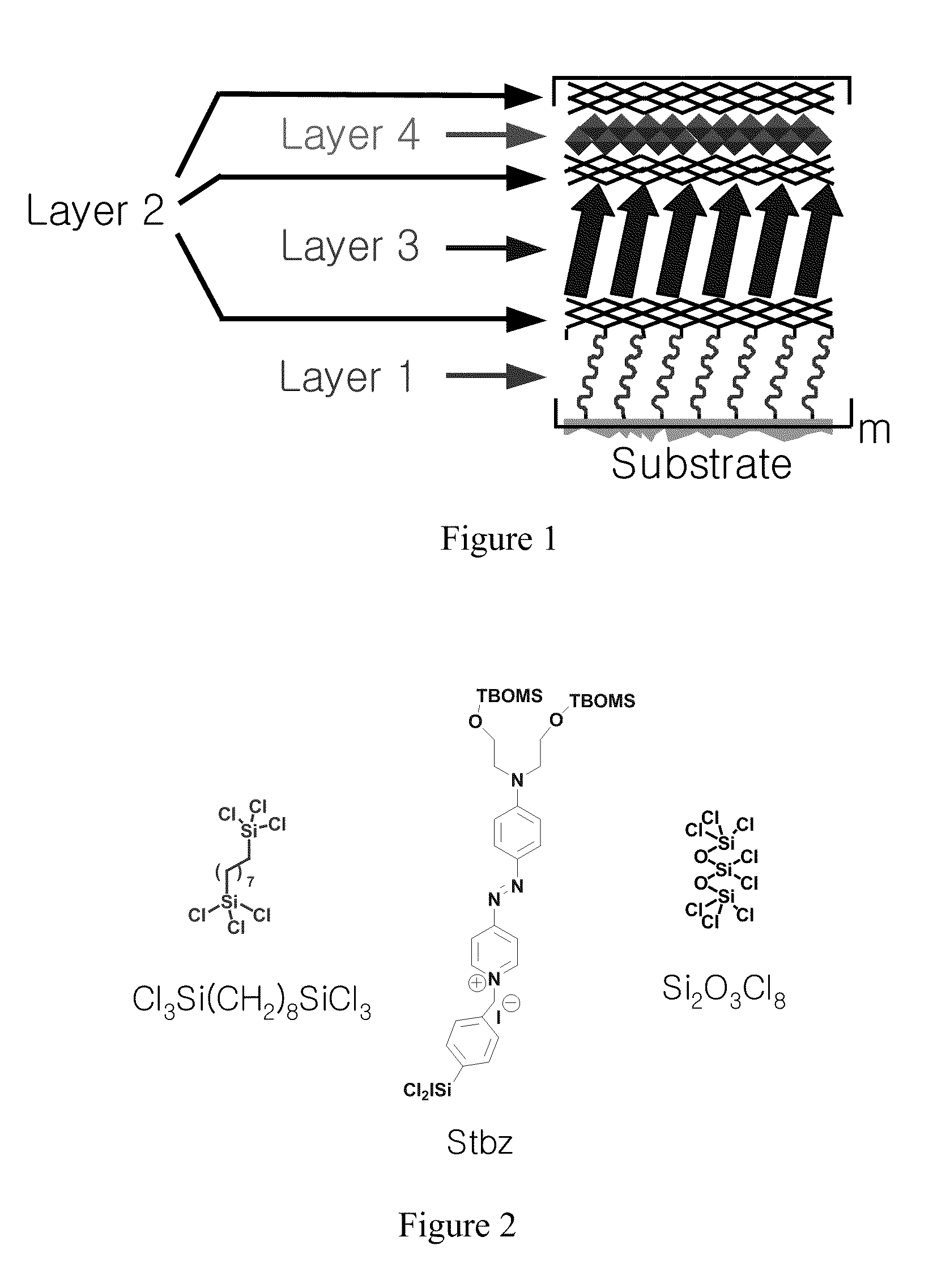

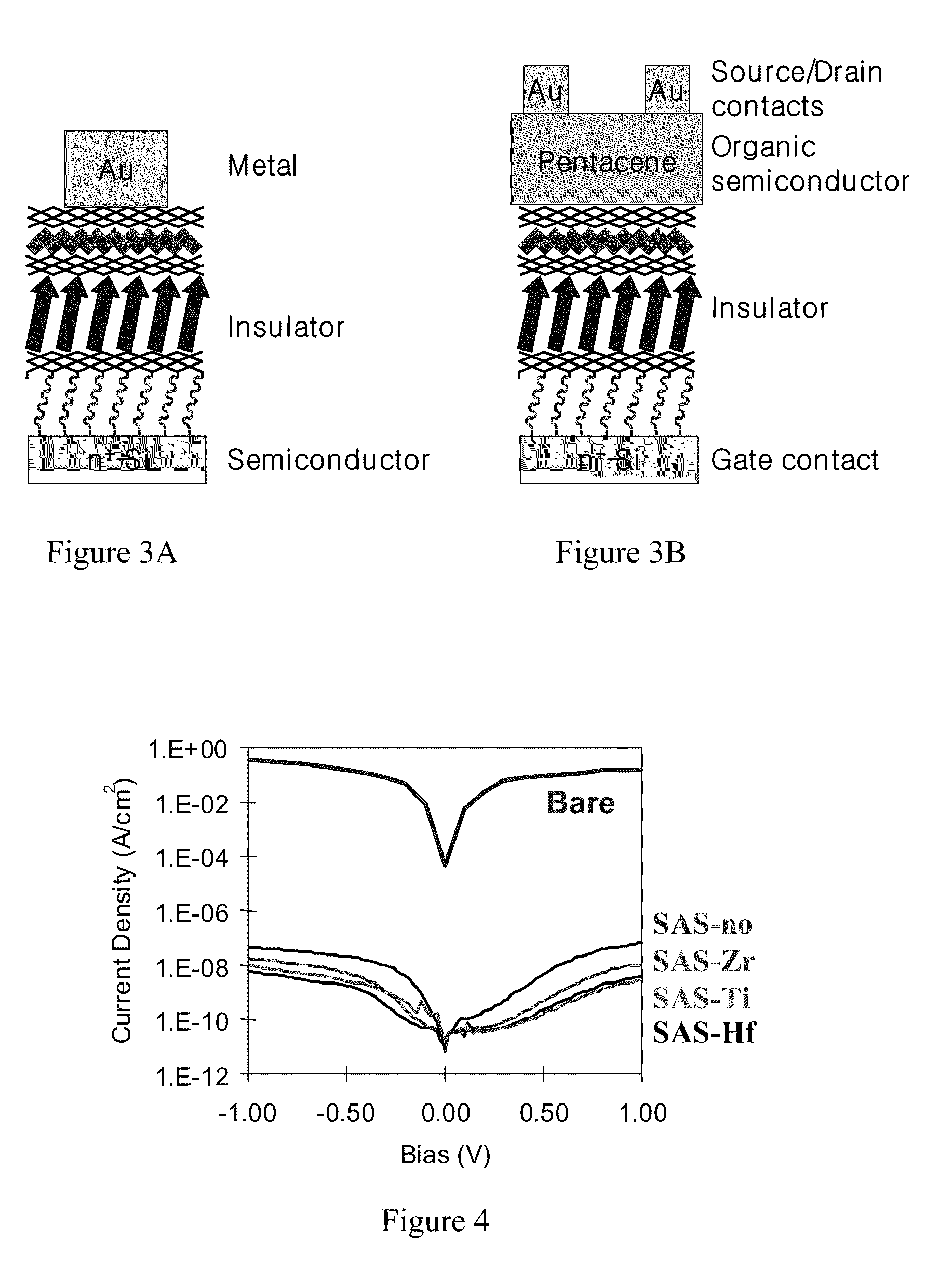

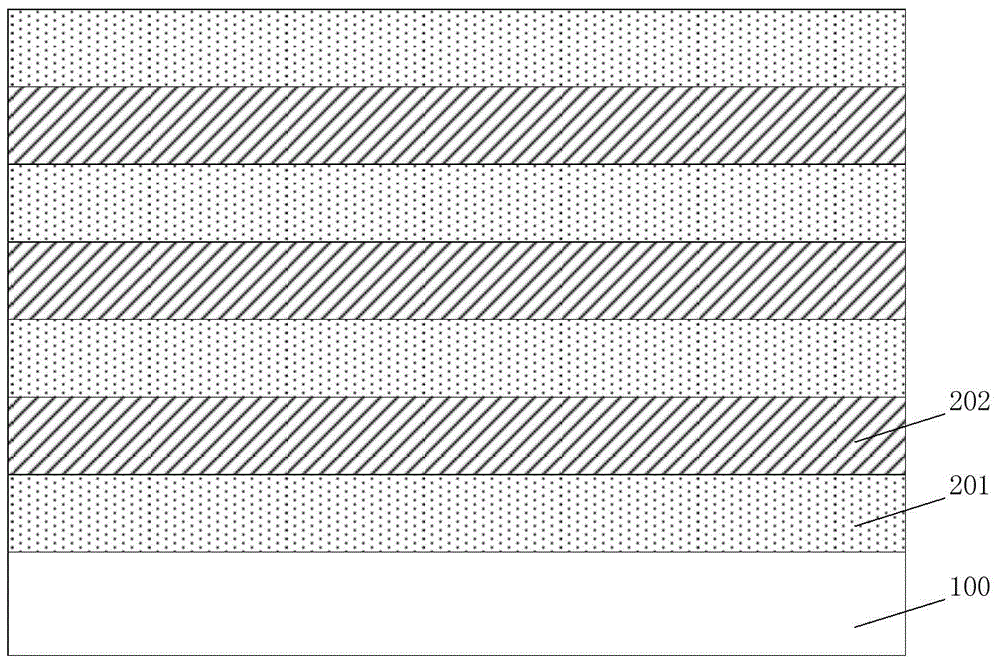

Intercalated superlattice compositions and related methods for modulating dielectric property

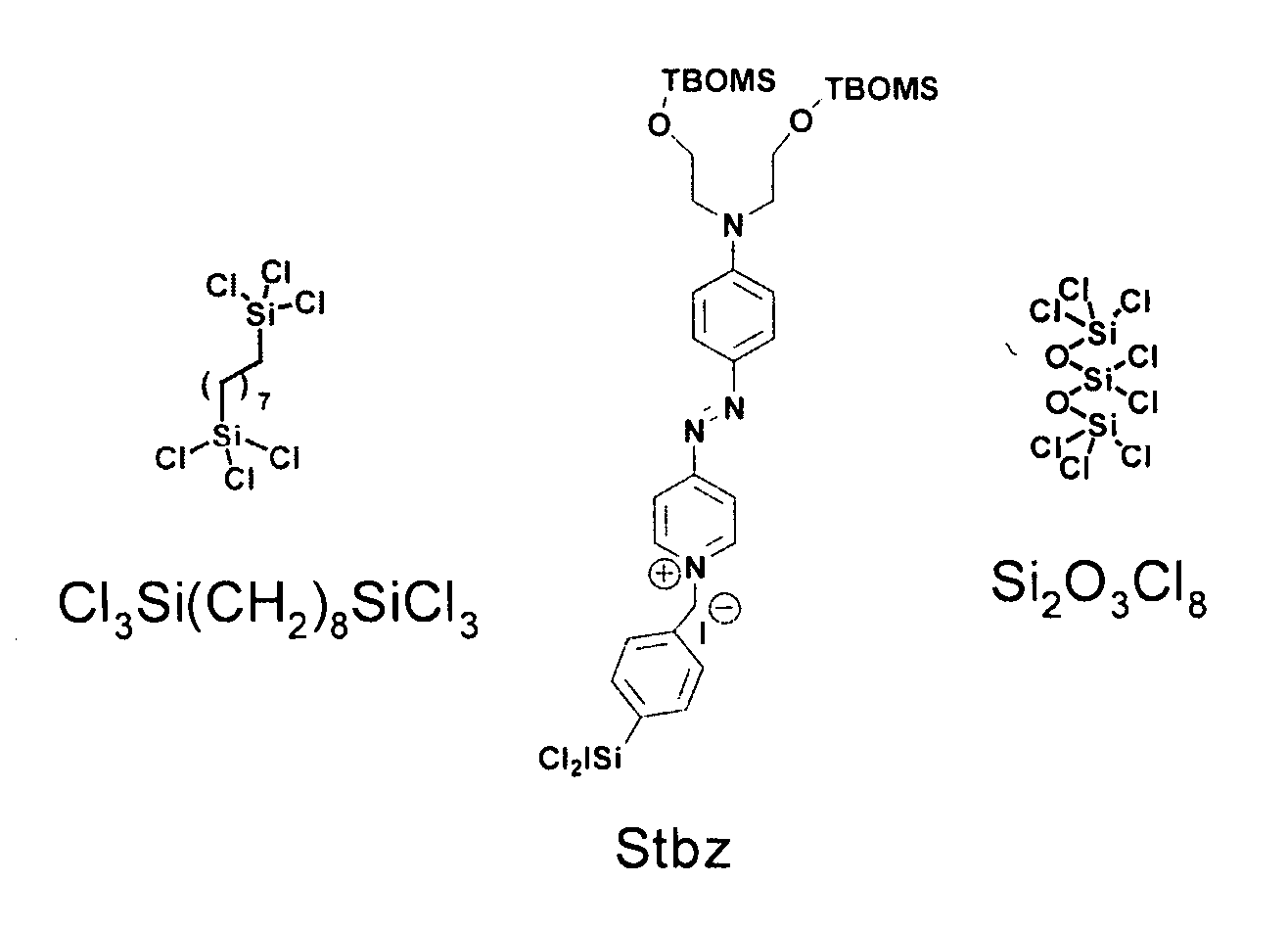

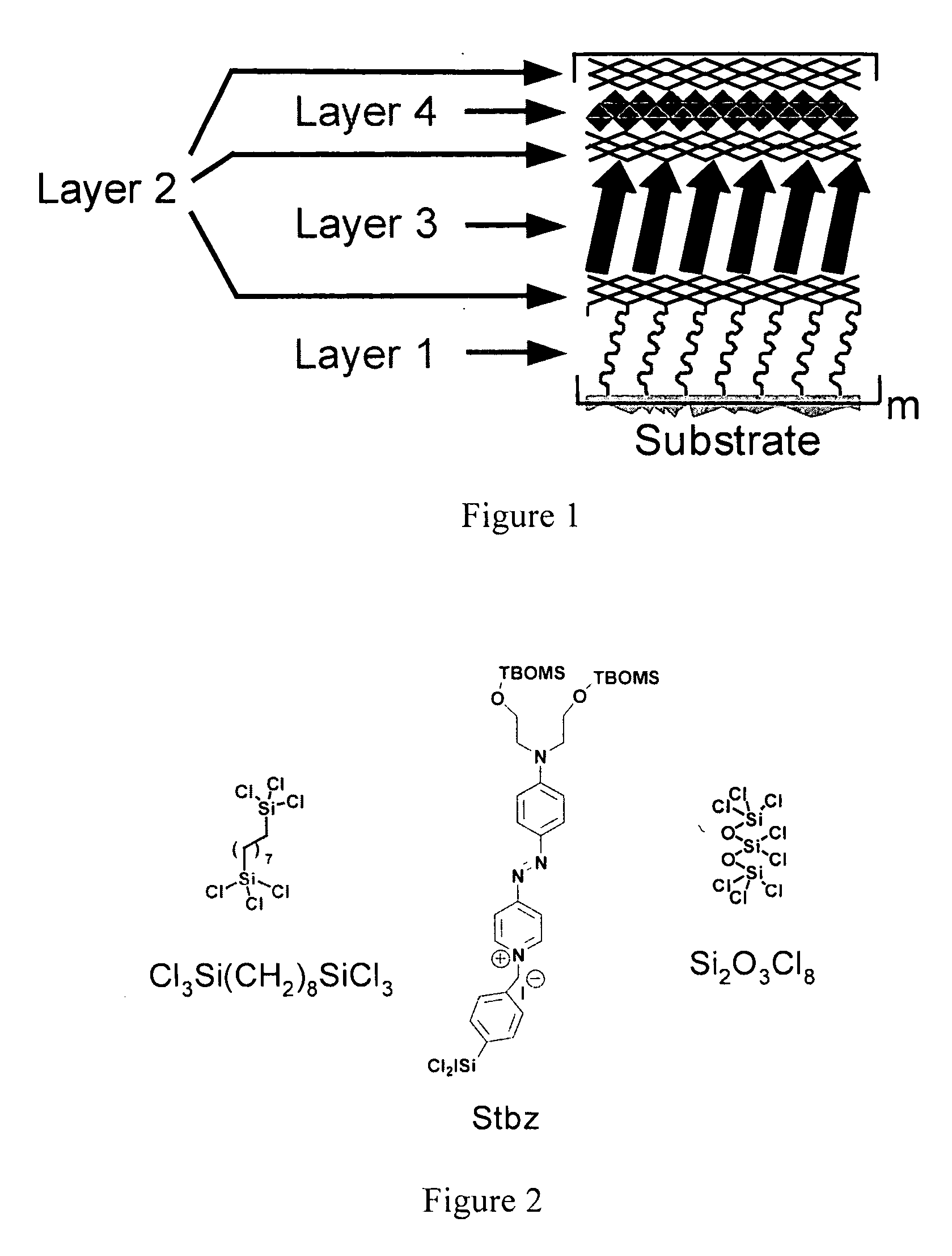

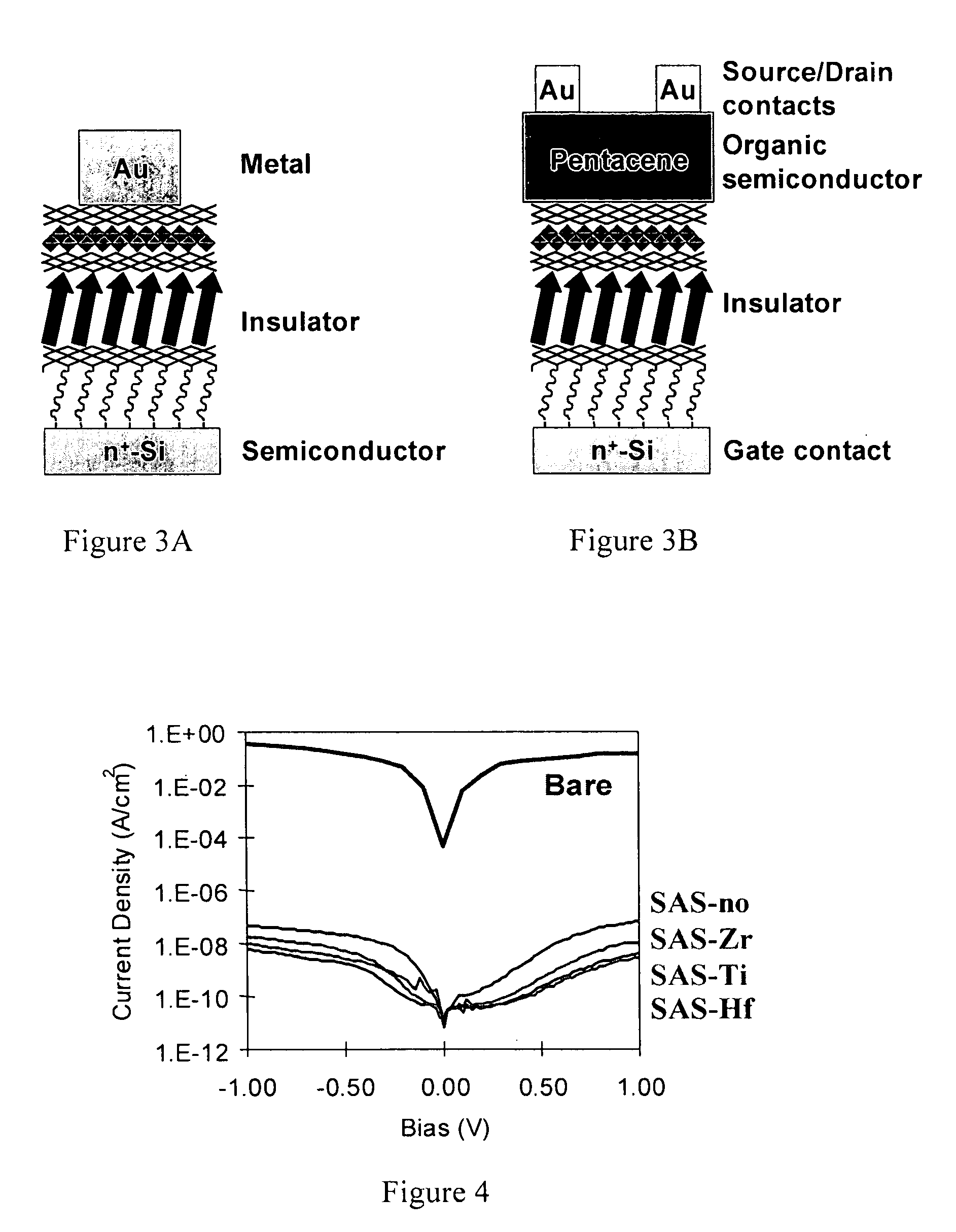

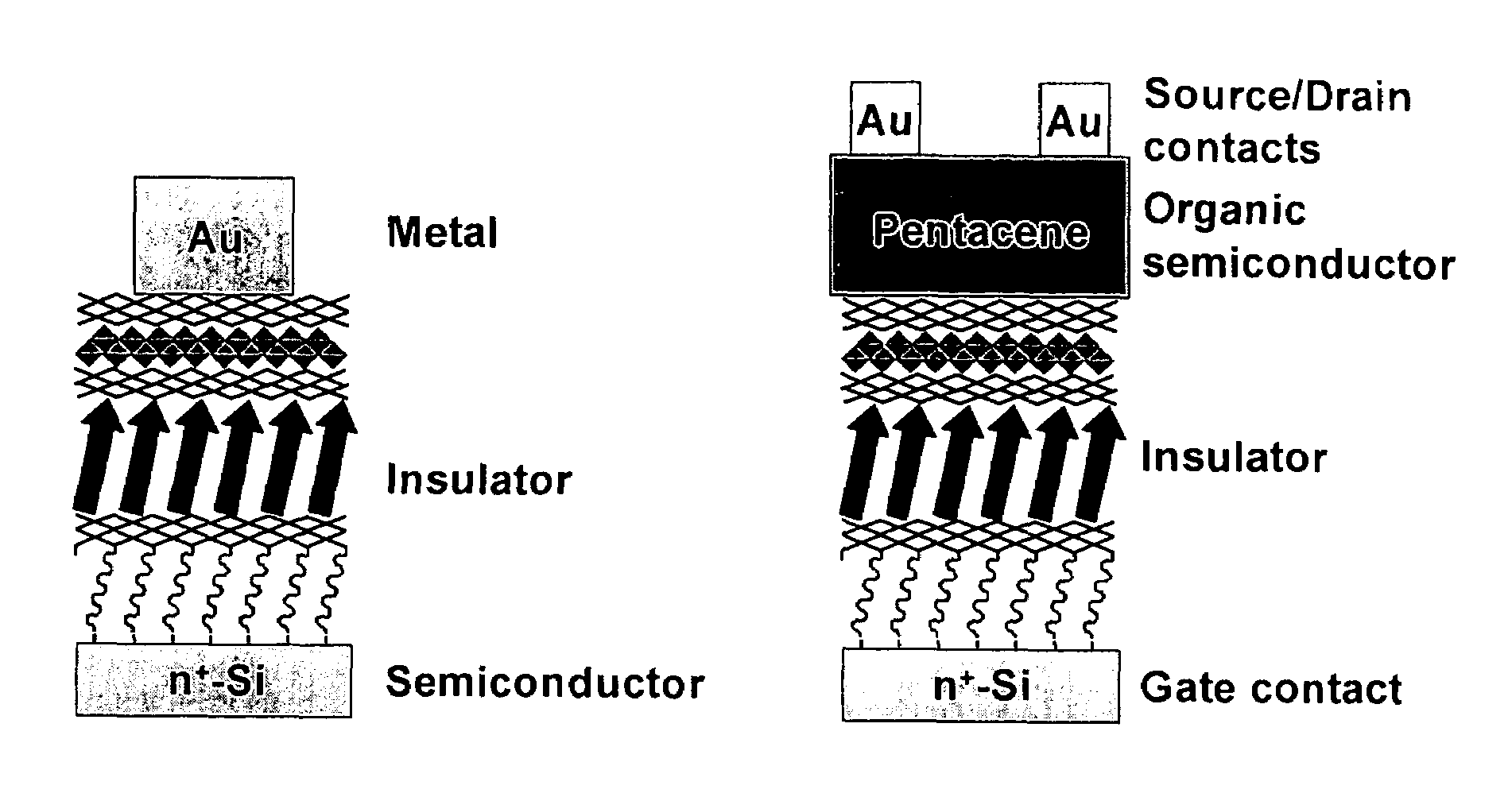

ActiveUS20070181961A1Low working voltageDrain current increasesMaterial nanotechnologyLiquid surface applicatorsDielectricSuperlattice

Compositions, methods of using inorganic moieties for dielectric modulation, and related device structures.

Owner:NORTHWESTERN UNIV

Intercalated superlattice compositions and related methods for modulating dielectric property

ActiveUS7678463B2Low working voltageDrain current increasesMaterial nanotechnologySolid-state devicesCrystallographyDielectric

Compositions, methods of using inorganic moieties for dielectric modulation, and related device structures.

Owner:NORTHWESTERN UNIV

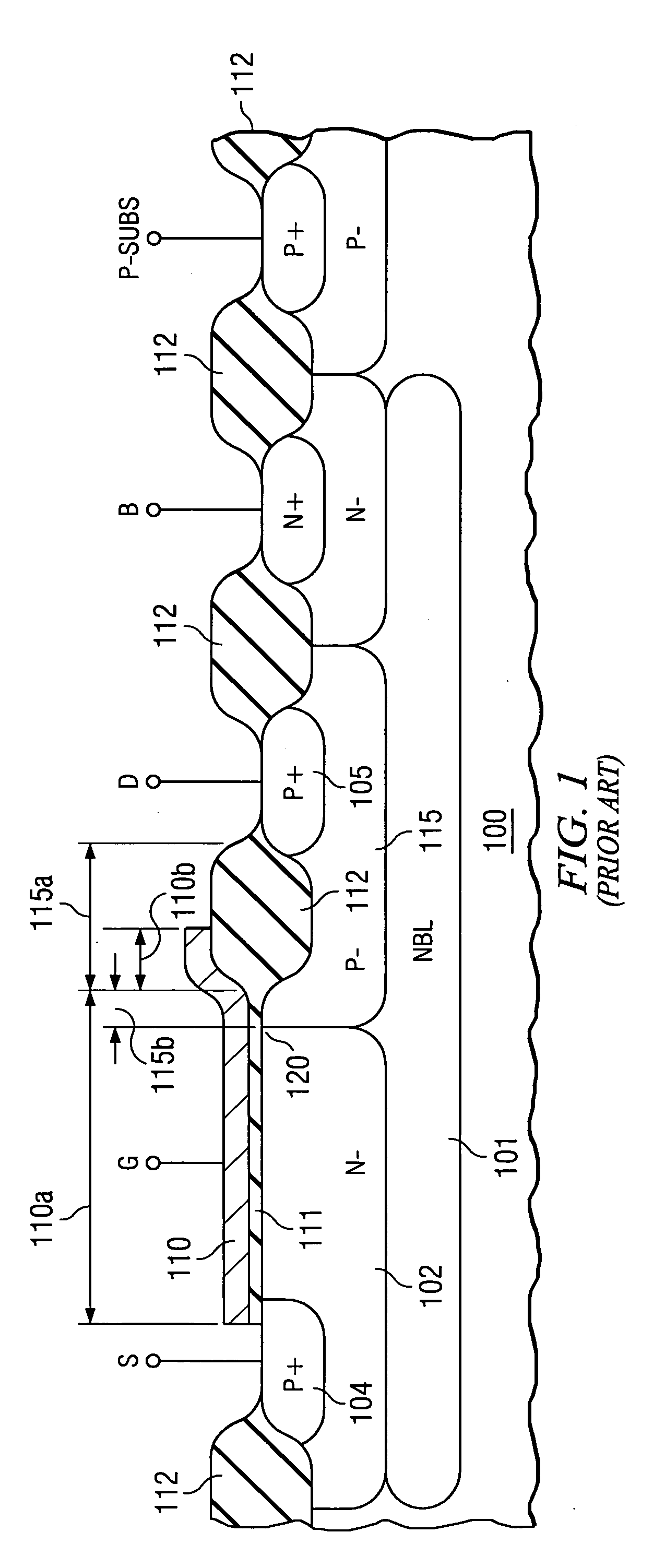

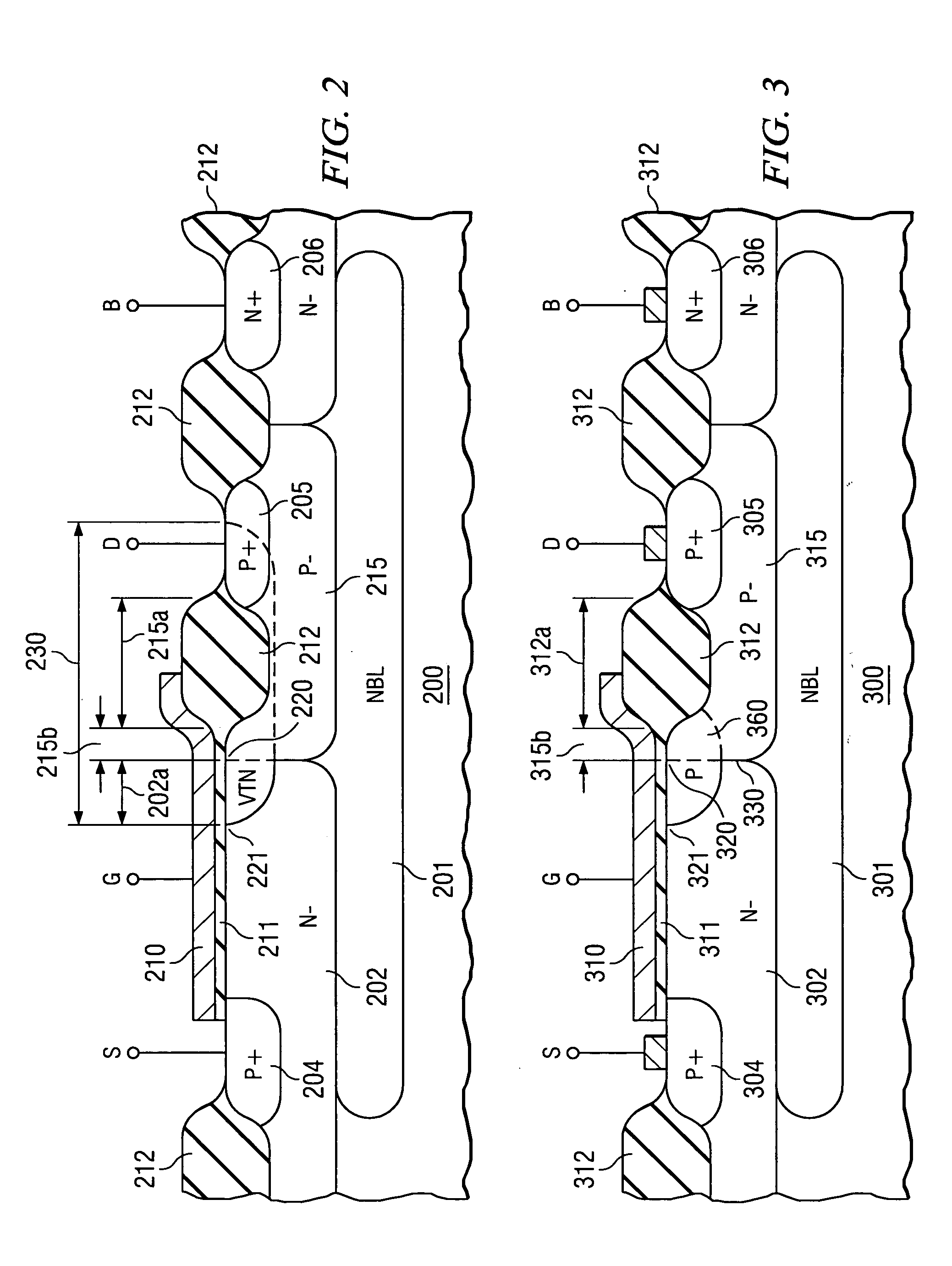

Low cost fabrication method for high voltage, high drain current MOS transistor

ActiveUS20050118753A1Reduce resistanceEliminating resistance uncertaintySemiconductor/solid-state device manufacturingSemiconductor devicesHigh pressureDrain current

A method for reducing the drain resistance of a drain-extended MOS transistor in a semiconductor wafer, while maintaining a high transistor breakdown voltage. The method provides a first well (502) of a first conductivity type, operable as the extension of the transistor drain (501) of the first conductivity type; portions of the well are covered by a first insulator (503) having a first thickness. A second well (504) of the opposite conductivity type is intended to contain the transistor source (506) of the first conductivity type; portions of the second well are covered by a second insulator (507) thinner than the first insulator. The first and second wells form a junction (505) that terminates at the second insulator (530a, 530b). The method deposits a photoresist layer (510) over the wafer, which is patterned by opening a window (510a) that extends from the drain to the junction termination. Next, ions (540) of the first conductivity type are implanted through the window into the first well; these said ions have an energy to limit the penetration depth (541) to the first insulator thickness, and a dose to create a well region (560) of high doping concentration adjacent to the junction termination (530a).

Owner:TEXAS INSTR INC

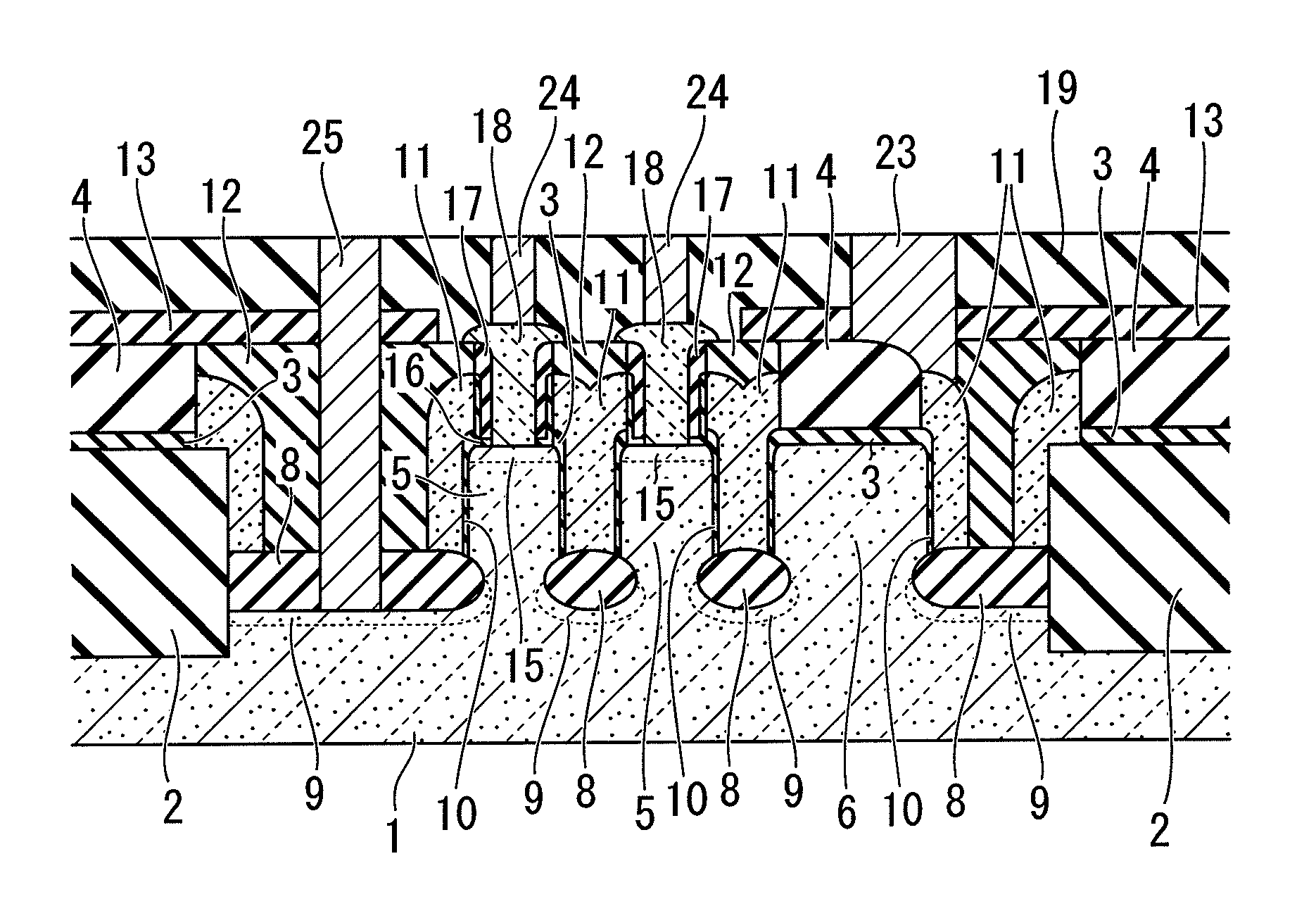

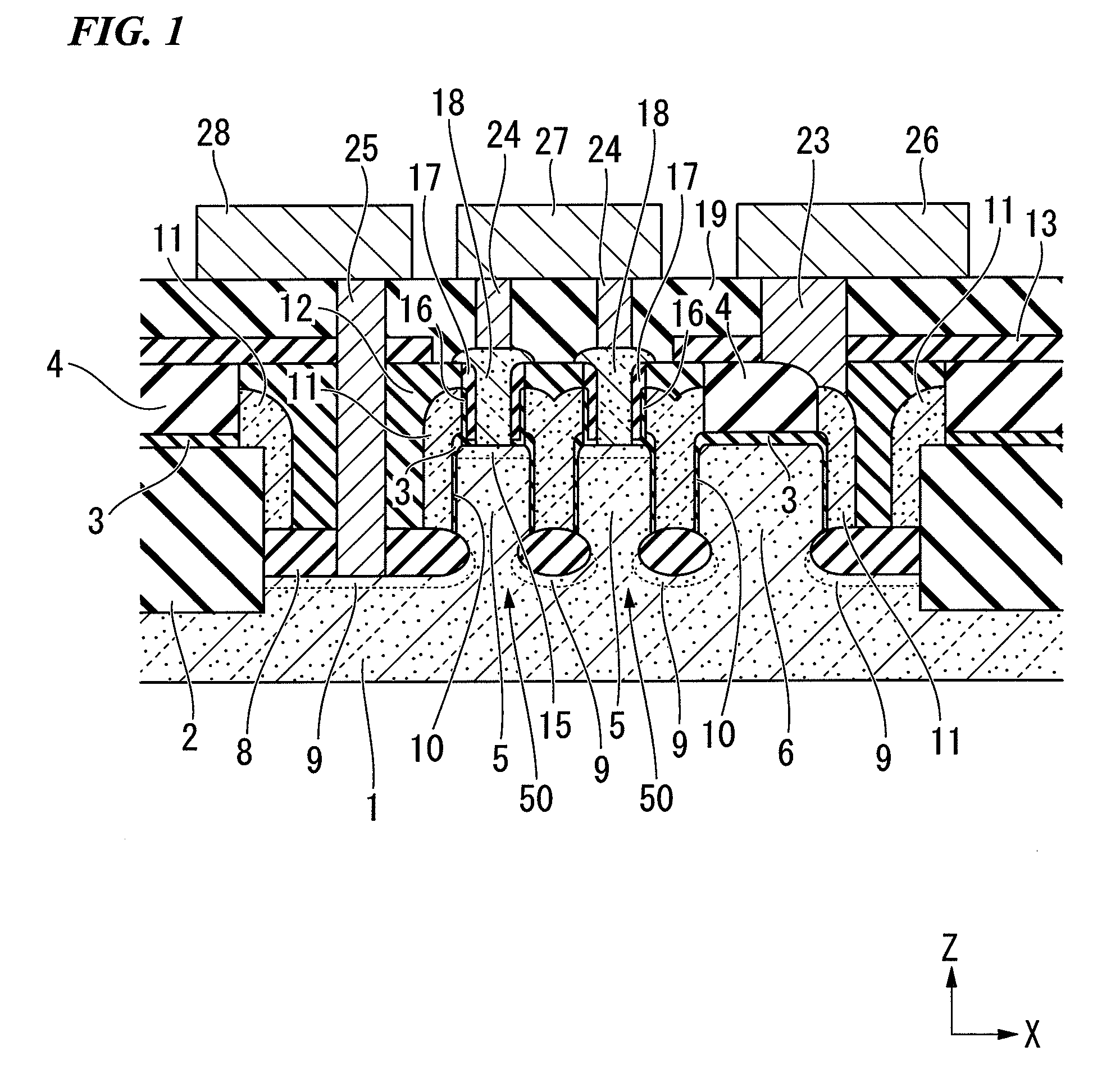

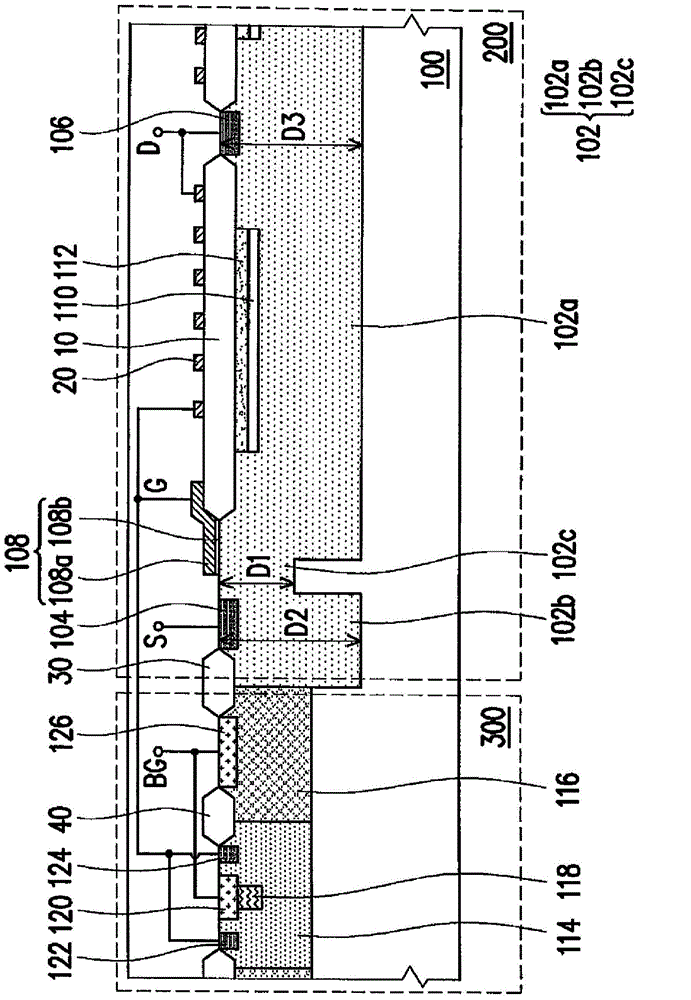

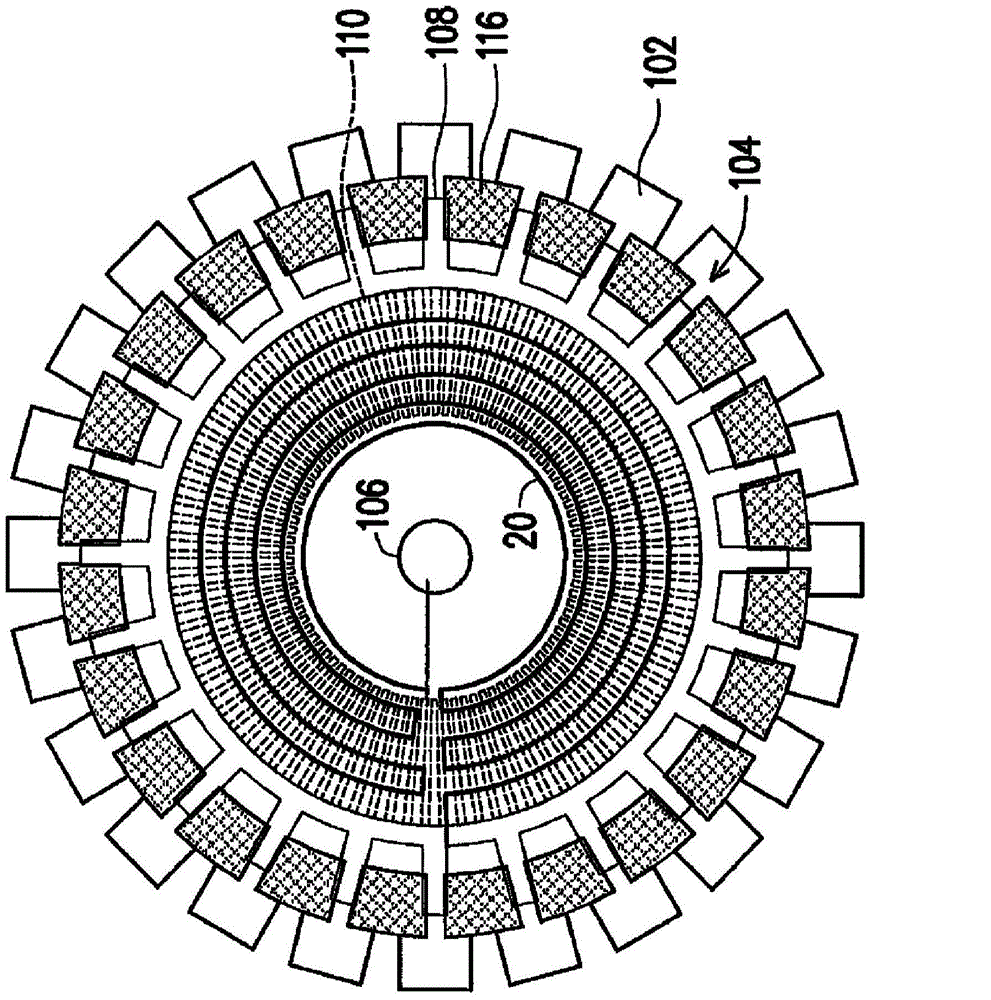

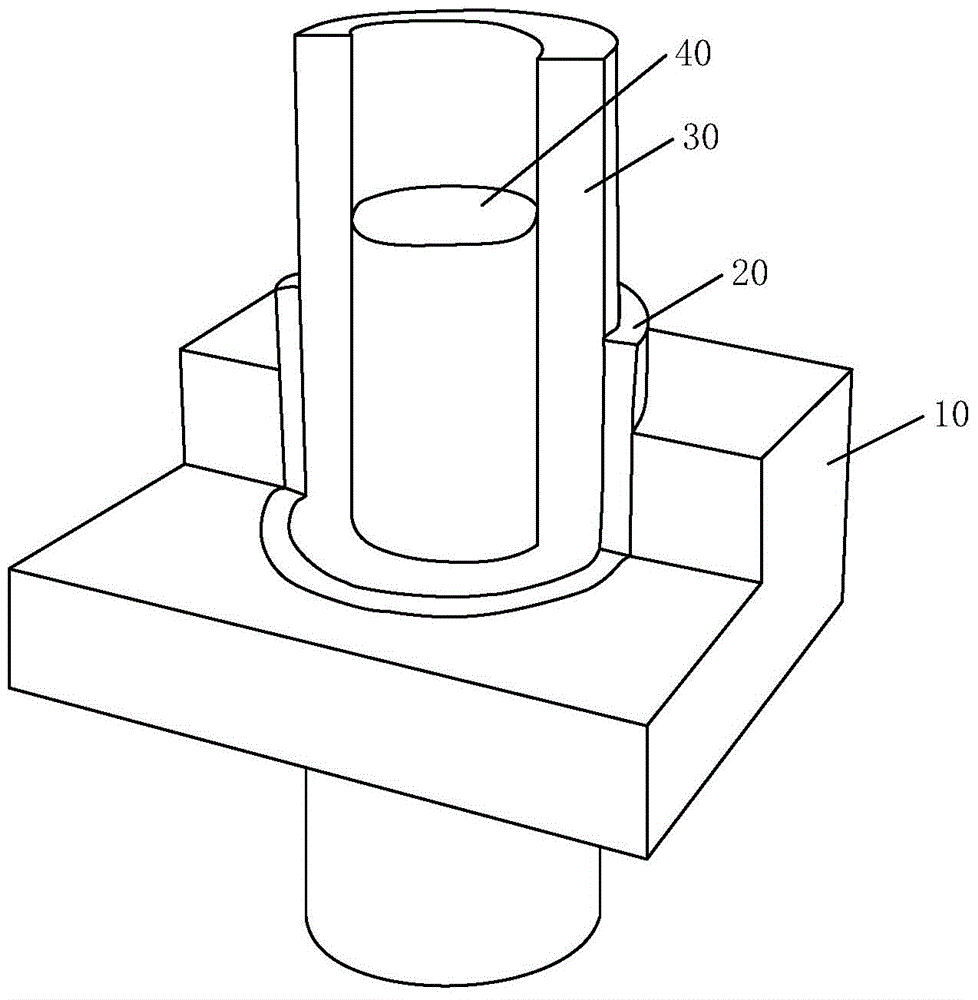

Semiconductor device having vertical surrounding gate transistor structure, method for manufacturing the same, and data processing system

InactiveUS20090085102A1Rapid responseReduce power consumptionBulk negative resistance effect devicesSemiconductor devicesData processing systemImpurity

A semiconductor device is provided which includes: semiconductor pillars which include impurity diffused layers, each semiconductor pillar having a width which allows full depletion of a semiconductor forming each semiconductor pillar, the impurity diffused layers being electrically connected to each other; and a common gate section which covers side faces of the pillars.

Owner:LONGITUDE SEMICON S A R L

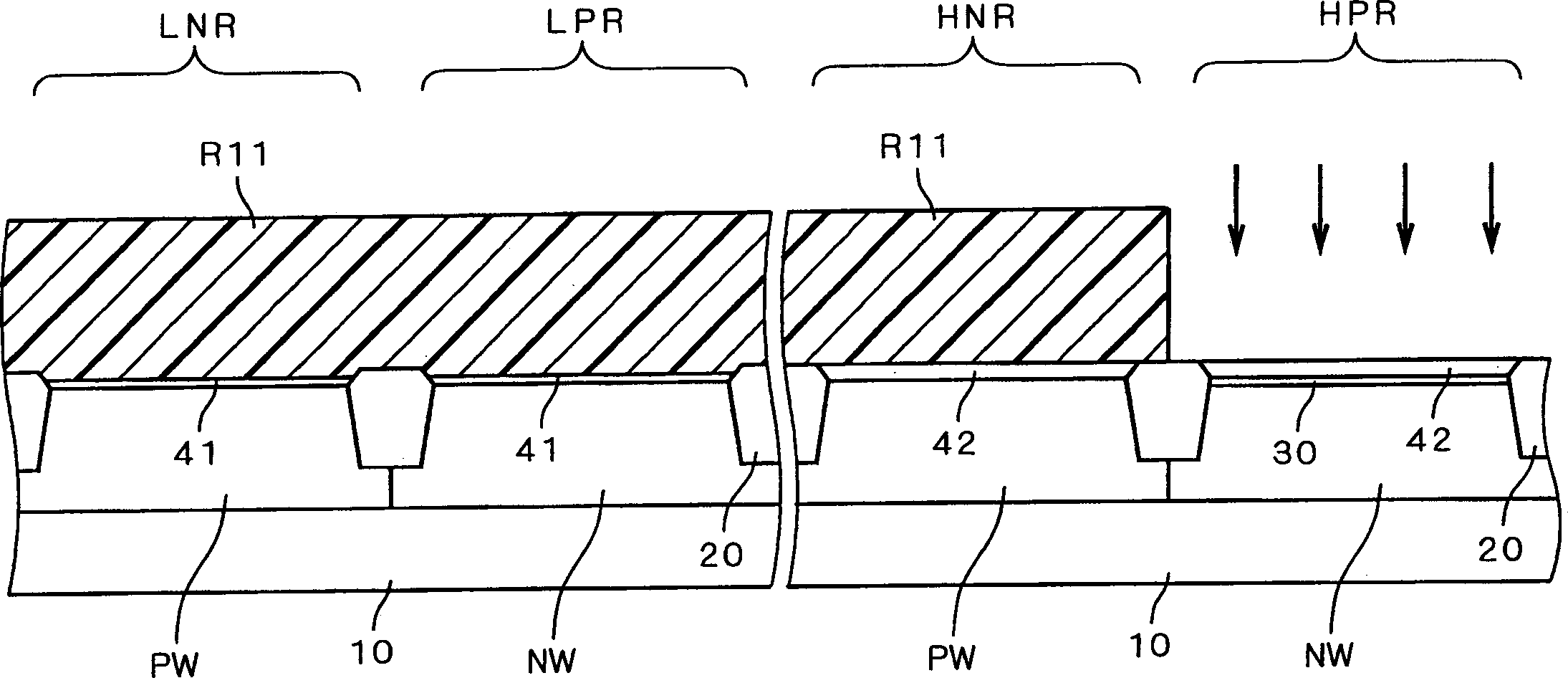

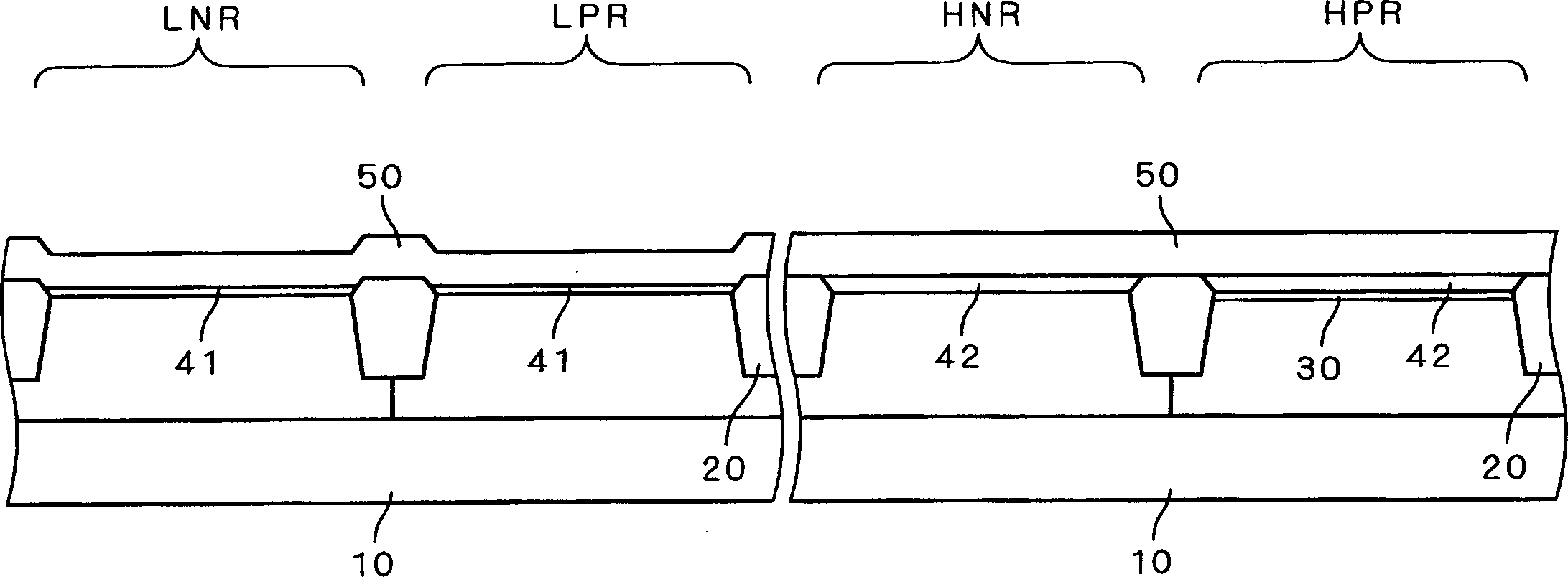

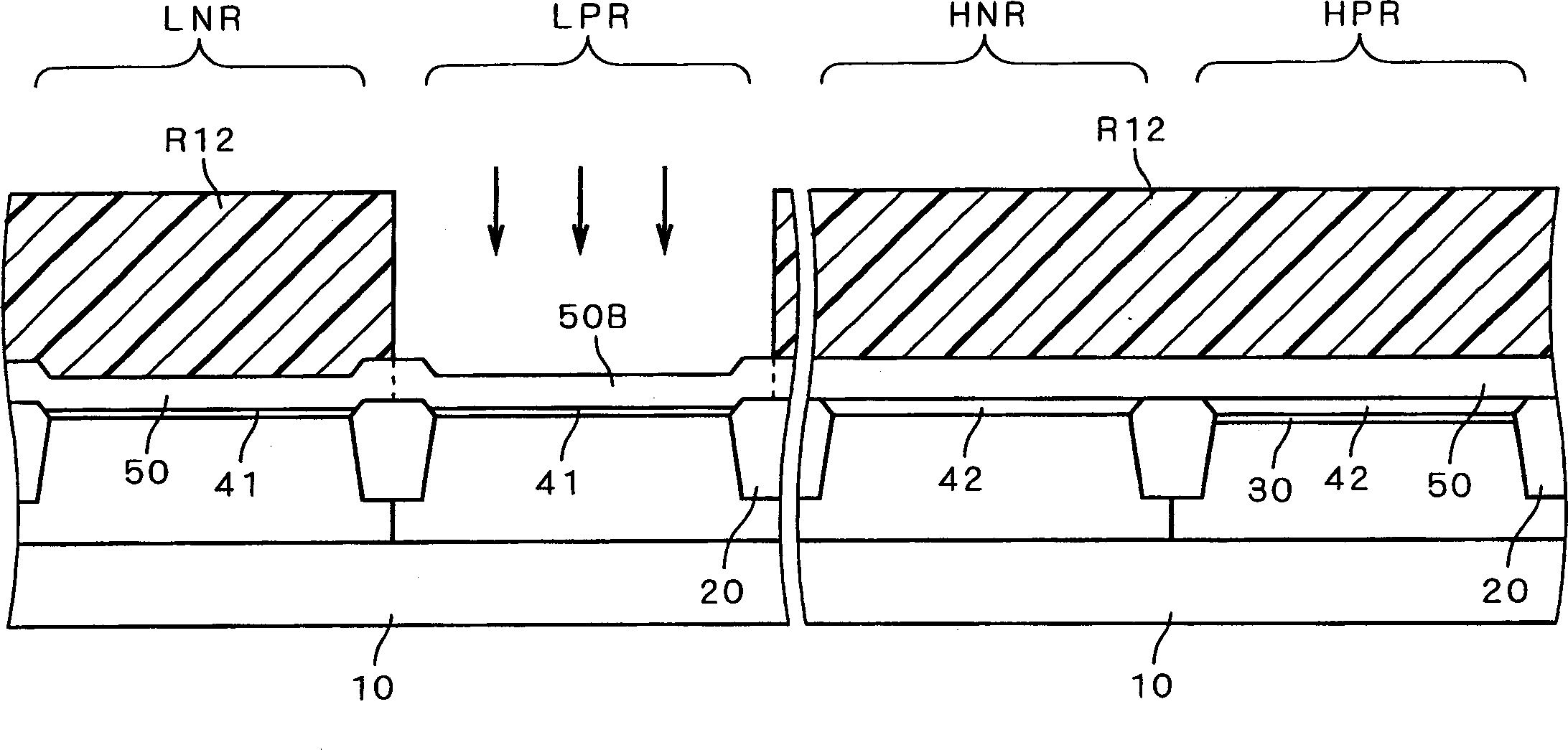

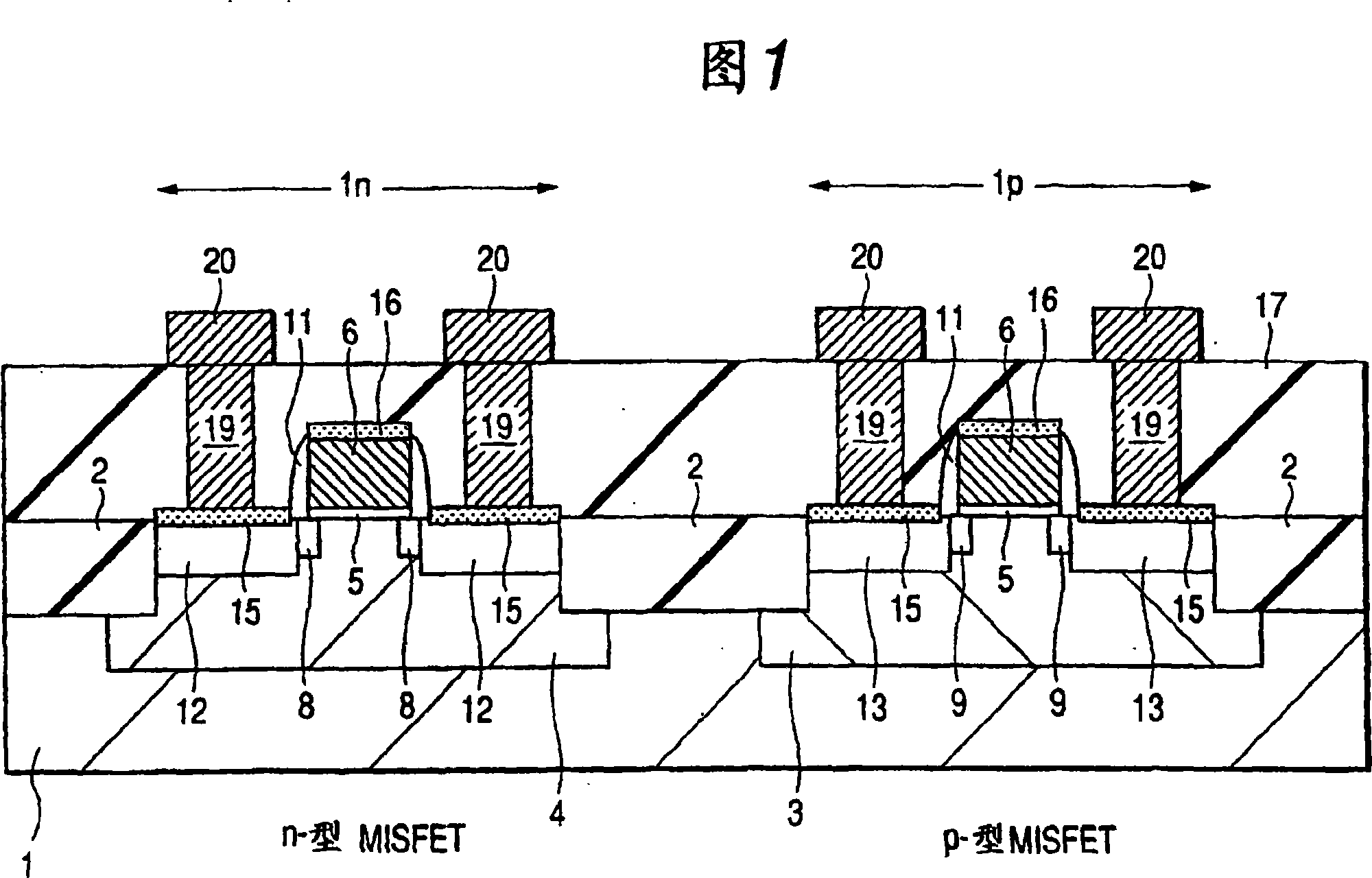

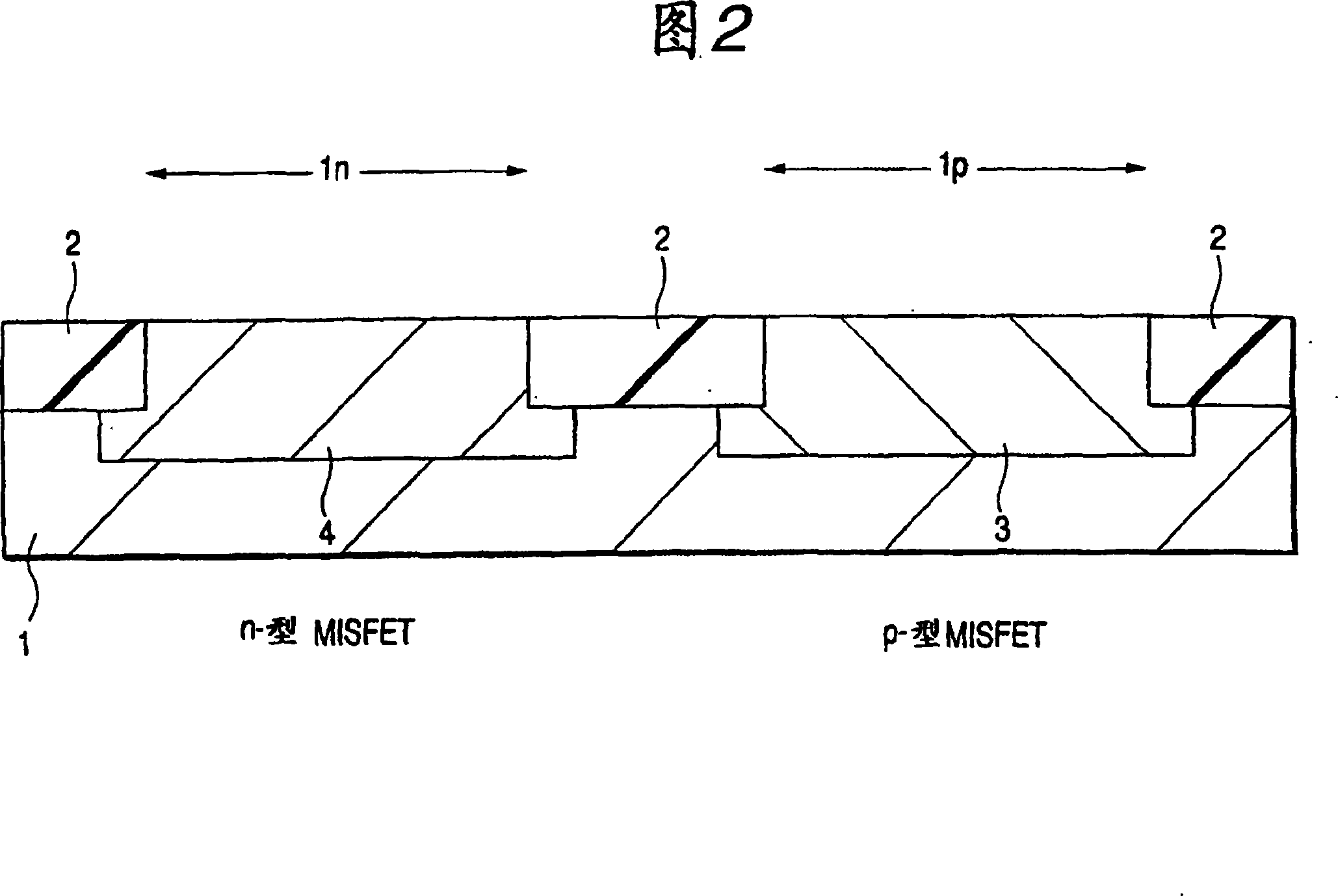

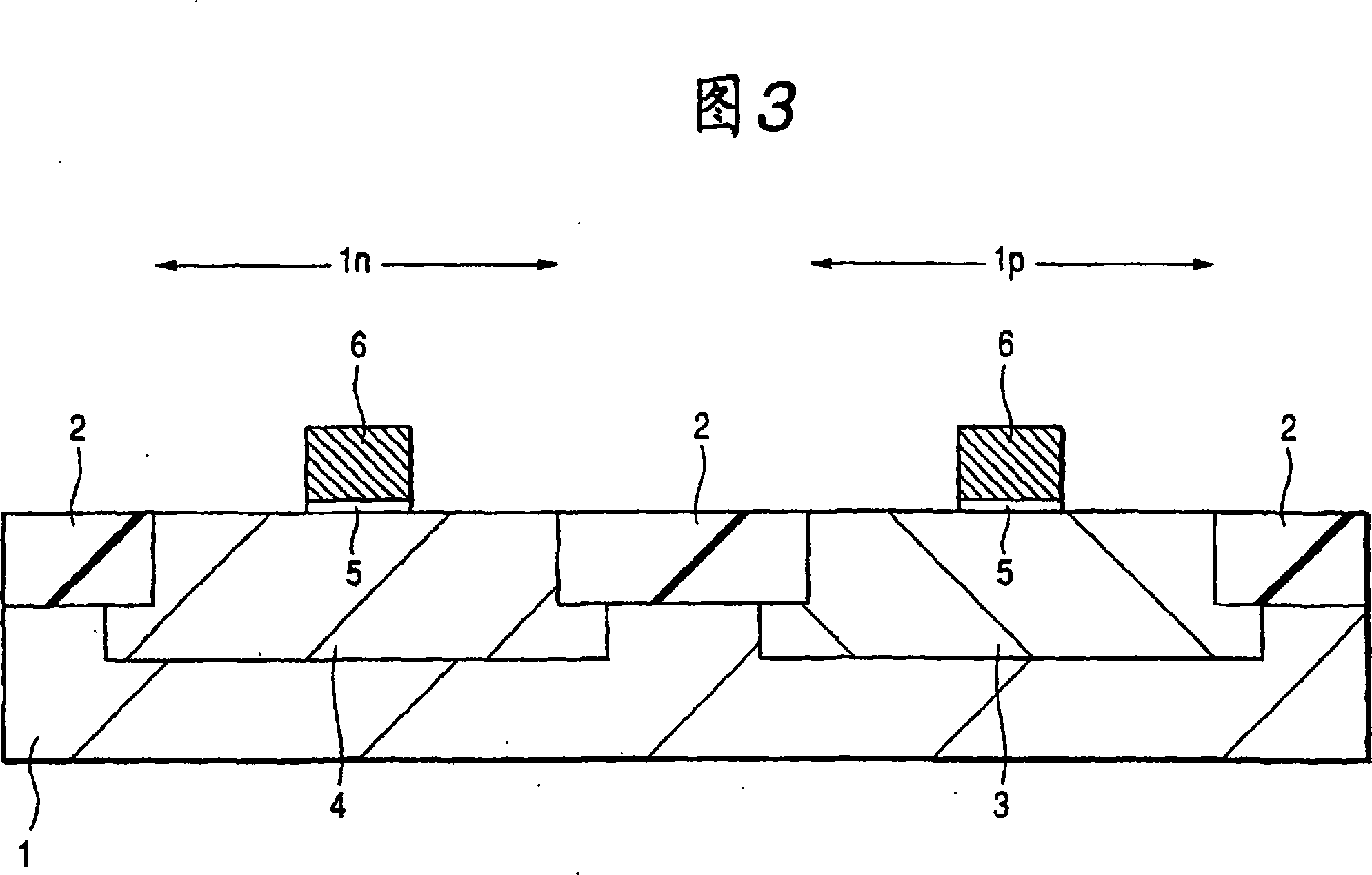

Semiconductor device and its manufacture

InactiveCN1384547AMiniaturizationImprove mobilityTransistorSemiconductor/solid-state device manufacturingCMOSLow voltage

Provided are a CMOS transistor capable of meeting miniaturization requirements and reliability requirements and a manufacturing method thereof. A buried channel type PMOS transistor is arranged only in the CMOS transistor 100B corresponding to the high voltage, a surface channel type NMOS transistor is formed in the low voltage NMOS region LNR and a high voltage NMOS region HNR, and a surface channel type NMOS transistor is formed in the low voltage PMOS region LPR. Surface channel type PMOS transistor.

Owner:MITSUBISHI ELECTRIC CORP

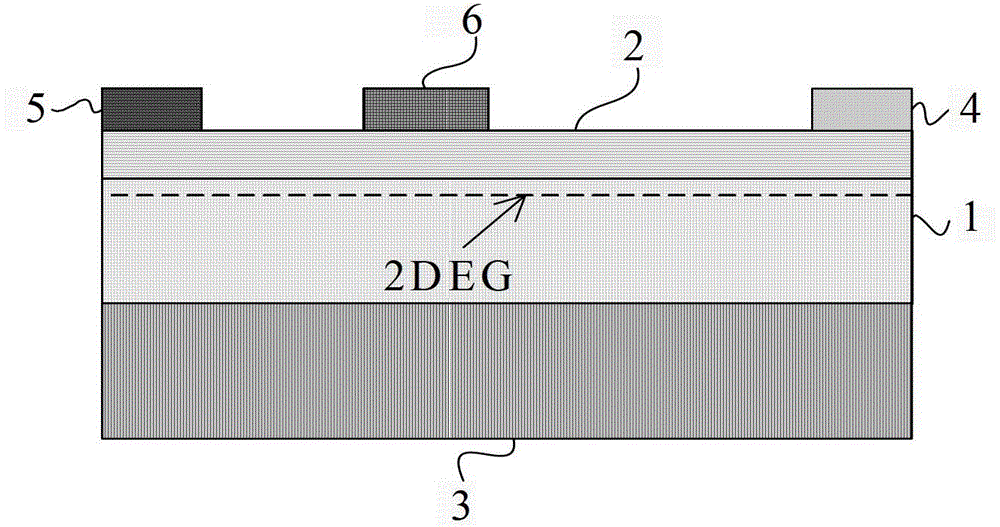

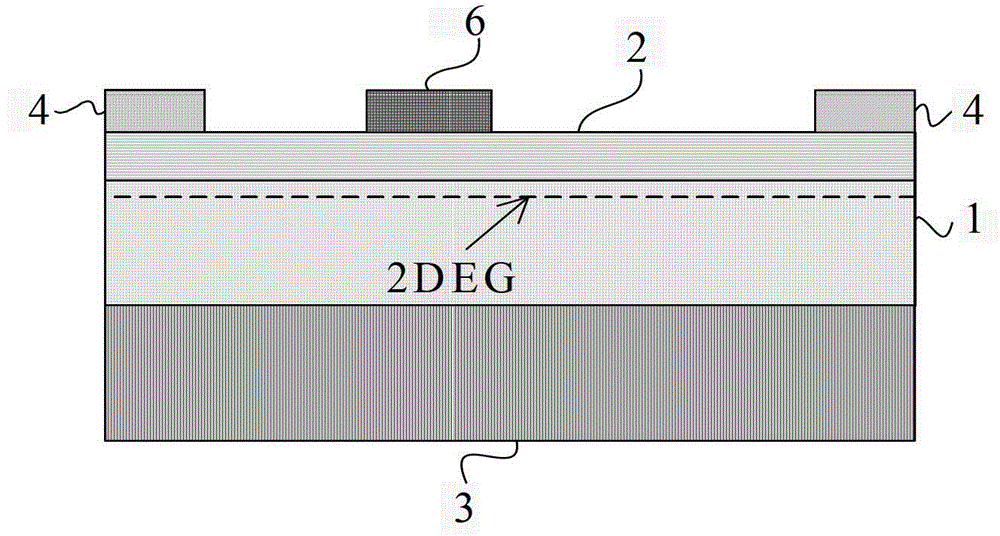

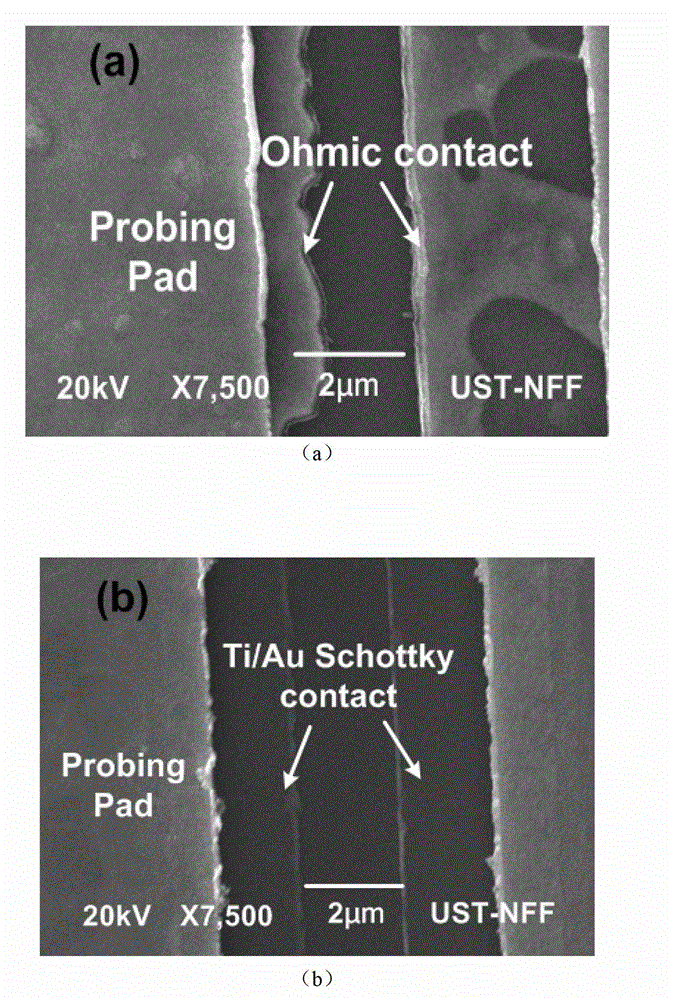

GaN heterojunction HEMT (High Electron Mobility Transistor) device

InactiveCN102945859AImprove off-state breakdown voltageLower on-resistanceSemiconductor devicesHeterojunctionElectron injection

The invention discloses a GaN heterojunction HEMT (High Electron Mobility Transistor) device, belonging to the technical field of semiconductor devices. The GaN heterojunction HEMT device comprises a substrate and an InAIN / GaN heterojunction, wherein the InAIN / GaN heterojunction is positioned on the surface of the substrate; the surface of an InAIN layer is provided with a grid electrode, a source electrode and a drain electrode; and the drain electrode and the surface of the InAIN layer form ohmic contact, while the source electrode and the surface of the InAIN layer form Schottky contact. The GaN heterojunction HEMT device disclosed by the invention has the advantages that the Schottky contact is adopted at the source electrode, the electric field in GaN under the source electrode is uniformly distributed due to a good appearance characteristic, the electron injection of the source electrode is effectively restrained, and the current leakage of GaN and collision ionization and current leakage of the grid electrode caused by the current leakage are reduced, so that the off-state puncture voltage of the device is improved; the drain electrode adopts ohmic contact still, so that the positive on resistance of the device is reduced as low as possible, and better positive current driving capability of the device is ensured; in addition, the GaN heterojunction HEMT device is compatible to the traditional process, simultaneously the distance between the grid electrode and the source electrode can be very short, and the wafer occupying area is smaller, so that lower cost of the device is ensured.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

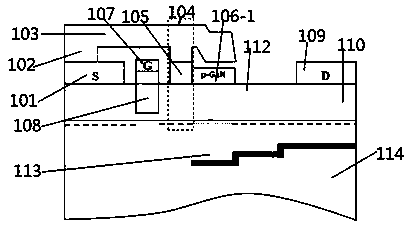

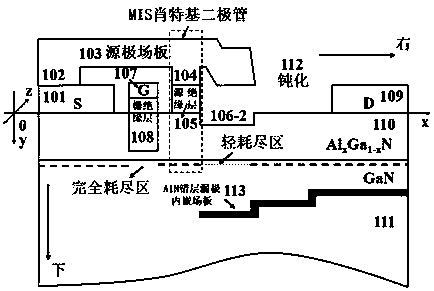

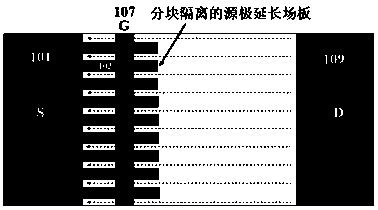

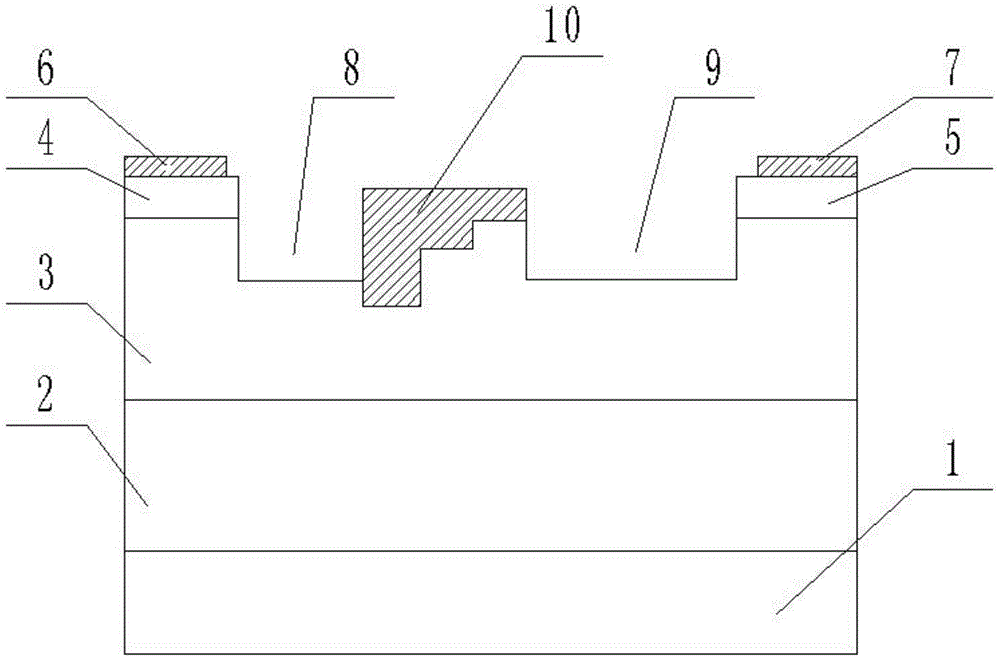

Lateral diffusion eGaN HEMT device integrating reverse diode and embedded drain electrode field plate

ActiveCN110212028AImprove breakdown characteristicsImprove breakdown resistanceSemiconductor devicesLateral diffusionBackward diode

The invention discloses a lateral diffusion eGaN HEMT device integrating a reverse diode and an embedded drain electrode field plate. The device comprises a GaN buffer layer, an AlGaN barrier layer, agate electrode, an under-gate insulating layer, a source electrode, a source electrode extension section, a source electrode field plate, an MIS schottky diode extension section, an MIS schottky diode insulating layer, a p-type GaN or groove, a drain electrode, a passivation layer and an AlN staggered-layer drain electrode embedded field plate, wherein the MIS schottky diode insulating layer is prepared in the middle region, towards the MIS schottky diode extension section and the AlGAN barrier layer surface, of the source electrode field plate; the side, close to the drain electrode, of thediode adopts the p-type GaN or groove, so that the breakdown characteristic of the device is improved; the embedded staggered-layer field plate is adopted below the drain electrode, so that anti-breakdown capability of the drain electrode to the substrate is improved; the design of the staggered layer is suitable for the gradual change distribution of the drain electrode electric field from rightto left, so that the breakdown characteristic of the device is improved; and the source electrode field plate is extended, the gate electrode is wrapped, the MIS schottky diode is formed on the gate drain side, and the diode is made into a block isolation mode, so that the drain electrode current is greatly improved.

Owner:SHANDONG JIANZHU UNIV

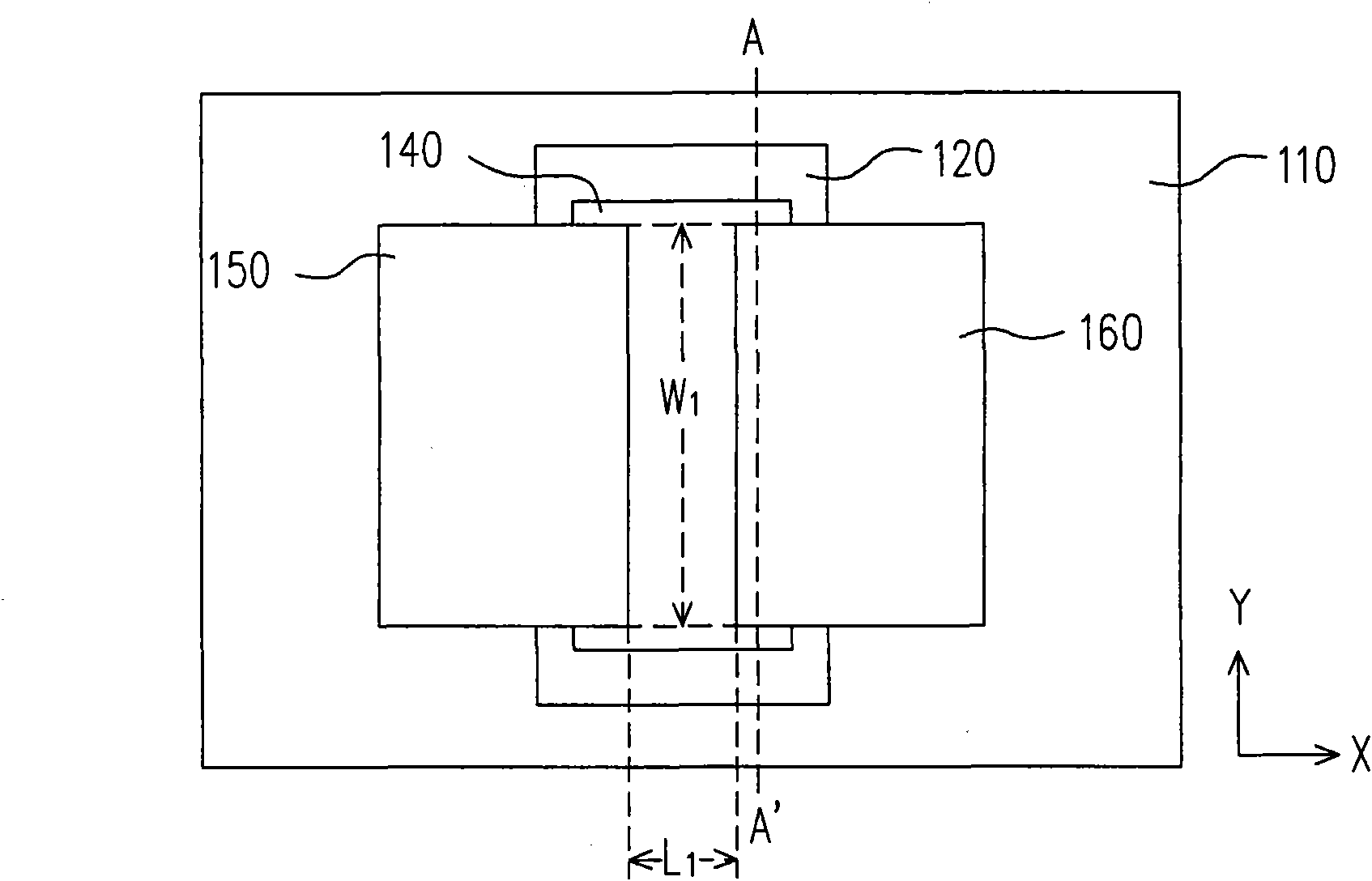

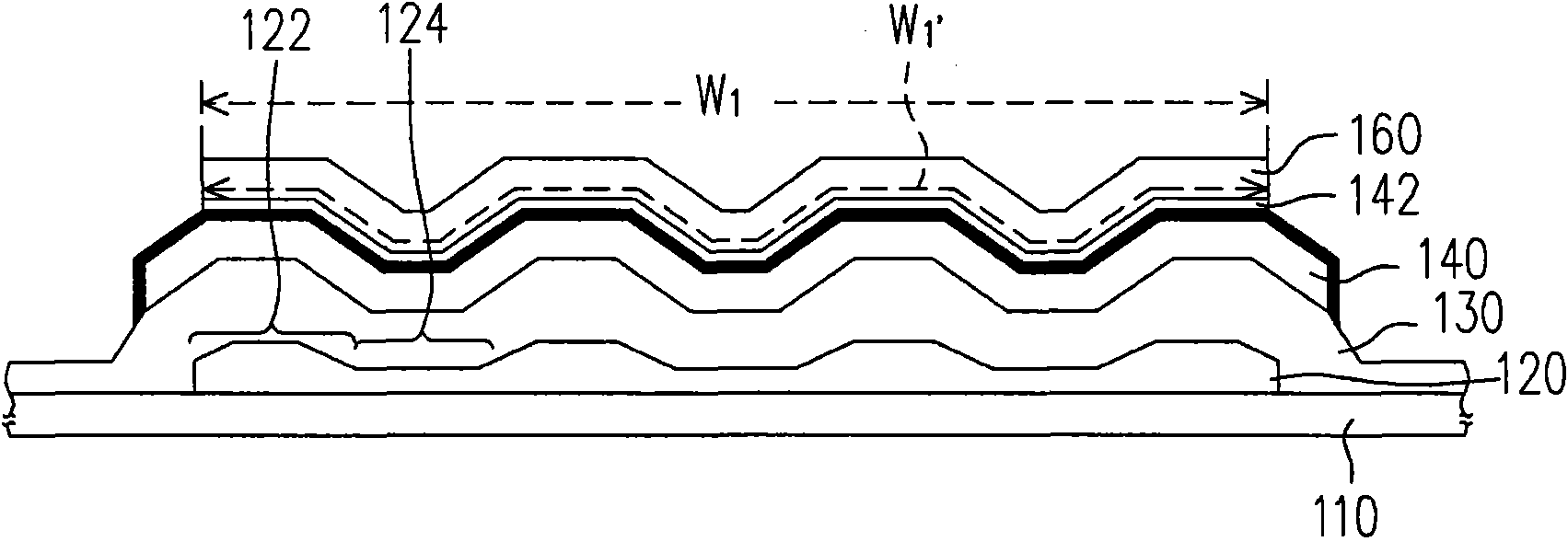

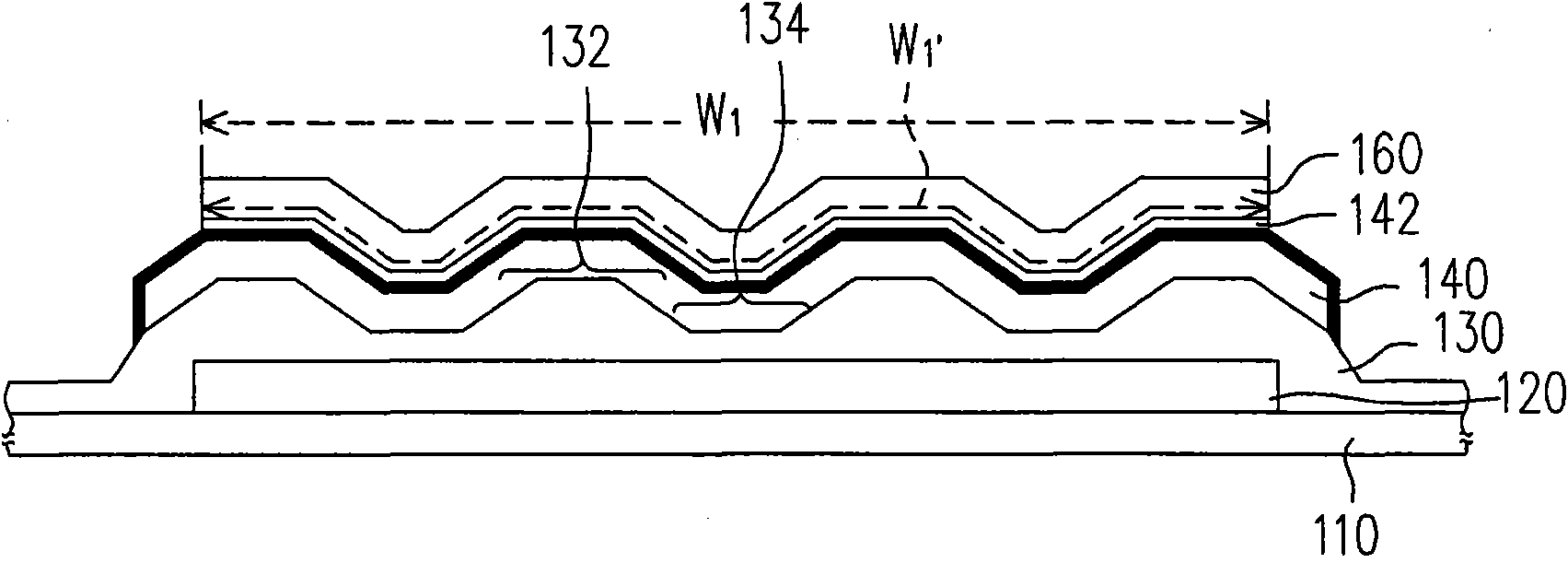

Thin film transistor

The invention provides a thin film transistor, which comprises a grid, a grid insulating layer, a channel layer, a source electrode and a drain electrode, wherein the grid is arranged on a substrate; the grid insulating layer is covered on the grid; the channel layer is arranged on the grid insulating layer above the grid; the longitudinal section of the channel layer can be of a wave shape; and the source electrode and the drain electrode are arranged on the channel layer; in addition, the longitudinal section of the channel layer can be flat in surface, and the source electrode and the drain electrode at two sides covered on the channel layer are in nonlinear line list structures.

Owner:CHUNGHWA PICTURE TUBES LTD

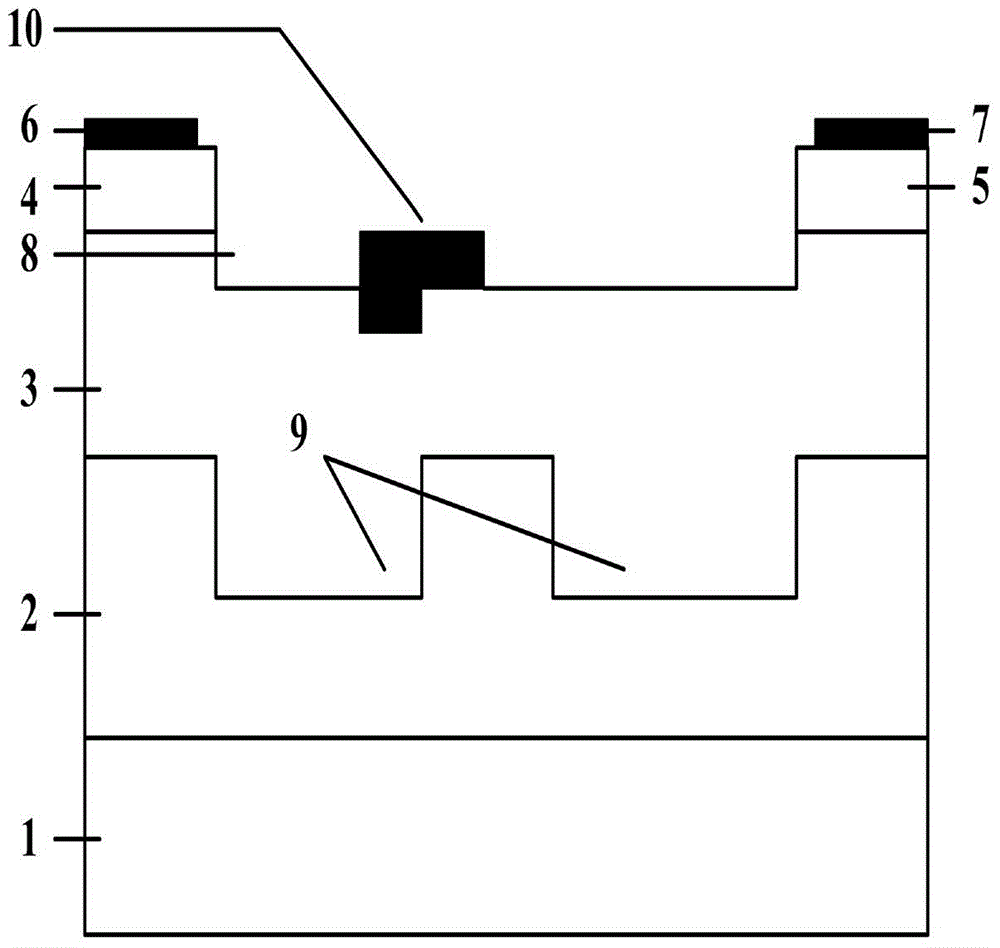

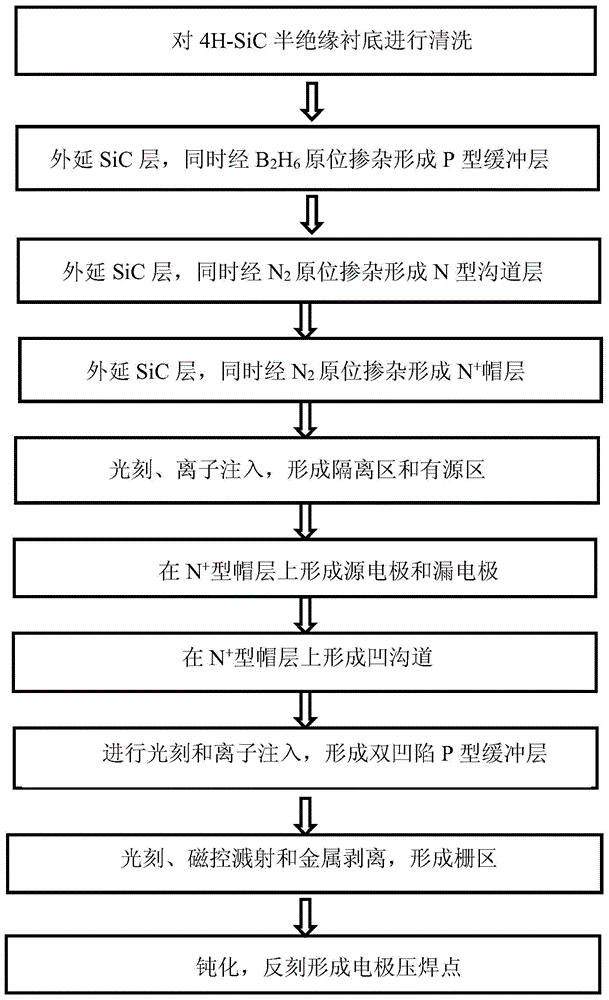

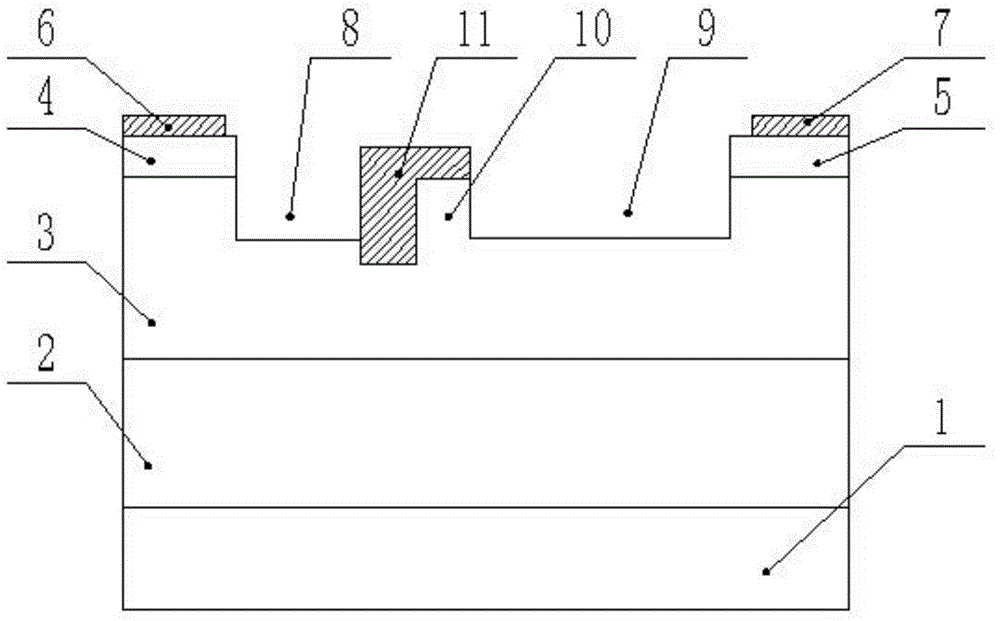

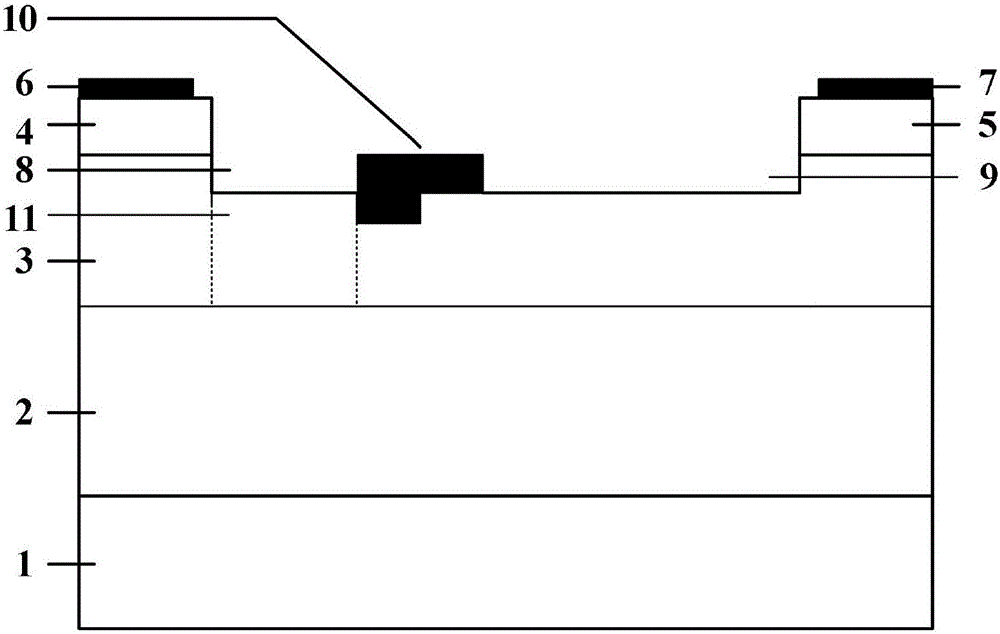

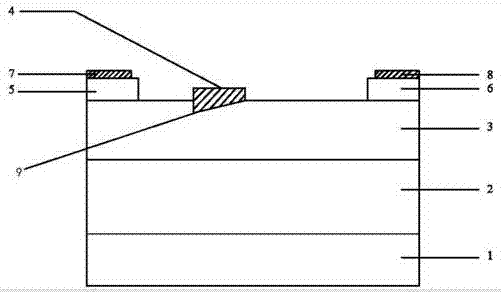

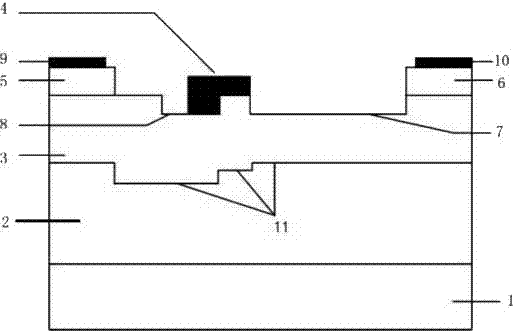

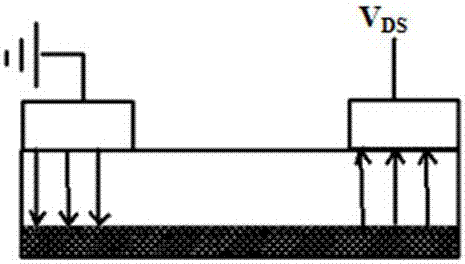

4H-SiC metal-semiconductor field effect transistor with double-sunken buffer layer

ActiveCN104681618ADrain current increasesLarge channel thicknessSemiconductor devicesPower flowSemi insulating

The invention discloses a 4H-SiC metal-semiconductor field effect transistor with a double-sunken buffer layer. The 4H-SiC metal-semiconductor field effect transistor comprises a 4H-SiC semi-insulating substrate, a P type buffer layer and an N type channel layer from bottom to top, wherein a source electrode cap layer and a drain electrode cap layer are respectively arranged on two sides of the N type channel layer; a source electrode and a drain electrode are respectively arranged on the surfaces of the source electrode cap layer and the drain electrode cap layer; a gate electrode is formed on one side, close to the source electrode cap layer, above a channel; grooves are arranged on the upper end face of the P type buffer layer and under a gate source and a gate leakage. The 4H-SiC metal-semiconductor field effect transistor has the advantages that the output drain electrode current is obviously improved, and the breakdown voltage is stable.

Owner:XIDIAN UNIV

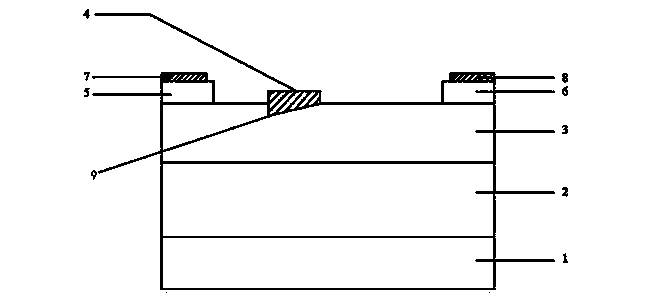

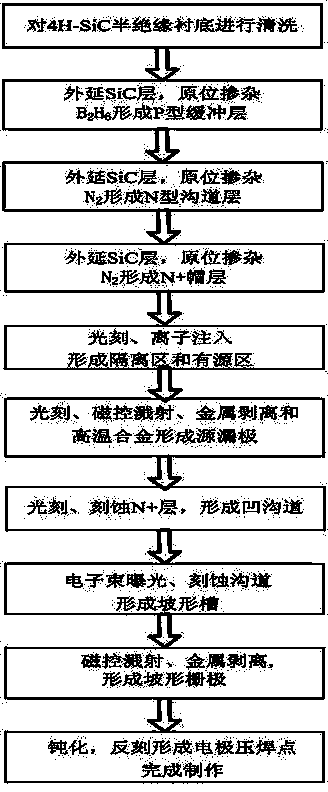

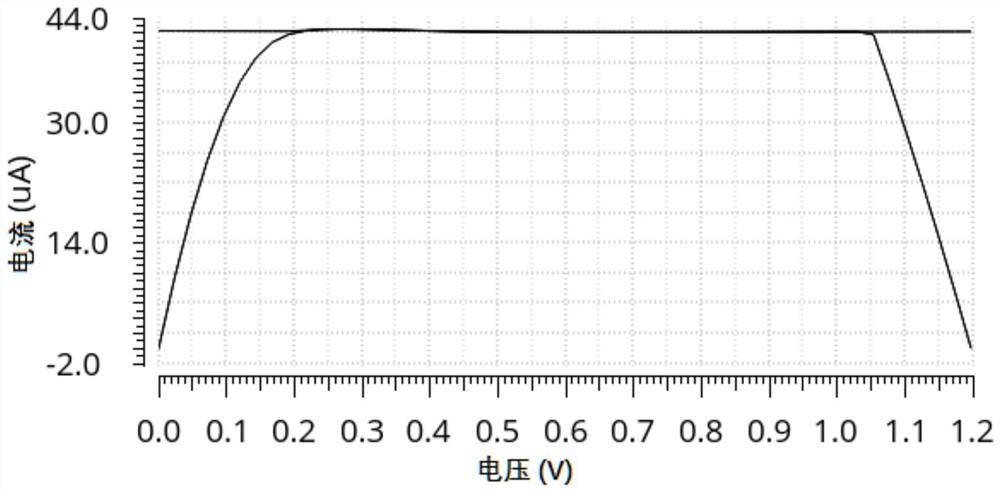

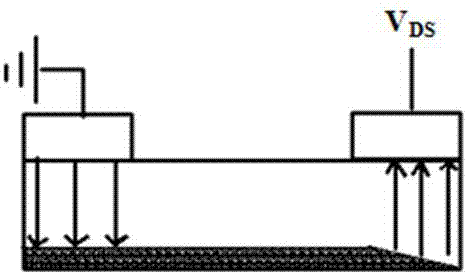

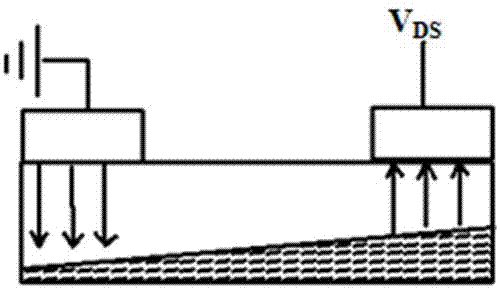

4H-SiC metal semiconductor field effect transistor with slope-shaped grid and manufacturing method

ActiveCN104282764ADrain current increasesLower channel resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowMetal

The invention discloses a 4H-SiC metal semiconductor field effect transistor with a slope-shaped grid. The 4H-SiC metal semiconductor field effect transistor comprises a 4H-SiC semi-insulating substrate, a P-type buffer layer and an N-type channel layer from bottom to top, a source electrode cap layer and a drain electrode cap layer are arranged on the surface of the N-type channel layer, a source electrode and a drain electrode are arranged on the surface of the source electrode cap layer and the surface of the drain electrode cap layer respectively, a slope-shaped groove inclined towards one side of the source electrode cap layer is formed in the upper end face of the N-type channel layer, the slope-shaped grid is arranged is arranged in the slope-shaped groove, the lower end face of the slope-shaped grid is matched with the slope-shaped groove, the upper end face of the slope-shaped grid is parallel to the upper end face of the N-type channel layer, and the distance between the slope-shaped grid and the source electrode cap layer is smaller than that between the slope-shaped grid and the drain electrode cap layer. The field effect transistor has the advantages of being high in drain electrode output current and excellent in frequency property.

Owner:XIDIAN UNIV

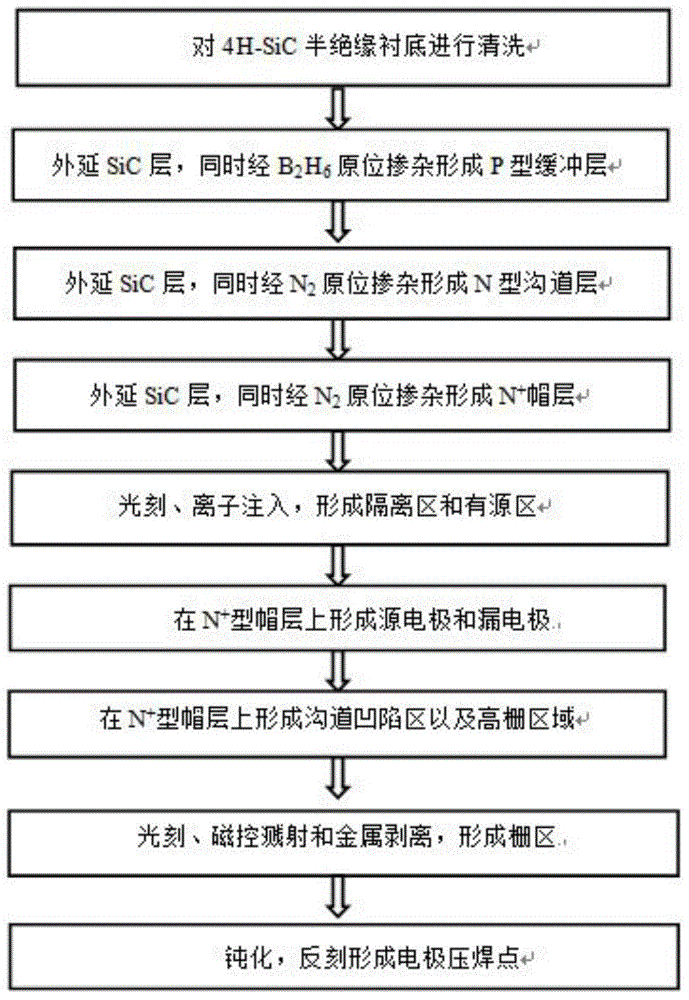

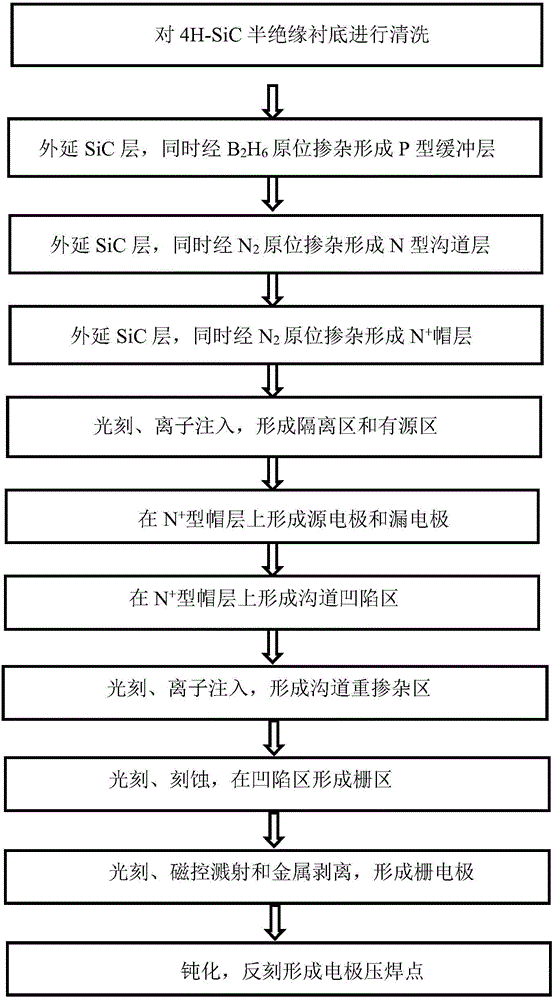

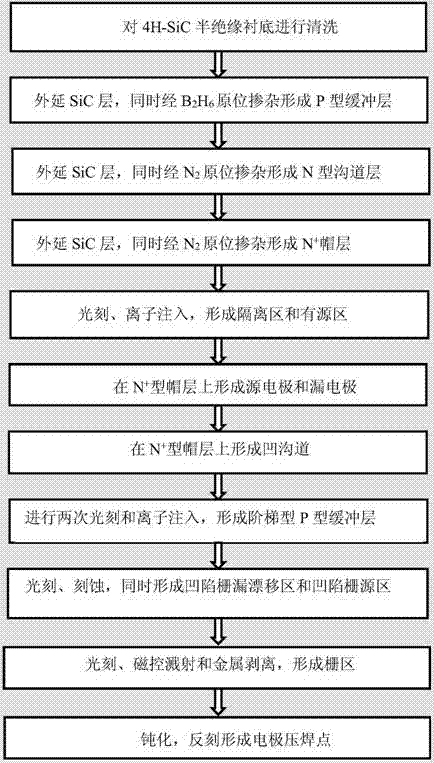

Preparation method for metal semiconductor field effect transistor with wide channel and deep recesses

InactiveCN104867835AGood barrierSimple processSemiconductor/solid-state device manufacturingSemiconductor devicesLithographic artistPower flow

The invention belongs to the technical field of field effect transistors, and particularly discloses a preparation method for a metal semiconductor field effect transistor with wide channels and deep recesses. The preparation method for the metal semiconductor field effect transistor with the wide channels and deep recesses settles the problems in prior art and has advantages of realizing simple manufacture process, enlarging an output current and a breakdown voltage, and improving frequency characteristic. The preparation method comprises the steps of cleaning a semi-insulating substrate; realizing epitaxial growth of a P-type buffer layer; realizing epitaxial growth of an N-type channel layer on the P-type buffer layer; realizing epitaxial growth of an N<+> cap layer on the N-type channel layer; preparing an isolation region and an active region; preparing a source electrode and a drain electrode; performing lithography and etching on the N<+> between the source electrode and the drain electrode, thereby forming a high-gate area; manufacturing a gate electrode; and manufacturing an electrode pads, thereby finishing device preparation.

Owner:XIDIAN UNIV

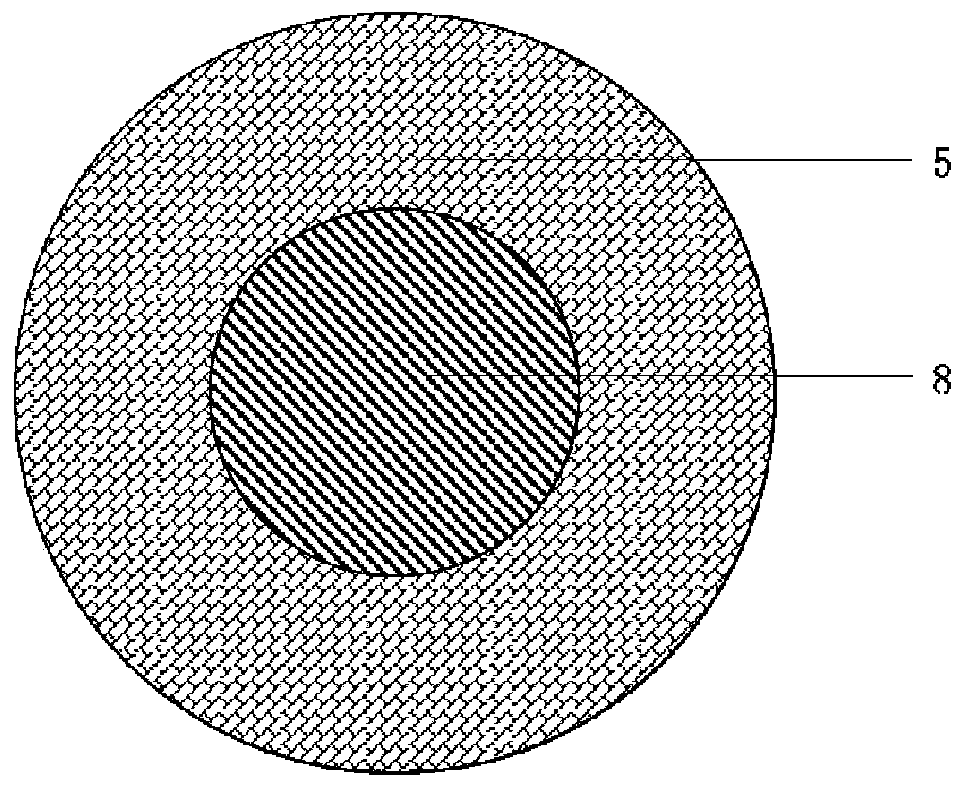

Ferroelectric material reconfigurable field effect transistor

InactiveCN110707152AReduce power consumptionReduce Logic LatencyNanoinformaticsSemiconductor devicesGate dielectricElectrical polarity

The invention discloses a ferroelectric material reconfigurable field effect transistor. The transistor includes a channel; a drain electrode arranged at one end of the channel; a source electrode arranged at the other end of the channel; a gate dielectric buffer layer arranged at the outer side of the channel, a ferroelectric material layer which wraps the outer side of the gate dielectric bufferlayer, a control gate and a polar gate which are arranged at the source electrode end and the drain electrode end respectively and at the outer side of the ferroelectric material layer, and an innerside wall and an outer side wall which are used for electrically isolating the control gate and the polar gate from the source electrode and the drain electrode. The ferroelectric material layer arranged at the outer side of the gate dielectric buffer layer can generate the polarized charges at the channel below the ferroelectric material layer, so that the control capability of the gate to the channel is improved, the turn-on voltage under a same gate voltage is increased, the sub-threshold swing of a device is reduced, and the static power consumption of the device is reduced. The gate dielectric buffer layer isolates the channel from the ferroelectric material, prevents the mutual diffusion of the channel and the ferroelectric material, and does not affect the polarization characteristics of the ferroelectric material layer.

Owner:EAST CHINA NORMAL UNIV +1

Semiconductor device having vertical surrounding gate transistor structure, method for manufacturing the same, and data processing system

InactiveUS8735970B2Drain current increasesMiniaturized and quickly responsive and low power consumptionSemiconductor devicesData processing systemEngineering

Owner:LONGITUDE SEMICON S A R L

Semiconductor device and manufacturing method thereof

InactiveCN101075582AThe drain current Ids increasesImproved current drive performanceSemiconductor/solid-state device manufacturingDrain currentField-effect transistor

A method of manufacturing a semiconductor device having a field effect transistor with improved current driving performance (increase of drain current) of a field effect transistor comprising the steps of ion implanting a group IV element from the main surface to the inside of a silicon layer as a semiconductor substrate to a level shallower than the implantation depth of the impurities in the step of forming the semiconductor region before the step of ion implanting impurities from the main surface to the inside of the silicon layer as a semiconductor substrate to form the semiconductor region being aligned with the gate electrode.

Owner:RENESAS TECH CORP

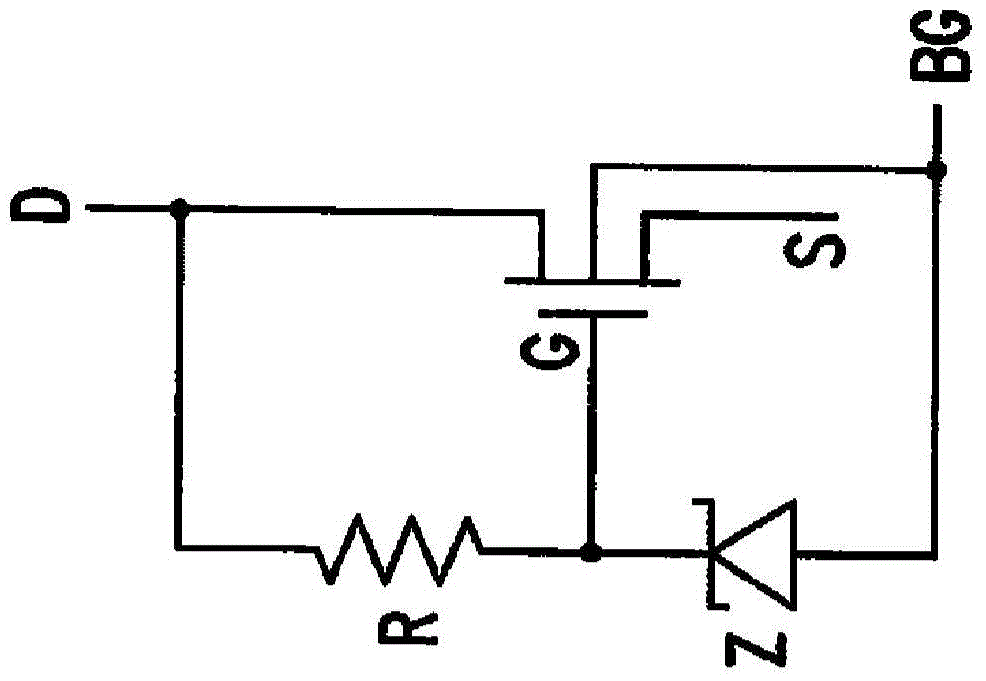

Semiconductor component, manufacturing method thereof and operating method thereof

ActiveCN105097801AIncrease maskAdvanced technologySolid-state devicesSemiconductor/solid-state device manufacturingZener diodeEngineering

The invention discloses a semiconductor component, a manufacturing method thereof and an operating method thereof. The semiconductor component includes a metal oxide semiconductor transistor, a resistor and a Zener diode. The metal oxide semiconductor transistor includes a grid electrode, a source electrode and a drain electrode. One end of the resistor is electrically connected with the drain electrode, and the resistor has a resistance value high enough to enable most current to flow through the metal oxide semiconductor transistor. The Zener diode includes a cathode and an anode, the cathode is electrically connected with the grid electrode and the other end of the resistor, and the anode is electrically connected with a grid electrode of a substrate.

Owner:MACRONIX INT CO LTD

Metal semiconductor field effect transistor with wide-channel deep sags

InactiveCN104916706ADrain current increasesTotal charge increaseSemiconductor devicesFrequency characteristicBreakdown voltage

The invention belongs to the technical field of field effect transistors, and especially discloses a metal semiconductor field effect transistor with wide-channel deep sags. The invention aims to provide a metal semiconductor field effect transistor with wide-channel deep sags which has higher output current and breakdown voltage and better frequency characteristic. The technical scheme adopted is as follows: a 4h-SiC half-insulating substrate, a P-type buffer layer and an N-type channel layer are arranged from top to bottom; a source cap layer and a drain cap layer are respectively arranged at the two sides of the N-type channel layer; a gate electrode is arranged in the middle of the N-type channel layer and close to the side where the source cap layer is arranged; the gate electrode enables a left channel sag area and a right channel sag area to be formed at the two sides of the N-type channel layer; the depths of the left channel sag area and the right channel sag area are 0.15-0.25 microns; the width of the left channel sag area is 0.5 microns, and the width of the right channel sag area is 1 micron; and a high-gate area is formed between the channel surface and the gate electrode.

Owner:XIDIAN UNIV

GaN-based P-type grid-enhanced type HEMT device and preparation method thereof

InactiveCN105655388AImprove reliabilityEnhanced featuresSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsDrain current

The invention provides a GaN-based P-type grid-enhanced type HEMT device and a preparation method thereof. The device comprises a substrate layer, a channel layer, a barrier layer, a grid electrode and a drain electrode; the channel layer is arranged on the substrate layer, the barrier layer is arranged on the channel layer, the grid electrode penetrates through the barrier layer, the drain electrode is arranged on the barrier layer, and P-type diamond is adopted as the grid electrode. The preparation method of the device comprises the following steps that 1, GaN deposition is performed on the substrate layer to form the channel layer; 2, an AlGaN layer grows on the channel layer; 3, a layer of the p-type diamond grows on the barrier layer to form the grid electrode; 4, a source electrode and the drain electrode are formed on the portions, on the two sides of the grid electrode, of the barrier layer respectively. According to the GaN-based P-type grid-enhanced type HEMT device and the preparation method thereof, the P-type diamond grid electrode is adopted, an energy band can be improved, the enhanced characteristic is achieved by using up channel electrons when the grid voltage is 0, regulation on threshold voltage of the device can be achieved, and small grid currents are kept while drain currents are increased.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS

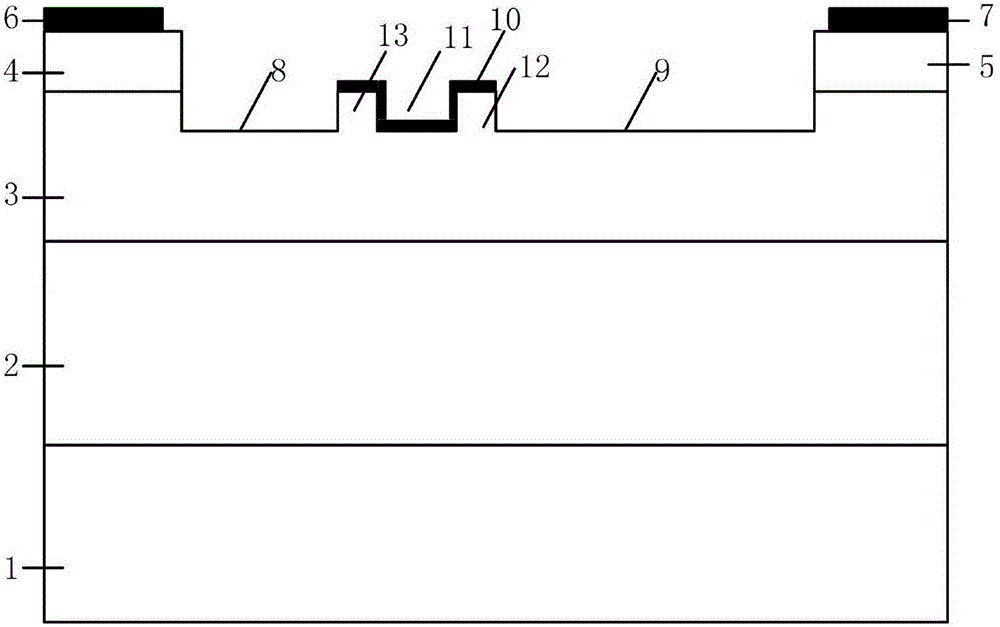

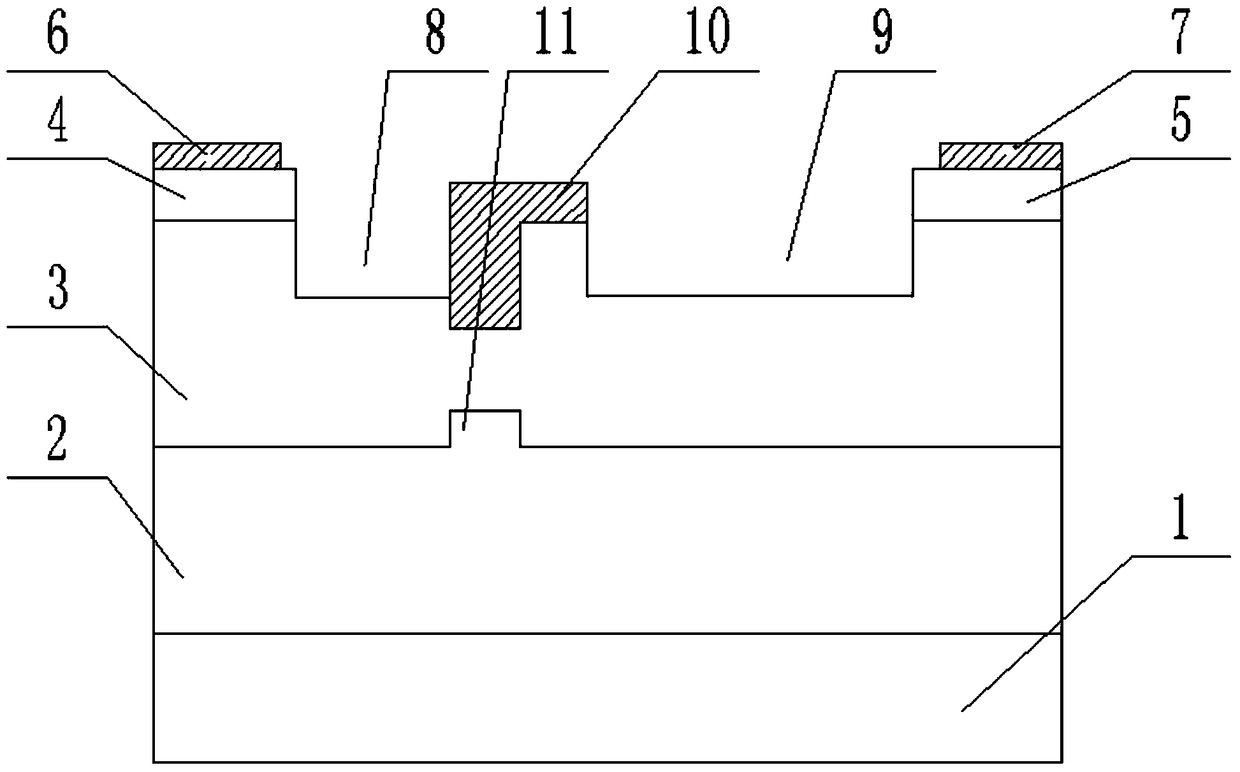

Field effect transistor with three-sag structure and preparation method thereof

ActiveCN104916698ADrain current increasesIncreased saturation leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsPower flow

The invention belongs to the technical field of field effect transistors, and especially discloses a field effect transistor with a three-sag structure and a preparation method thereof. The invention aims to provide a field effect transistor with a three-sag structure which has wide-channel deep sags and has higher output current and breakdown voltage and better frequency characteristic, and a preparation method thereof. The technical scheme adopted is as follows: a 4h-SiC half-insulating substrate, a P-type buffer layer and an N-type channel layer are arranged from top to bottom; a source cap layer and a drain cap layer are respectively arranged at the two sides of the N-type channel layer; a source electrode and a drain electrode are respectively arranged on the surfaces of the source cap layer and the drain cap layer; a ladder-shaped gate electrode is arranged in the middle of the N-type channel layer and close to the side where the source cap layer is arranged; and a left channel and a right channel are respectively formed at the two sides of the gate electrode and the N-type channel layer.

Owner:XIDIAN UNIV

Intercalated Superlattice Compositions and Related Methods for Modulating Dielectric Property

InactiveUS20100173165A1Low working voltageDrain current increasesMaterial nanotechnologySemiconductor/solid-state device detailsDielectricElectric properties

Compositions, methods of using inorganic moieties for dielectric modulation, and related device structures.

Owner:MARKS TOBIN J +1

Transistor and formation method

ActiveCN104952921AIncrease the number ofHighly integratedSemiconductor/solid-state device manufacturingSemiconductor devicesMedia layerTransistor

The invention provides a transistor and a formation method thereof. The formation method of the transistor includes providing a substrate and forming a plurality of insulating layers and a plurality of fake grid layers stacked at intervals on the surface of the substrate; forming a through hole in the insulating layers and the fake grid layers, wherein the bottom of the through hole is at the surface of the substrate; forming a channel layer on the surface of the through hole; removing the fake grid layers so as to form grooves between adjacent insulating layers; forming grid medium layers on the surface of the inner wall of a grooves and the surface of the channel layer; forming grids filling the grooves and the through hole on the surfaces of the grid medium layers. By adopting the above method, integration level of the transistor can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

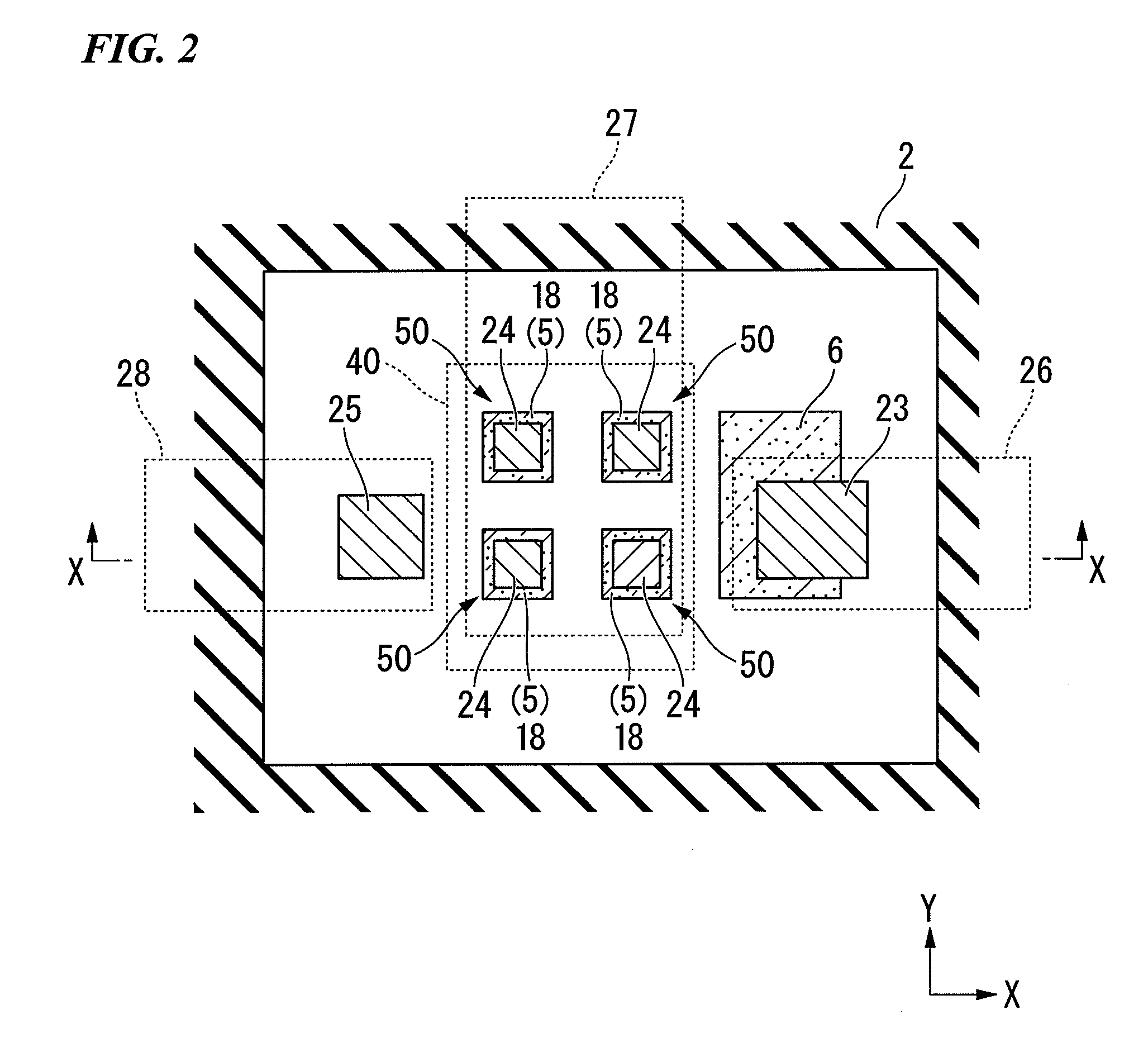

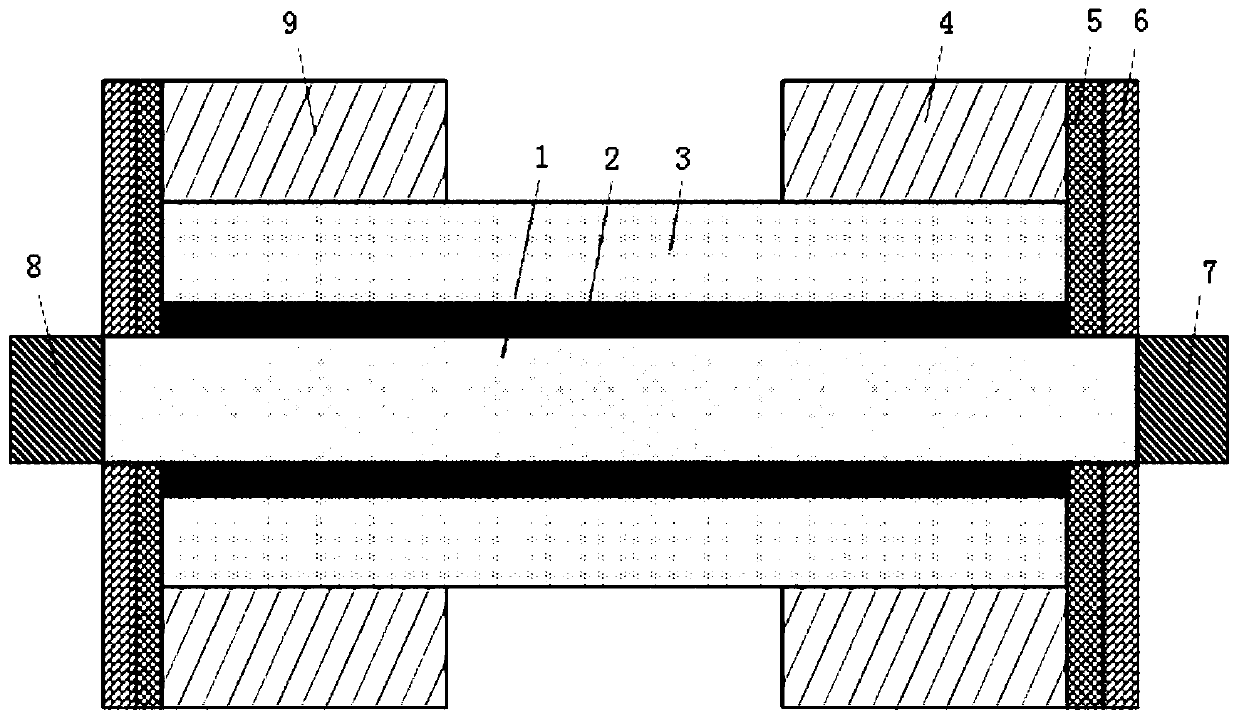

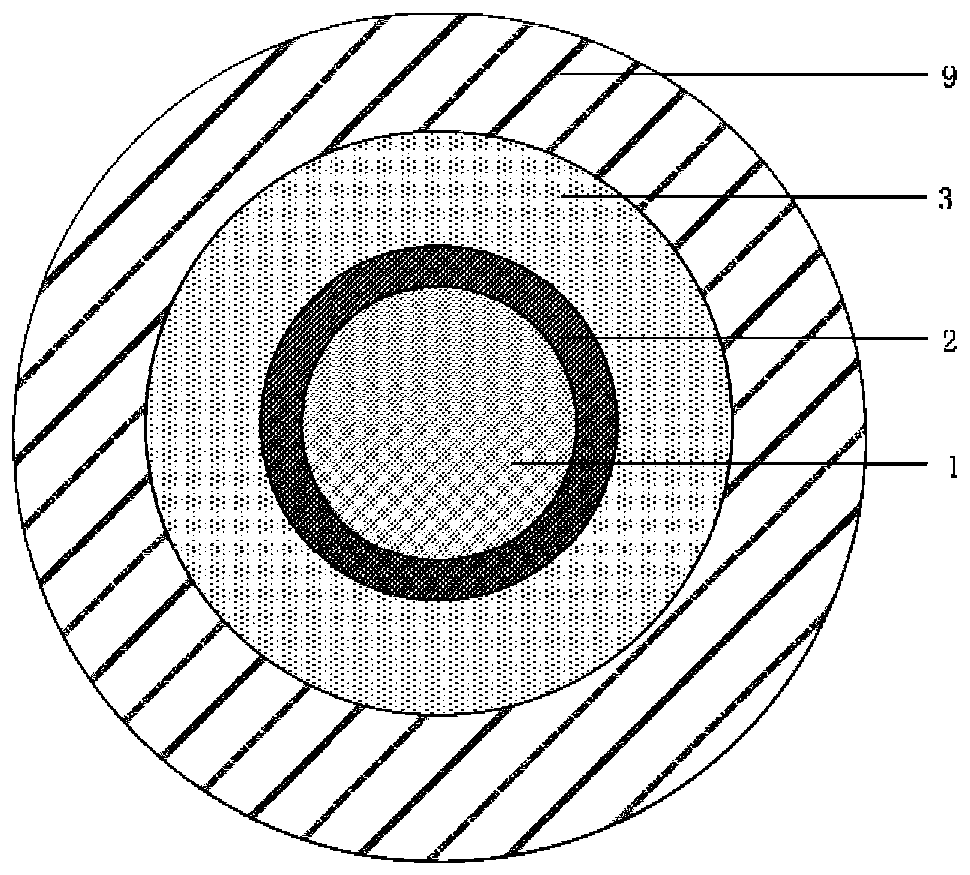

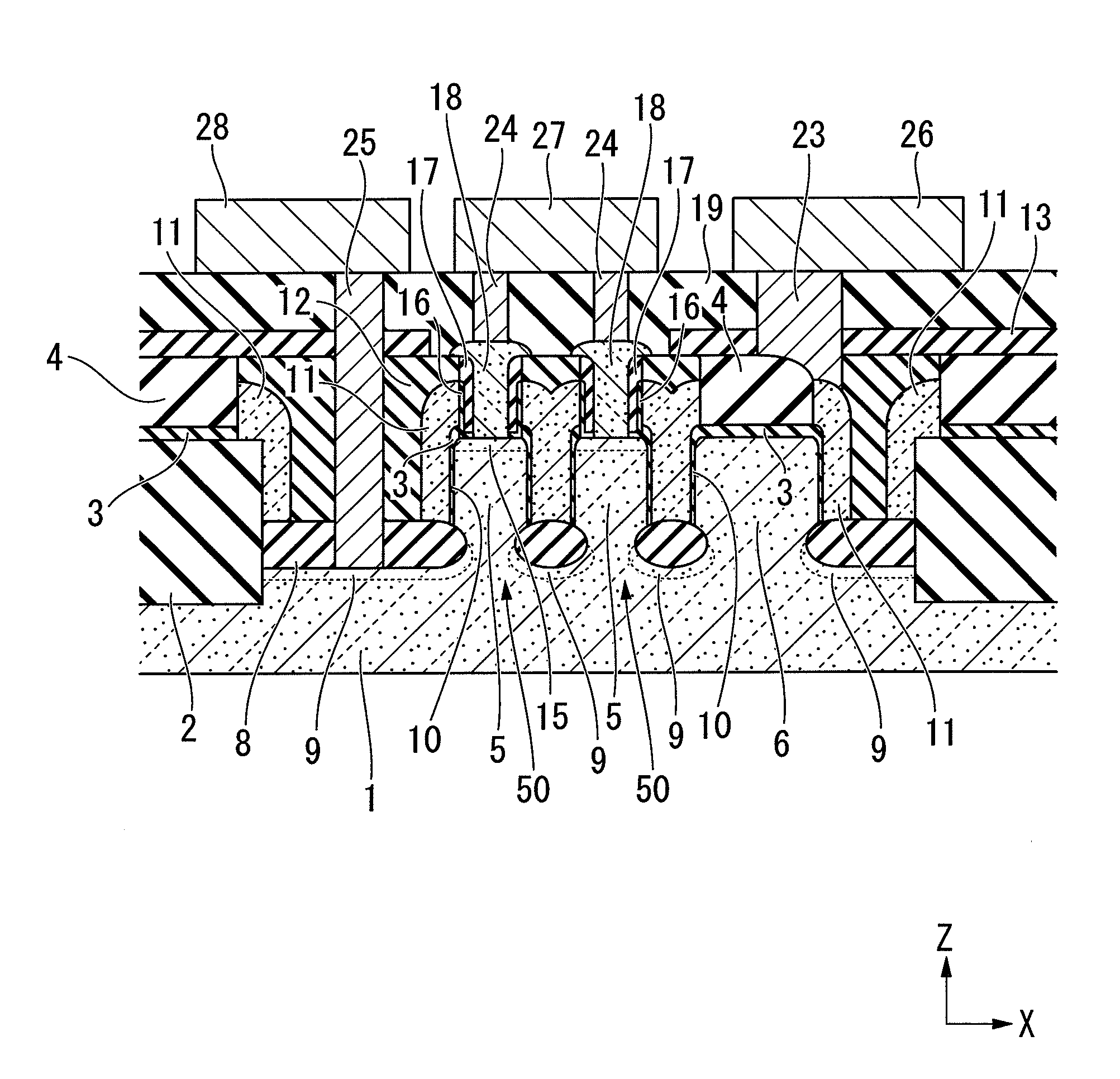

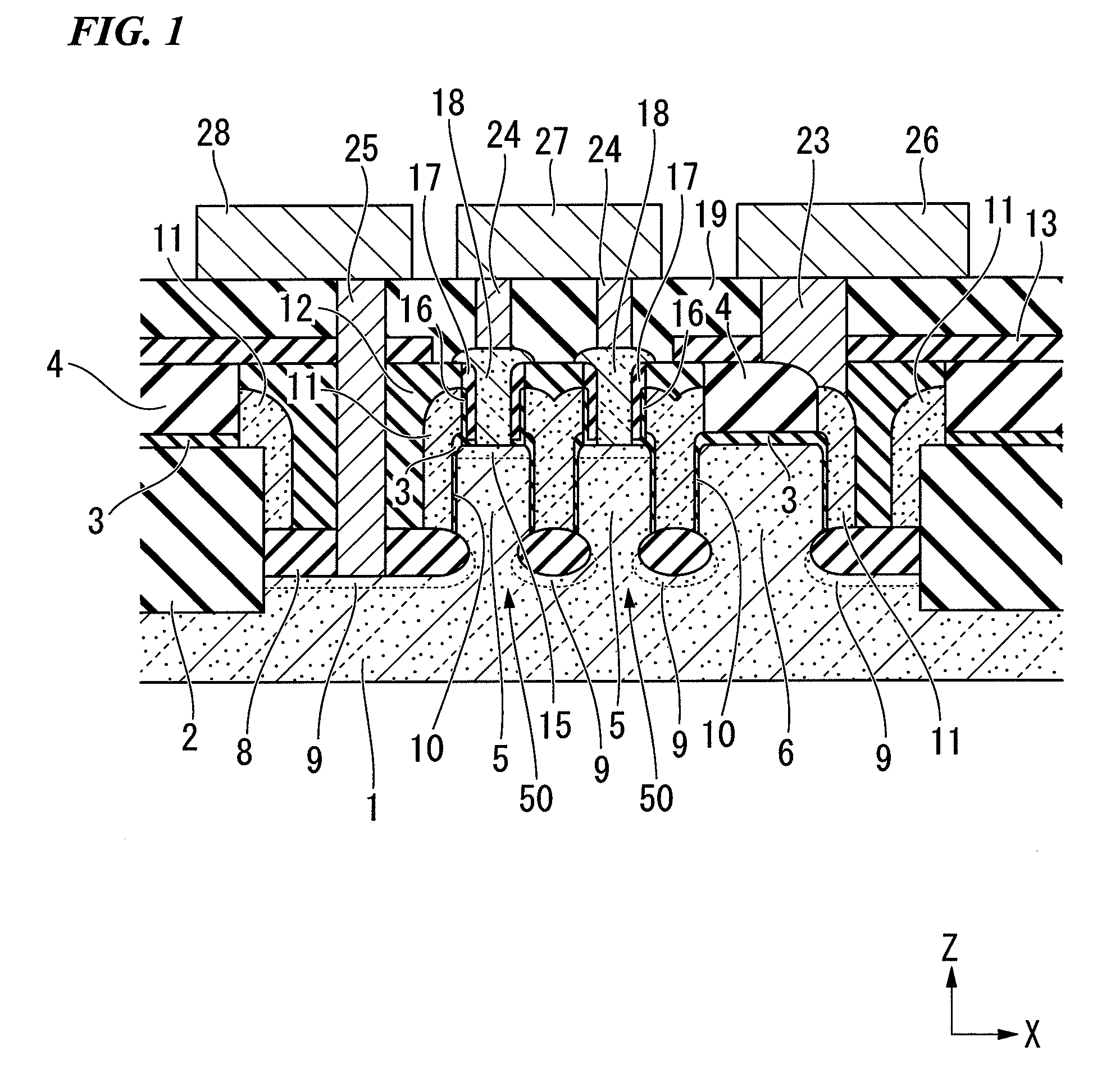

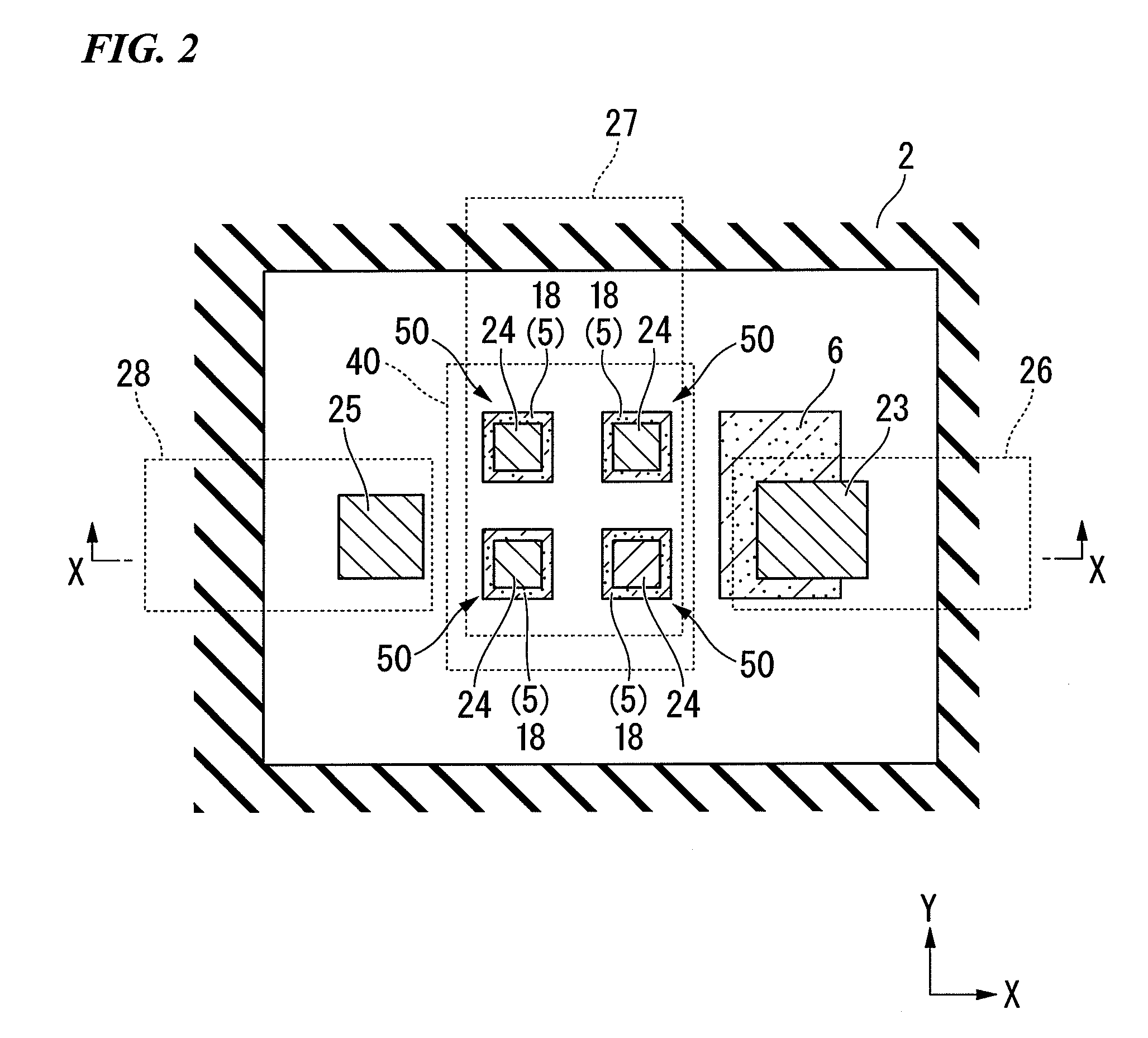

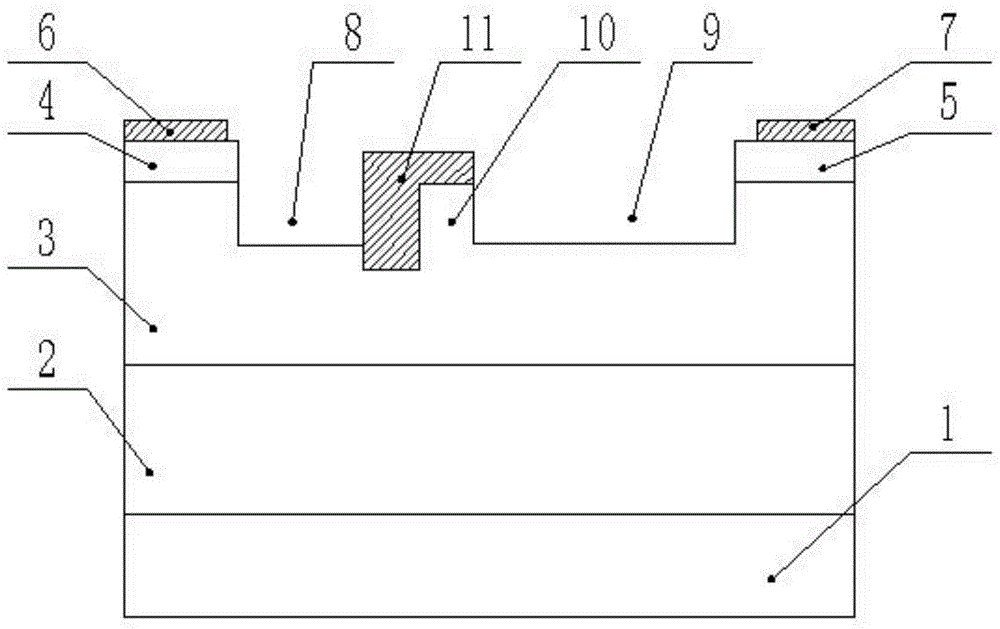

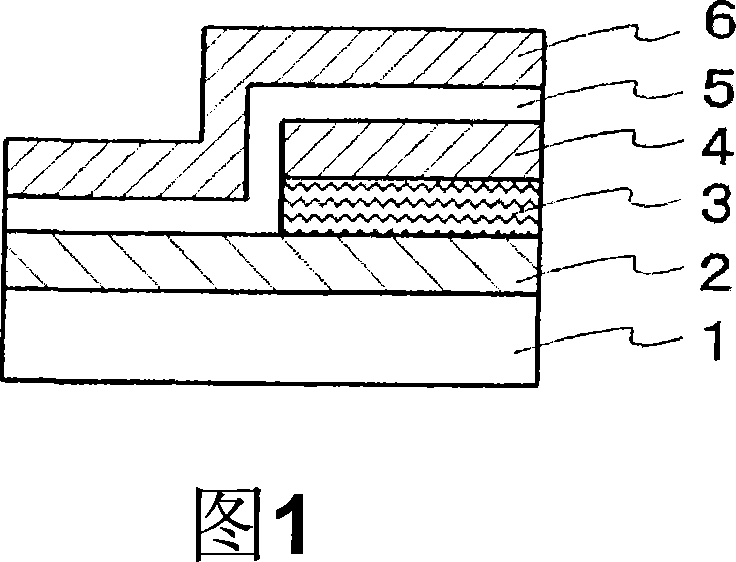

Organic semiconductor element and organic el display device using the same

InactiveCN1934714AImprove featuresNo coverage issuesTransistorSolid-state devicesDisplay deviceSemiconductor package

An organic semiconductor element provided with an FET having a structure that can control a channel length short and prevents contact resistance due to a step part from increasing, and a high aperture ratio organic light emitting display device using the organic FET. On a substrate (1), a first conductive layer (2) is provided as one of source / drain electrodes, and on the first conductive layer (2), an organic semiconductor layer (3) and a second conductive layer (4) to be the other of the source / drain electrodes are provided. Then, on a side plane of the organic semiconductor layer or a front plane of the semiconductor layer (3) exposed by removing a part of the second conductive layer, and on a side plane of the second conductive layer, a gate electrode (third conductive layer) (6) is provided through an insulating layer (5) to form the FET. The organic semiconductor element is provided with the FET. The organic EL display device has the FET having such structure stacked on an organic EL part as a drive element.

Owner:ROHM CO LTD

Semiconductor device

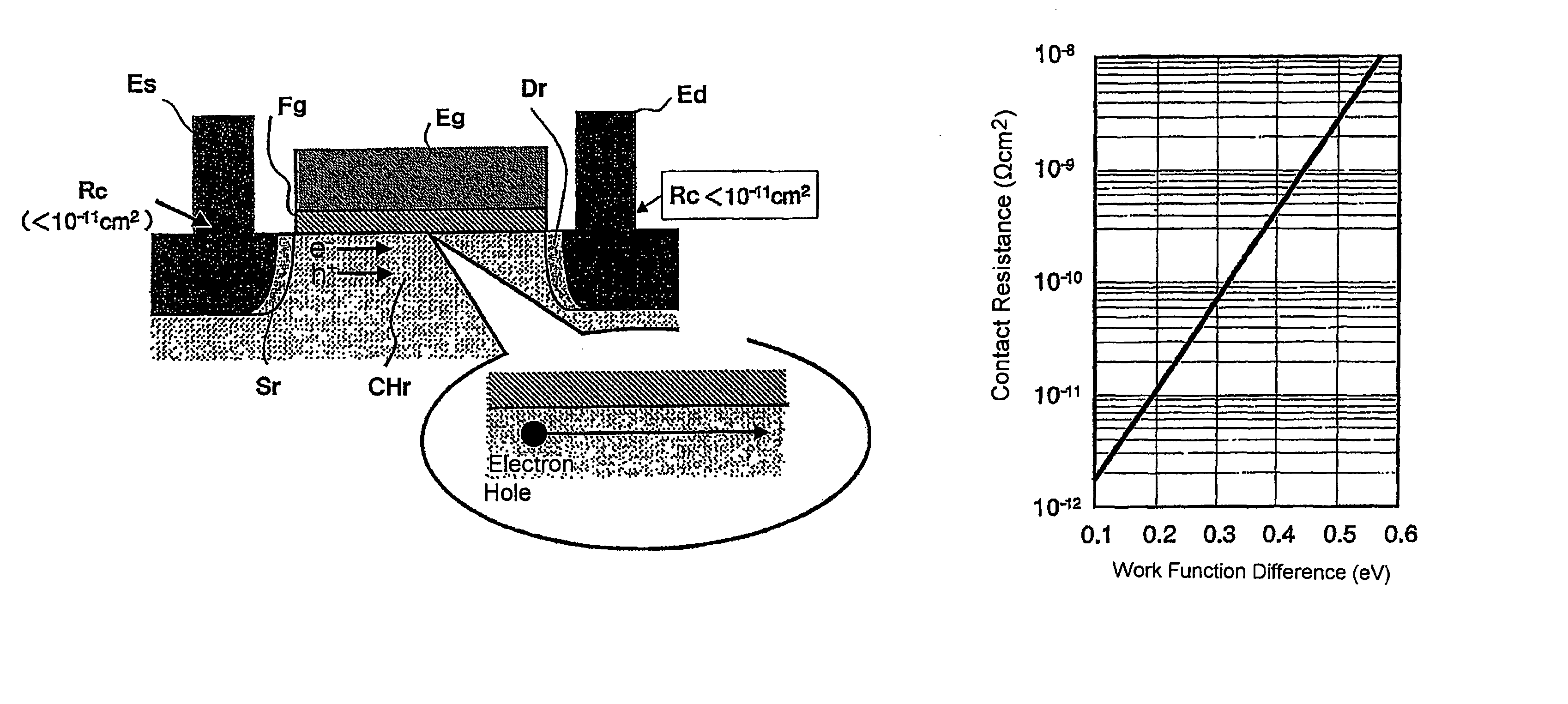

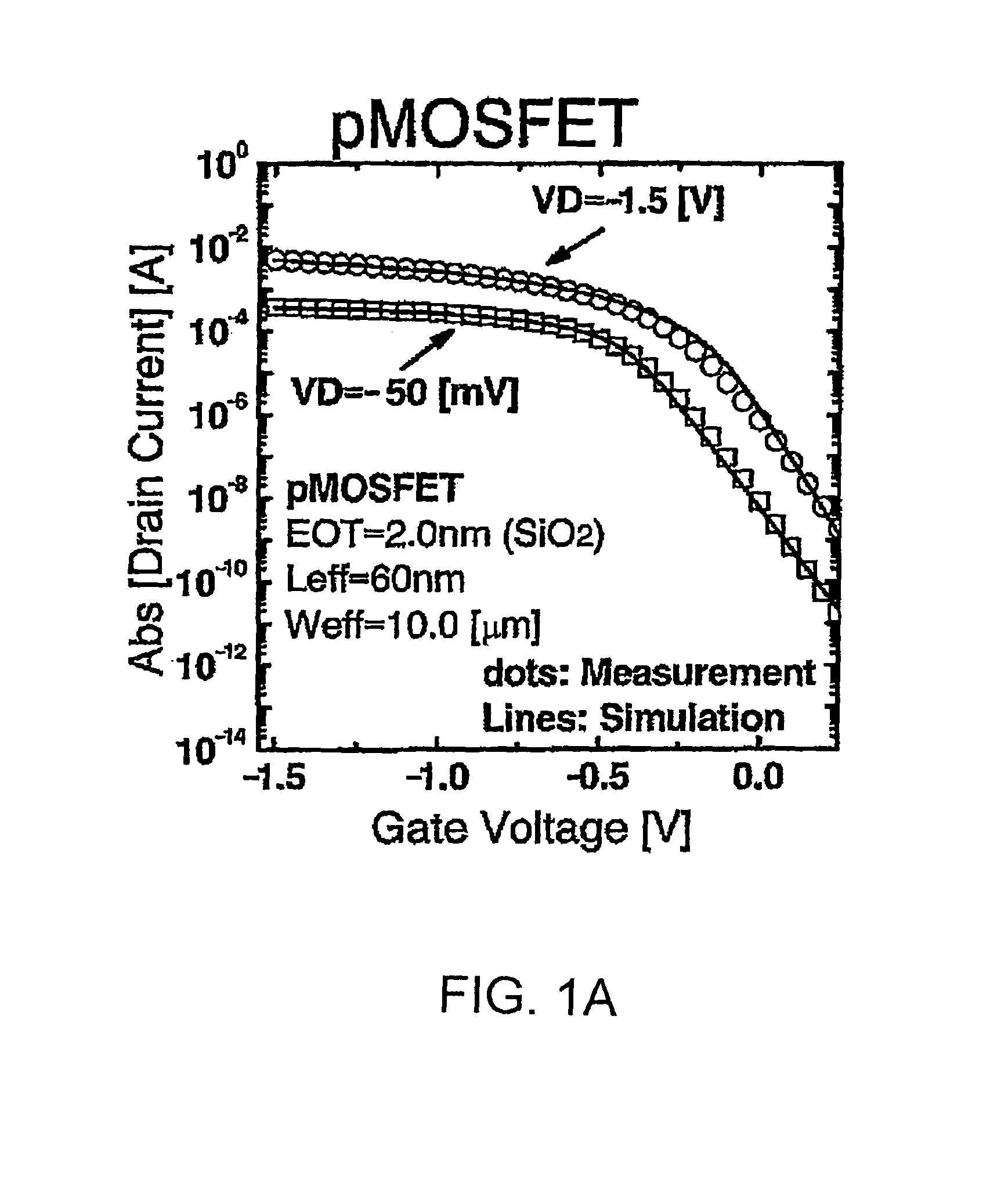

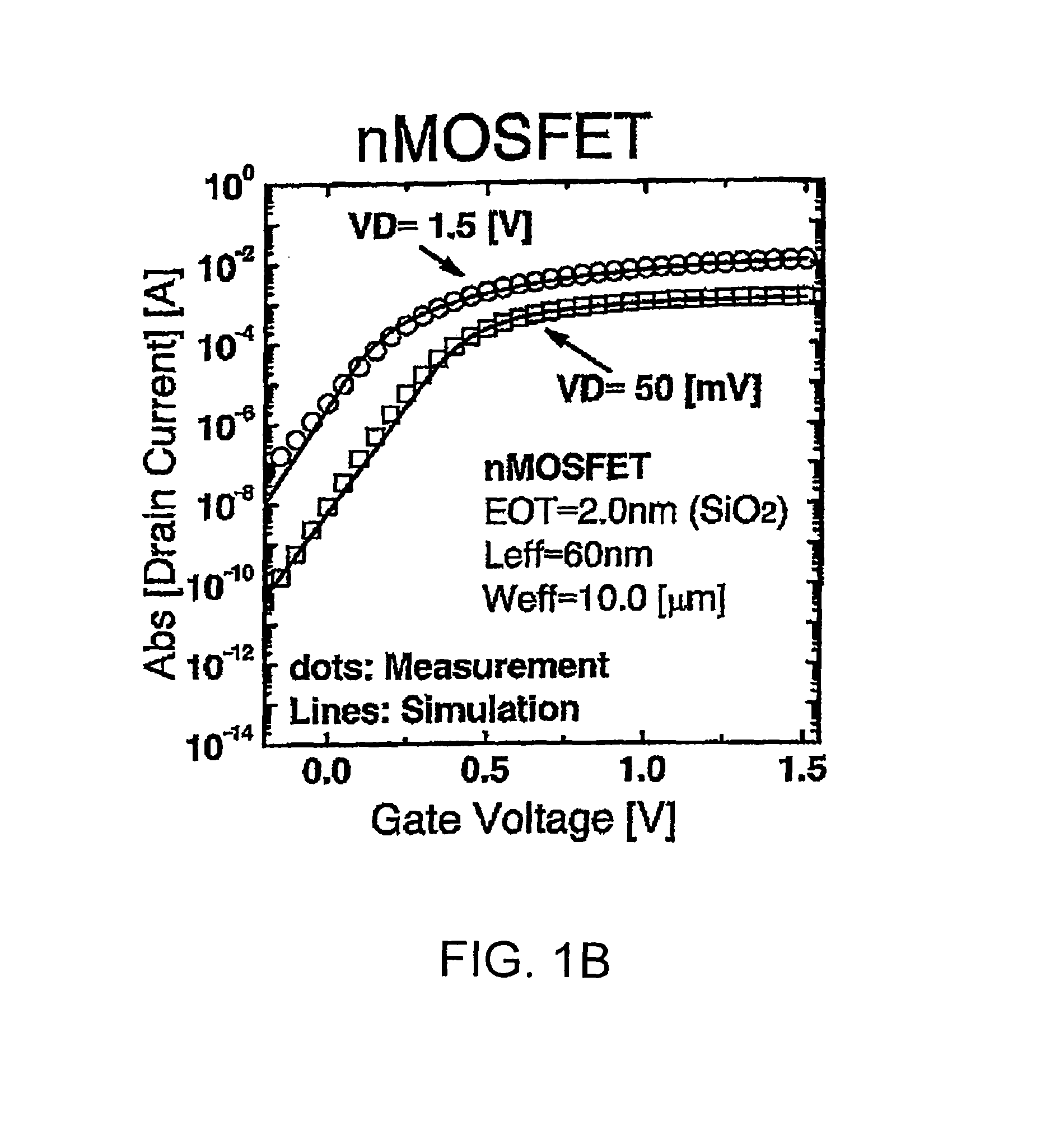

ActiveUS8362567B2Drain current increasesIncrease currentSolid-state devicesSemiconductor/solid-state device manufacturingHydrogenDevice material

In a semiconductor device, the degree of flatness of 0.3 nm or less in terms of a peak-to-valley (P-V) value is realized by rinsing a silicon surface with hydrogen-added ultrapure water in a light-screened state and in a nitrogen atmosphere and a contact resistance of 10−11 Ωcm2 or less is realized by setting a work function difference of 0.2 eV or less between an electrode and the silicon. Thus, the semiconductor device can operate on a frequency of 10 GHz or higher.

Owner:TOHOKU UNIV +1

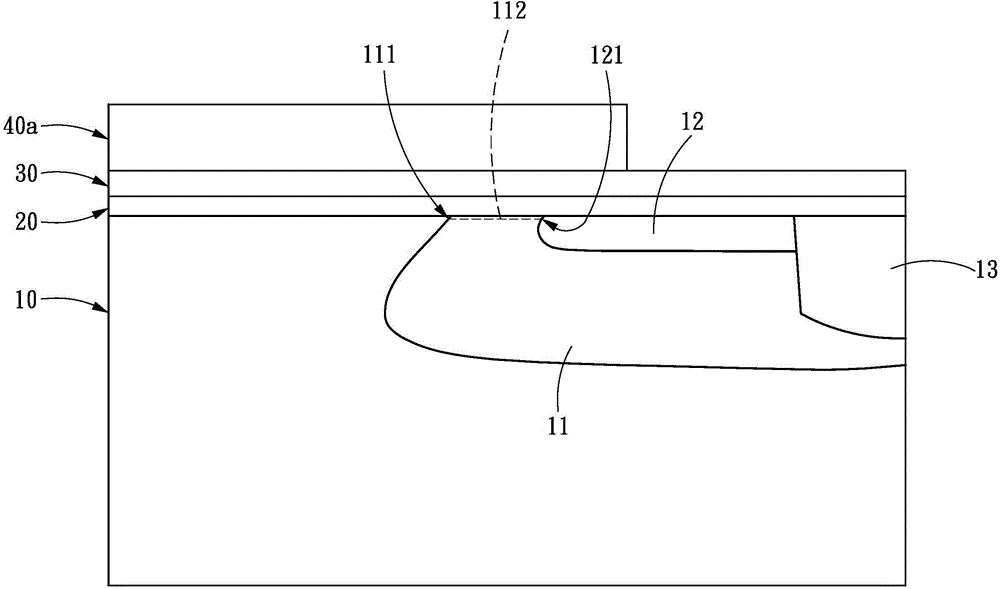

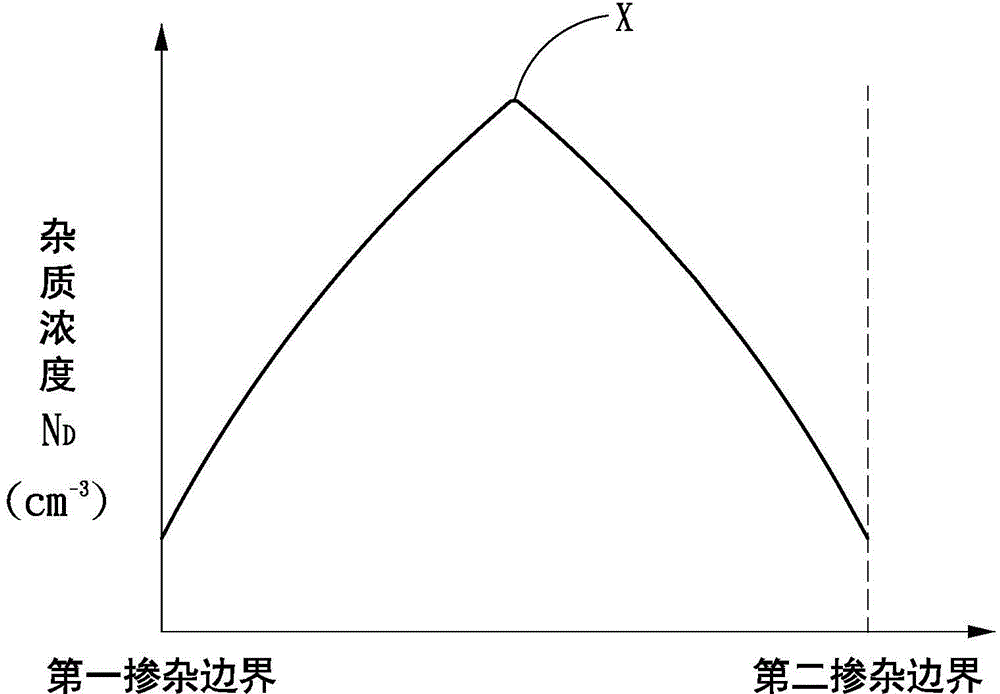

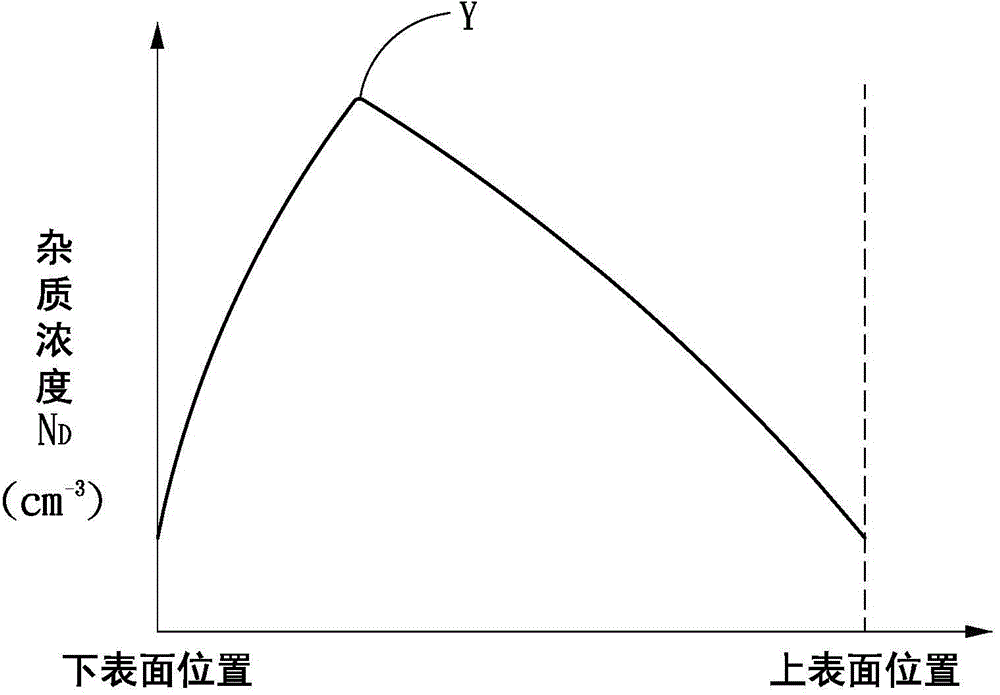

Carborundum semiconductor element and manufacture method for the same

ActiveCN105810731APrevent accidental openingIncrease the on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDrain currentEngineering

The invention discloses a carborundum semiconductor element and a manufacture method for the same. The manufacture method comprises steps of arranging a channel control area, and enabling the channel control area to have a foreign matter concentration distribution which progressively increases from a first doped boundary, achieves a maximum value between the first doped boundary and a second doped boundary, and progressively decreases toward the second doped boundary. The manufacture method enables the carborundum semiconductor element to reduce the conduction resistor and improve the drain current without sacrificing the critical voltage.

Owner:SHANGHAI HESTIA POWER INC

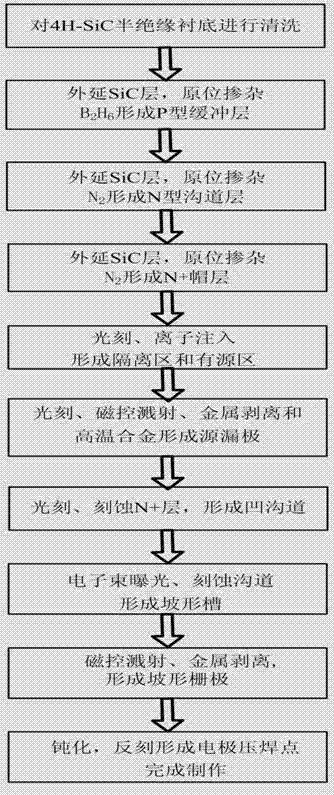

Method of preparing 4H-SiC metal semiconductor field effect transistor with part highly-doped channel

InactiveCN105789056AImprove transconductanceSimple processTransistorSemiconductor/solid-state device manufacturingFrequency characteristicTransconductance

The invention discloses a method of preparing a 4H-SiC metal semiconductor field effect transistor with a part highly-doped channel, which can improve output current and device transconductance and improve frequency characteristics. According to the adopted technical scheme, a P-type buffer layer is formed on a 4H-SiC semi-insulated substrate; an N-type channel layer is formed on the P-type buffer layer; an N<+>-type cap layer is formed on the N-type channel layer; an isolation area and an active area are formed on the N<+>-type cap layer; the active area is processed to form a source electrode and a drain electrode; the N<+>-type cap layer between the source electrode and the drain electrode is processed to form a concave channel area; heavy doping is carried out on an area right below the concave channel area; the concave channel between the source electrode and the drain electrode is processed to form a gate area; the gate area is processed to form a gate electrode; and the surface of the formed 4H-SiC metal semiconductor field effect transistor is processed to form an electrode pressure welding point. And thus, manufacturing of the device is completed.

Owner:XIDIAN UNIV

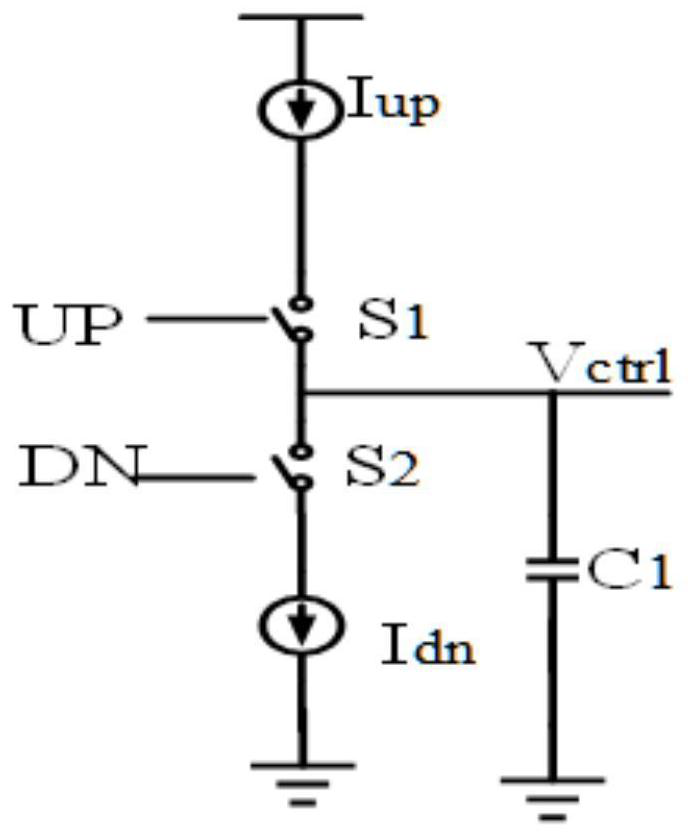

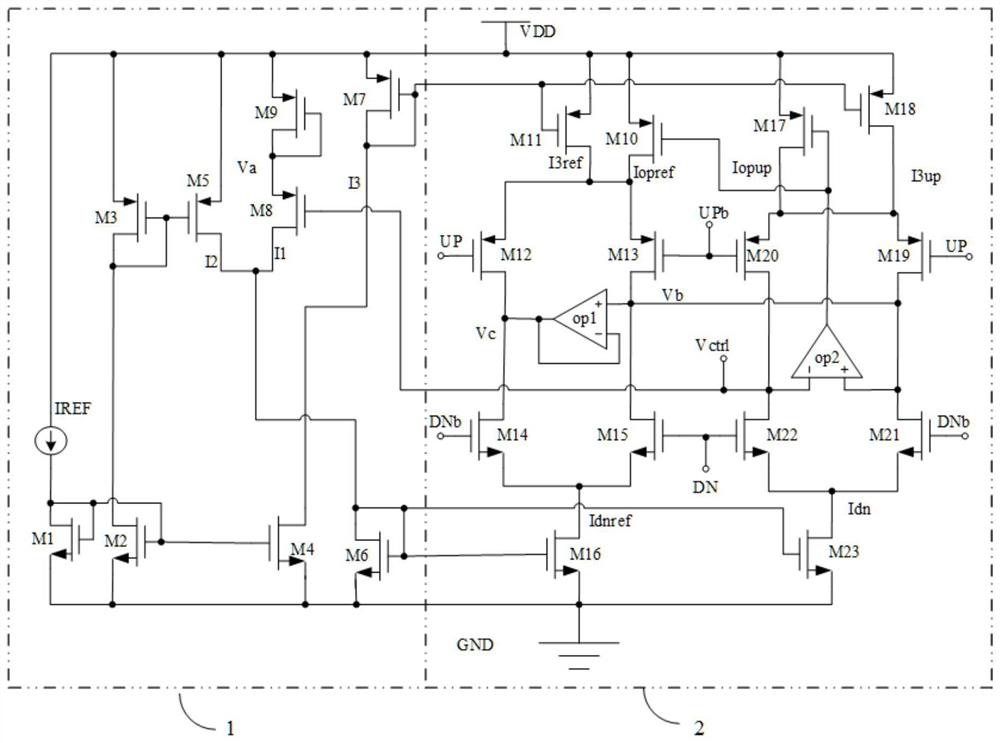

Charge pump with wide locking range and low current mismatch

ActiveCN112653327AReduce current mismatchDrain current increasesApparatus without intermediate ac conversionCharge currentGate voltage

The invention discloses a charge pump with a wide locking range and low current mismatch. The charge pump comprises a charge pump biasing circuit, a charge pump core circuit and the like. According to the invention, the PMOS tube M9 of the charge pump biasing circuit is connected through a diode, and the grid electrode of the PMOS tube M8 is connected with the output end of the charge pump, so that the problem that the discharge current is small when the output voltage of the charge pump is low is solved in the discharge state, and the voltage dynamic range of the output end of the charge pump is enlarged; an error amplifier op1 in a charge pump core circuit adopts unit gain connection, so that a charge sharing effect can be suppressed at the moment of charge / discharge conversion; and the PMOS tube M17 and the PMOS tube M10 respectively form a feedback compensation circuit with an error amplifier op2, and the voltage of the output end of the charge pump in a charging state is gradually increased so as to reduce the grid voltage of the PMOS tube M17 and the grid voltage of the PMOS tube M10 and increase the charging current, so that the dynamic range of the voltage of the output end of the charge pump is further enlarged so as to achieve the charge pump with wide locking range and low current mismatch.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

4h-sic metal-semiconductor field-effect transistor with sloped gate and manufacturing method

ActiveCN104282764BDrain current increasesLower channel resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowSemi insulating

The invention discloses a 4H-SiC metal semiconductor field effect transistor with a slope-shaped grid. The 4H-SiC metal semiconductor field effect transistor comprises a 4H-SiC semi-insulating substrate, a P-type buffer layer and an N-type channel layer from bottom to top, a source electrode cap layer and a drain electrode cap layer are arranged on the surface of the N-type channel layer, a source electrode and a drain electrode are arranged on the surface of the source electrode cap layer and the surface of the drain electrode cap layer respectively, a slope-shaped groove inclined towards one side of the source electrode cap layer is formed in the upper end face of the N-type channel layer, the slope-shaped grid is arranged is arranged in the slope-shaped groove, the lower end face of the slope-shaped grid is matched with the slope-shaped groove, the upper end face of the slope-shaped grid is parallel to the upper end face of the N-type channel layer, and the distance between the slope-shaped grid and the source electrode cap layer is smaller than that between the slope-shaped grid and the drain electrode cap layer. The field effect transistor has the advantages of being high in drain electrode output current and excellent in frequency property.

Owner:XIDIAN UNIV

4H-SiC metal semiconductor field effect transistor having double high gates

ActiveCN105932047ADrain current increasesIncreased maximum output power densitySemiconductor devicesPhysicsSemi insulating

The invention relates to a 4H-SiC metal semiconductor field effect transistor having double high gates. The 4H-SiC metal semiconductor field effect transistor comprises a 4H-SiC semi-insulating substrate, a P-type buffer layer and an N-type channel layer which are arranged from the bottom to the top in turn. The two sides of the N-type channel layer are respectively provided with a source cap layer and a drain cap layer. The surfaces of the source cap layer and the drain cap layer are respectively provided with a source electrode and a drain electrode. A gate electrode is formed on one side which is close to the source cap layer and arranged above the N-type channel layer. A left channel concave region, a right channel concave region and a middle channel concave region are formed at the left side, the right side and the middle of the N-type channel by the gate electrode. A left high gate region and a right high gate region are formed between the surface of the channel and the gate electrode. The advantages of the 4H-SiC metal semiconductor field effect transistor are that drain current is enhanced, breakdown voltage is enabled and the frequency characteristics are improved.

Owner:XIDIAN UNIV

4h-sic metal-semiconductor field-effect transistor with stepped buffer layer structure

ActiveCN104393047BDrain current increasesIncrease currentSemiconductor/solid-state device manufacturingSemiconductor devicesTwo stepSemi insulating

The invention discloses a 4H-SiC metal semiconductor field effect transistor with a step buffer layer structure. The 4H-SiC metal semiconductor field effect transistor comprises a 4H-SiC semi-insulating substrate, a P-type buffer layer and an N-type channel layer from the bottom to the top. The two sides of the N-type channel layer are respectively provided with a source electrode cap layer and a drain electrode cap layer. The surface of the source electrode cap layer and the drain electrode cap layer is respectively provided with a source electrode and a drain electrode. A gate electrode is formed on one side which is arranged above the N-type channel layer and close to the source electrode cap layer. A concave gate source drift region is formed between the gate electrode and the source electrode cap layer. A concave gate drain drift region is formed between the gate electrode and the drain electrode cap layer. The position, which is arranged on the upper end surface of the P-type buffer layer and close to the source electrode cap layer, is provided with a groove. One side, which is arranged in the groove and close to the drain electrode cap layer, is provided with two steps. The 4H-SiC metal semiconductor field effect transistor with the step buffer layer structure has advantages of being stable in breakdown voltage and high in output drain electrode current.

Owner:XIDIAN UNIV

Field effect transistor with gamma gate and recessed buffer layer and its preparation method

ActiveCN104882483BDrain current increasesTotal charge increaseSemiconductor devicesPhysical chemistryEngineering

The invention belongs to the technical field of field effect transistors and provides a field effect transistor equipped with a gamma-gate and a recessed buffer layer and a preparation method thereof, wherein the field effect transistor has a wide channel and a deep recess and is increased in output current and breakdown voltage and improved in frequency characteristic. An employed technical scheme is that a 4F-SiC semi-insulated substrate, a P-type buffer layer, an N-type channel layer are arranged from top to bottom; a source electrode cap layer and a drain electrode cap layer are arranged on both sides of the N-type channel layer respectively; the surface of the source electrode cap layer and the surface of the drain electrode cap layer are provided with a source electrode and a drain electrode respectively; a stepped gate electrode is disposed on a side, close to the source electrode cap layer, of the middle of the N-type channel layer; a left channel and a right channel are formed between both sides of the N-type channel layer and the gate electrode respectively; the low gate surface of the gate electrode is flush with the surface of the N-type channel layer; and a groove is disposed on the P-type buffer layer right under the low gate surface of the gate electrode.

Owner:XIDIAN UNIV

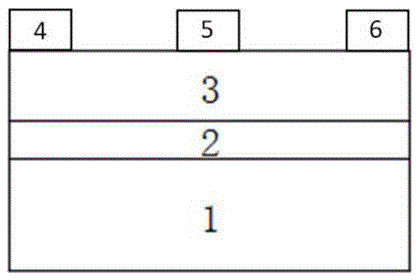

A Thin Film Transistor with Improved Drain Current

ActiveCN104900708BFast switching speedDrain current increasesTransistorSwitched currentCharge carrier

The invention provides a drain current-improved thin film transistor. The drain current-improved thin film transistor includes a substrate, a gate insulating layer, an active layer, a source, a drain and a gate. The drain current-improved thin film transistor is characterized in that the active layer is doped, and a doping layer is gradient, or doping concentration is gradient; the gradient of the doping layer is increased from the source to the drain; and the gradient of the doping concentration is increased from the source to the drain. A material with a certain gradient is doped in the active layer, and therefore, when voltage of the source and the drain is boosted, a large number of carriers are adjacent to the drain, and thus, so the drain current at a saturated region will be increased, and a higher switching current ratio can be realized, and the switching speed of the component will become higher.

Owner:FUZHOU UNIV