4h-sic metal-semiconductor field-effect transistor with sloped gate and manufacturing method

A field-effect transistor and metal-semiconductor technology, which is applied in the field of 4H-SiC metal-semiconductor field-effect transistors and fabrication, can solve the problems of limited increase in device breakdown voltage, reduced device breakdown voltage, etc. Reduced channel resistance and small depletion area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

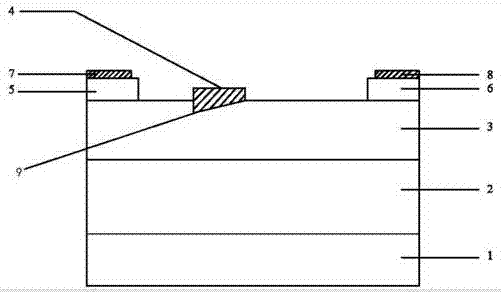

[0031] A 4H-SiC metal-semiconductor field-effect transistor with a 0.07 μm deep and 0.7 μm long sloped gate was fabricated.

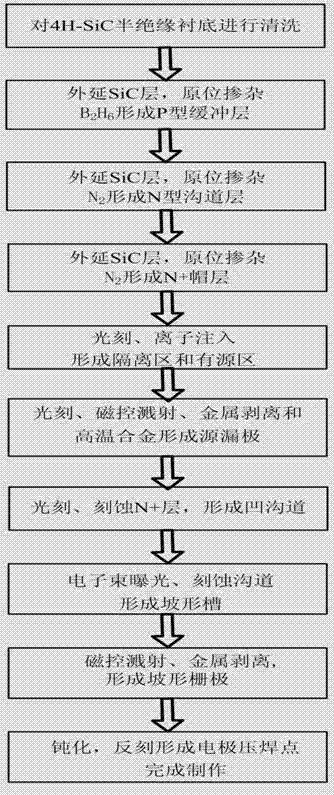

[0032] The manufacturing steps of this embodiment are as follows:

[0033] Step 1: cleaning the 4H-SiC semi-insulating substrate 1 to remove surface pollutants.

[0034] (1.1) Carefully wash the substrate twice with a cotton ball dipped in methanol to remove SiC particles of various sizes on the surface;

[0035] (1.2) Place the substrate in H 2 SO 4 :HNO 3 = Ultrasound for 5 minutes in 1:1;

[0036] (1.3) Put the substrate in 1# cleaning solution (NaOH:H 2 o 2 :H 2 O=1:2:5), boiled for 5 minutes, rinsed with deionized water for 5 minutes, and then put into 2# cleaning solution (HCl:H 2 o 2 :H 2 O=1:2:7) and boiled for 5 minutes. Finally rinsed with deionized water and rinsed with N 2 Blow dry and set aside.

[0037] Step 2: epitaxially grow a SiC layer on the surface of the 4H-SiC semi-insulating substrate 1, and diborane B 2 h 6 In-situ...

Embodiment 2

[0071] A 4H-SiC metal-semiconductor field-effect transistor with a sloped gate 0.06 μm deep and 0.7 μm long was fabricated.

[0072] In the manufacturing steps of this embodiment:

[0073] Step 8: Form a slope-shaped groove 9 on the concave channel between the source electrode 7 and the drain electrode 8 .

[0074] 1) Under the conditions of glue coating speed: 3000R / min, glue thickness > 2μm, use positive photoresist to carry out photolithography on the concave groove, make a photolithography plate according to the position of the slope grid, and expose it with electron beam;

[0075] 2) In special developer solution ((CH 3 ) 4 NOH:H 2 In O=1:4), the channel is developed, and the pattern on the photolithography plate is transferred to the concave channel between the source region and the drain region to form a gate pattern window, and then the reactive ion etching process is used to etch the concave groove At the same time, a groove with a length of 0.7 μm, a distance of ...

Embodiment 3

[0082] Embodiment 3: Fabricate a 4H-SiC metal-semiconductor field-effect transistor with a 0.08 μm deep and 0.7 μm long slope gate.

[0083] In the manufacturing steps of this embodiment:

[0084] Step 8: Form a slope-shaped groove 9 on the concave channel between the source electrode 7 and the drain electrode 8 .

[0085] 1) Under the conditions of coating speed: 3000R / min and glue thickness > 2μm, use positive photoresist to perform photolithography on the concave groove, make a photolithography plate according to the position of the slope grid, and expose it with electron beams;

[0086] 2) In special developer solution ((CH 3 ) 4 NOH:H 2 In O=1:4), the channel is developed, and the pattern on the photolithography plate is transferred to the concave channel between the source region and the drain region to form a gate pattern window, and then the reactive ion etching process is used to etch the concave groove At the same time, a groove with a length of 0.7 μm, a distanc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More