Preparation method for metal semiconductor field effect transistor with wide channel and deep recesses

A metal semiconductor and field effect transistor technology is applied in the field of preparation of metal semiconductor field effect transistors with wide channels and deep recesses, which can solve the problems of saturation current degradation, reduce drain current, lattice damage, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

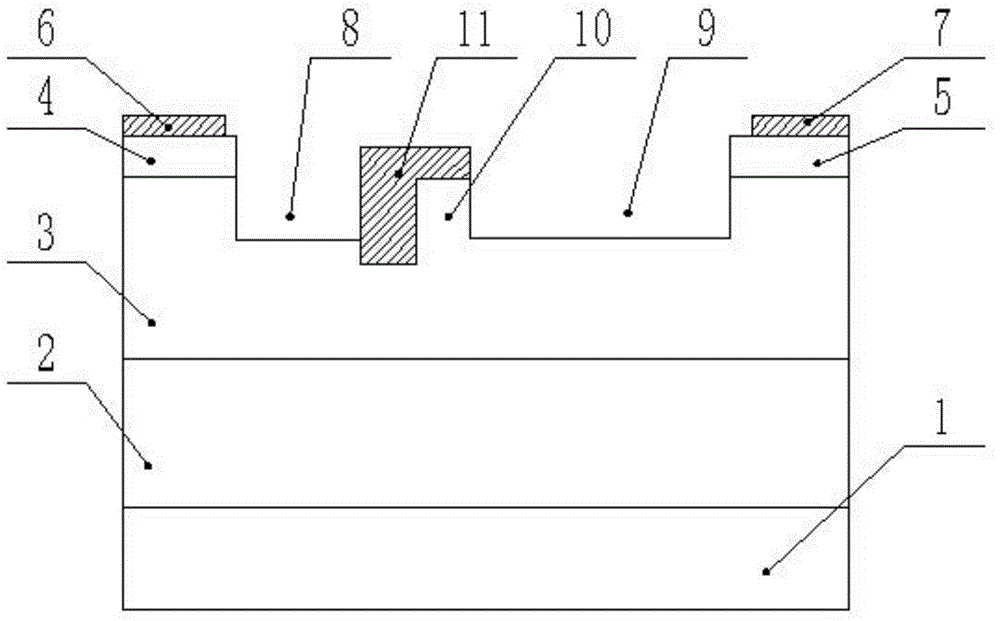

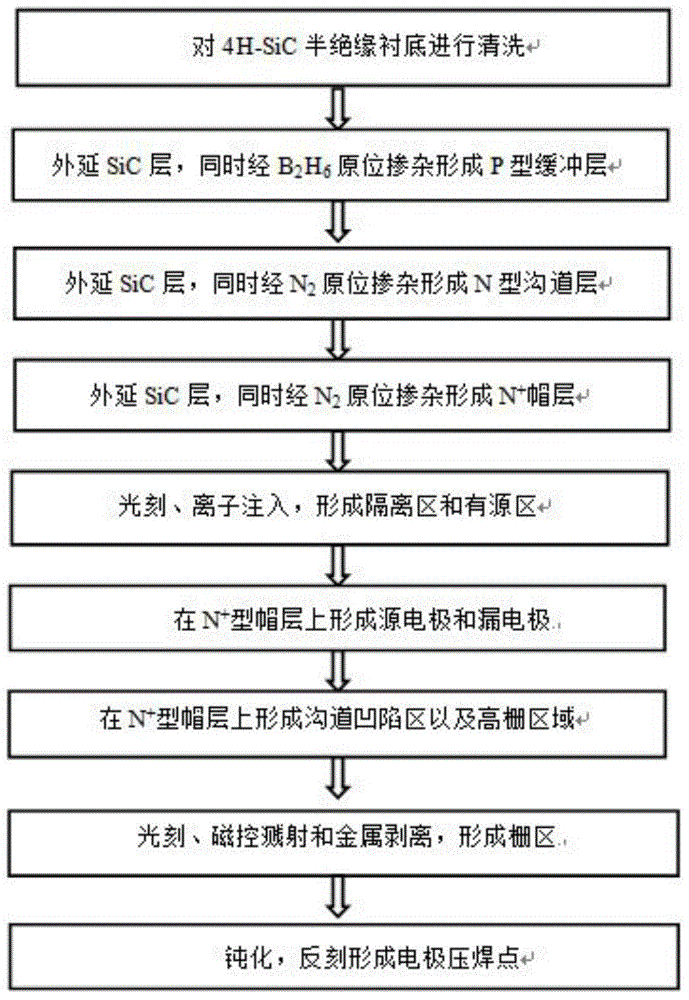

[0054] The method for fabricating a wide-channel deep-recess metal-semiconductor field-effect transistor with a thickness of 0.45 μm and a high gate region with a length of 0.35 μm and a height of 0.2 μm is as follows:

[0055] Step 1) cleaning the 4H-SiC semi-insulating substrate 1 to remove dirt on the surface of the substrate;

[0056] a. Carefully clean the substrate two or three times with a cotton ball dipped in methanol to remove SiC particles of various sizes on the surface;

[0057] b. Place 4H-SiC semi-insulating substrate 1 in H 2 SO 4 :HNO 3 = Ultrasound for 5 minutes in 1:1;

[0058] c. Put the 4H-SiC semi-insulating substrate 1 in 1# cleaning solution (NaOH:H 2 o 2 :H 2 O=1:2:5) and boiled for 5 minutes, then rinsed with deionized water for 5 minutes and then put into 2# cleaning solution (HCl:H 2 o 2 :H 2 O=1:2:7) and boiled for 5 minutes, 2# cleaning solution is HCl:H 2 o 2 :H 2 O=1:2:7, finally rinsed with deionized water and washed with N 2 Blow ...

Embodiment 2

[0090] A wide-channel deep recess metal-semiconductor field-effect transistor with a thickness of 0.4 μm and a high gate region 10 with a length of 0.35 μm and a height of 0.15 μm is fabricated. The difference between the manufacturing steps of this embodiment and Embodiment 1 is:

[0091] Step 3) epitaxially grow a 0.45 μm thick SiC layer on the P-type buffer layer 2, and at the same time 2 In-situ doping, forming a concentration of 3×10 17 cm -3 N-type channel layer 3;

[0092] The specific operation process is: put the 4H-SiC epitaxial wafer into the growth chamber, feed silane at a flow rate of 20ml / min, propane at 10ml / min and high-purity hydrogen at 80l / min into the growth chamber, and simultaneously feed 2ml / min N 2 , the growth temperature is 1550℃, the pressure is 10 5 Pa, last for 5min, complete doping concentration and thickness are 3×10 17 cm -3 and an N-type channel layer 3 of 0.4 μm.

[0093] Step 7) To the N between the source electrode 6 and the drain e...

Embodiment 3

[0098] A 4H-SiC metal-semiconductor field-effect transistor with a thickness of 0.5 μm and a high gate region 10 with a length of 0.35 μm and a height of 0.25 μm is fabricated. The difference between the manufacturing steps of this embodiment and the first embodiment is:

[0099] Step 3) epitaxially grow a 0.45 μm thick SiC layer on the P-type buffer layer 2, and at the same time 2 In-situ doping, forming a concentration of 3×10 17 cm -3 N-type channel layer 3;

[0100] The specific operation process is: put the 4H-SiC epitaxial wafer into the growth chamber, feed silane at a flow rate of 20ml / min, propane at 10ml / min and high-purity hydrogen at 80l / min into the growth chamber, and simultaneously feed 2ml / min N 2 , the growth temperature is 1550℃, the pressure is 10 5 Pa, last for 5min, complete doping concentration and thickness are 3×10 17 cm -3 and an N-type channel layer 3 of 0.5 μm.

[0101] Step 7) To the N between the source electrode 6 and the drain electrode 7...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More