Transistor and formation method

A technology of transistors and insulating layers, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., to achieve the effect of improving integration and reducing substrate area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

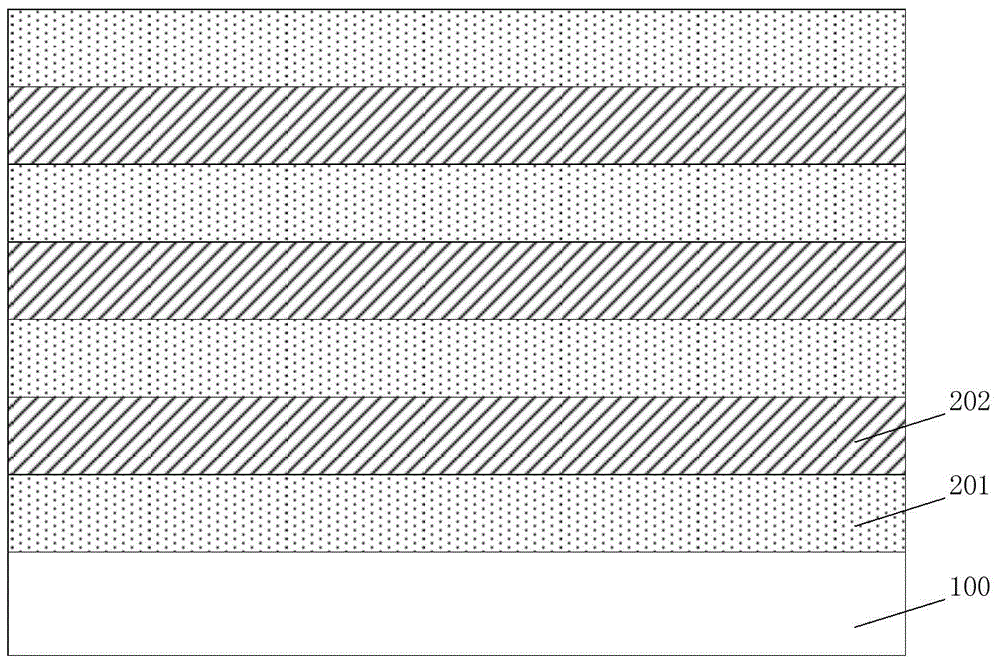

[0032] As described in the prior art, the transistors in the existing integrated circuits are arranged in a planar manner, occupying a relatively large chip area, which is not conducive to the improvement of device integration.

[0033] The study found that the columnar transistor structure is beneficial to increase the channel area of the transistor and is easy to integrate.

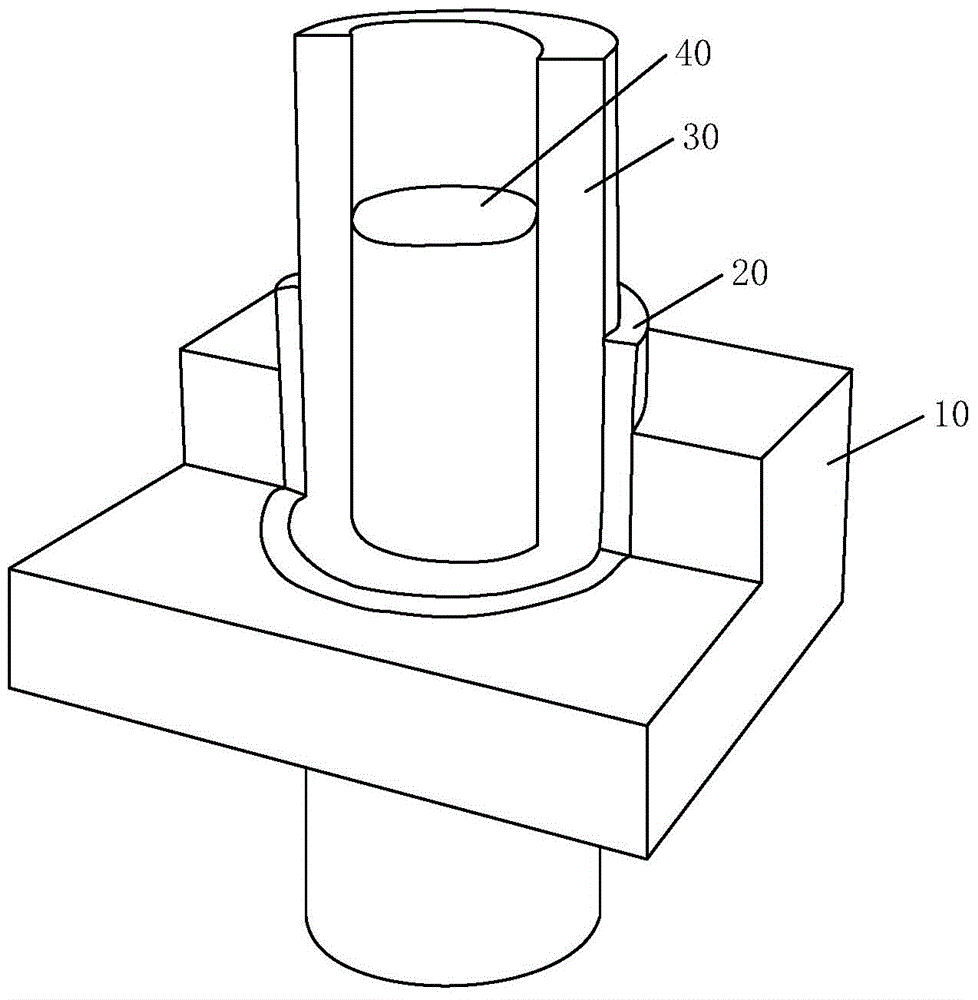

[0034] Please refer to figure 1 , which provides a schematic cross-sectional structure diagram of a columnar transistor according to an embodiment of the present invention.

[0035] The columnar transistor includes: a dielectric layer 40 at the center, a channel layer 30 surrounding and covering the surface of the dielectric layer, a gate dielectric layer 20 surrounding and covering the surface of the channel layer, and a part of the gate dielectric layer surrounding and covering 20 of the grid 10.

[0036] The channel area of the columnar transistor is larger, which can increase the saturation c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More