Formation method of semiconductor structure

A semiconductor and gate technology, applied in the field of semiconductor structure formation, can solve the problems of difficult channel and poor control ability of the gate structure to the channel, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] It can be known from the background art that the devices formed at present still have the problem of poor performance. Now combined with a method of forming a semiconductor structure, the reasons for the poor performance of the device are analyzed.

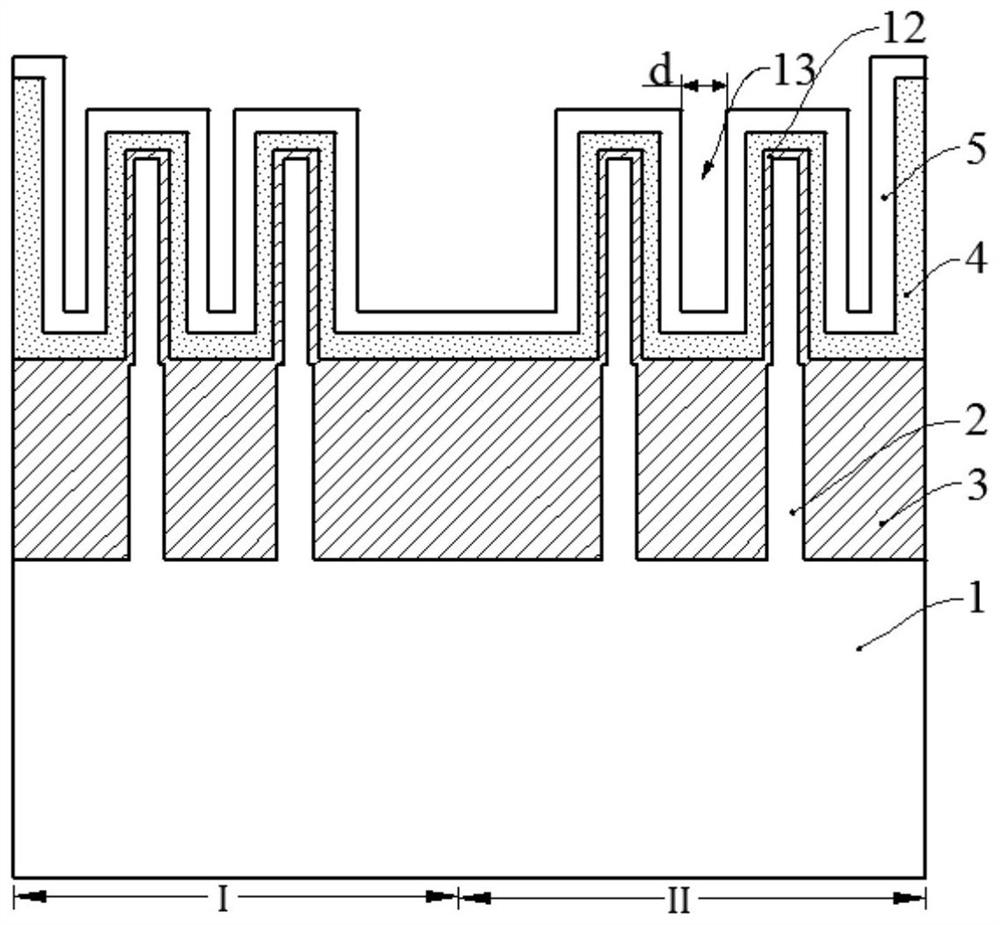

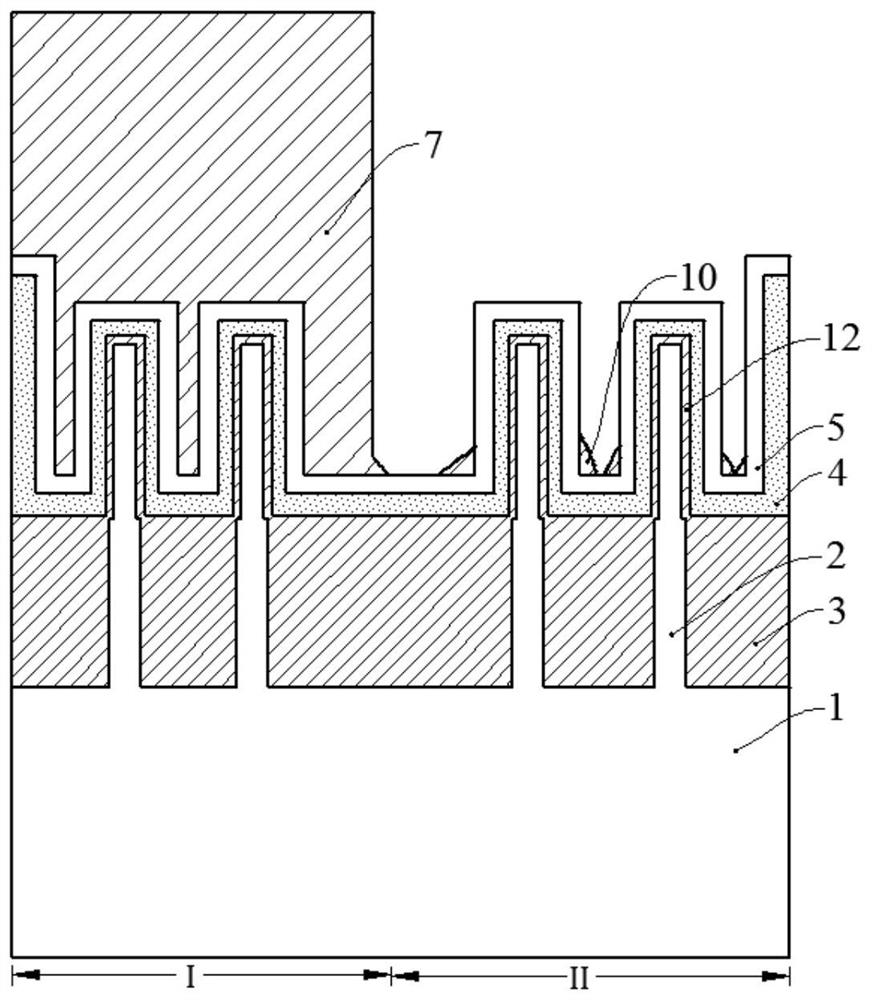

[0030] refer to Figure 1 to Figure 6 , a schematic diagram of the structure corresponding to each step in a method for forming a semiconductor structure is shown.

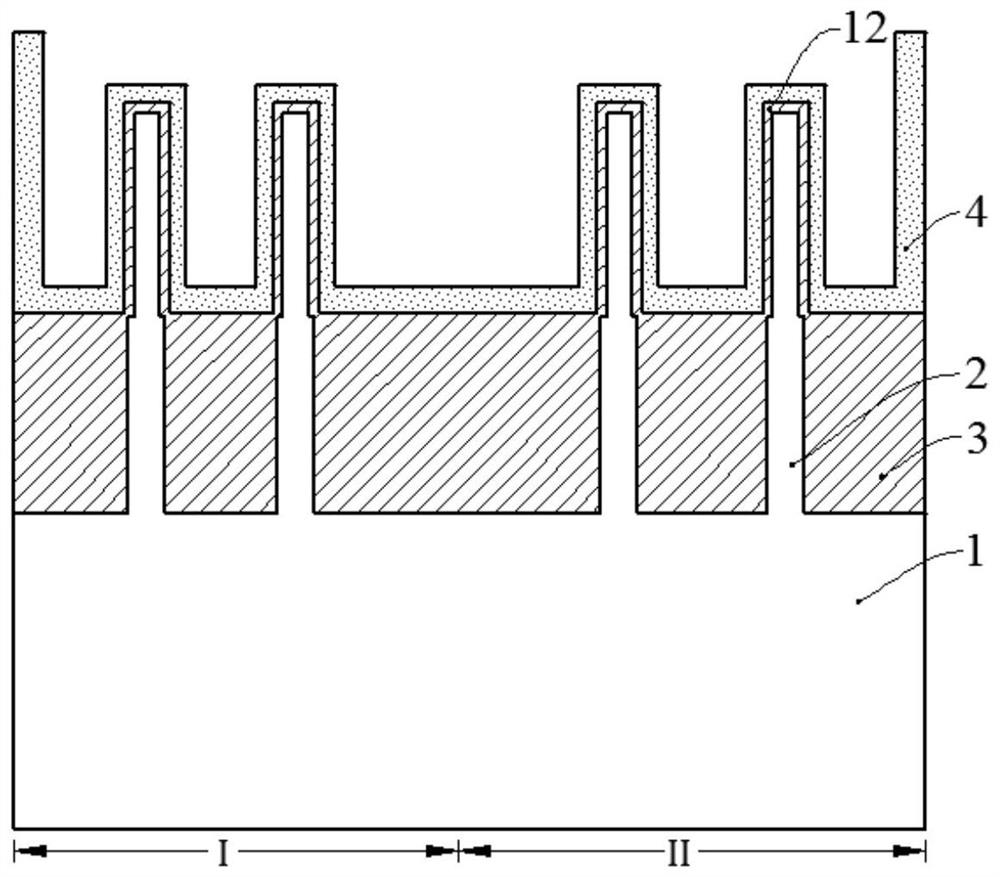

[0031] like figure 1 As shown, a substrate is provided comprising a first region I for forming a PMOS and a second region II for forming an NMOS, the substrate comprising a substrate 1, fins 2 separate from the substrate 1 and an isolation layer 3 covering part of the sidewall of the fin portion 2; an interface layer 12 is formed on the surface of the fin portion 2 exposing the isolation layer 3; after the interface layer 12 is formed, the fin of the isolation layer 3 is exposed The gate dielectric layer 4 is conformally covered on the portion 2 .

[0032] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More