Junction field-effect transistor and manufacturing method thereof

A technology for field effect transistors and manufacturing methods, applied in the field of junction field effect transistors and their manufacturing, to achieve the effects of short advance time, large source area, and small gate resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The following will clearly and completely describe the technical solutions in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, rather than all the embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

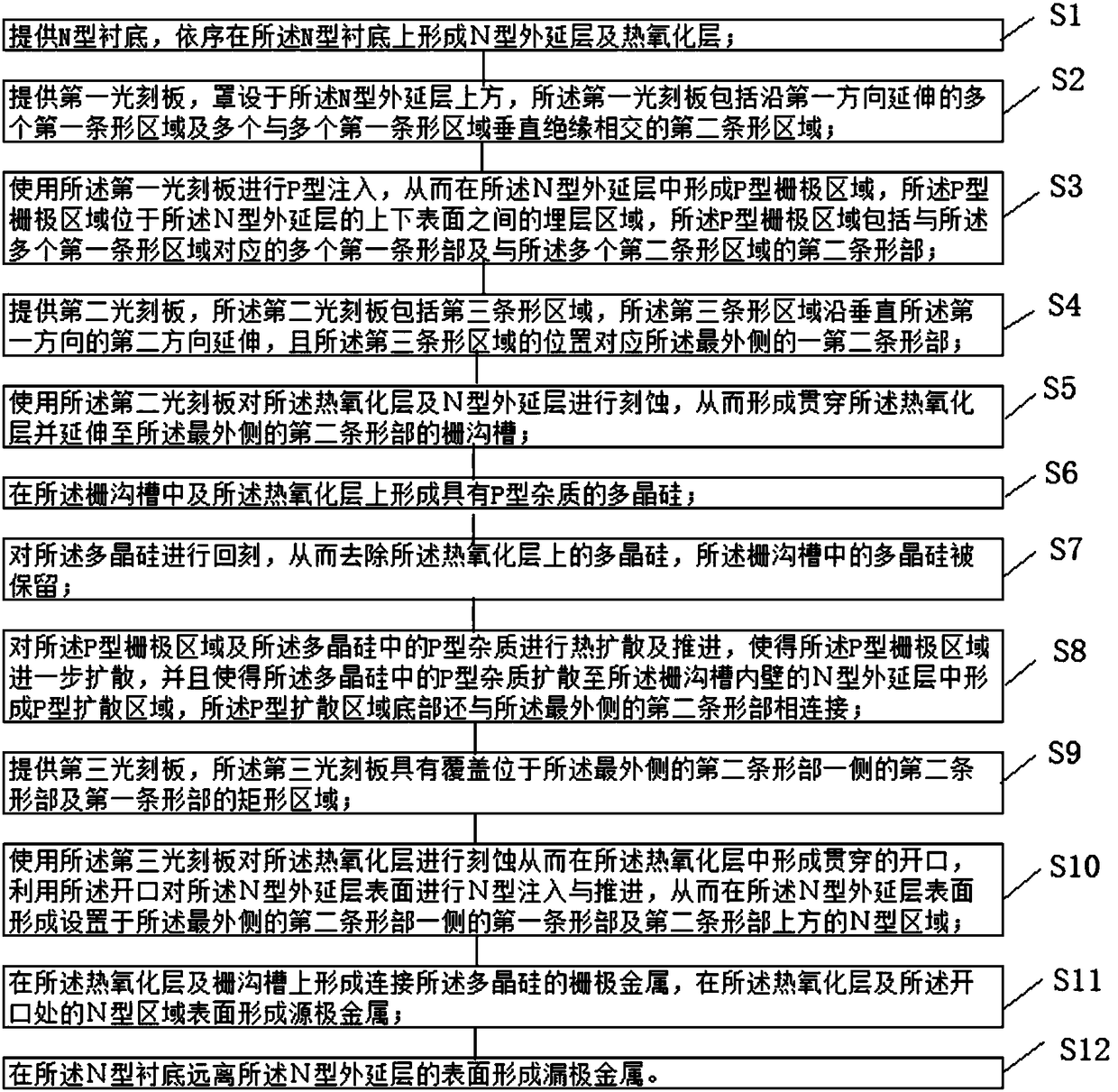

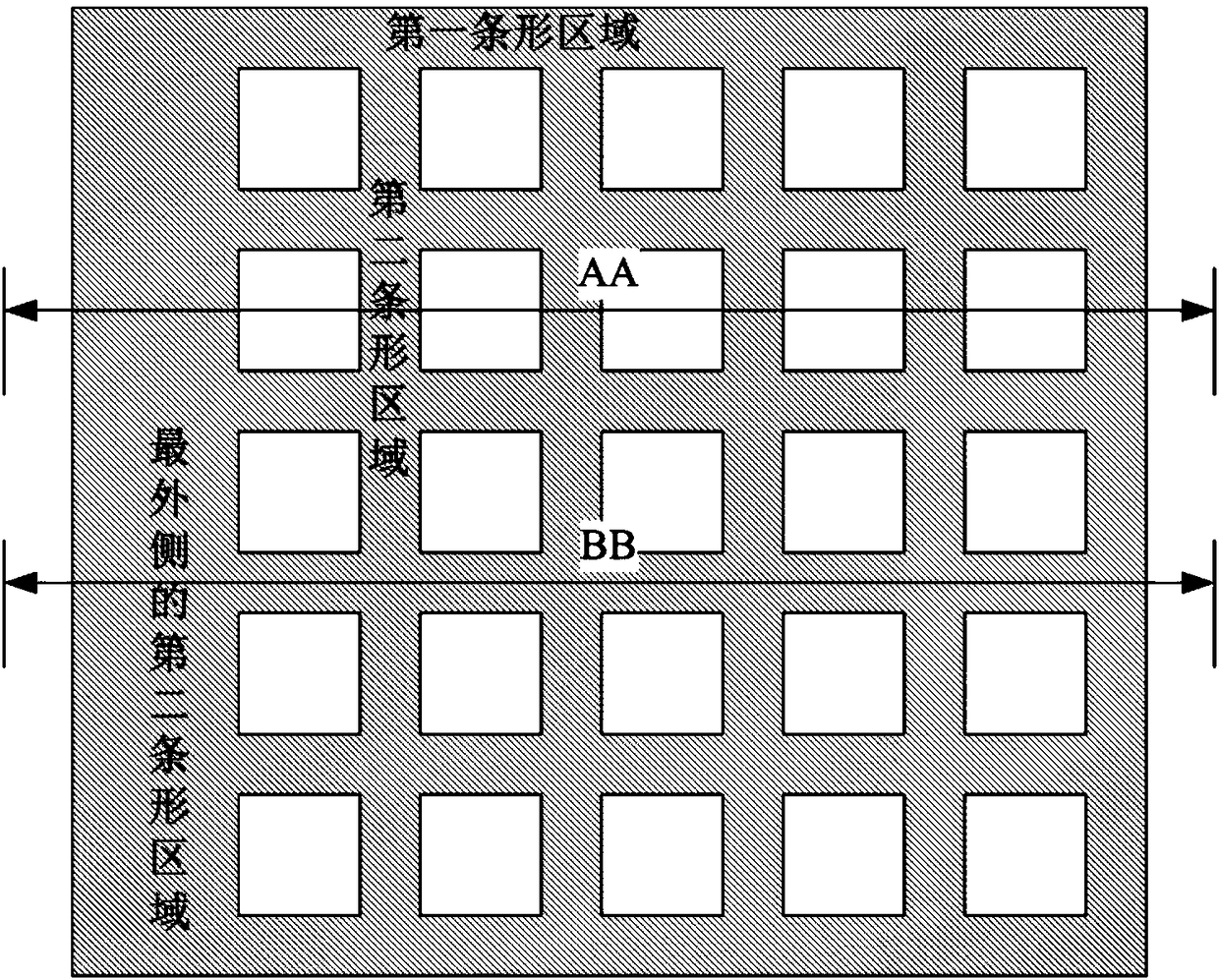

[0037] see Figure 1 to Figure 14 , figure 1 It is a flowchart of the fabrication method of the junction field effect transistor of the present invention, Figure 2 to Figure 14 for figure 1 The structure diagram of each step of the fabrication method of the junction field effect transistor is shown. The manufacturing method of the junction field effect transistor includes the following steps.

[0038] Step S1, see figure 2 , providing an N-type substrate, and sequentially forming an N-type epitaxial layer and ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Growth temperature | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More