Patents

Literature

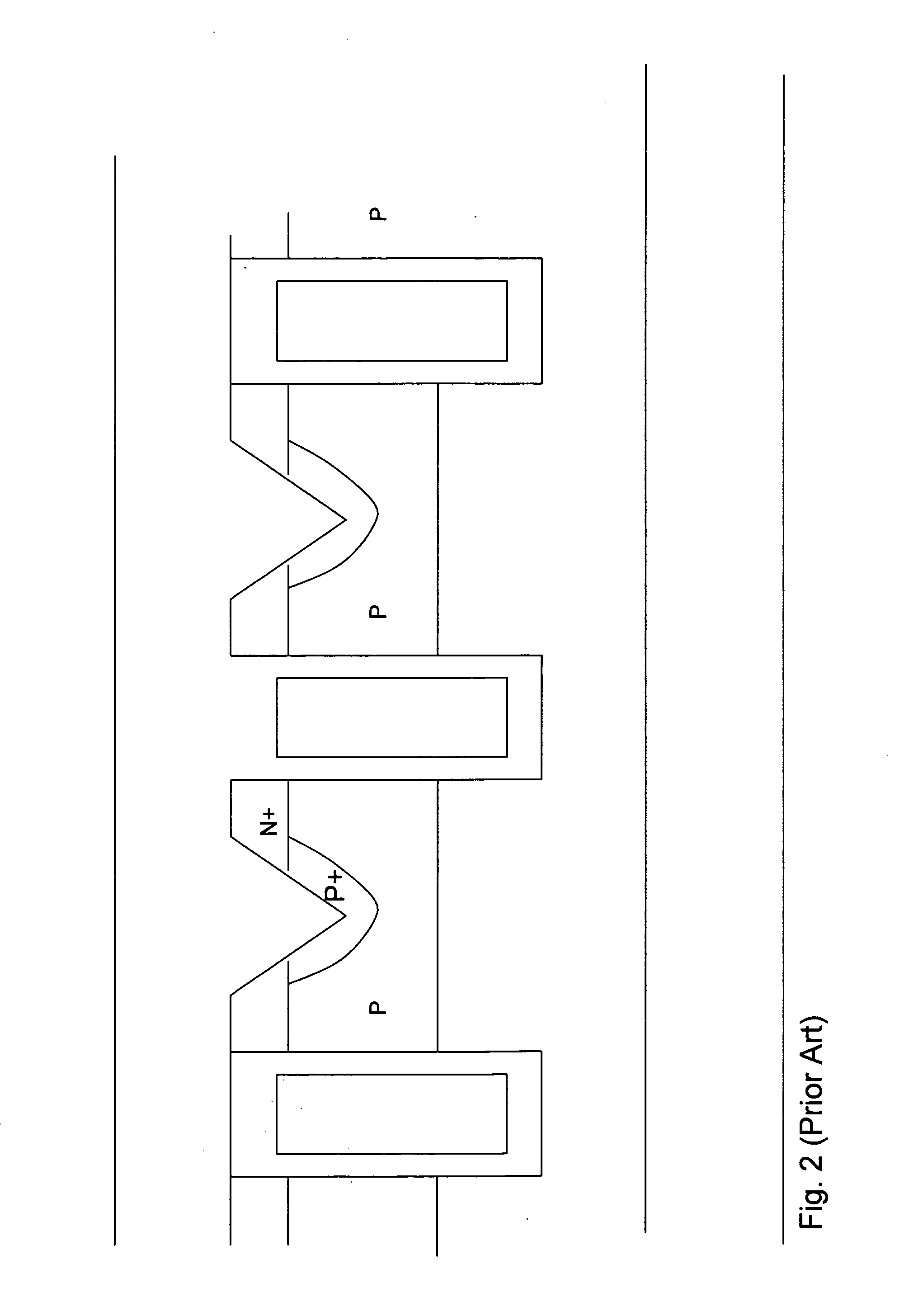

42results about How to "Improved avalanche capability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

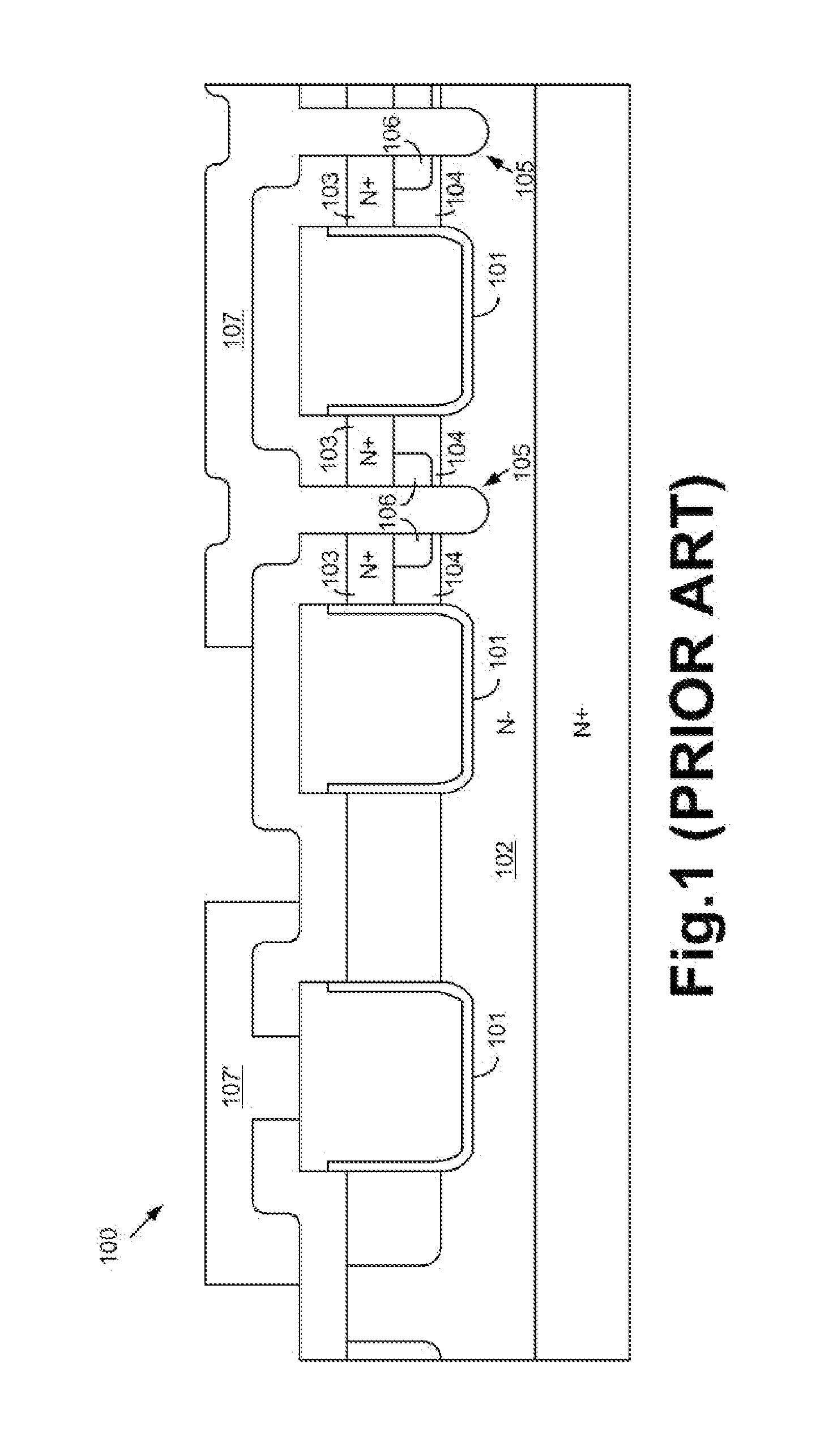

Trench MOSFET with on-resistance reduction

InactiveUS20110006362A1Reducing drain-source resistanceLowering substrate resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetInsulation layer

A trench MOSFET with on-resistance reduction comprises a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate, wherein the said MOSFET further comprises a plurality of source-body contact trenches opened relative to a top surface into said source and body regions and each of the source-body contact trenches is filled with a contact metal plug as a source-body contact; a insulation layer covered over the top of the trenched gate, the body region and the source region; a front metal layer formed on a top surface of the MOSFET; wherein a low-resistivity phosphorus substrate and retrograded P-body formed by medium or high energy Ion Implantation to reduce Rds contribution from substrate and drift region.

Owner:FORCE MOS TECH CO LTD

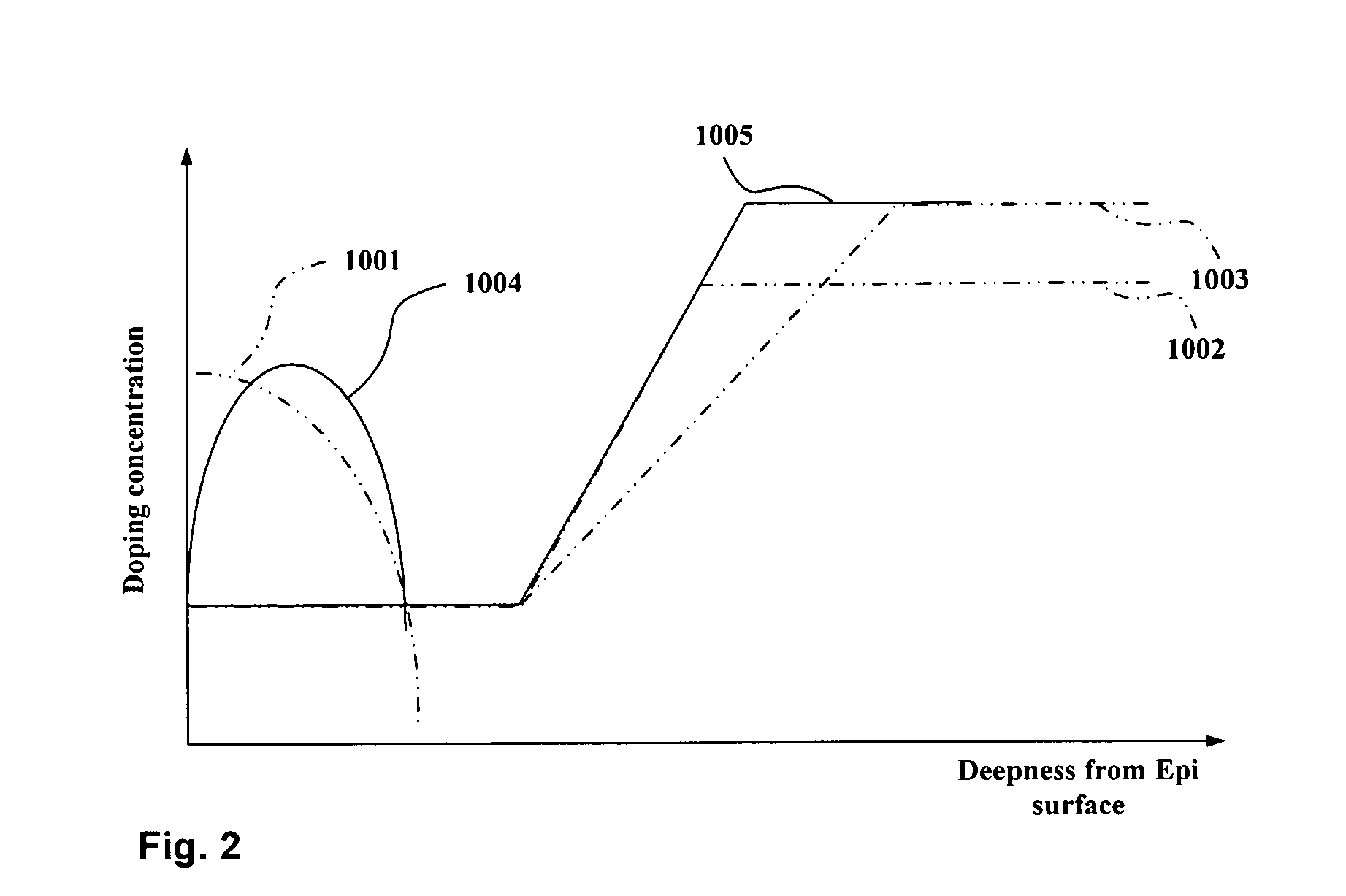

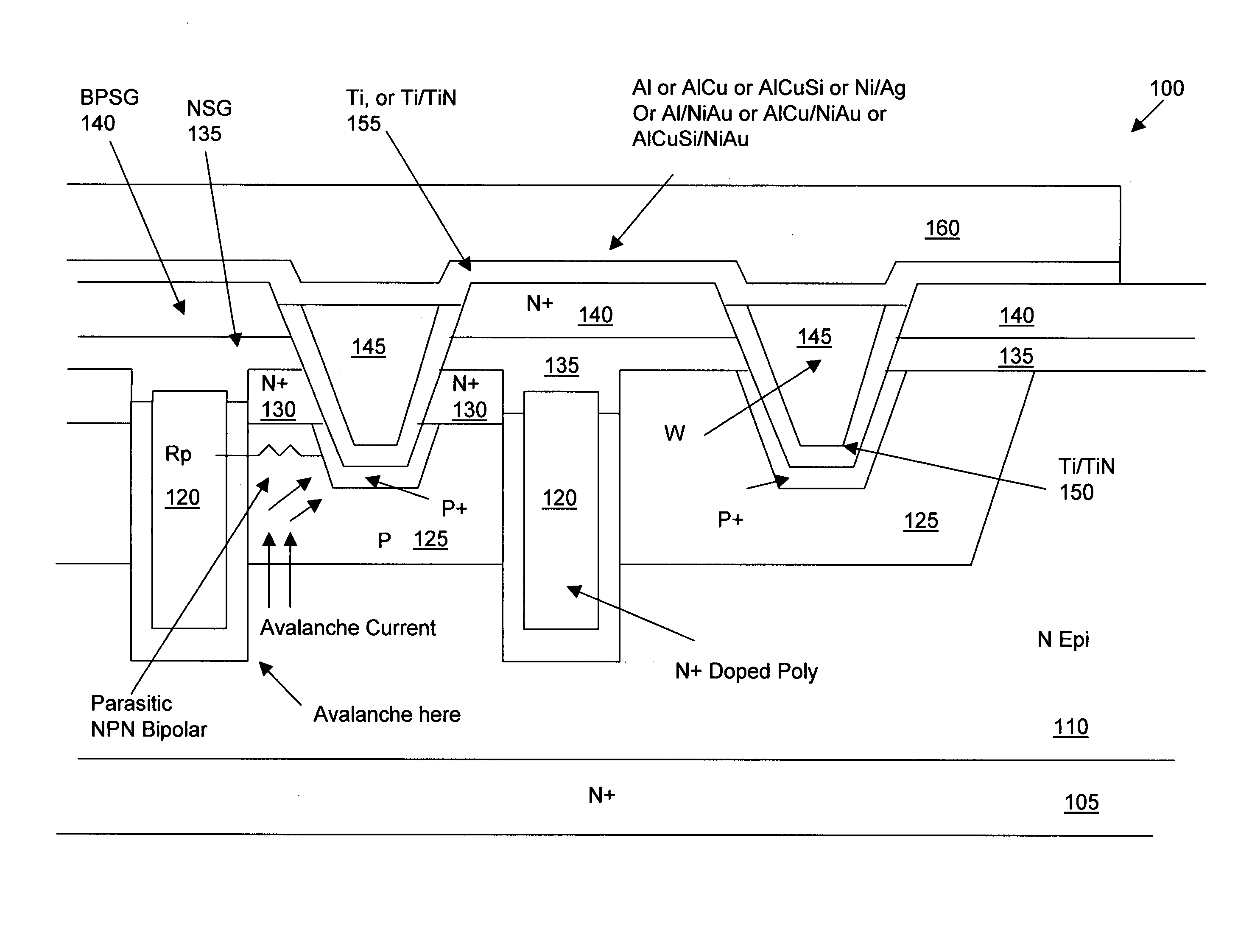

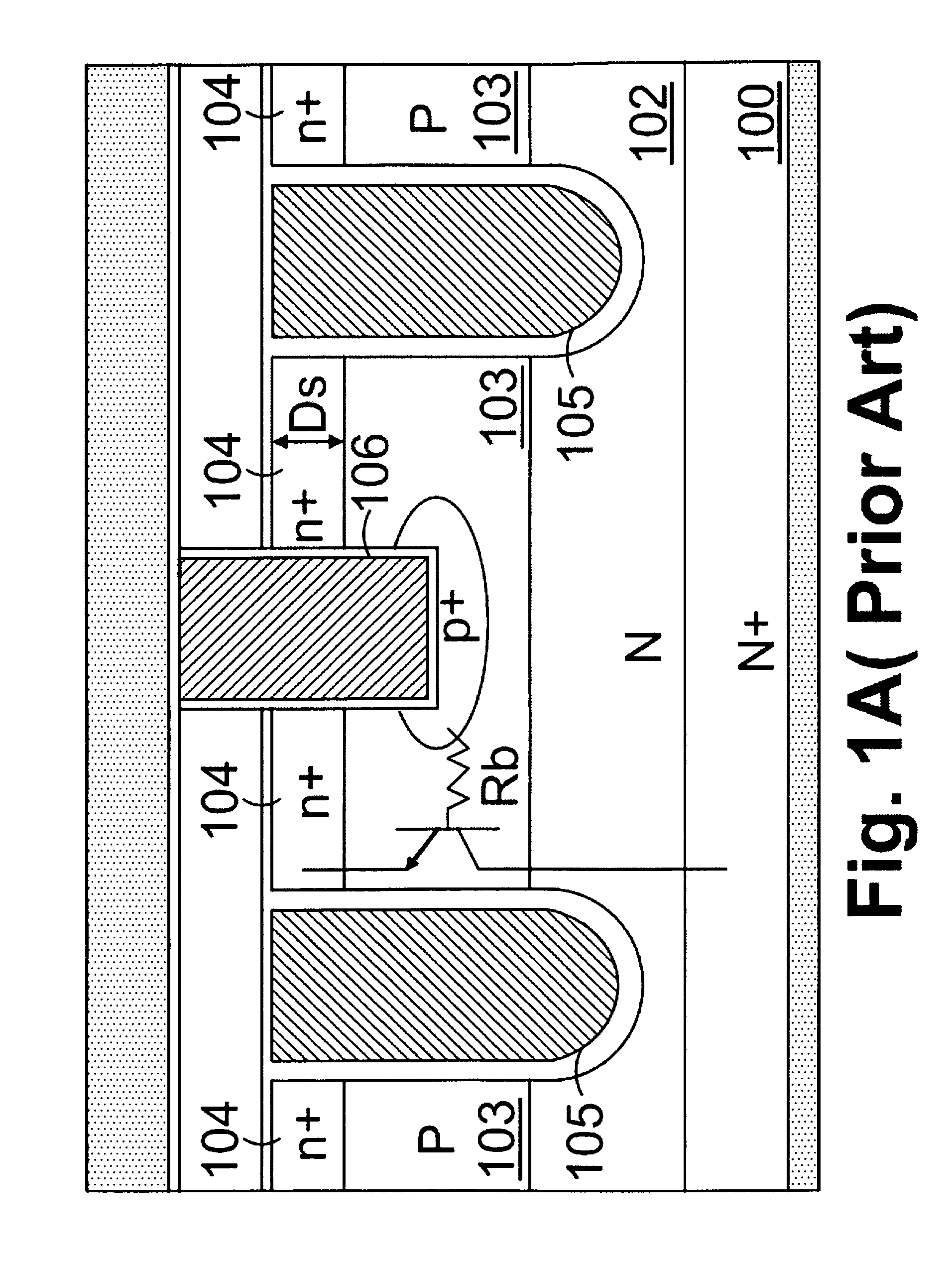

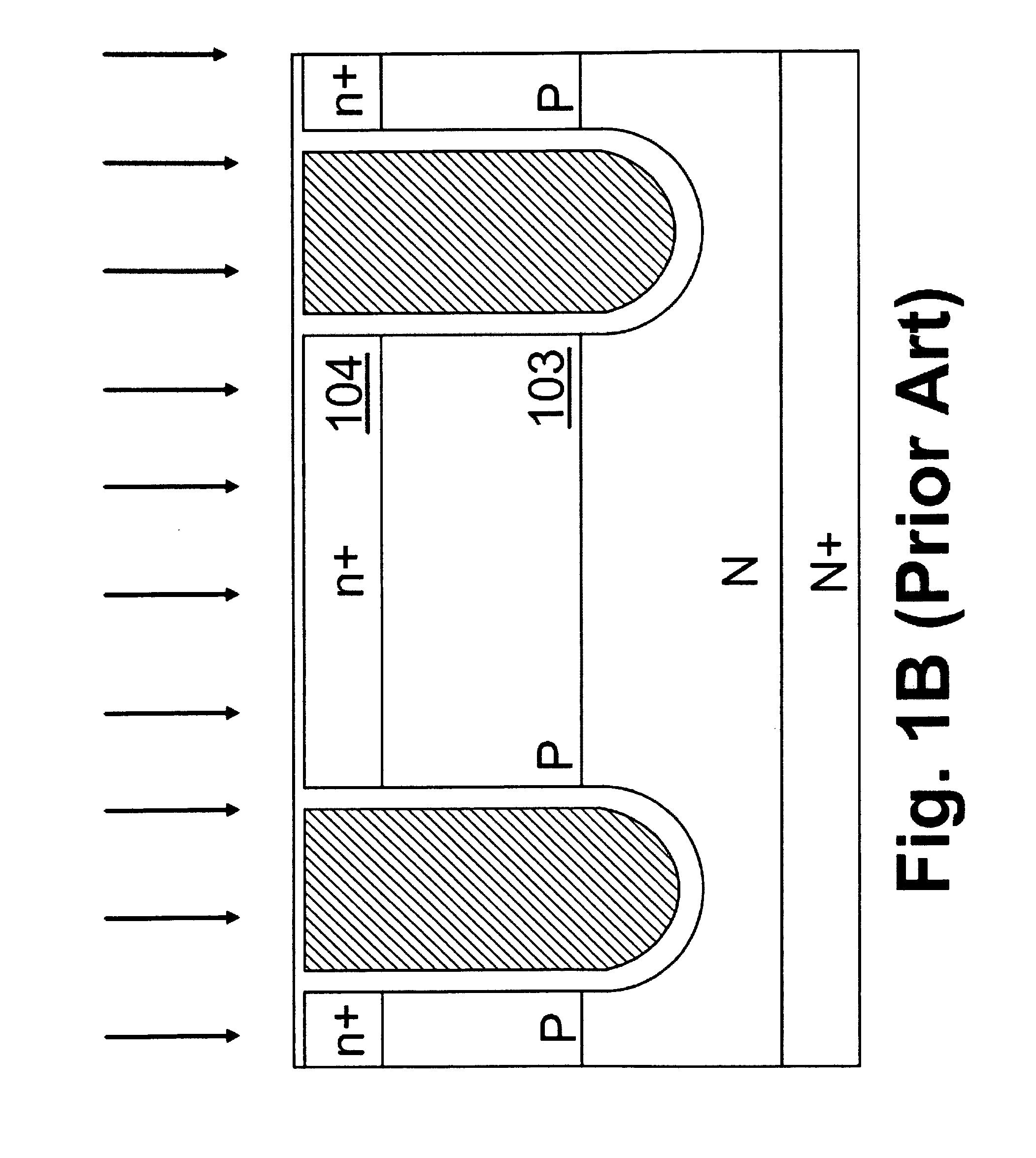

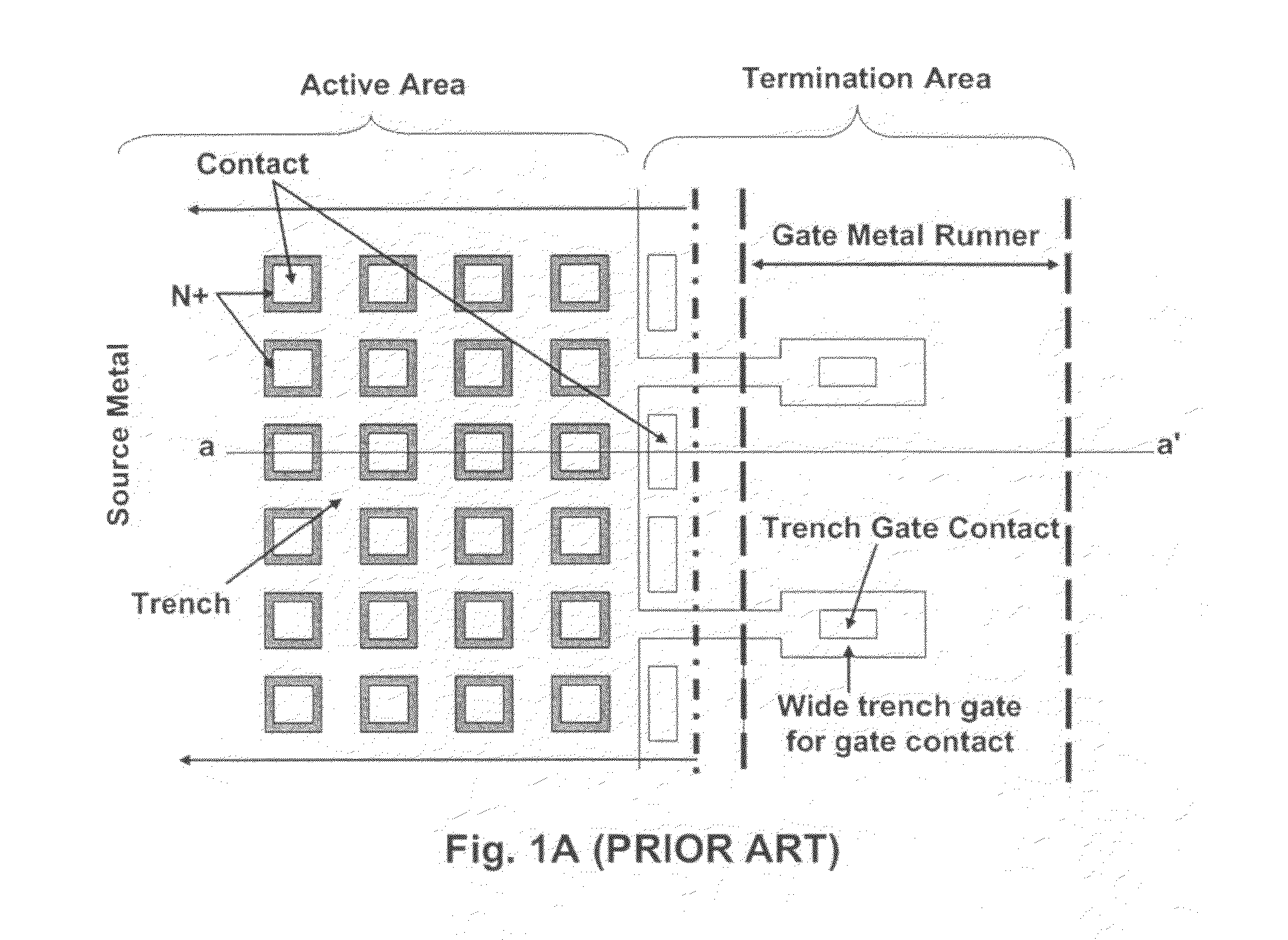

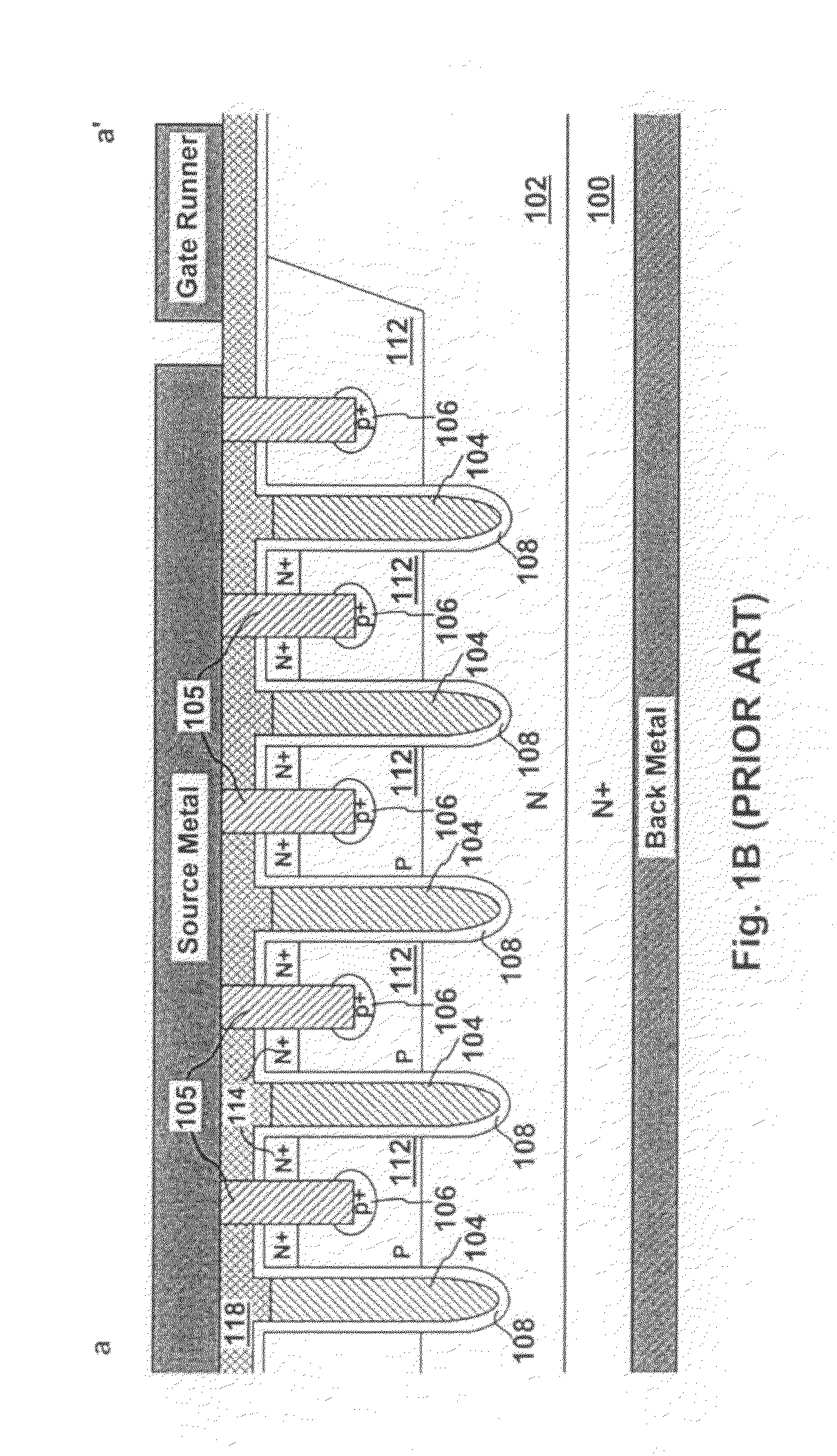

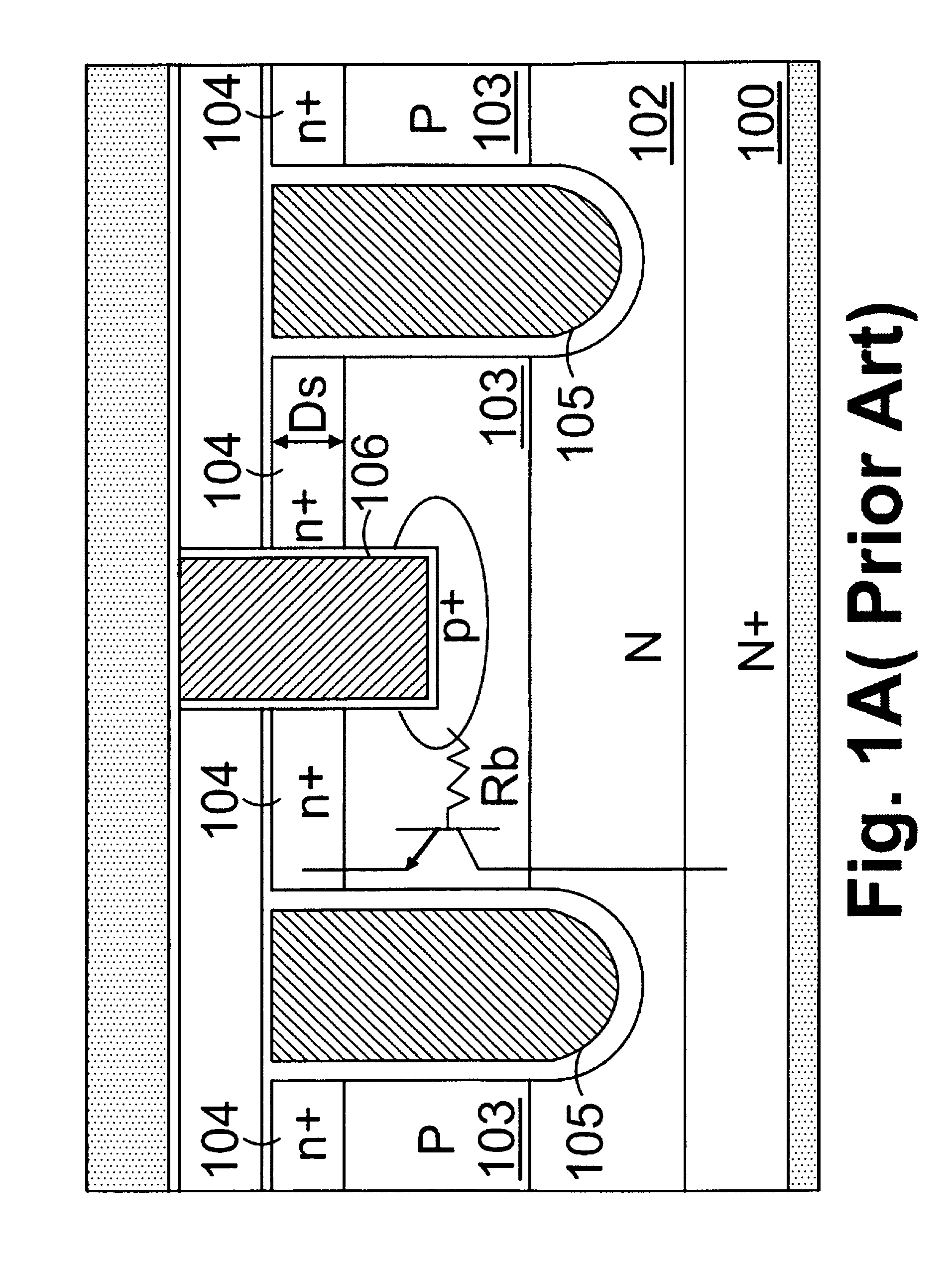

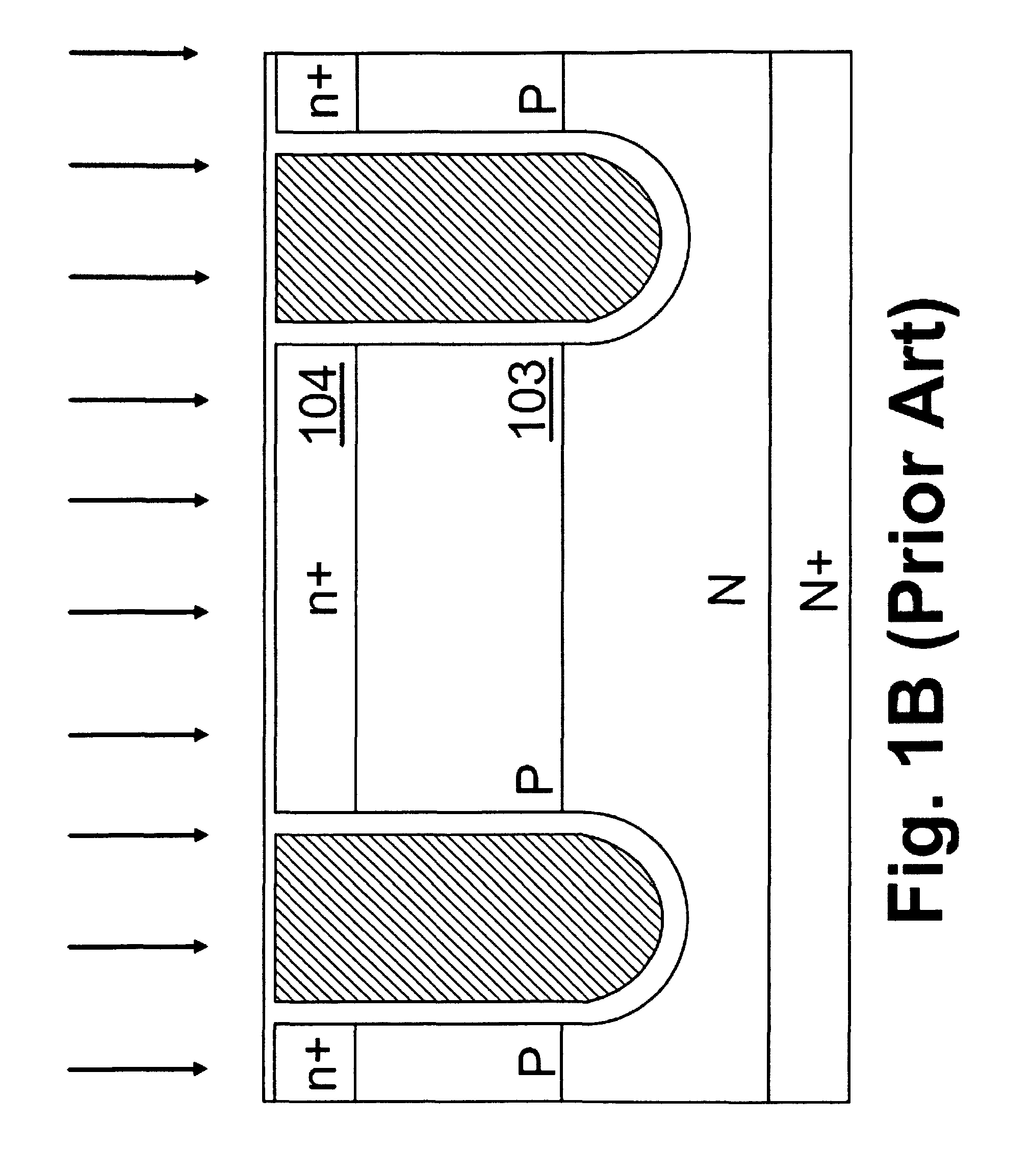

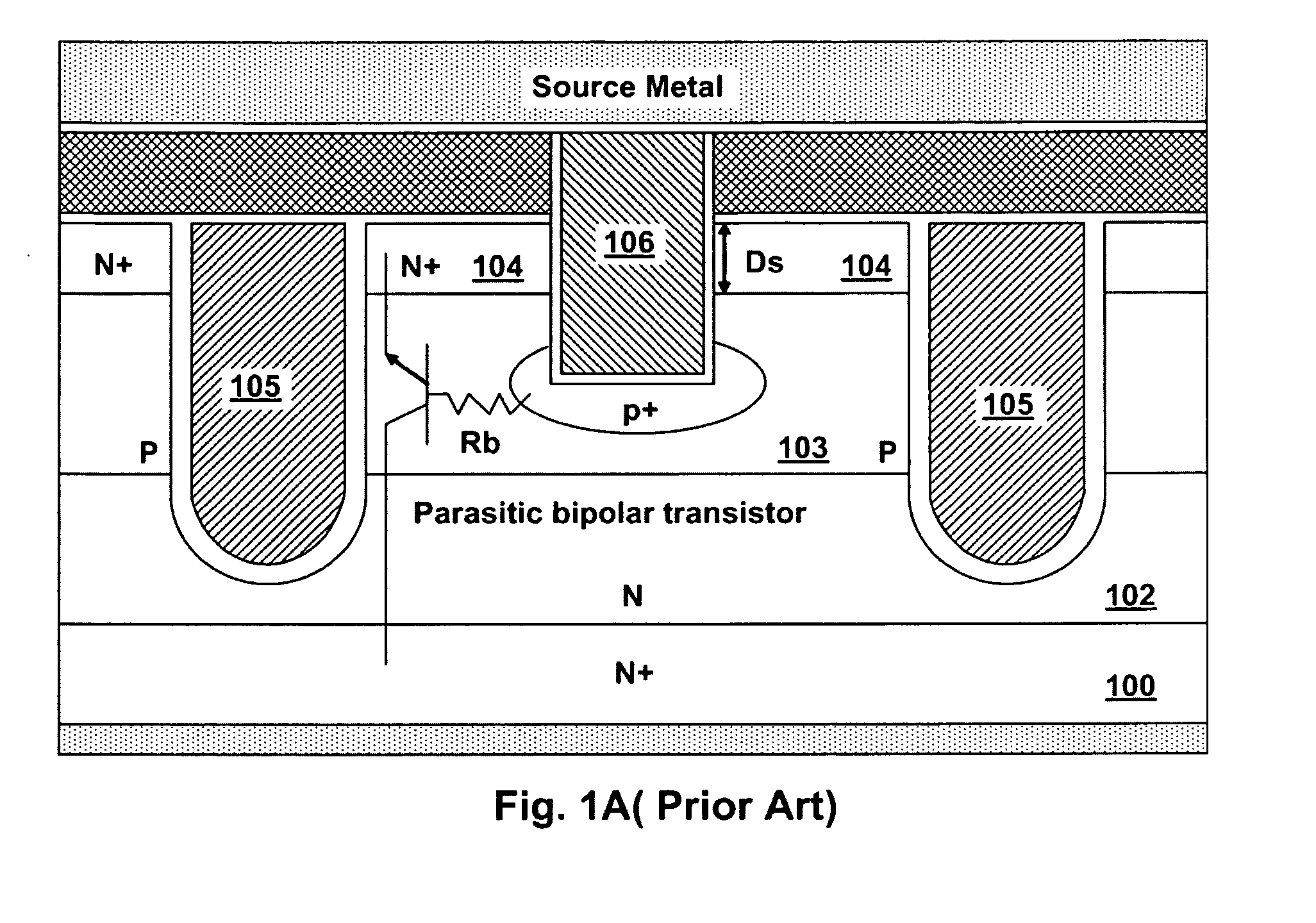

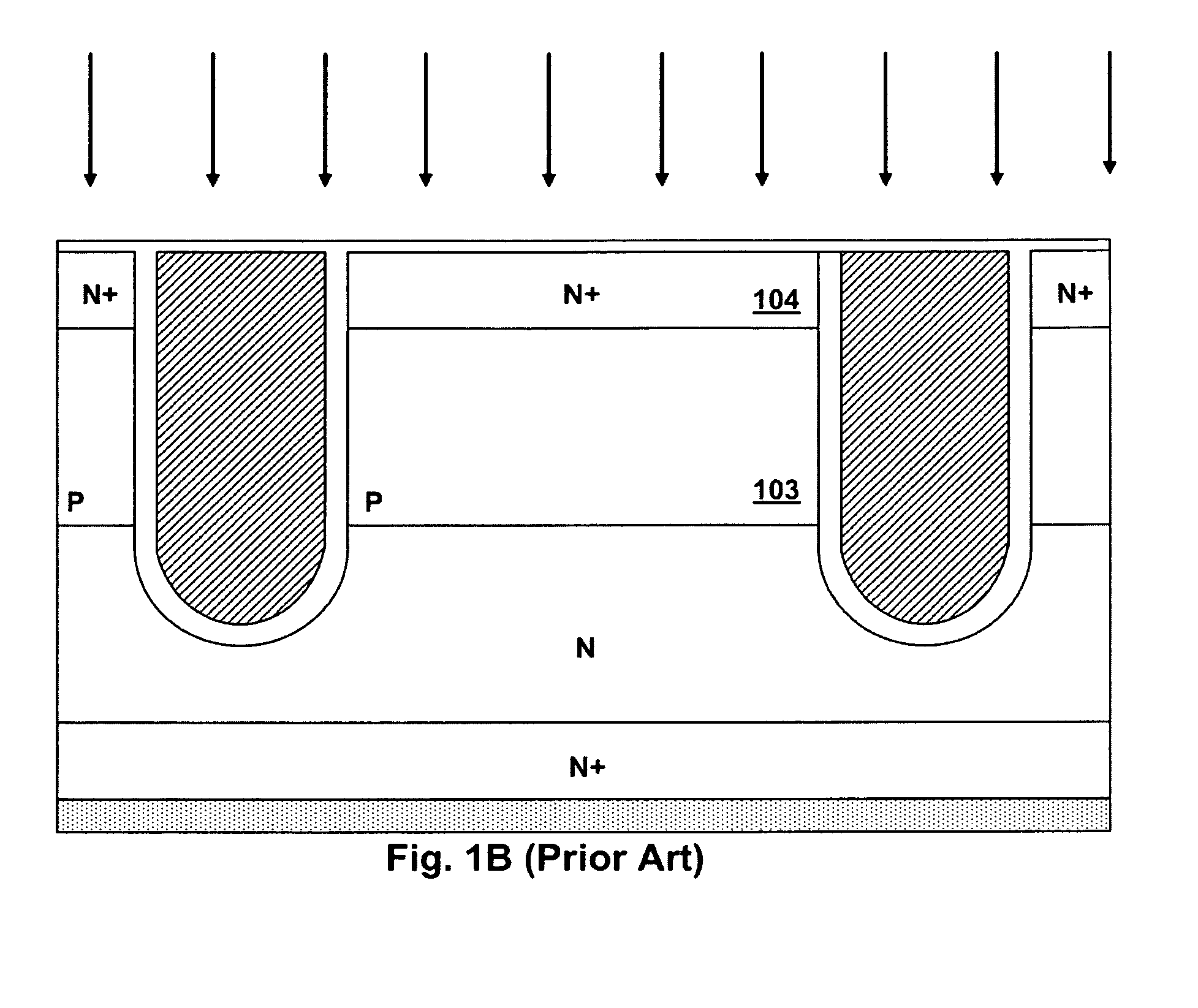

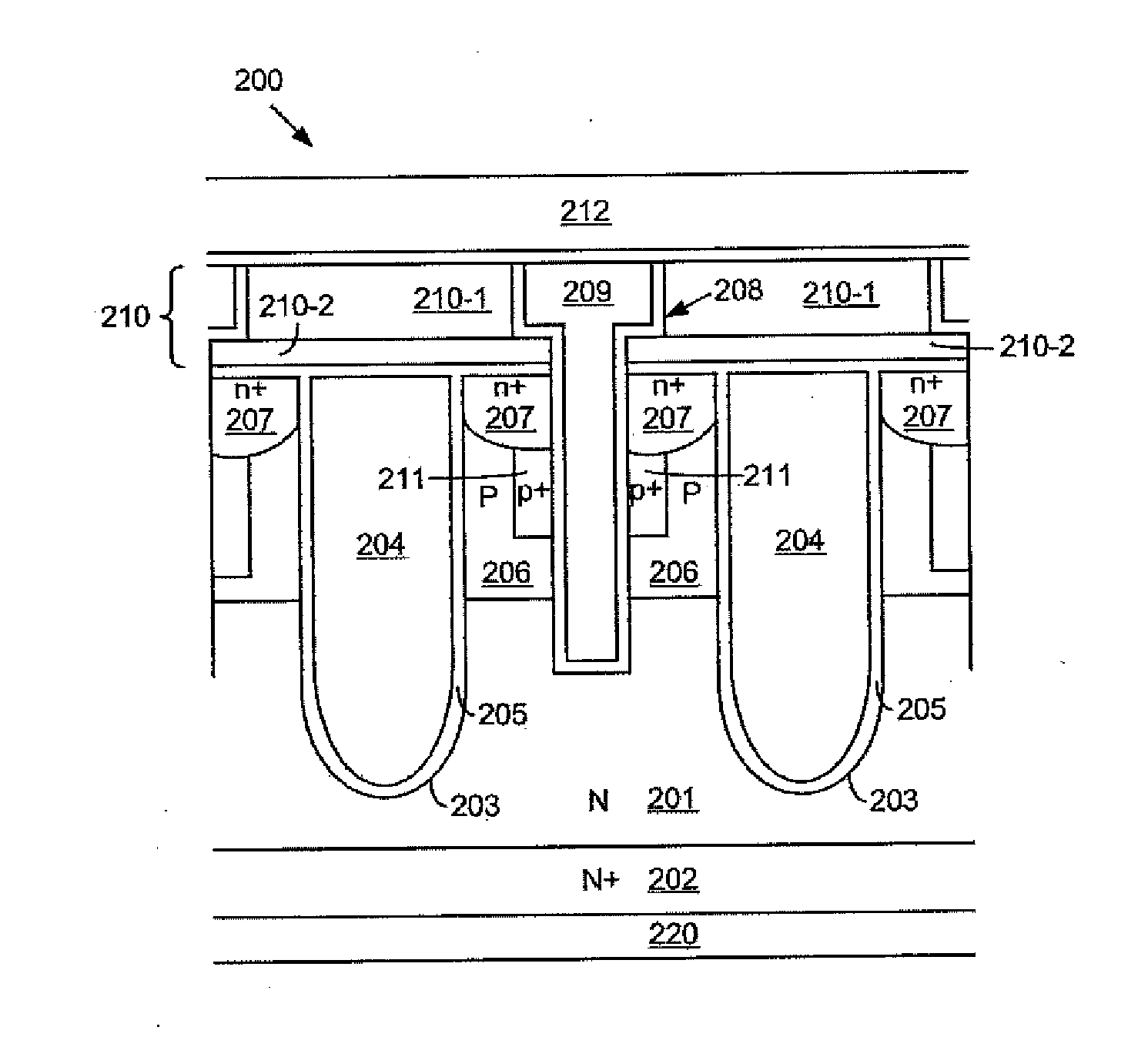

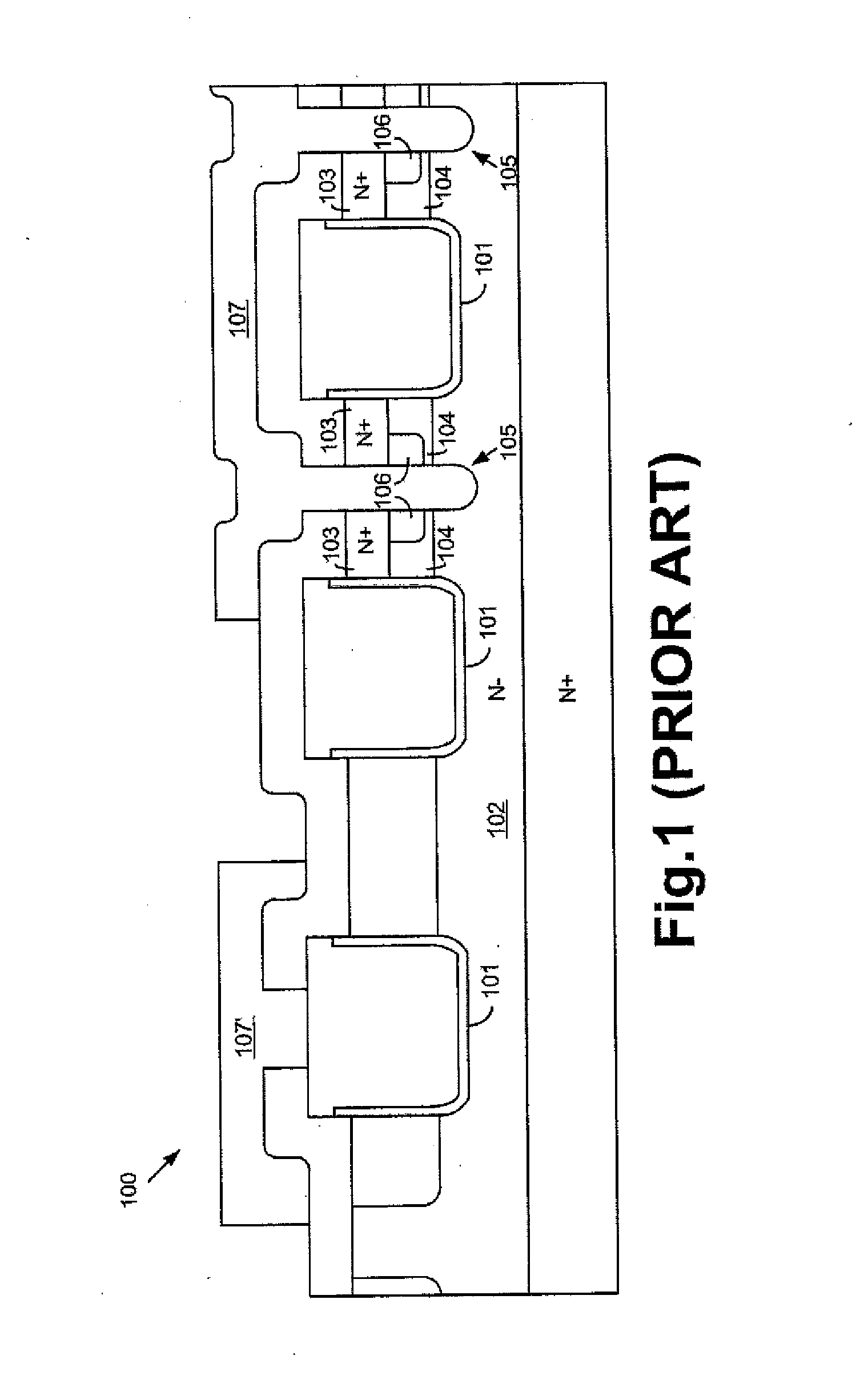

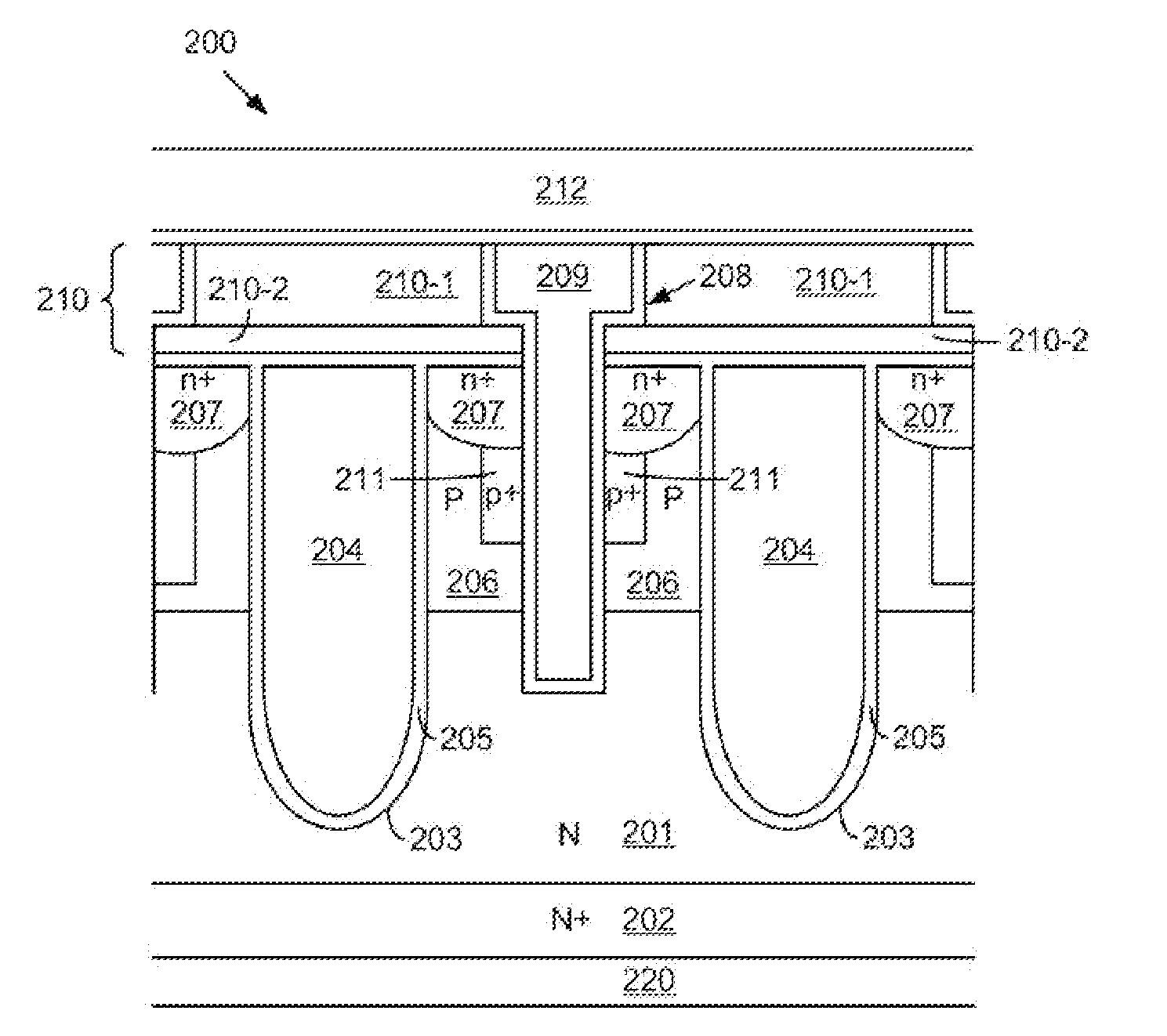

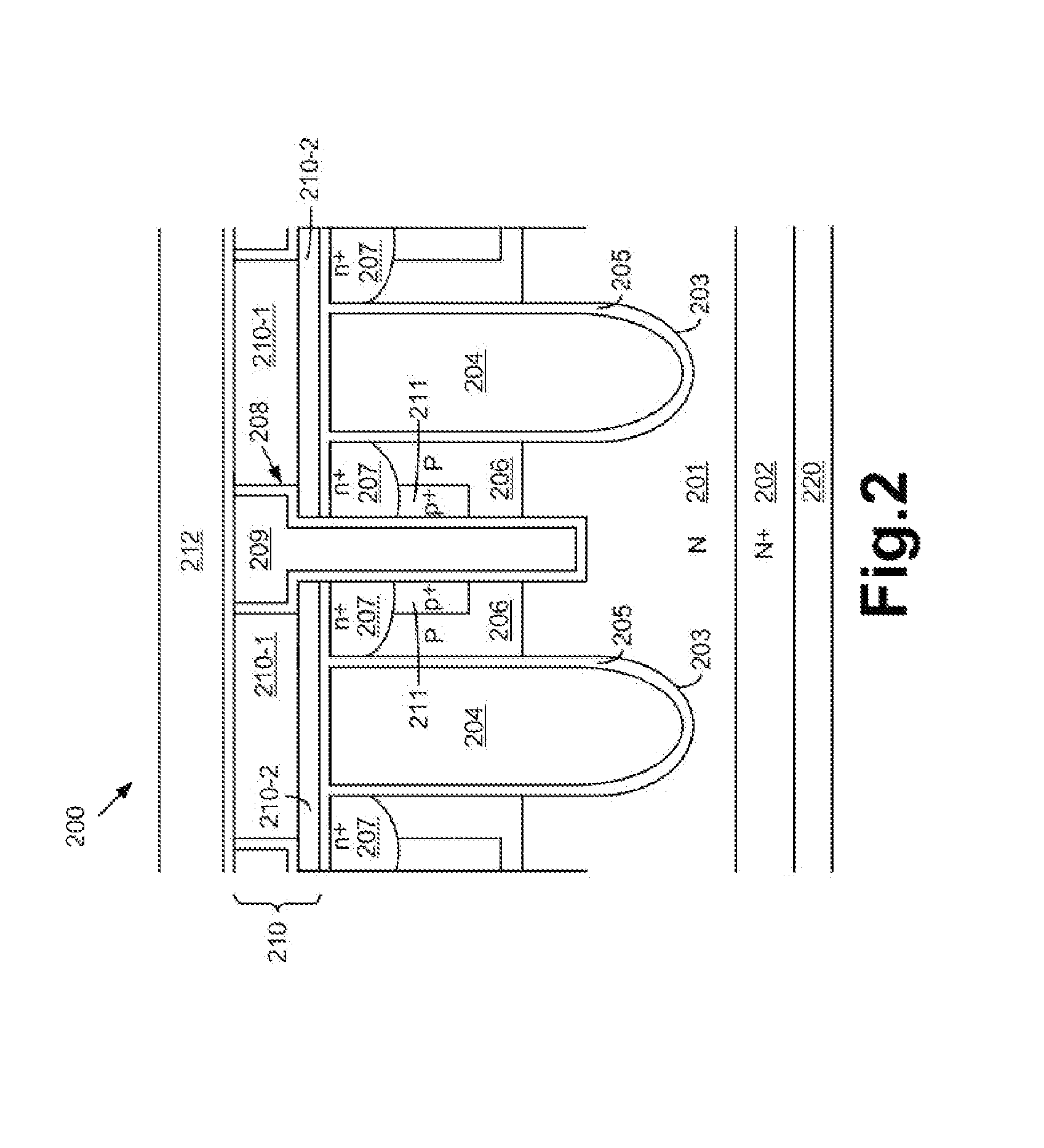

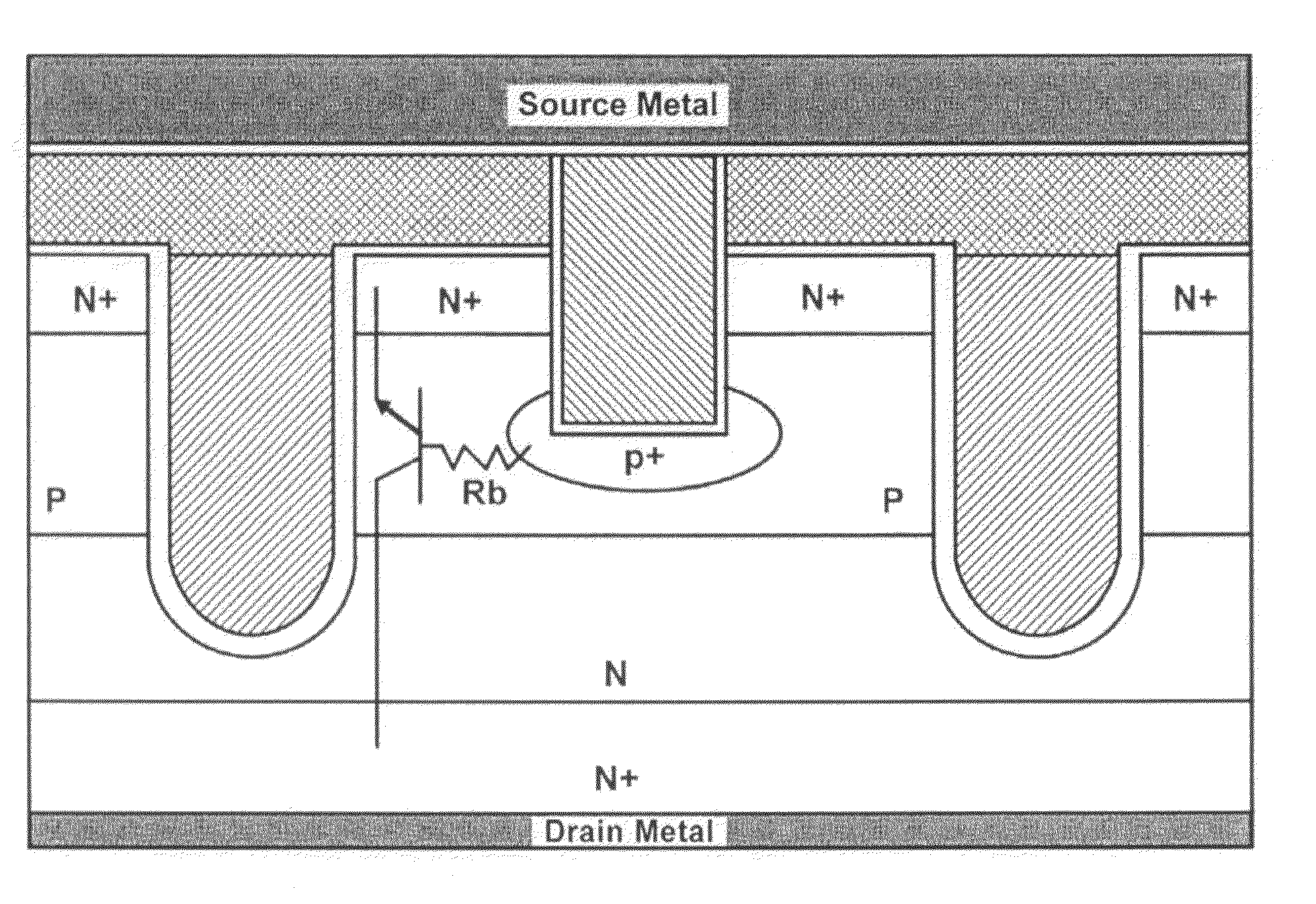

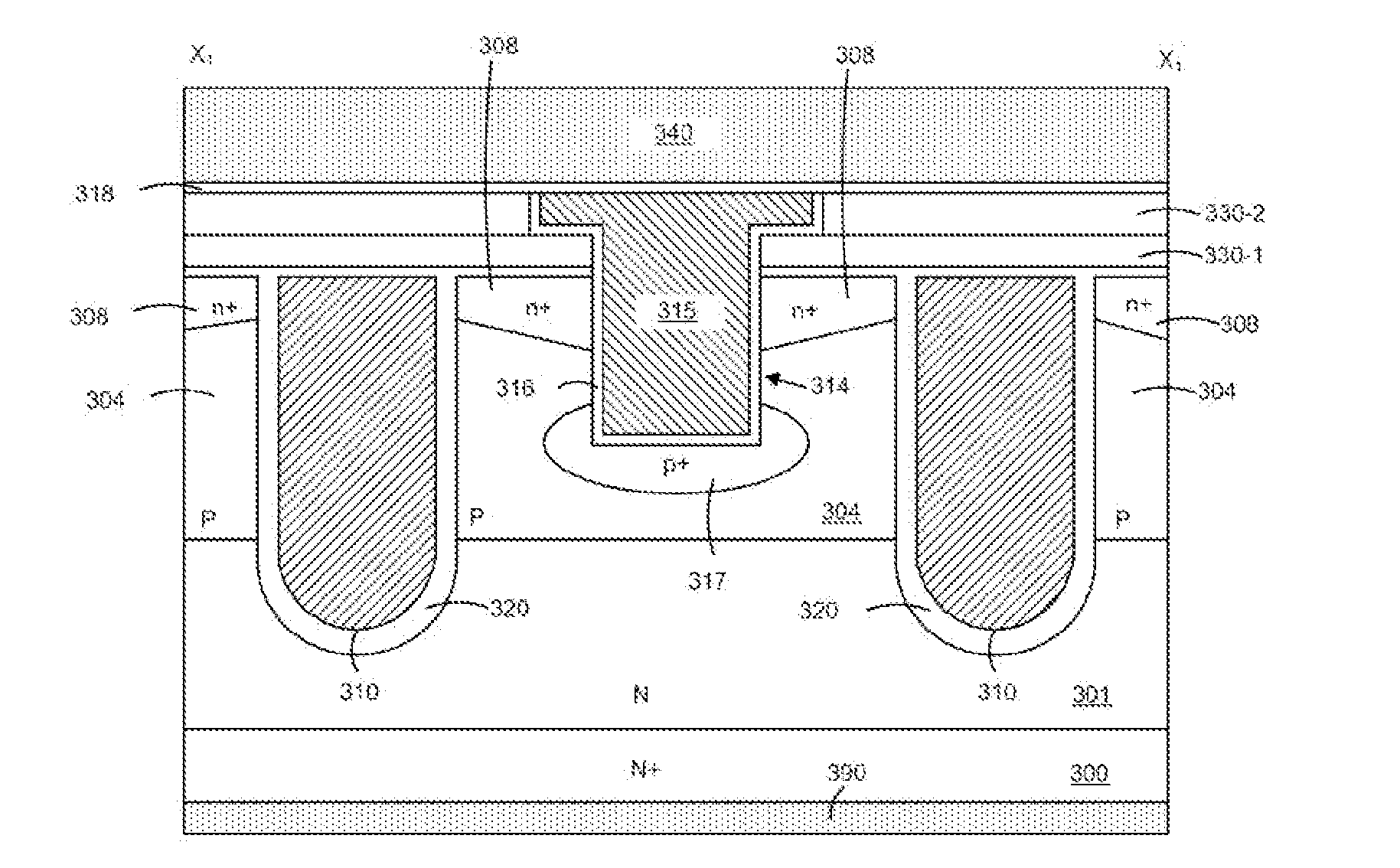

Trench MOSFET structure having improved avalanche capability using three masks process

ActiveUS7816720B1Improve contact effectReduce manufacturing costTransistorSolid-state devicesTrench mosfetBody contact

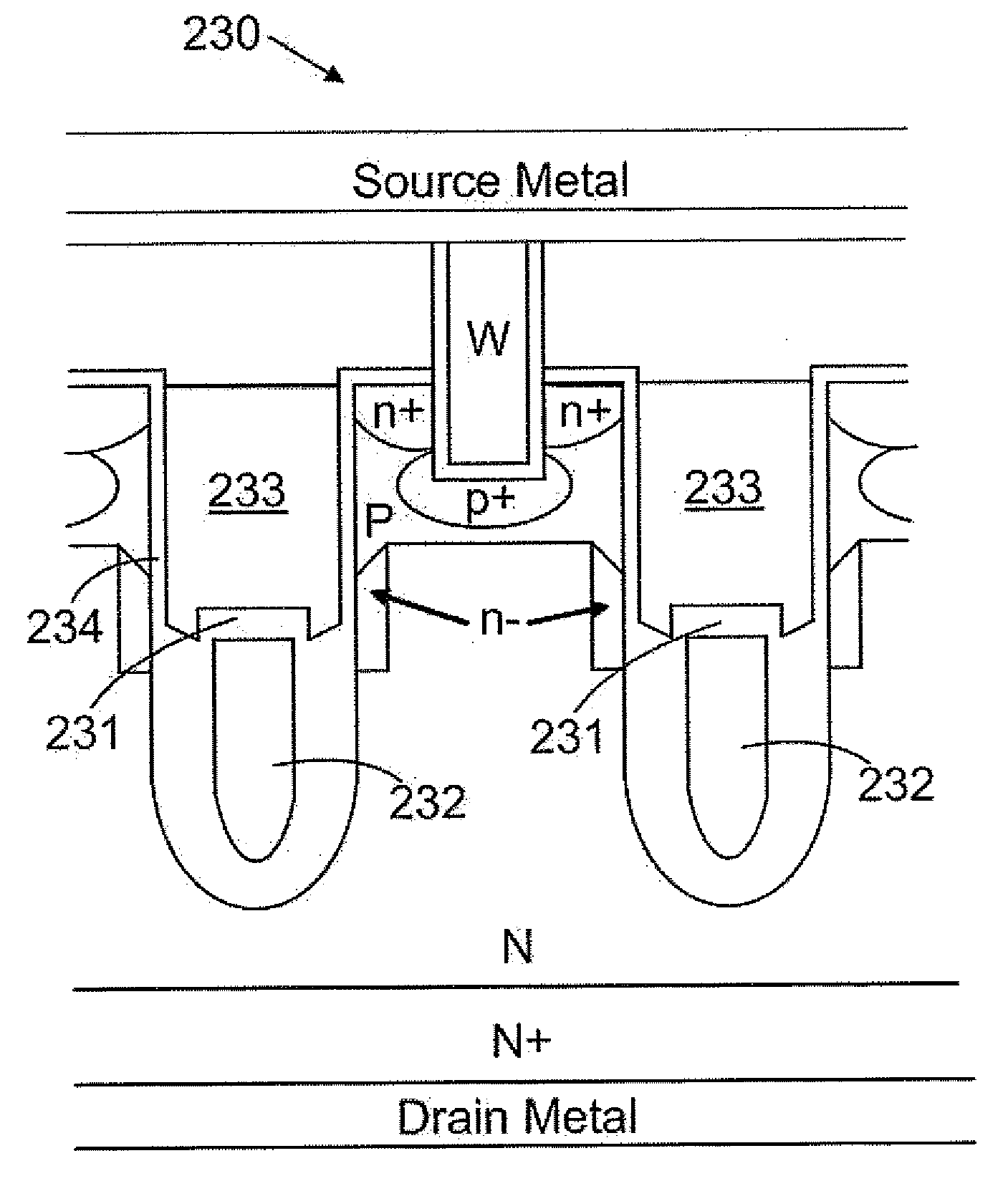

A trench MOSFET structure having improved avalanche capability is disclosed, wherein the source region is formed by performing source Ion Implantation through contact open region of a thick contact interlayer, and further diffused to optimize a trade-off between Rds and the avalanche capability. Thus, only three masks are needed in fabrication process, which are trench mask, contact mask and metal mask. Furthermore, said source region has a doping concentration along channel region lower than along contact trench region, and source junction depth along channel region shallower than along contact trench, and source doping profile along surface of epitaxial layer has Gaussian-distribution from trenched source-body contact to channel region.

Owner:FORCE MOS TECH CO LTD

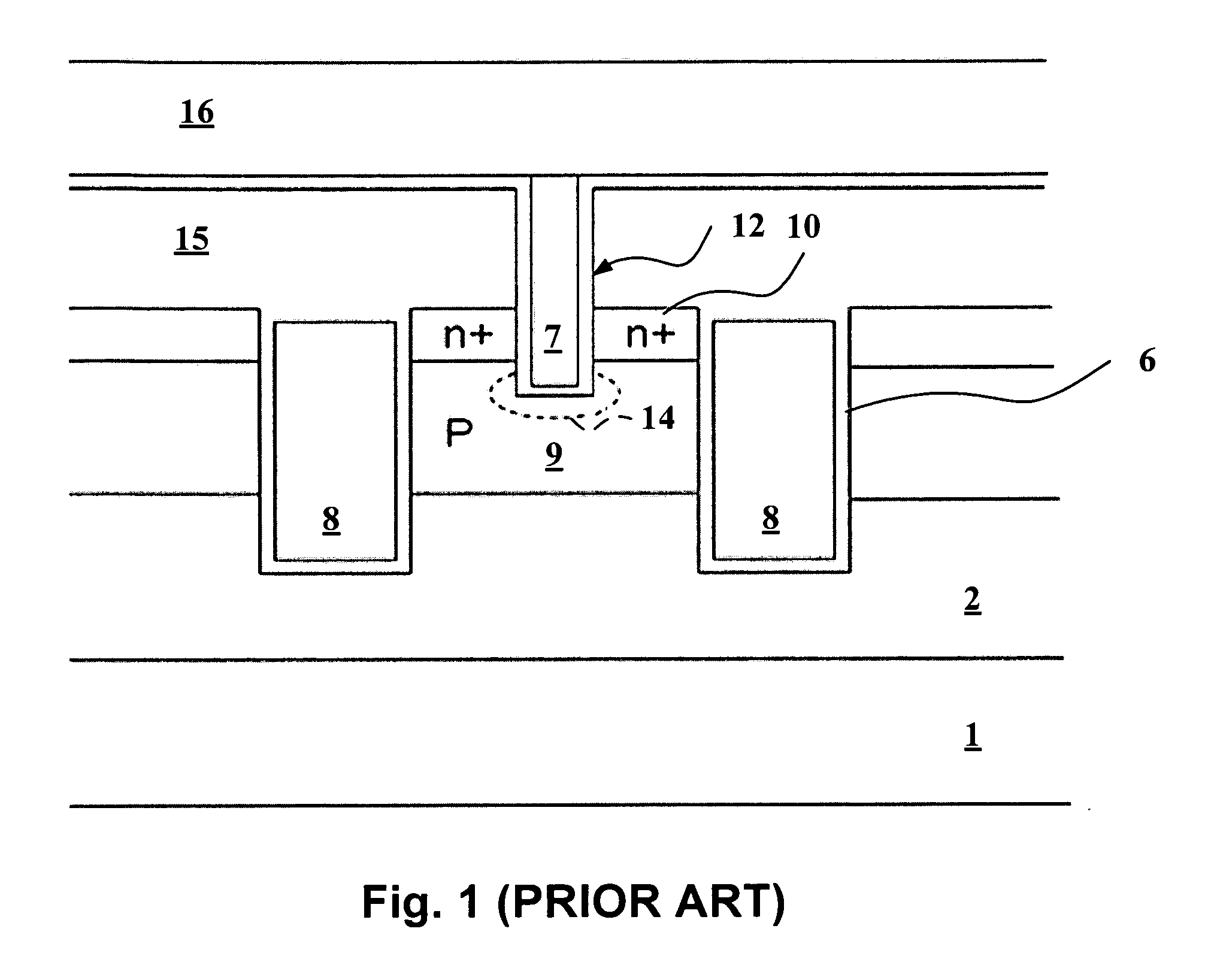

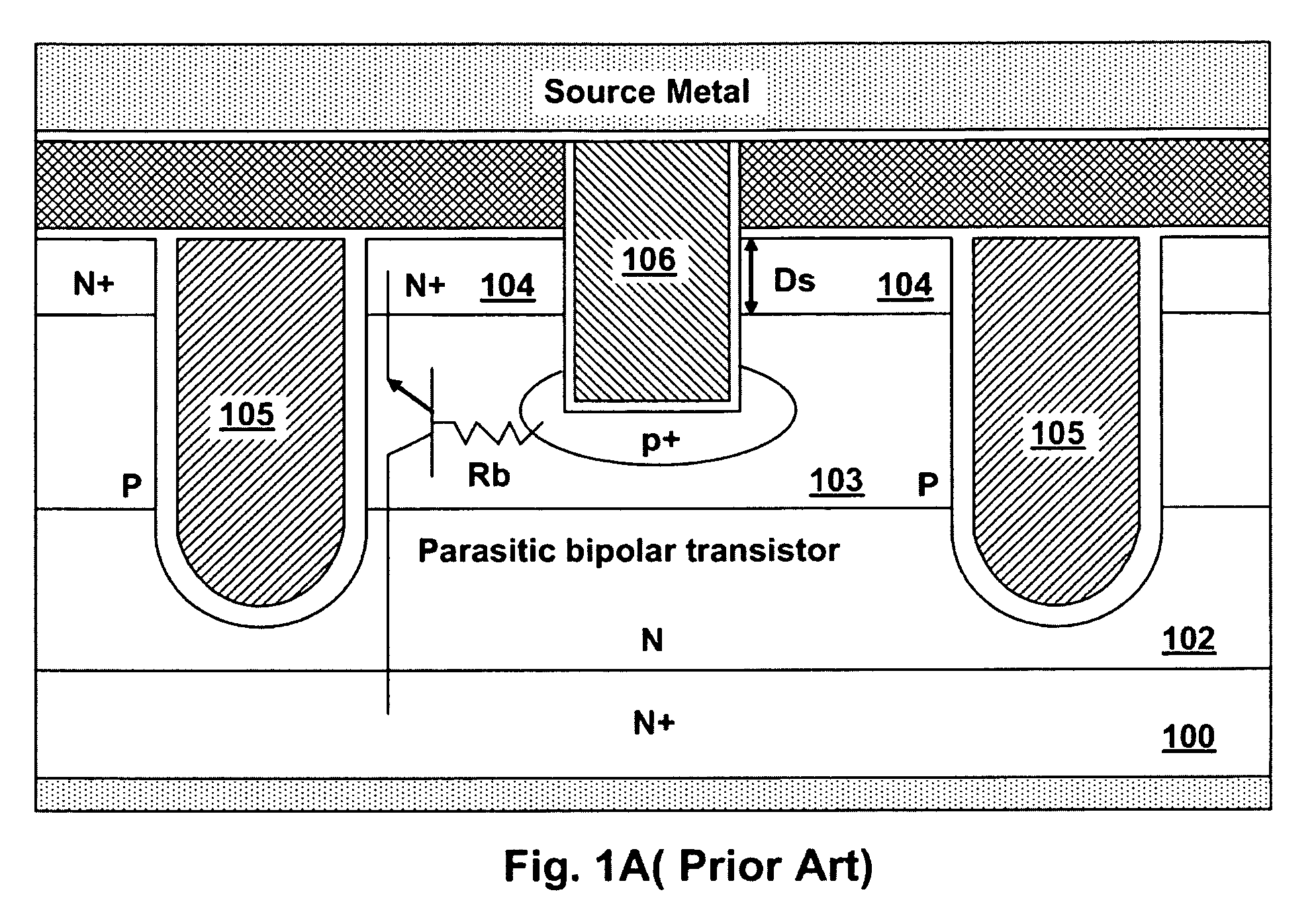

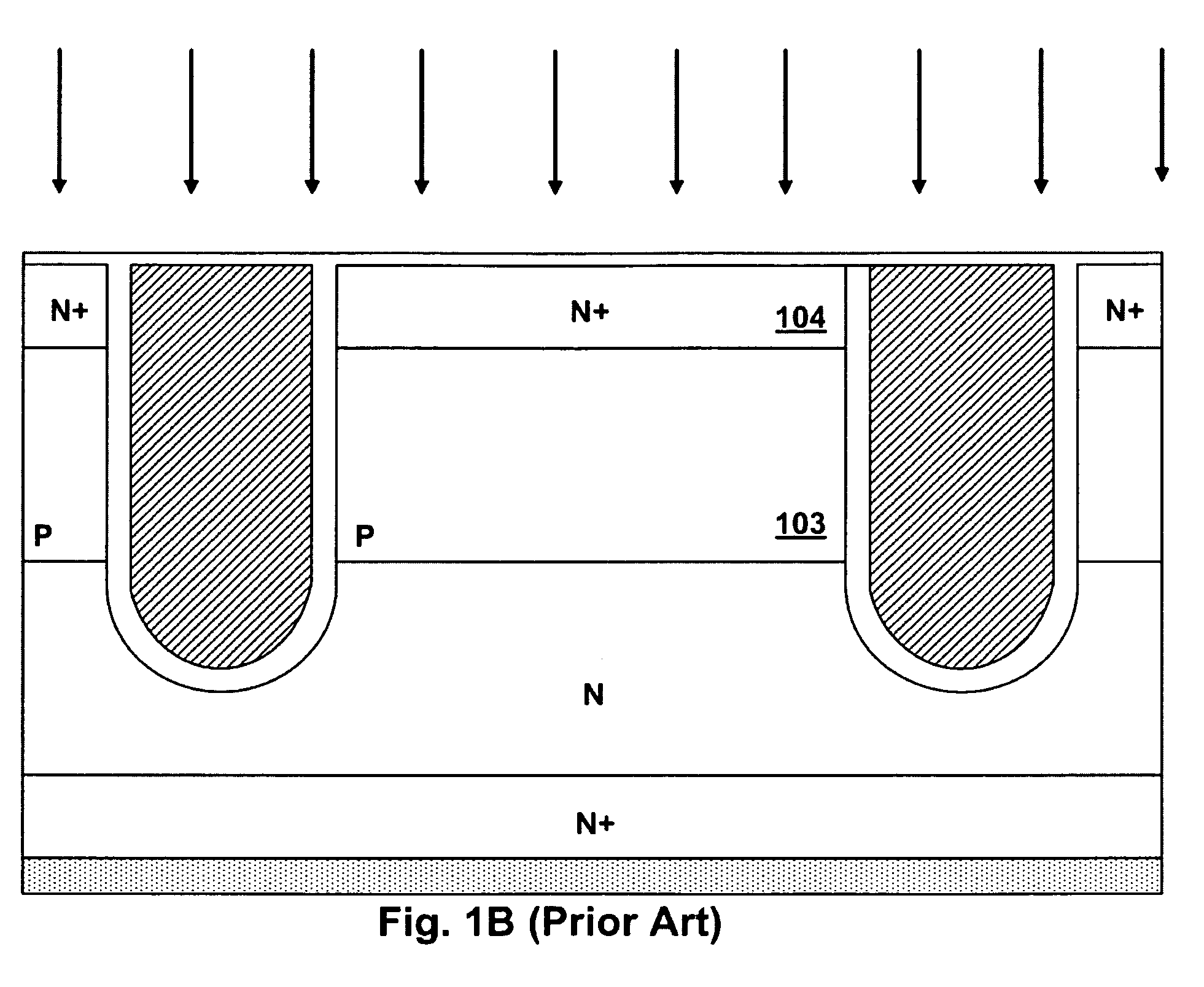

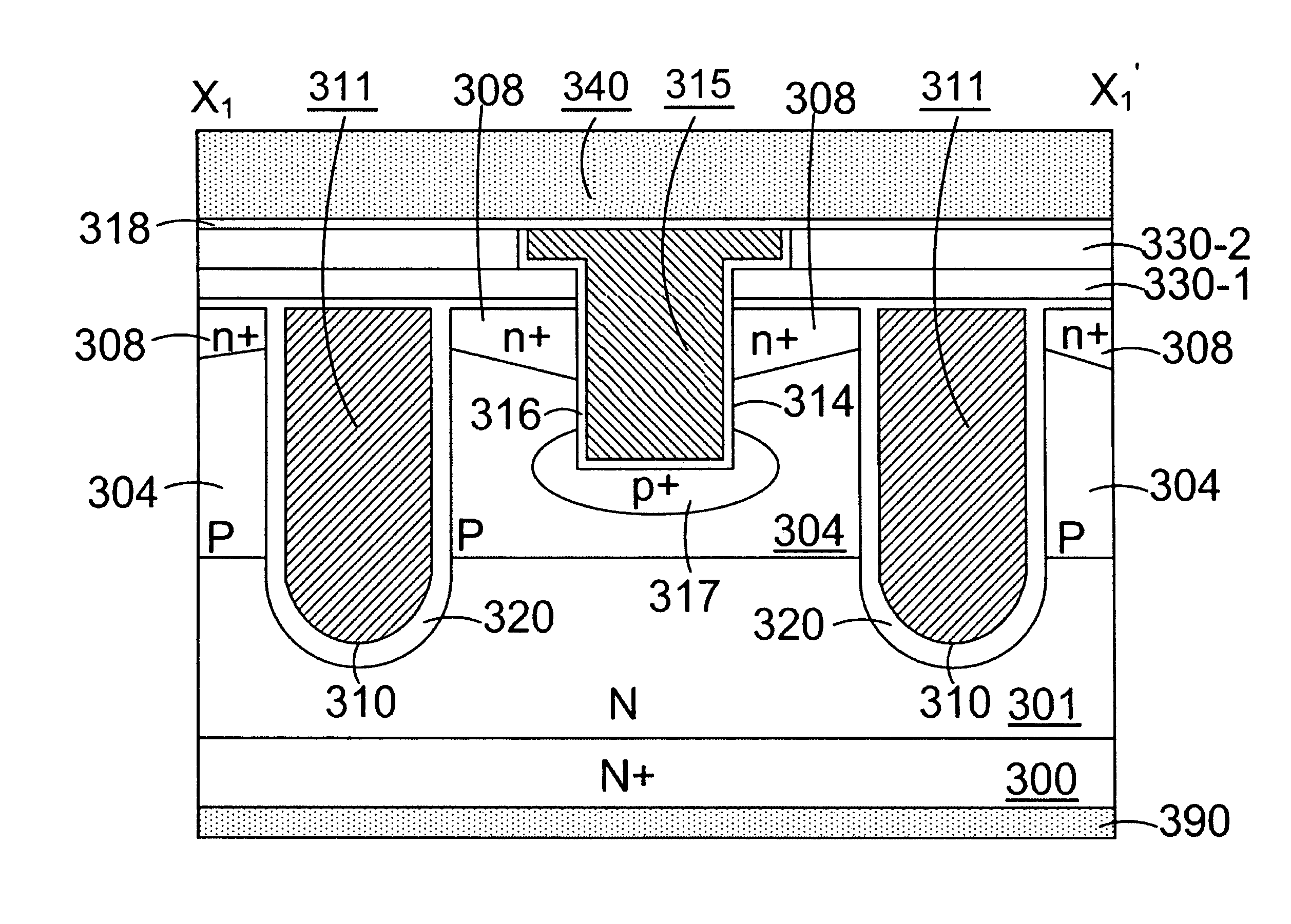

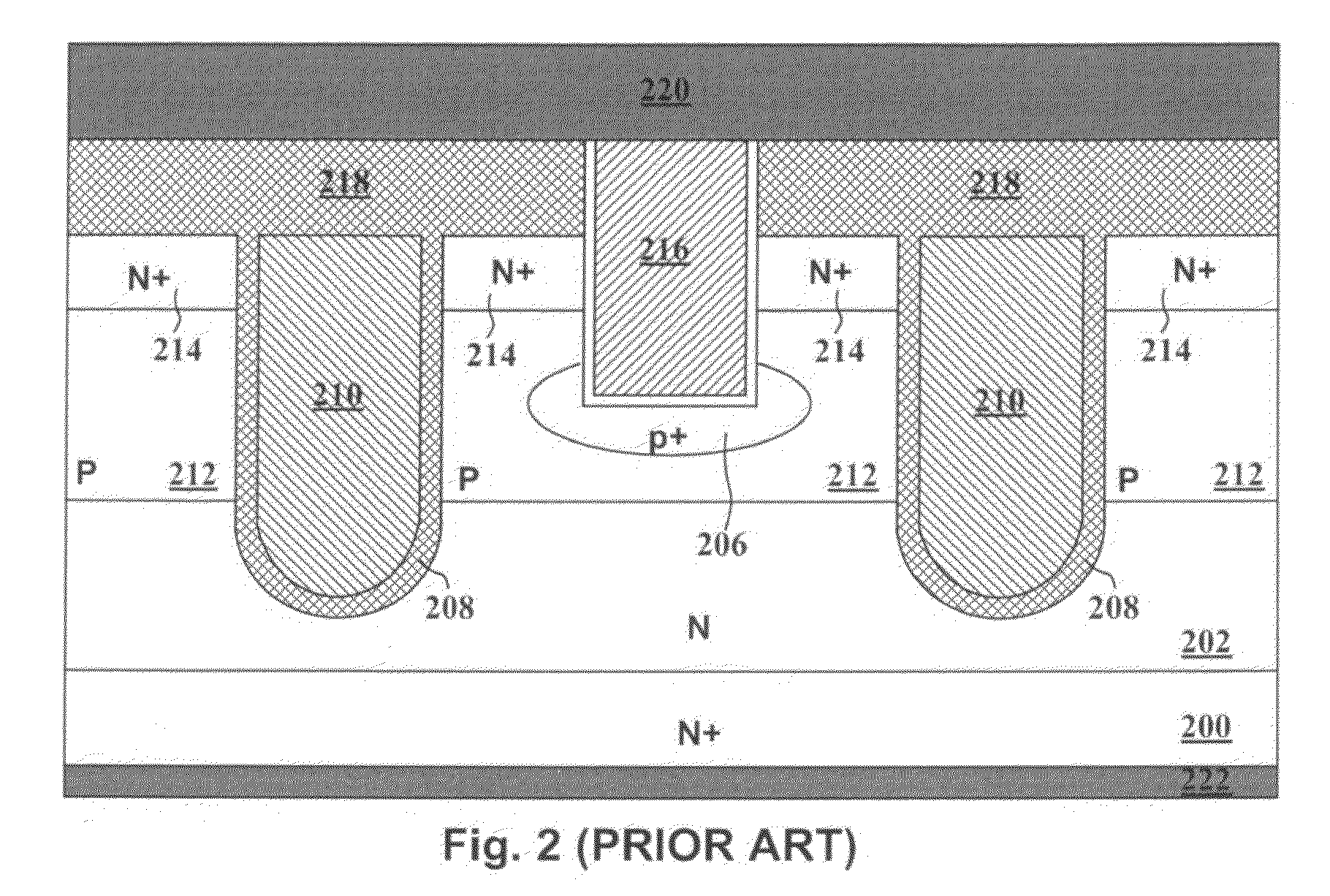

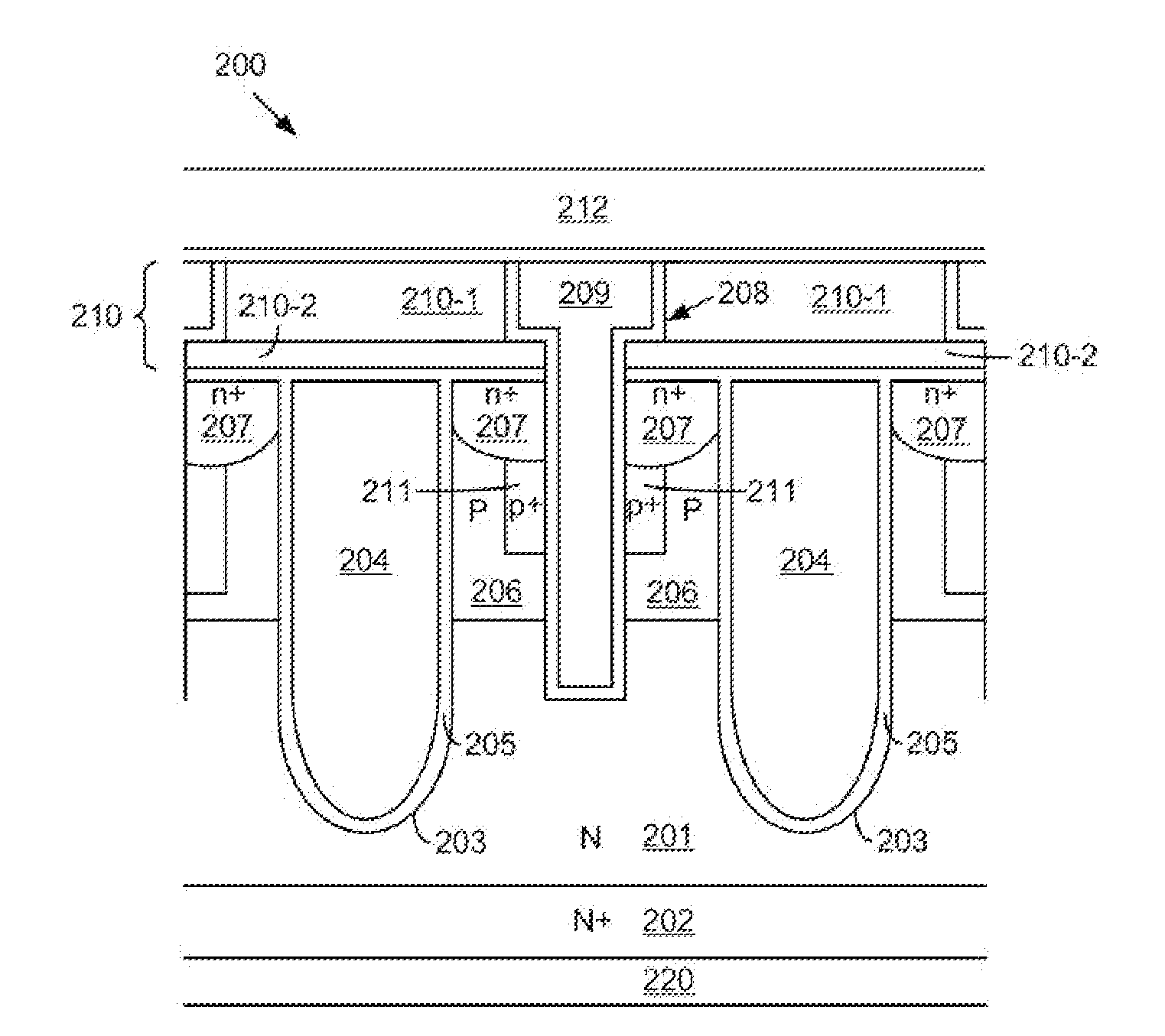

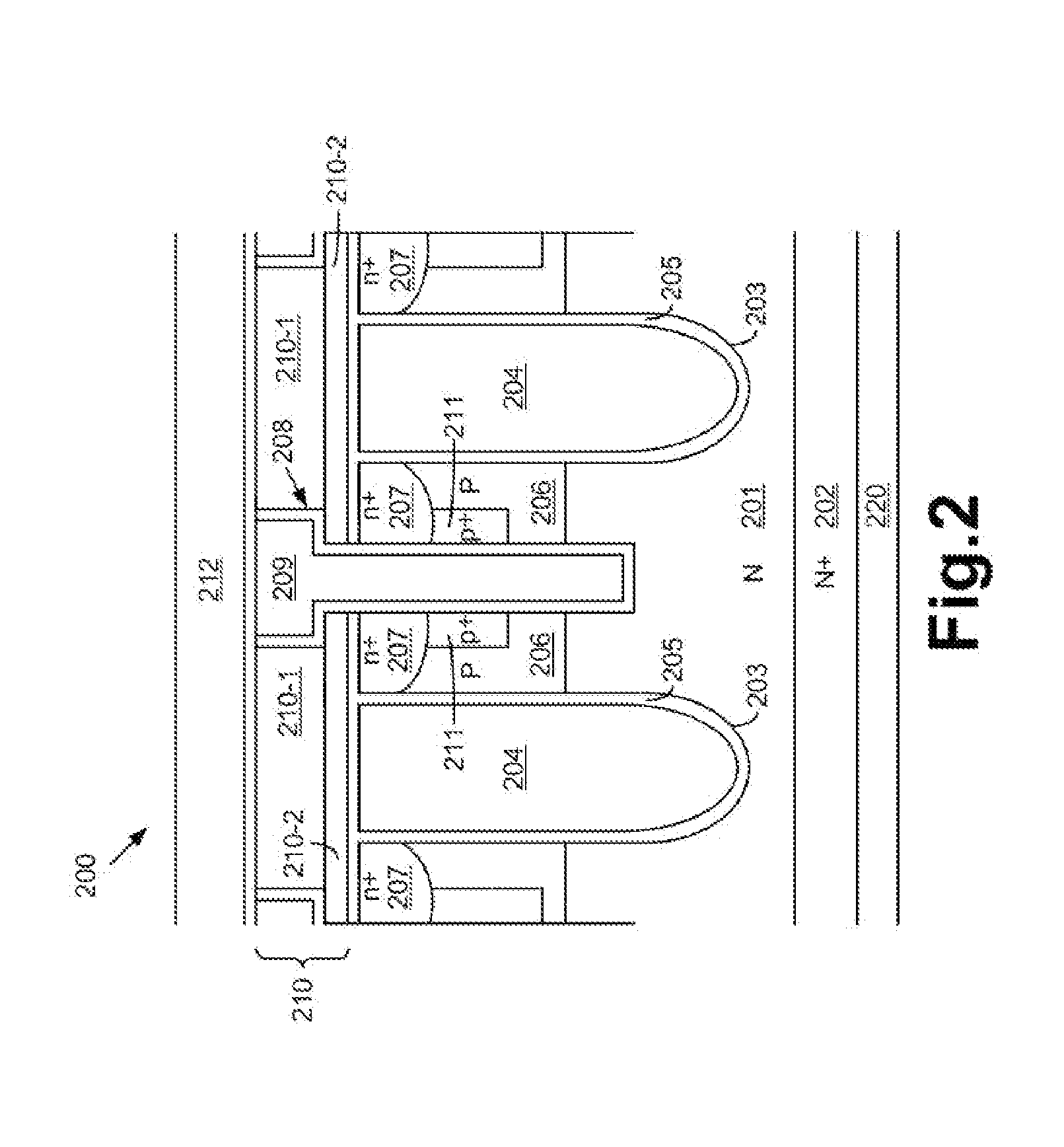

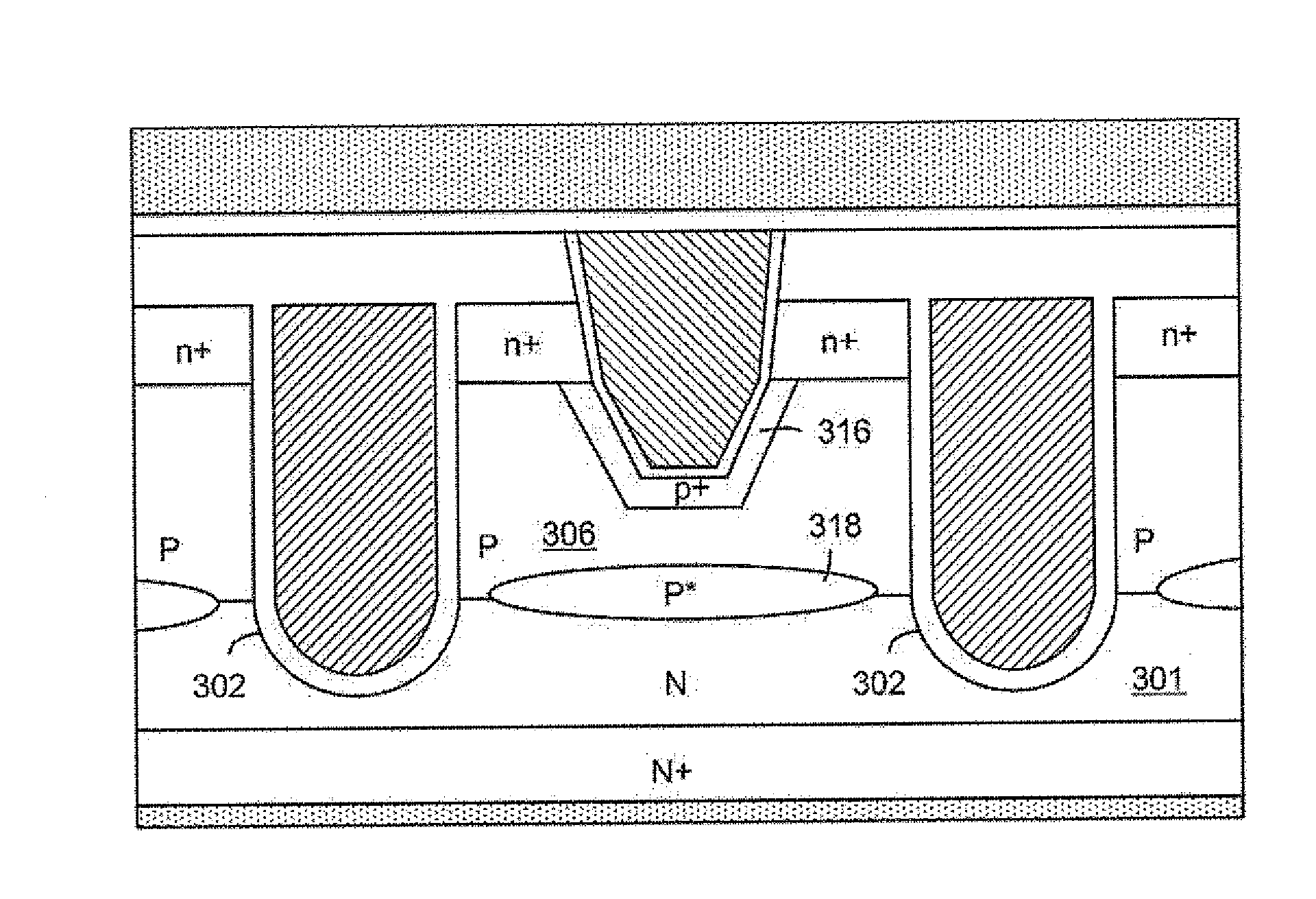

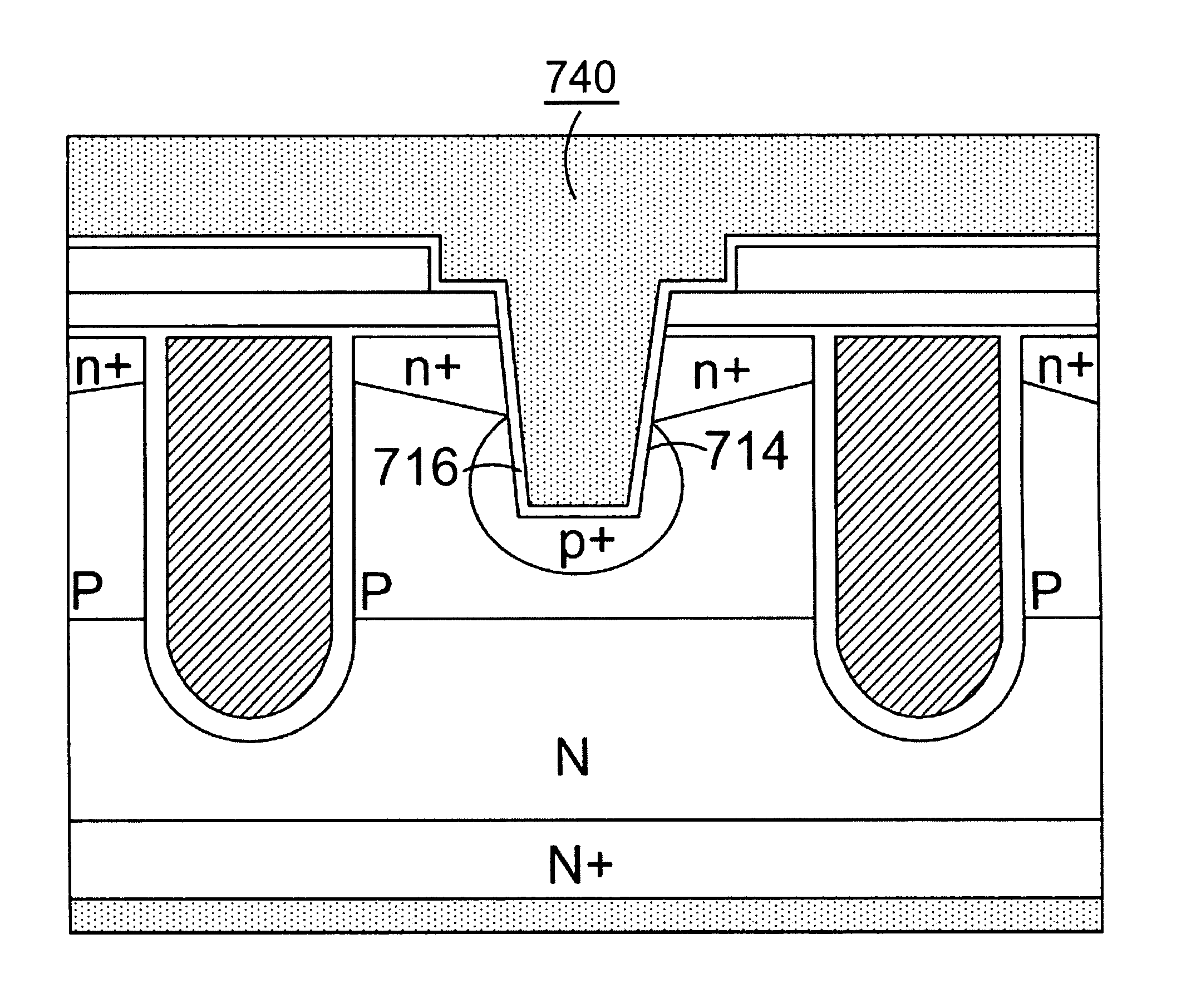

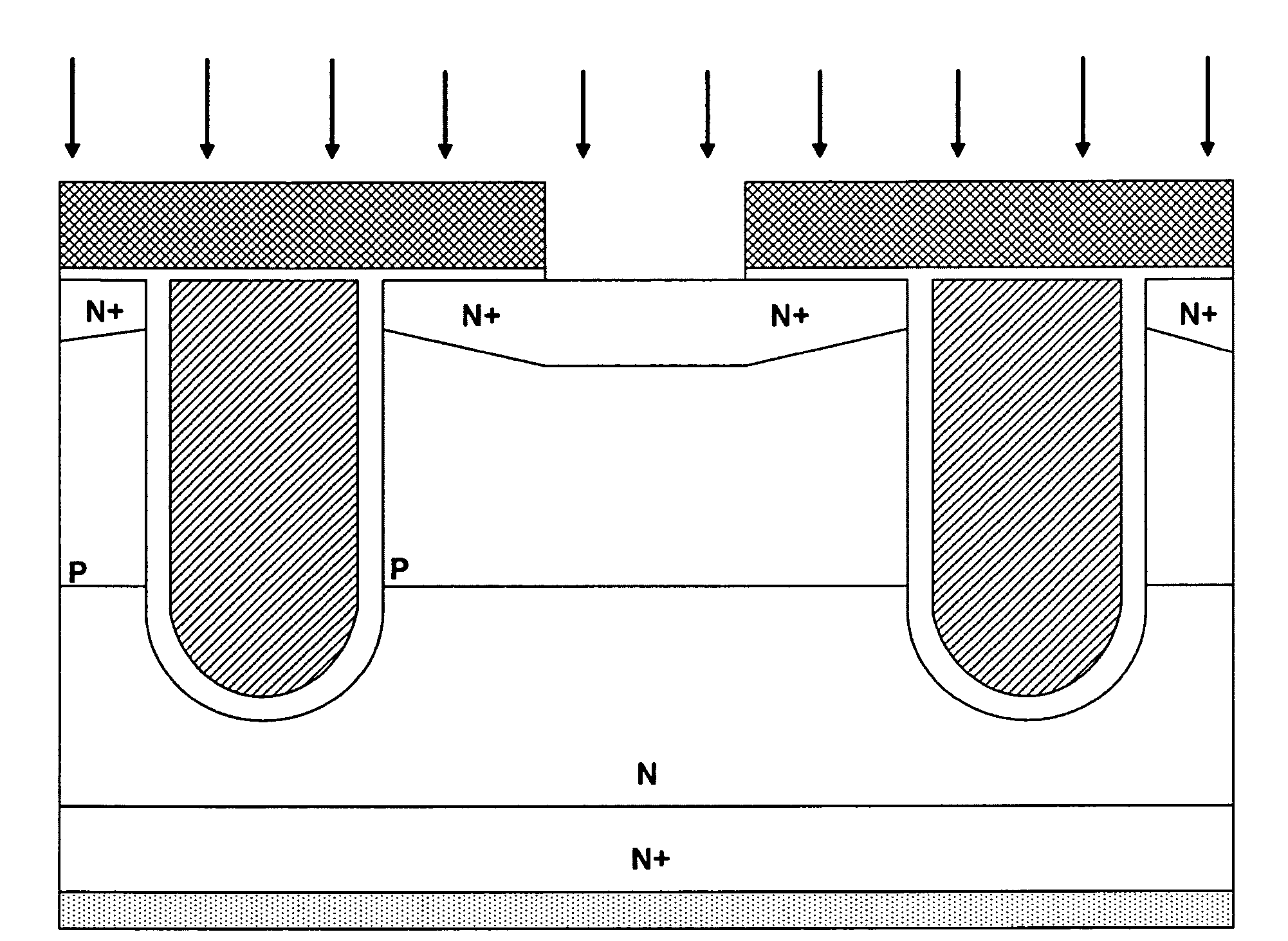

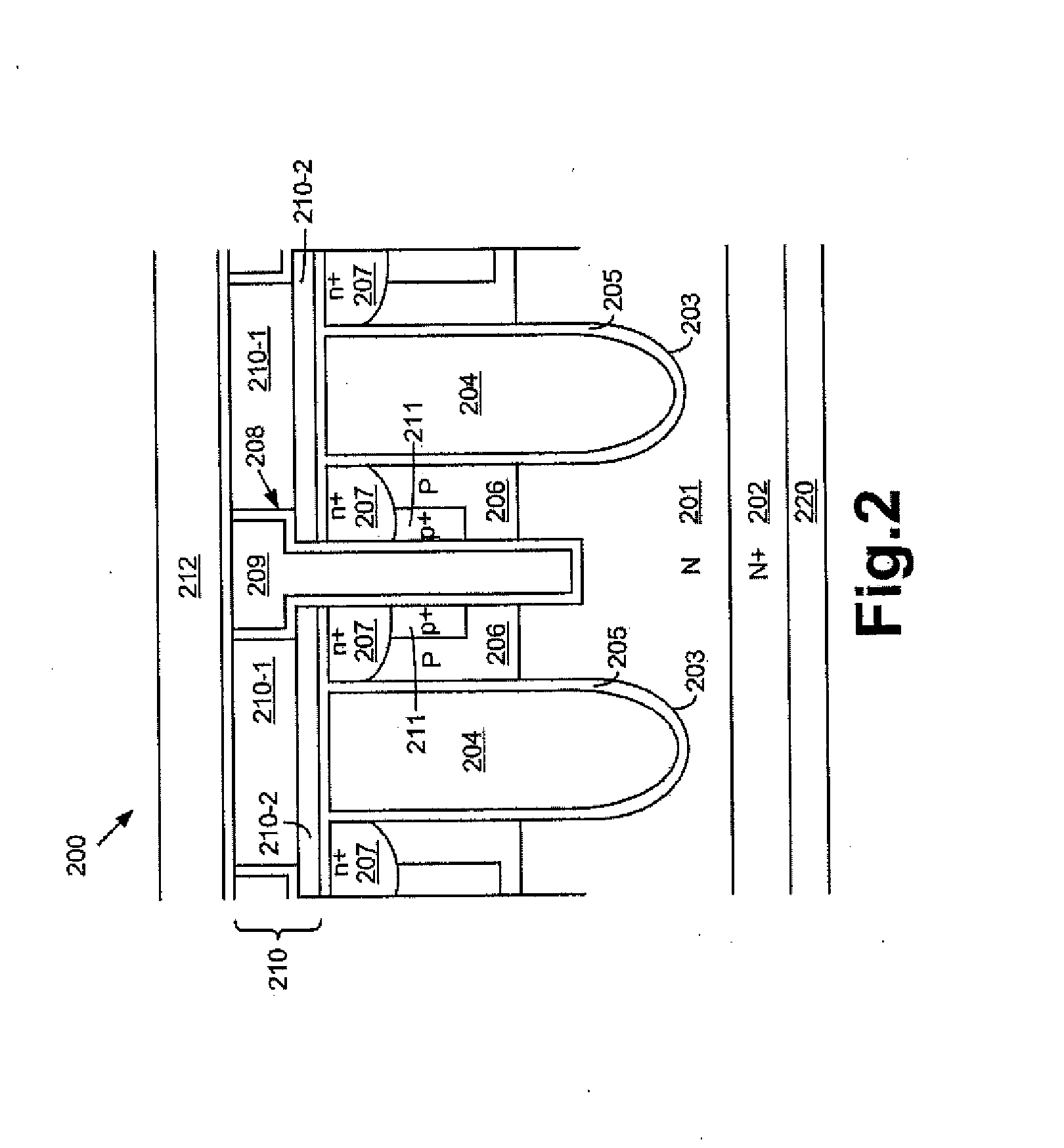

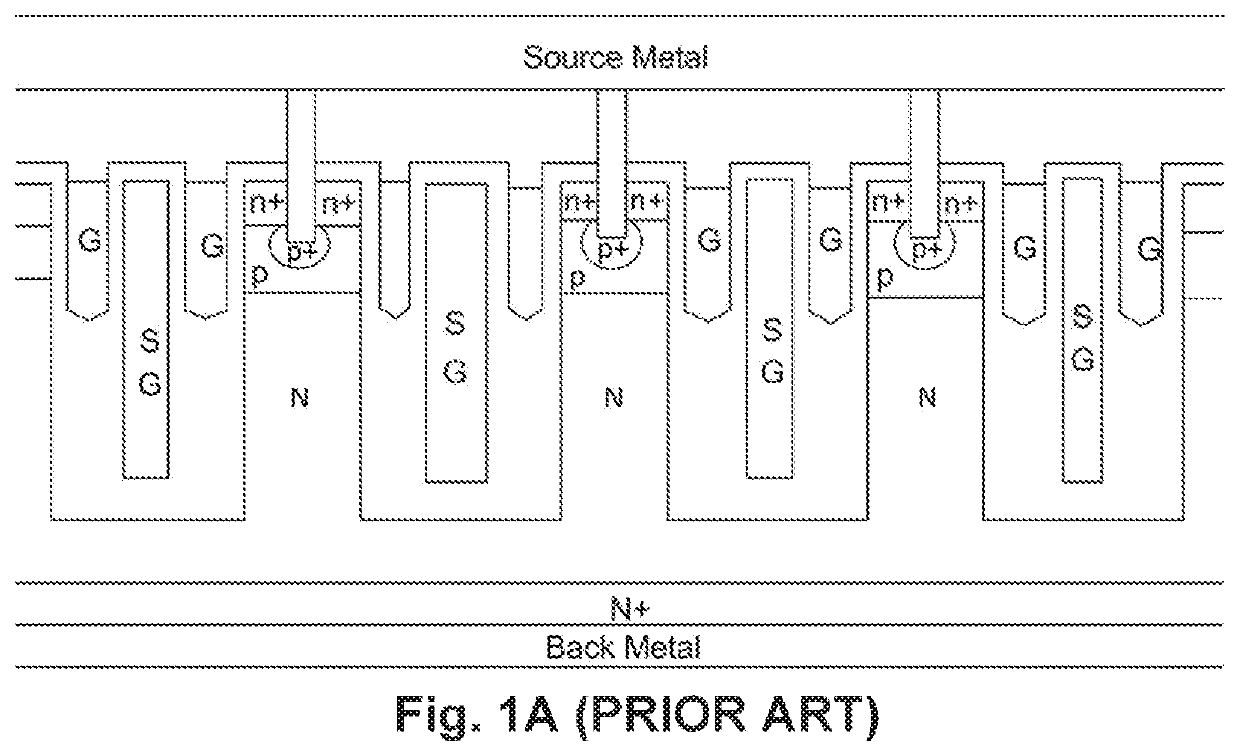

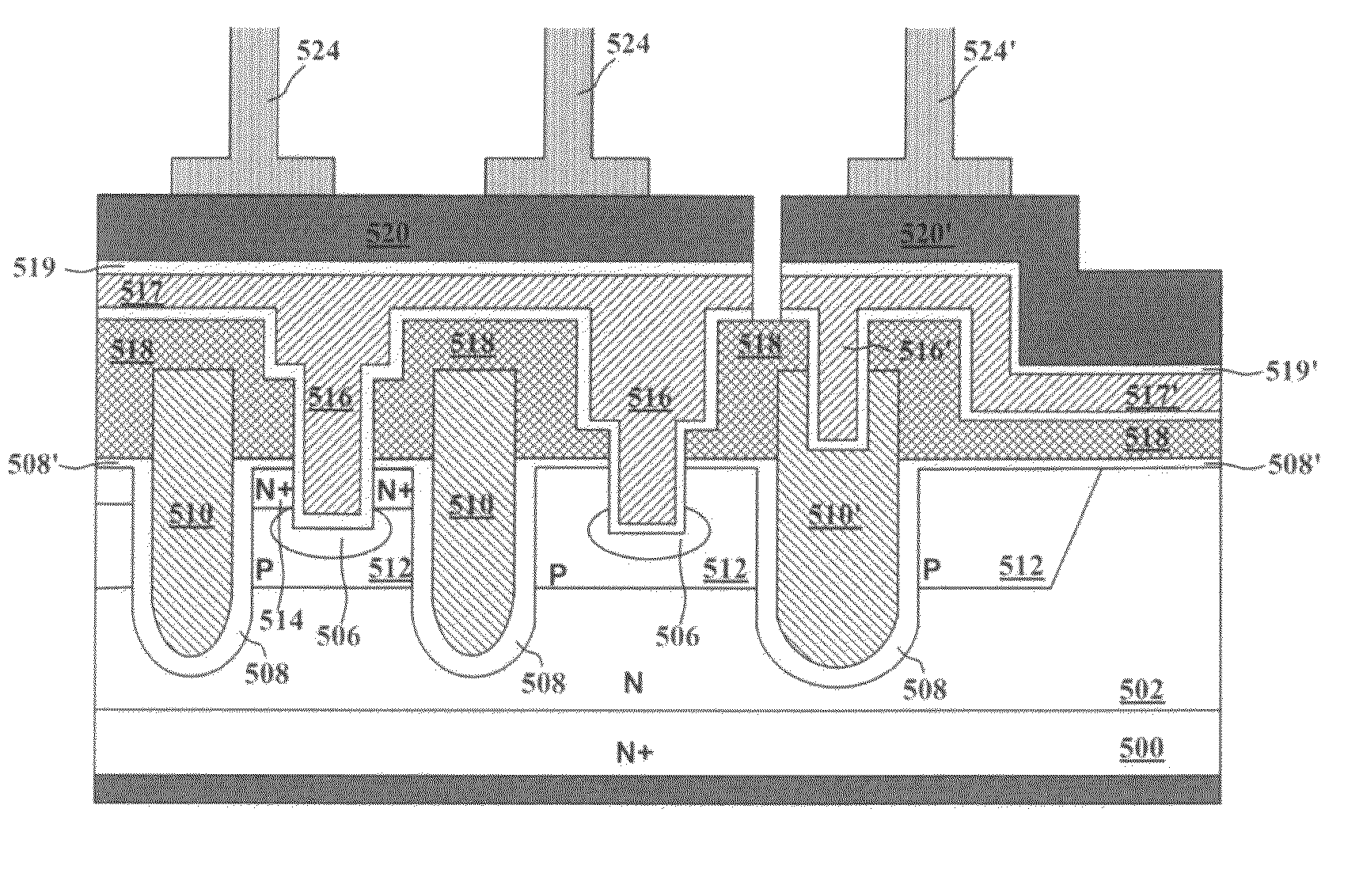

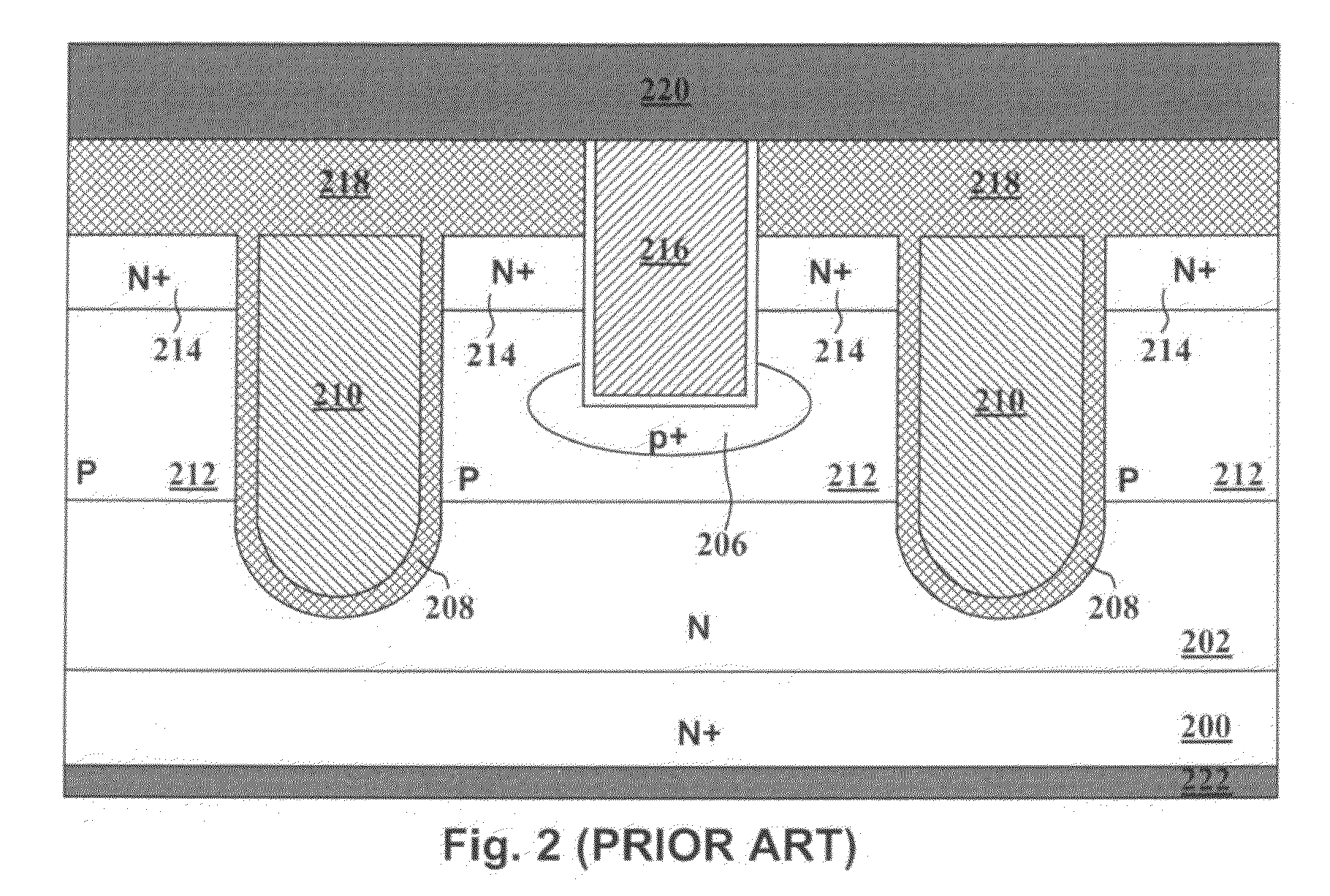

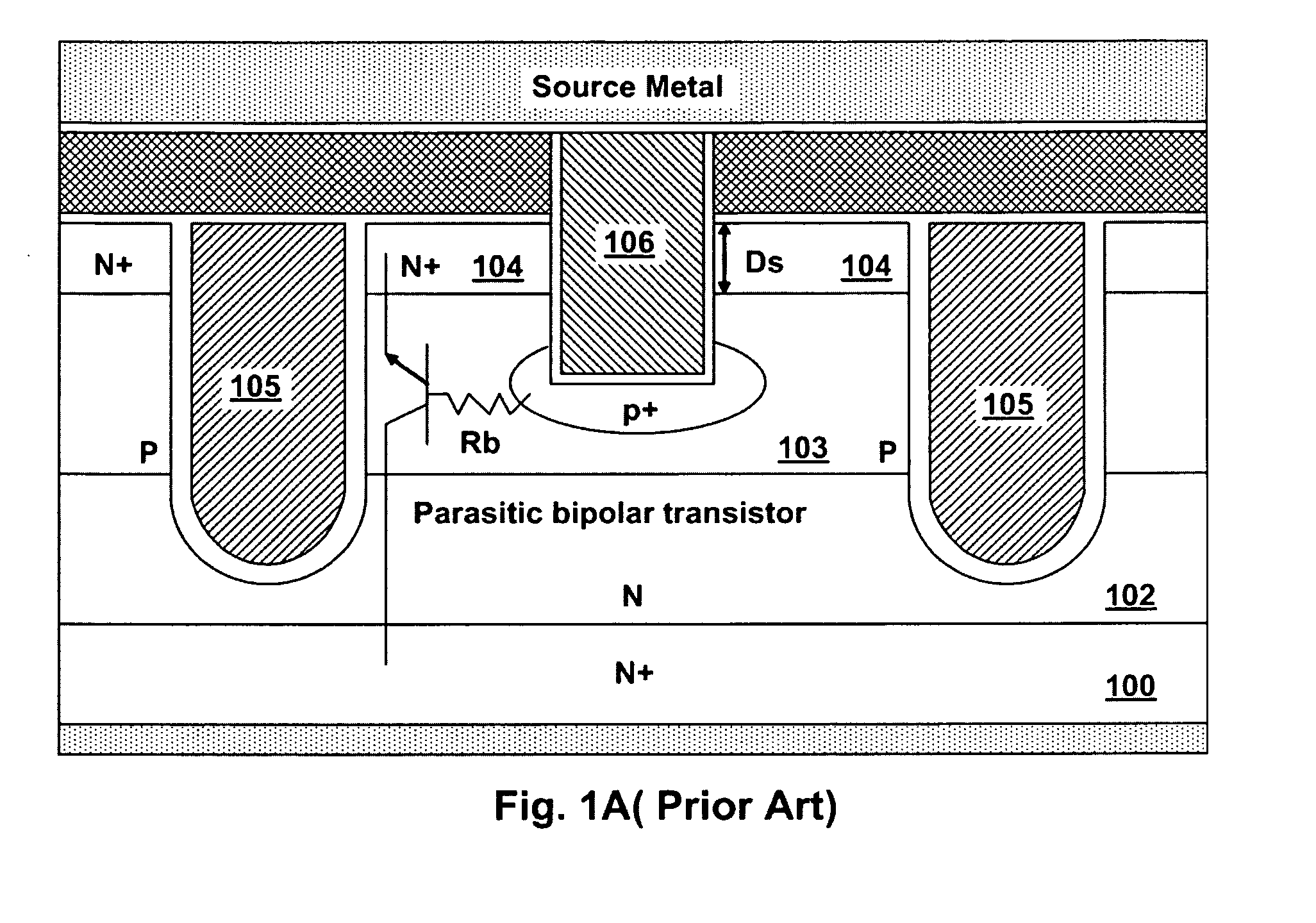

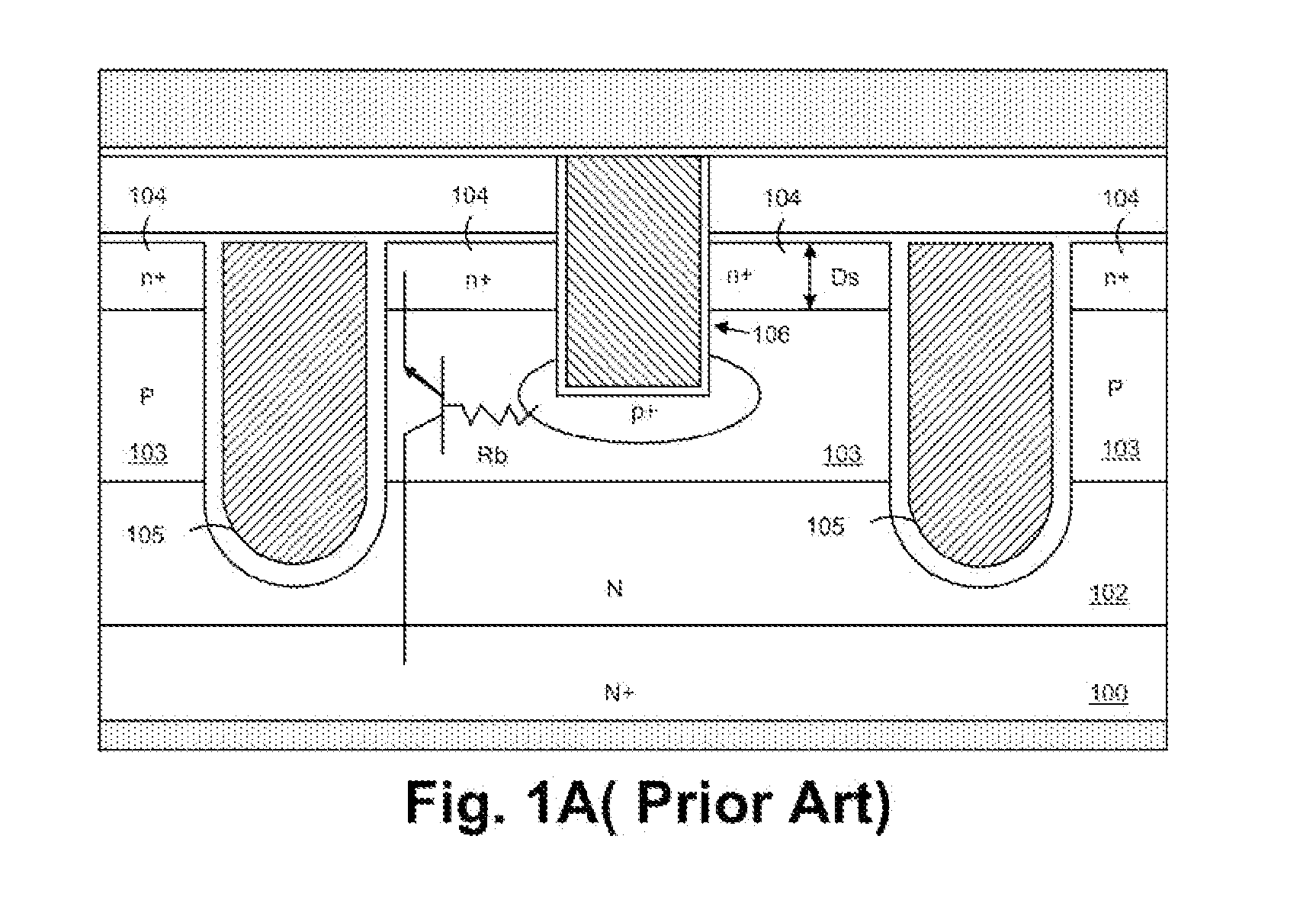

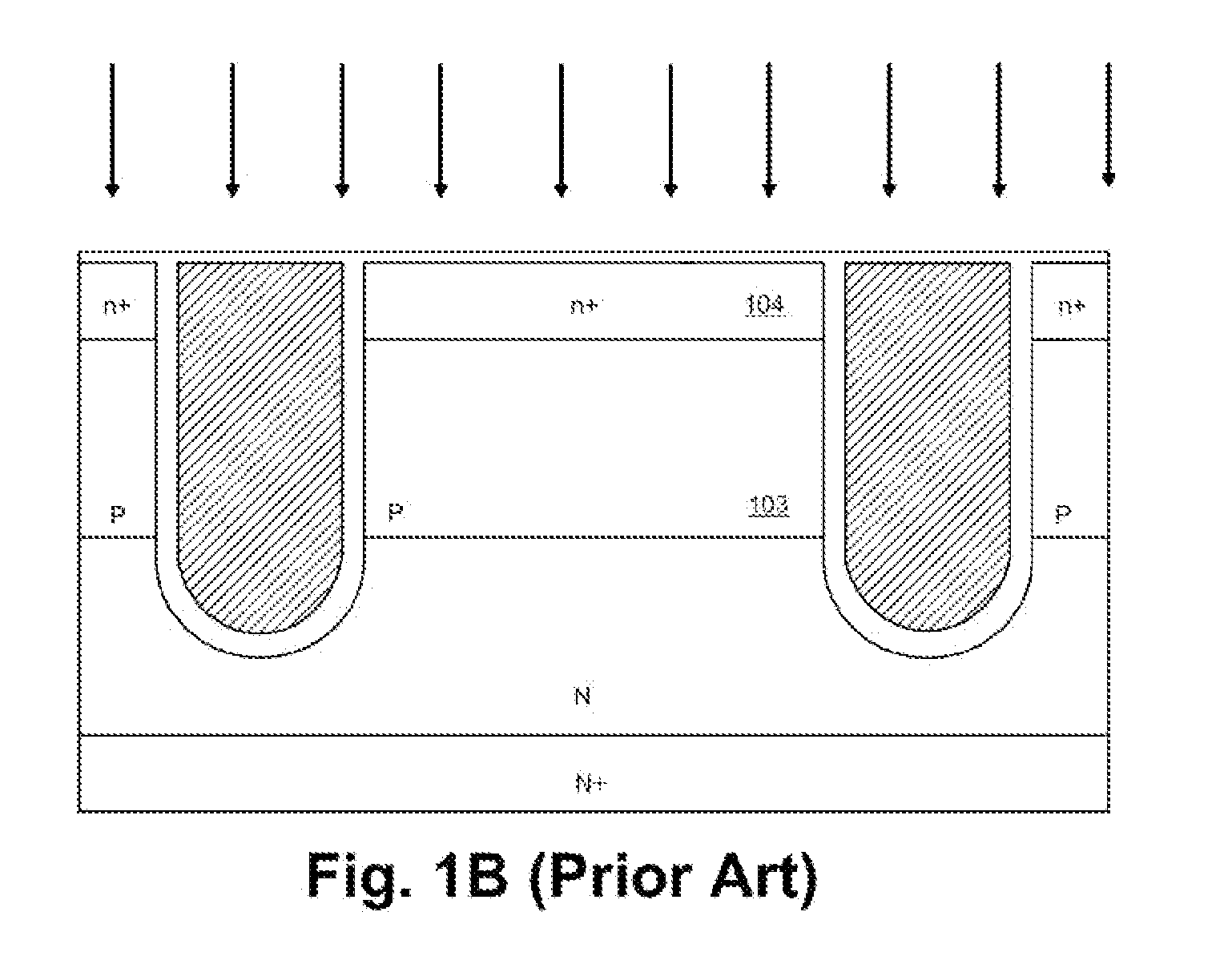

Structure for avalanche improvement of ultra high density trench MOSFET

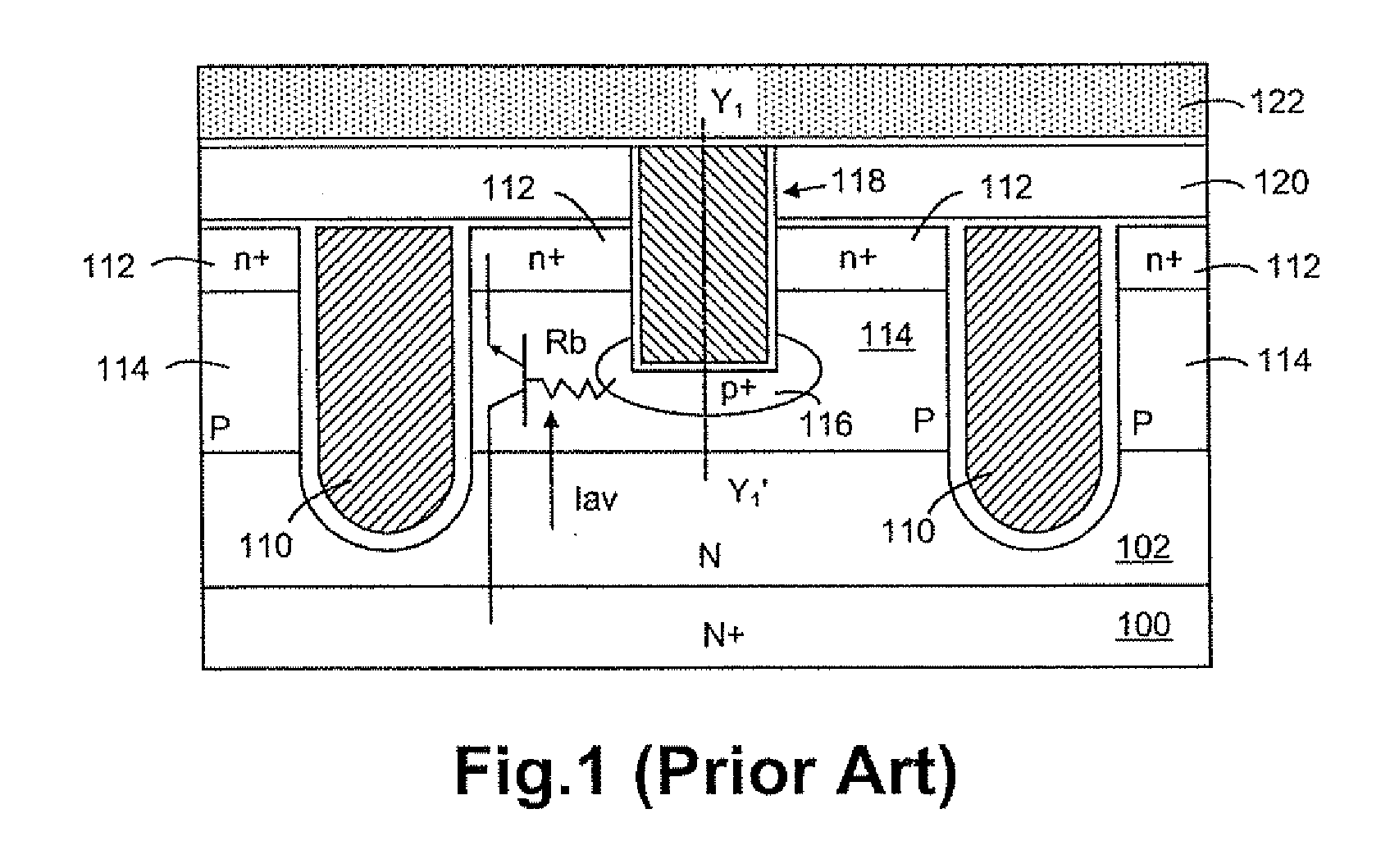

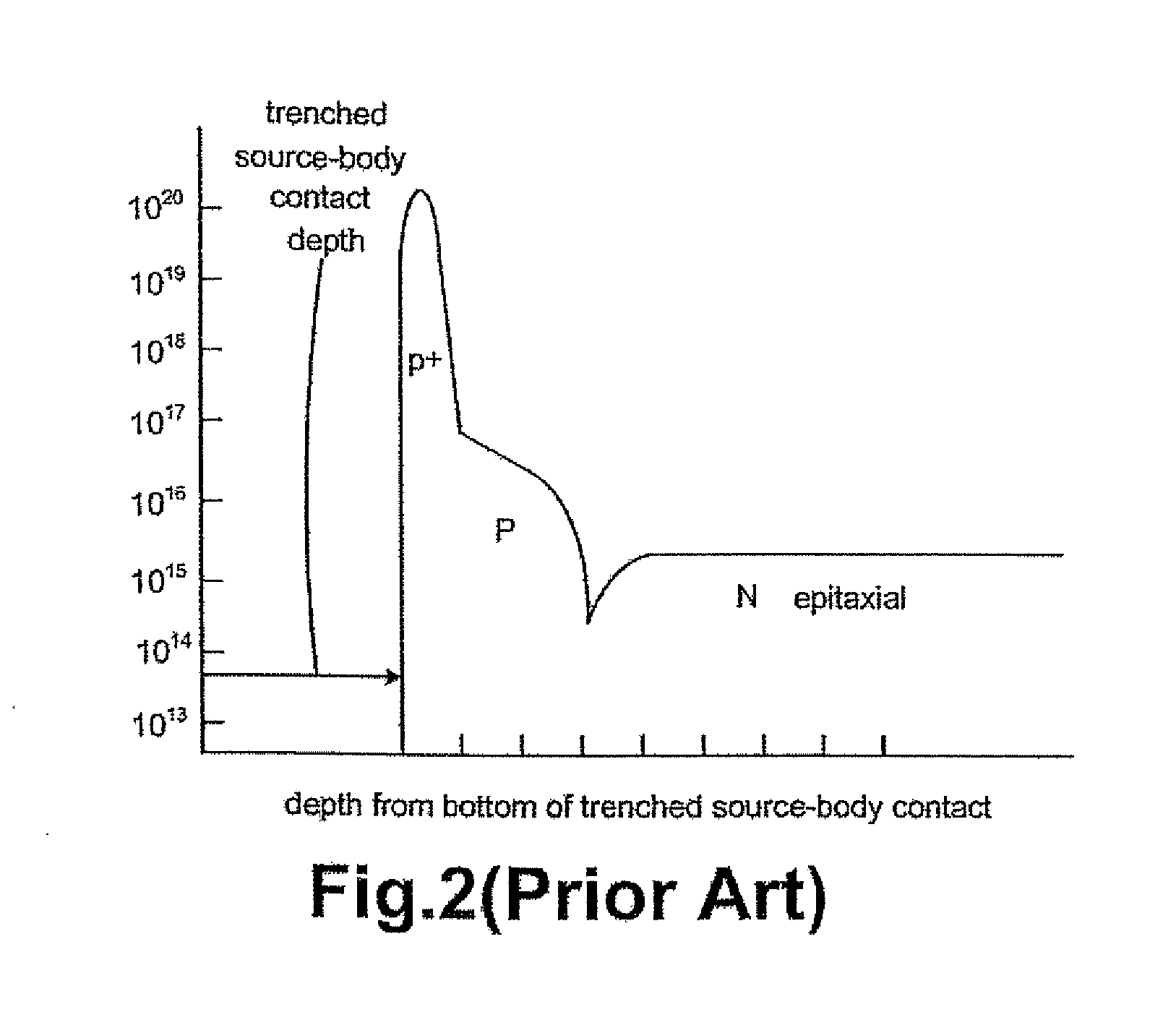

InactiveUS20060273384A1Increase cell densityLower body resistanceSolid-state devicesSemiconductor/solid-state device manufacturingTrench mosfetBody contact

A trenched metal oxide semiconductor field effect transistor (MOSFET) cell that includes a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate. The MOSFET cell further includes a source-body contact trench opened with sidewalls substantially extend vertically relative to a top surface into the source and body regions and filled with contact metal plug. A body-resistance reduction region doped with body-doped is formed to surround the source-body contact trench to reduce a body-region resistance between the source-body contact metal and the trenched gate to improve an avalanche capability.

Owner:M MOS SEMICON

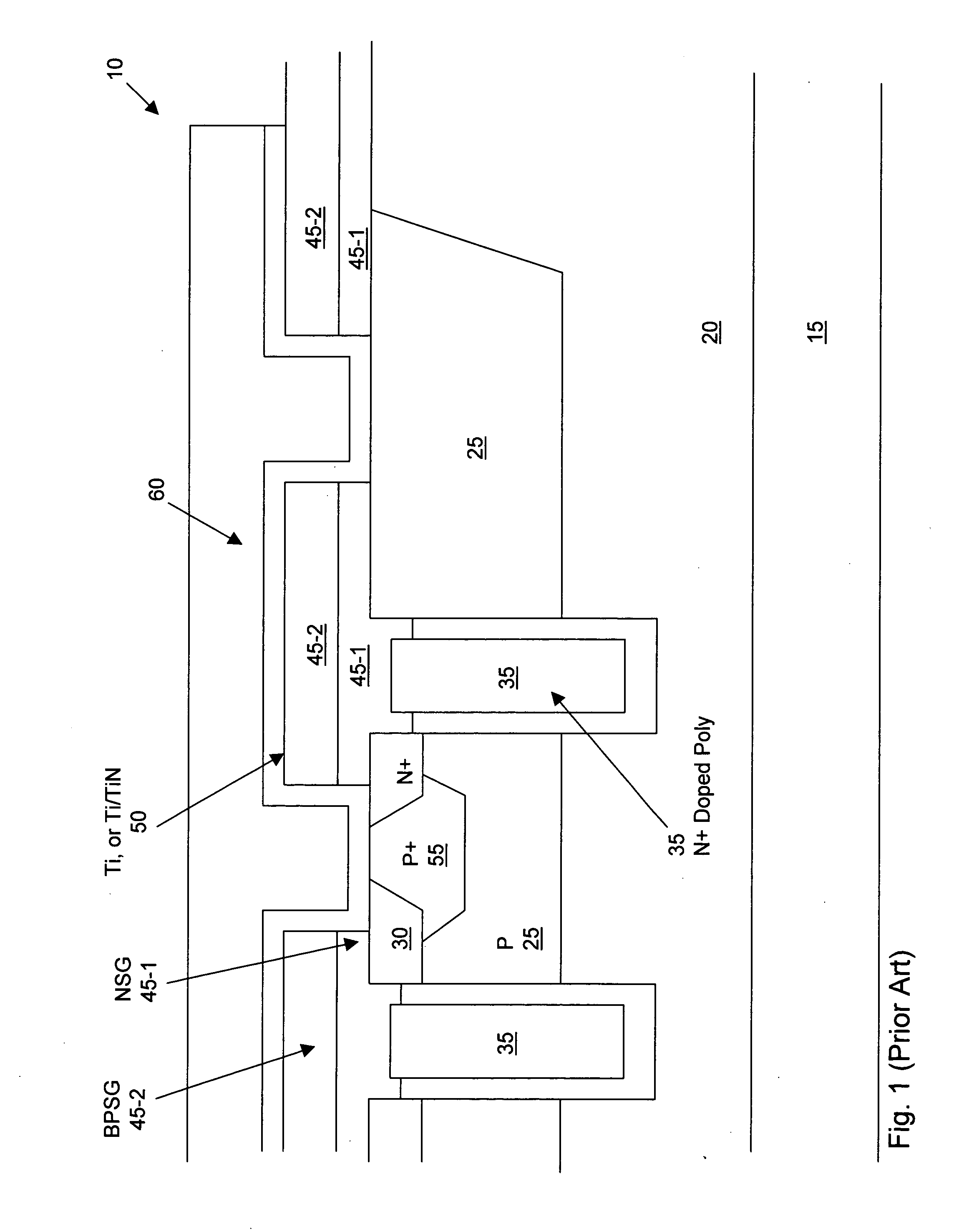

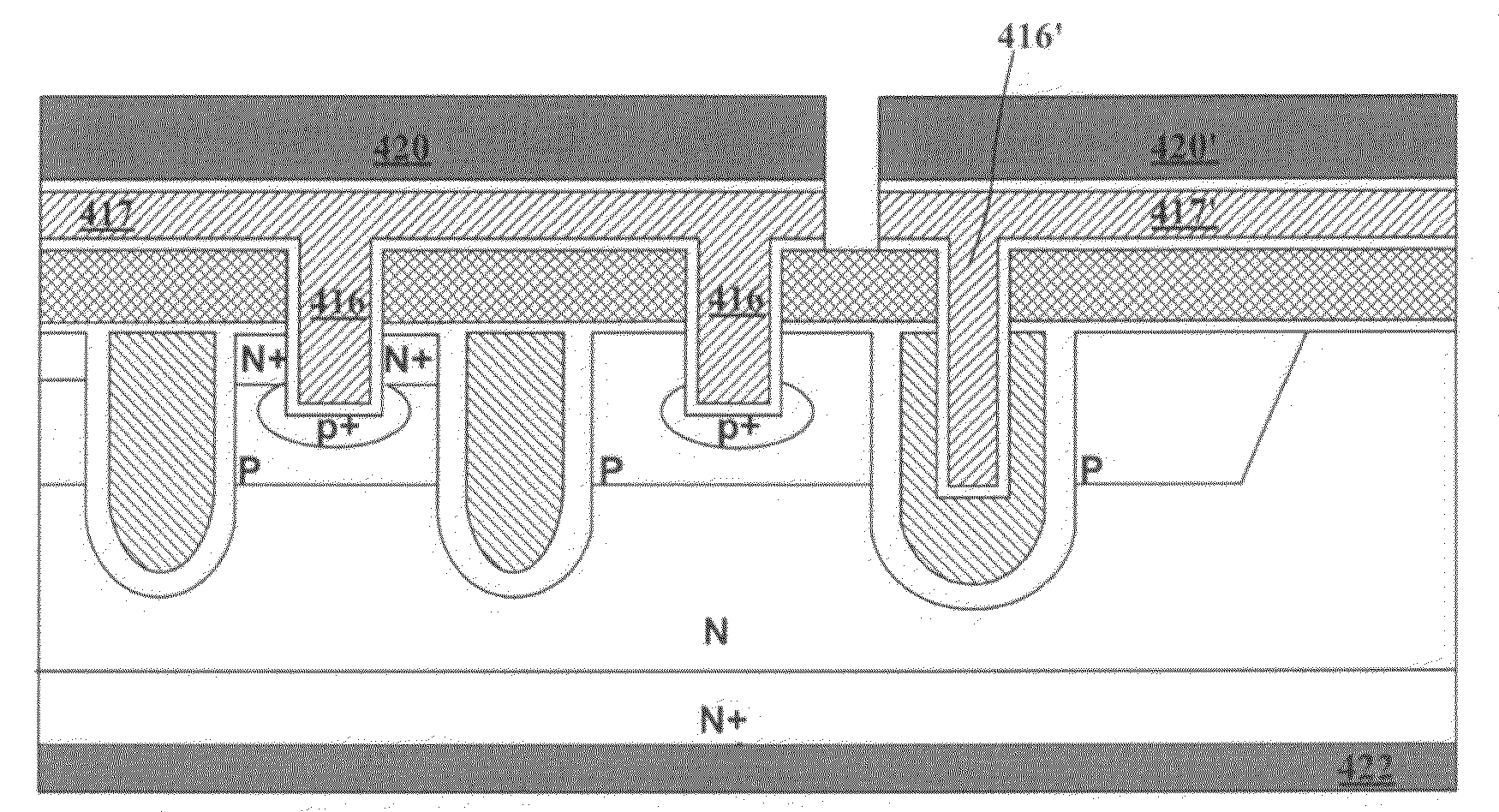

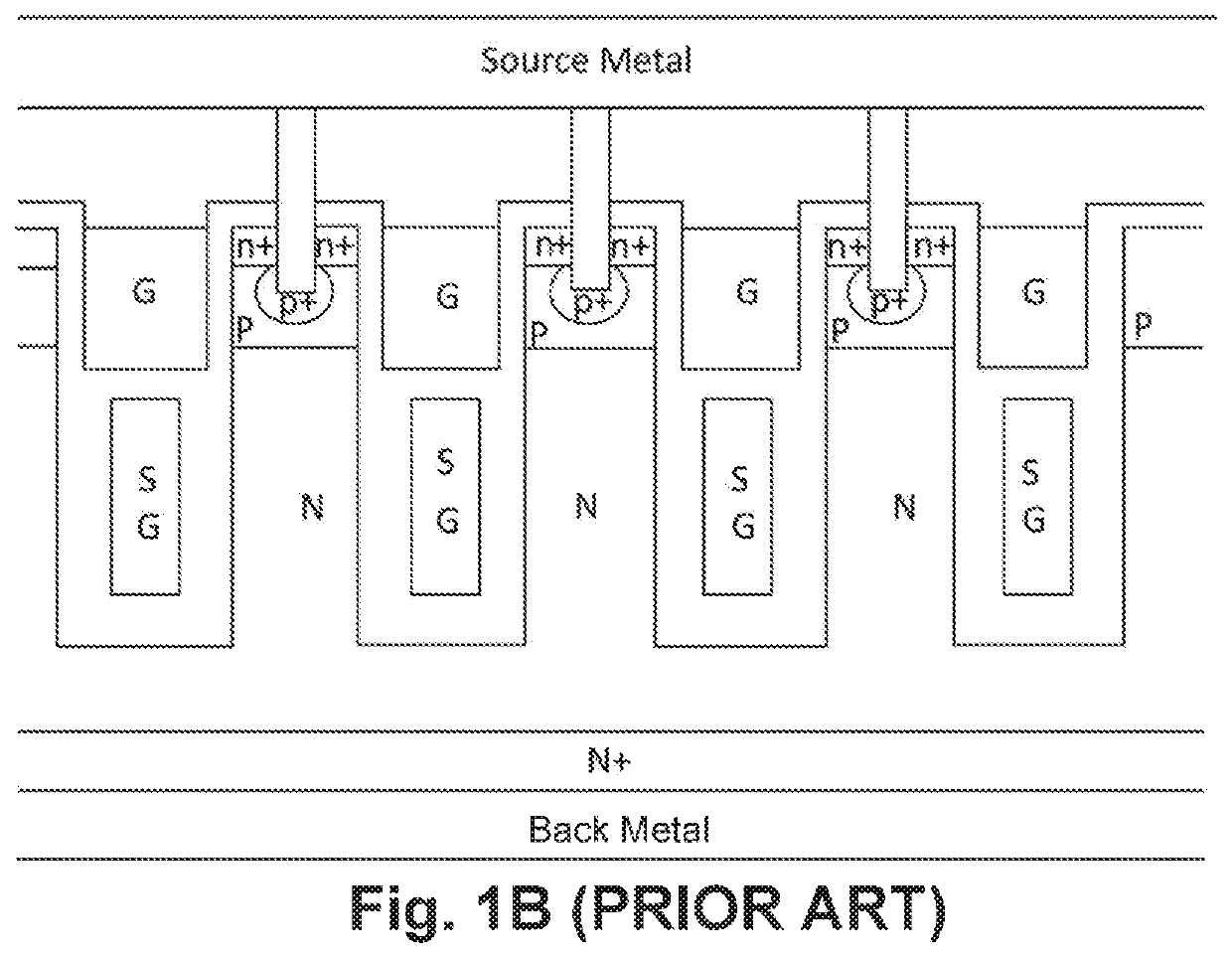

Trench MOSFET structures using three masks process

ActiveUS20110006363A1Reduced footprintSmall sizeTransistorSolid-state devicesTrench mosfetInter layer

A trench MOSFET structure having improved avalanche capability is disclosed, wherein the source region is formed by performing source Ion Implantation through contact open region of a contact interlayer, and further diffused to optimize a trade-off between Rds and the avalanche capability. Thus, only three masks are needed in fabrication process, which are trench mask, contact mask and metal mask. Furthermore, said source region has a doping concentration along channel region lower than along contact trench region, and source junction depth along channel region shallower than along contact trench, and source doping profile along surface of epitaxial layer has Guassian-distribution from trenched source-body contact to channel region.

Owner:FORCE MOS TECH CO LTD

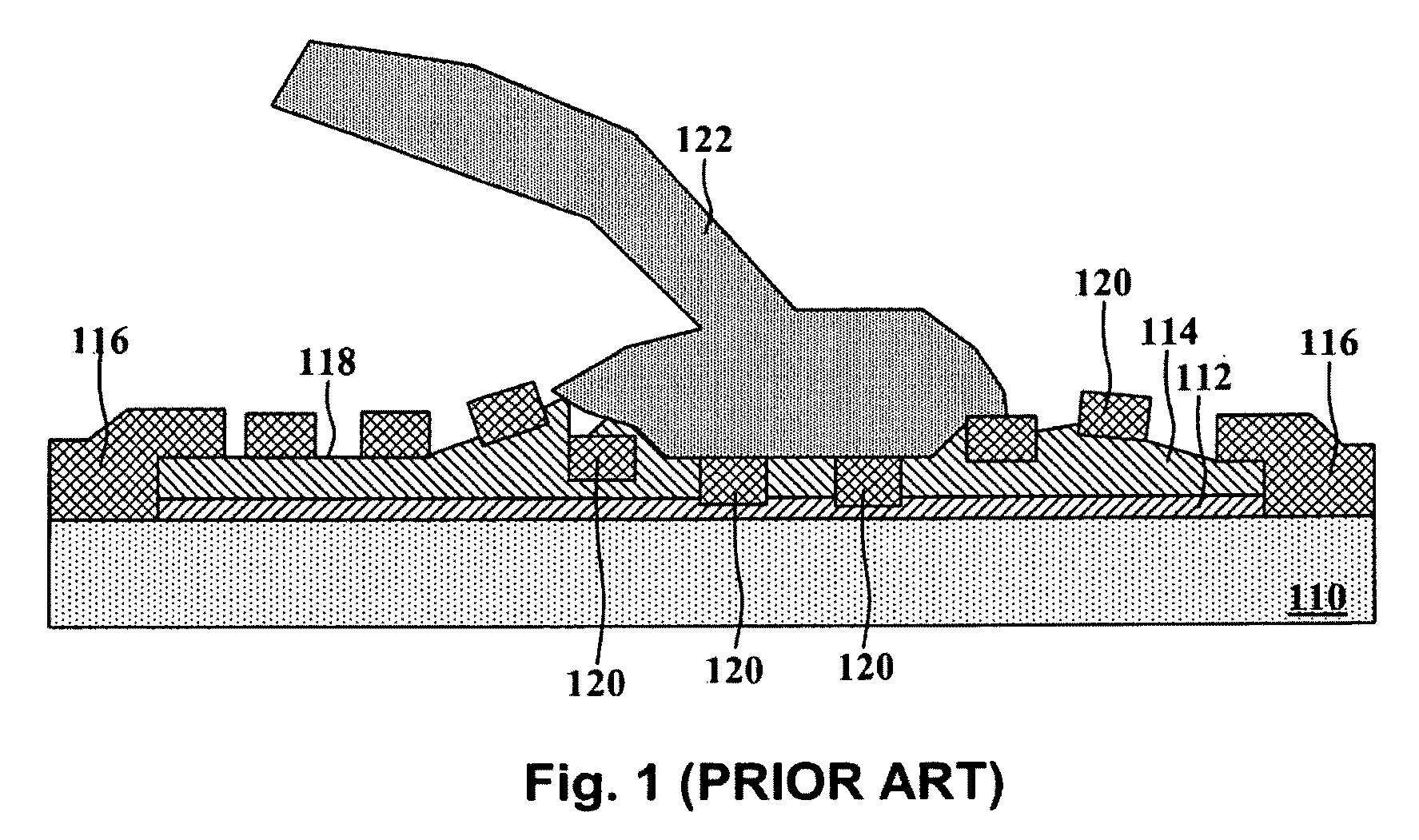

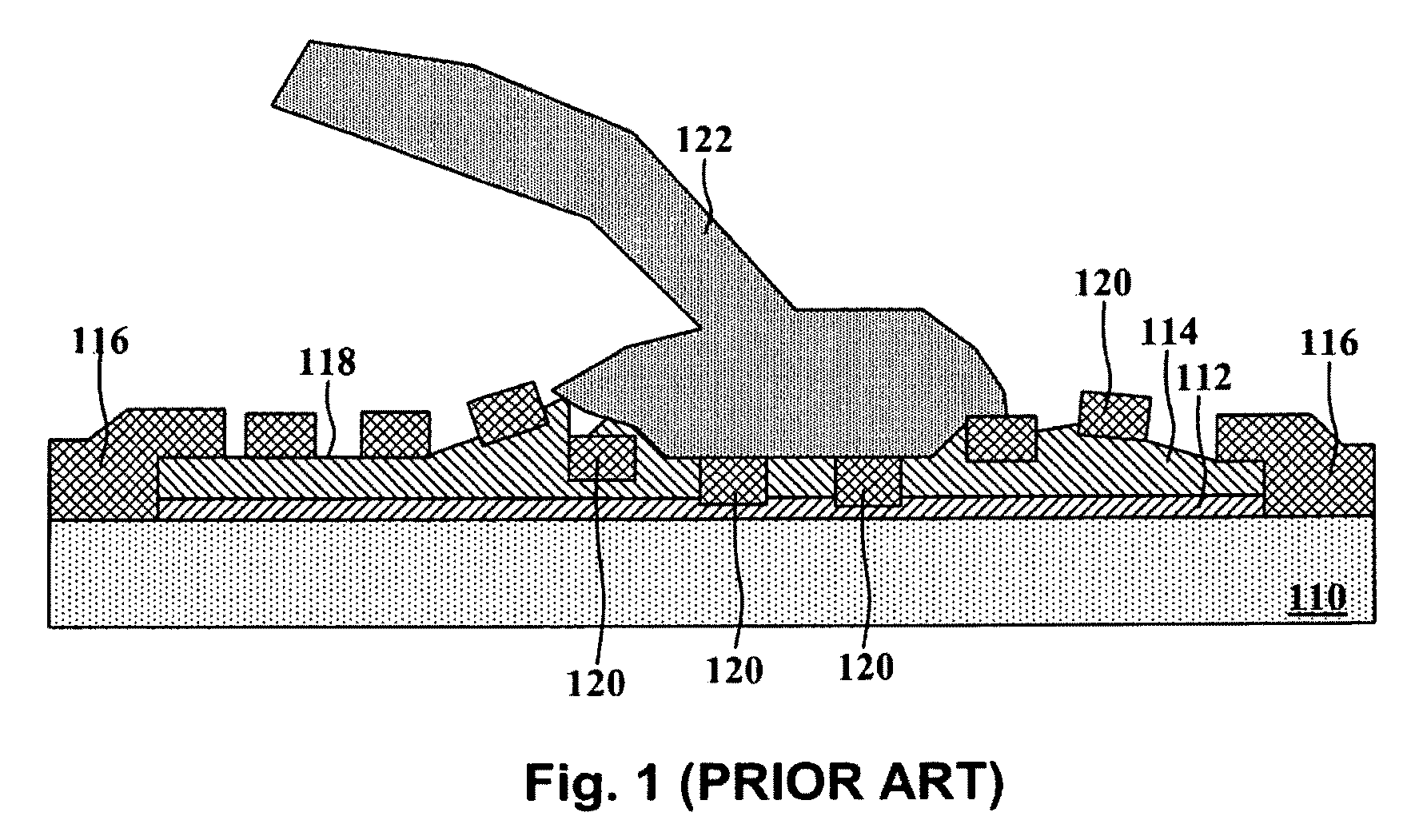

Metal schemes of trench MOSFET for copper bonding

ActiveUS20100176445A1Increase costMinimize Cu wire bonding damageSemiconductor/solid-state device detailsSolid-state devicesTrench mosfetCopper wire

A trench MOSFET with improved metal schemes is disclosed. The improved contact structure applies a buffer layer to minimize the bonding damage to semiconductor when bonding copper wire upon front source and gate metal without additional cost.

Owner:FORCE MOS TECH CO LTD

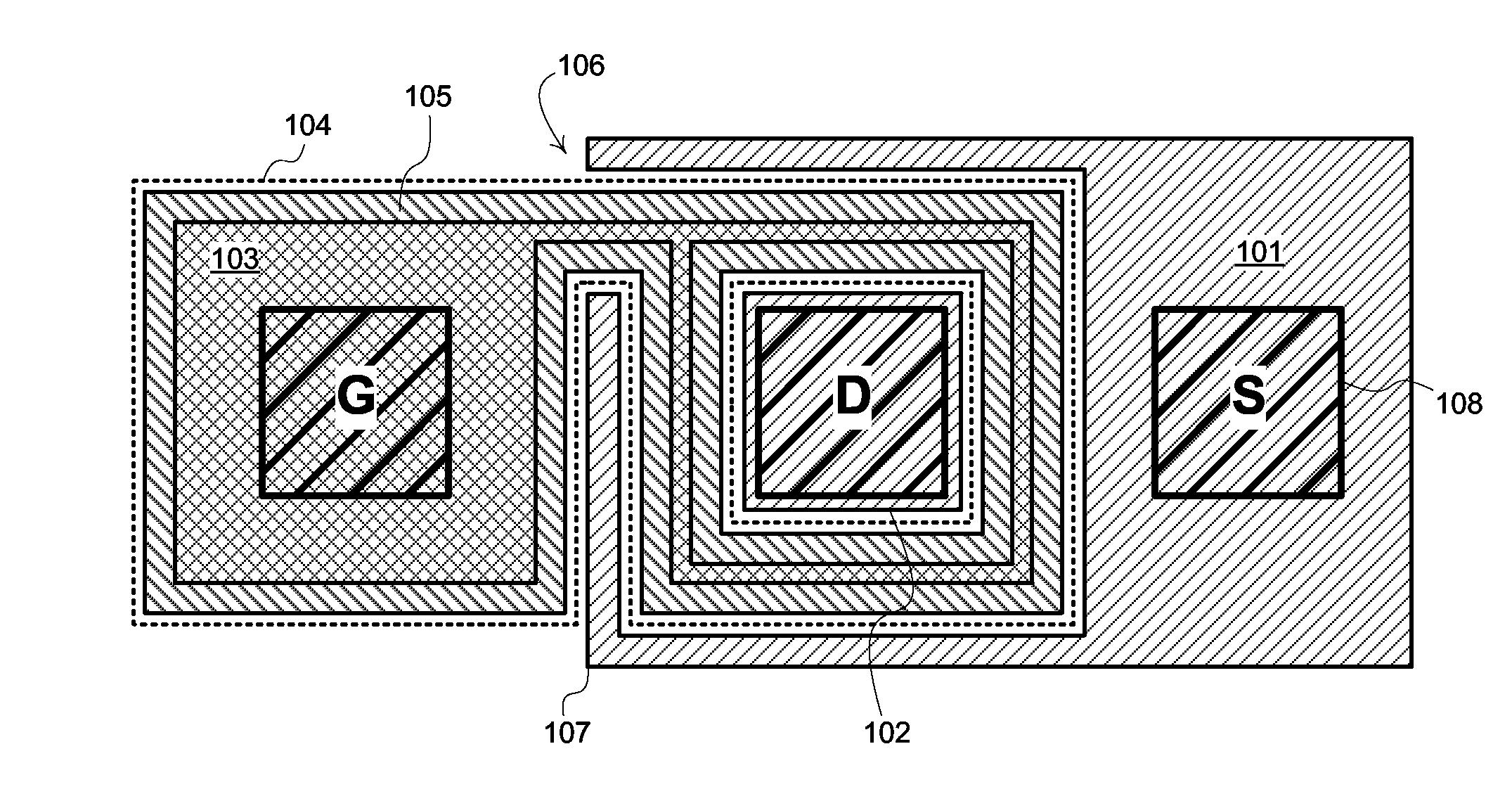

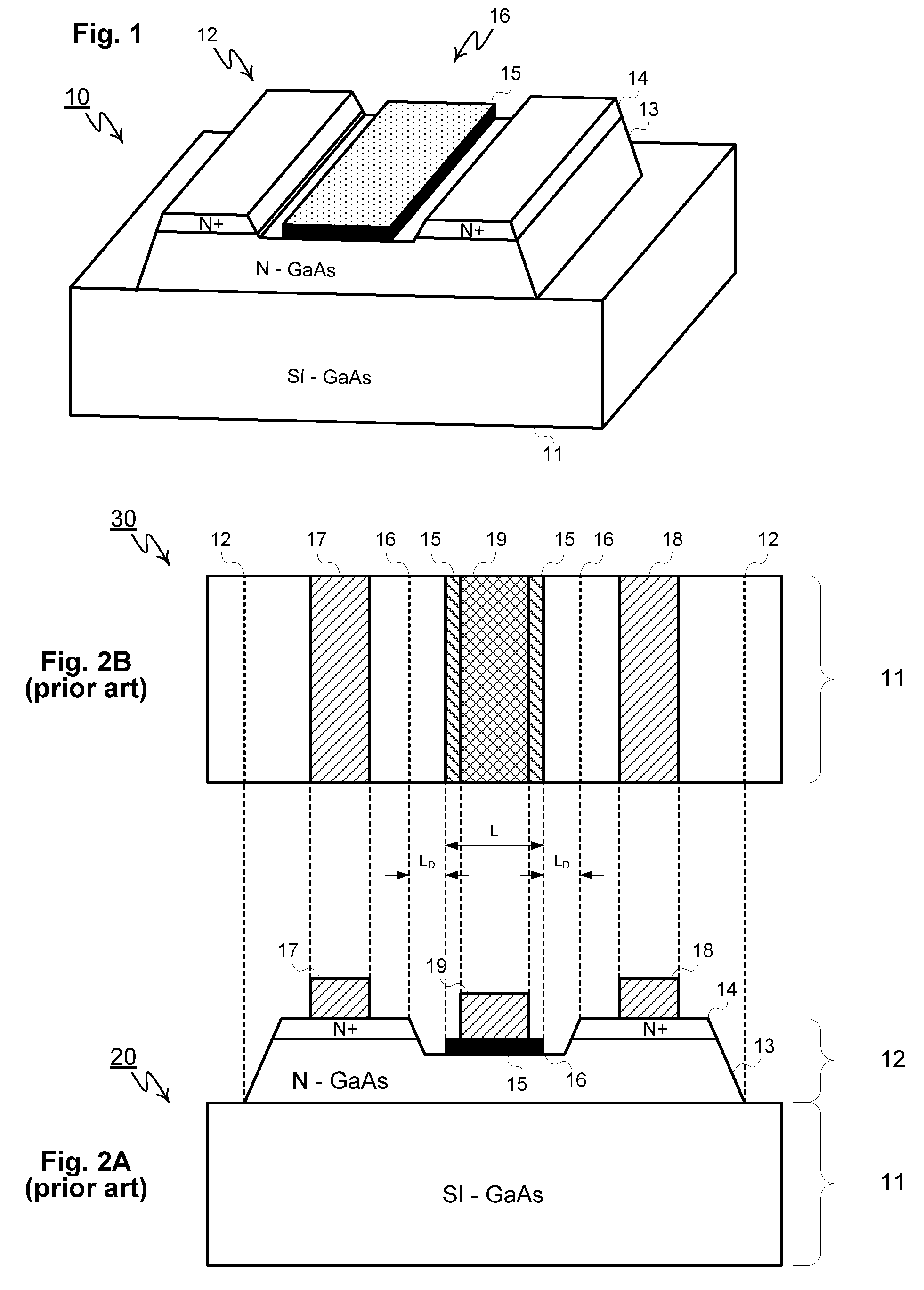

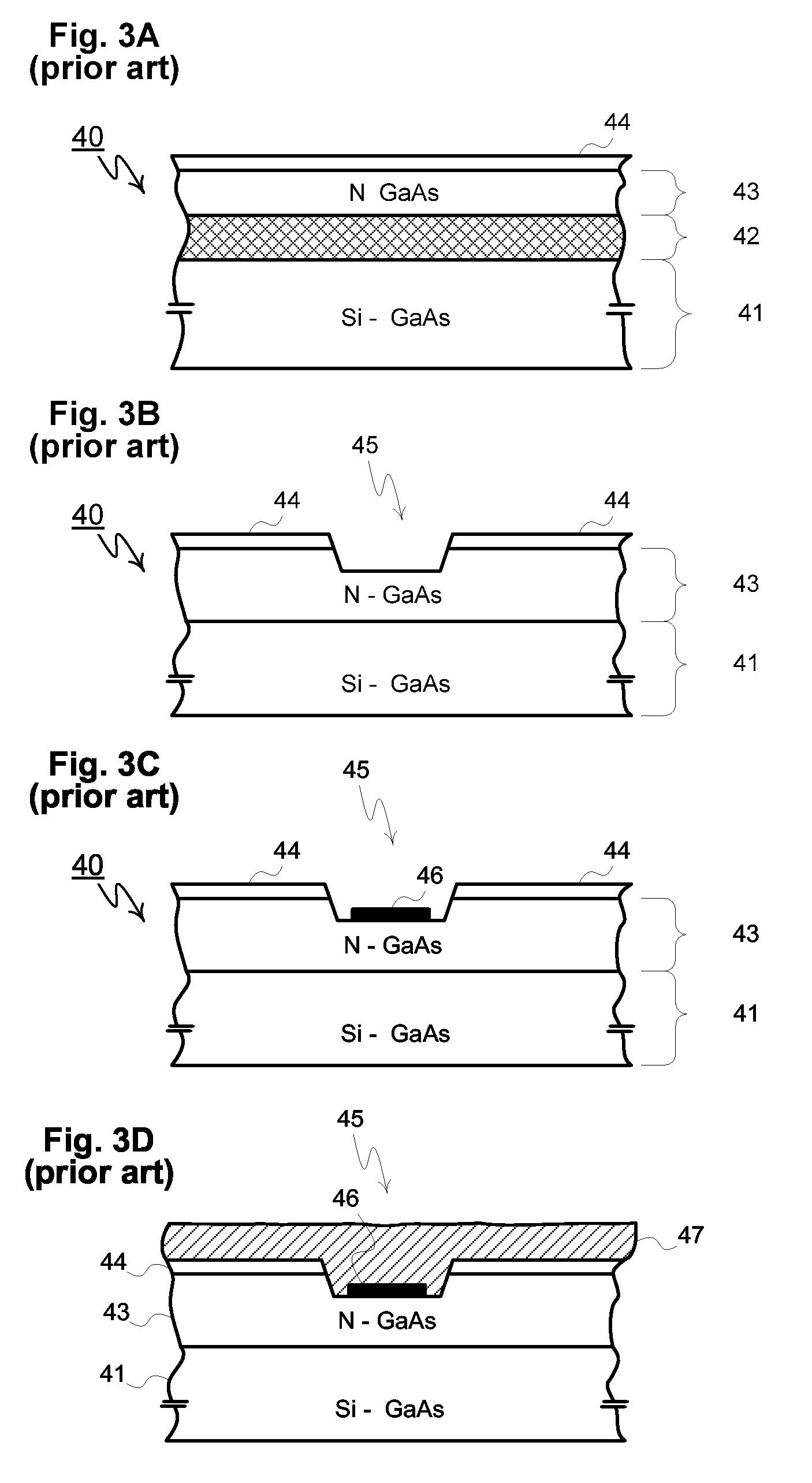

Rugged MESFET for Power Applications

InactiveUS20070120153A1Improved avalanche capabilityEnsure adequate isolationSolid-state devicesSemiconductor/solid-state device manufacturingPower applicationMESFET

A rugged MESFET for power applications includes a drain region surrounded by a ring shaped gate. The gate is surrounded, in turn by a source region. This eliminates the high-field point between gate and drain along the device's etched mesa surface and results in improved avalanche capability.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

Trench metal oxide semiconductor field effect transistor with embedded schottky rectifier using reduced masks process

ActiveUS20140077290A1Increase the doping concentrationGreat junction depthSolid-state devicesSemiconductor/solid-state device manufacturingTrench mosfetPhysical chemistry

A trench MOSFET with embedded schottky rectifier having at least one anti-punch through implant region using reduced masks process is disclosed for avalanche capability enhancement and cost reduction. The source regions have a higher doping concentration and a greater junction depth along sidewalls of the trenched source-body contacts than along adjacent channel regions near the gate trenches.

Owner:FORCE MOS TECH CO LTD

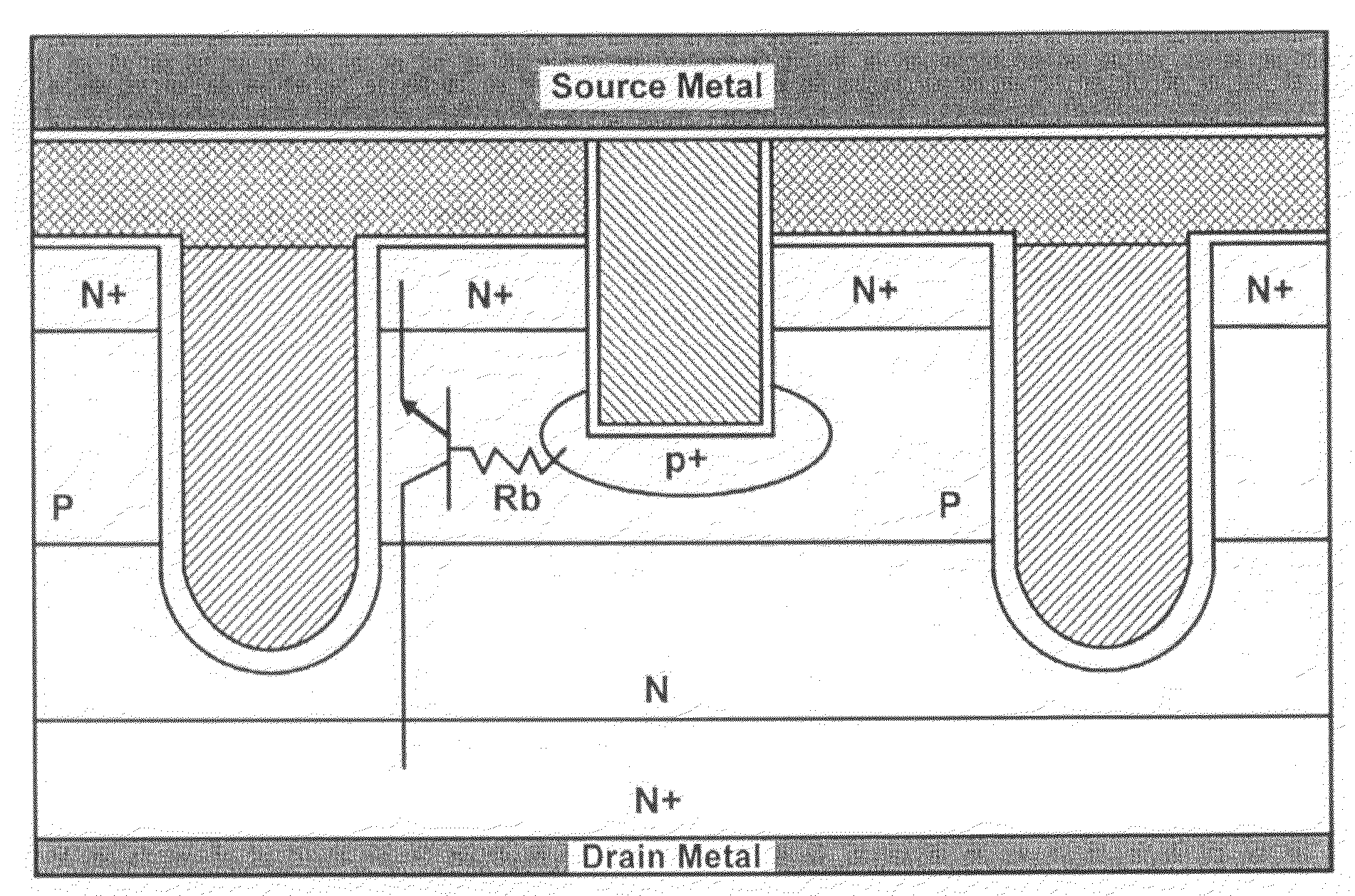

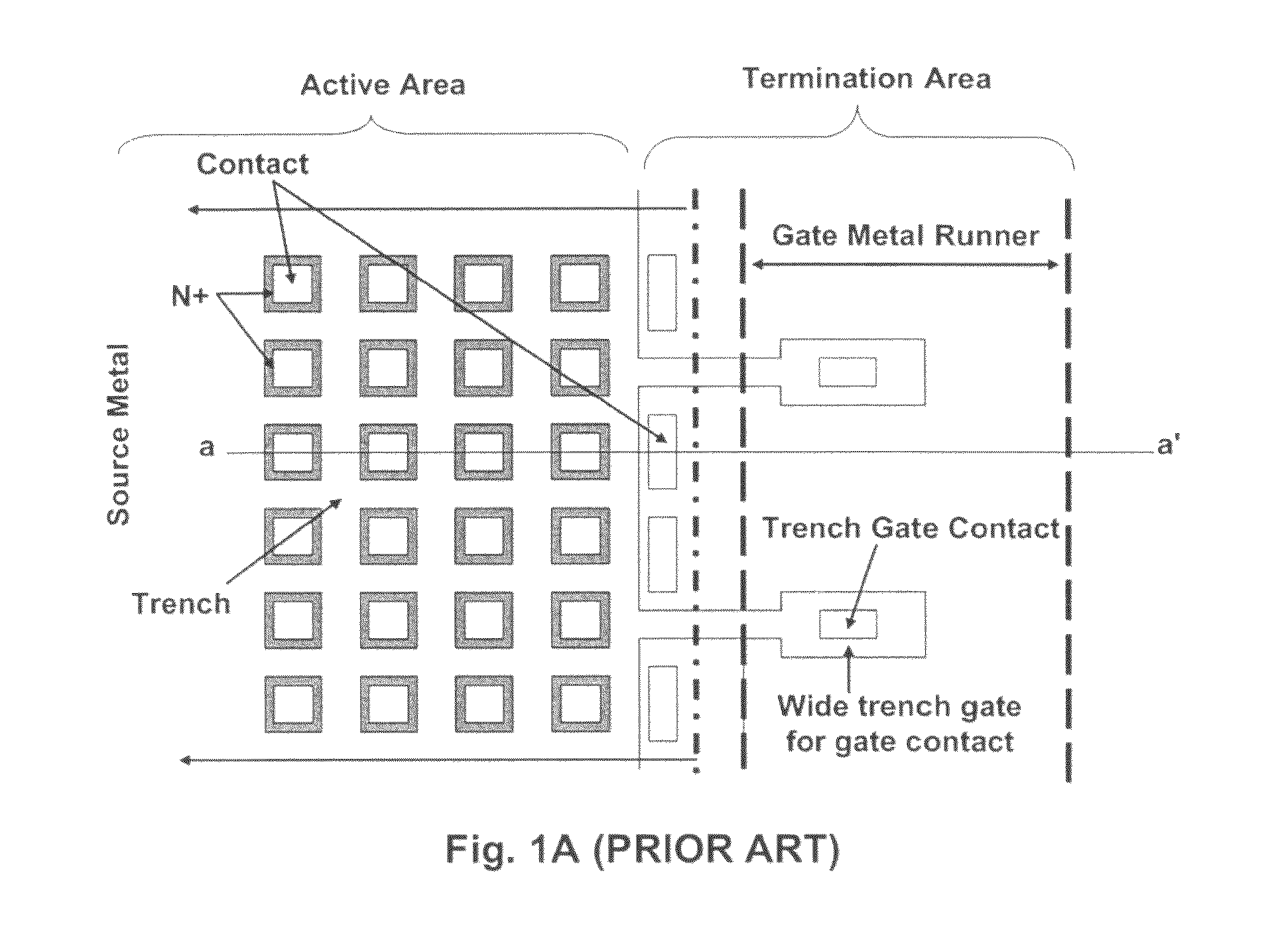

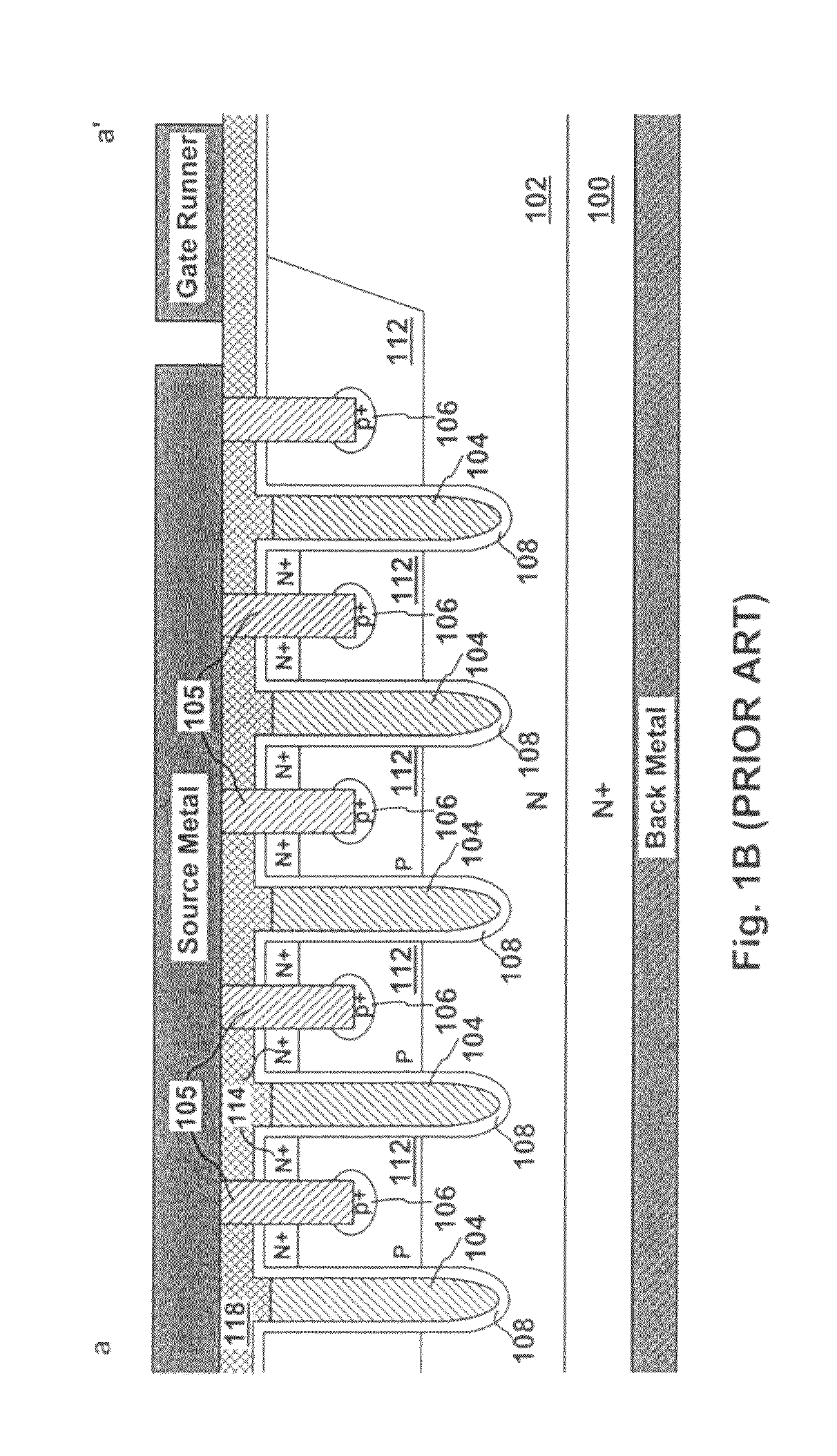

Avalanche capability improvement in power semiconductor devices having dummy cells around edge of active area

ActiveUS20100276728A1Increase valueNarrow distributionSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceSemiconductor

A structure of power semiconductor device having dummy cells around edge of active area is disclosed. The UIS test result of said improved structure shows that failed site after UIS test randomly located in active area which means avalanche capability of the semiconductor power device is enhanced by implementation of the dummy cells.

Owner:FORCE MOS TECH CO LTD

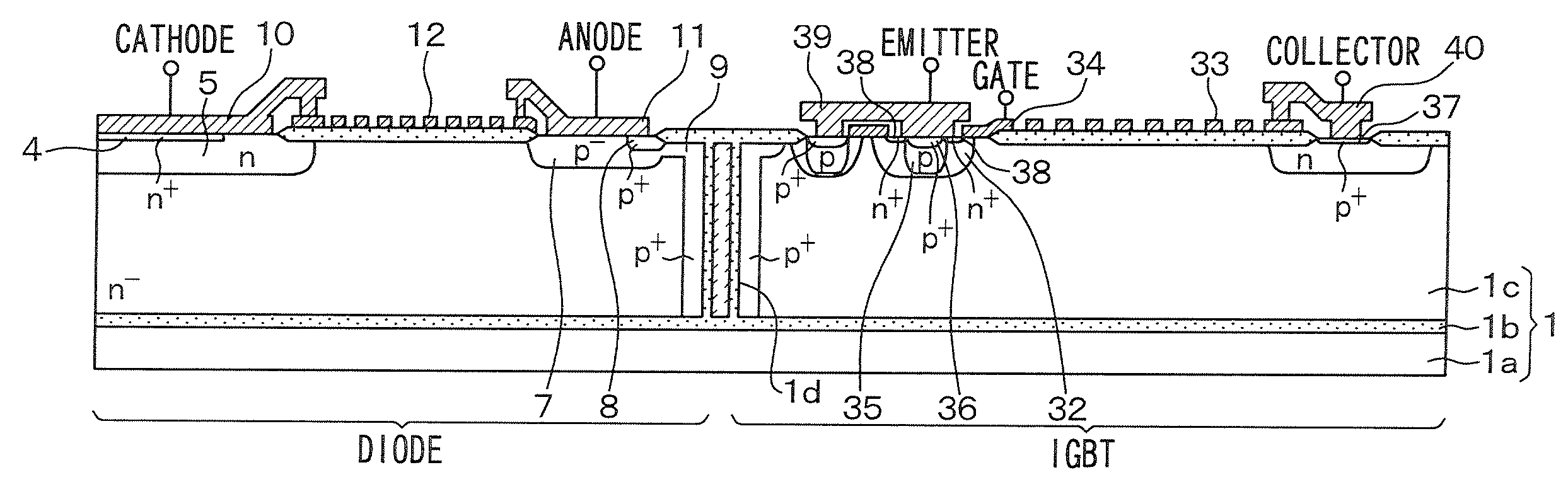

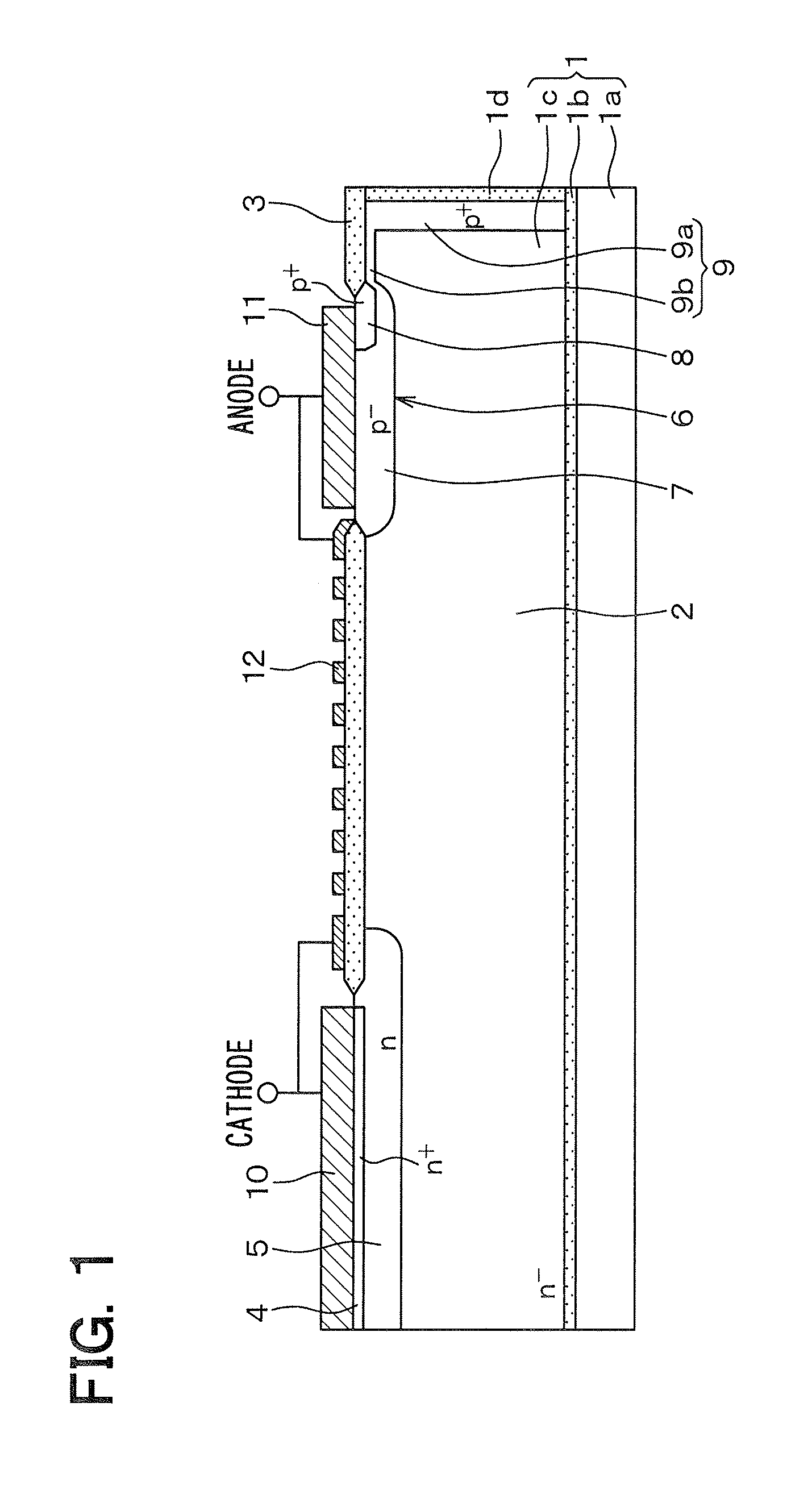

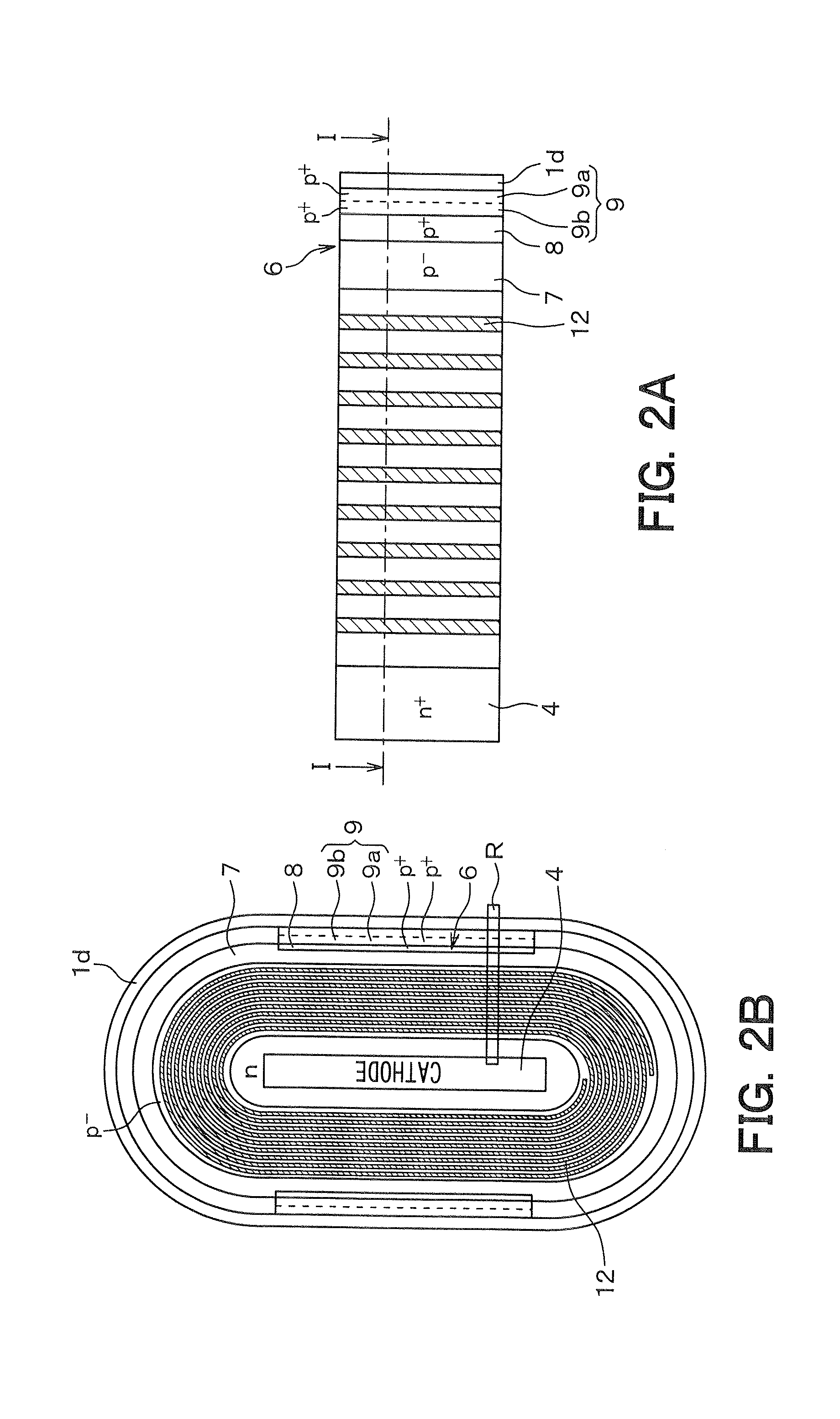

Semiconductor device having lateral diode

InactiveUS20120032313A1Improve rendering capabilitiesImproved avalanche capabilityTransistorDiodeDevice materialOhmic contact

A semiconductor device having a lateral diode includes a semiconductor layer, a first semiconductor region in the semiconductor layer, a contact region having an impurity concentration greater than that of the first semiconductor region, a second semiconductor region located in the semiconductor layer and separated from the contact region, a first electrode electrically connected through the contact region to the first semiconductor region, and a second electrode electrically connected to the second semiconductor region. The second semiconductor region includes a low impurity concentration portion, a high impurity concentration portion, and an extension portion. The second electrode forms an ohmic contact with the high impurity concentration portion. The extension portion has an impurity concentration greater than that of the low impurity concentration portion and extends in a thickness direction of the semiconductor layer.

Owner:DENSO CORP

Avalanche capability improvement in power semiconductor devices using three masks process

ActiveUS20140048872A1Improve avalanche capabilityImproved avalanche capabilityThyristorSemiconductor/solid-state device manufacturingPhysicsPower semiconductor device

A power semiconductor device with improved avalanche capability is disclosed by forming at least one avalanche capability enhancement doped region underneath an ohmic contact doped region. Moreover, a source mask is saved by using three masks process and the avalanche capability is further improved.

Owner:HSIEH FU YUAN +1

Trench mosfet with shielded electrode and avalanche enhancement region

InactiveUS20130256786A1Improved avalanche capabilityReduce concentrationTransistorThyristorTrench mosfetOptoelectronics

A trench MOSFET with shielded electrode and improved avalanche enhancement region is disclosed. The inventive structure can achieve a better avalanche capability by applying an improved avalanche enhancement region having a same doping concentration as the epitaxial layer where said trench MOSFET is formed without increasing Rds.

Owner:FEEL CHERNG ENTERPRISE

Trench MOSFET structures using three masks process

A trench MOSFET structure having improved avalanche capability is disclosed, wherein the source region is formed by performing source Ion Implantation through contact open region of a contact interlayer, and further diffused to optimize a trade-off between Rds and the avalanche capability. Thus, only three masks are needed in fabrication process, which are trench mask, contact mask and metal mask. Furthermore, said source region has a doping concentration along channel region lower than along contact trench region, and source junction depth along channel region shallower than along contact trench, and source doping profile along surface of epitaxial layer has Guassian-distribution from trenched source-body contact to channel region.

Owner:FORCE MOS TECH CO LTD

Method of making a trench MOSFET having improved avalanche capability using three masks process

ActiveUS20110008939A1Improve contact effectReduce manufacturing costTransistorSemiconductor/solid-state device manufacturingTrench mosfetBody contact

A method of forming trench MOSFET structure having improved avalanche capability is disclosed. In a preferred embodiment according to the present invention, only three masks are needed in the fabricating process, wherein the source region is formed by performing source Ion Implantation through contact open region of a thick contact interlayer for saving source mask. Furthermore, said source region has a doping concentration along channel region lower than along contact trench region, and source junction depth along channel region shallower than along contact trench, and source doping profile along surface of epitaxial layer has Guassian-distribution from trenched source-body contact to channel region.

Owner:FORCE MOS TECH CO LTD

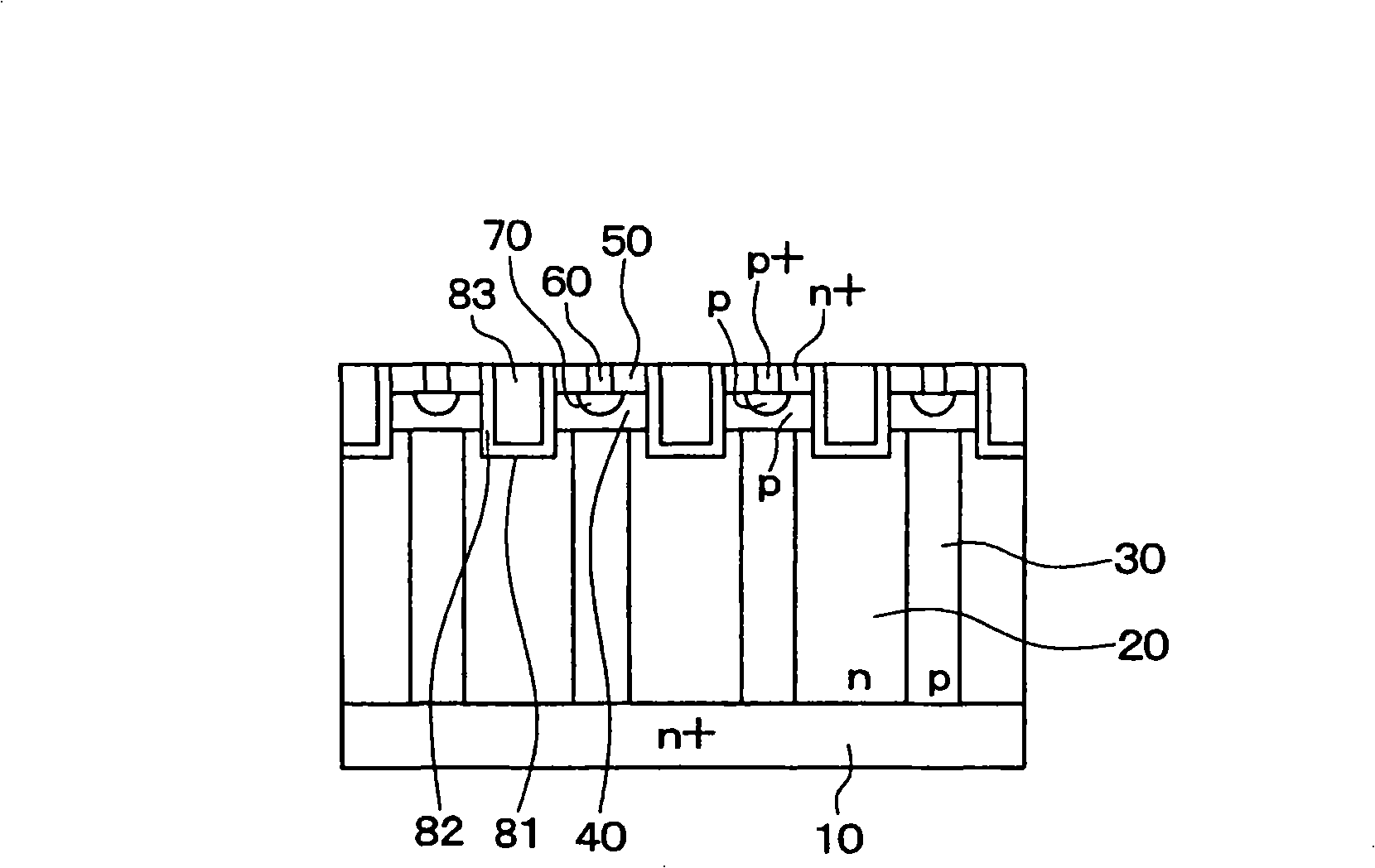

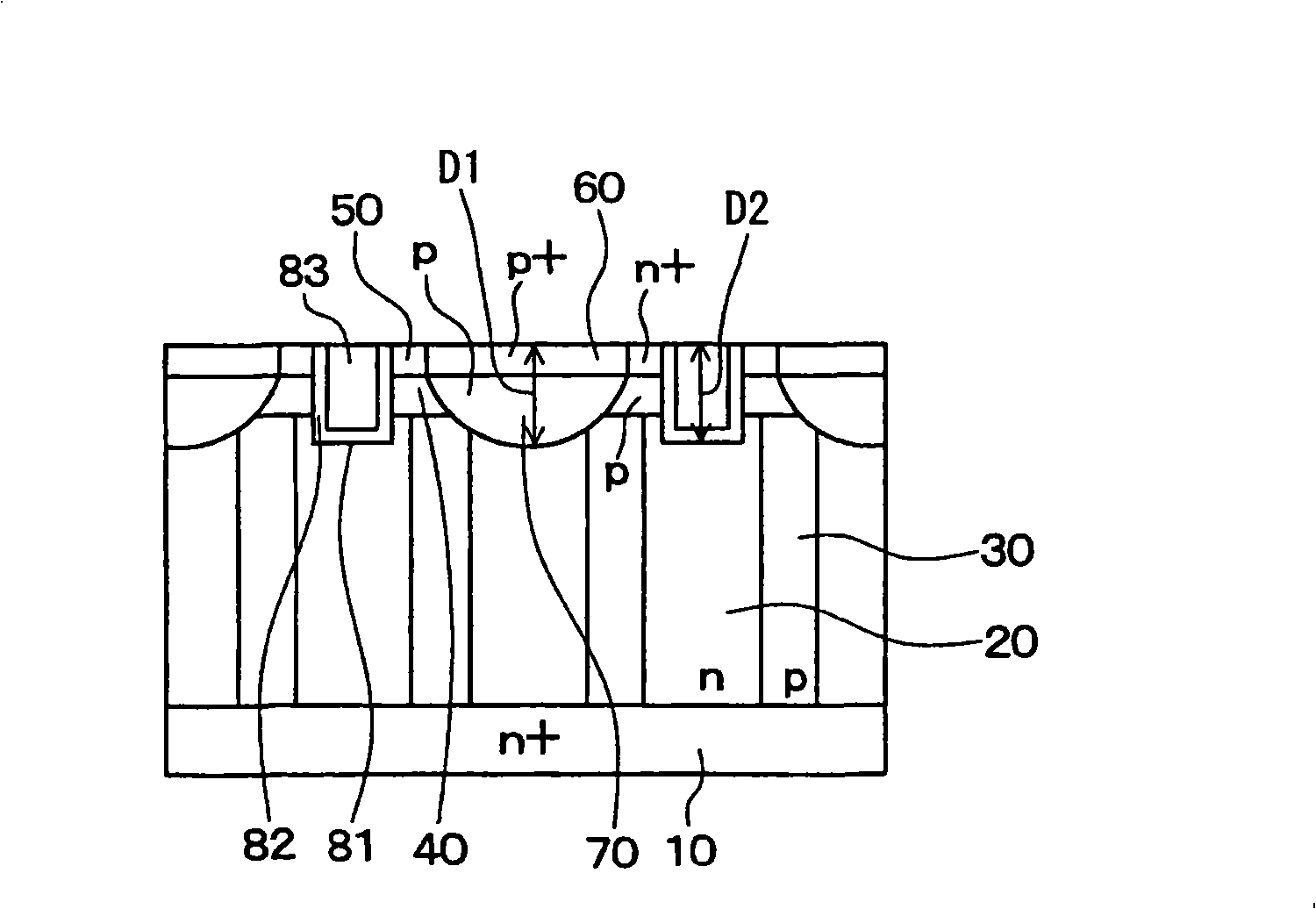

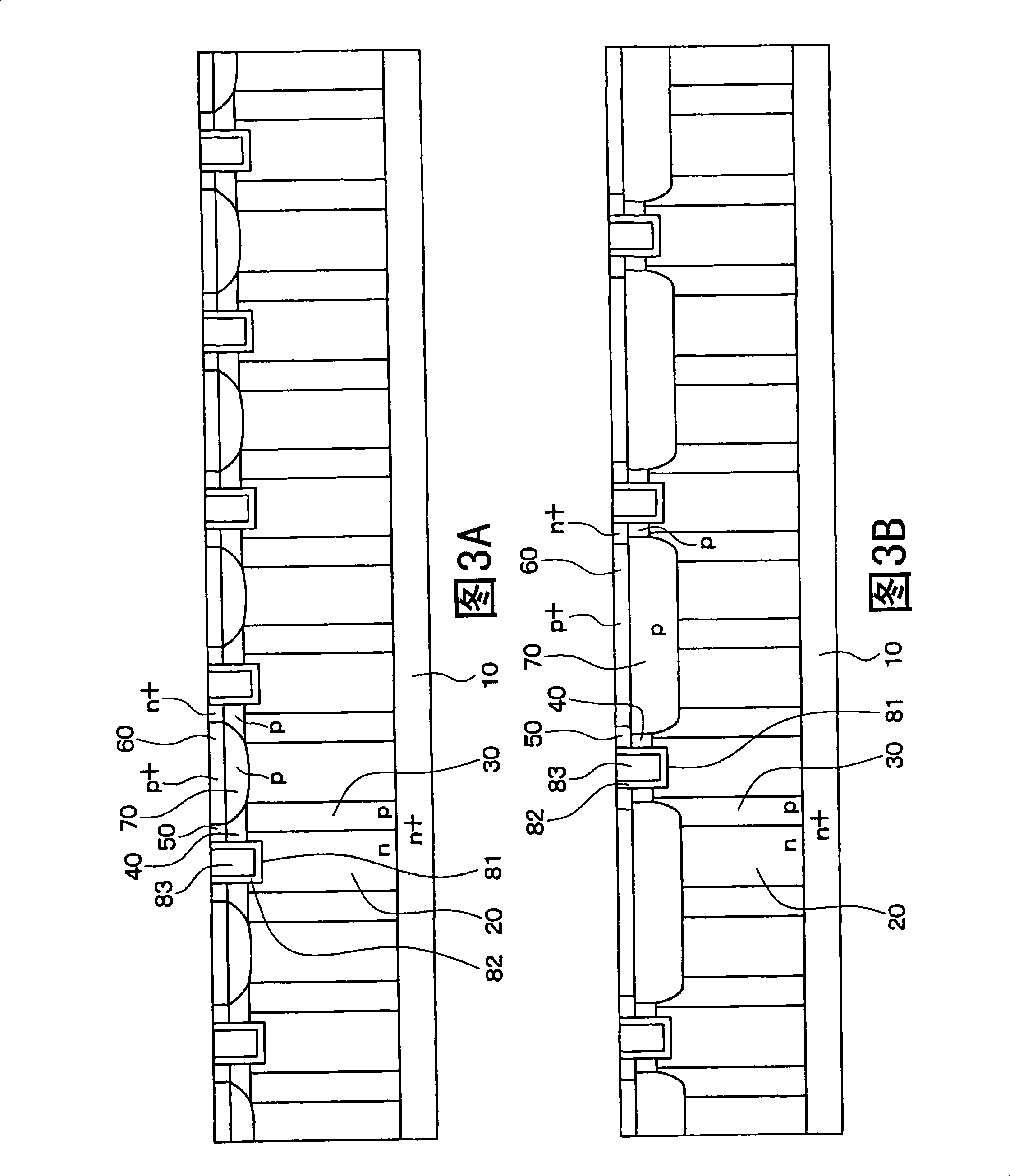

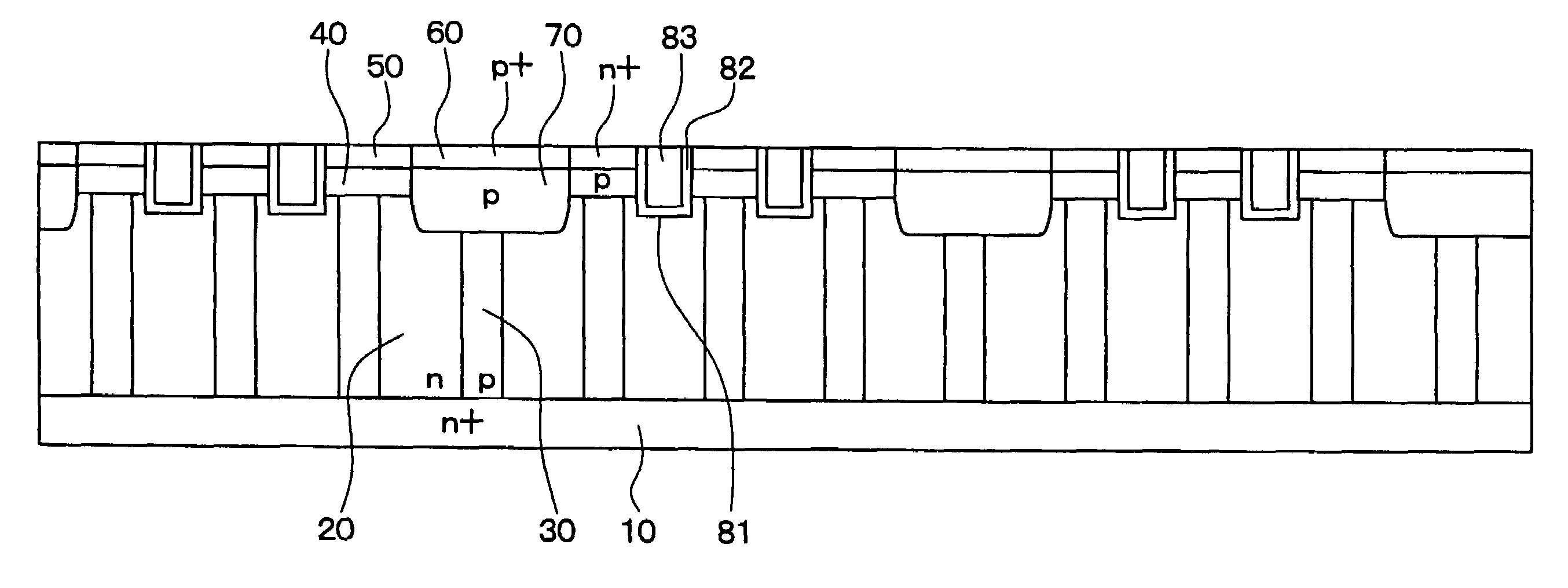

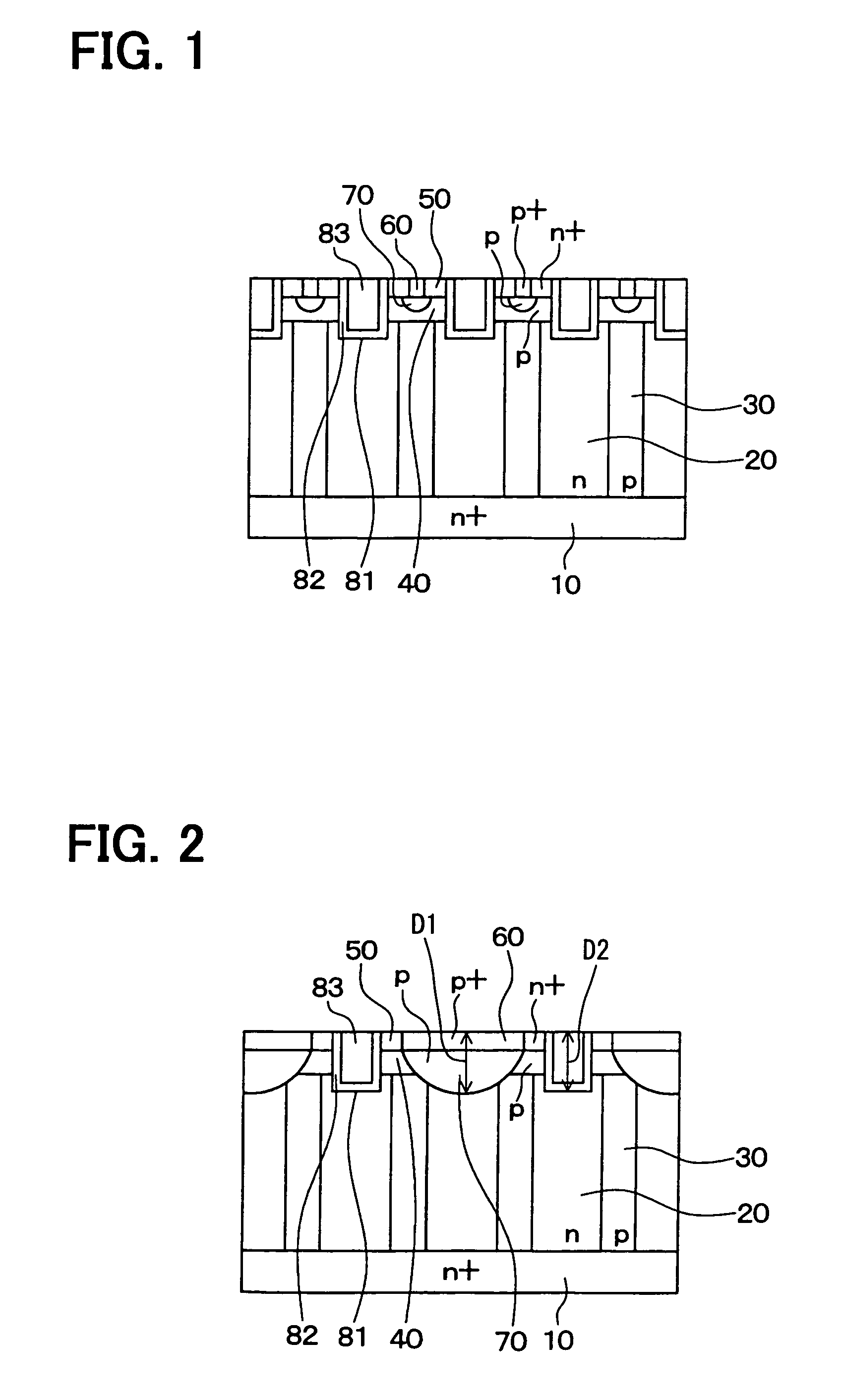

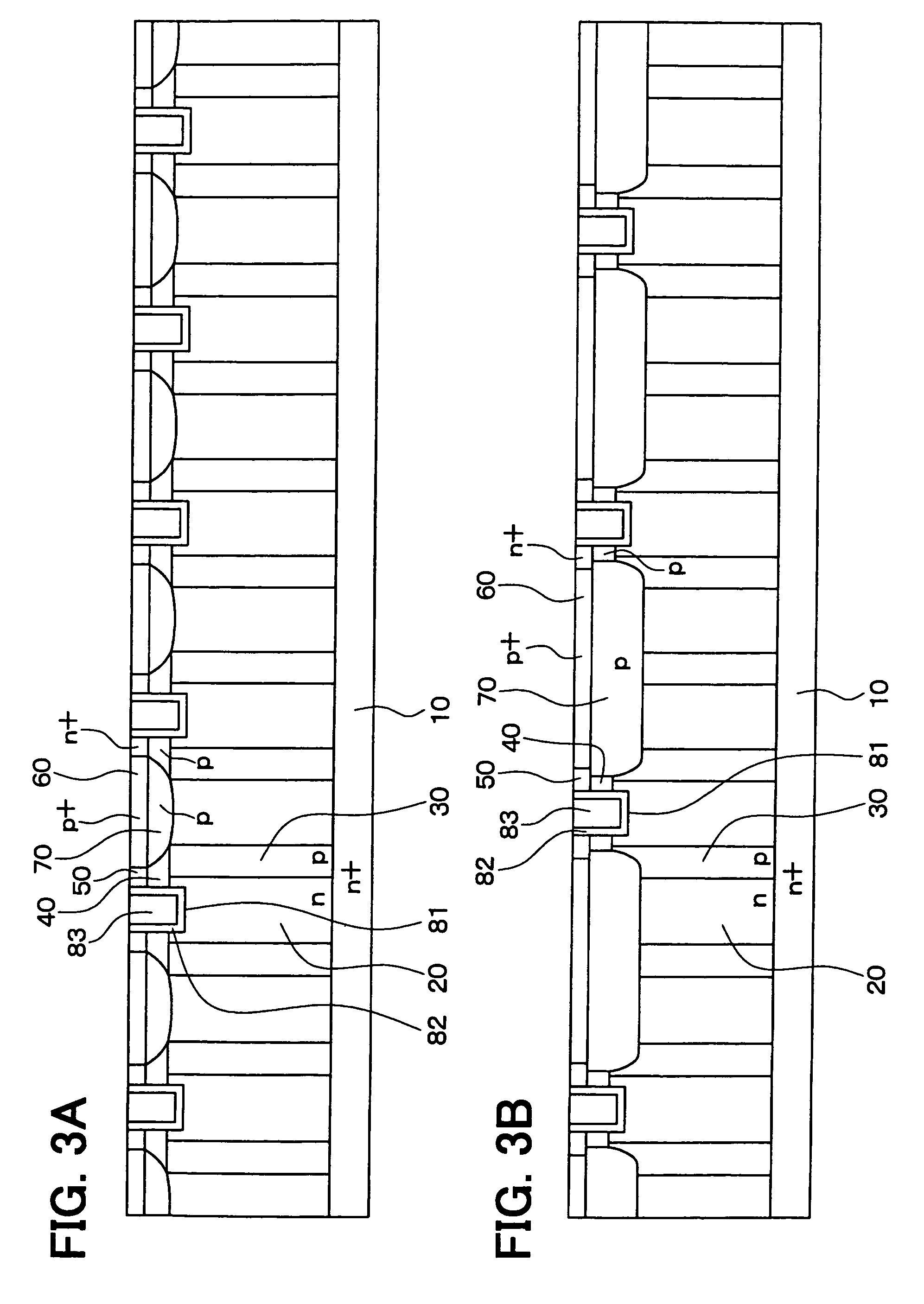

Semiconductor device

The invention relates to a semiconductor device which comprises a semiconductor substrate (10) and a super junction structure on the substrate. The super junction structure consists of p-type and n-type column regions which are alternately arranged. A p-type channel layer (40) is formed to a surface of the super junction structure. A trench gate structure is formed to the n-type column region. An n+-type source region (50) is formed to a surface of the channel layer near the trench structure. A p+-type region (60) is formed to the surface of the channel layer between adjacent n+-type source regions. A p-type body region (70) is formed in the channel layer between adjacent trench gate structures and in contact with the p+-type region. Avalanche current is caused to flow from the body region to a source electrode via the p+-type region without passing through the n+-type source region.

Owner:DENSO CORP

Trench metal oxide semiconductor field effect transistor with embedded schottky rectifier using reduced masks process

InactiveUS20140213026A1Increase concentrationAdd depthSolid-state devicesSemiconductor/solid-state device manufacturingTrench mosfetPhysical chemistry

A trench MOSFET with embedded schottky rectifier having at least one anti-punch through implant region using reduced masks process is disclosed for avalanche capability enhancement and cost reduction. The source regions have a higher doping concentration and a greater junction depth along sidewalls of the trenched source-body contacts than along adjacent channel regions near the gate trenches.

Owner:FORCE MOS TECH CO LTD

Trench metal oxide semiconductor field effect transistor with embedded schottky rectifier using reduced masks process

ActiveUS8723317B2Increase concentrationAdd depthSemiconductor/solid-state device detailsSolid-state devicesTrench mosfetBody contact

Owner:FORCE MOS TECH CO LTD

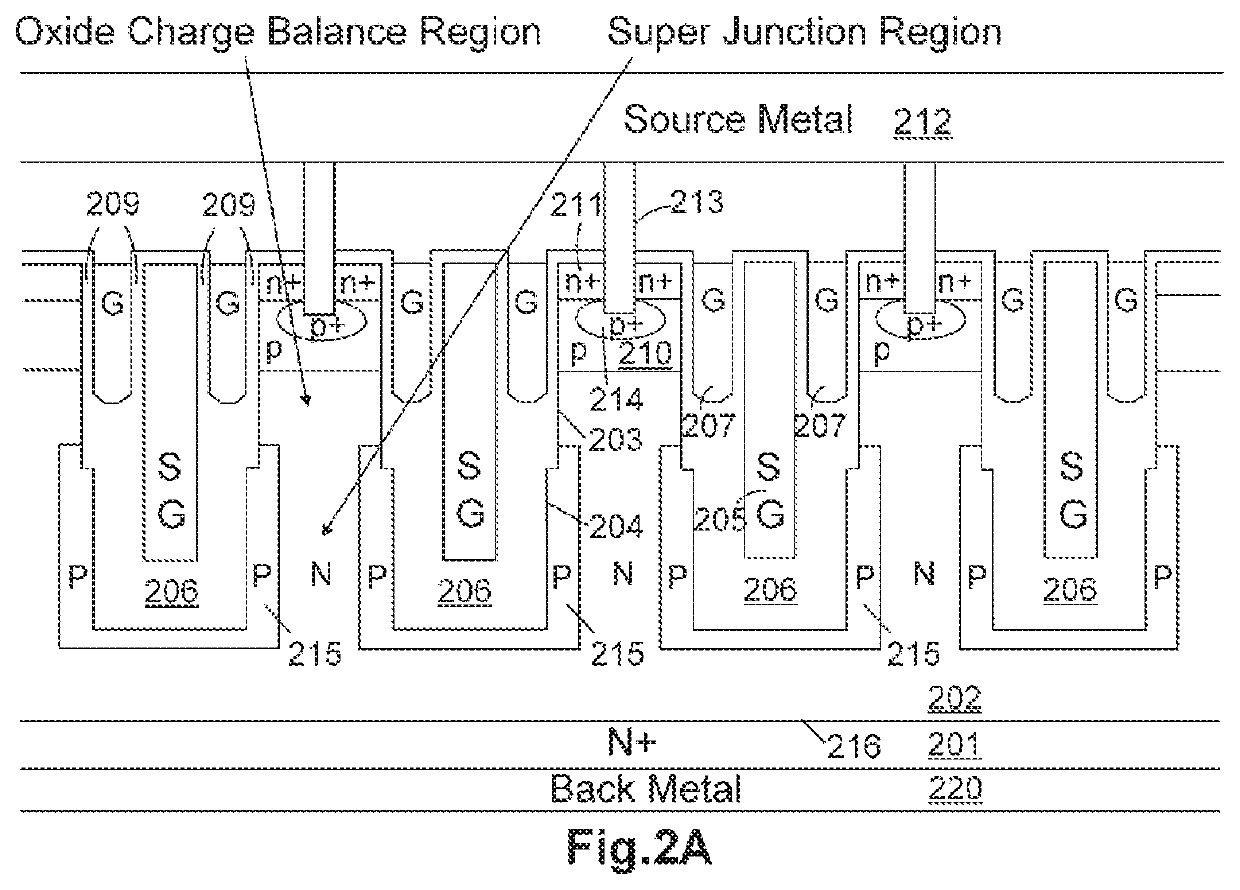

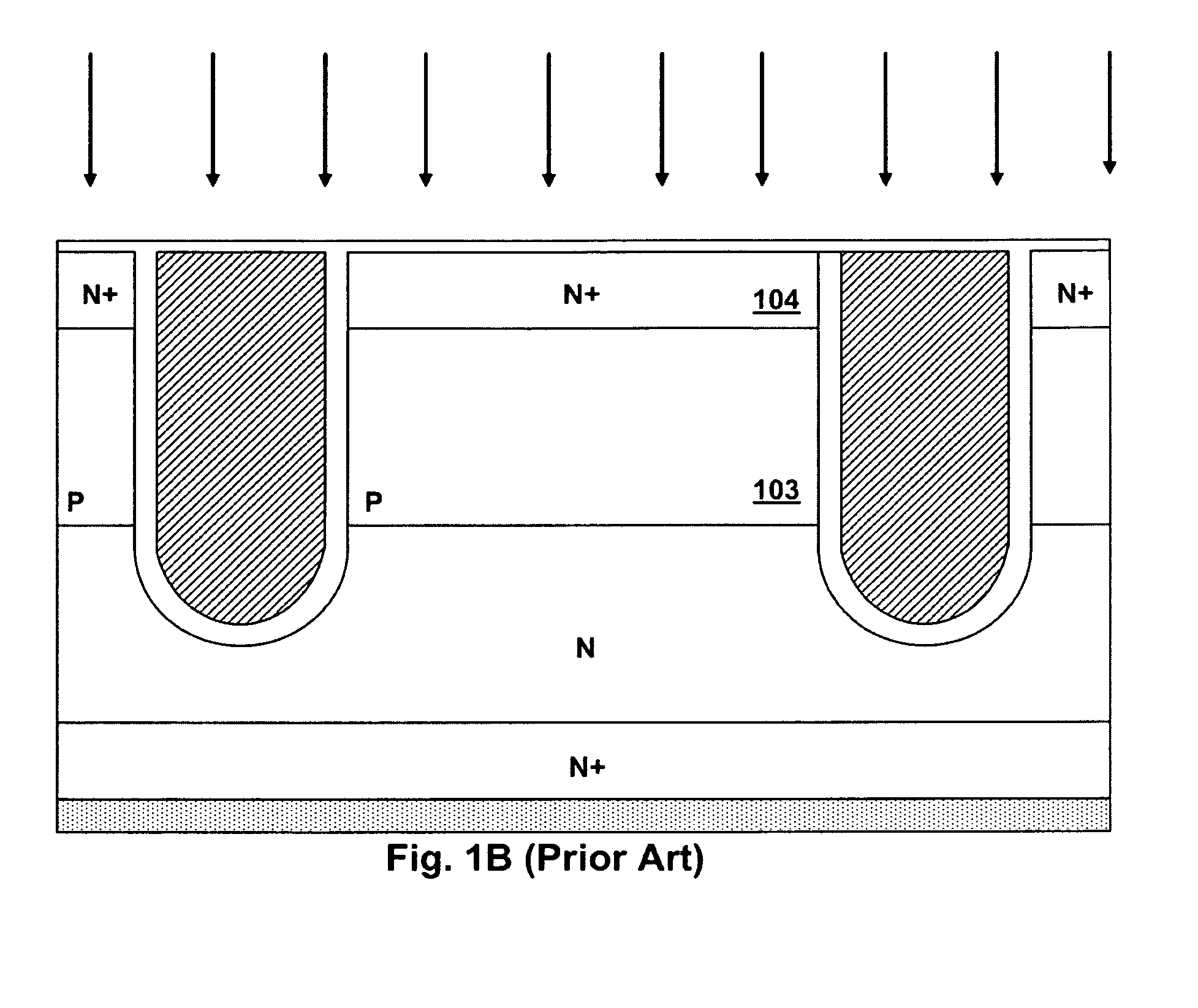

Shielded gate trench mosfet having super junction surrounding lower portion of trenched gates

InactiveUS20210384346A1Enhanced capabilityImproved avalanche capabilitySemiconductor devicesTrench mosfetMaterials science

An SGT MOSFET having super junction surrounding lower portion of trenched gates is disclosed. The super junction structure is surrounding lower portion of trenched gates to ensure whole drift region is fully depleted and breakdown occurs at middle of adjacent trenched gates without having early breakdown occurring at trench bottom. Moreover, sensitivity of breakdown voltage on trench bottom oxide thickness and trench depth is significantly relaxed or immune. Avalanche capability is also enhanced.

Owner:NAMI MOS CO LTD

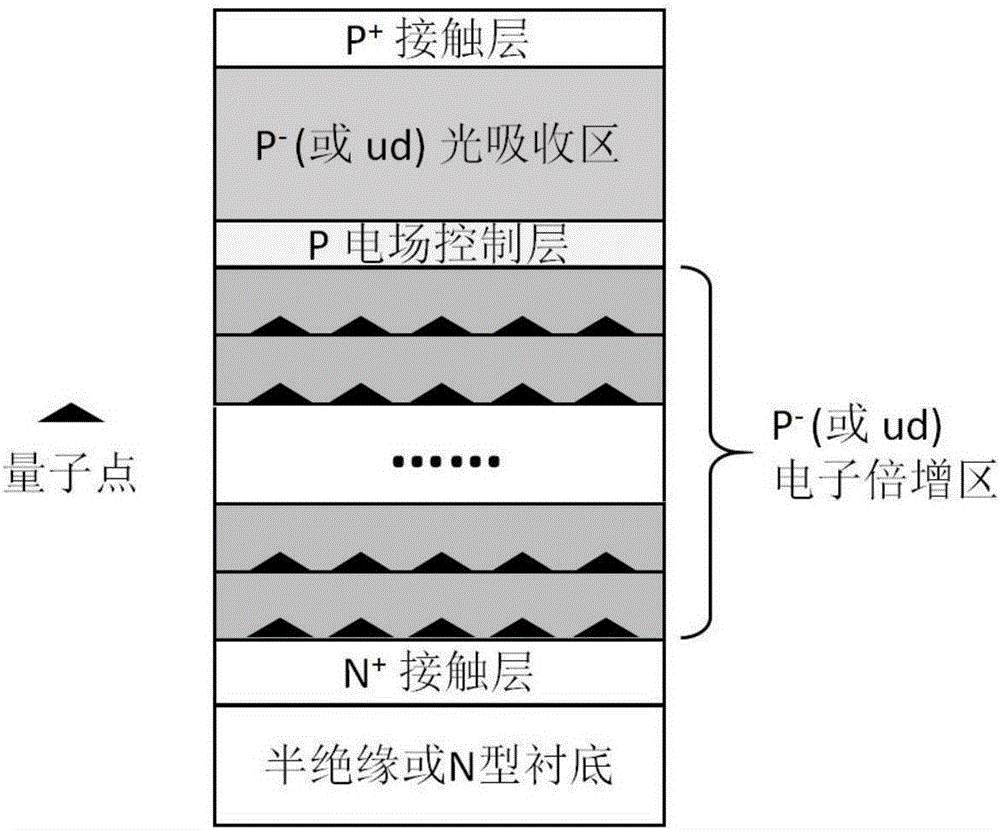

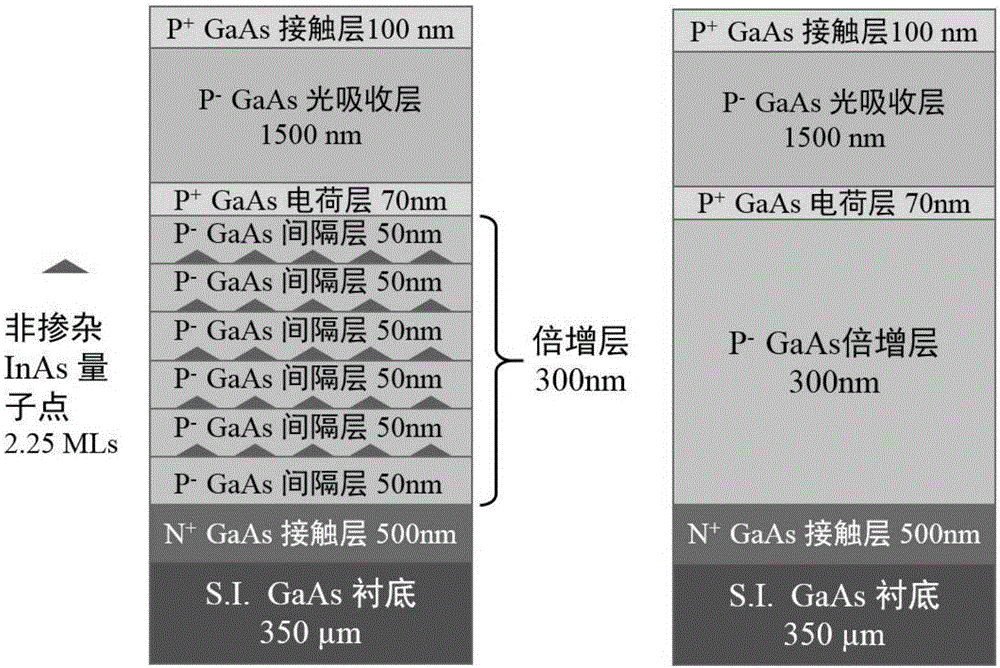

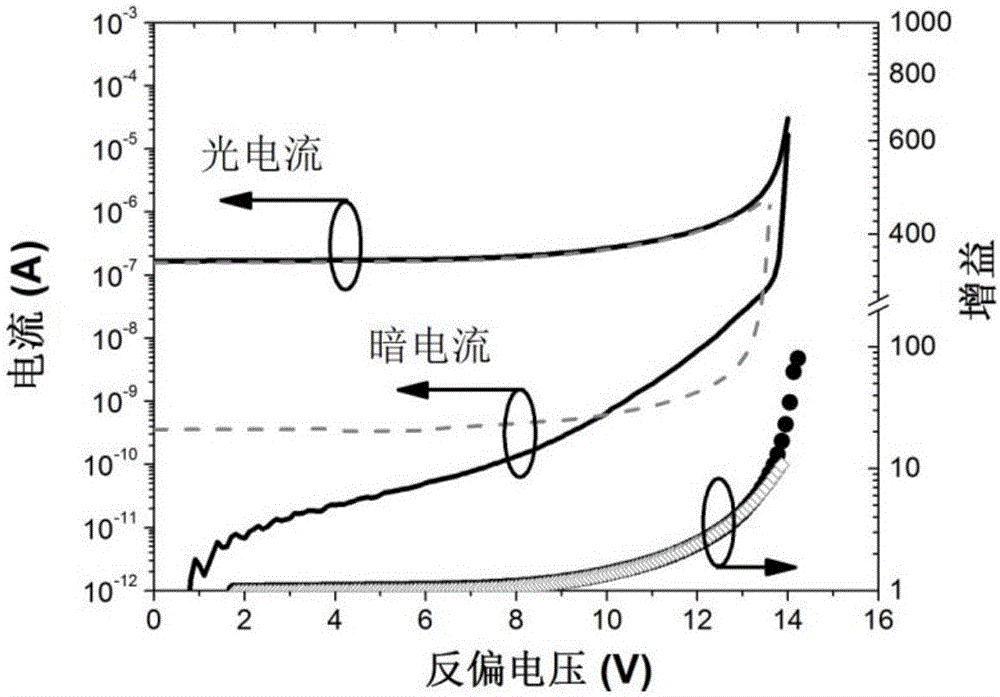

Semiconductor avalanche photoelectric detector using a low dimensional quantum dot multiplication layer

InactiveCN106299015AIncreased Avalanche Gain FactorReduce Excess Noise FactorSemiconductor devicesQuantum informationElectronic band structure

The invention relates to a semiconductor avalanche photoelectric detector using a low dimensional quantum dot multiplication layer. In the multiplication layer of the semiconductor avalanche photoelectric detector, there are several quantum dot layers which have a narrower band gap than the multiplication layer and form an I-type band structure with the multiplication layer materials. With the detector provided by the invention, the gain coefficient increases obviously; excess noise can be suppressed; and it can be widely used to enhance the performance of the avalanche detector in different bands such as Si-Ge, GaAs-InAs, InP-InGaAs, InAlAs-InGaAs, and GaAs-AlSb, and raise the application level of avalanche detector systems including high speed optical communication, single photon counting, laser radar, quantum information and etc.

Owner:弦海(上海)量子科技有限公司

Metal schemes of trench MOSFET for copper bonding

ActiveUS7786528B2Minimize Cu wire bonding damageAdditional costTransistorSemiconductor/solid-state device detailsTrench mosfetCopper wire

A trench MOSFET with improved metal schemes is disclosed. The improved contact structure applies a buffer layer to minimize the bonding damage to semiconductor when bonding copper wire upon front source and gate metal without additional cost.

Owner:FORCE MOS TECH CO LTD

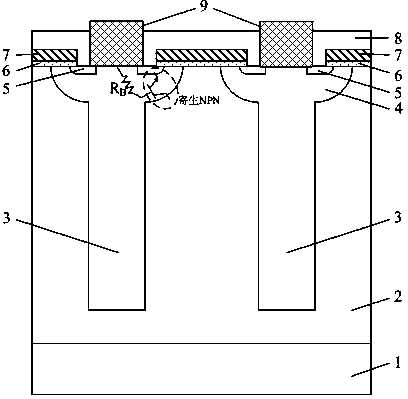

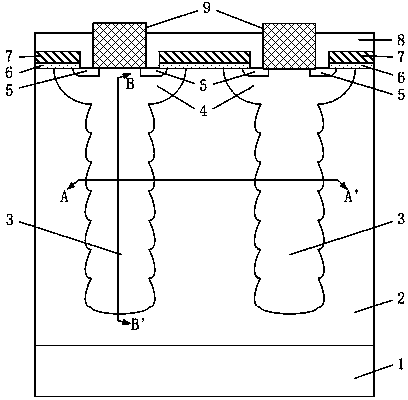

Super junction semiconductor device manufacturing method capable of improving avalanche capacity

ActiveCN103560086AImproved avalanche capabilityReduce the equivalent resistance R

<sub>B</sub>

resistance valueSemiconductor/solid-state device manufacturingSemiconductor devicesElectron avalancheHigh dosage

The invention relates to a super junction semiconductor device manufacturing method capable of improving the avalanche capacity. On-resistance is increased correspondingly due to transverse diffusion caused by the traditional high dosage concentration of a column P, and puncture voltage is reduced due to electric charge unbalance of the column P and a column N. According to the method, the epitaxy technology is utilized to form an N-type epitaxy layer; a P-type and N-type epitaxy layer is formed by injecting boron ions; the injection amount of the boron ions increases gradually, and the boron ions are pushed under the high temperature to form a P-type and N-type alternant epitaxy layer; a Pbody area is formed by injecting the boron ions; a polycrystalline silicon gate electrode is formed by etching polycrystalline silicon through the dry method; an N+ source area is formed by injecting arsenic ions; a layer of aluminum is deposited on the upper surface of a whole device, a source metal electrode is formed by etching the aluminum, and a drain electrode is formed on the back face through metallization. According to the super junction semiconductor device obtained through the method, the avalanche capacity of the super junction semiconductor device is improved, and at the same time, on-resistance is reduced.

Owner:XIAN LONTEN RENEWABLE ENERGY TECH +1

Avalanche capability improvement in power semiconductor devices having dummy cells around edge of active area

ActiveUS8072000B2Increase valueNarrow distributionThyristorSolid-state devicesPower semiconductor deviceEngineering

A structure of power semiconductor device having dummy cells around edge of active area is disclosed. The UIS test result of said improved structure shows that failed site after UIS test randomly located in active area which means avalanche capability of the semiconductor power device is enhanced by implementation of the dummy cells.

Owner:FORCE MOS TECH CO LTD

Method of making a trench MOSFET having improved avalanche capability using three masks process

ActiveUS8222108B2Reduce doping concentrationReduces Emitter injection efficiencyTransistorSemiconductor/solid-state device manufacturingTrench mosfetBody contact

Owner:FORCE MOS TECH CO LTD

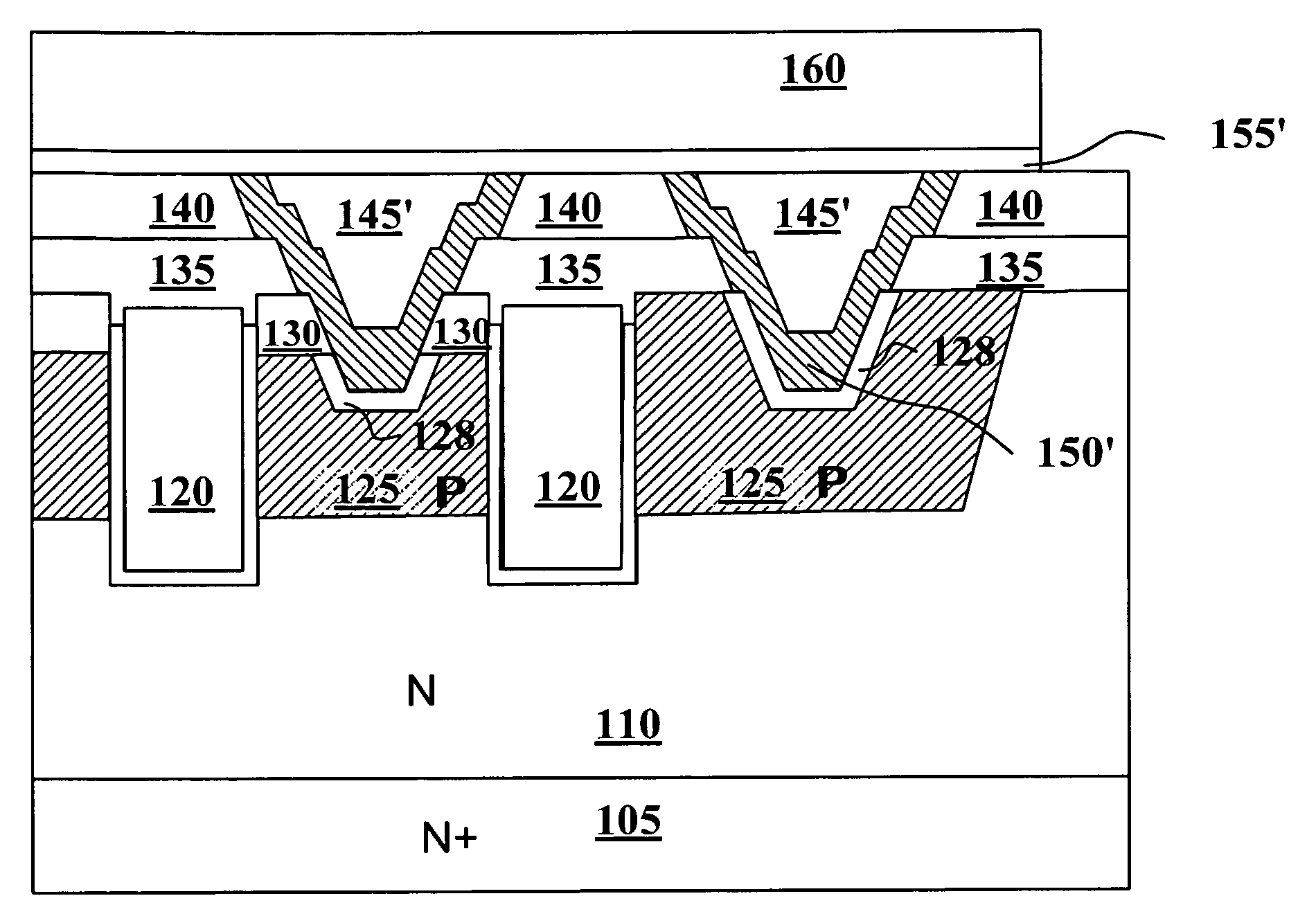

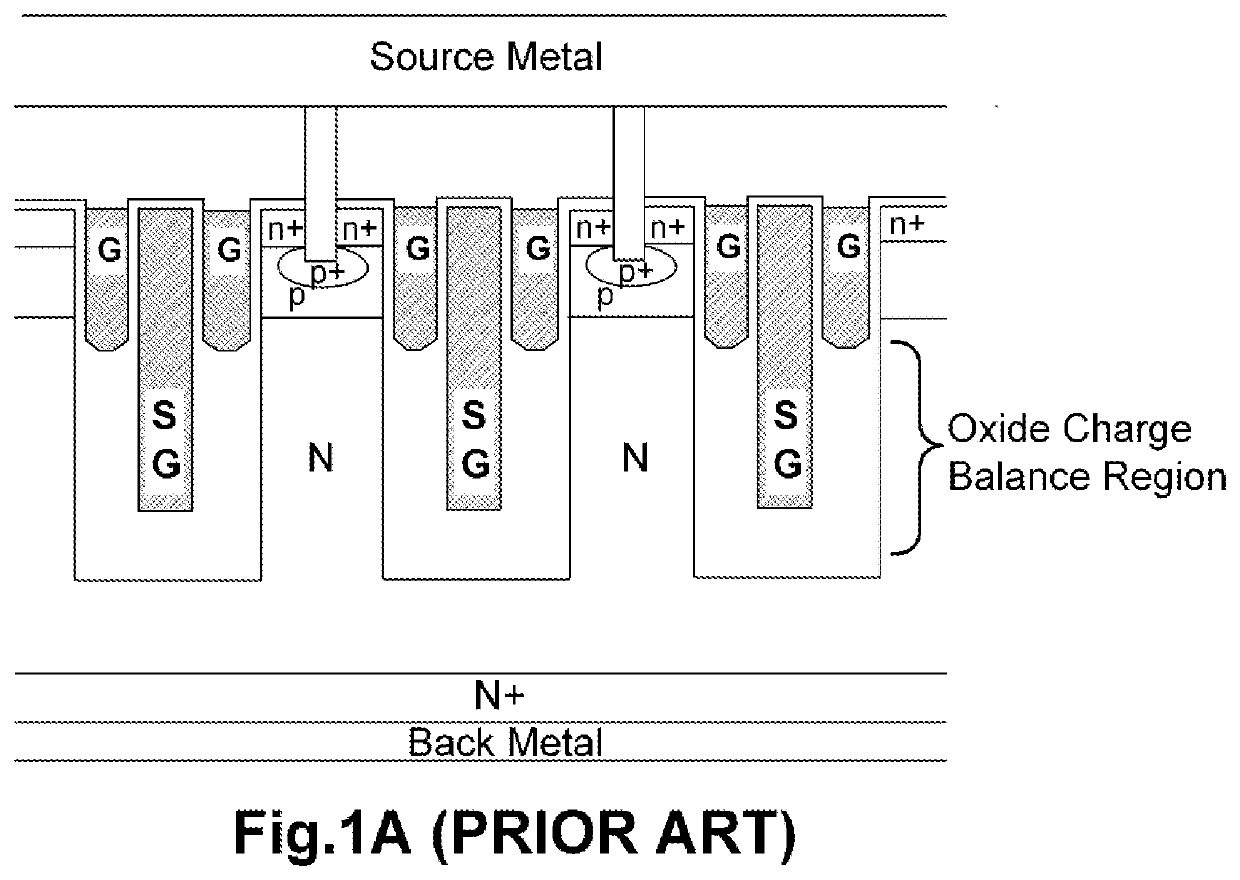

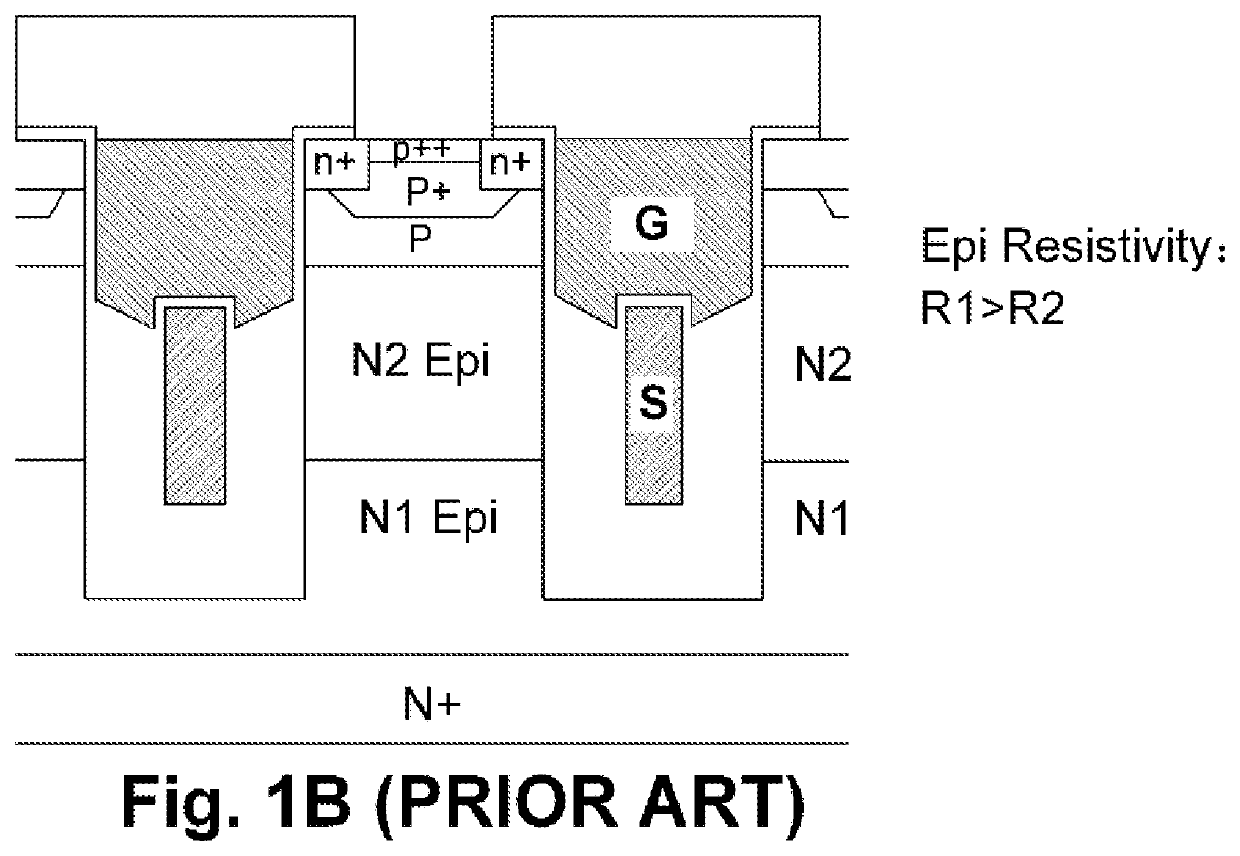

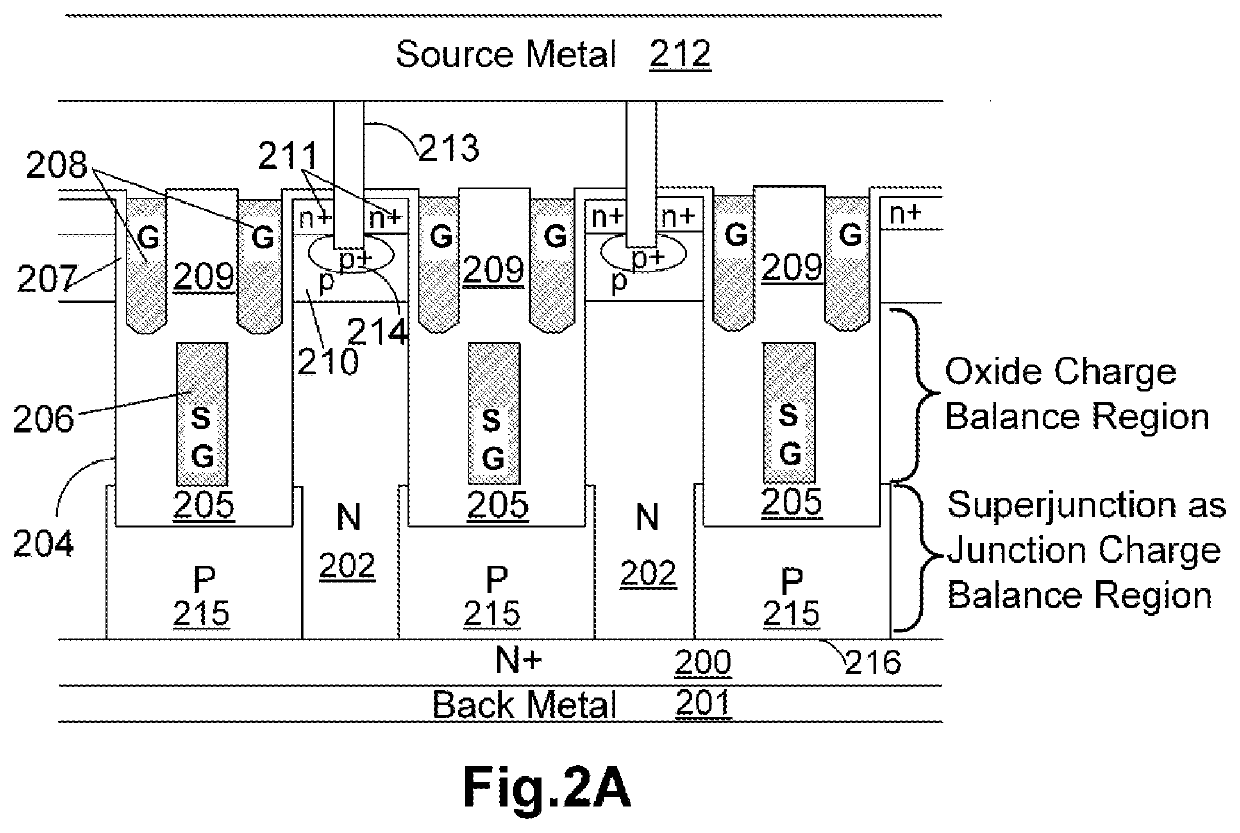

Super Shielded Gate Trench MOSFET Having Superjunction Structure

InactiveUS20210320202A1Improved avalanche capabilitySemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetTrench gate

A trenched semiconductor power device is disclosed comprising a plurality of trenched gates, each including a pair of split gate electrodes and a shielded gate electrode forming an oxide charge balance region between adjacent trenched gates, and junction charge balance region below trench bottom. The trenched semiconductor power device further comprises a super junction structure including a plurality of alternating P and N regions disposed above a substrate forming a junction charge balance region below the oxide charge balance region for breakdown voltage enhancement and on-resistance reductions.

Owner:NAMI MOS CO LTD

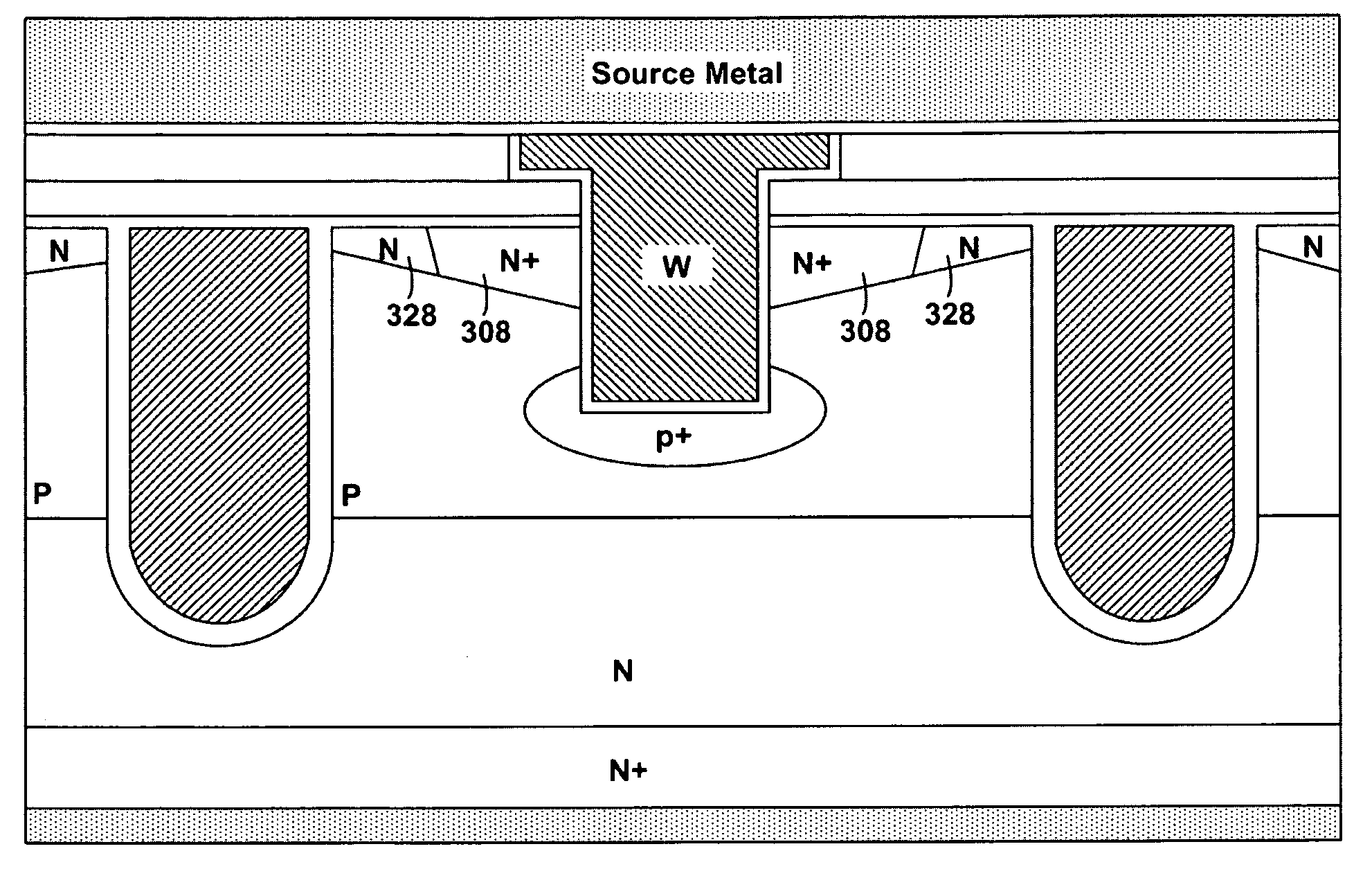

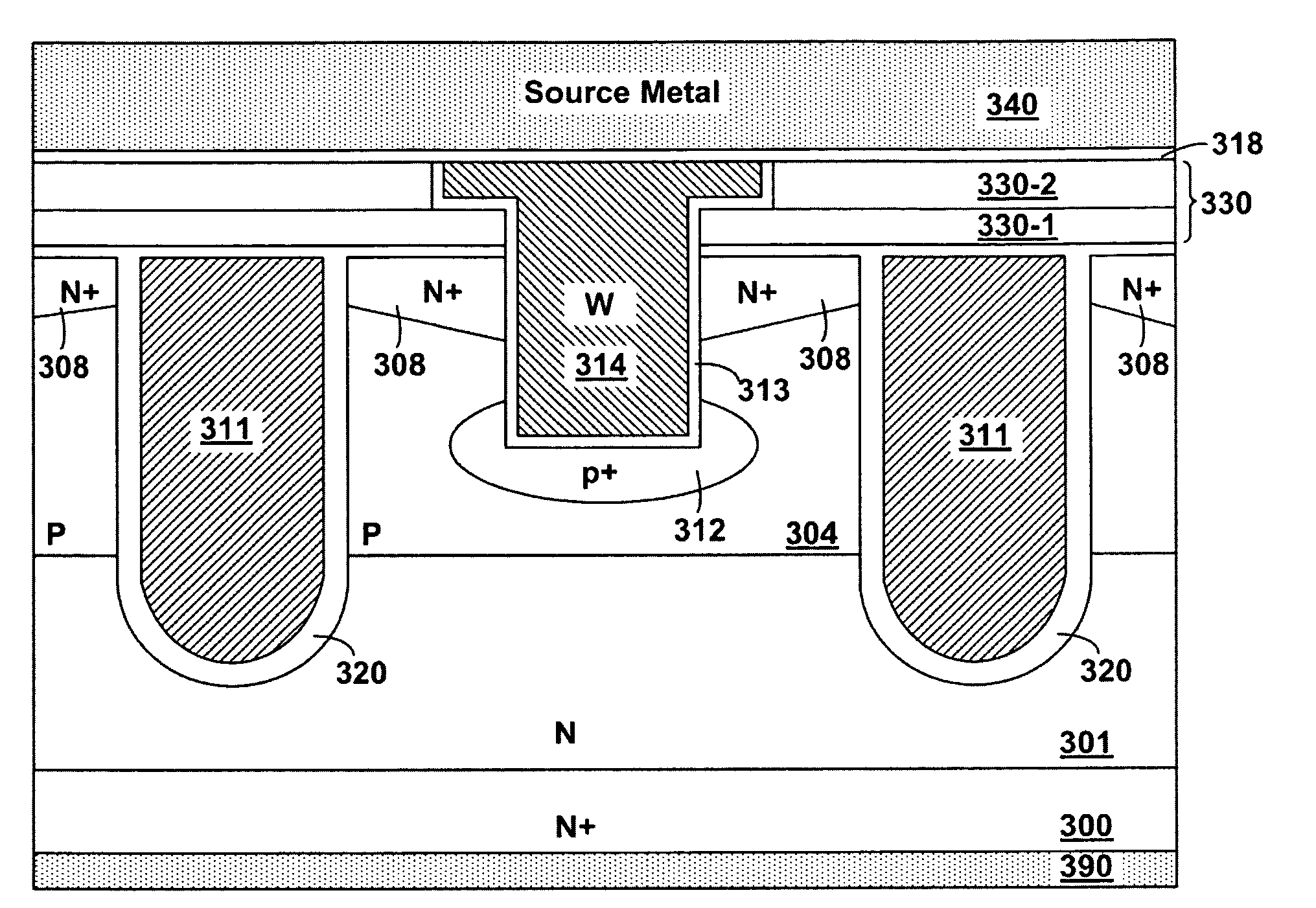

Trench mosfet structures using three masks process

InactiveUS20130299901A1Reduced footprintSmall sizeTransistorSemiconductor/solid-state device manufacturingTrench mosfetBody contact

A trench MOSFET comprising a plurality of trenched gates surrounded by source regions encompassed in body regions in active area. A plurality of trenched source-body contact structure penetrating through the source regions and extending into the body regions, are filled with tungsten plugs padded with a Ti layer, a first and a second TiN layer, wherein the second TiN layer is deposited after Ti silicide formation to avoid W spiking occurrence.

Owner:HSIEH FU YUAN +1

Semiconductor device

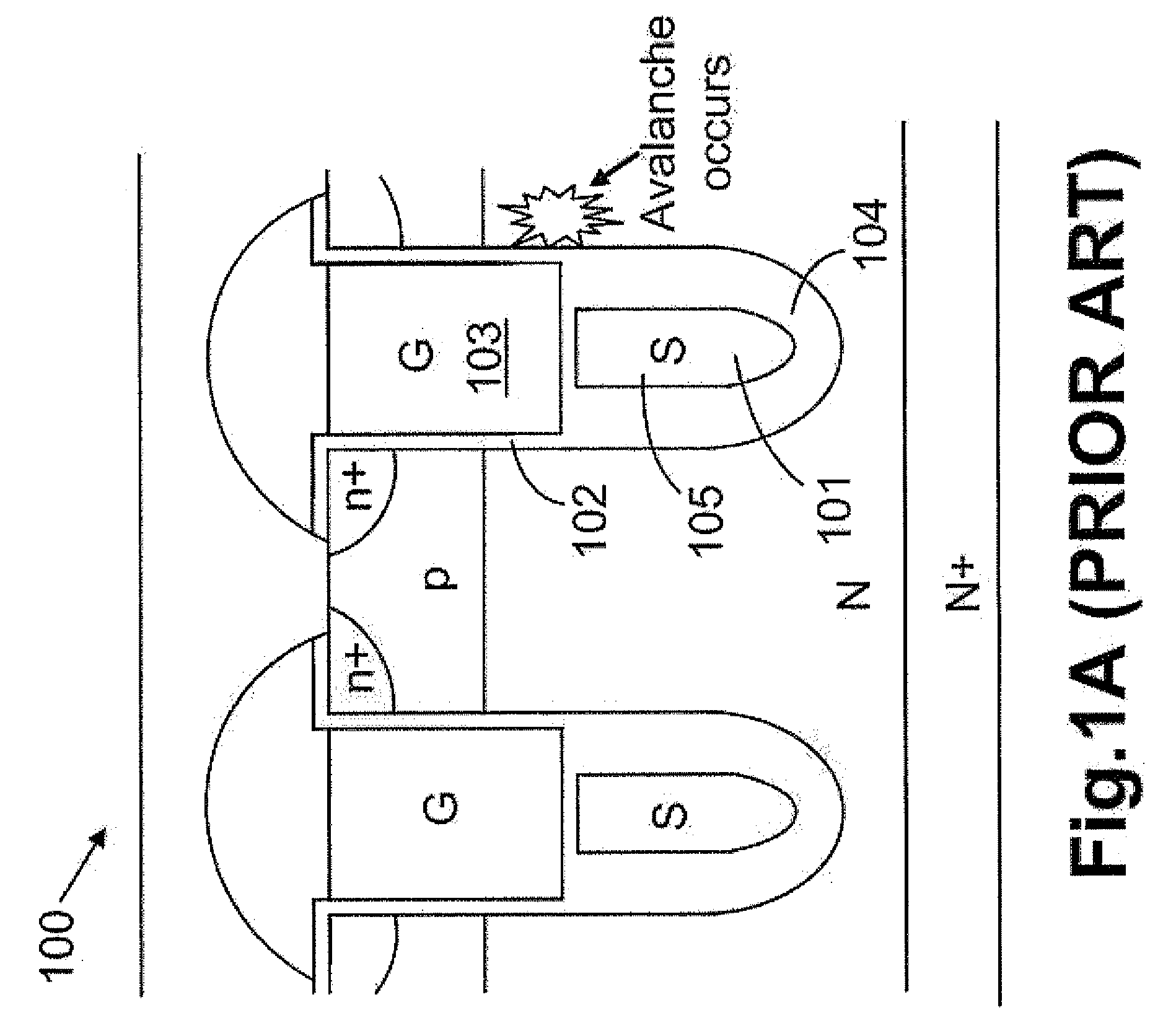

ActiveUS7692241B2Improved avalanche capabilityThyristorSemiconductor/solid-state device detailsBody regionTrench gate

A semiconductor device includes a semiconductor substrate and a super junction structure on the substrate. The super junction structure is constructed with p-type and n-type column regions that are alternately arranged. A p-type channel layer is formed to a surface of the super junction structure. A trench gate structure is formed to the n-type column region. An n+-type source region is formed to a surface of the channel layer near the trench structure. A p+-type region is formed to the surface of the channel layer between adjacent n+-type source regions. A p-type body region is formed in the channel layer between adjacent trench gate structures and in contact with the p+-type region. Avalanche current is caused to flow from the body region to a source electrode via the p+-type region without passing through the n+-type source region.

Owner:DENSO CORP

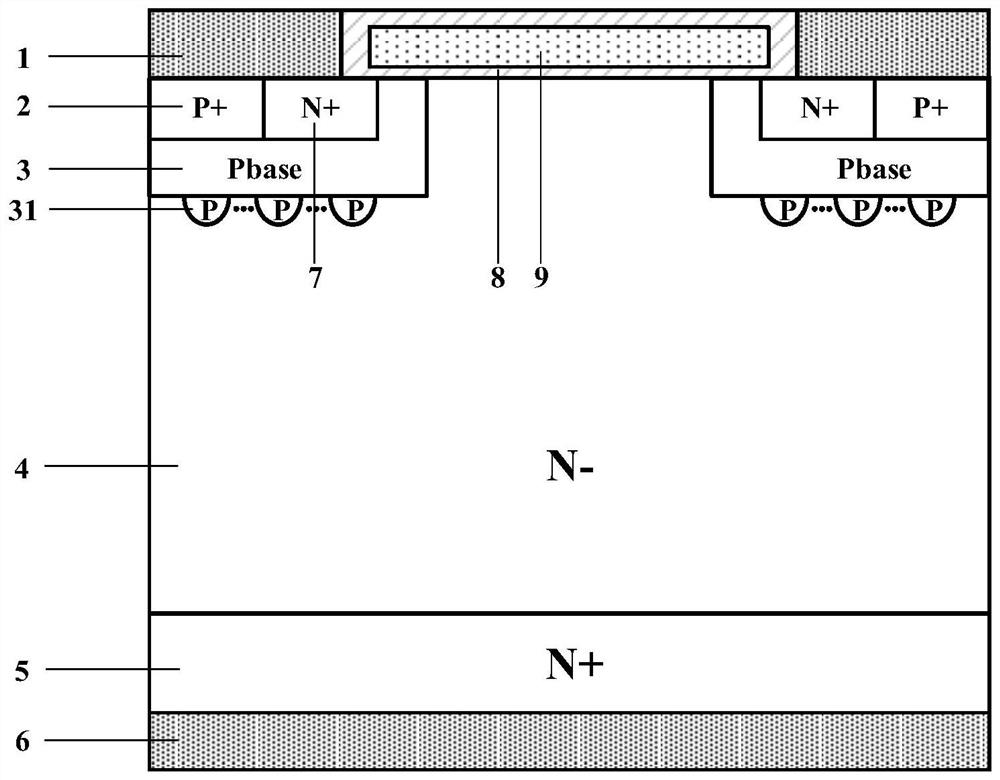

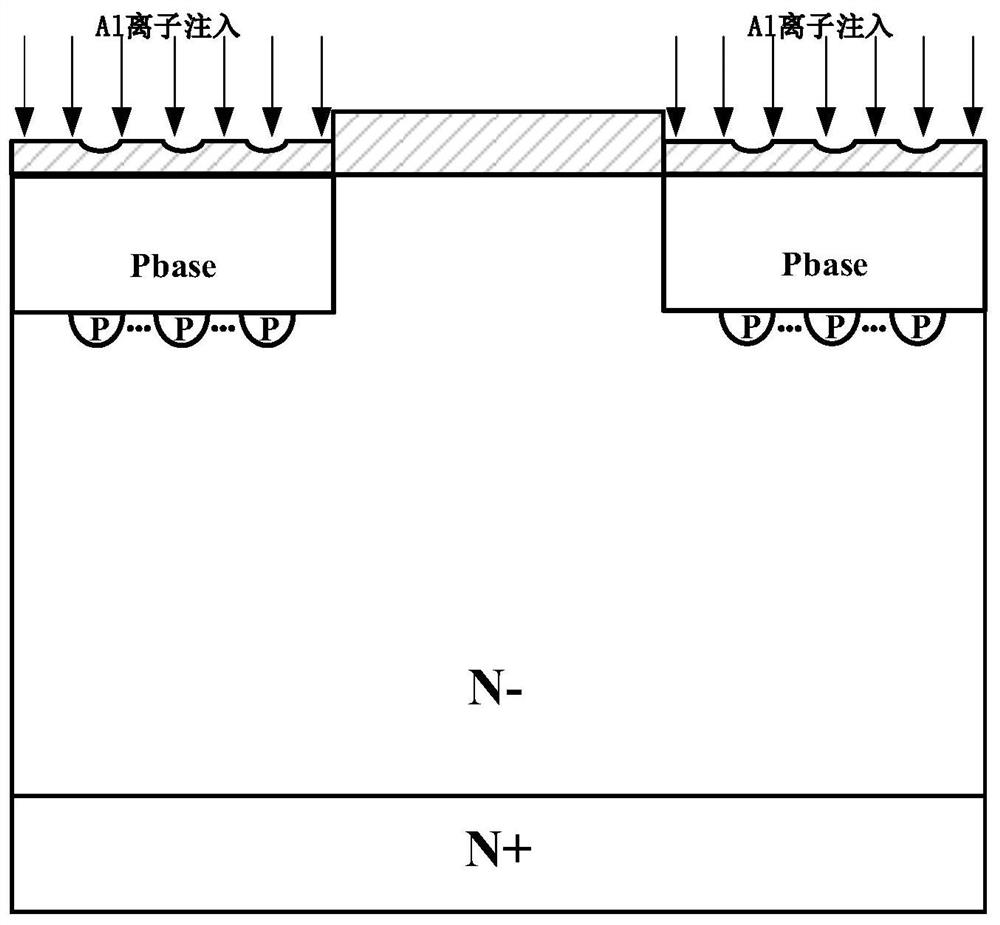

Silicon carbide MOSFET device with avalanche charge transition buffer layer and preparation method of silicon carbide MOSFET device

InactiveCN113314613AImproved avalanche capabilityEnhanced Avalanche ReliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesAluminum IonMOSFET

The invention provides a silicon carbide MOSFET device with an avalanche charge transition buffer layer and a manufacturing method of the silicon carbide MOSFET device, and the method comprises the steps: injecting aluminum ions into an N-epitaxial layer, forming a P-type avalanche charge transition buffer layer and a P-type base region at the same time, and adjusting the injection depth through the thickness of a SiO2 mask; injecting aluminum ions to form a P + ohmic contact region; performing nitrogen ion implantation to form an N + source region and activating annealing; performing thermal growth and nitriding annealing on the gate oxide layer; depositing and etching polycrystalline silicon; introducing a plurality of electric field peak values below the P-type base region through the P-type avalanche charge transition buffer layer, after avalanche occurs on the device, and discharging avalanche charges from the P-type avalanche charge transition buffer layer and the corner of the P-type base region, so the generated current is in discrete distribution, the increase of local temperature is greatly alleviated, the avalanche capability of the device is improved, and the avalanche reliability of the silicon carbide MOSFET device in the blocking state is successfully enhanced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

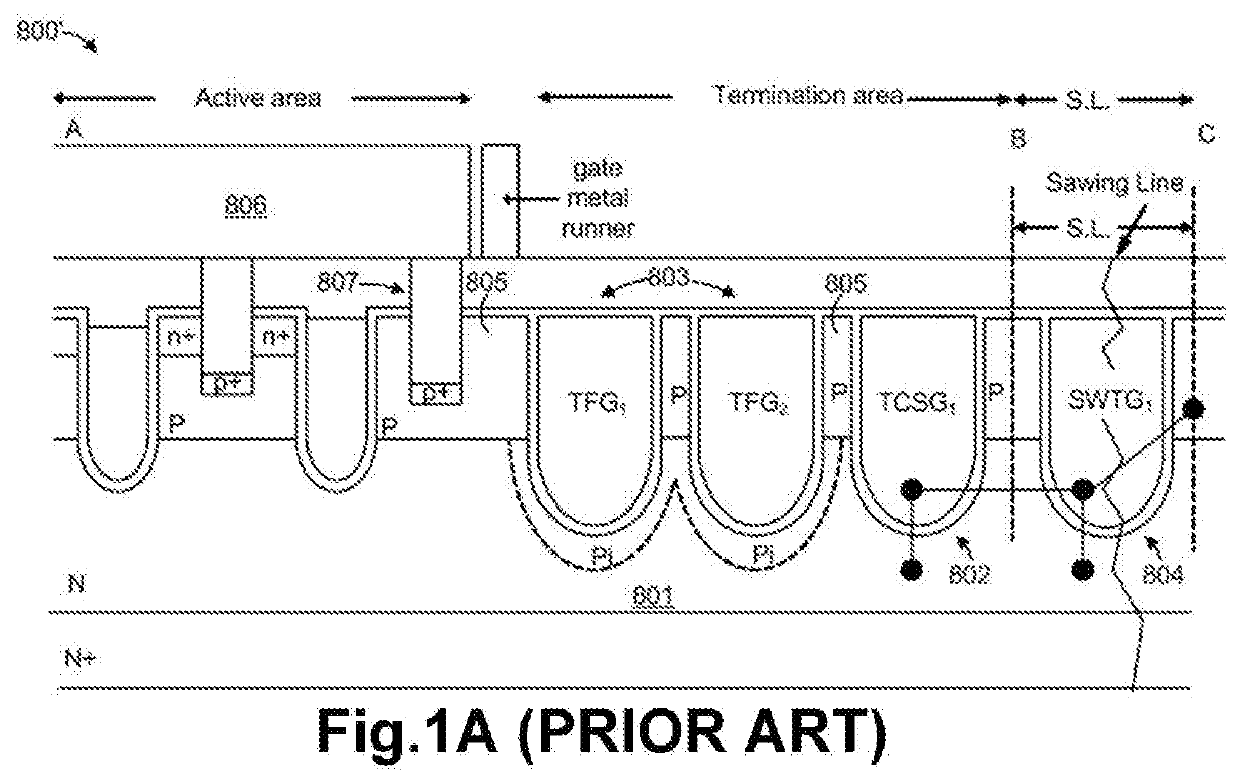

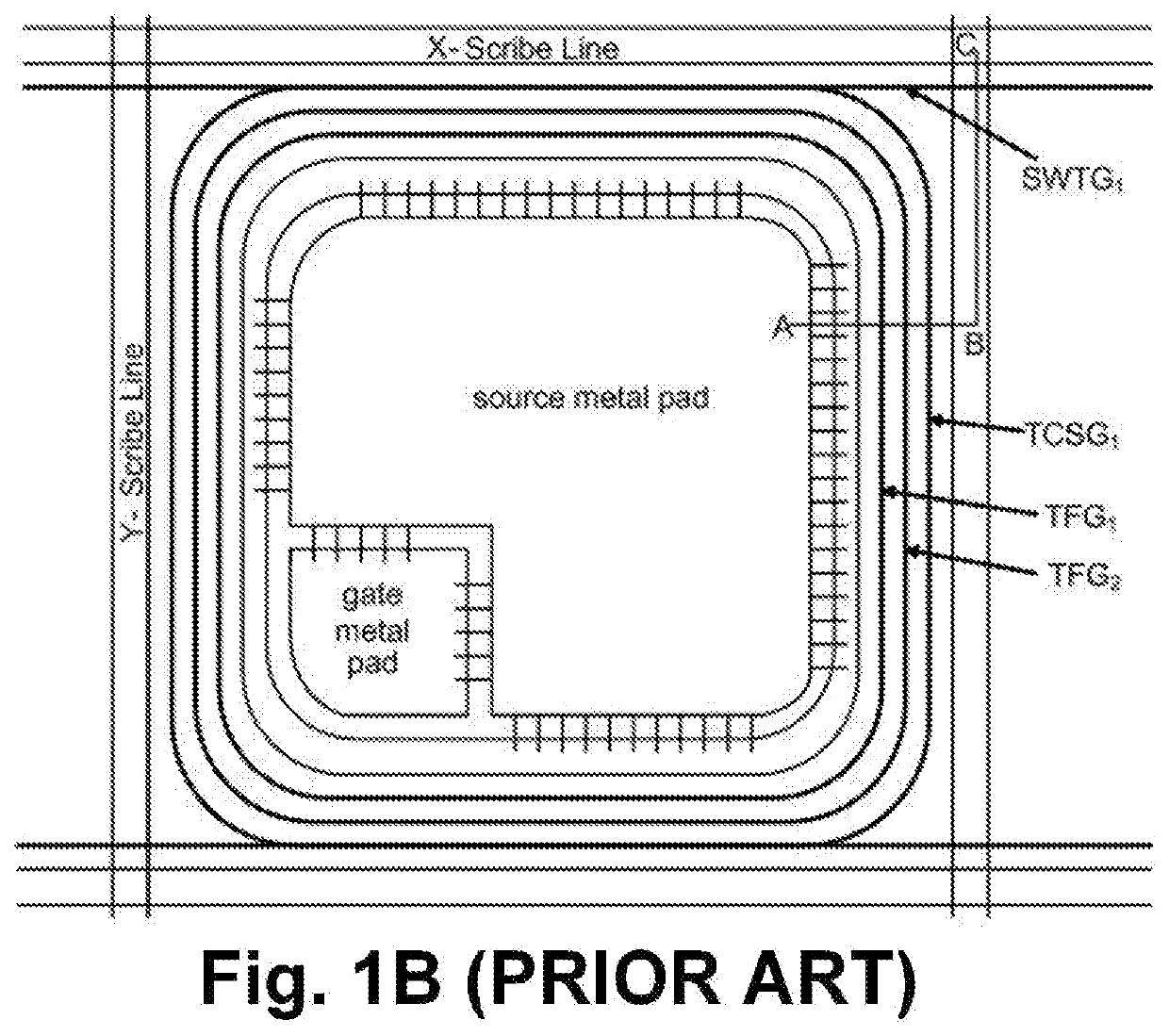

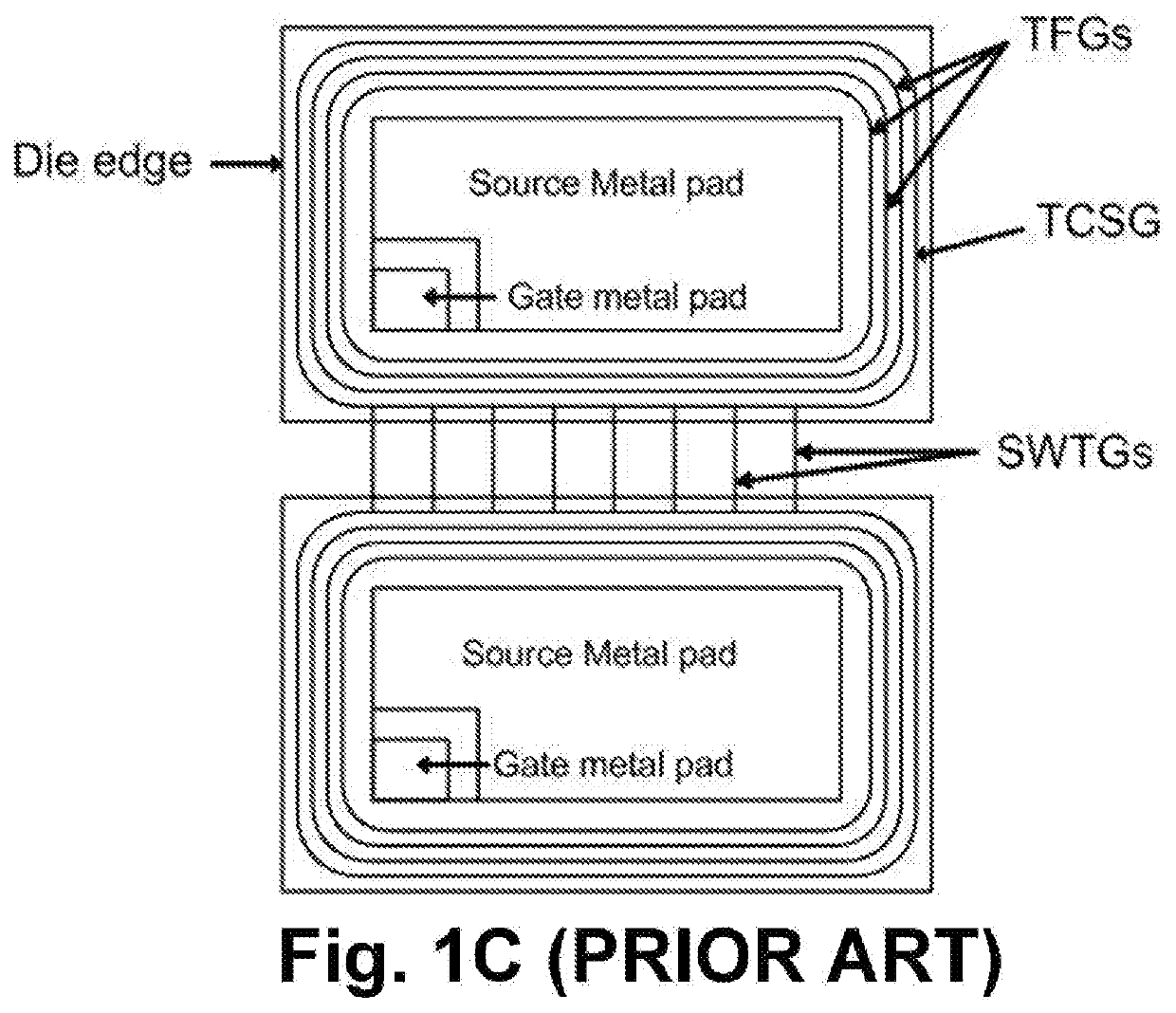

Trench mosfets having dummy cells for avalanche capability improvement

ActiveUS20210104624A1Improved avalanche capabilityTransistorTrench mosfetElectrical and Electronics engineering

A trench MOSFET layout with multiple trenched floating gates and at least one trenched channel stop gate in termination area shorted with drain region is disclosed to make it feasibly achieved after die sawing. The layout consisted of multiple trench MOSFETs connected together with multiple sawing trenched gates across a space between two trench MOSFETs having a width same as scribe line. Dummy cells formed between an edge trench and active area act as butler cells to absorb avalanche energy when gate bias is increasing for turning on channel, therefore, the UIS failure issue is avoided and the avalanche capability of the trench MOSFET is enhanced.

Owner:NAMI MOS CO LTD

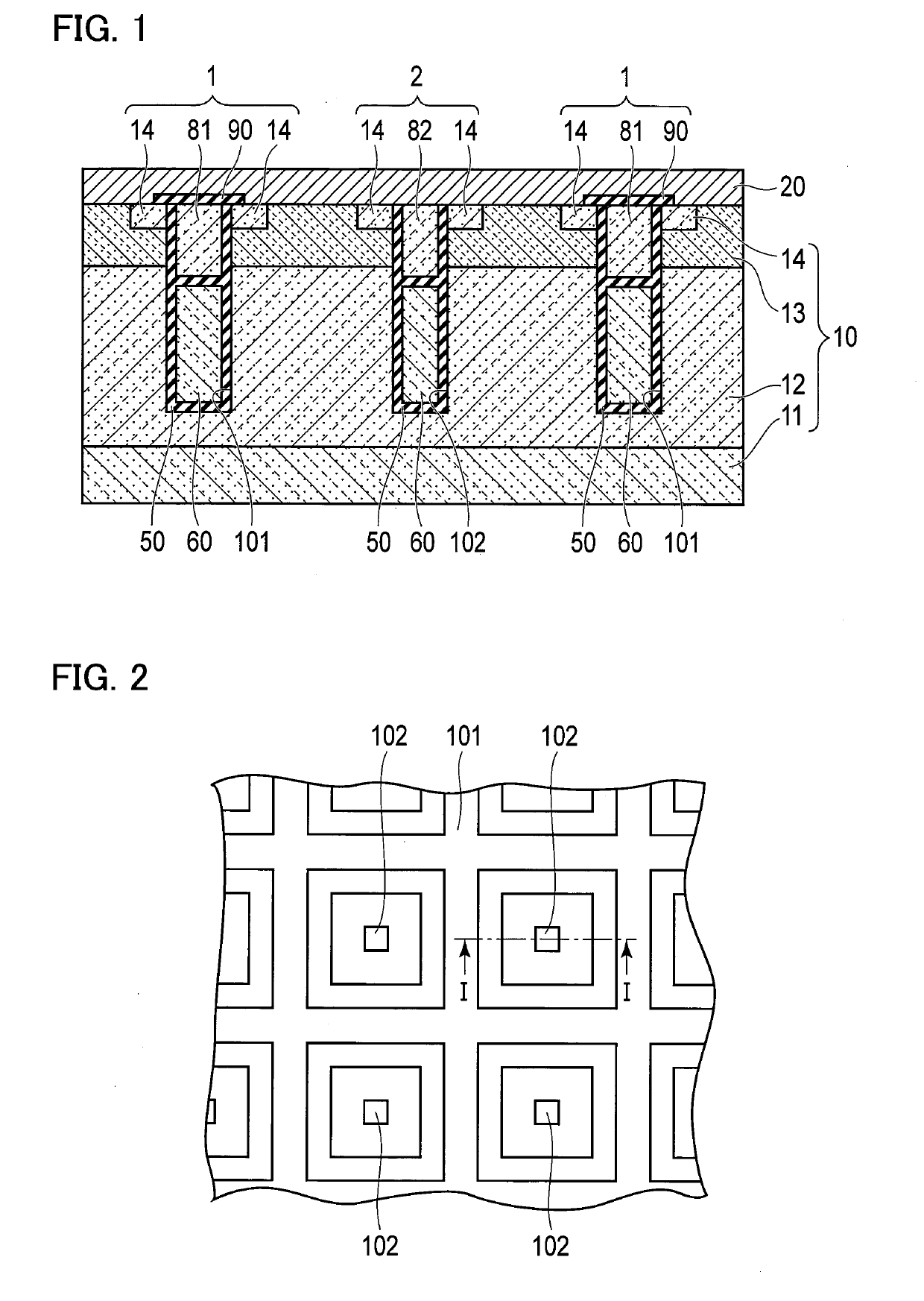

Semiconductor device

ActiveUS20190252543A1Lower on-state resistanceImproved avalanche capabilityTransistorEngineeringSemiconductor device

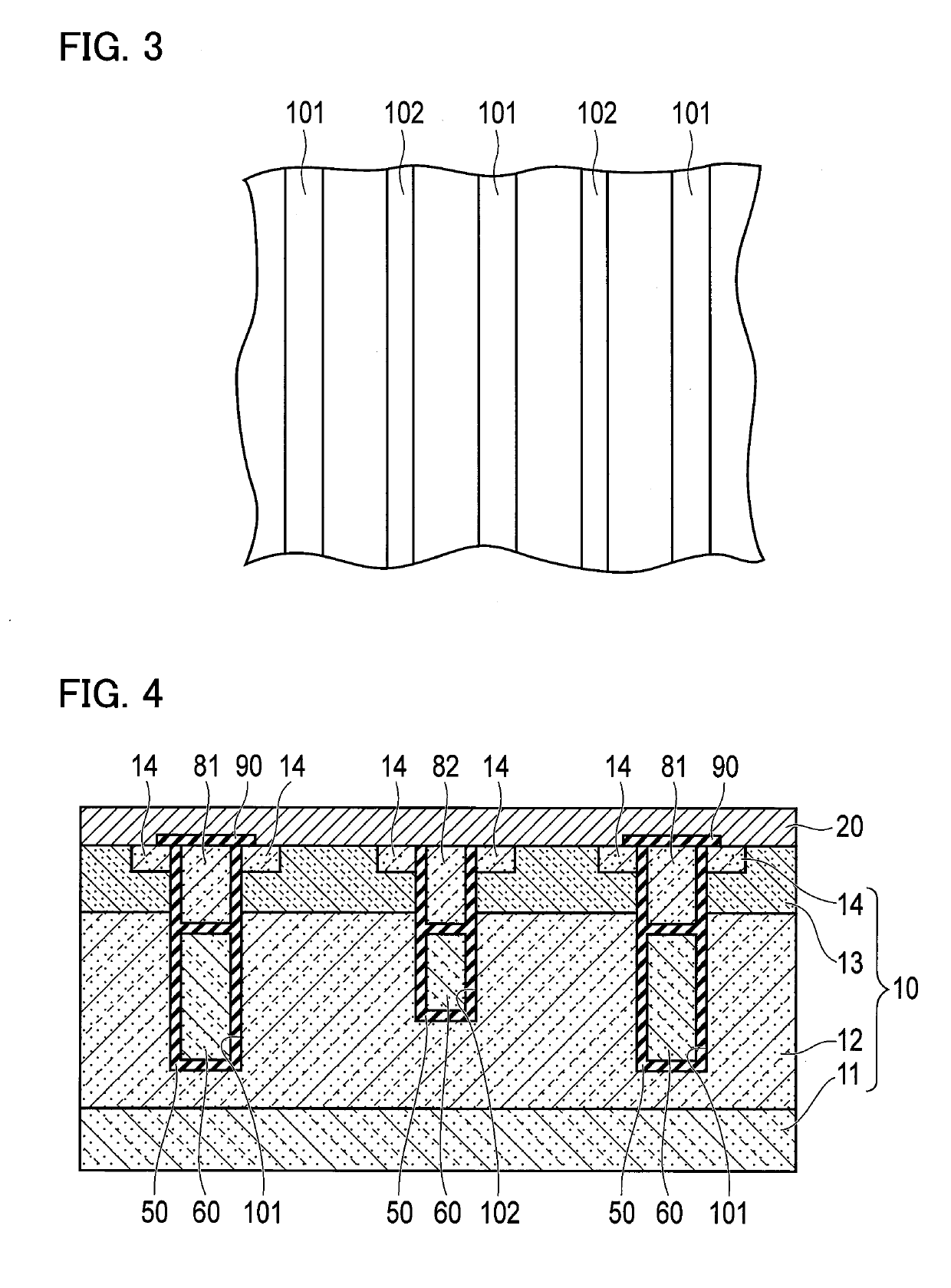

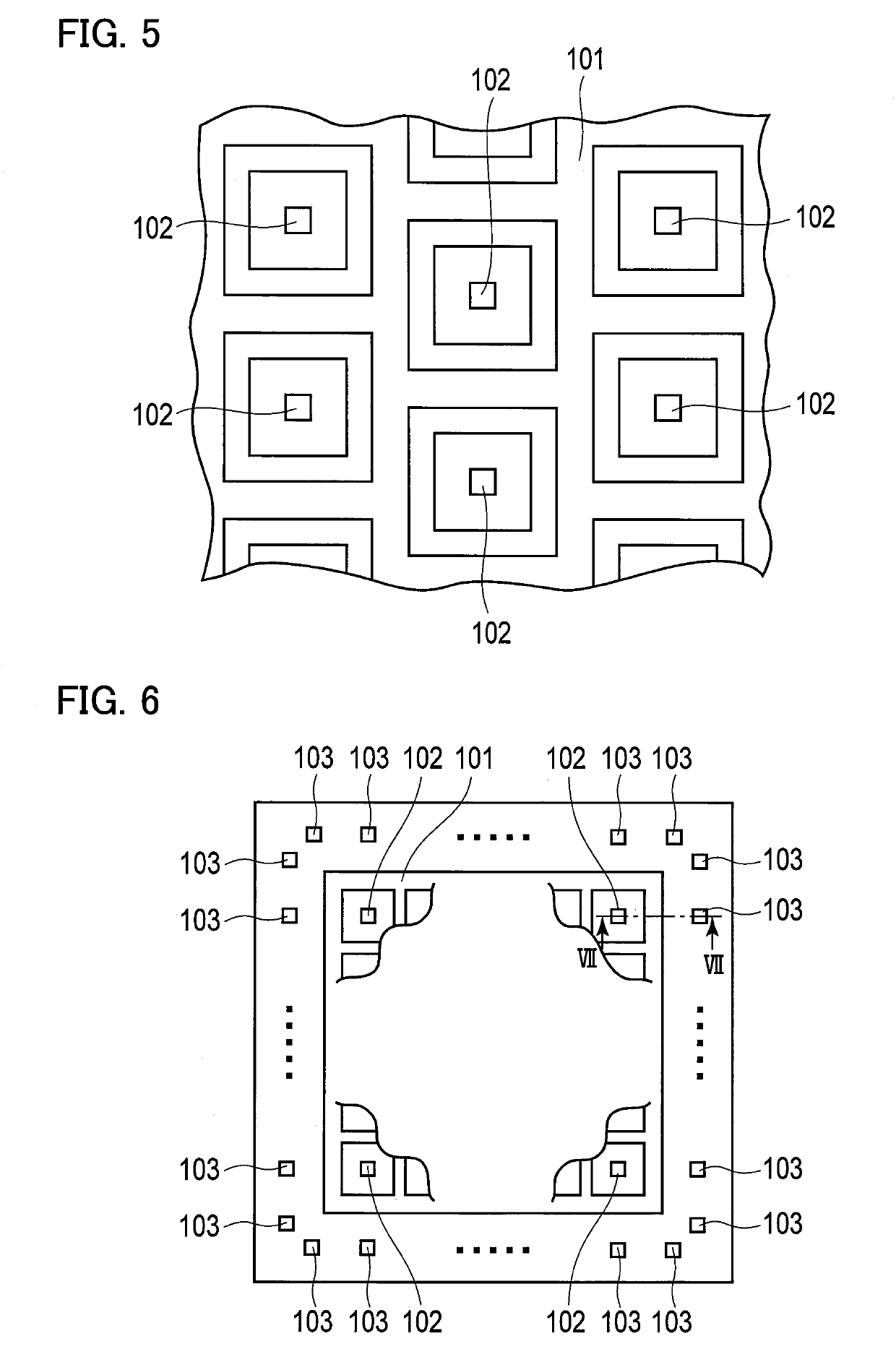

A semiconductor device includes: a semiconductor base 10 in which a first trench 101 is formed in a mesh-like shape in a plan view and a second trench 102 is formed in a mesh opening surrounded by the first trench 101; a first semiconductor element 1 which is formed in the semiconductor base 10 and includes a first gate electrode 81 provided within the first trench 101; and a second semiconductor element 2 which is formed in the semiconductor base 10 and includes a second gate electrode 82 provided within the second trench 102 surrounded by the first gate electrode 81.

Owner:SANKEN ELECTRIC CO LTD

Combined type ion lens ion wind generation device

PendingCN107335544AFull collisionGather and fullyElectrode constructionsElectrodes cleaningIon windEngineering

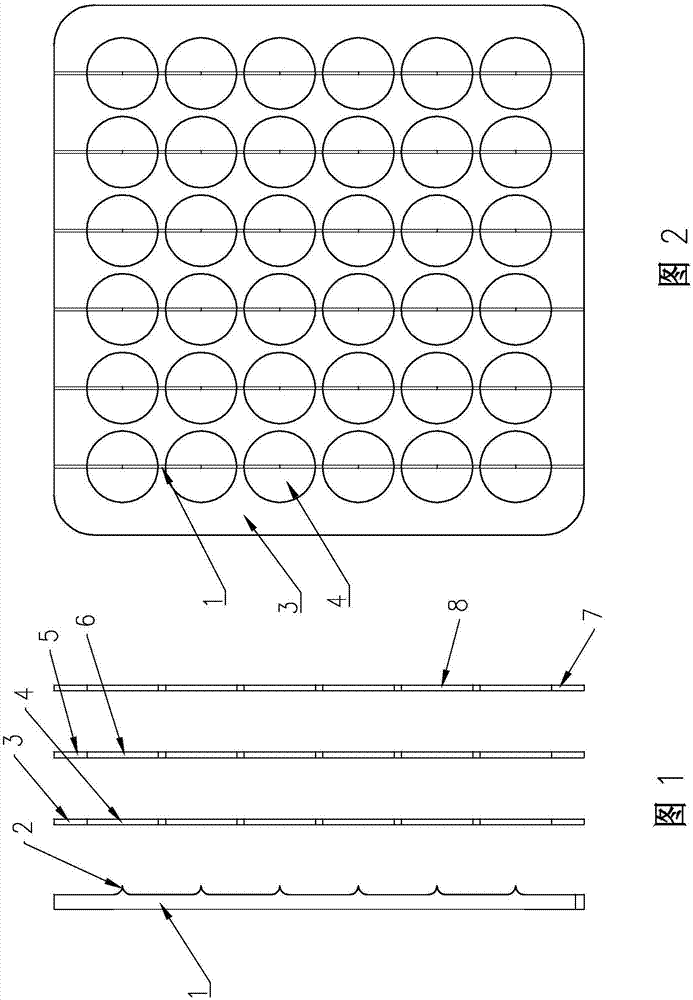

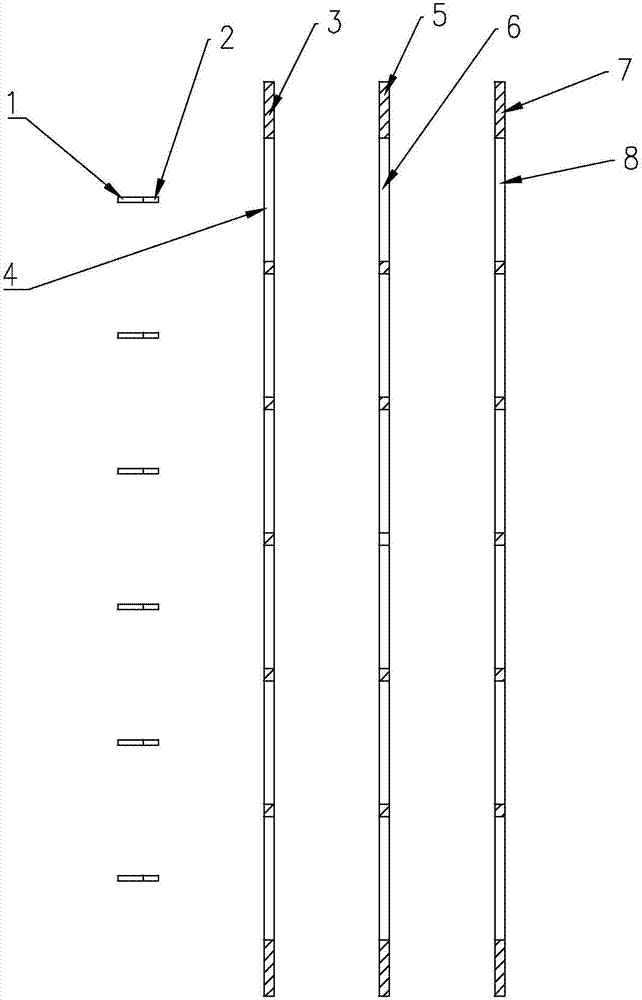

The invention provides a combined type ion lens ion wind generation device. The combined type ion lens ion wind generation device comprises an emitting electrode, wherein the emitting electrode comprises a plurality of electrode plates made of a conducting material; plate surfaces of the plurality of electrode plates are located in the front-back vertical direction; a row of discharging needles are uniformly arrayed on a backward side face of each electrode plate along the vertical direction; each discharging needle backward stretches out along the horizontal direction; a front lens plate is arranged behind the emitting electrode; a plate surface of the front lens plate is located in the left-back vertical direction; a plurality of grades of circular front lens through holes are uniformly arrayed on the a plate surface of the front lens plate along the vertical direction; the backward side face of each electrode plate faces one row of the front lens through holes; and a needle point of each discharging needle points to the middle part of one front lens through hole. The invention aims at providing the combined type ion lens ion wind generation device, which can be applied to an outdoor open space system, can be used for reducing the concentration of particulate matters at the periphery of a region of the device can be reduced within relatively short time, does not need to be driven by utilizing a draught fan in a purification process and has extremely low power consumption.

Owner:北京中和锦程科技有限公司

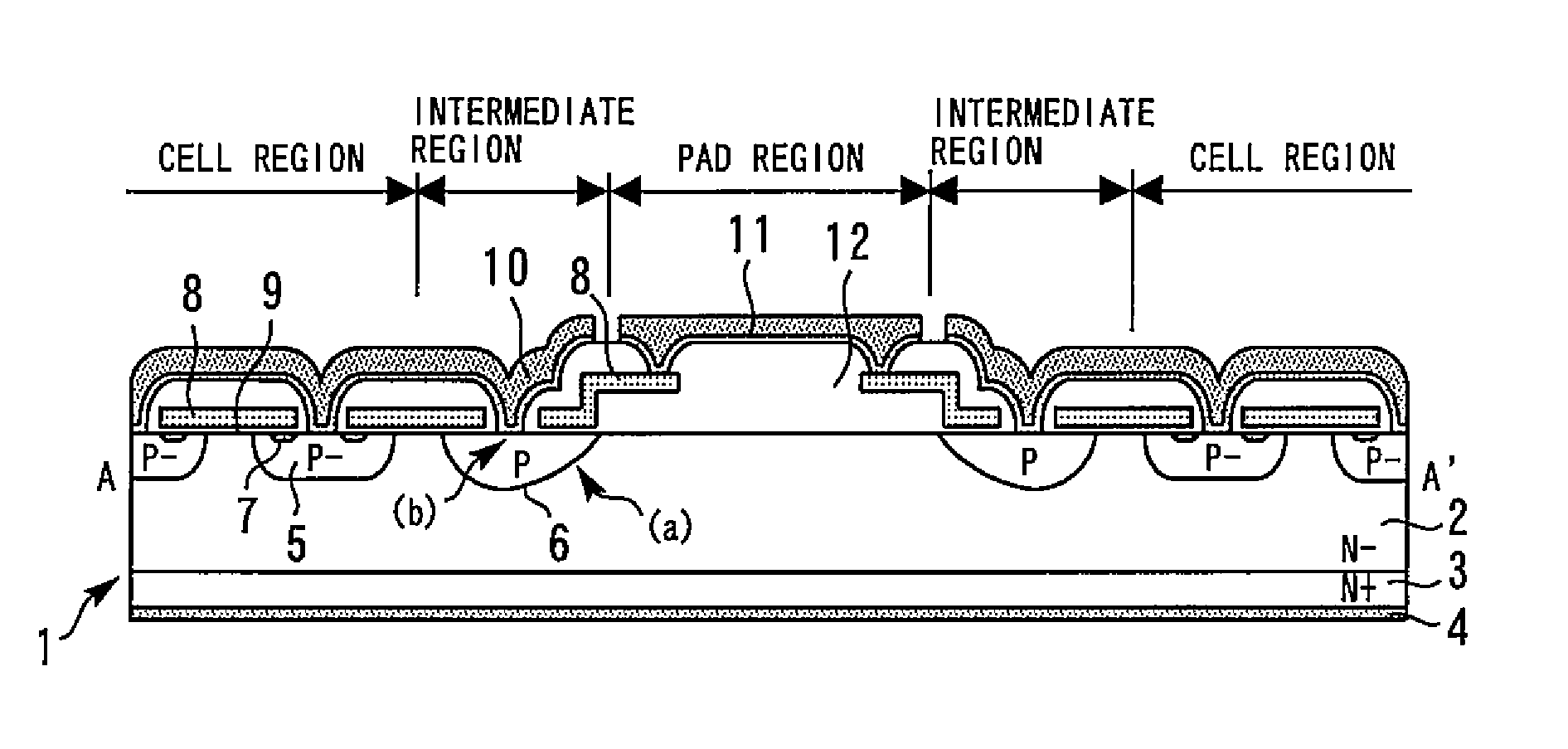

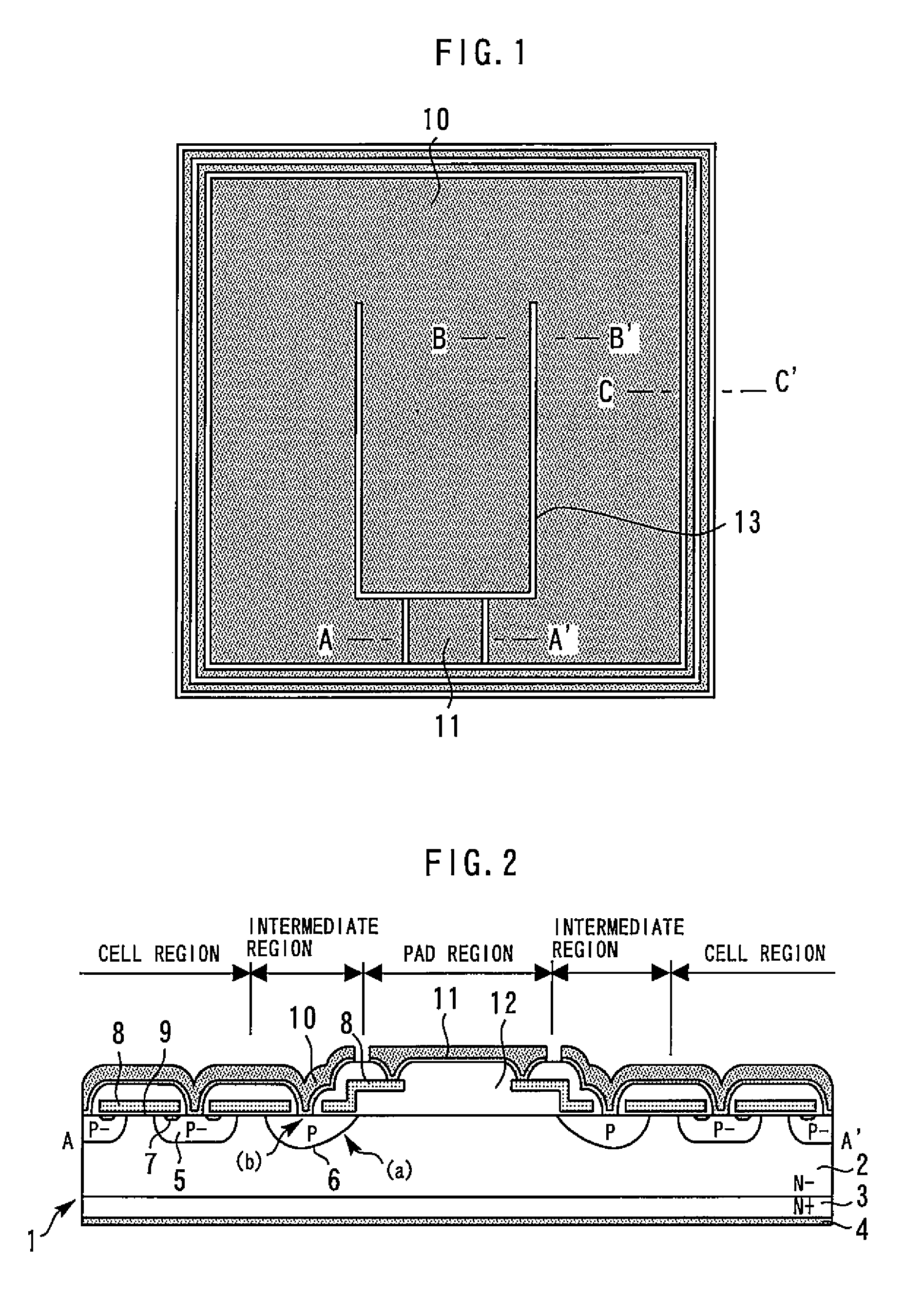

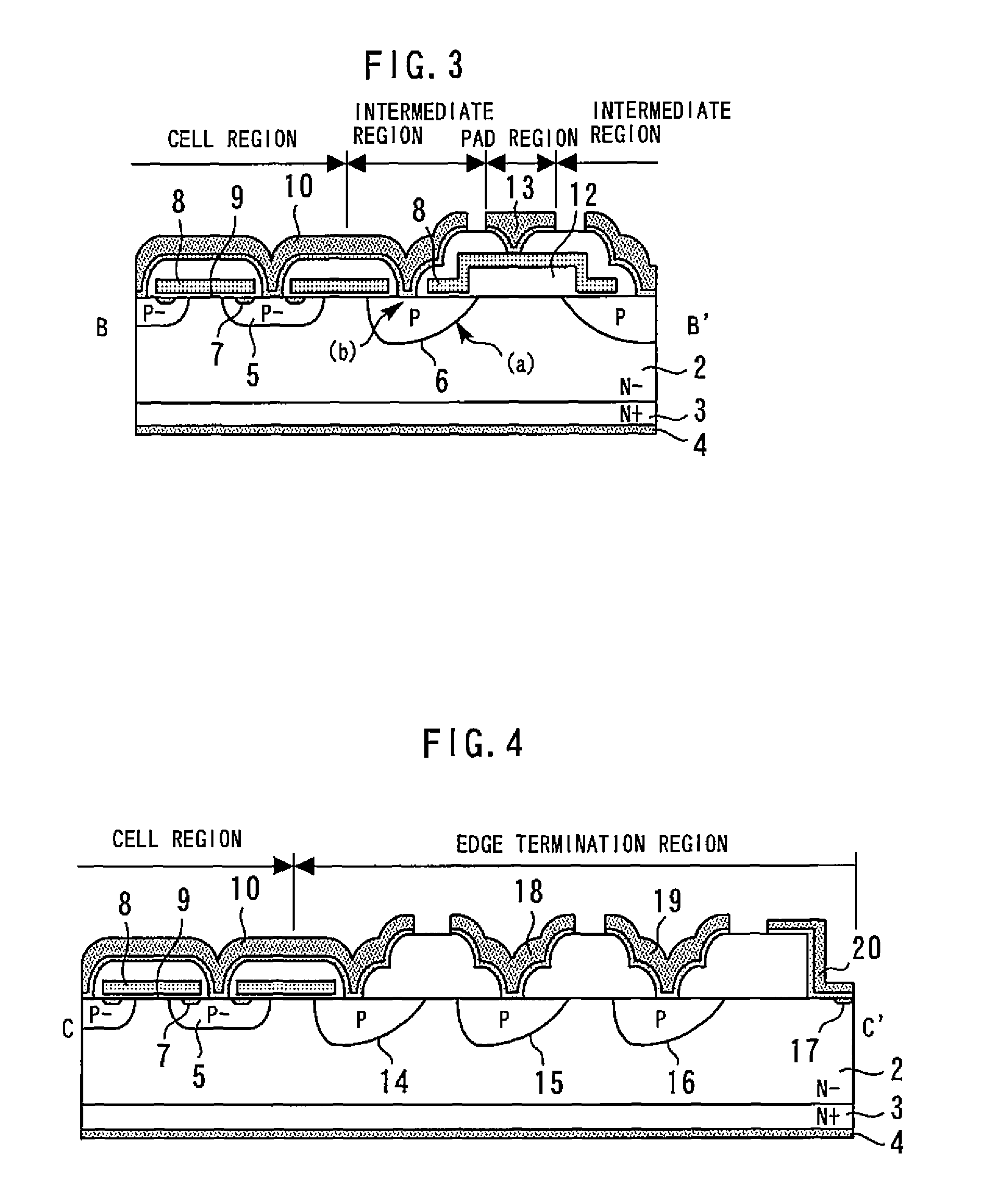

Semiconductor device having a variation lateral doping structure and method for manufaturing the same

ActiveUS9093310B2Improved avalanche capabilityIncrease capacityTransistorSemiconductor/solid-state device manufacturingCell regionImpurity

A semiconductor device including a semiconductor layer of a first conductivity type in a cell region, a first base layer of a second conductivity type on the semiconductor layer in the cell region; a second base layer of the second conductivity type on the semiconductor layer in an intermediate region; a conductive region of a first conductivity type in the first base layer; a gate electrode on a channel region placed between the conductive region and the semiconductor layer; a first electrode connected to the first and second base layers; a second electrode connected to the semiconductor layer; and a gate pad on the semiconductor layer via an insulating film in a pad region and connected to the gate electrode, an impurity concentration gradation in the gate pad side of the second base layer has a gentler VLD structure than an impurity concentration gradation in the first base layer.

Owner:MITSUBISHI ELECTRIC CORP