Patents

Literature

37results about How to "Breakdown voltage of device" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Super junction / resurf LDMOST (SJR-LDMOST)

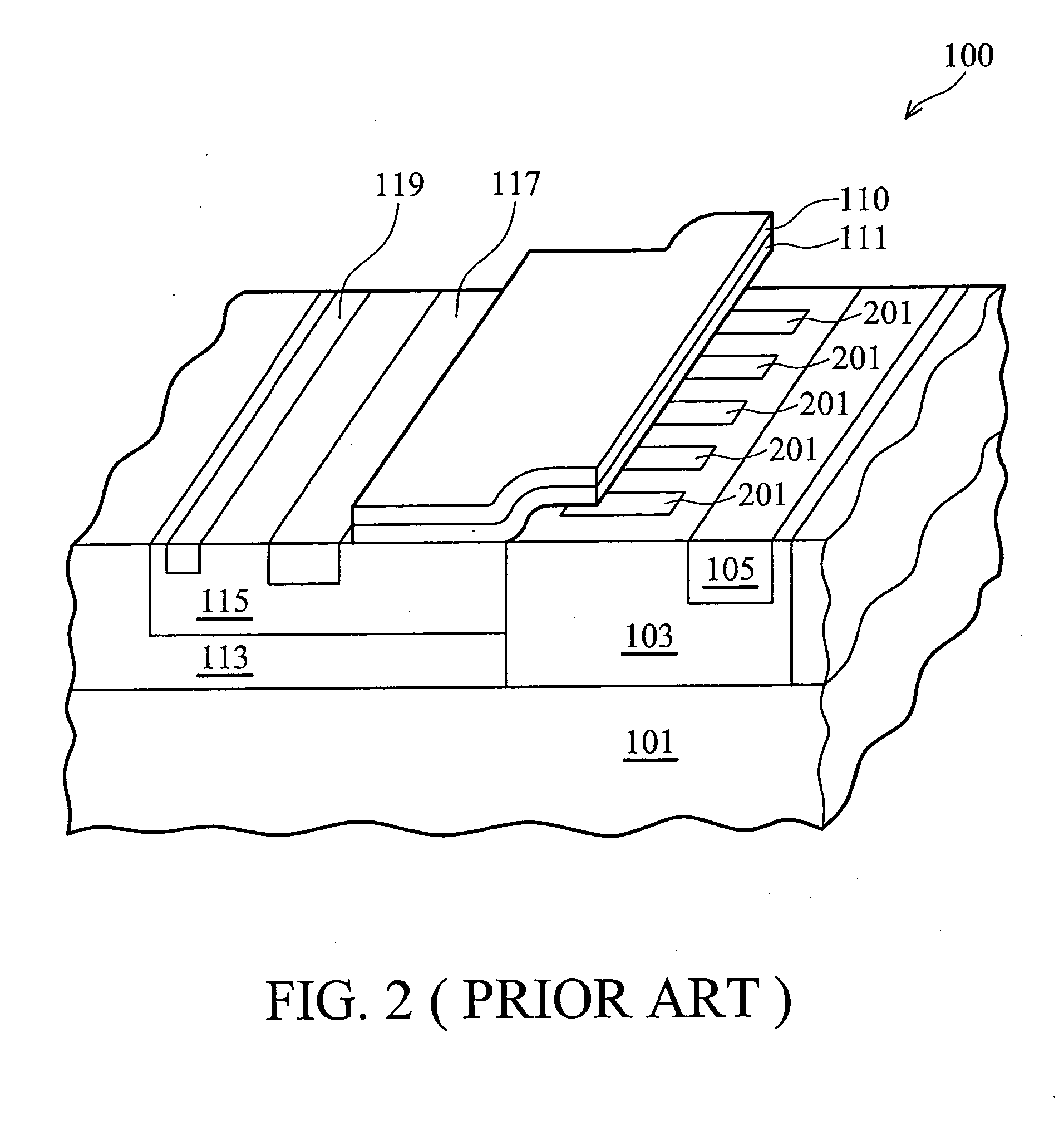

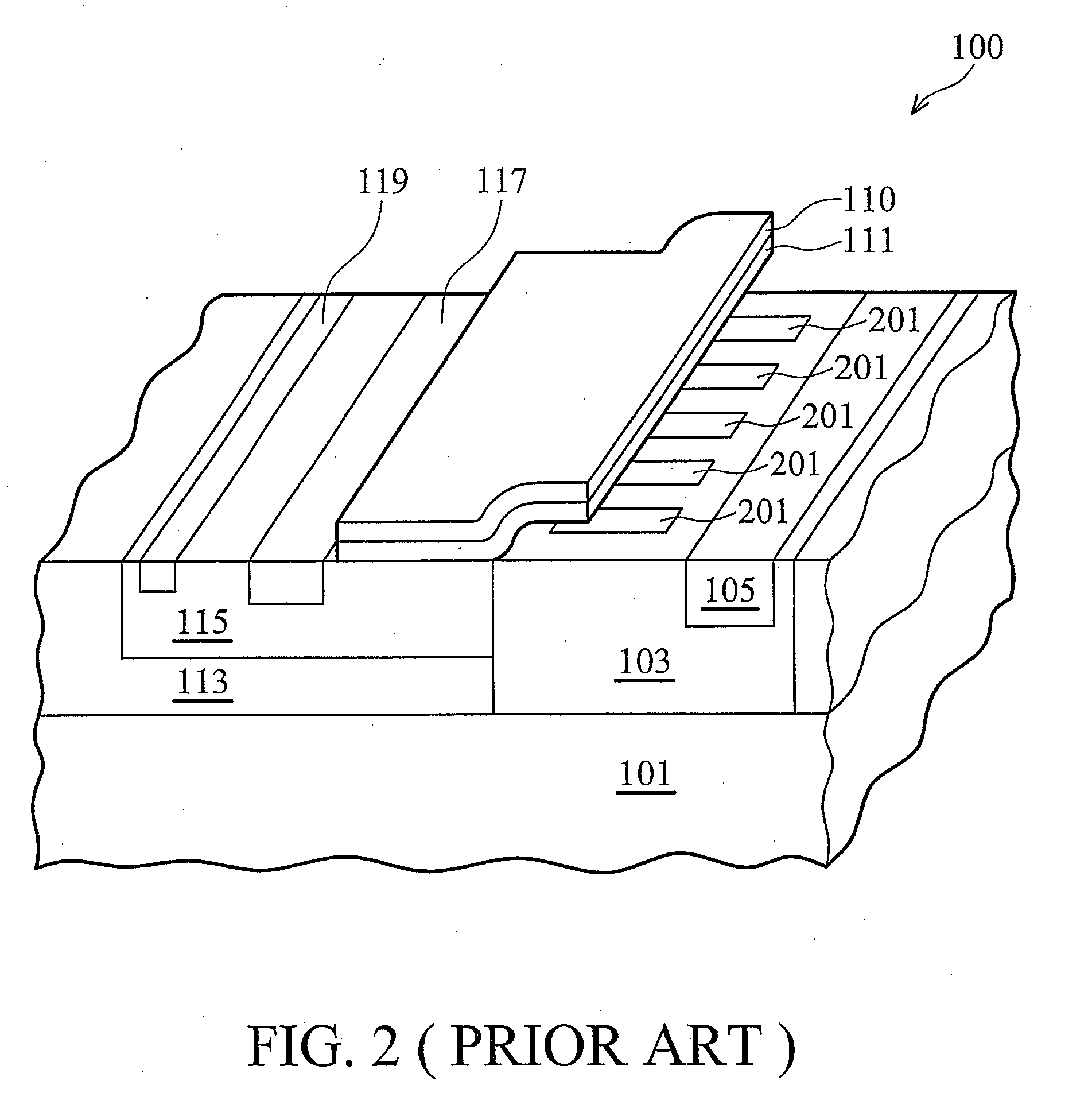

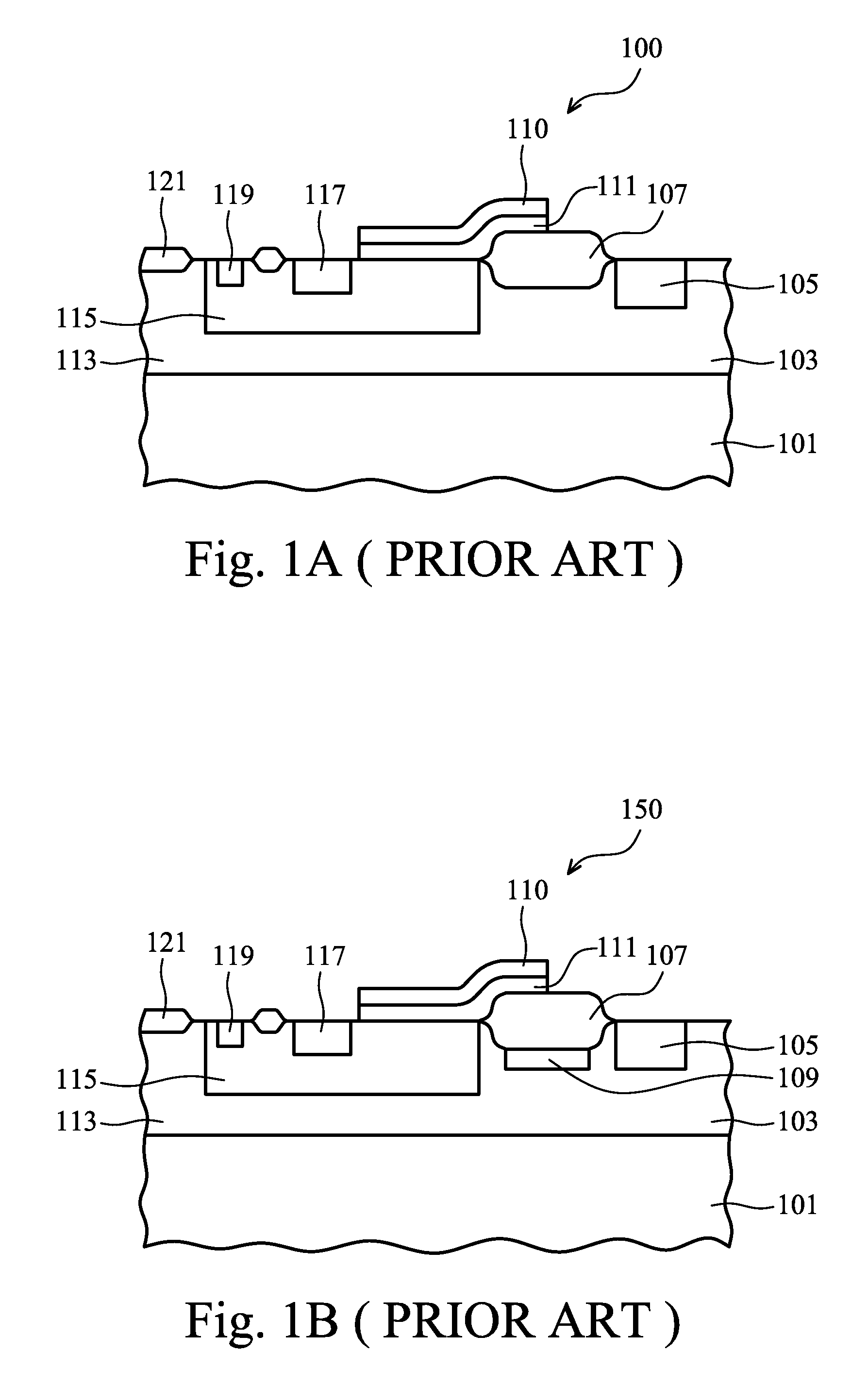

InactiveUS7023050B2Reduce doping concentrationBreakdown voltage of deviceSemiconductor devicesMOSFETDisplay device

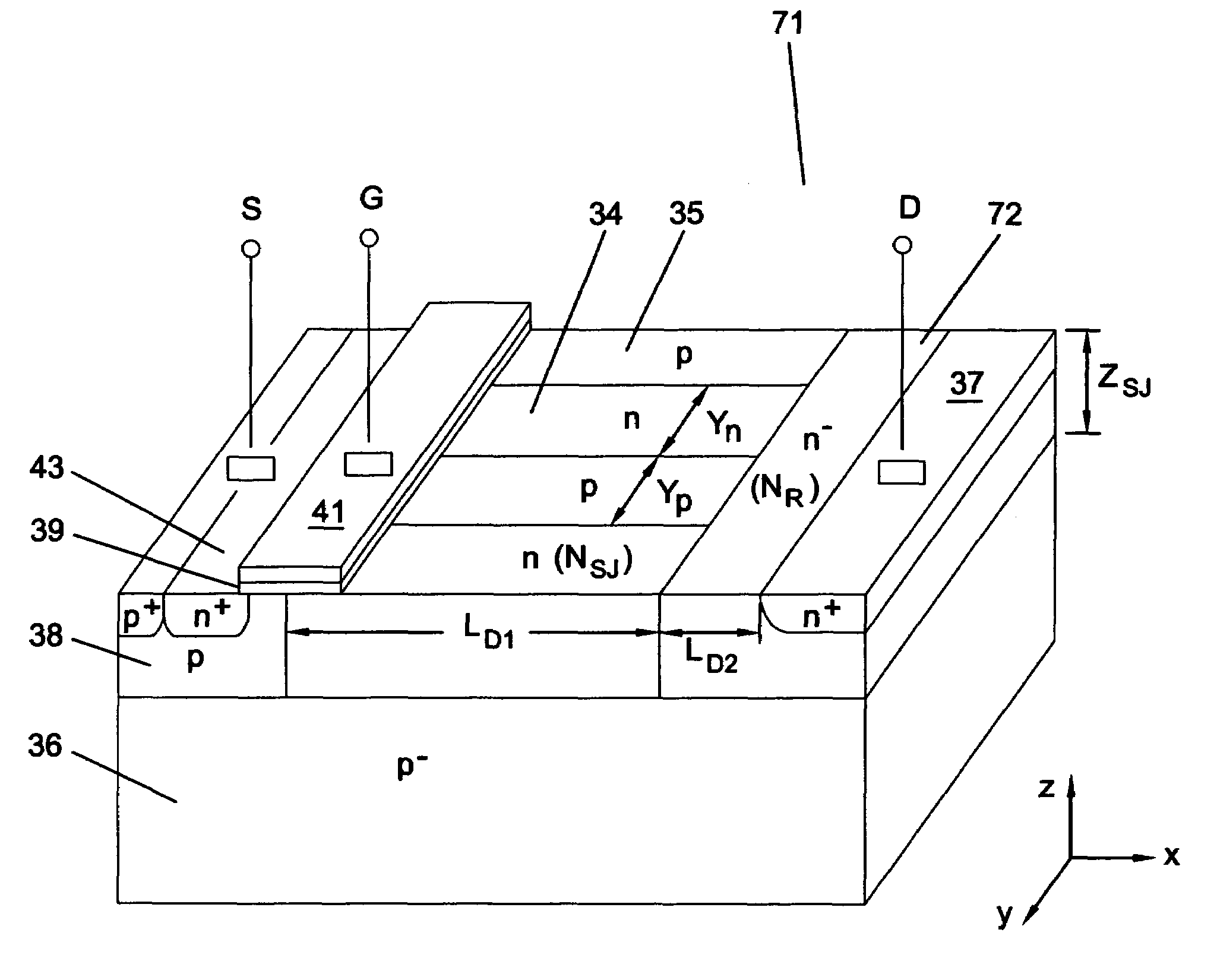

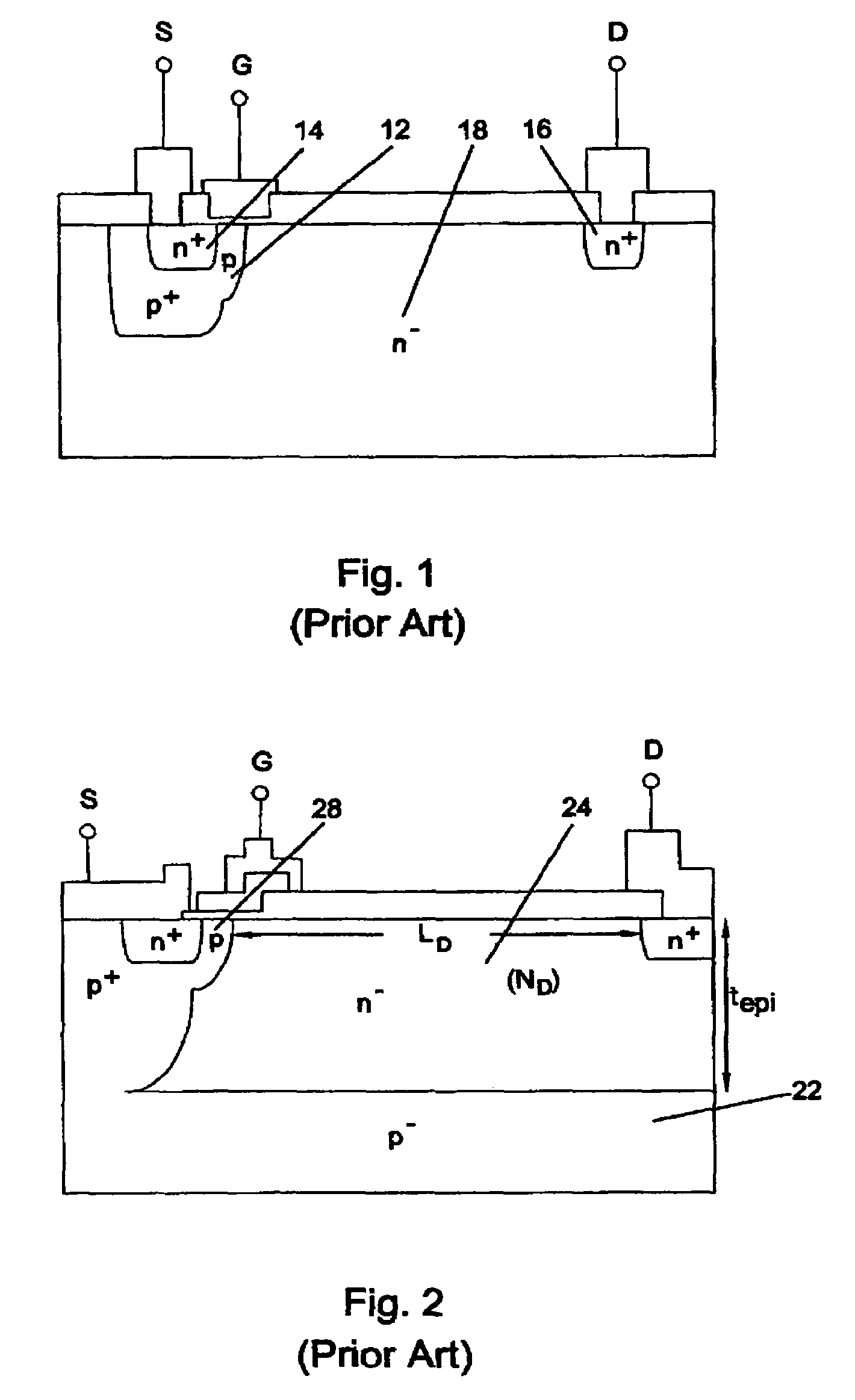

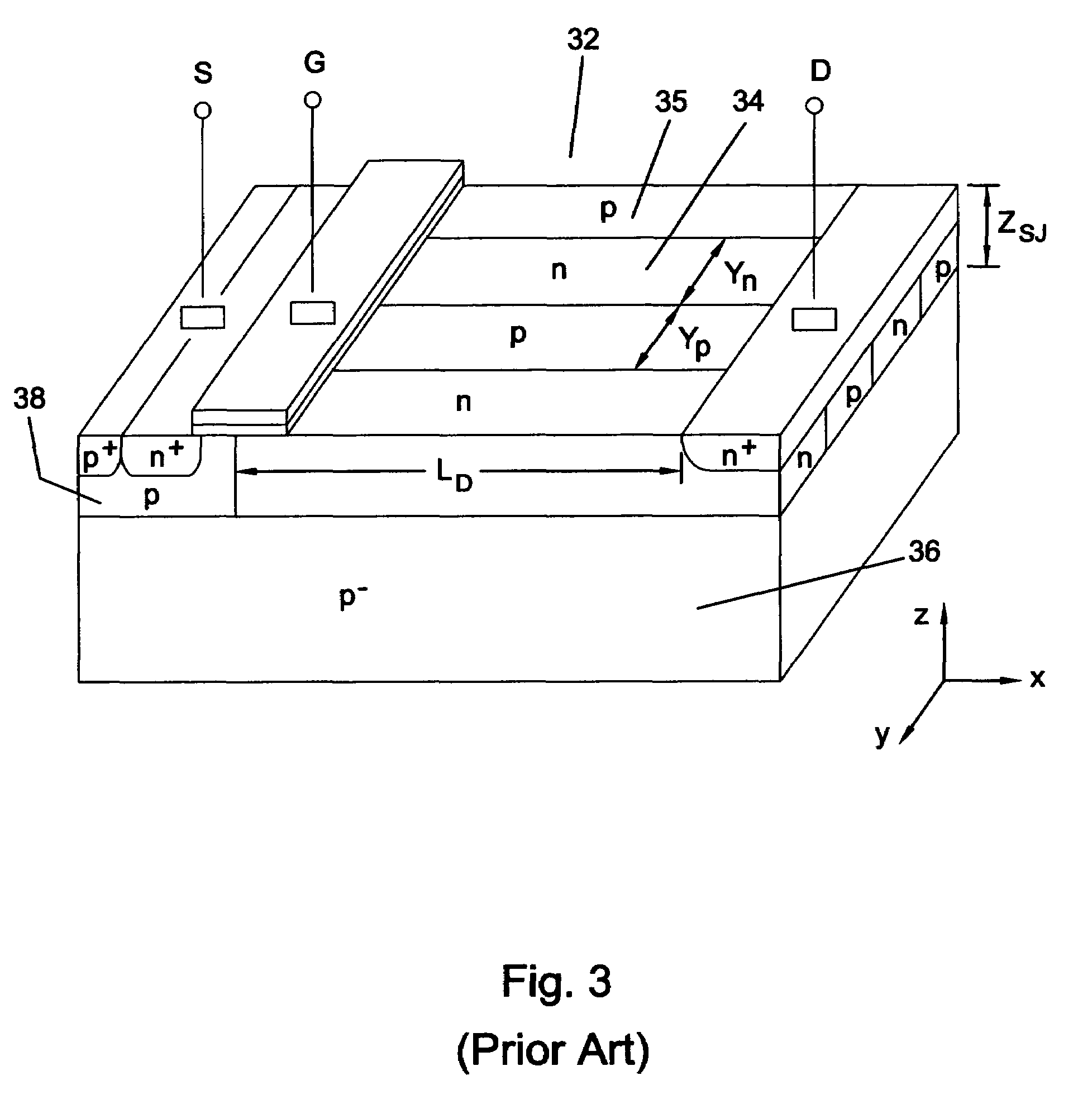

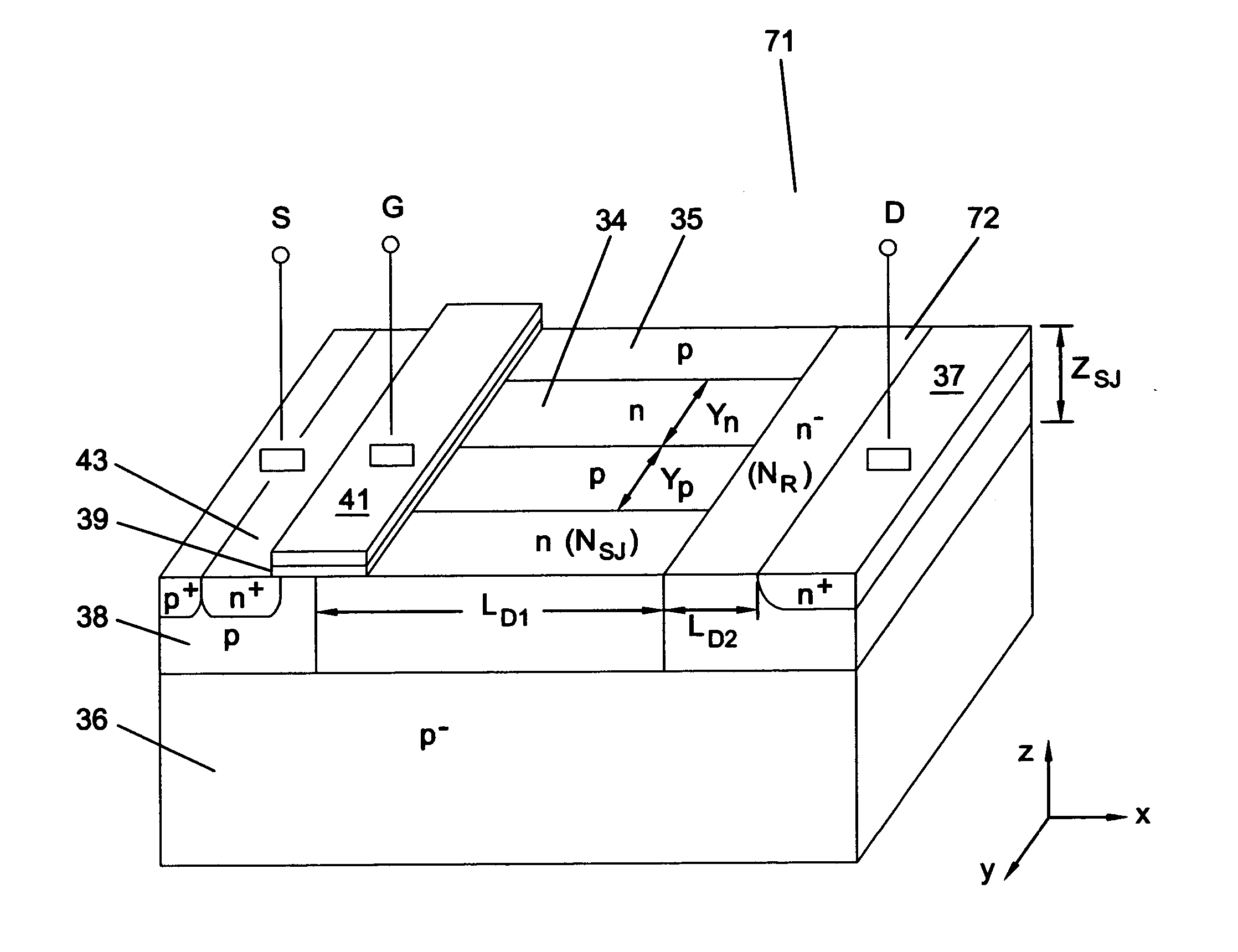

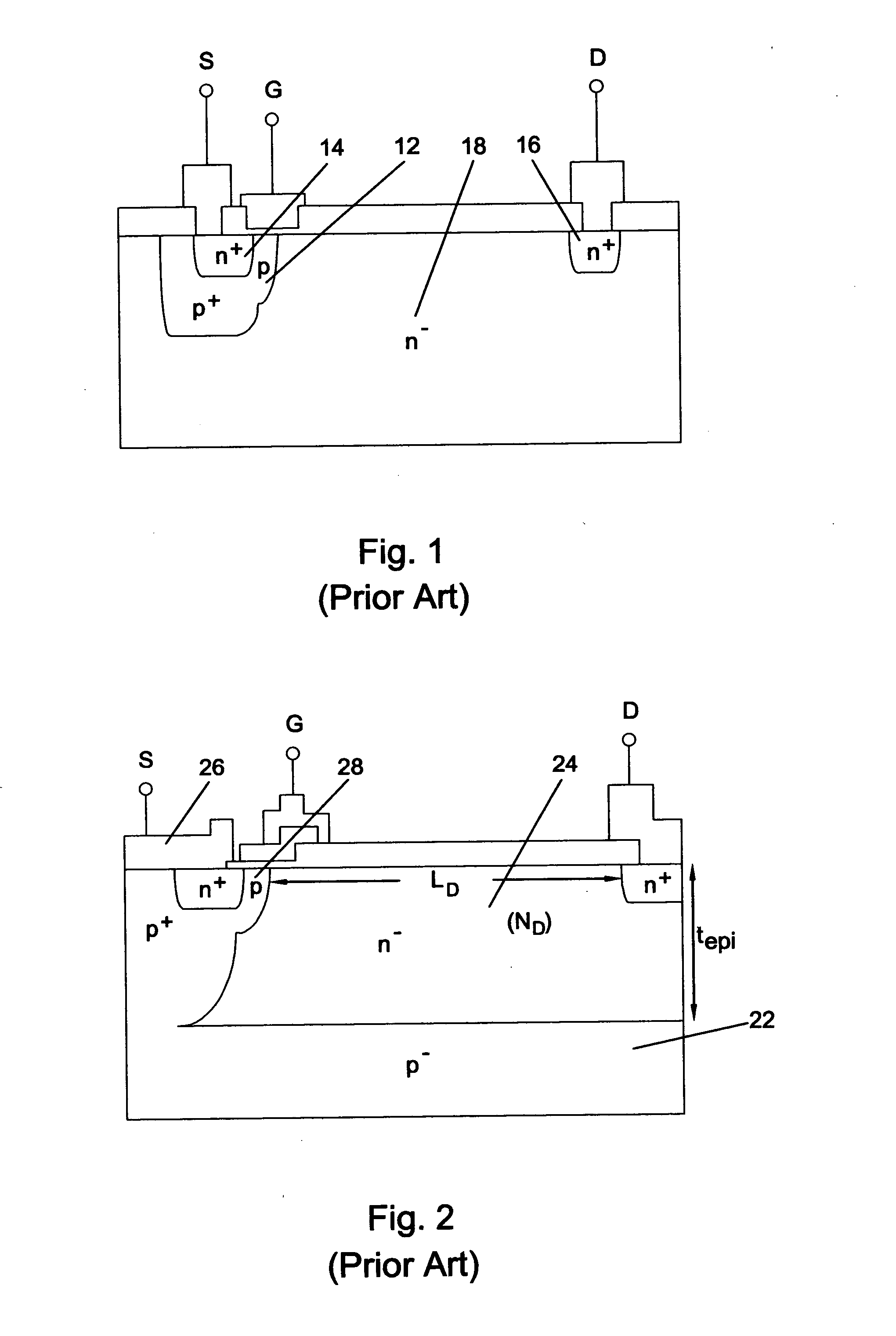

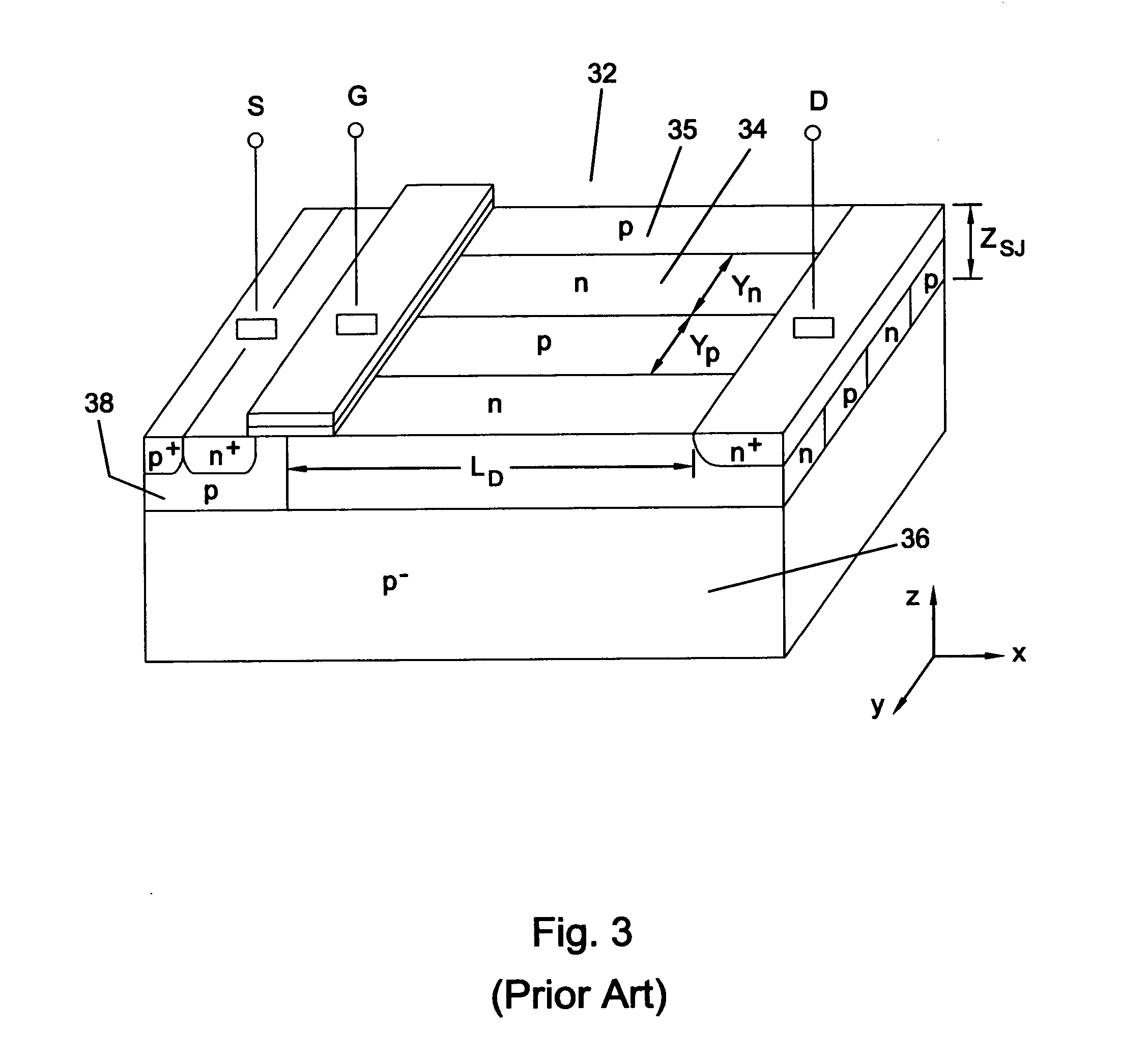

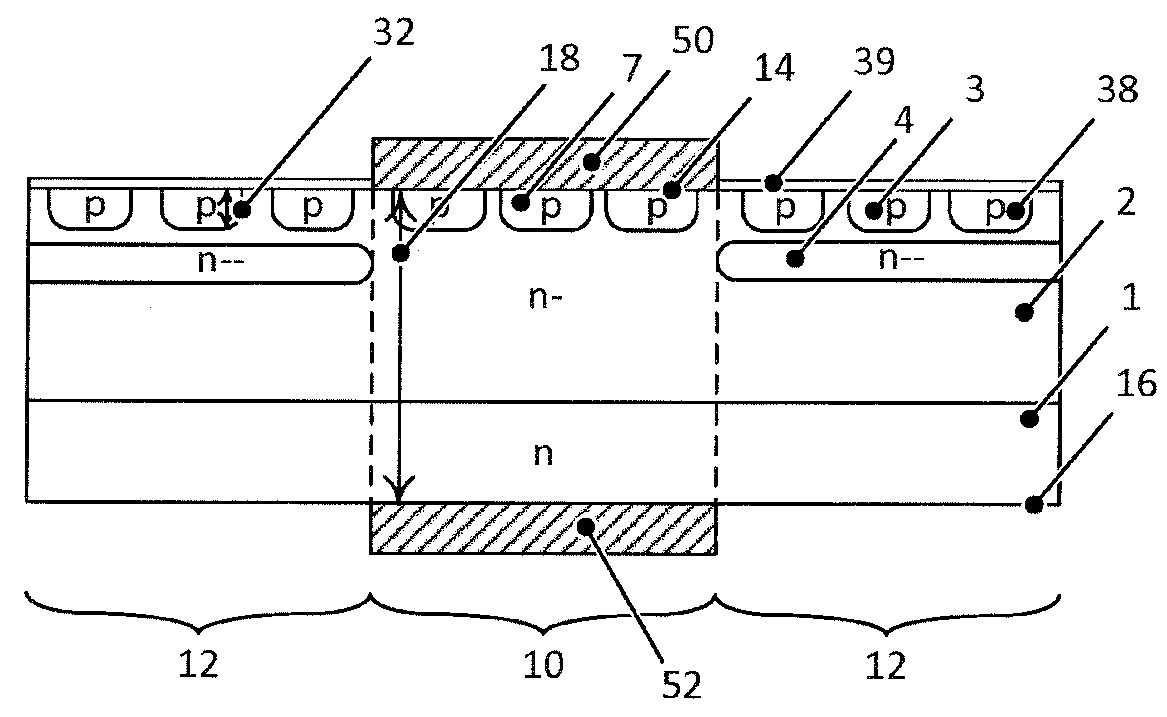

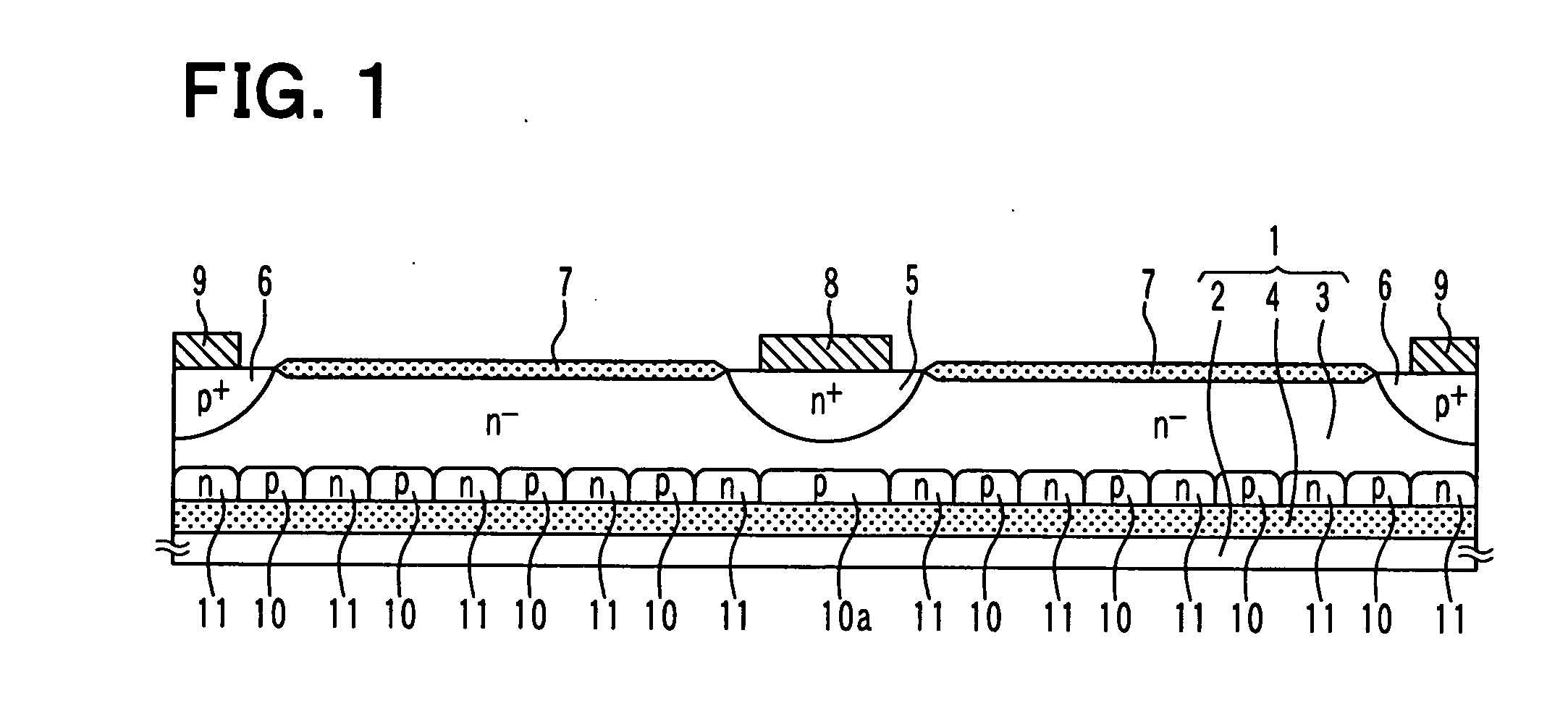

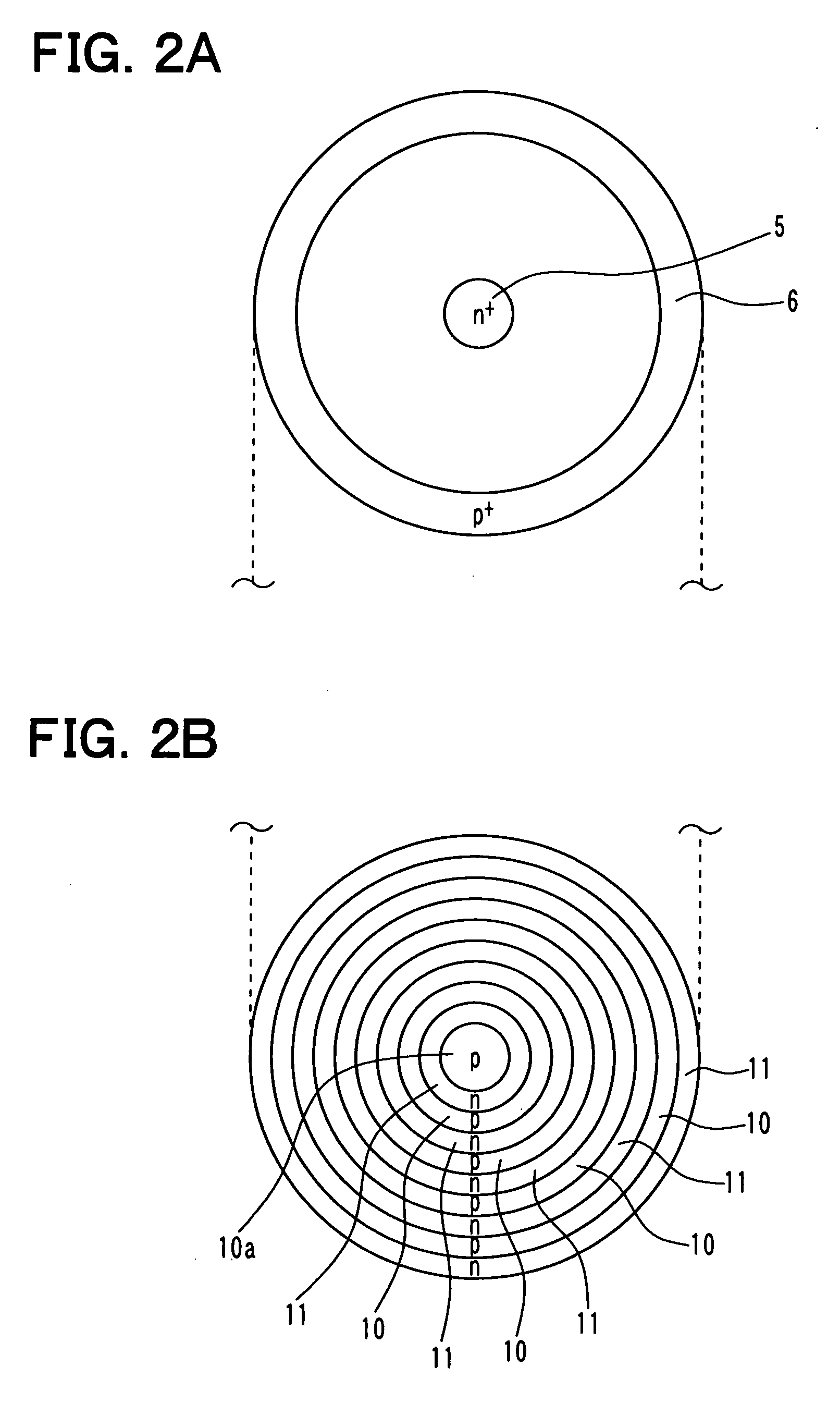

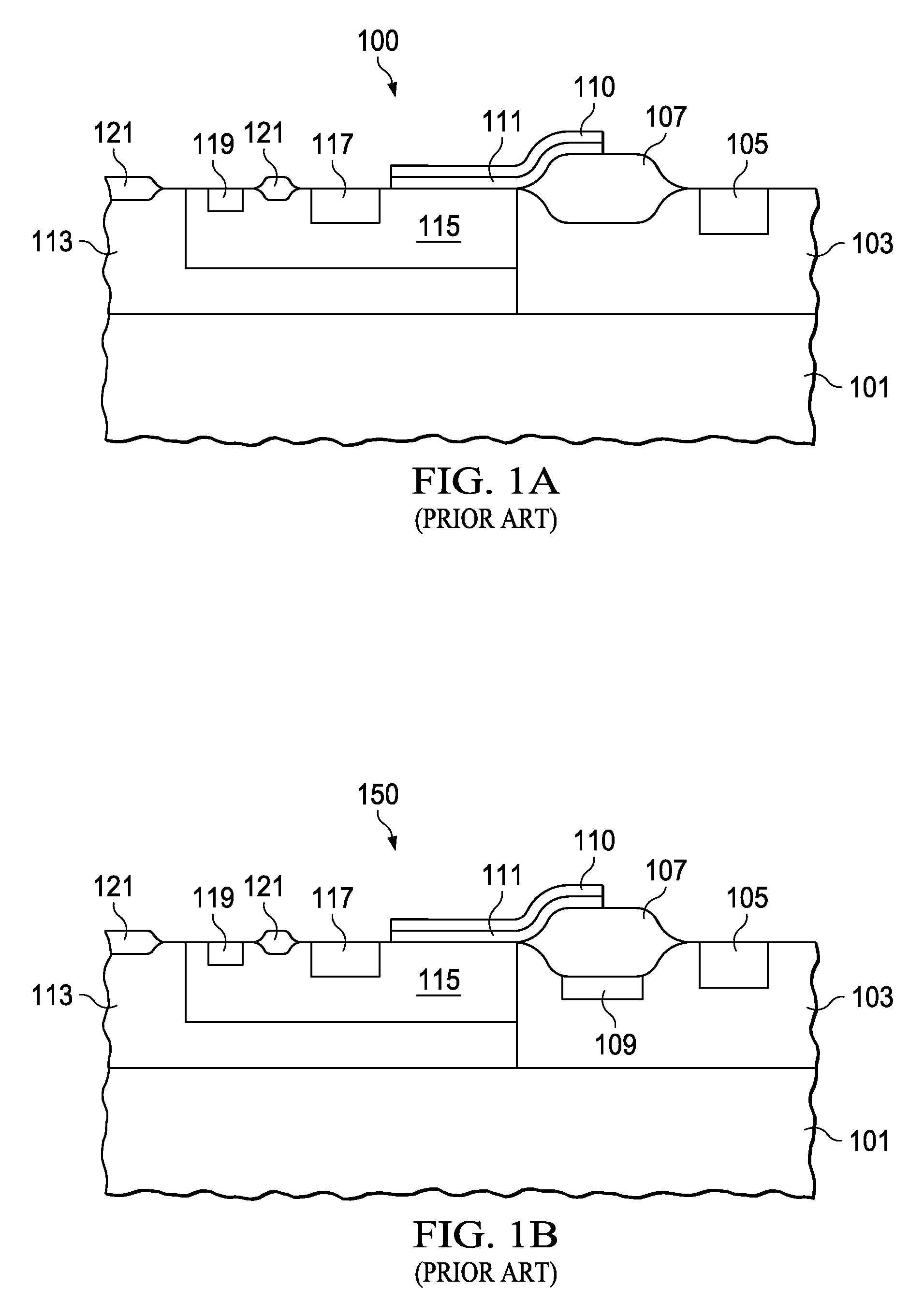

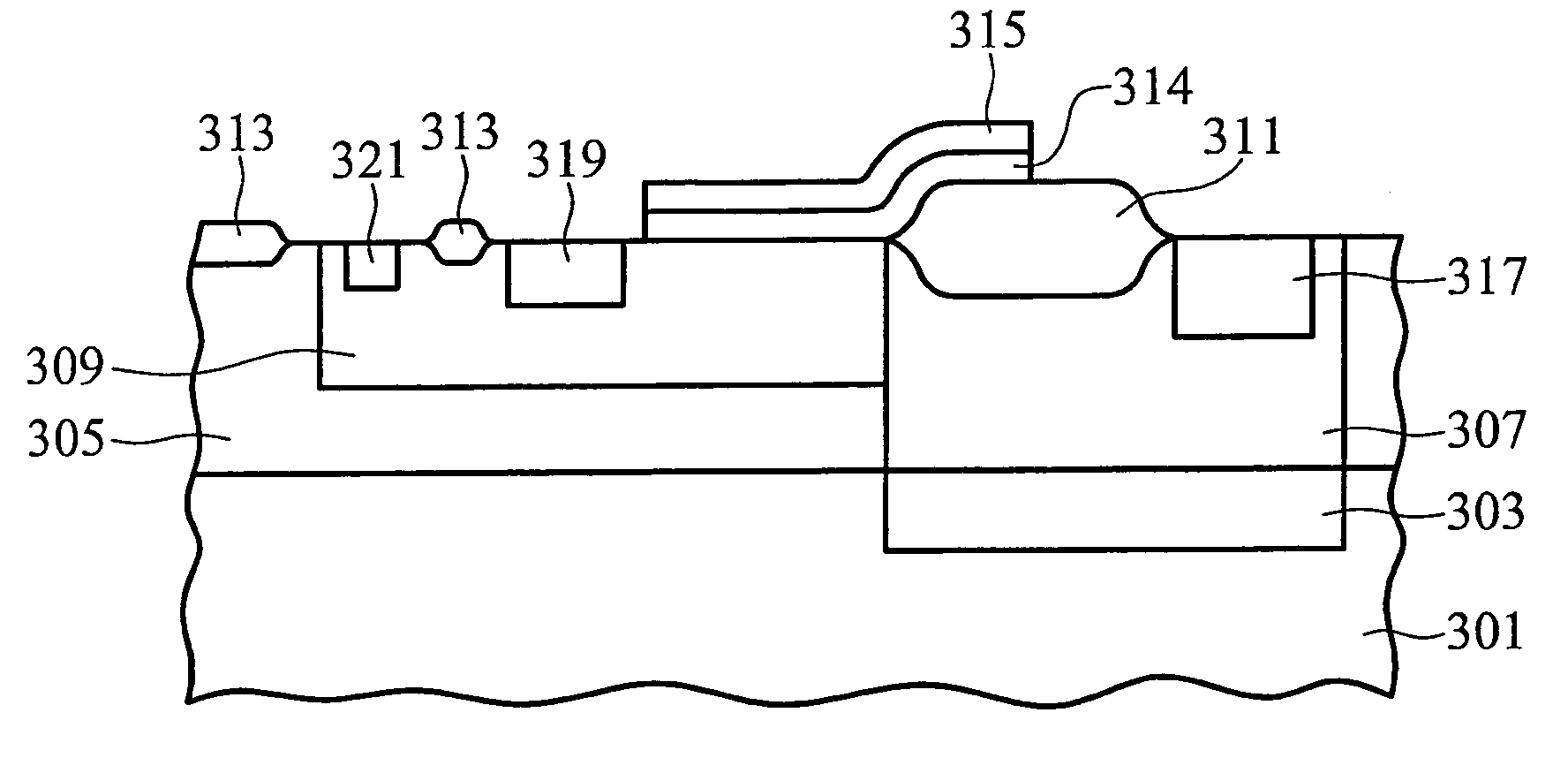

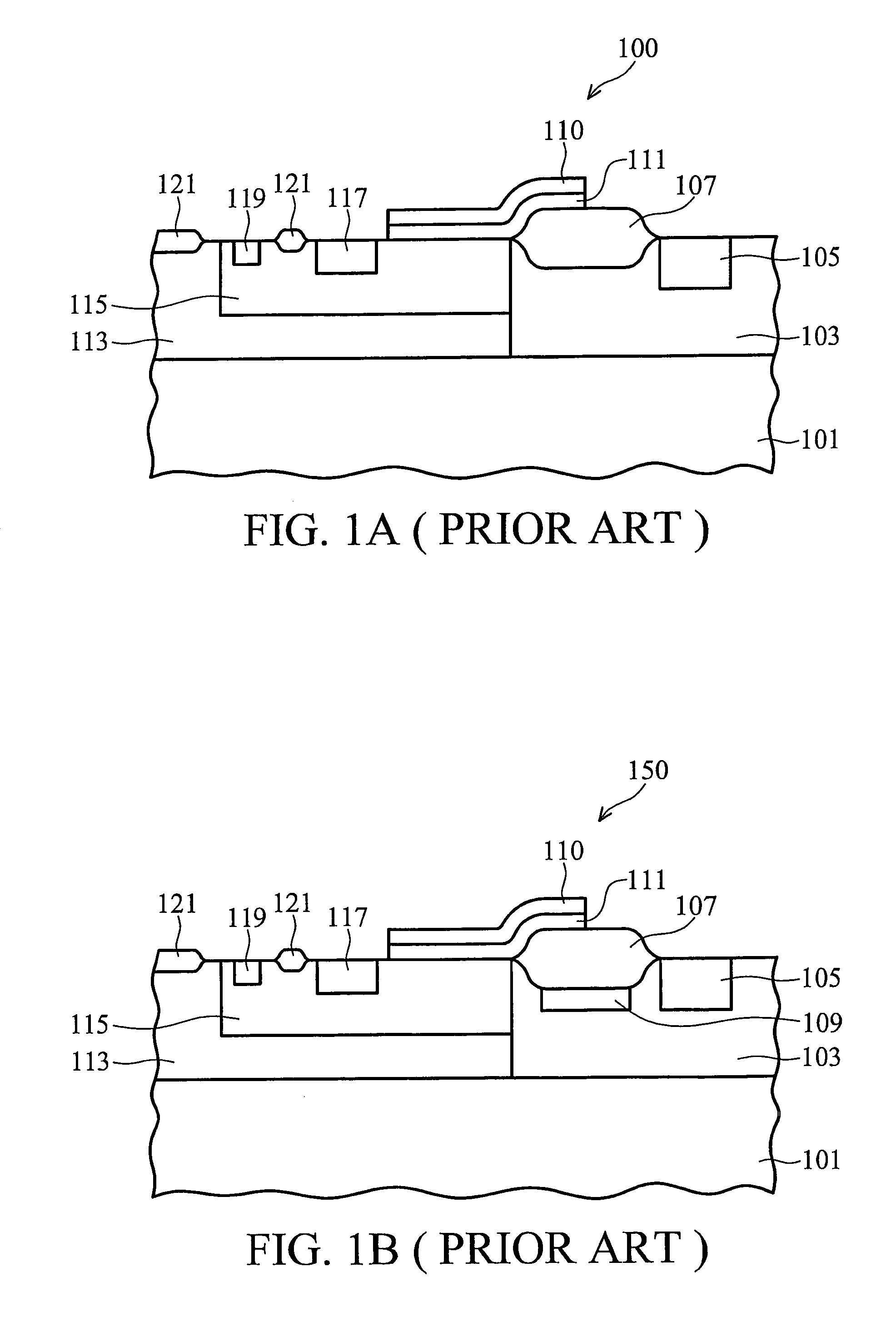

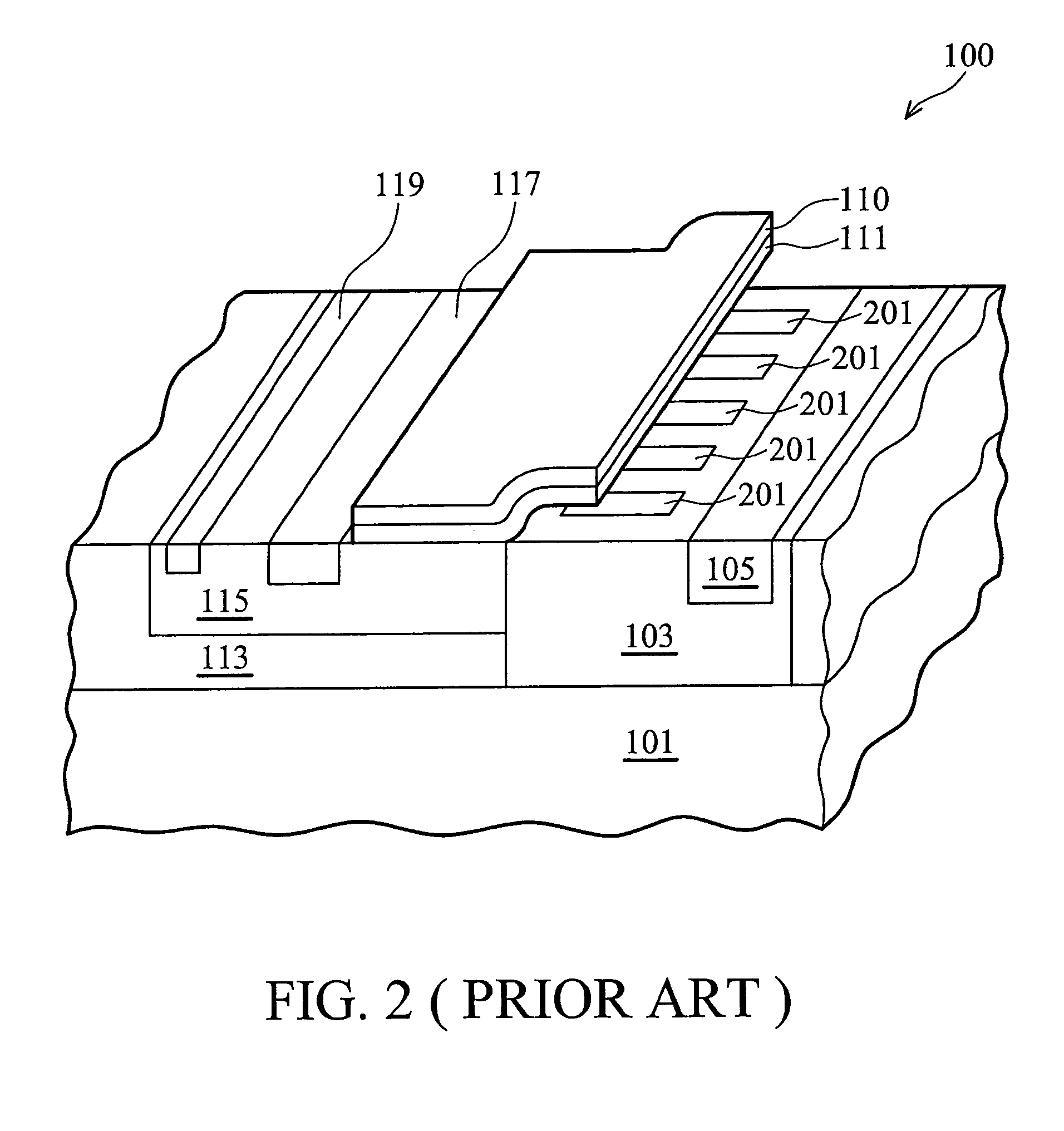

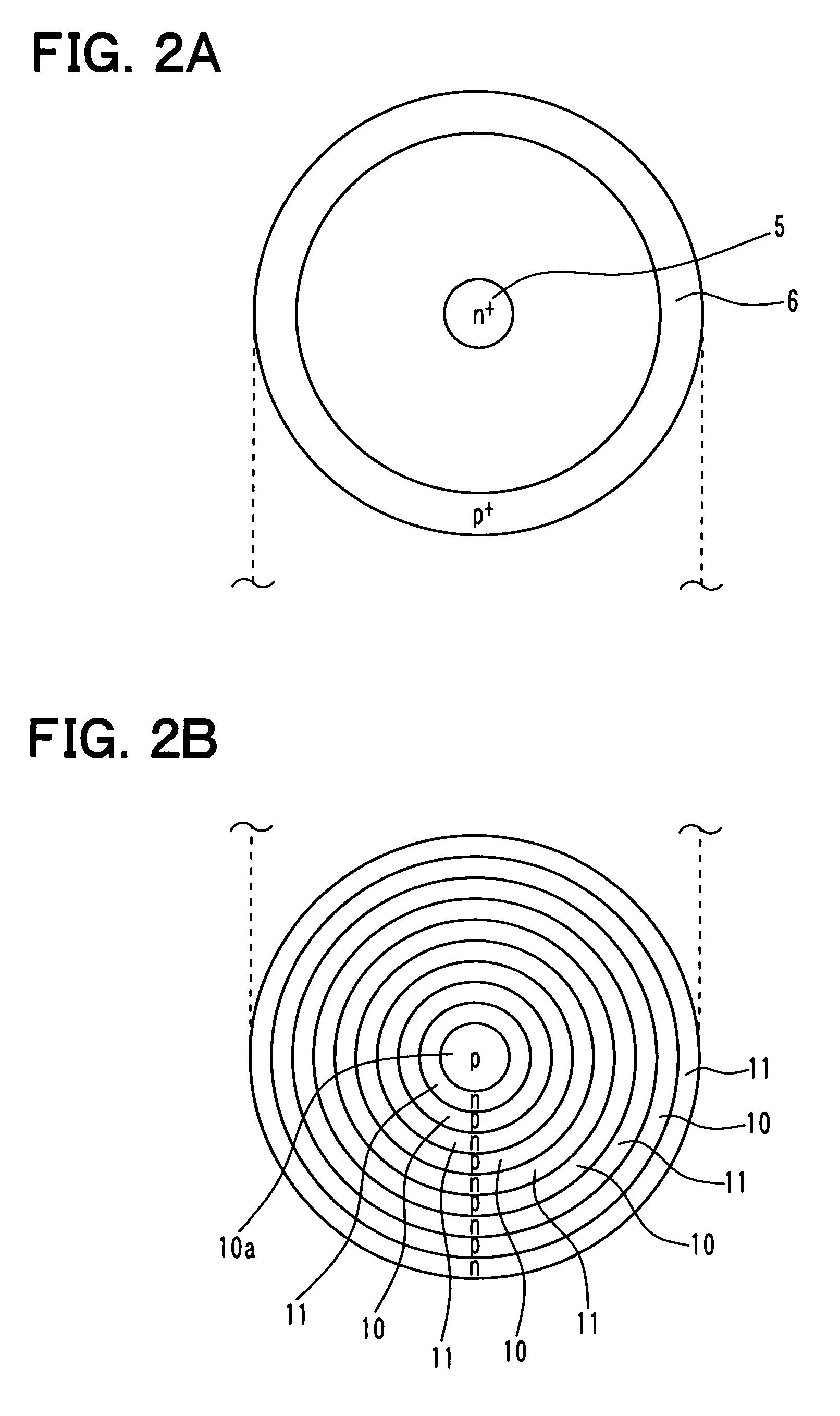

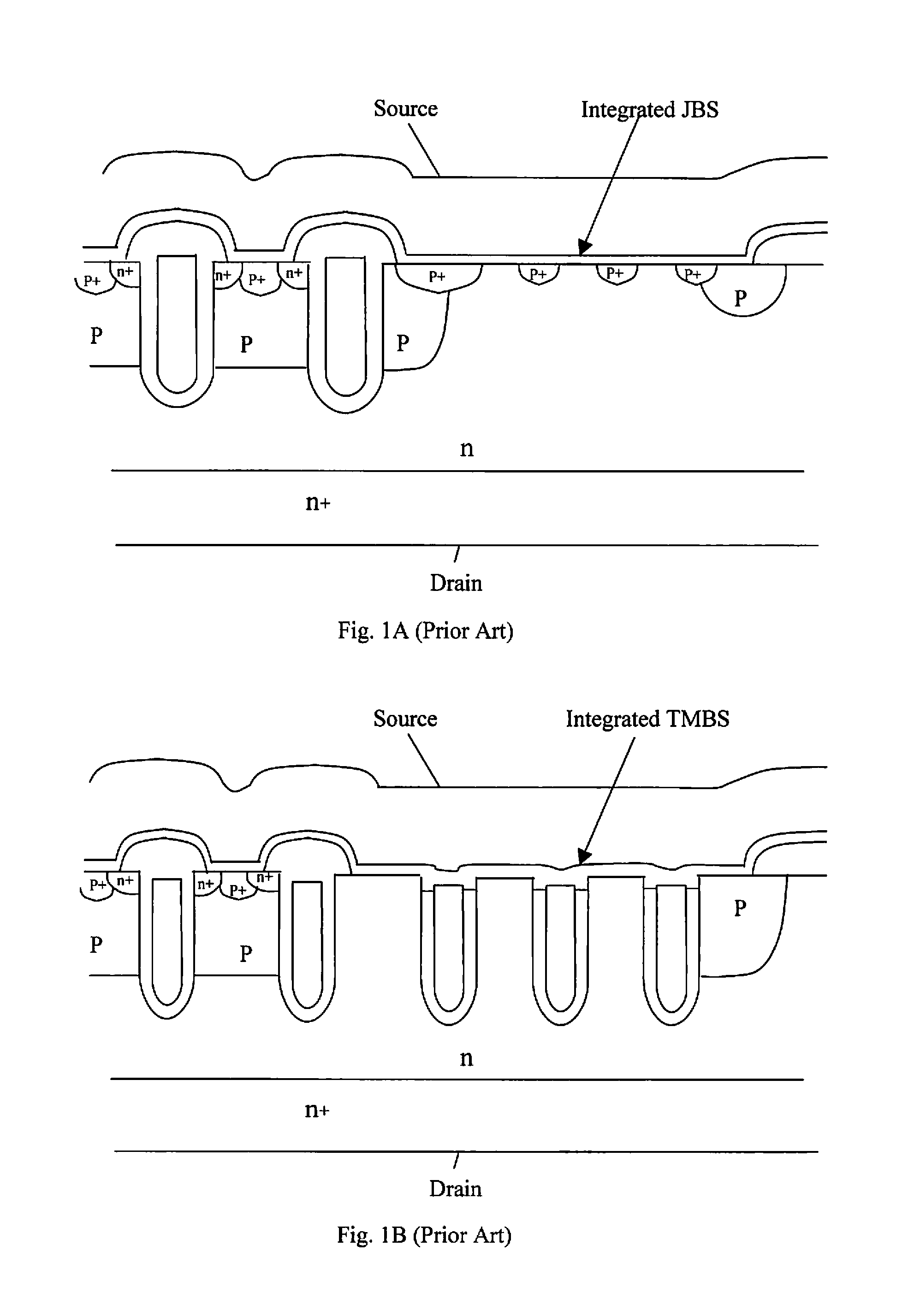

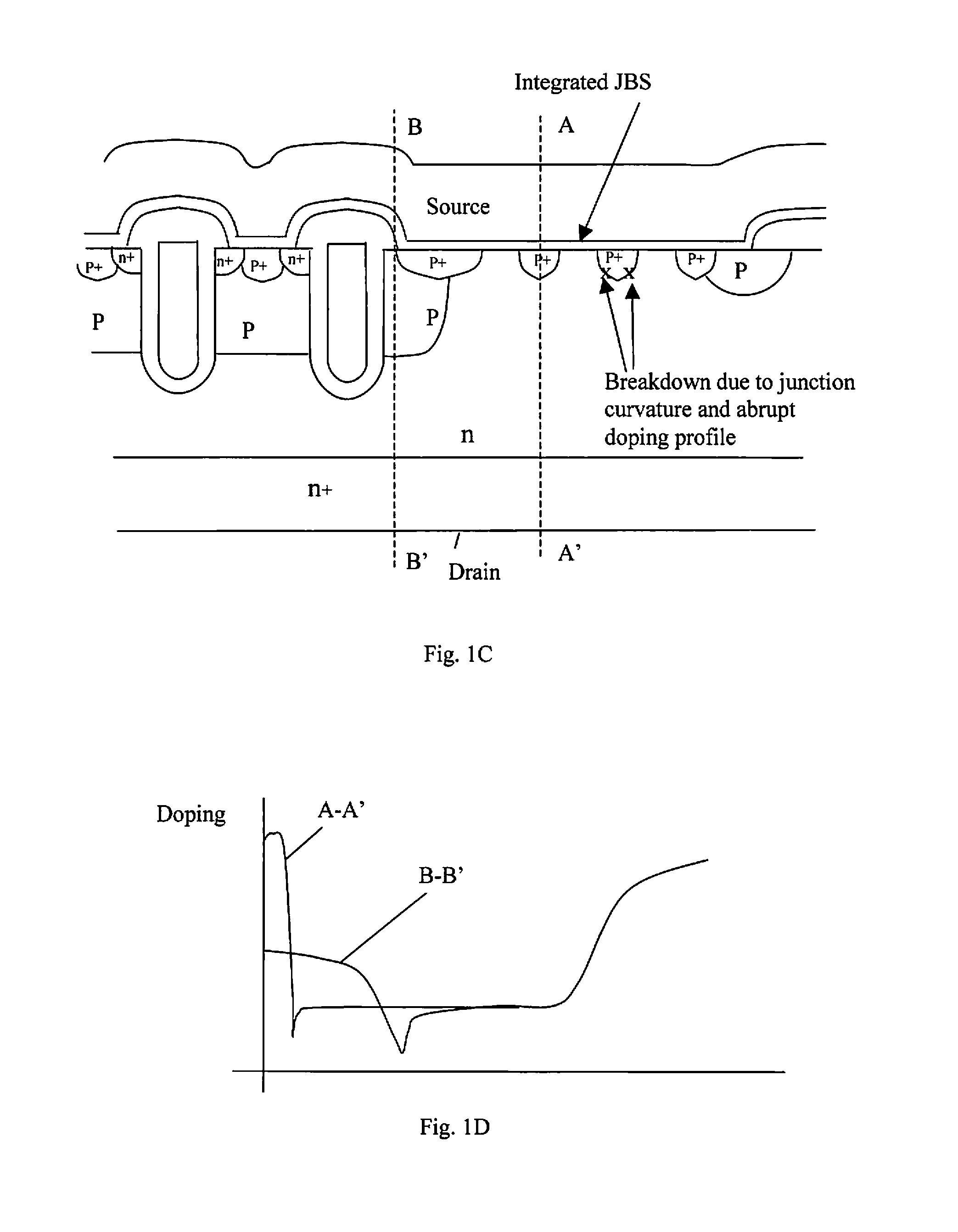

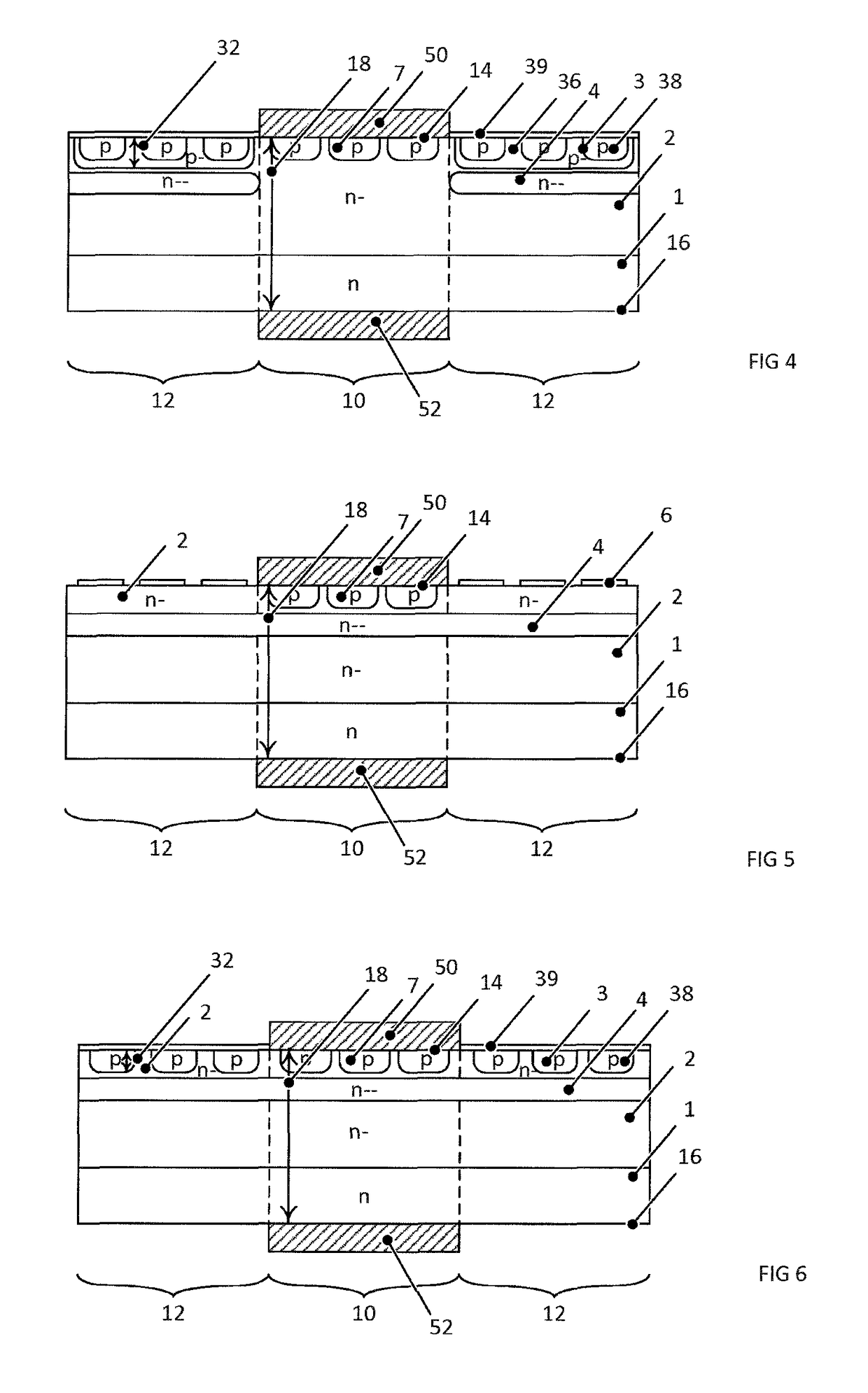

A lateral double diffused MOSFET (LDMOST) incorporates both the reduced surface field (RESURF) and super junction (SJ) in a split-drift region to significantly improve the on-state, off-state and switching characteristics in junction-isolated (JI) technology. The structure effectively suppresses substrate-assisted-depletion which is the main problem encountered when applying the SJ concept to lateral power devices. The device structure features a split-drift region formed of two parts: a SJ structure that extends over most of the drift region, and a terminating RESURF region occupying a portion of the drift region next to the drain. The structure offers improved breakdown voltage and reduced specific on resistance as compared to convention structures, and is useful in power integrated circuits suitable for a variety of applications including flat plasma panel display, automotive electronics, motor control, power supply and high voltage lamp ballasts.

Owner:SALAMA C ANDRE T +1

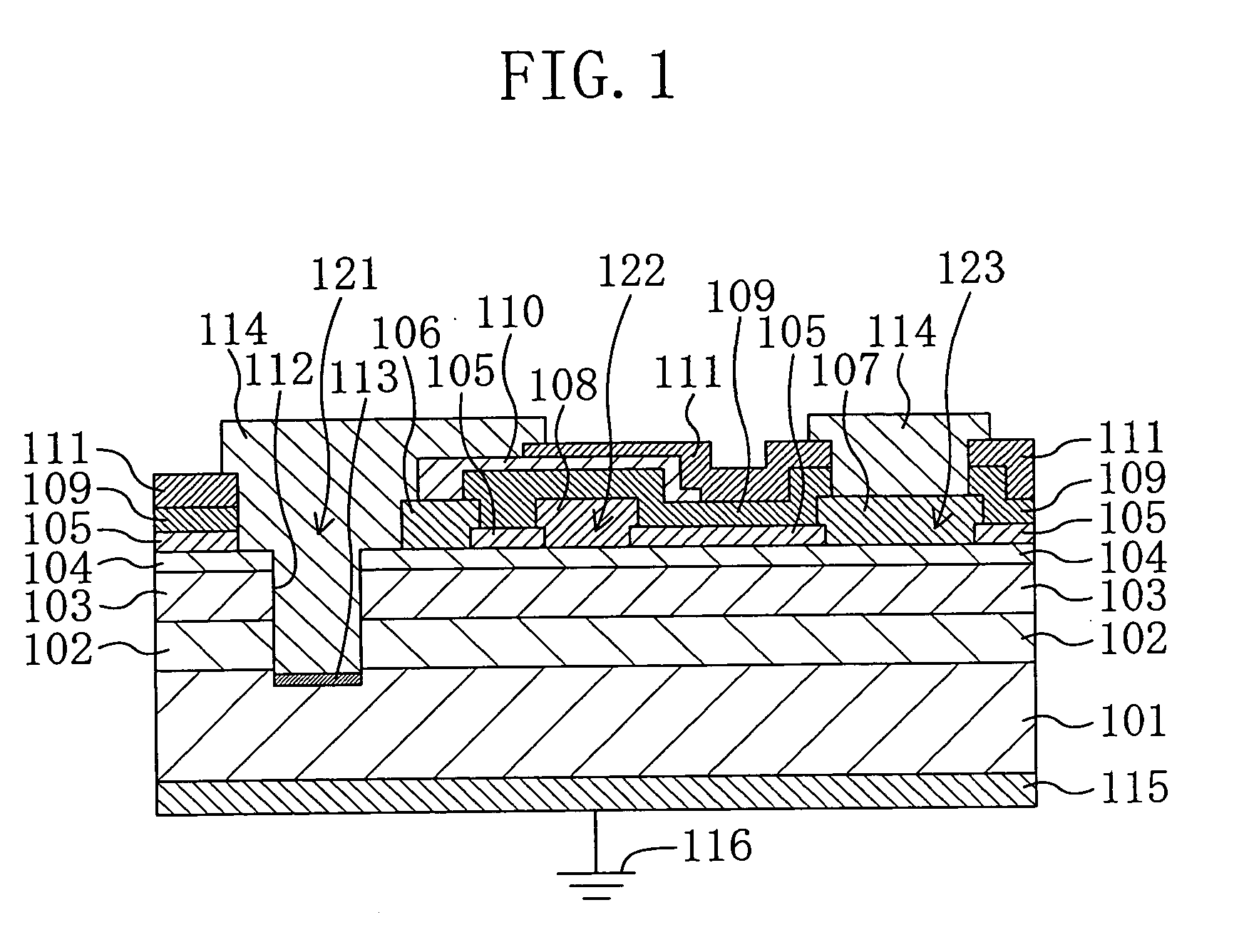

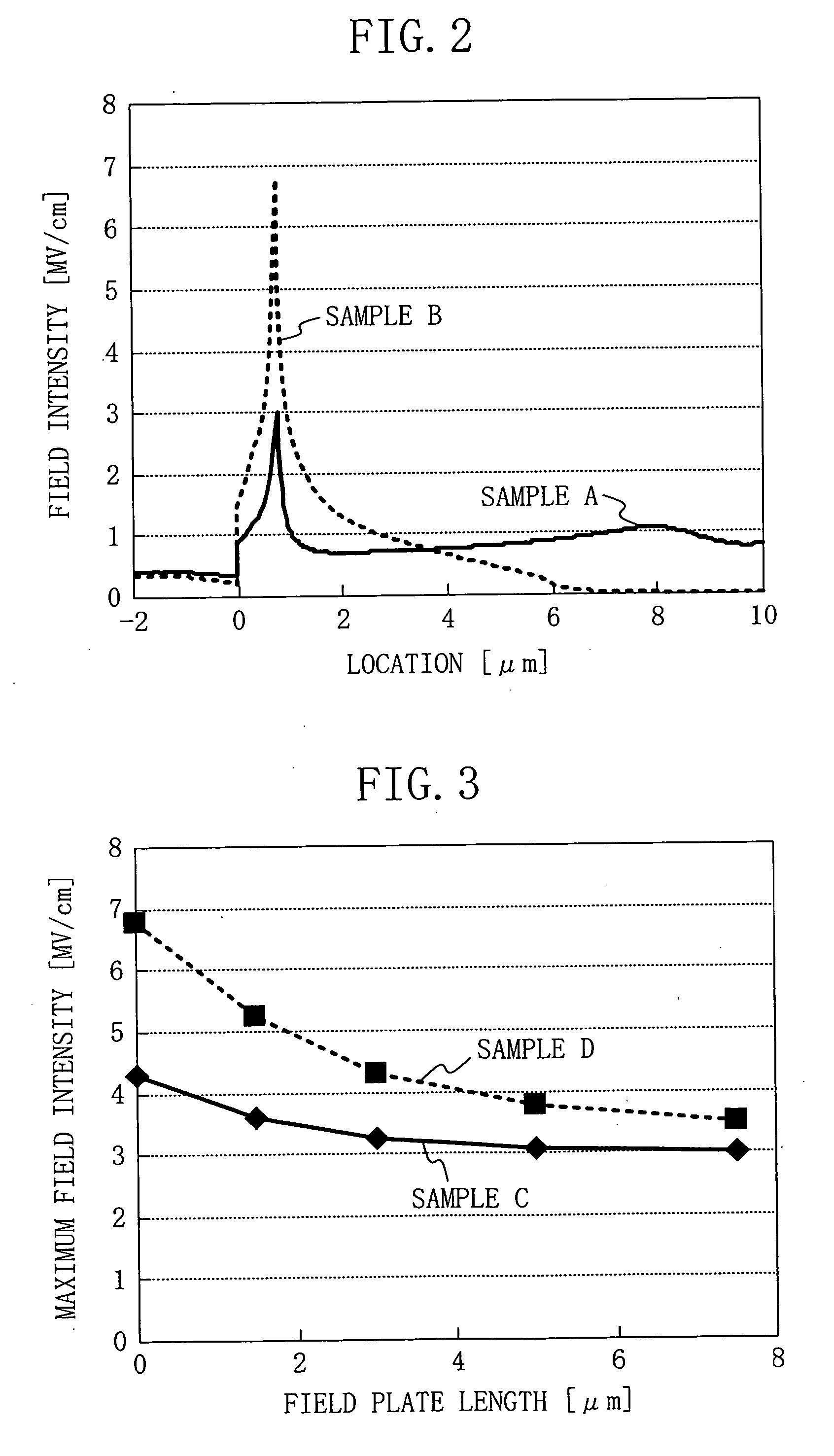

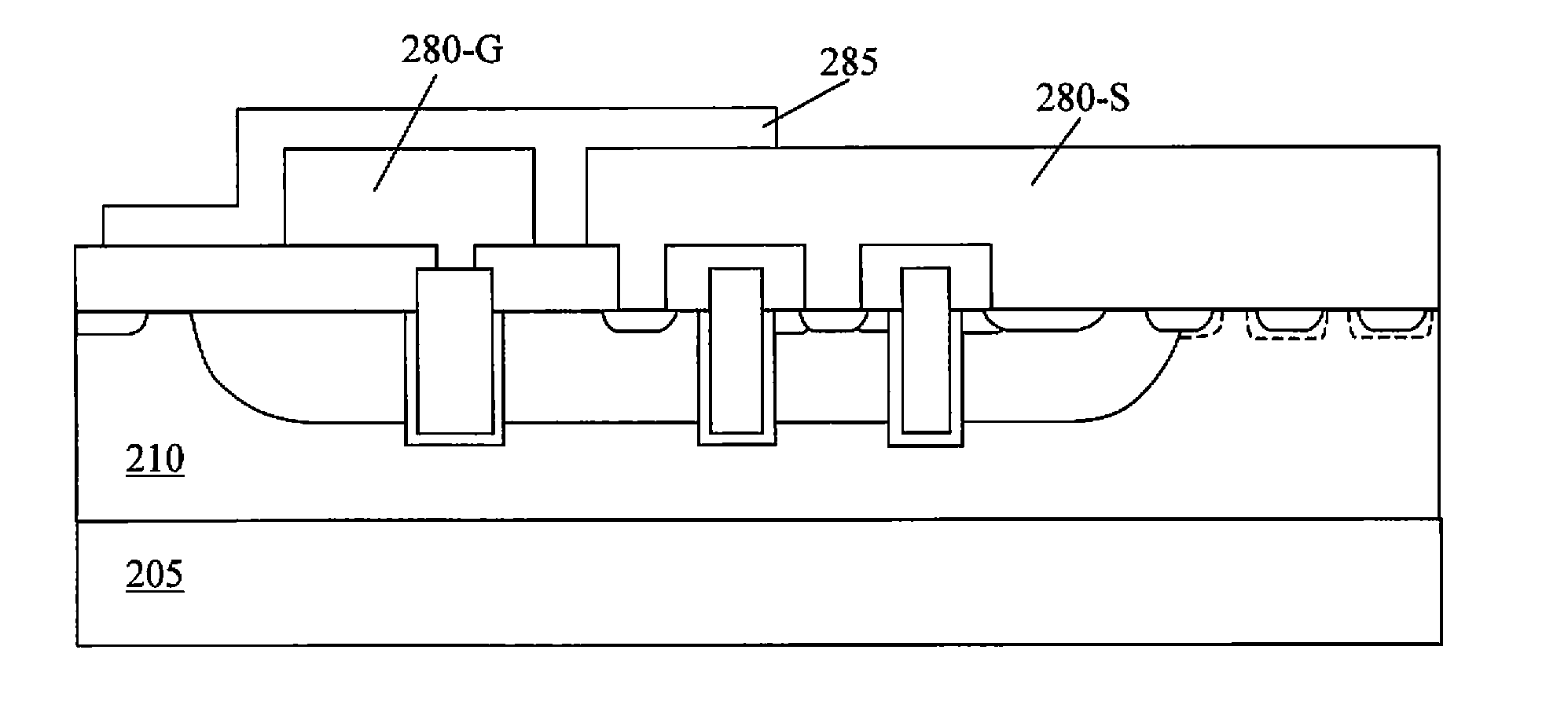

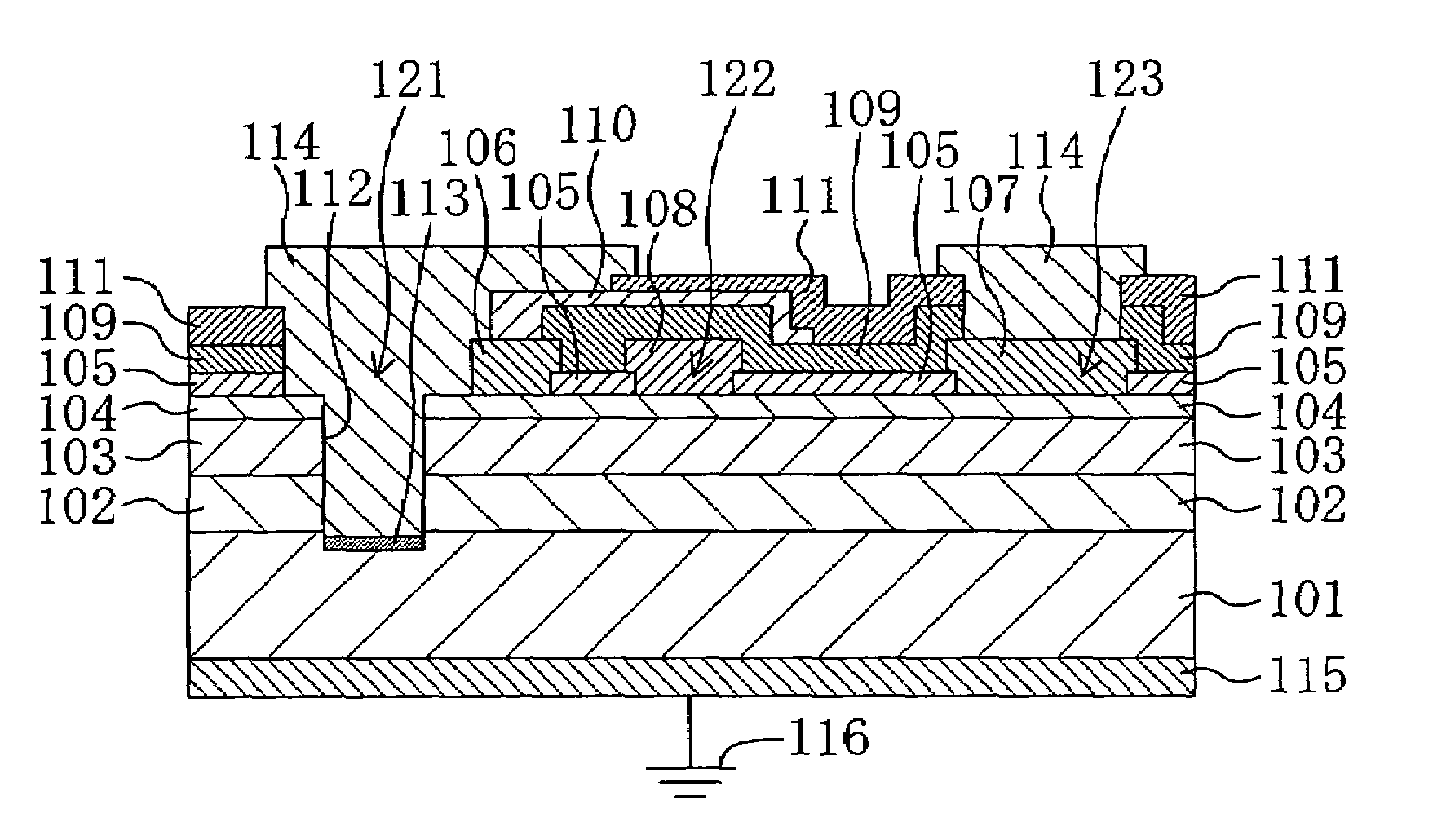

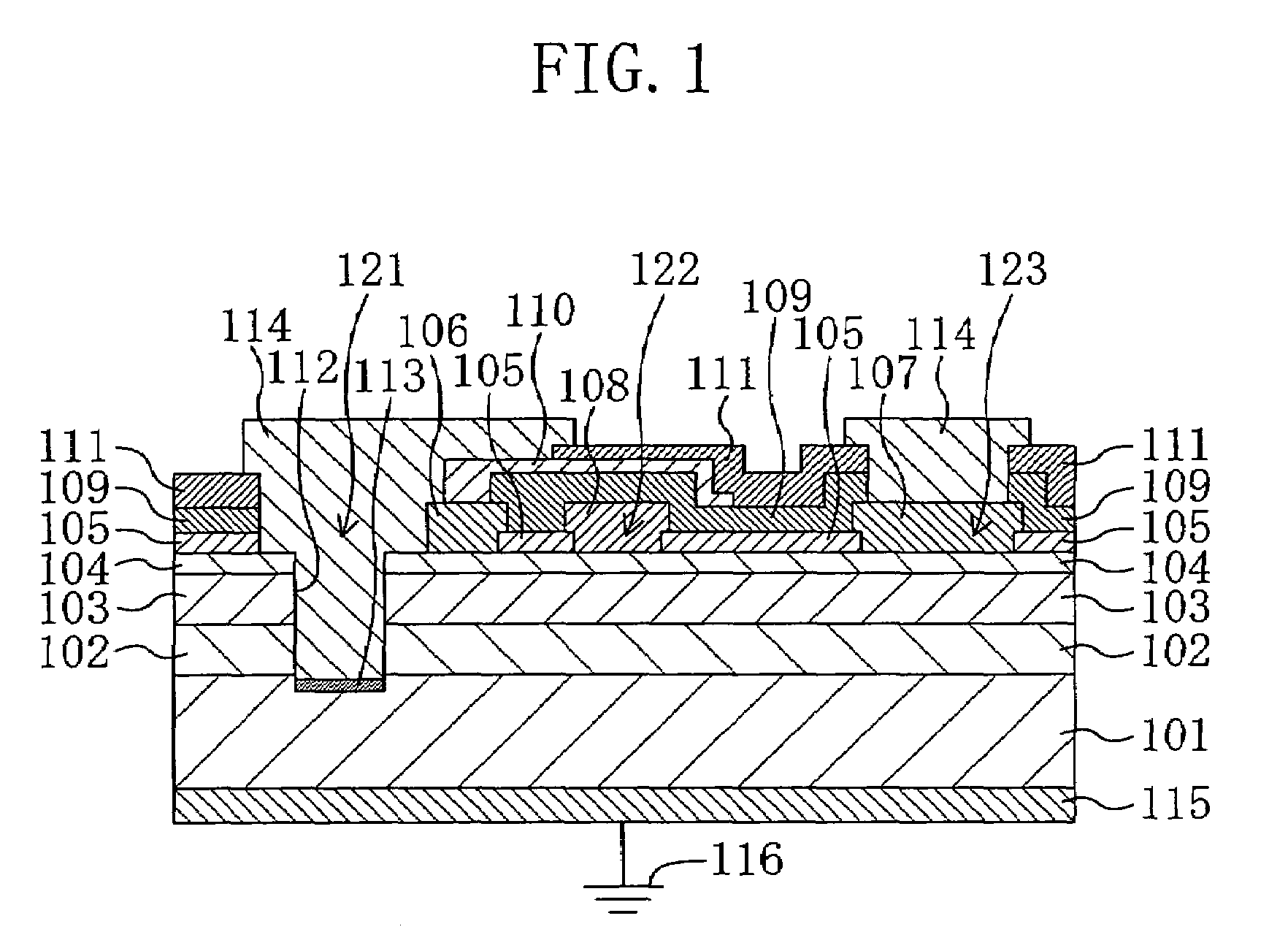

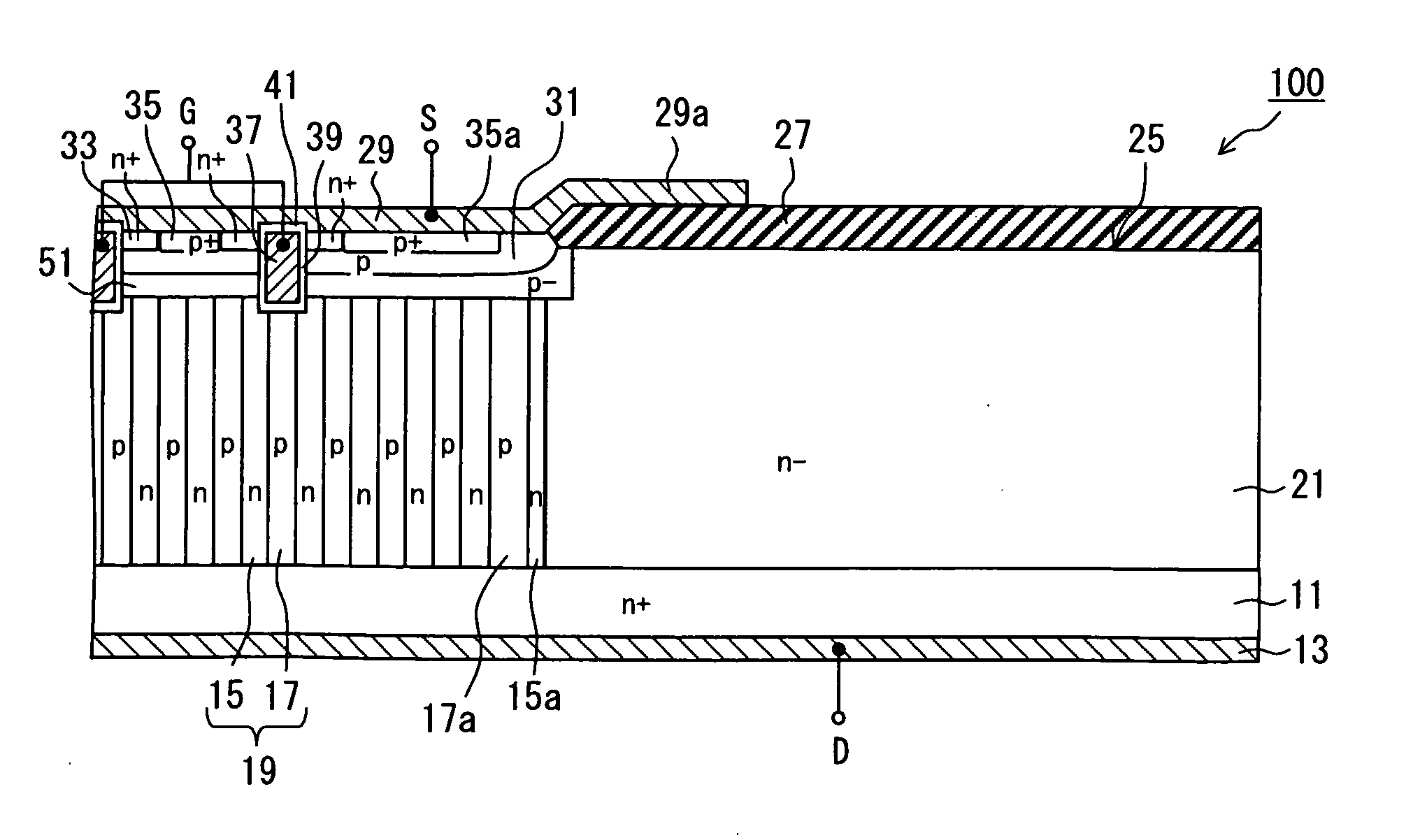

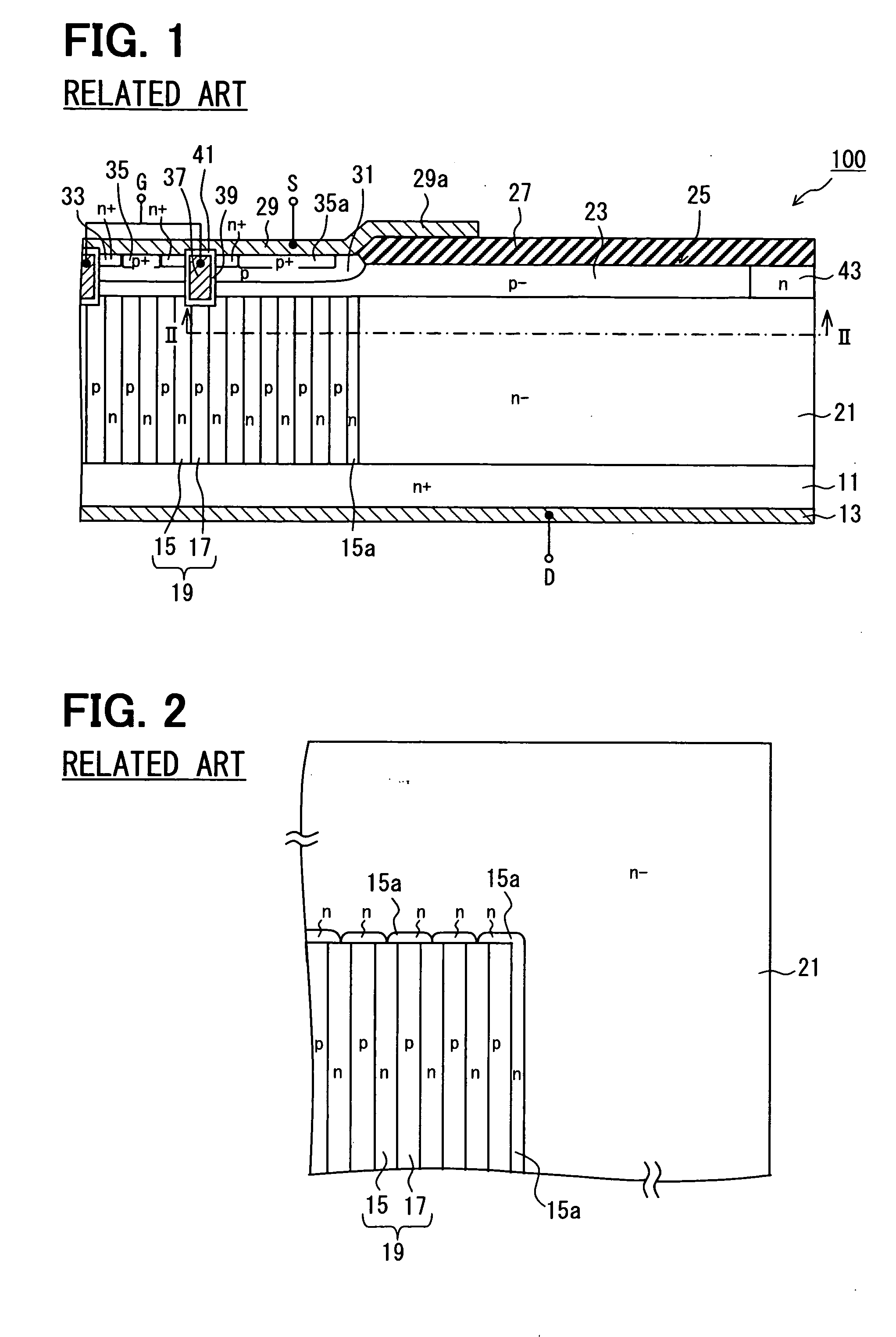

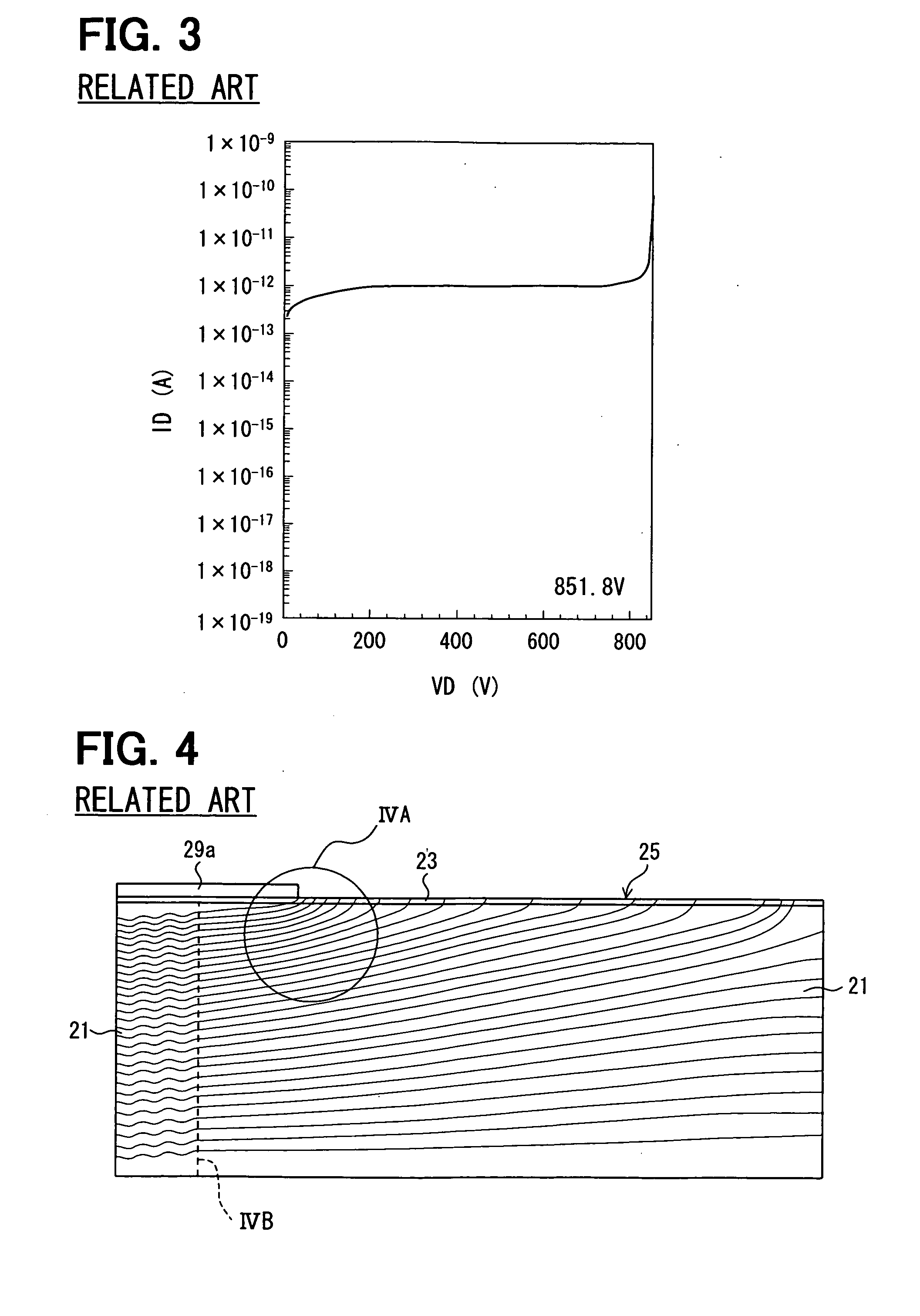

Semiconductor device and method for fabricating the same

ActiveUS20060060895A1Improve breakdown voltagePromote formationTransistorSemiconductor/solid-state device manufacturingDevice materialSemiconductor

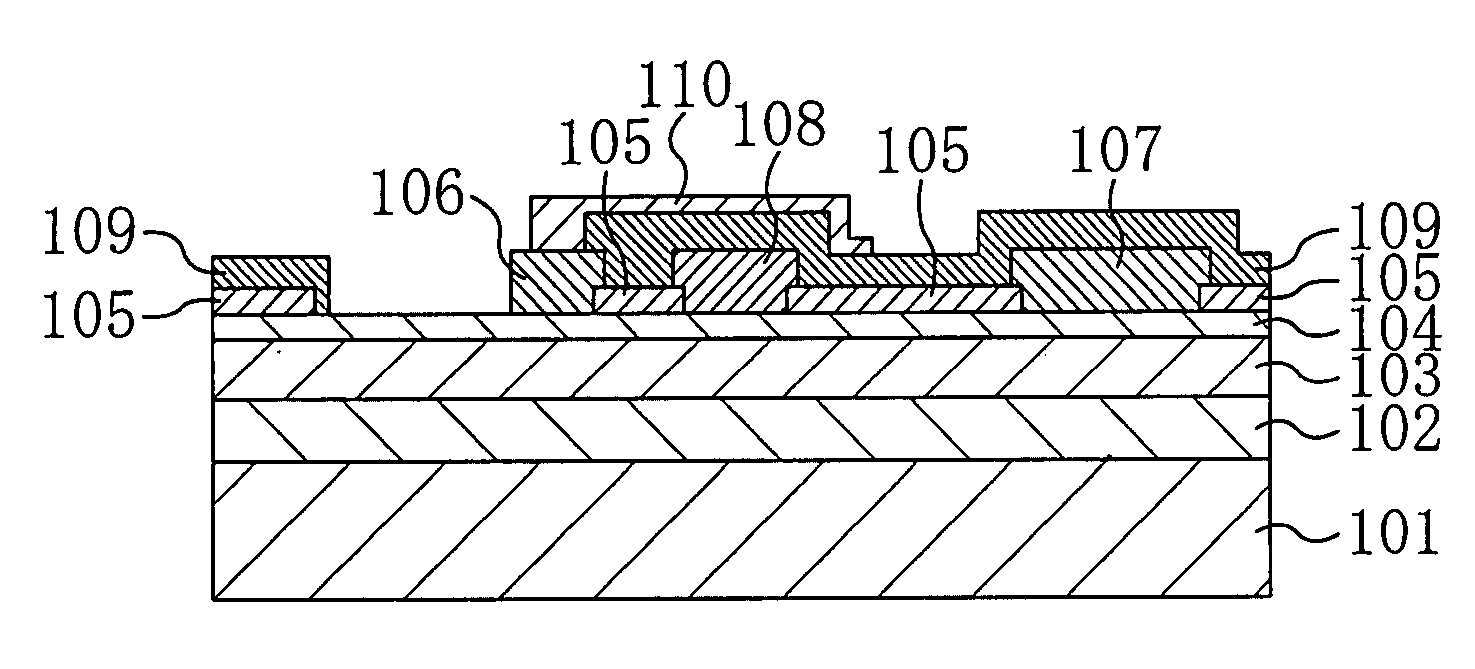

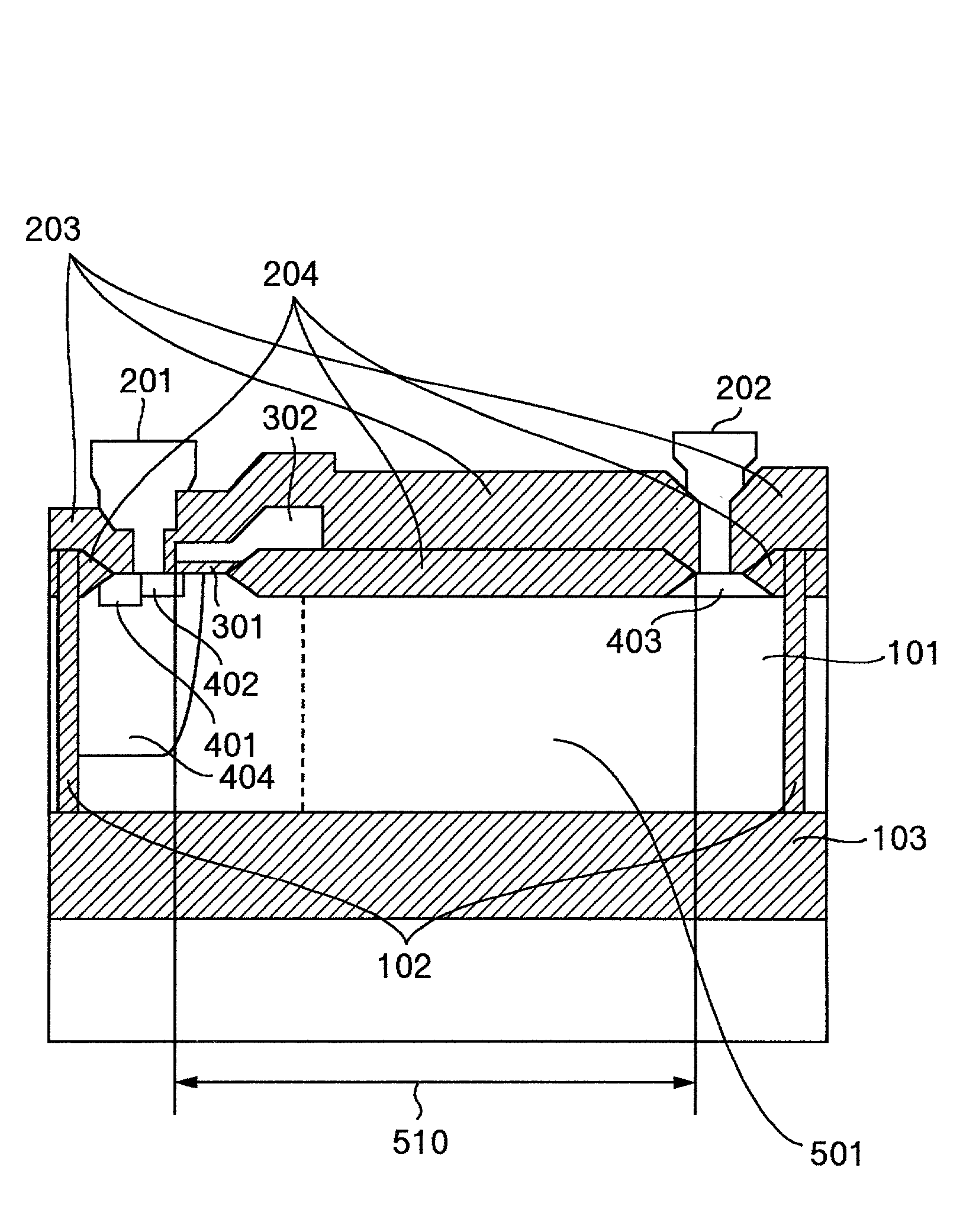

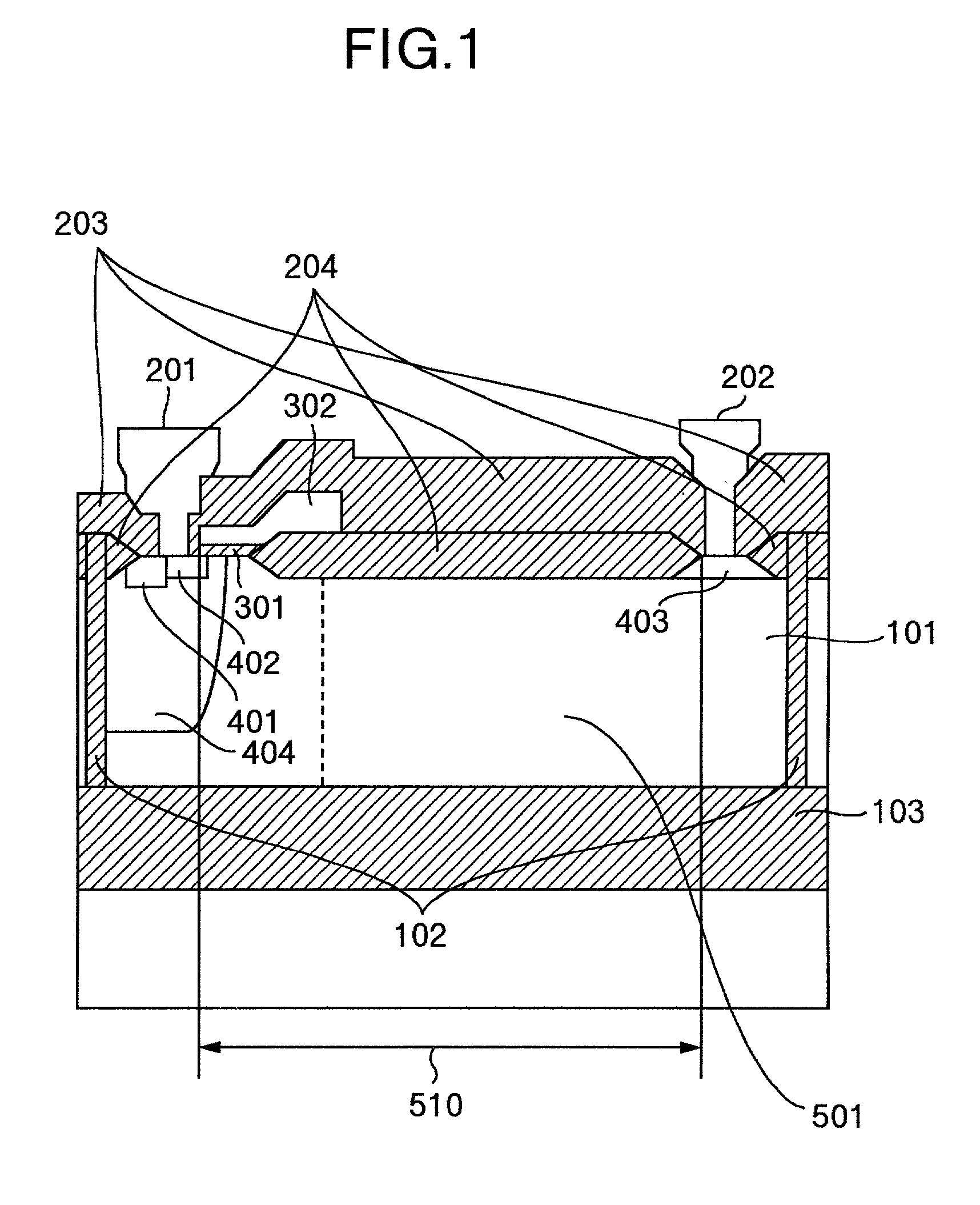

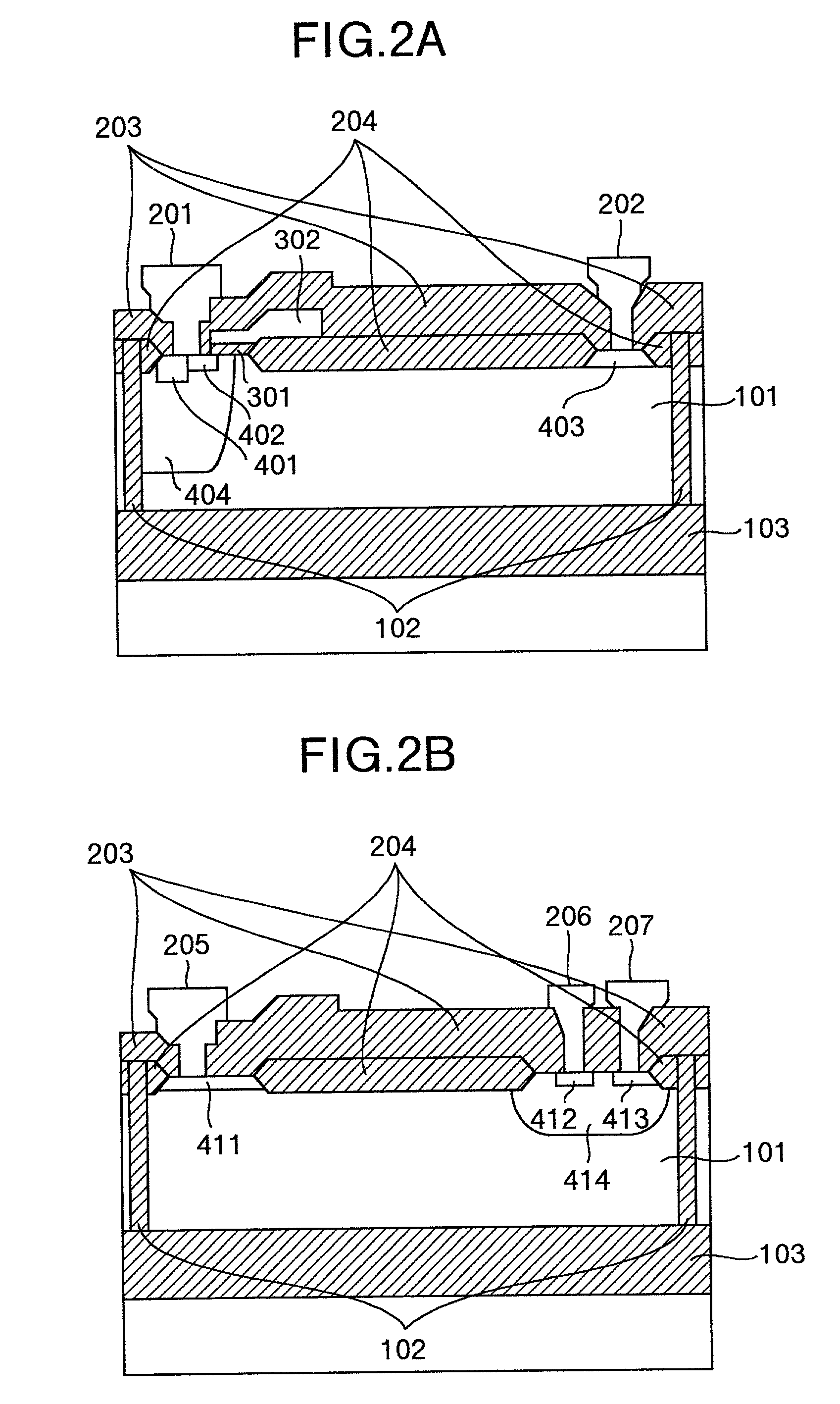

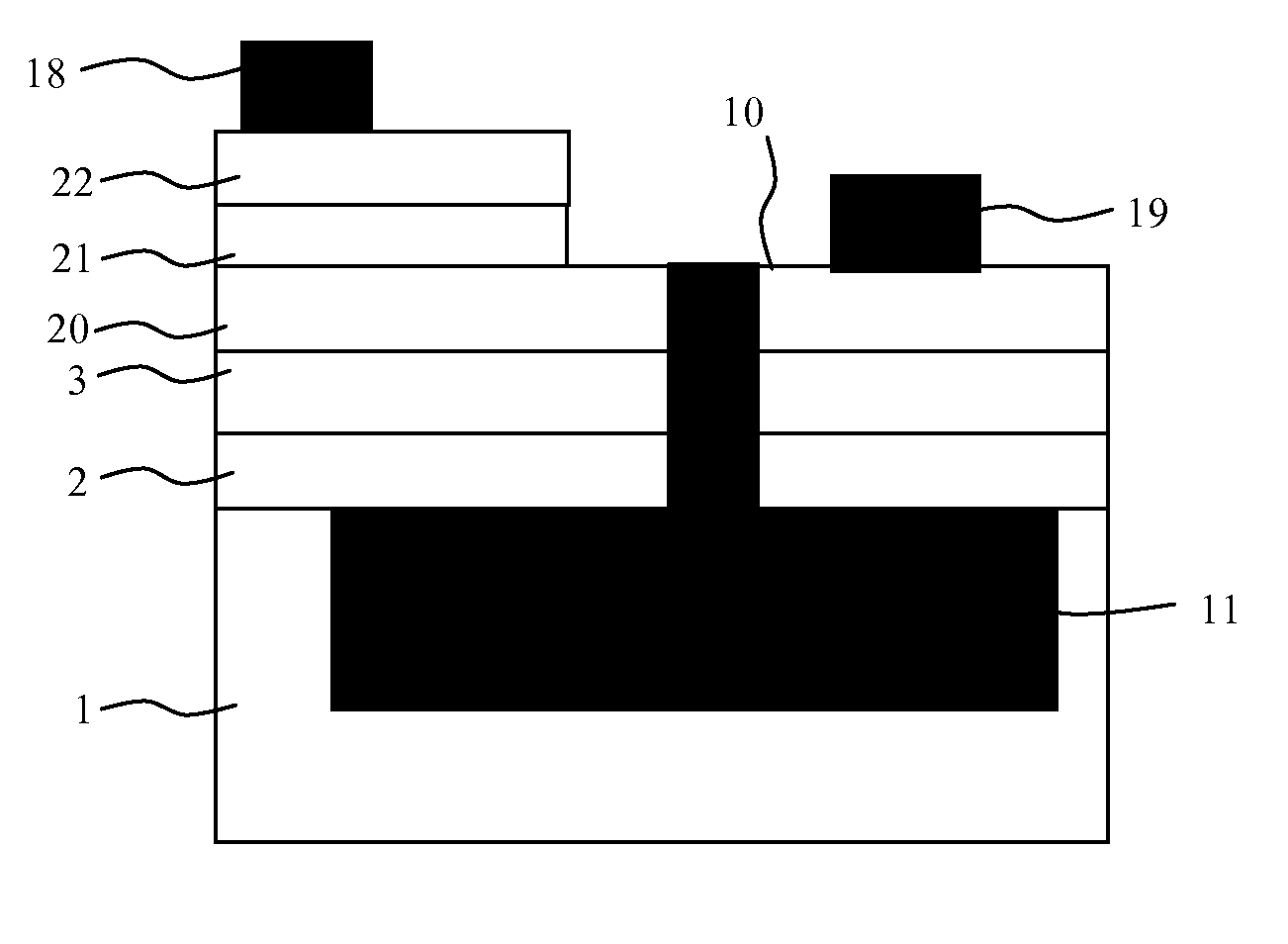

In the structure of a semiconductor device of the present invention, a first source electrode is connected to a conductive substrate through a via hole, and a second source electrode is formed. Thus, even if a high reverse voltage is applied between a gate electrode and a drain electrode, electric field concentration likely to occur at an edge of the gate electrode closer to the drain electrode can be effectively dispersed or relaxed. Moreover, the conductive substrate is used as a substrate for forming element formation layers, so that a via hole penetrating the substrate to reach the backside thereof does not have to be formed in the conductive substrate. Thus, with the strength necessary for the conductive substrate maintained, the first source electrode can be electrically connected to a backside electrode.

Owner:PANASONIC CORP

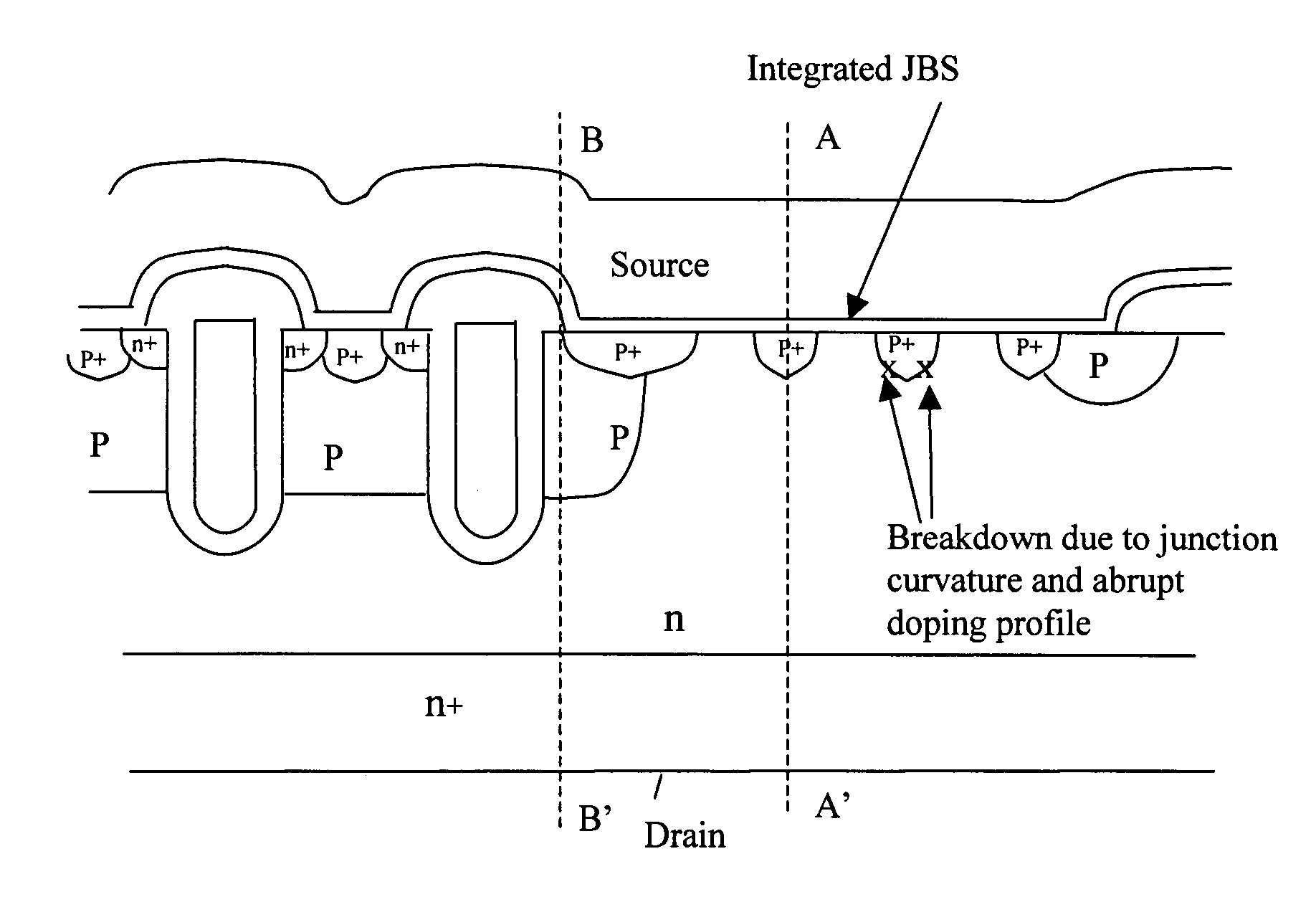

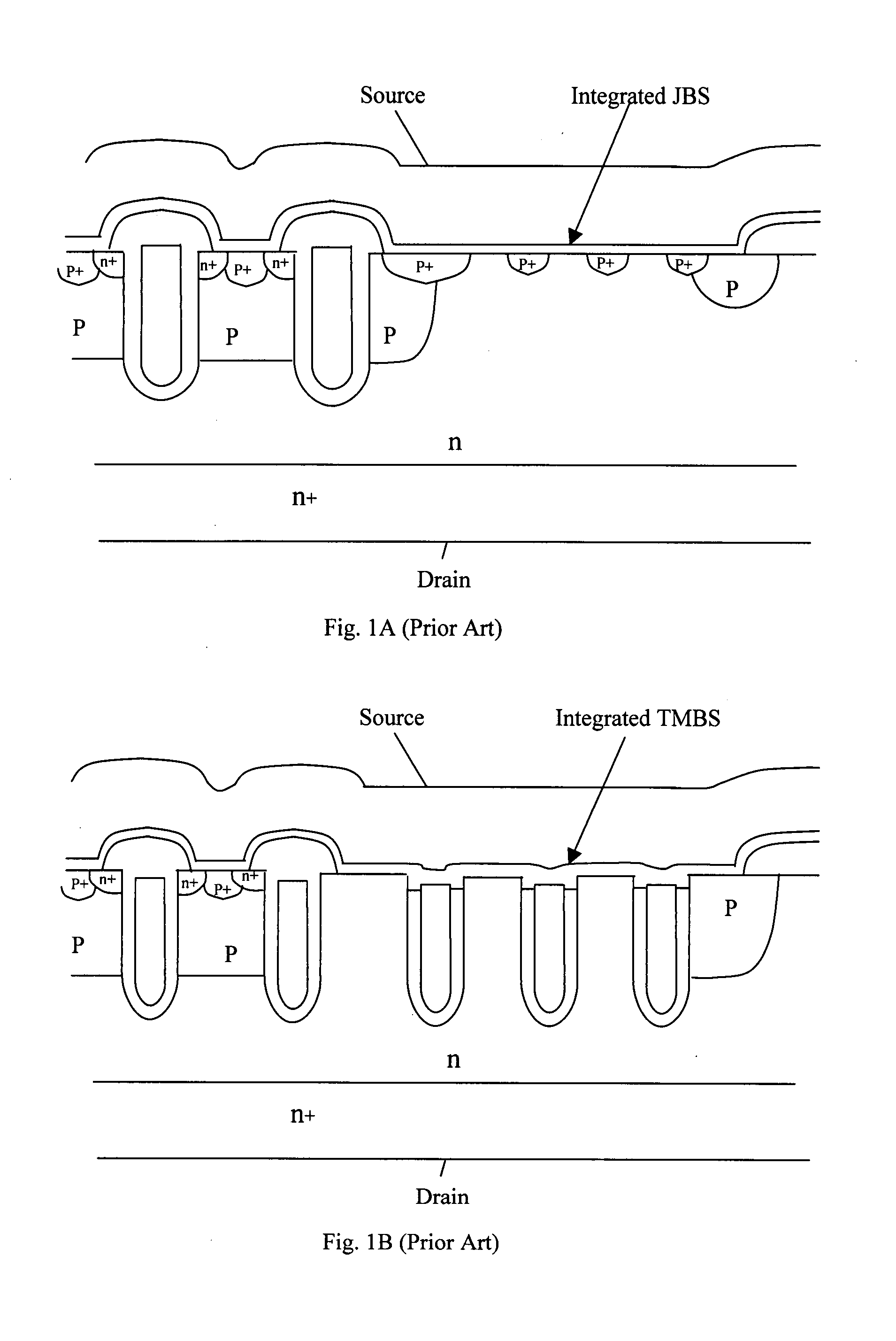

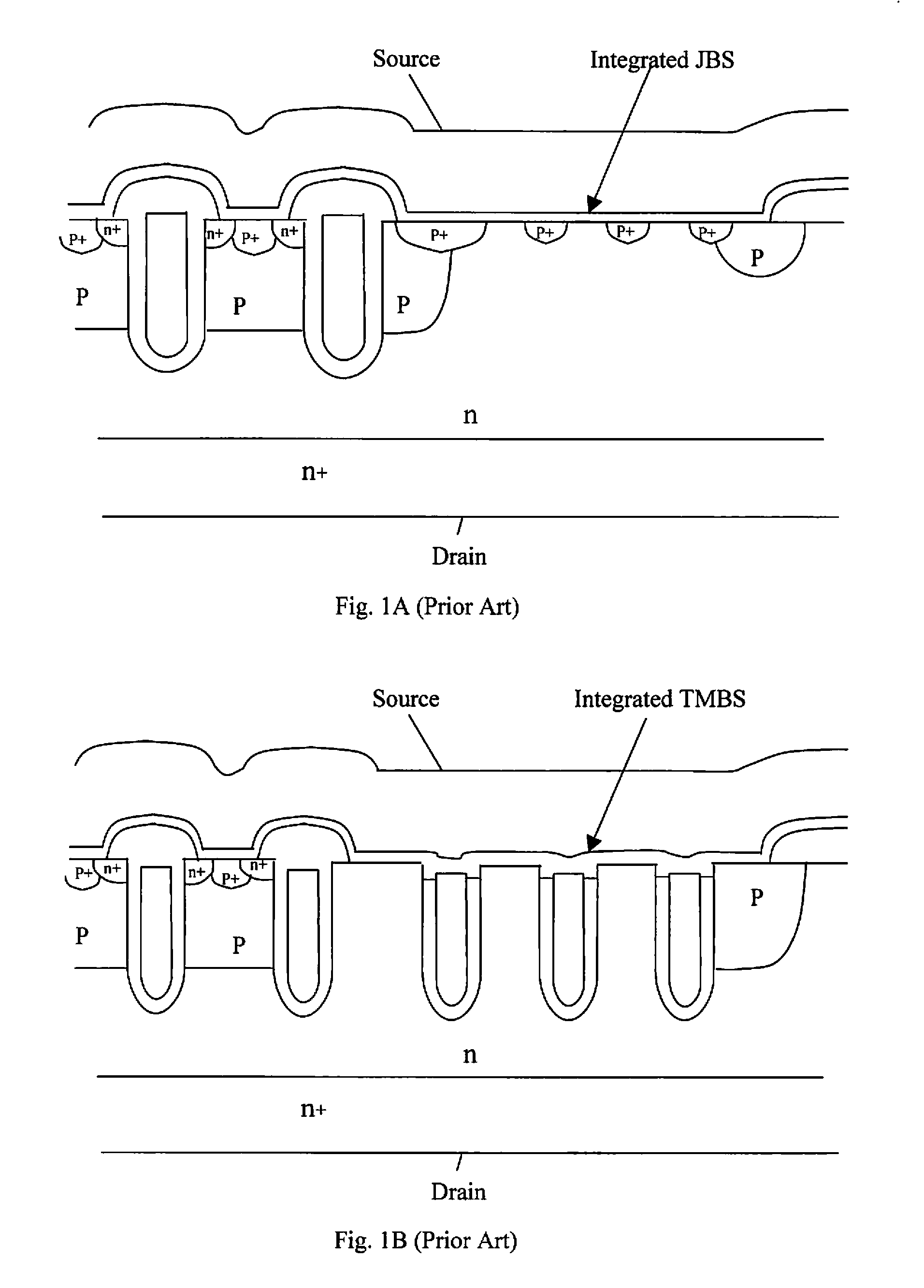

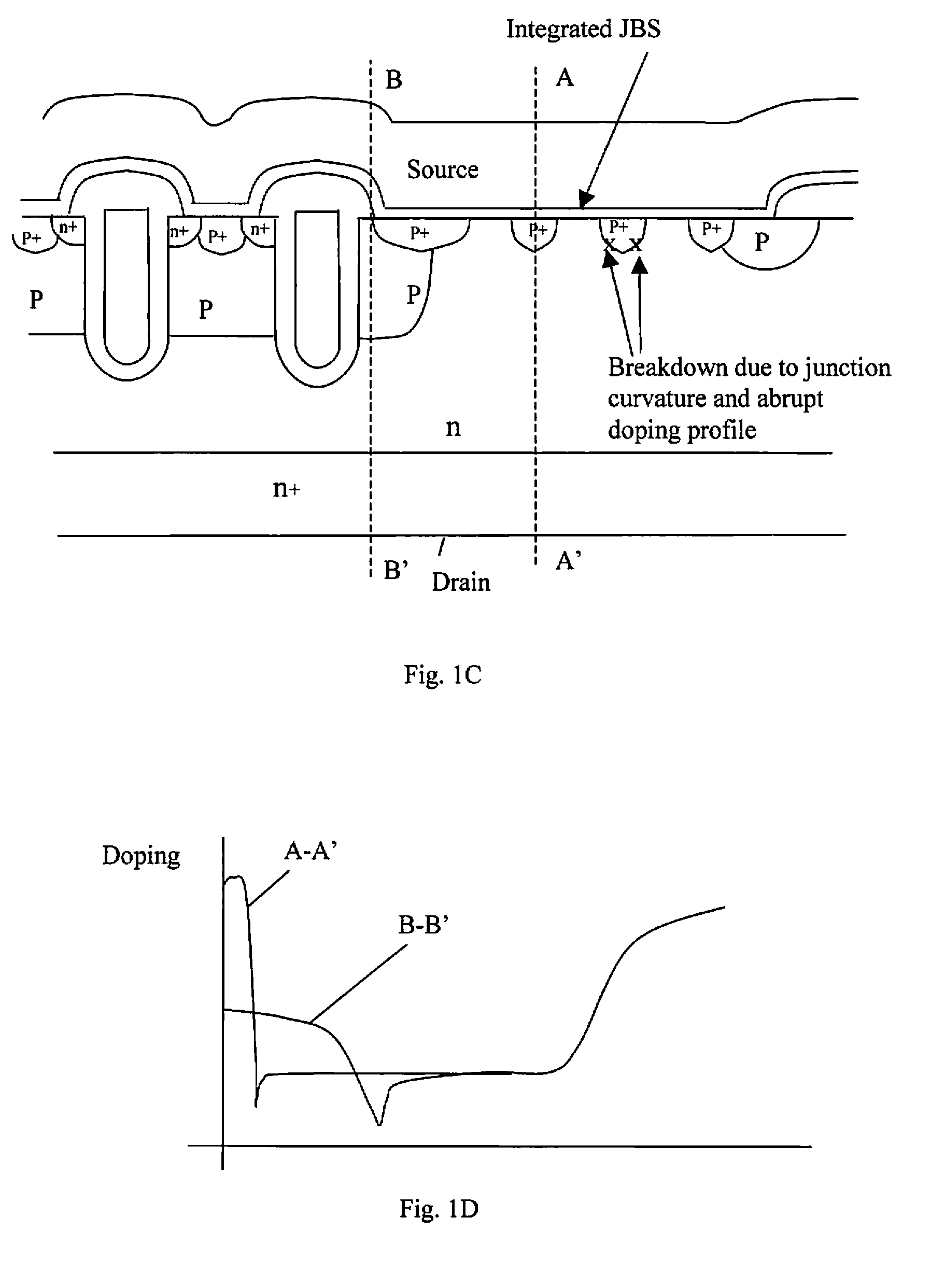

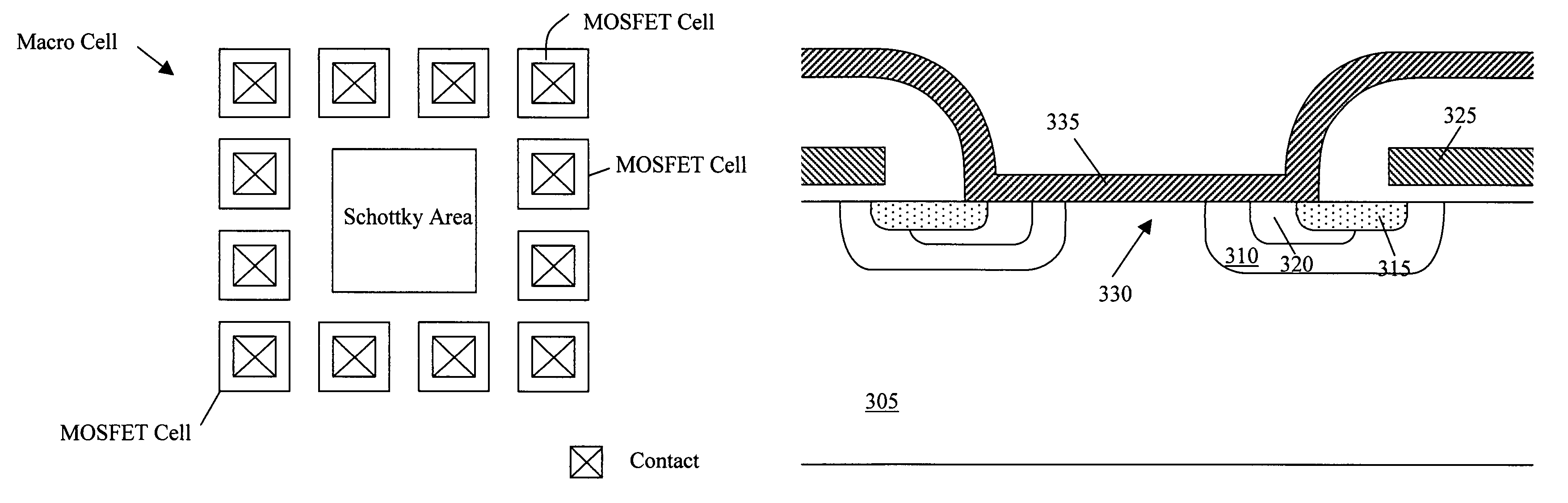

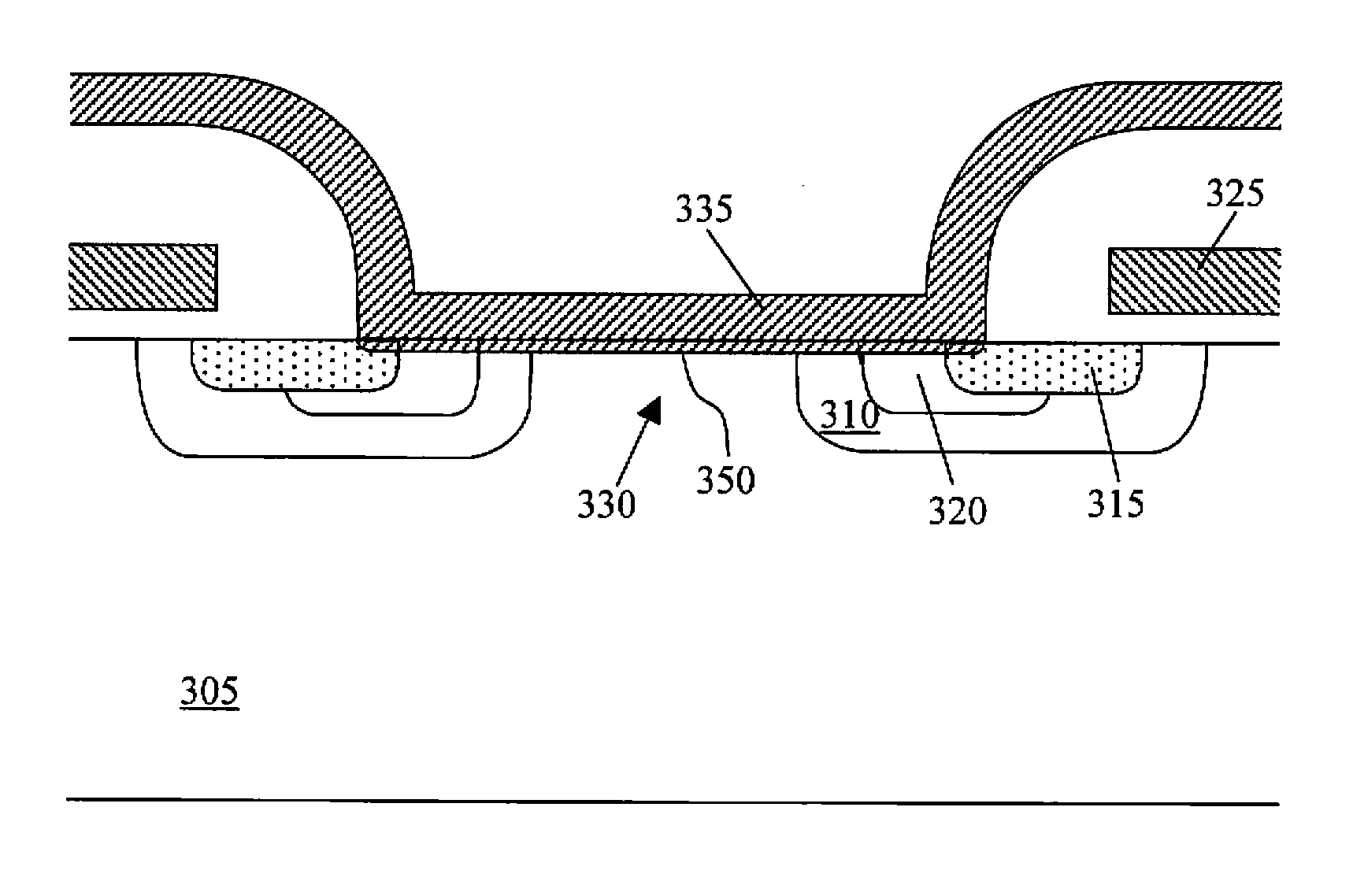

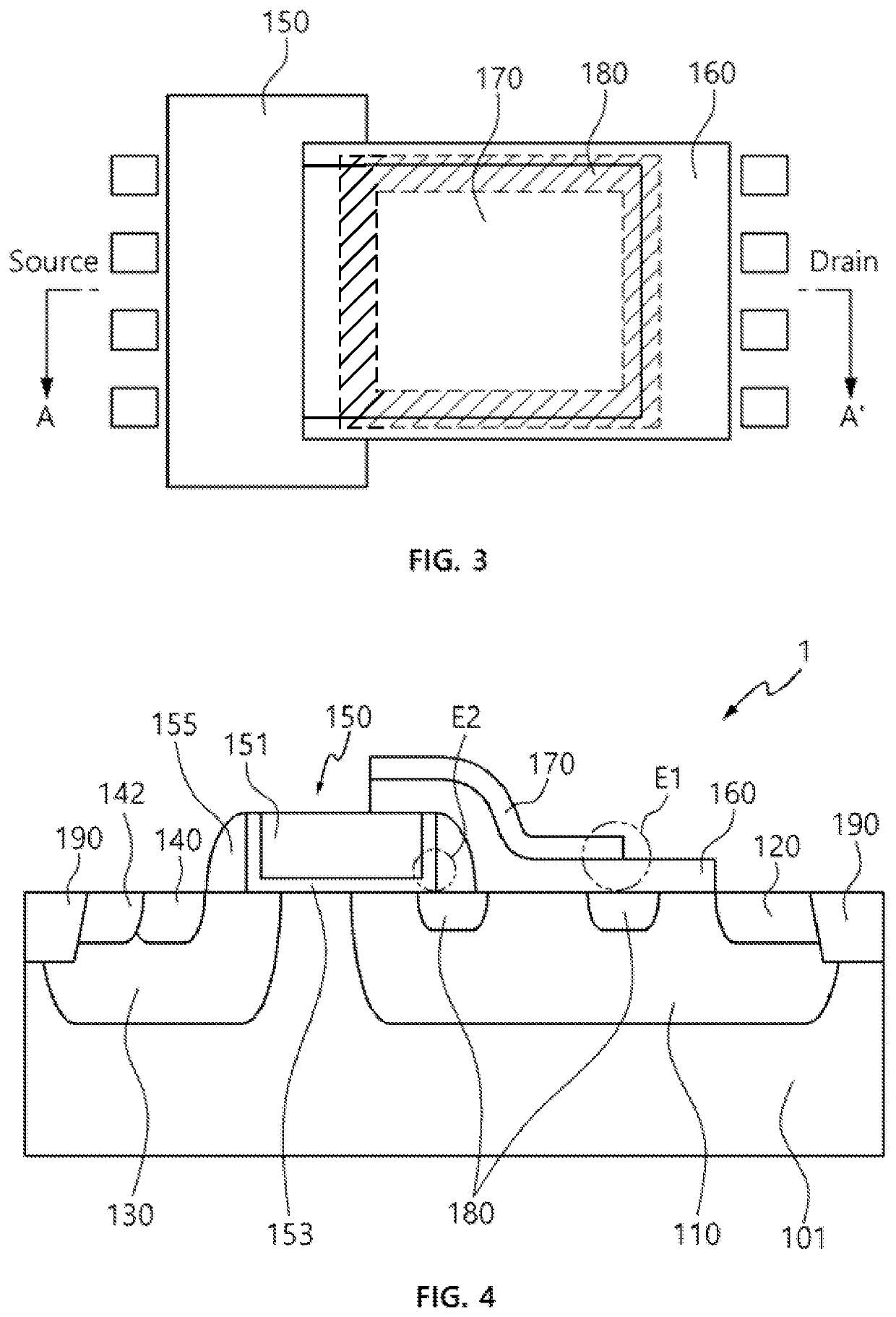

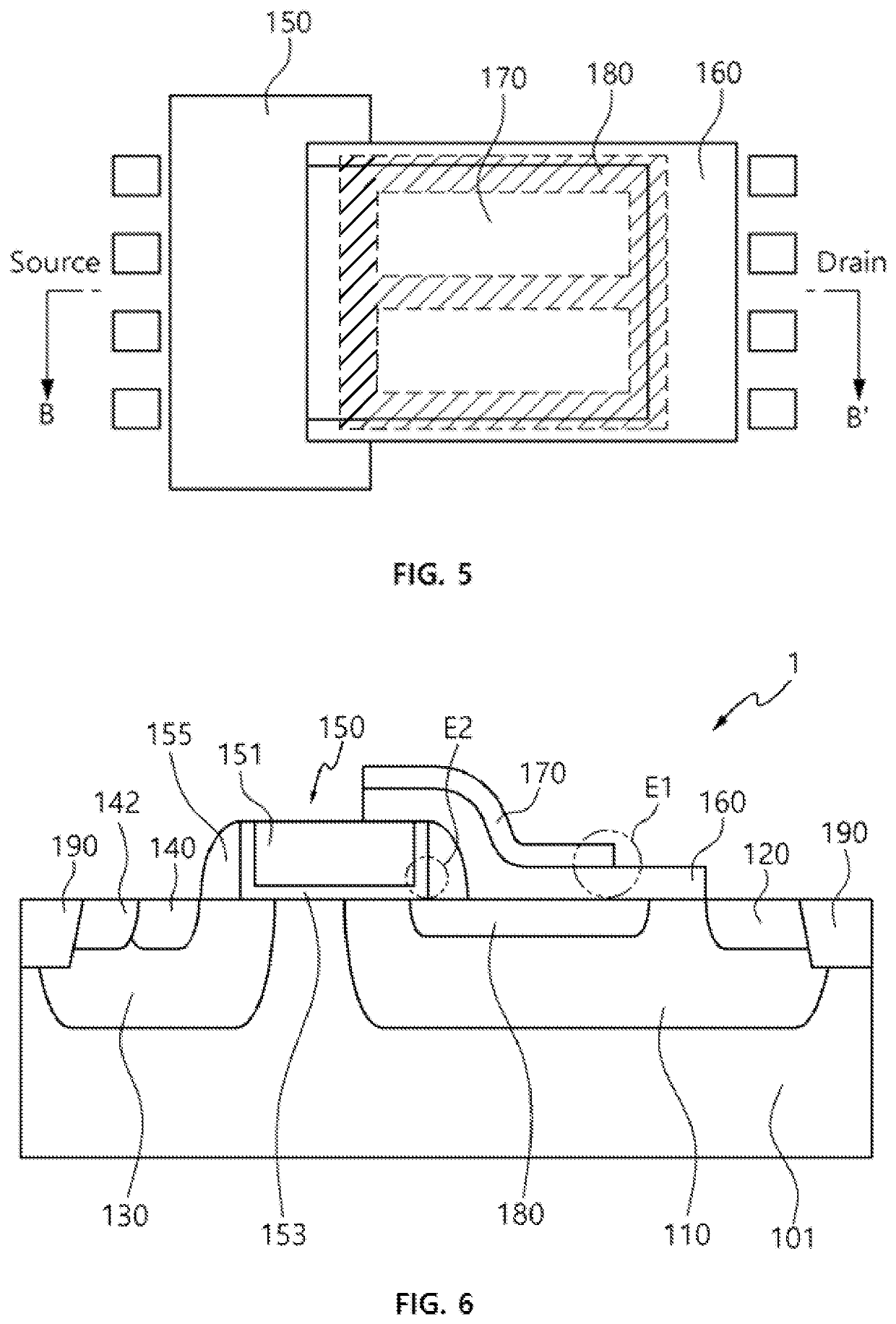

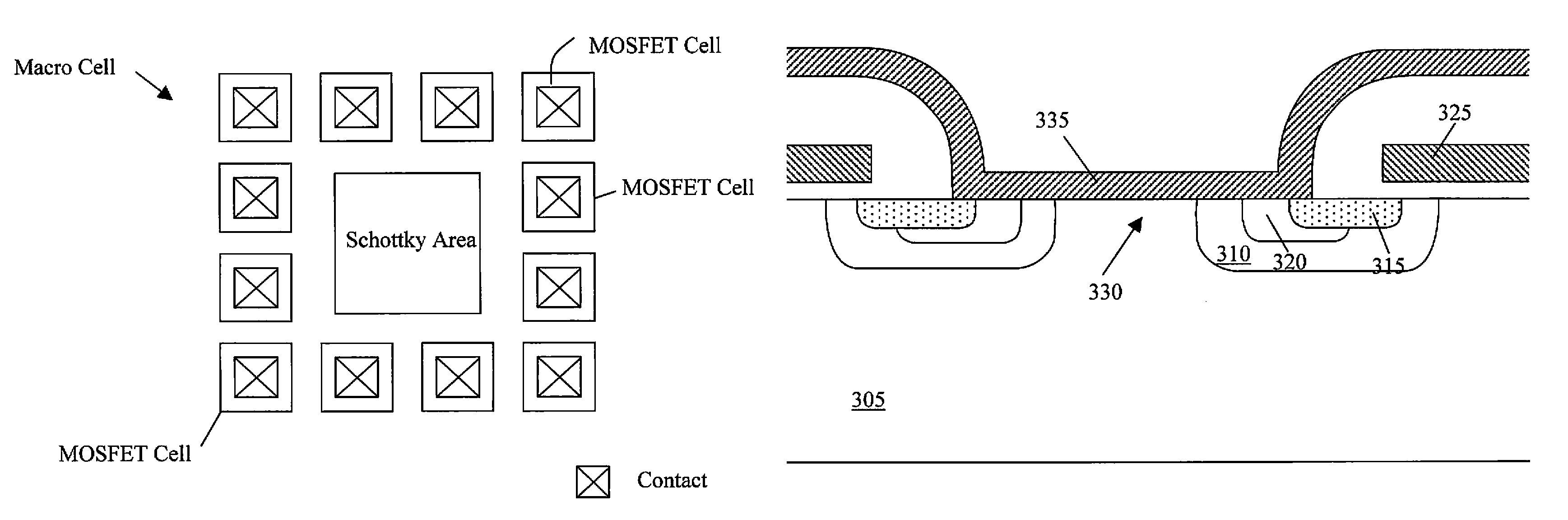

Planar SRFET using no additional masks and layout method

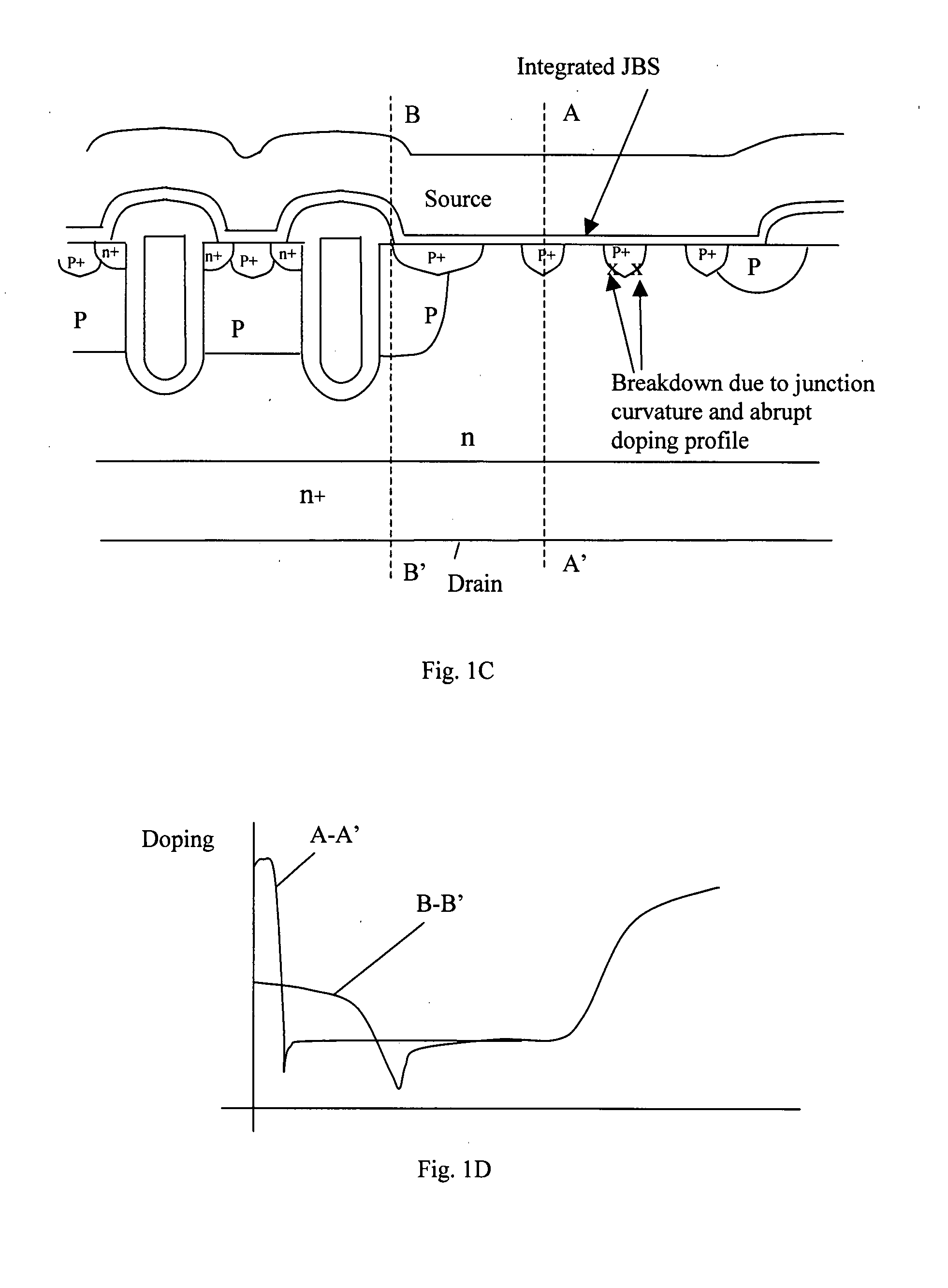

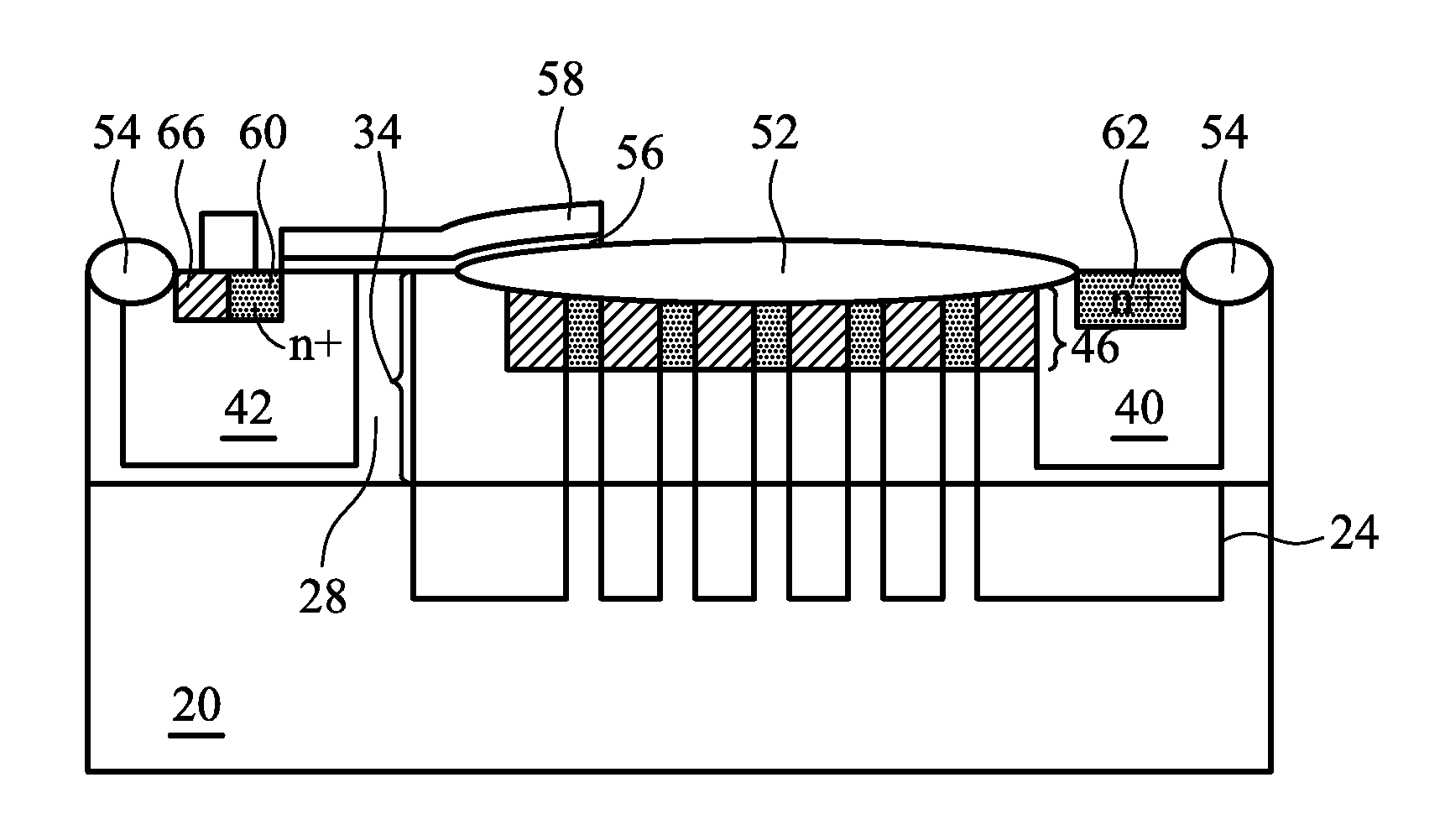

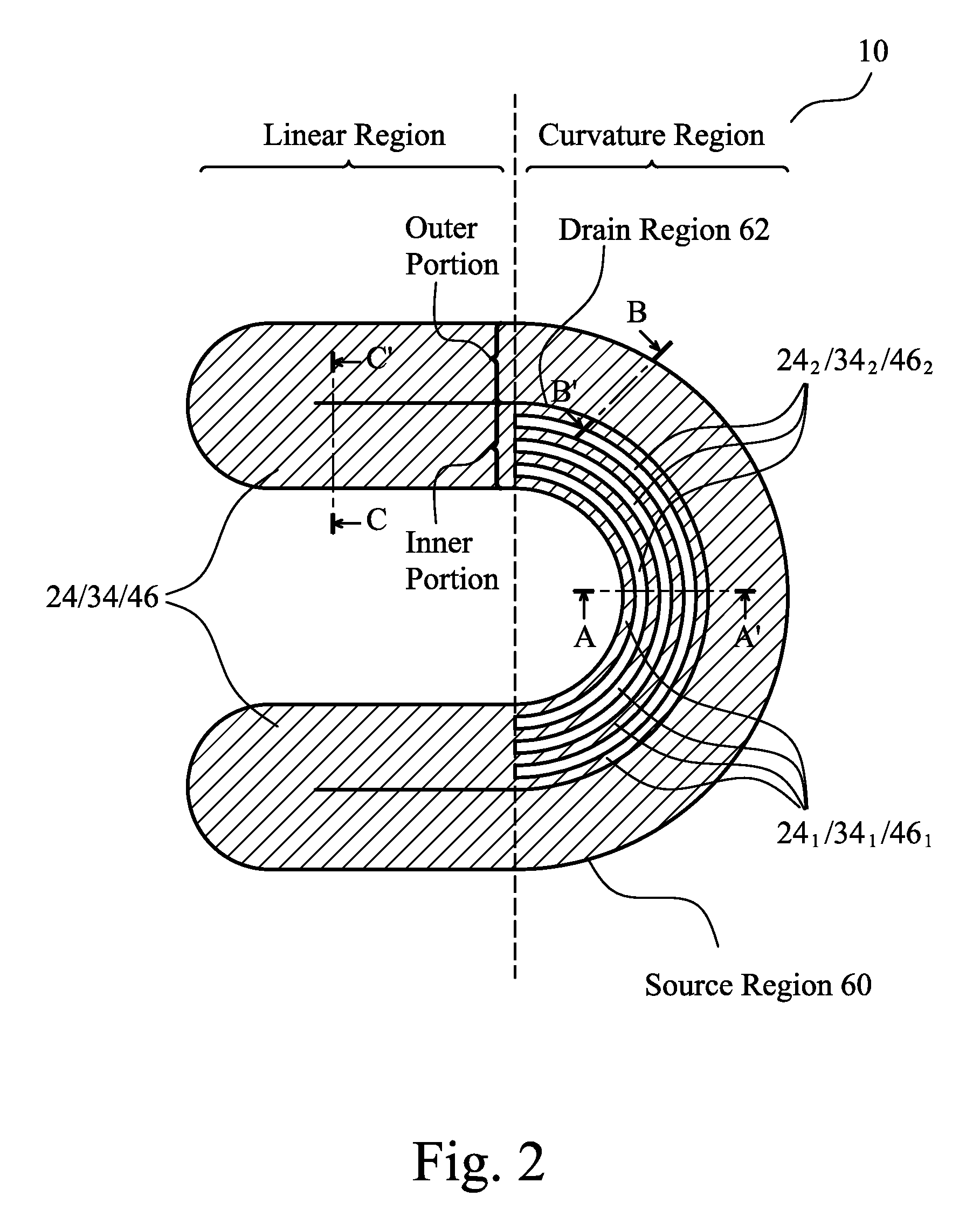

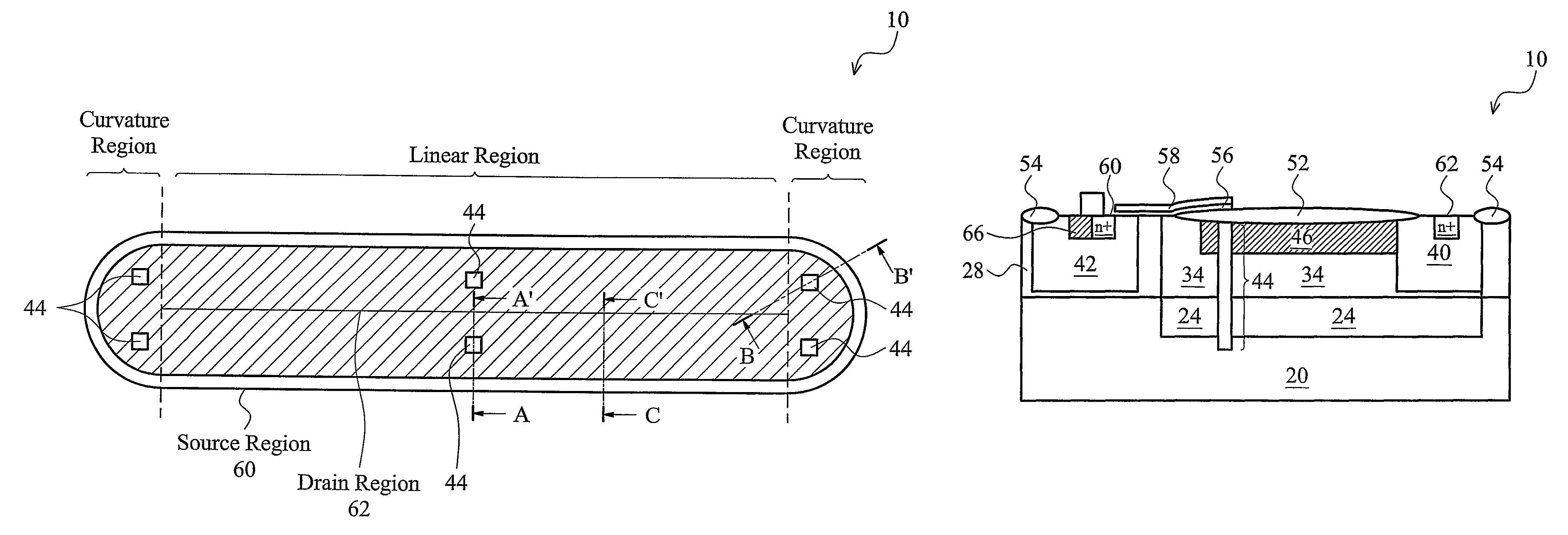

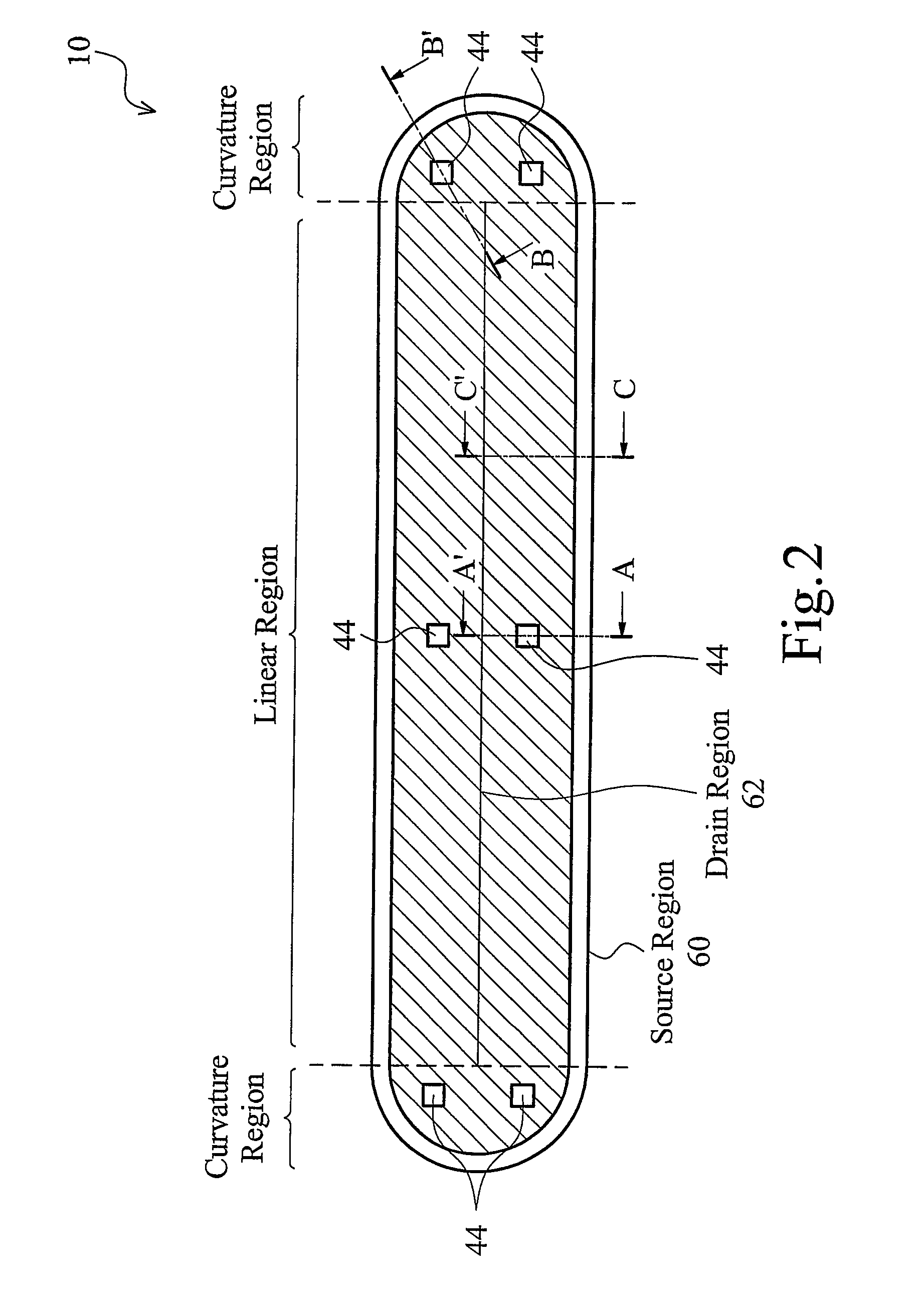

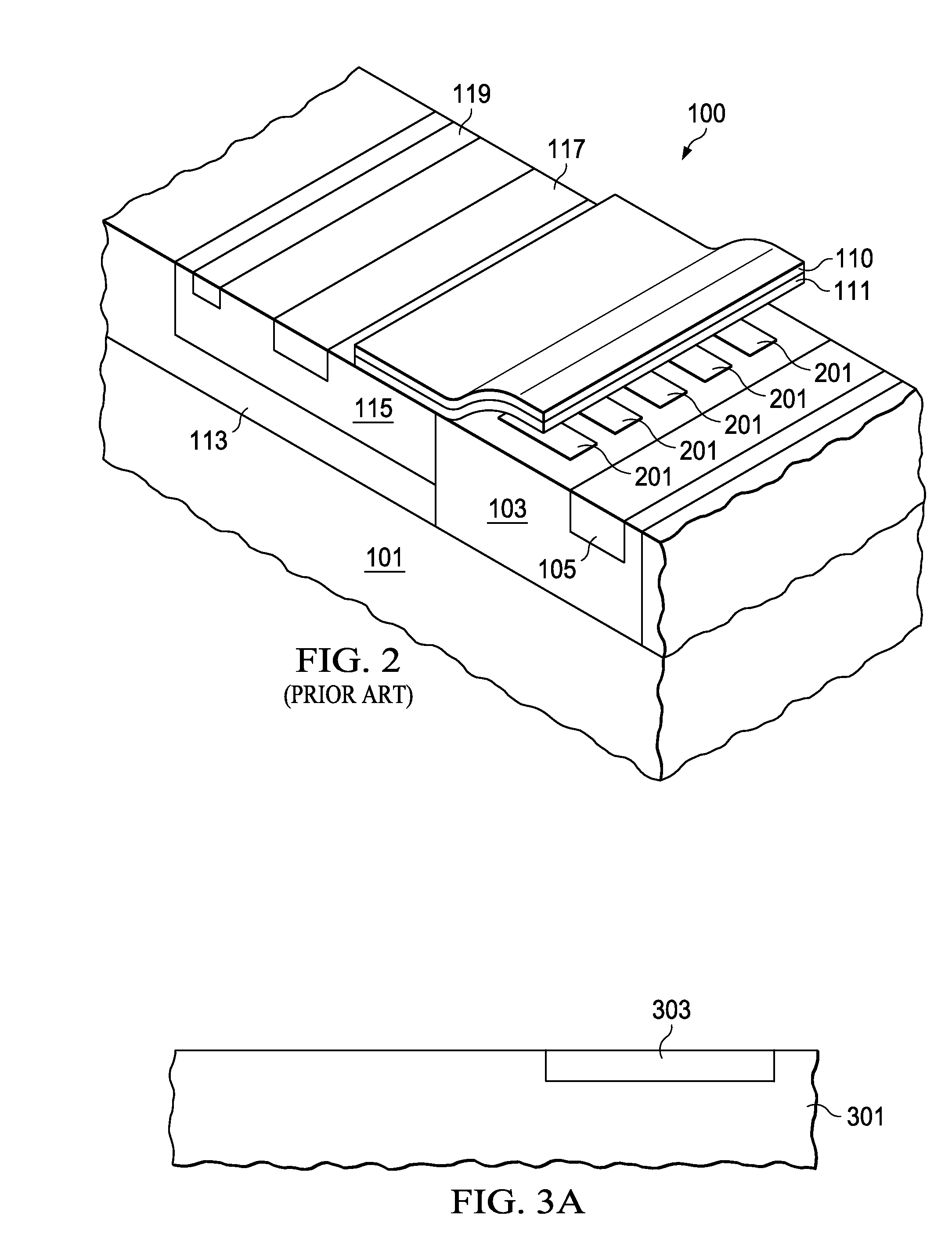

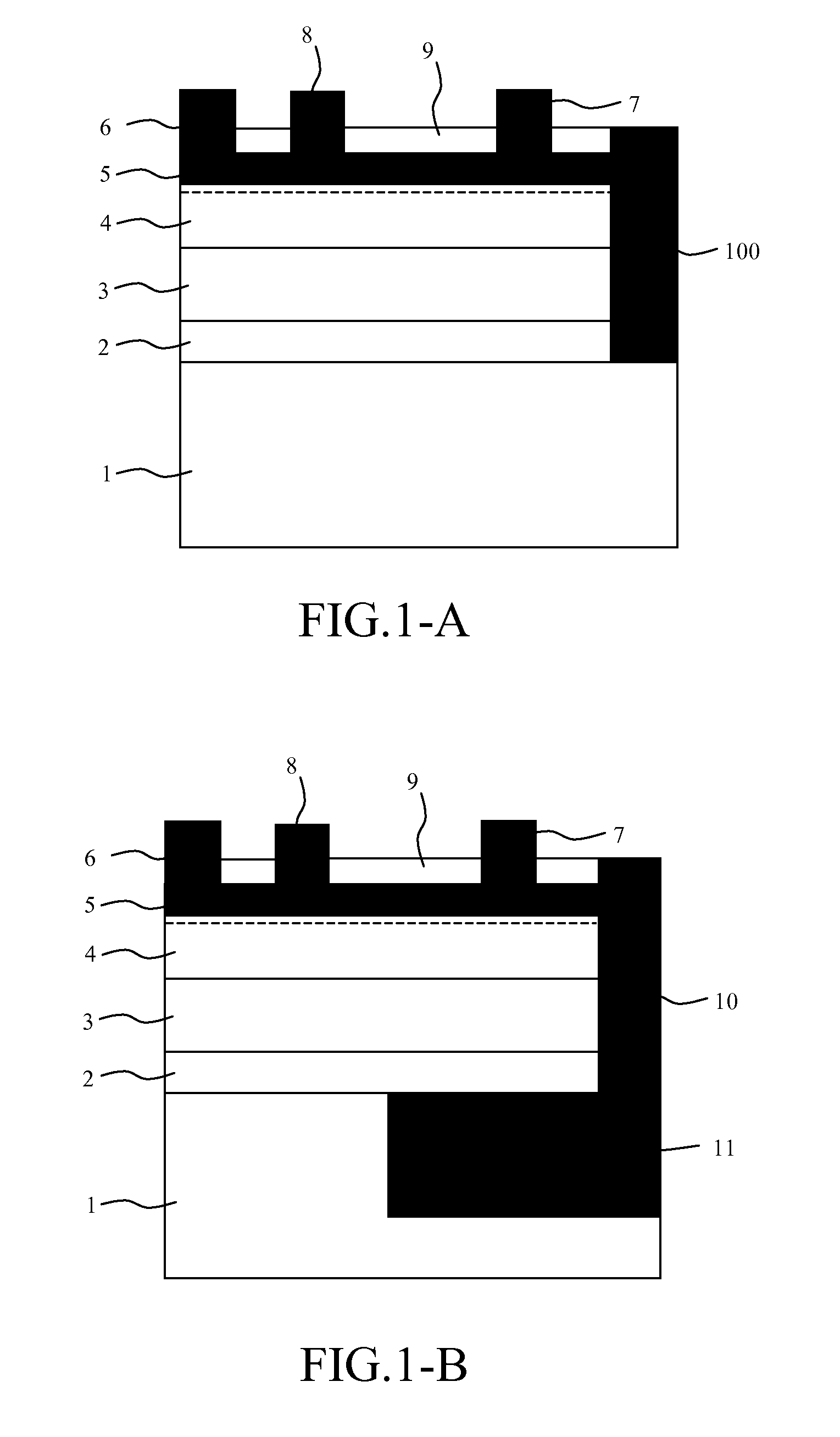

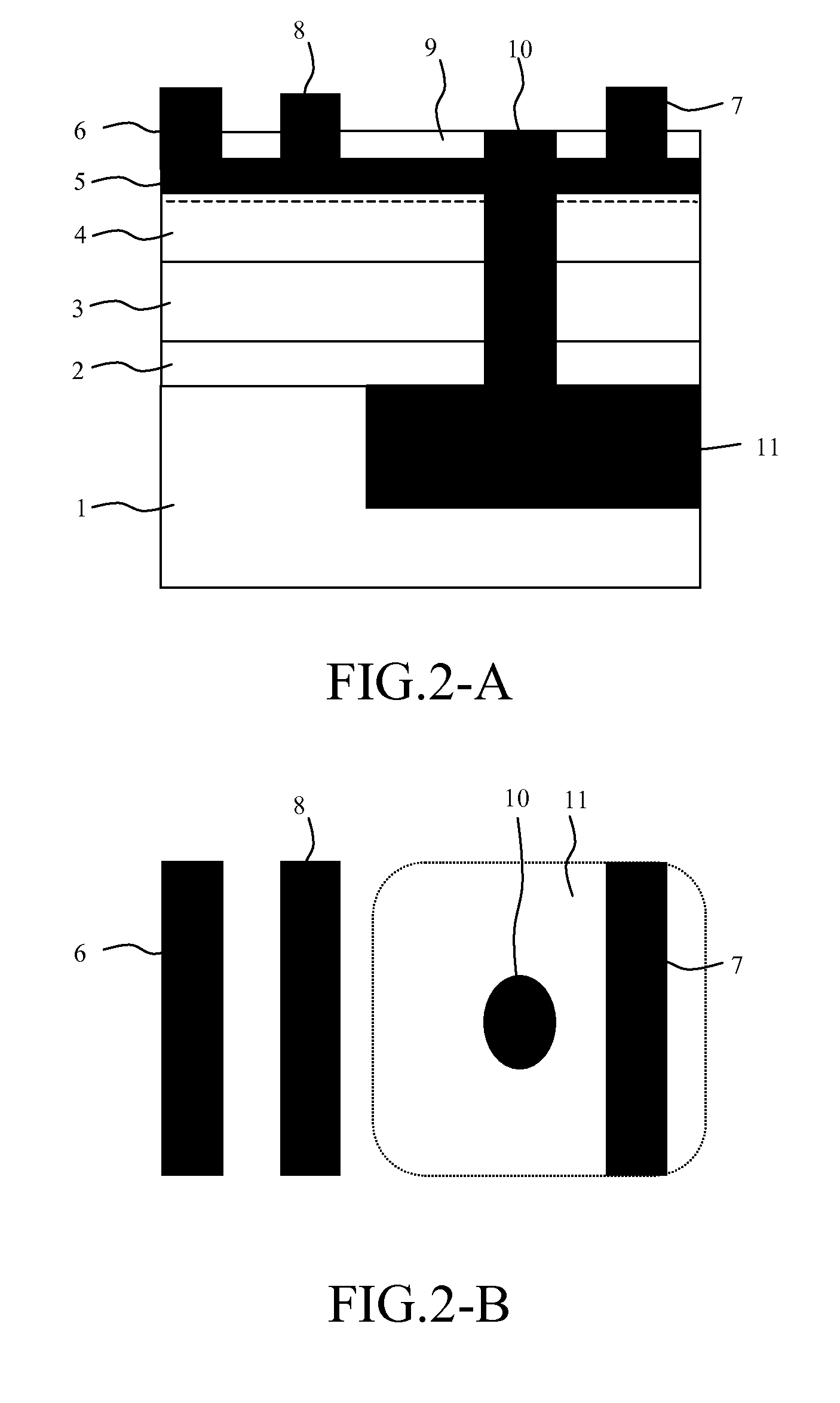

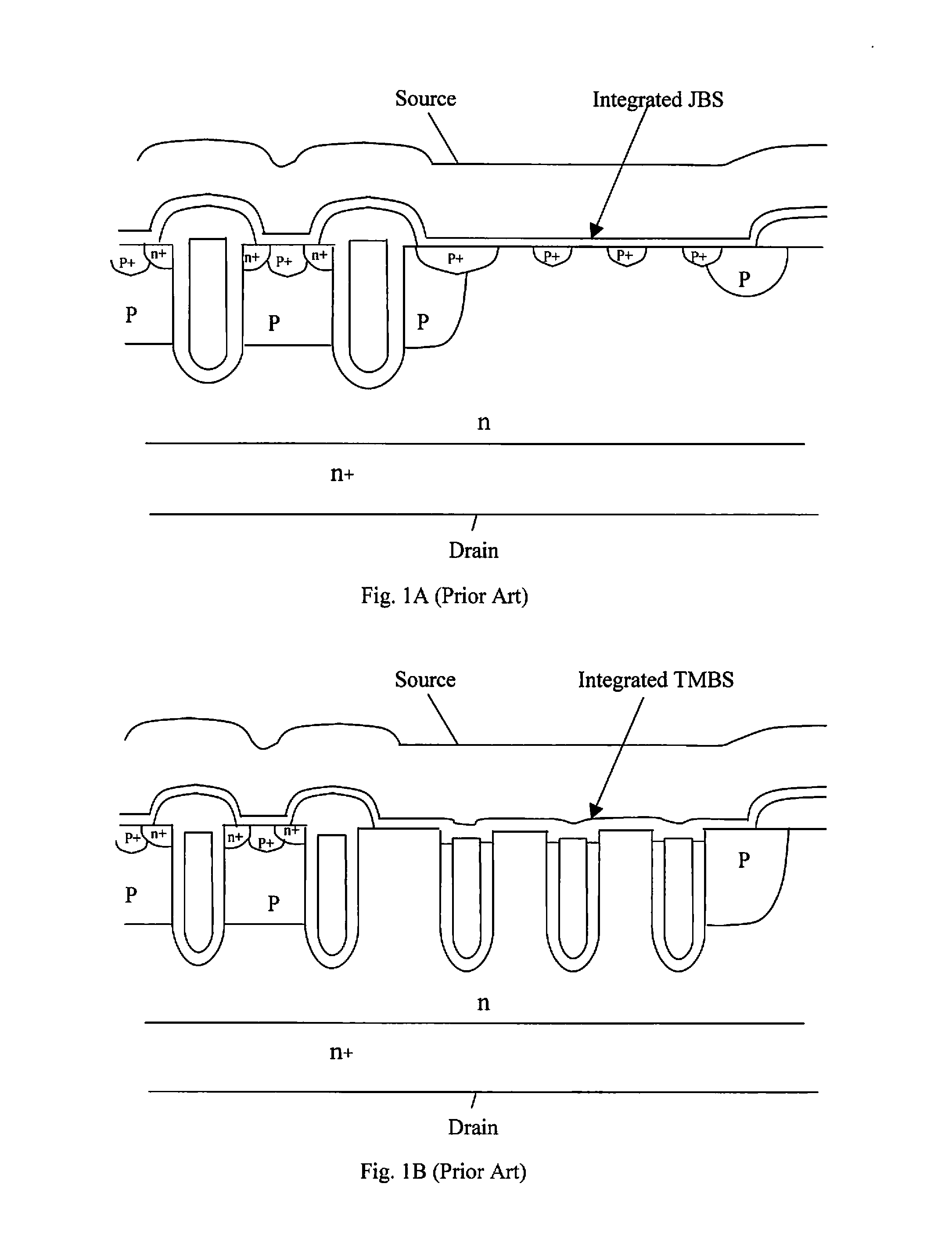

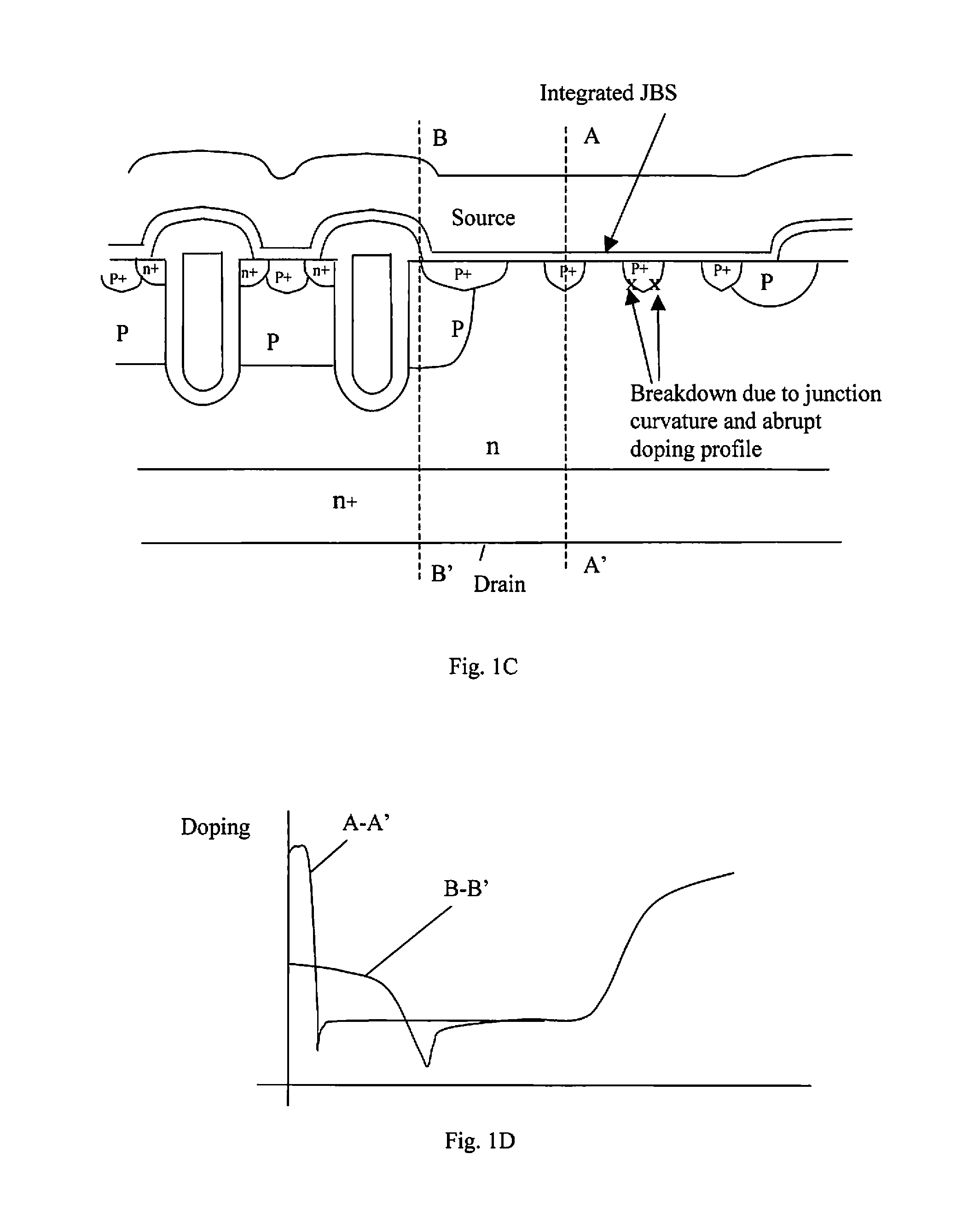

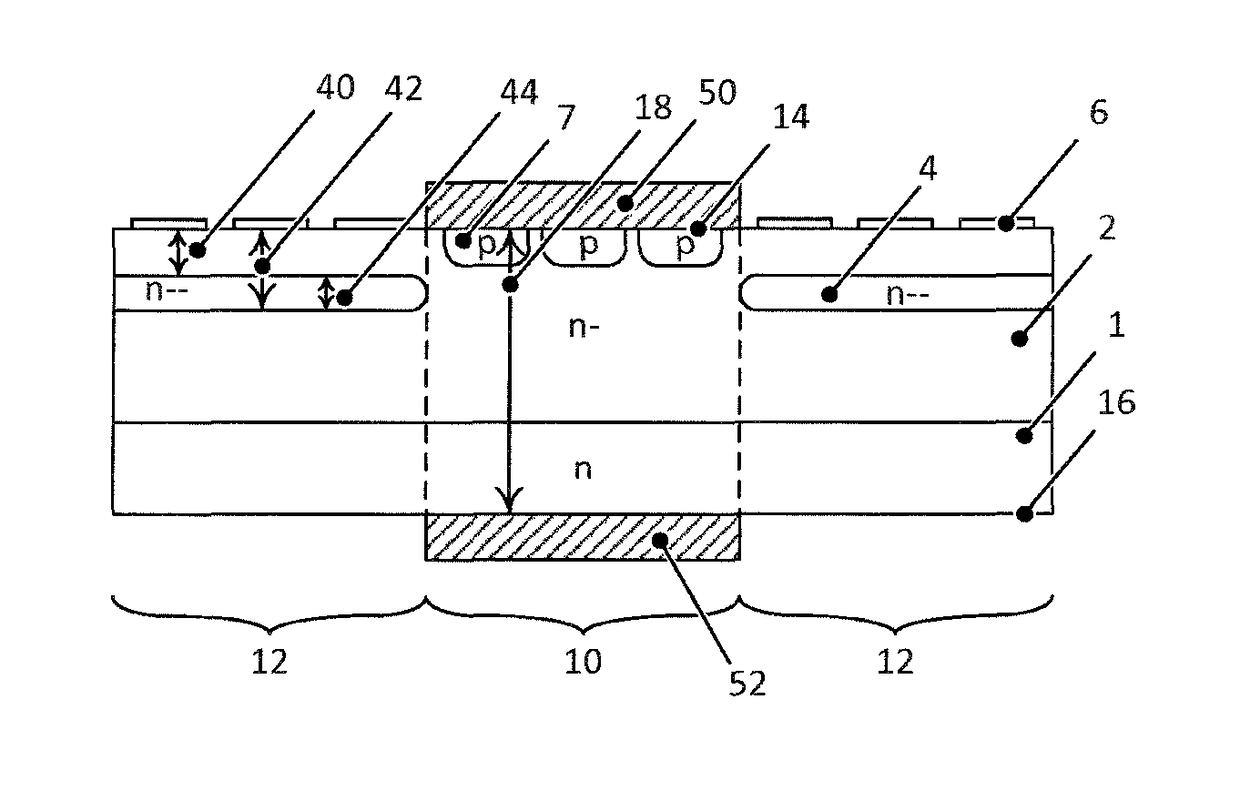

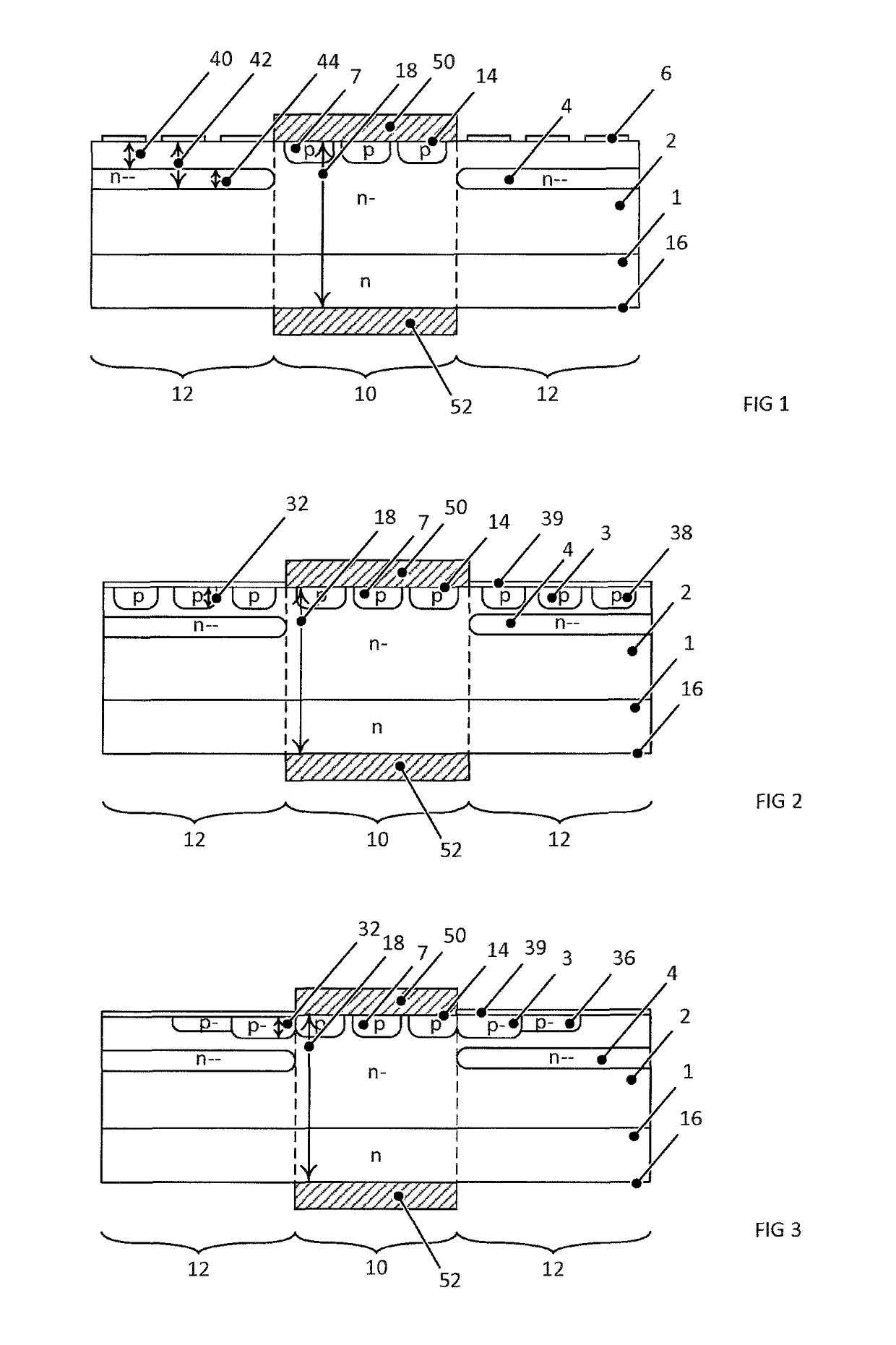

A semiconductor power device supported on a semiconductor substrate of a first conductivity type with a bottom layer functioning as a bottom electrode and an epitaxial layer overlying the bottom layer with a same conductivity type as the bottom layer. The semiconductor power device includes a plurality of FET cells and each cell further includes a body region of a second conductivity type extending from a top surface into the epitaxial layer. The body region encompasses a heavy body dopant region of second conductivity type. An insulated gate is disposed on the top surface of the epitaxial layer, overlapping a first portion of the body region. A barrier control layer is disposed on the top surface of the epitaxial layer next to the body region away from the insulated gate. A conductive layer overlies the top surface of the epitaxial layer covering a second portion of the body region and the heavy body dopant region extending over the barrier control layer forming a Schottky junction diode.

Owner:ALPHA & OMEGA SEMICON LTD

Super junction / resurf ldmost (sjr-LDMOST)

InactiveUS20050017300A1Reduce doping concentrationBreakdown voltage of deviceSemiconductor devicesMOSFETElectrical ballast

A lateral double diffused MOSFET (LDMOST) incorporates both the reduced surface field (RESURF) and super junction (SJ) in a split-drift region to significantly improve the on-state, off-state and switching characteristics in junction-isolated (JI) technology. The structure effectively suppresses substrate-assisted-depletion which is the main problem encountered when applying the SJ concept to lateral power devices. The device structure features a split-drift region formed of two parts: a SJ structure that extends over most of the drift region, and a terminating RESURF region occupying a portion of the drift region next to the drain. The structure offers improved breakdown voltage and reduced specific on resistance as compared to convention structures, and is useful in power integrated circuits suitable for a variety of applications including flat plasma panel display, automotive electronics, motor control, power supply and high voltage lamp ballasts.

Owner:SALAMA C ANDRE T +1

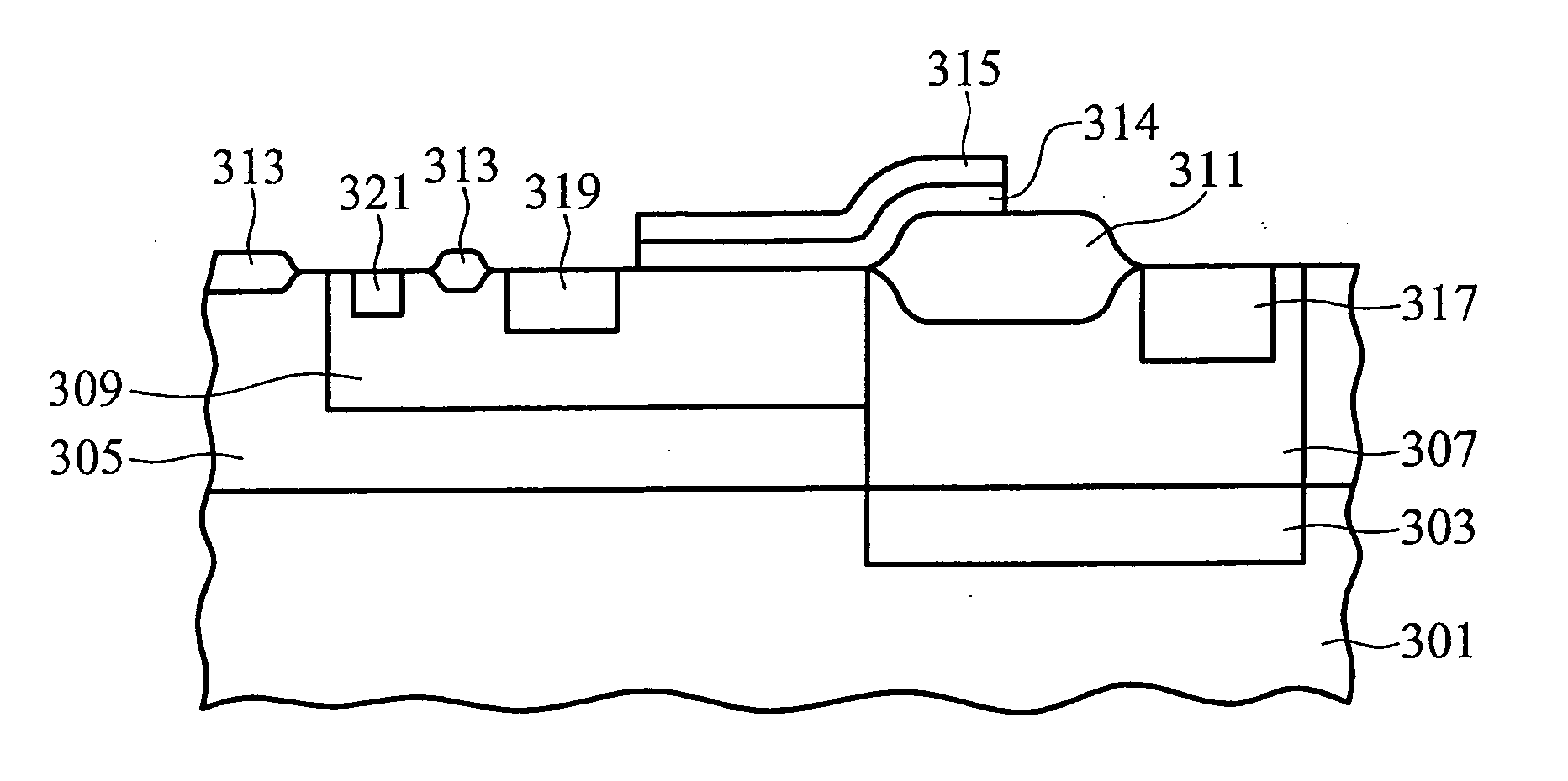

Planar srfet using no additional masks and layout method

ActiveUS20130026568A1Maximized Schottky areaImprove performanceTransistorSemiconductor/solid-state device manufacturingDopantControl layer

A semiconductor power device is supported on a semiconductor substrate with a bottom layer functioning as a bottom electrode and an epitaxial layer overlying the bottom layer as the bottom layer. The semiconductor power device includes a plurality of FET cells and each cell further includes a body region extending from a top surface into the epitaxial layer. The body region encompasses a heavy body dopant region. An insulated gate is disposed on the top surface of the epitaxial layer, overlapping a first portion of the body region. A barrier control layer is disposed on the top surface of the epitaxial layer next to the body region away from the insulated gate. A conductive layer overlies the top surface of the epitaxial layer covering a second portion of the body region and the heavy body dopant region extending over the barrier control layer forming a Schottky junction diode.

Owner:ALPHA & OMEGA SEMICON INC

Planar SRFET using no additional masks and layout method

ActiveUS8110869B2Improved body diode recovery behaviorLess voltage oscillationDiodeDopantControl layer

A semiconductor power device supported on a semiconductor substrate of a first conductivity type with a bottom layer functioning as a bottom electrode and an epitaxial layer overlying the bottom layer with a same conductivity type as the bottom layer. The semiconductor power device includes a plurality of FET cells and each cell further includes a body region of a second conductivity type extending from a top surface into the epitaxial layer. The body region encompasses a heavy body dopant region of second conductivity type. An insulated gate is disposed on the top surface of the epitaxial layer, overlapping a first portion of the body region. A barrier control layer is disposed on the top surface of the epitaxial layer next to the body region away from the insulated gate. A conductive layer overlies the top surface of the epitaxial layer covering a second portion of the body region and the heavy body dopant region extending over the barrier control layer forming a Schottky junction diode.

Owner:ALPHA & OMEGA SEMICON LTD

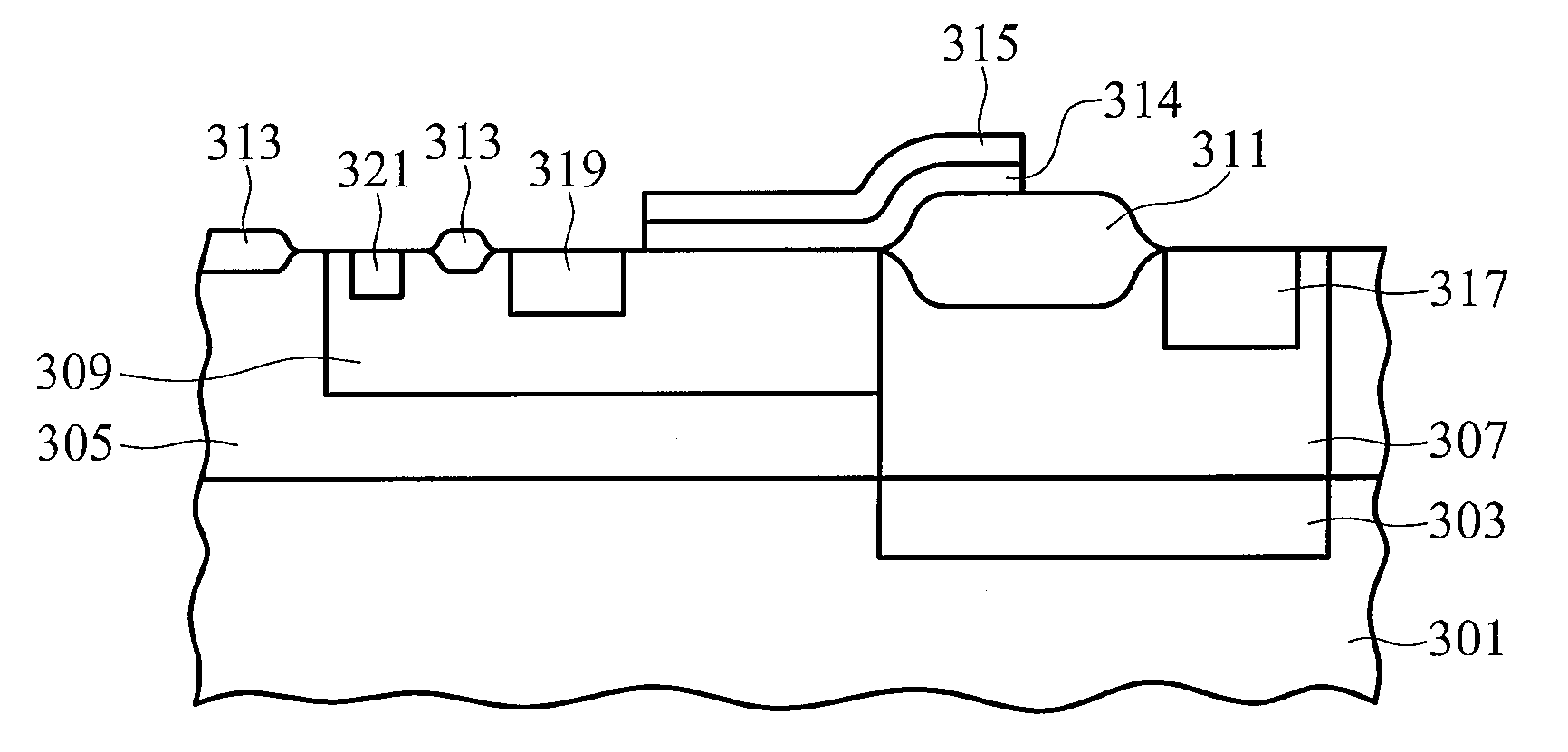

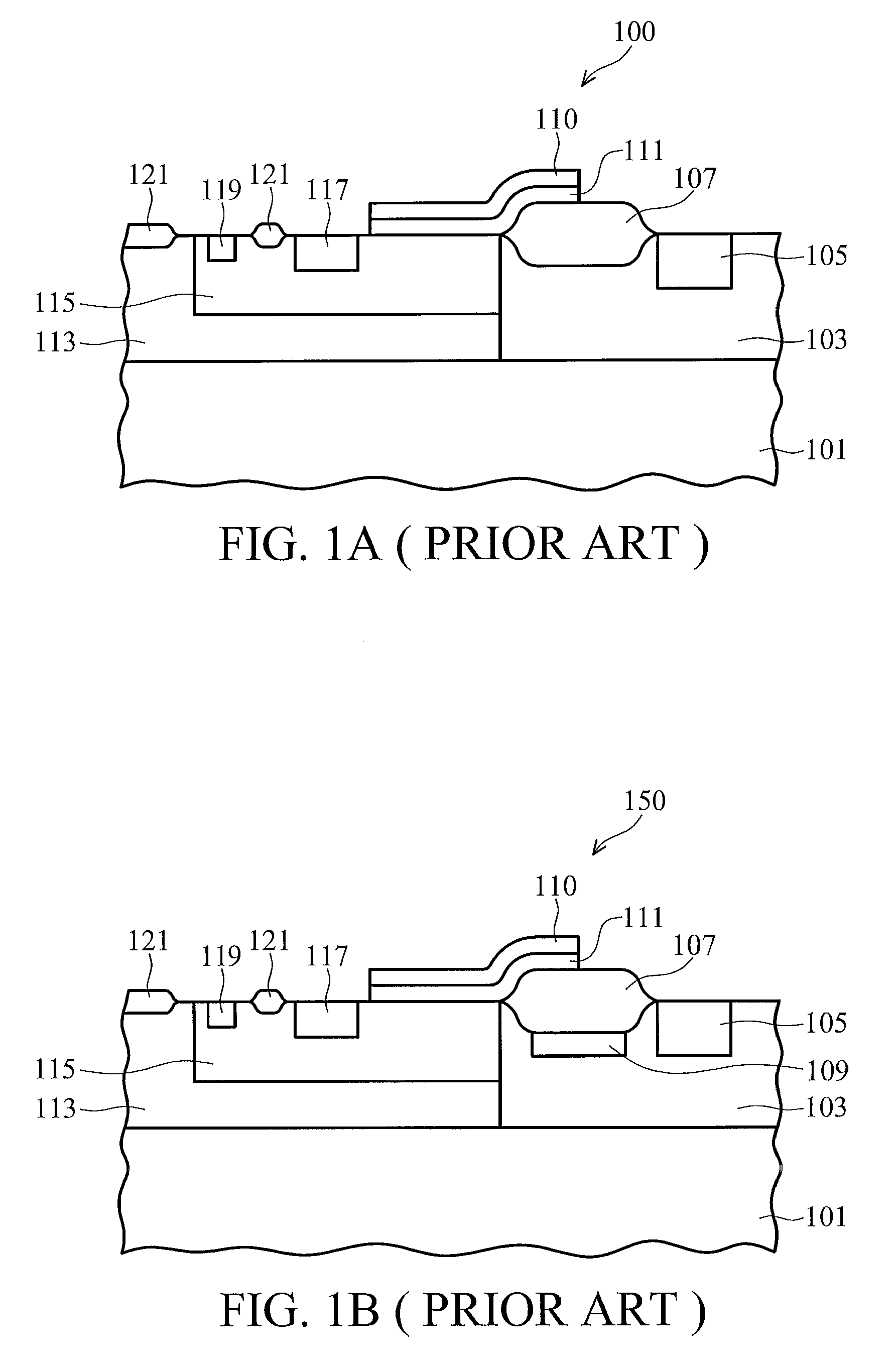

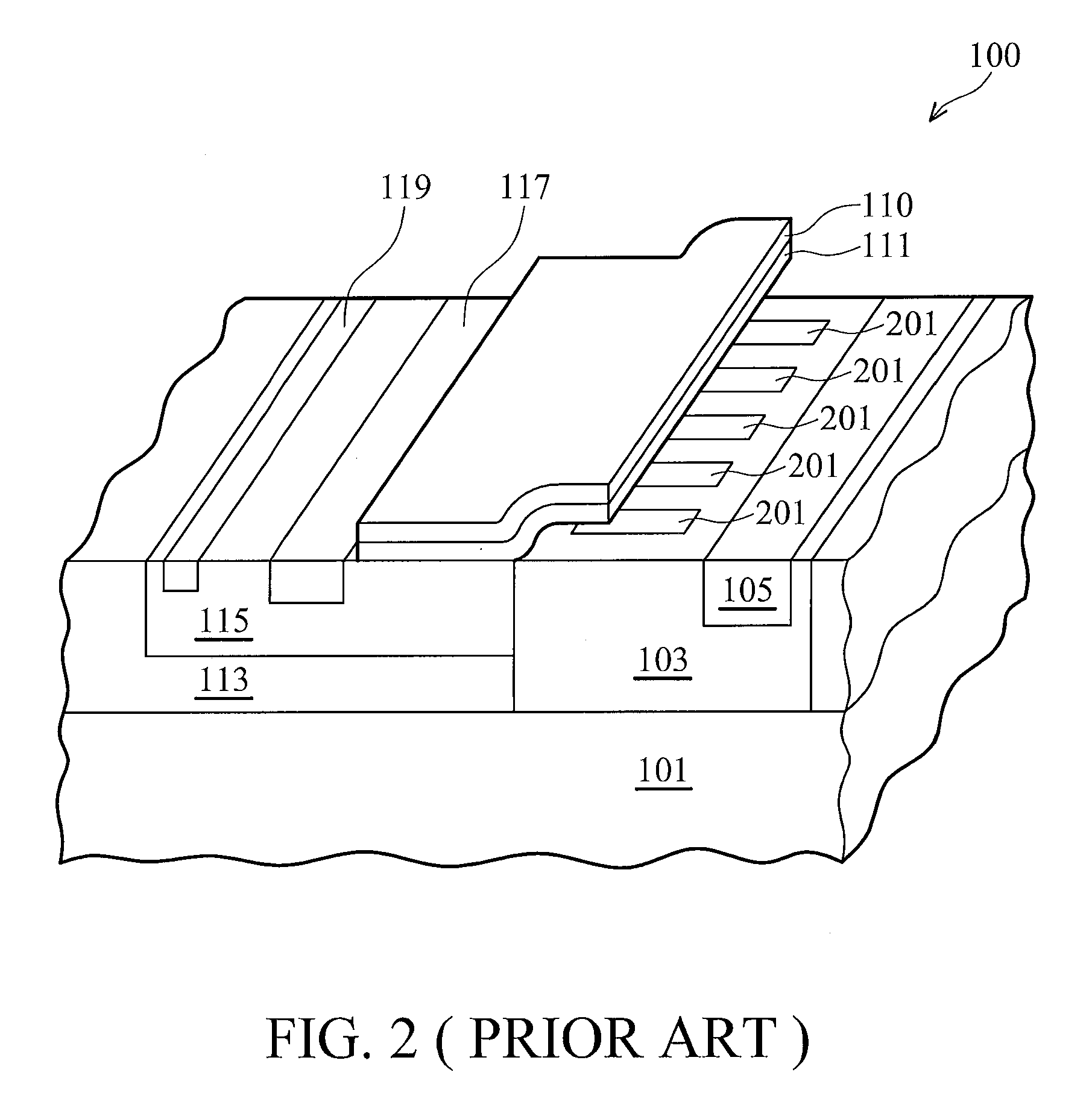

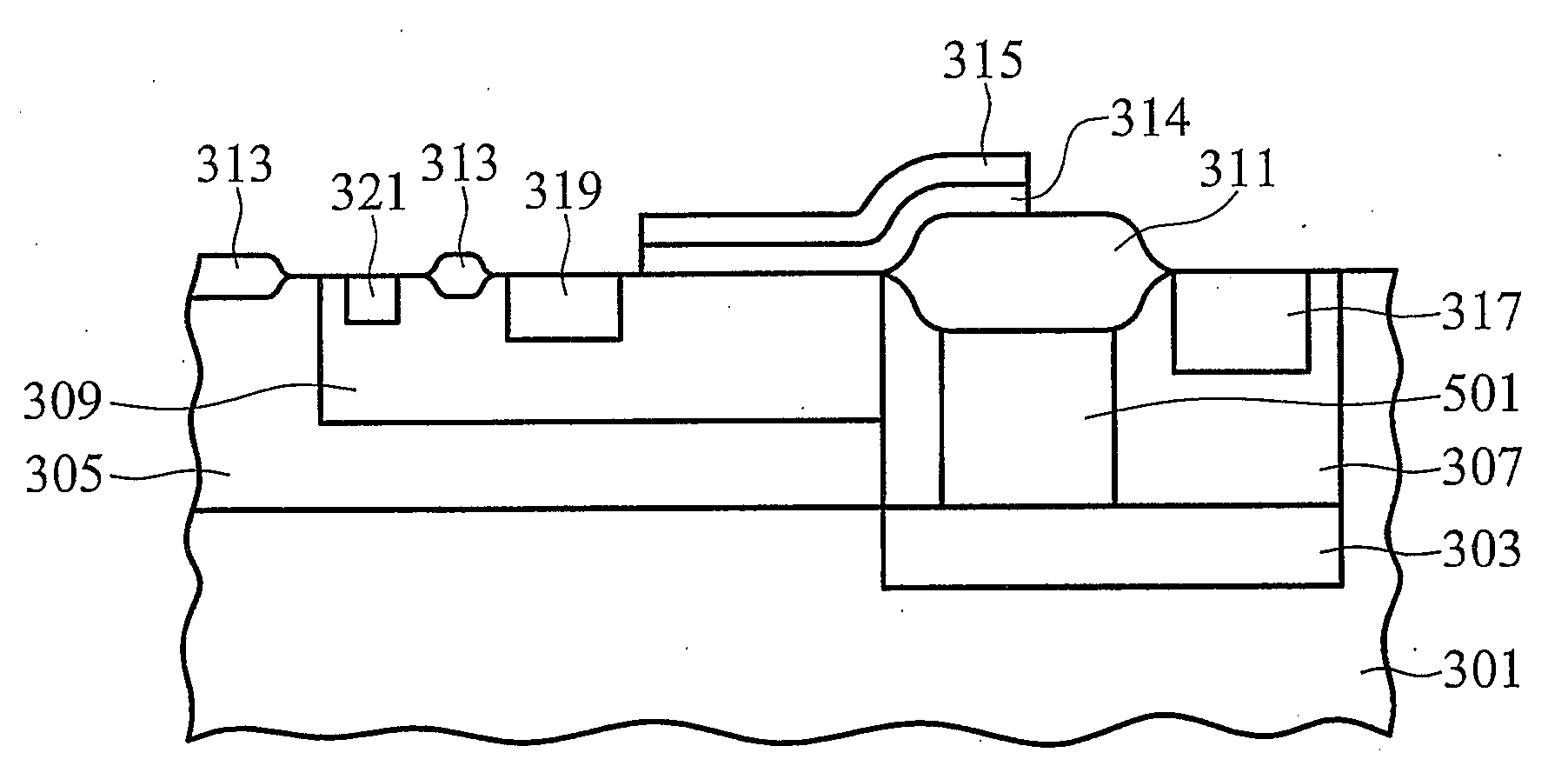

Lateral power MOSFET with high breakdown voltage and low on-resistance

ActiveUS20080090347A1Improve performance and efficiencyOn-resistance of the device is reducedSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricGate dielectric

A semiconductor device with high breakdown voltage and low on-resistance is provided. An embodiment comprises a substrate having a buried layer in a portion of the top region of the substrate in order to extend the drift region. A layer is formed over the buried layer and the substrate, and high-voltage N-well and P-well regions are formed adjacent to each other. Field dielectrics are located over portions of the high-voltage N-wells and P-wells, and a gate dielectric and a gate conductor are formed over the channel region between the high-voltage P-well and the high-voltage N-well. Source and drain regions for the transistor are located in the high-voltage P-well and high-voltage N-well. Optionally, a P field ring is formed in the N-well region under the field dielectric. In another embodiment, a lateral power superjunction MOSFET with partition regions located in the high-voltage N-well is manufactured with an extended drift region.

Owner:TAIWAN SEMICON MFG CO LTD

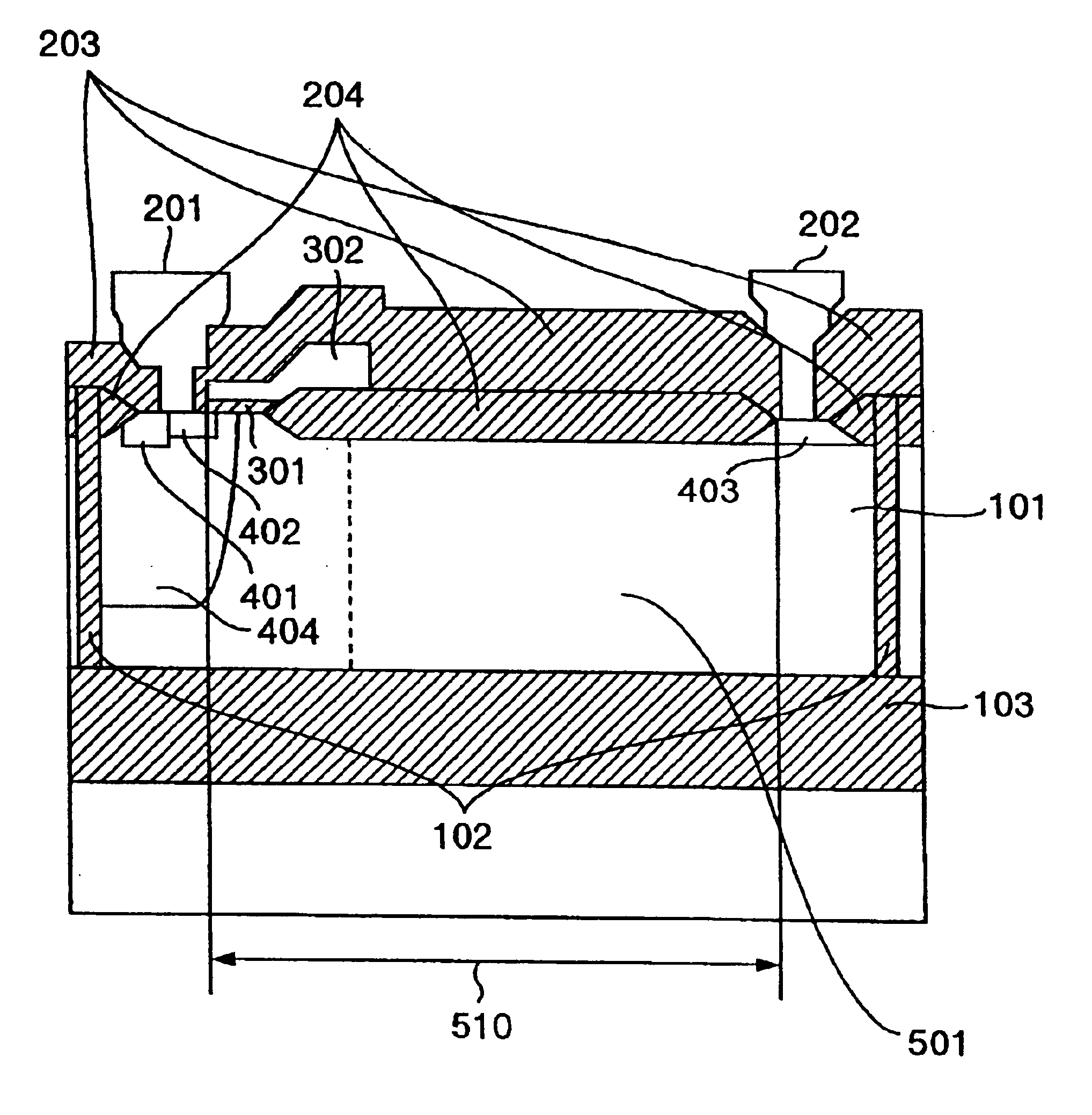

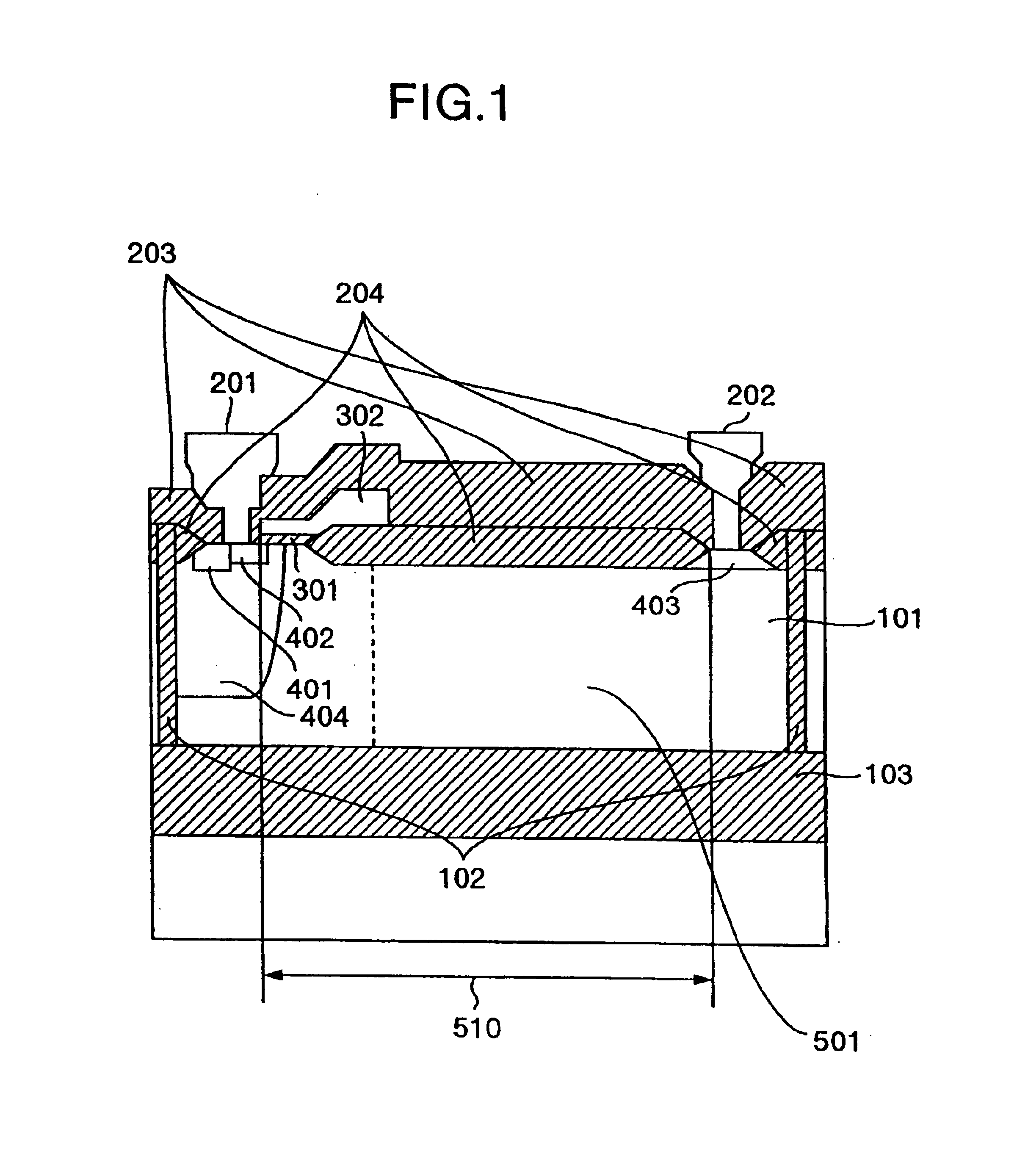

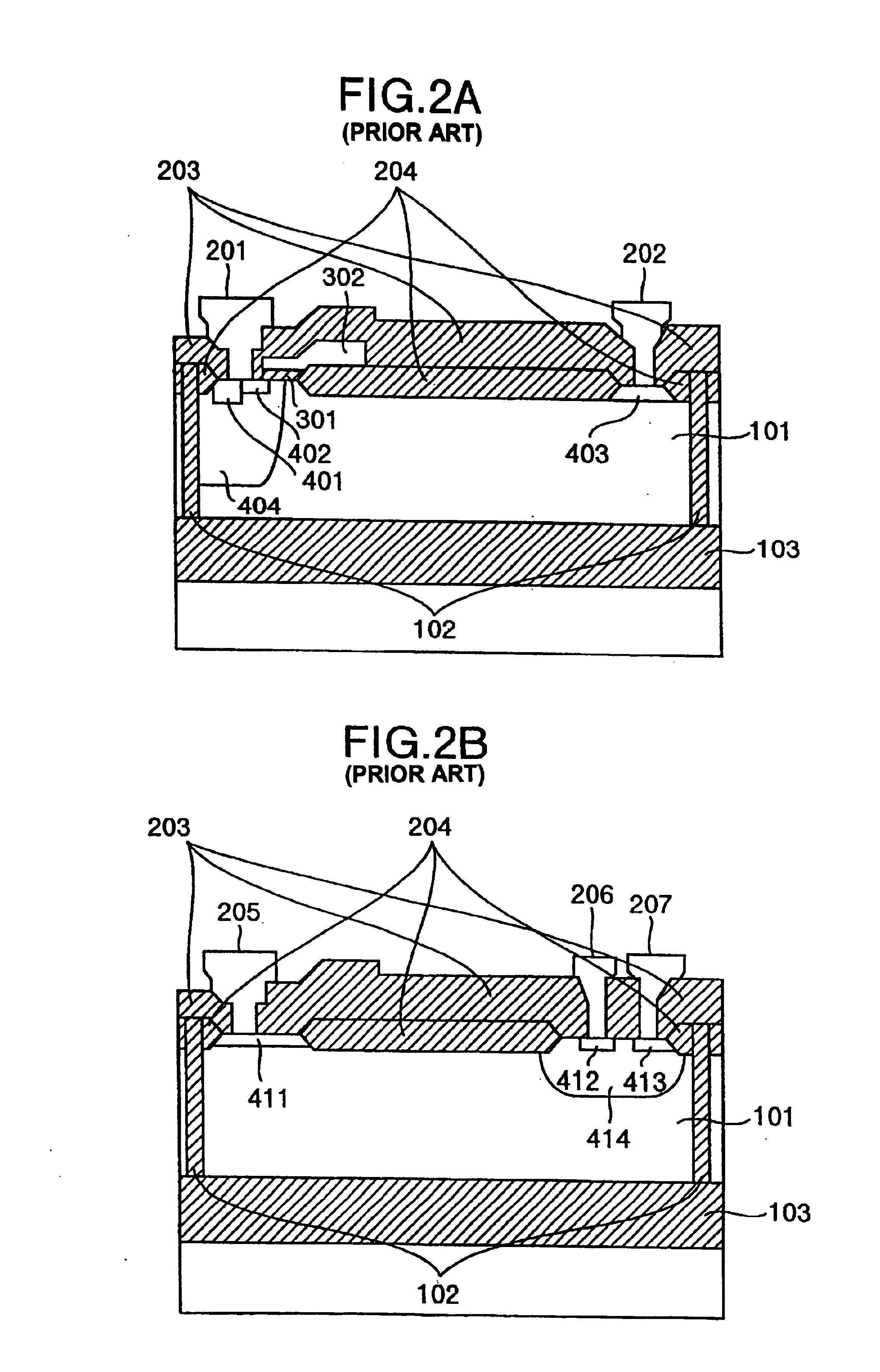

Semiconductor device and method for fabricating the same

ActiveUS7291872B2Breakdown voltage of deviceSimplify the manufacturing processSemiconductor devicesSemiconductorElectric field

In the structure of a semiconductor device of the present invention, a first source electrode is connected to a conductive substrate through a via hole, and a second source electrode is formed. Thus, even if a high reverse voltage is applied between a gate electrode and a drain electrode, electric field concentration likely to occur at an edge of the gate electrode closer to the drain electrode can be effectively dispersed or relaxed. Moreover, the conductive substrate is used as a substrate for forming element formation layers, so that a via hole penetrating the substrate to reach the backside thereof does not have to be formed in the conductive substrate. Thus, with the strength necessary for the conductive substrate maintained, the first source electrode can be electrically connected to a backside electrode.

Owner:PANASONIC CORP

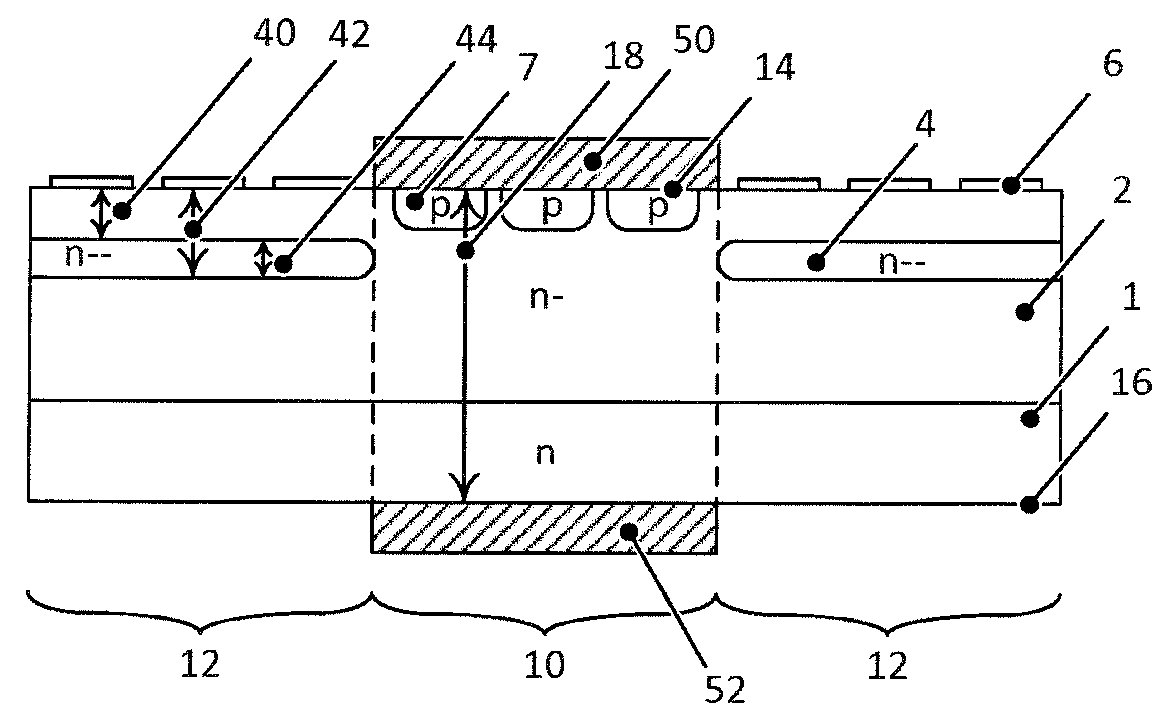

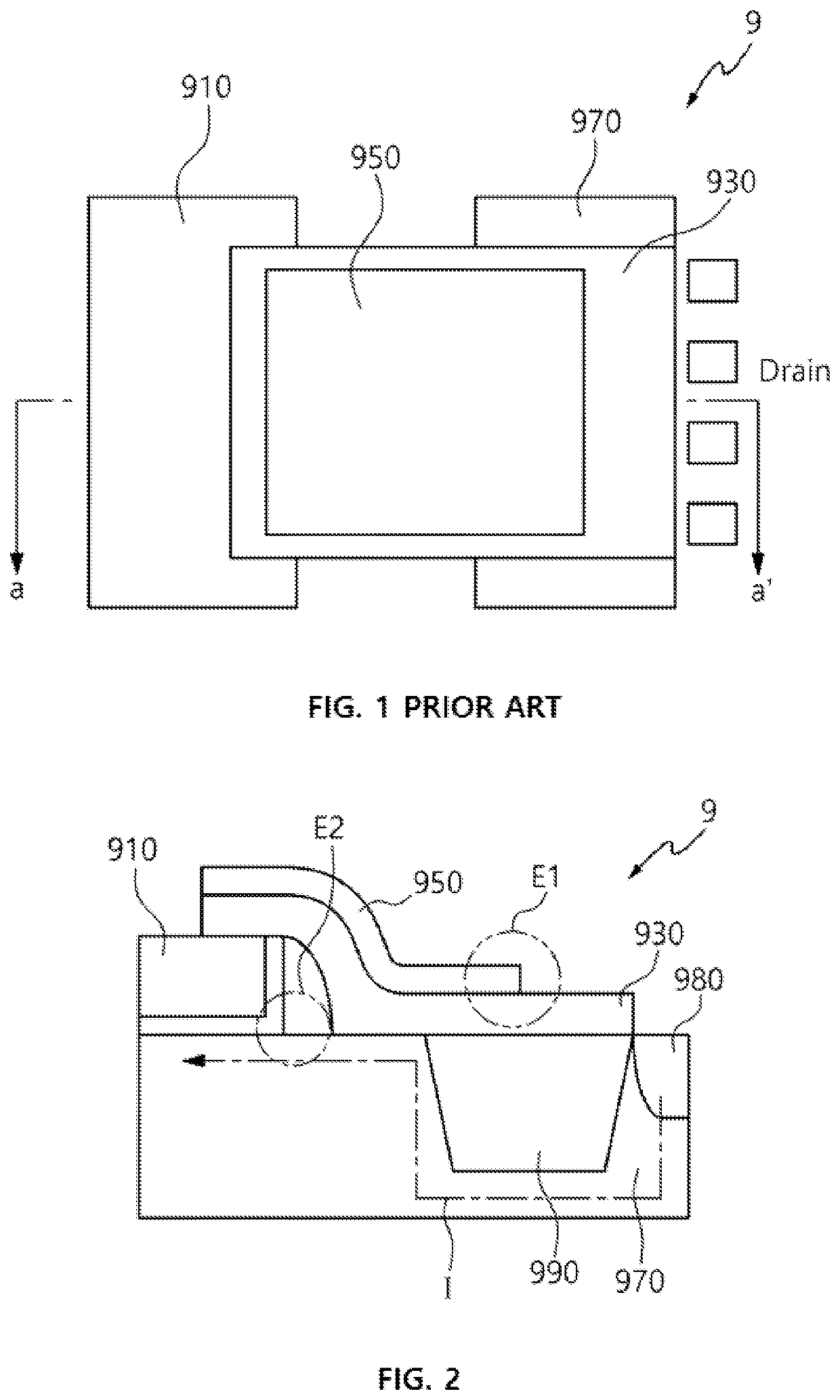

Lateral Power MOSFET with High Breakdown Voltage and Low On-Resistance

ActiveUS20090085101A1Improve performance and efficiencyOn-resistance of the device is reducedSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricElectrical conductor

A semiconductor device with high breakdown voltage and low on-resistance is provided. An embodiment comprises a substrate having a buried layer in a portion of the top region of the substrate in order to extend the drift region. A layer is formed over the buried layer and the substrate, and high-voltage N-well and P-well regions are formed adjacent to each other. Field dielectrics are located over portions of the high-voltage N-wells and P-wells, and a gate dielectric and a gate conductor are formed over the channel region between the high-voltage P-well and the high-voltage N-well. Source and drain regions for the transistor are located in the high-voltage P-well and high-voltage N-well. Optionally, a P field ring is formed in the N-well region under the field dielectric. In another embodiment, a lateral power superjunction MOSFET with partition regions located in the high-voltage N-well is manufactured with an extended drift region.

Owner:TAIWAN SEMICON MFG CO LTD

Lateral Power MOSFET with High Breakdown Voltage and Low On-Resistance

InactiveUS20090001462A1Improve performanceImprove efficiencySemiconductor/solid-state device detailsSolid-state devicesSemiconductor structurePower MOSFET

A semiconductor structure includes a semiconductor substrate of a first conductivity type; a pre-high-voltage well (pre-HVW) in the semiconductor substrate, wherein the pre-HVW is of a second conductivity type opposite the first conductivity type; a high-voltage well (HVW) over the pre-HVW, wherein the HVW is of the second conductivity type; a field ring in the HVW and occupying a top portion of the HVW, wherein the field ring is of the first conductivity type; an insulation region over and in contact with the field ring and a portion of the HVW; a gate electrode partially over the insulation region; a drain region in the HVW, wherein the drain region is of the second conductivity type; and wherein the HVW horizontally extends further toward the drain region than the pre-HVW; and a source region adjacent to, and on an opposite side of the gate electrode than the drain region.

Owner:TAIWAN SEMICON MFG CO LTD

Breakdown voltages of ultra-high voltage devices by forming tunnels

InactiveUS7960786B2On-resistances of the high-voltage MOSFETs are reducedBreakdown voltage of deviceTransistorSolid-state devicesSemiconductor structureUltra high voltage

A semiconductor structure includes a semiconductor substrate of a first conductivity type; a pre-high-voltage well (pre-HVW) in the semiconductor substrate, wherein the pre-HVW is of a second conductivity type opposite the first conductivity type; a high-voltage well (HVW) over the pre-HVW, wherein the HVW is of the second conductivity type; a field ring of the first conductivity type occupying a top portion of the HVW, wherein at least one of the pre-HVW, the HVW, and the field ring comprises at least two tunnels; an insulation region over the field ring and a portion of the HVW; a drain region in the HVW and adjacent the insulation region; a gate electrode over a portion the insulation region; and a source region on an opposite side of the gate electrode than the drain region.

Owner:TAIWAN SEMICON MFG CO LTD

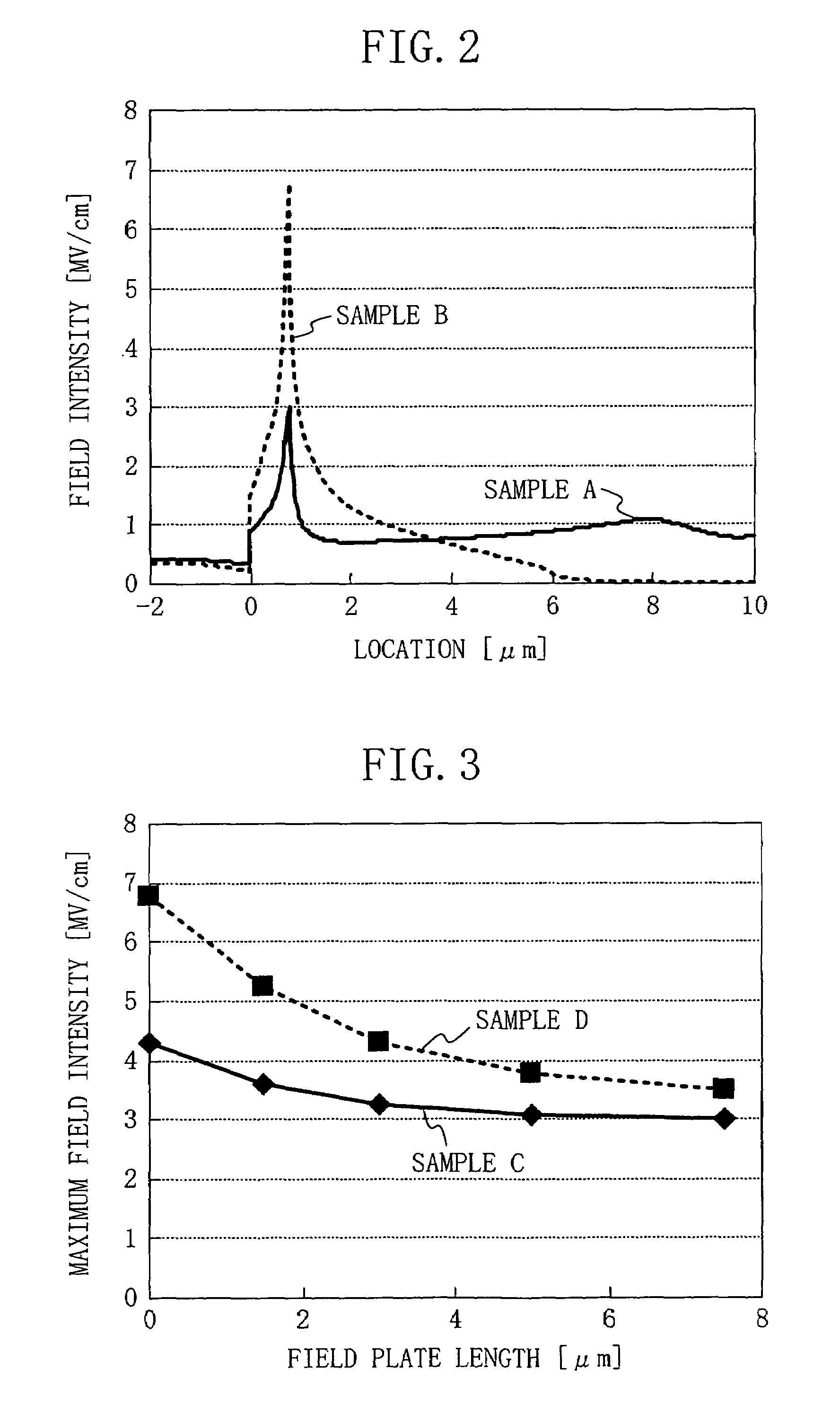

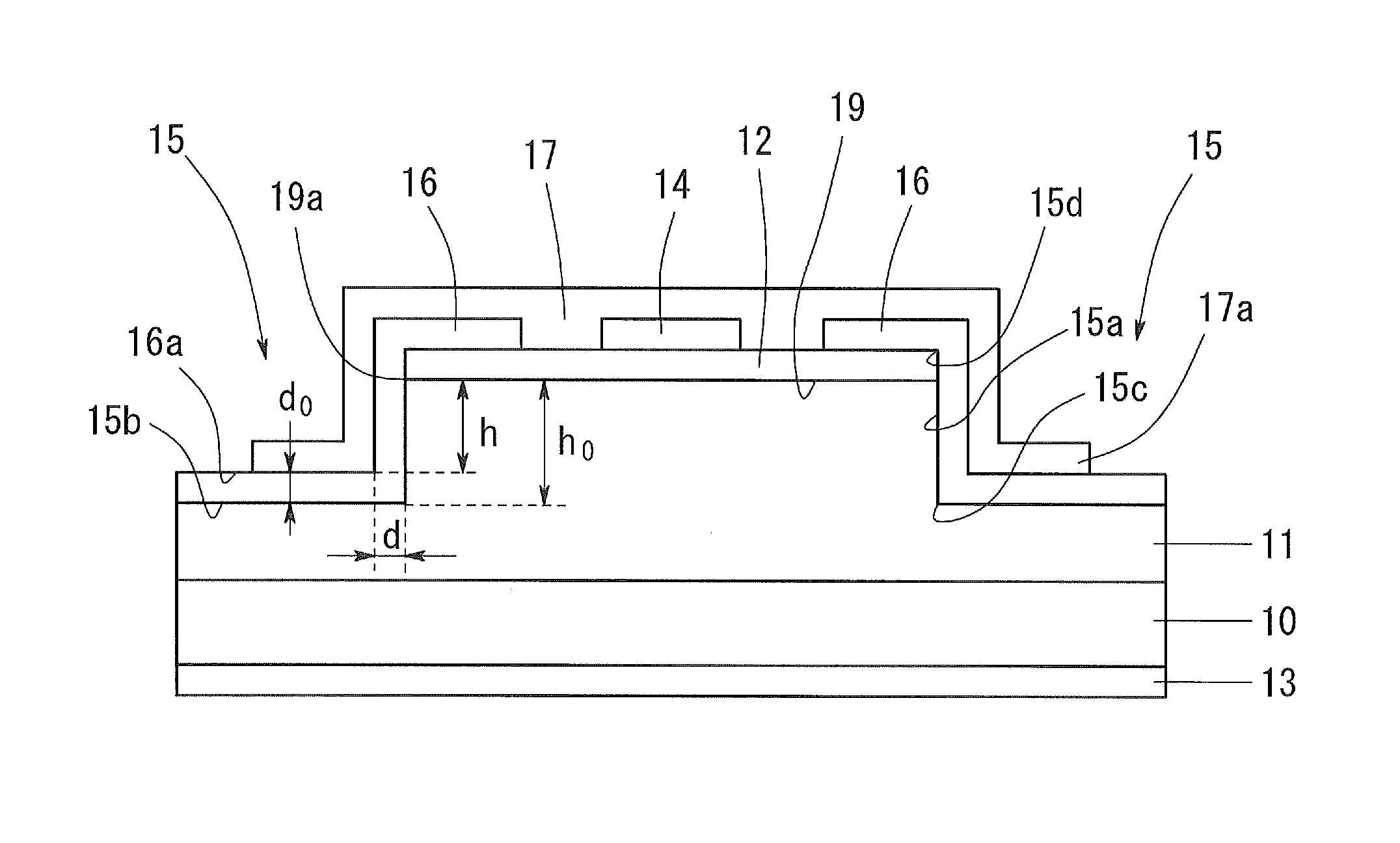

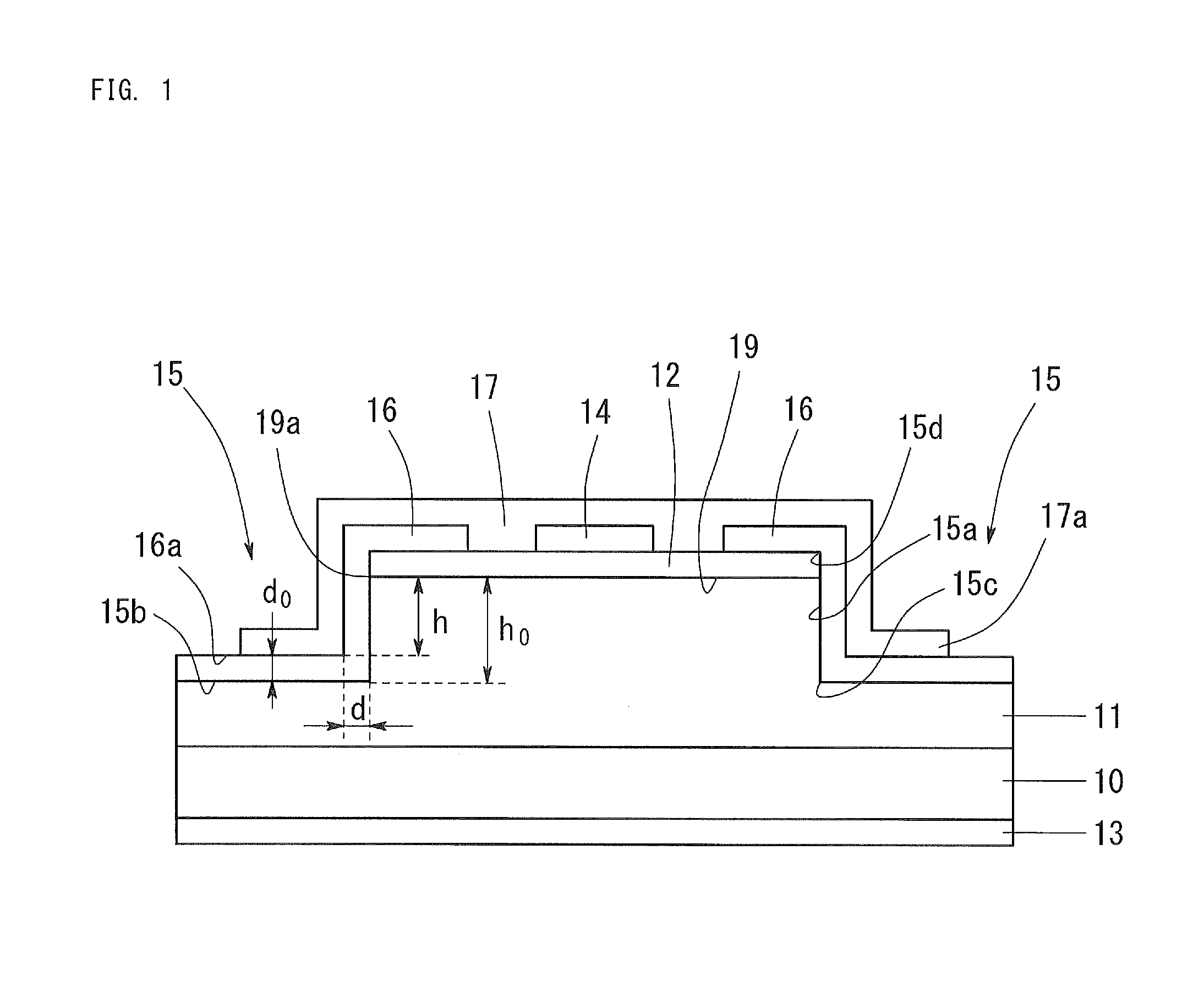

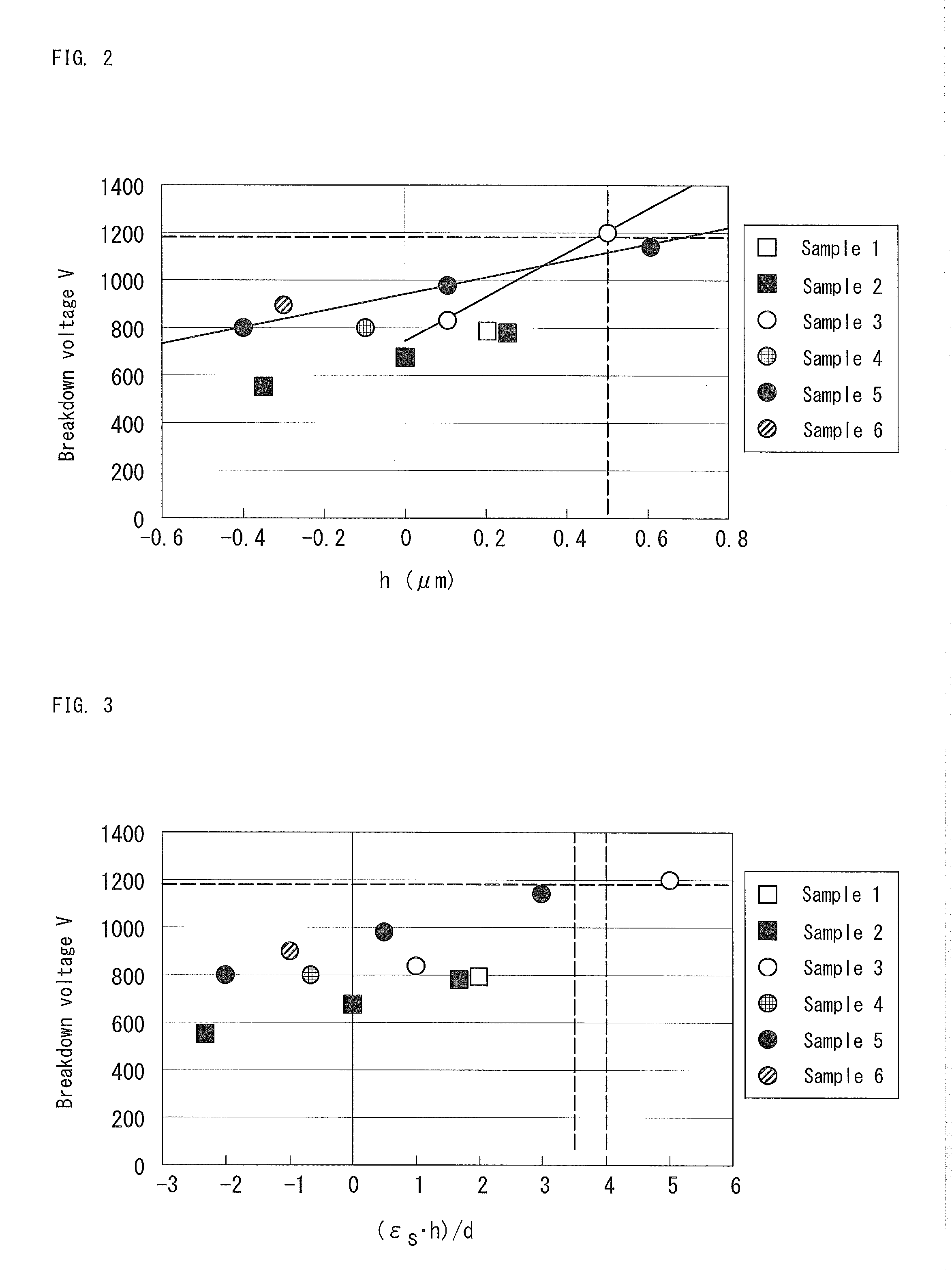

Semiconductor device

ActiveUS20130328120A1Large electric field relaxing regionImprove breakdown voltageSemiconductor devicesTectorial membraneSemiconductor

A device comprises a substrate, an n-layer and a p-layer, an n-electrode, and a p-electrode. A step is formed at an outer circumference of the device. A protective film is formed so as to continuously cover a side surface and a bottom surface of the step. A field plate electrode connected with the p-electrode is formed on the protective film. When a distance from the pn junction interface to the surface of the protective film on the bottom surface of the step is defined as h (μm), a dielectric constant of the protective film is defined as ∈s, and a thickness of the protective film at the pn junction interface on the side surface of the step is defined as d (μm), (∈s·h) / d is 4 or more, and ∈s / d is 3 (1 / μm) or more.

Owner:TOYODA GOSEI CO LTD

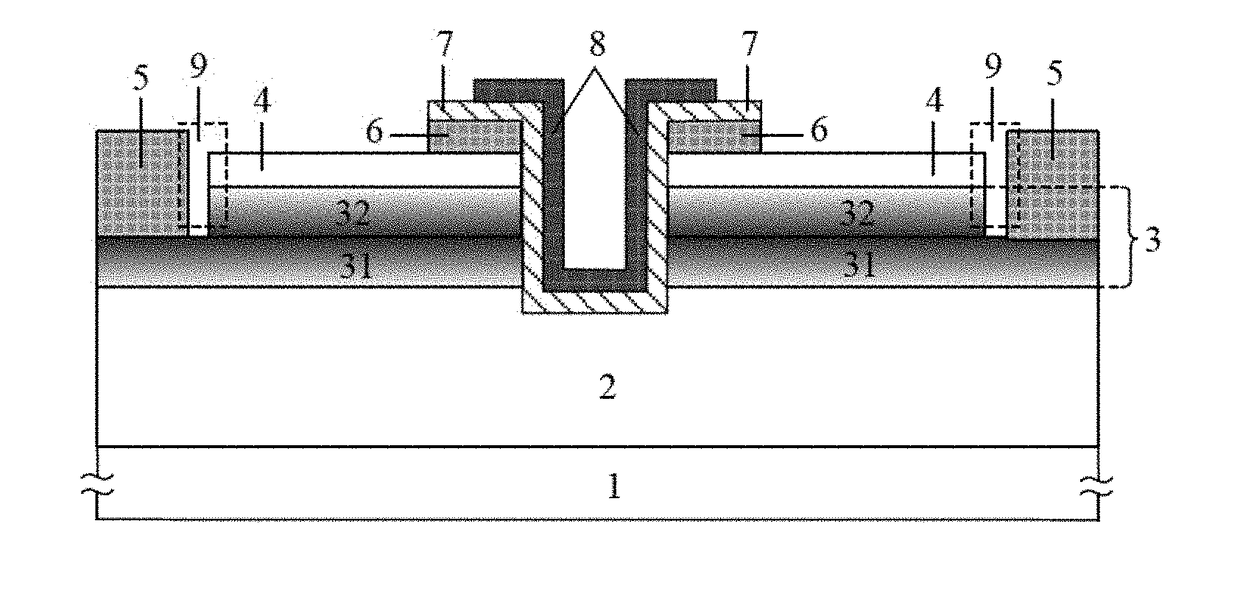

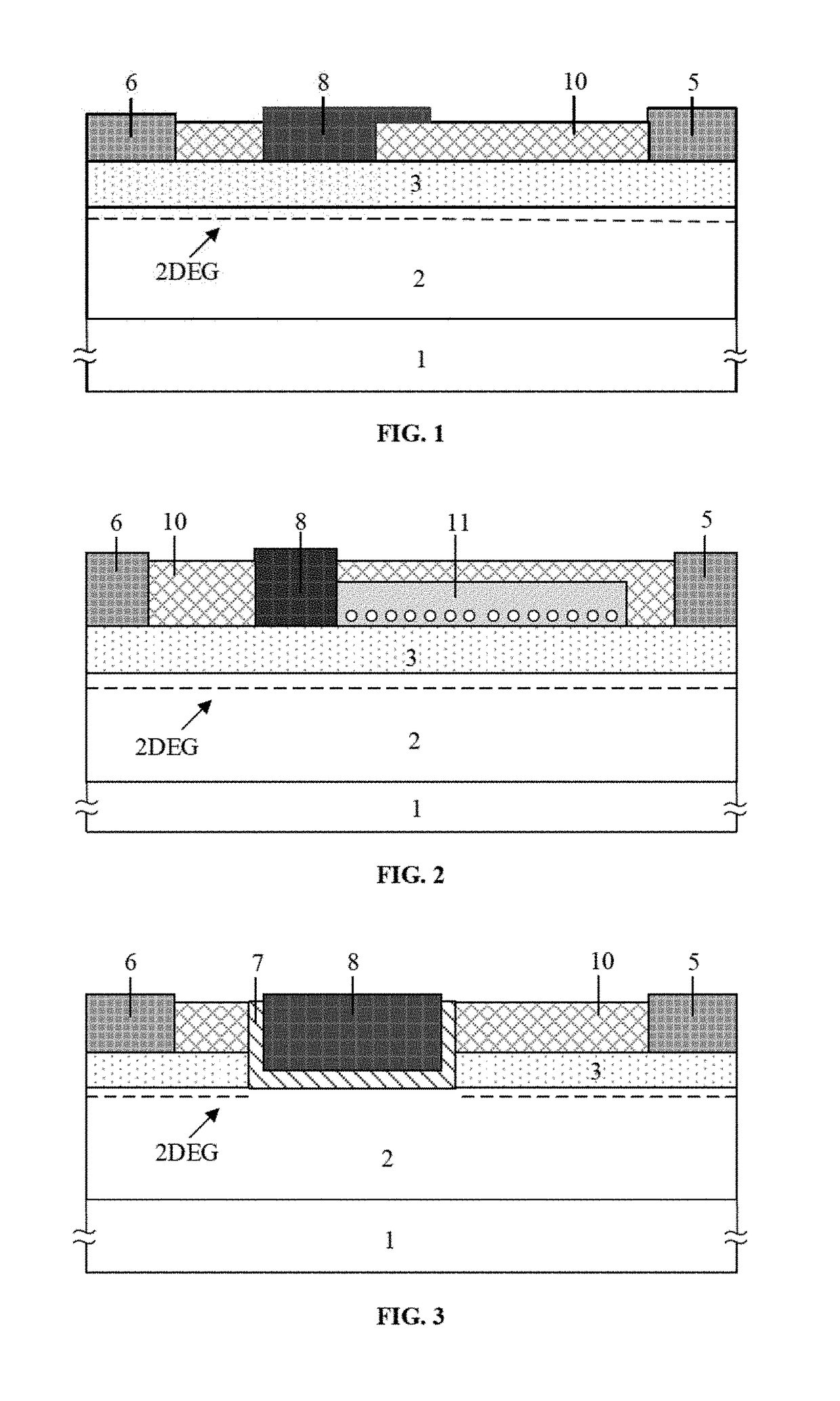

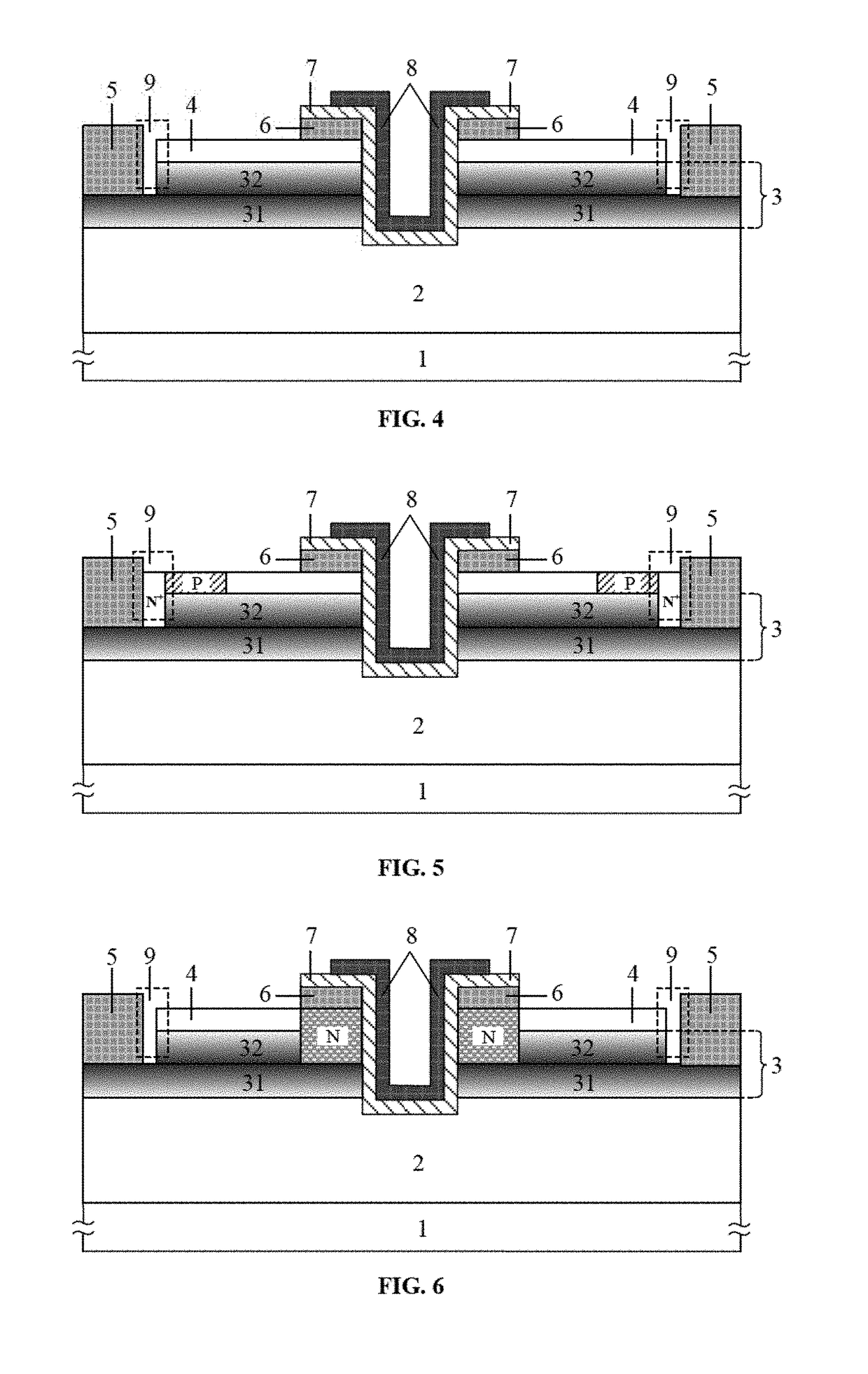

Polarization-doped enhancement mode HEMT

InactiveUS20180294335A1Assists depletionBreakdown voltage of deviceSemiconductor devicesSemiconductorSemiconductor technology

The present invention belongs to the field of semiconductor technology and relates to a polarization-doped enhancement mode HEMT device. The technical solution of the present invention grows the first barrier layer and the second barrier layer that contain gradient Al composition sequentially on the buffer layer. The gradient trends of the two layers are opposite. The three-dimensional electron gas (3DEG) and the three-dimensional hole gas (3DHG) are induced and generated in the barrier layers due to the inner polarization difference respectively. A trench insulated gate structure is at one side of the source which is away from the metal drain and is in contact with the source. First, since the highly concentrated electrons exist in the entire first barrier layer, the on-state current is improved greatly. Second, the vertical conductive channel between the source and the 3DEG are pinched off by the 3DHG, so as to realize the enhancement mode.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Method for manufacturing an edge termination for a silicon carbide power semiconductor device

ActiveUS20180108789A1Easy to manufactureEffective preventionSemiconductor devicesPower semiconductor deviceOptoelectronics

A method for manufacturing an edge termination structure for a silicon carbide power semiconductor device having a central region and an edge region is provided. The following manufacturing steps are performed: a) providing an n-doped silicon carbide substrate, b) epitaxially growing a silicon carbide n-doped drift layer on the substrate, which has a lower doping concentration than the substrate, c) creating at least one p-doped termination layer by implanting a second ion up to a maximum termination layer depth and annealing on the first main side, d) forming a doping reduction layer having a depth range, which doping reduction layer comprises at least one doping reduction region, wherein a depth of a doping concentration minimum of the doping reduction layer is greater than the maximum termination layer depth, wherein for the creation of each doping reduction region: implanting a first ion with an implantation energy in the drift layer at least in the edge region, wherein the first ion and the at least one implantation energy are chosen such that the doping reduction layer depth range is less than 10 μm, e) annealing the doping reduction layer, wherein step d) and e) are performed such that the doping concentration of the drift layer is reduced in the doping reduction layer.

Owner:HITACHI ENERGY SWITZERLAND AG

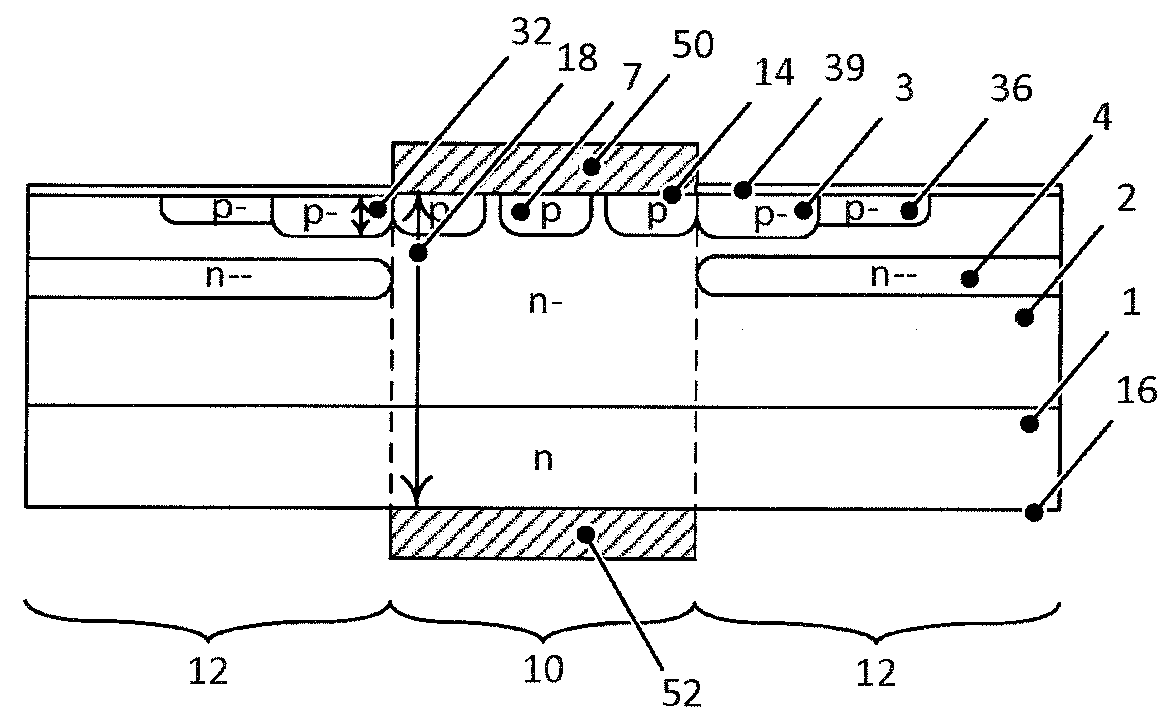

Stabilizing breakdown voltages by forming tunnels for ultra-high voltage devices

InactiveUS7768071B2High voltageBreakdown voltage of deviceTransistorSemiconductor/solid-state device detailsSemiconductor structureUltra high voltage

A semiconductor structure includes a semiconductor substrate of a first conductivity type; a pre-high-voltage well (pre-HVW) in the semiconductor substrate, wherein the pre-HVW is of a second conductivity type opposite the first conductivity type; a high-voltage well (HVW) over the pre-HVW, wherein the HVW is of the second conductivity type; a field ring of the first conductivity type occupying a top portion of the HVW; and a tunnel of the first conductivity type in the pre-HVW and the HVW, and electrically connecting the field ring and the semiconductor substrate.

Owner:TAIWAN SEMICON MFG CO LTD

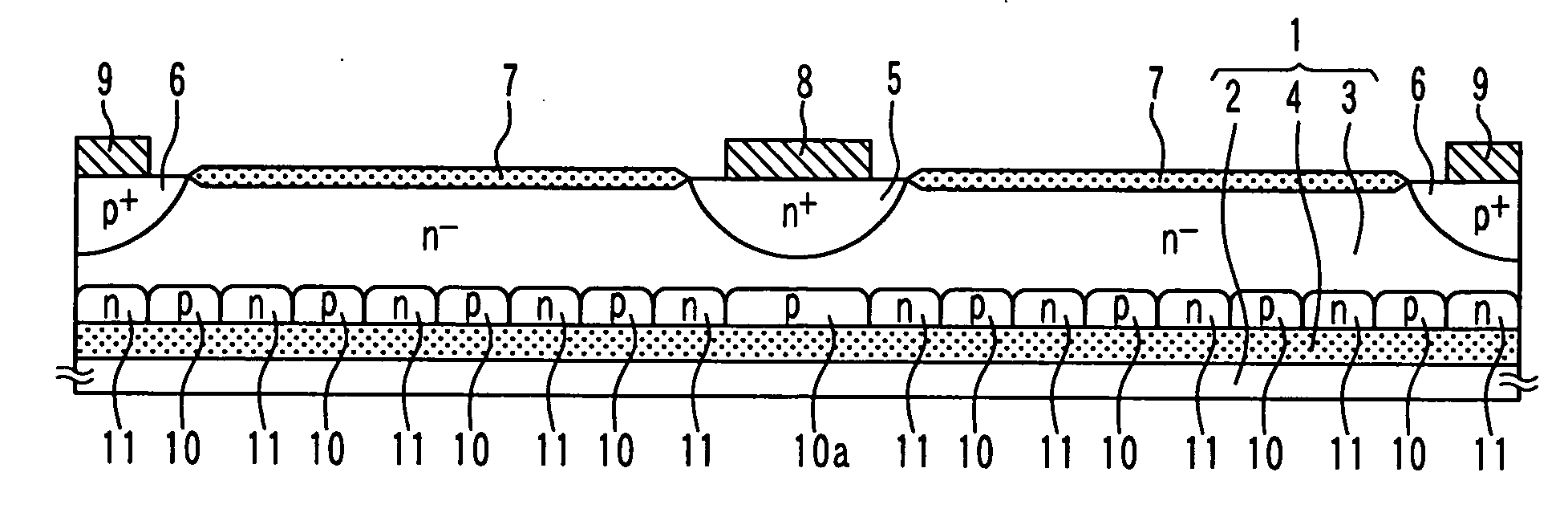

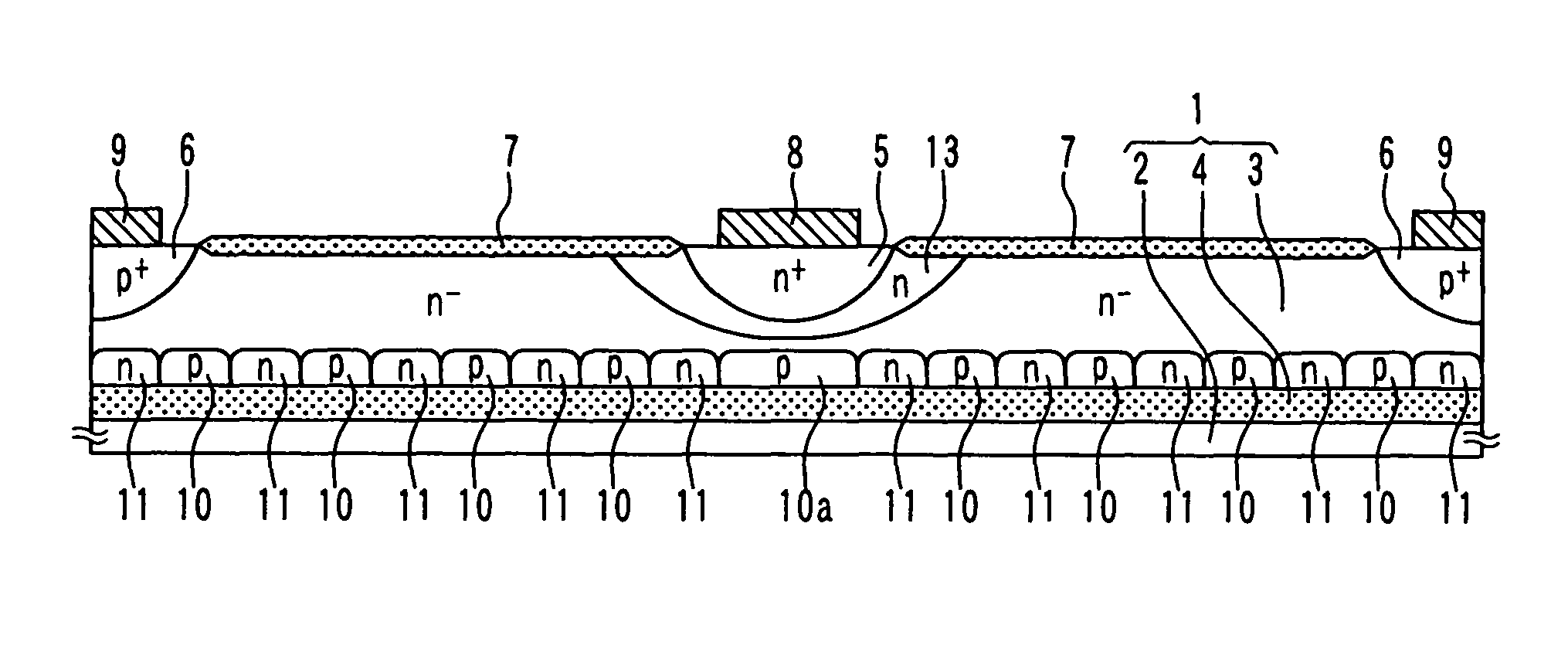

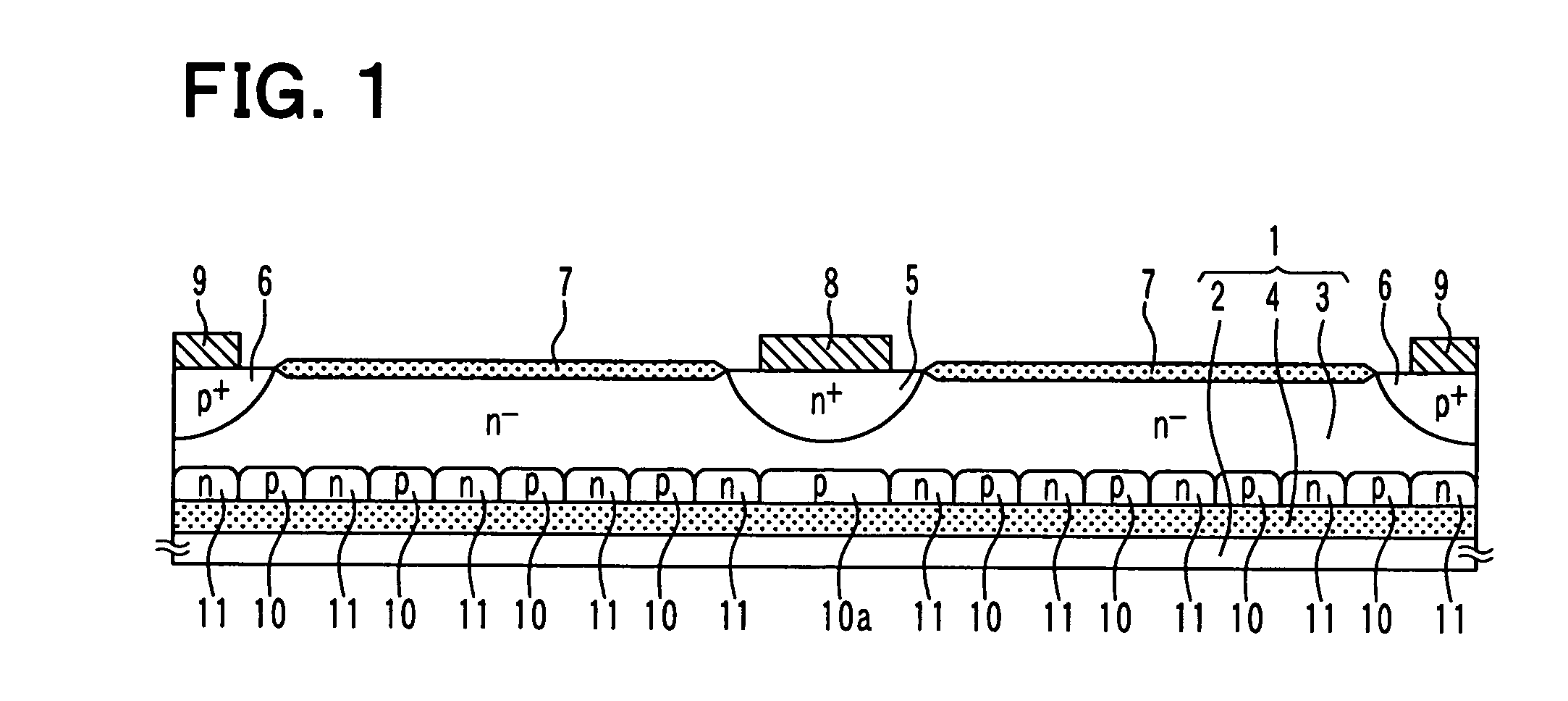

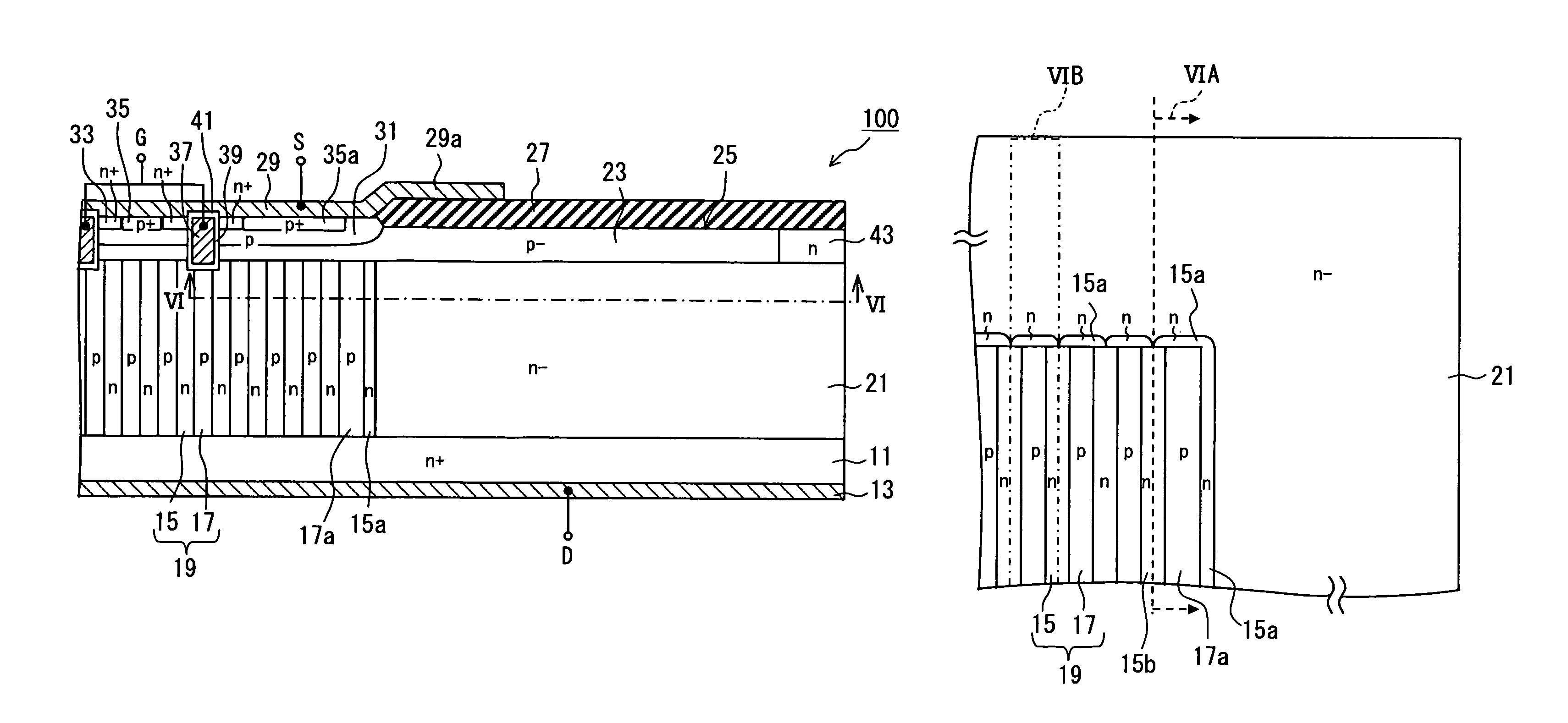

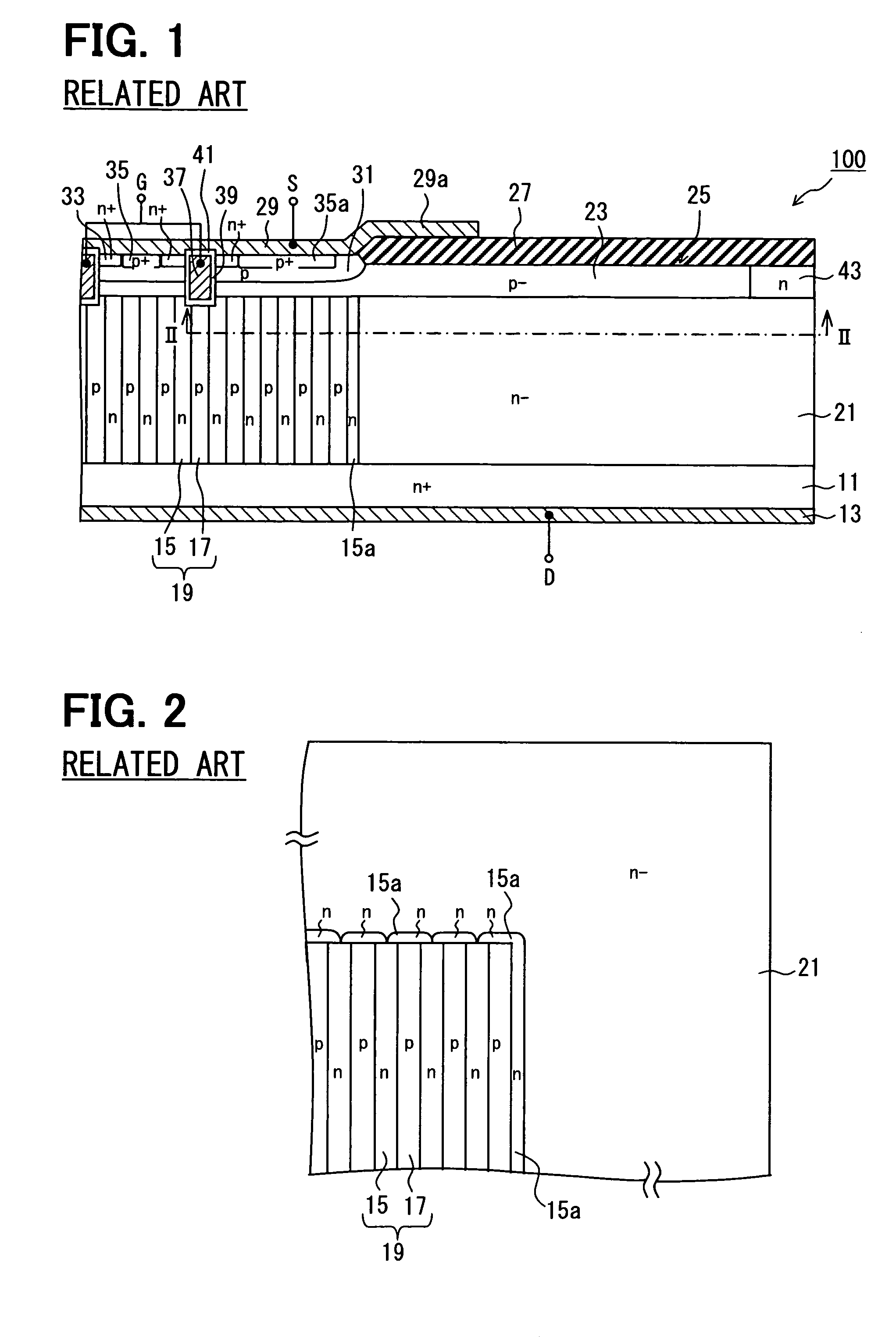

Seminconductor device having P-N column portion

InactiveUS20090032965A1Breakdown voltage of deviceImprove breakdown voltageSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorOptoelectronics

A semiconductor device includes: a first semiconductor layer; a p-n column portion over the first semiconductor layer and including second and third semiconductor layers, which are alternately arranged; and a peripheral portion adjacently to the p-n column portion and including a fourth semiconductor layer. An end second semiconductor layer has an impurity amount equal to or larger than a half of other second semiconductor layers. The third semiconductor layers include a large impurity amount portion adjacent to the end second semiconductor layer. The large impurity amount portion includes at least one third semiconductor layer having an impurity amount larger than an impurity amount of other third semiconductor layers.

Owner:DENSO CORP

Semiconductor device having SOI substrate and method for manufacturing the same

InactiveUS20110073904A1Prevent breakdown voltageReduced dimensionSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSoi substrate

A semiconductor device includes: a SOI substrate; a semiconductor element having first and second impurity layers disposed in an active layer of the SOI substrate, the second impurity layer surrounding the first impurity layer; and multiple first and second conductive type regions disposed in a part of the active layer adjacent to an embedded insulation film of the SOI substrate. The first and second conductive type regions are alternately arranged. The first and second conductive type regions have a layout, which corresponds to the semiconductor element.

Owner:DENSO CORP

Semiconductor device and manufactruing method therefor

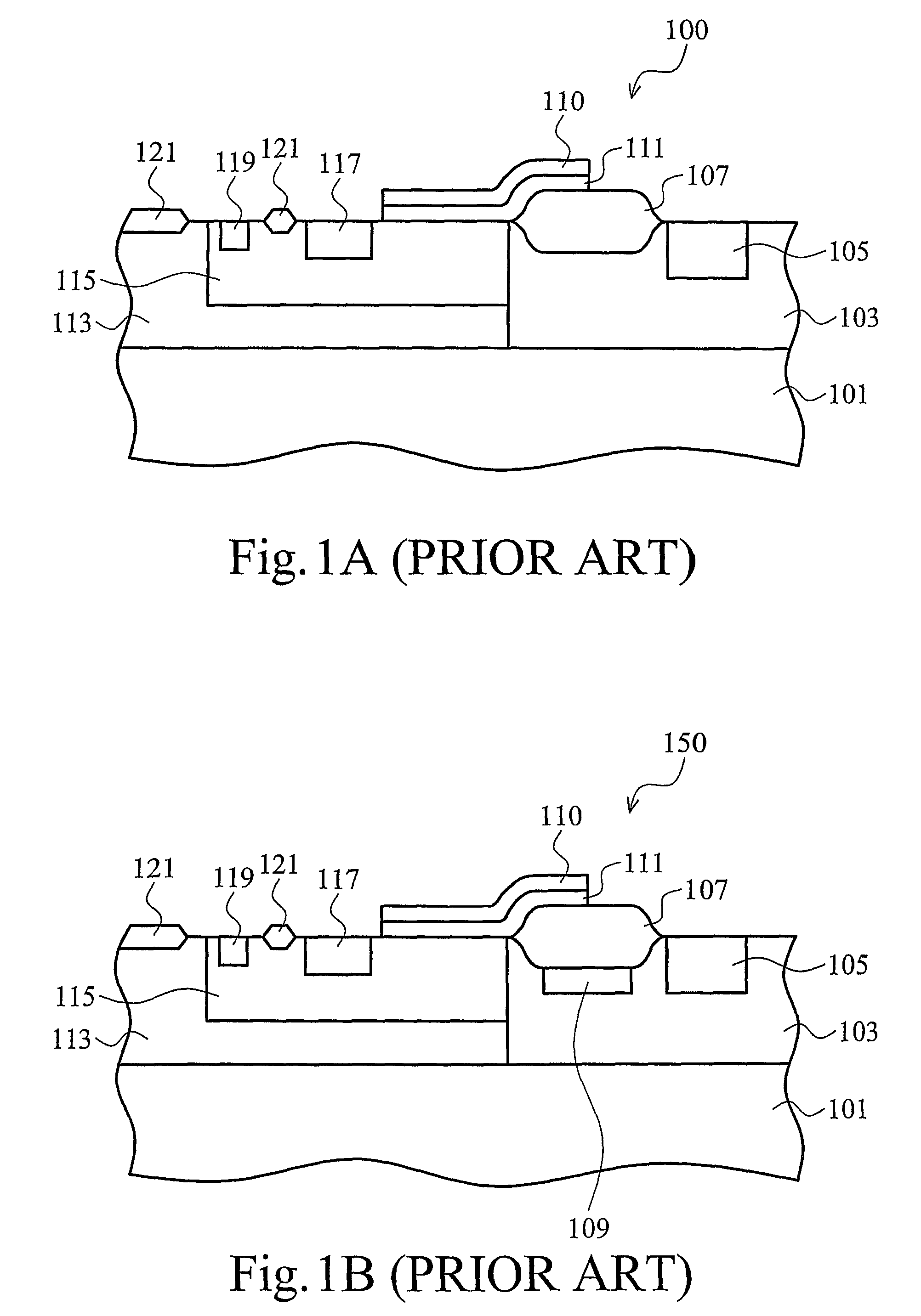

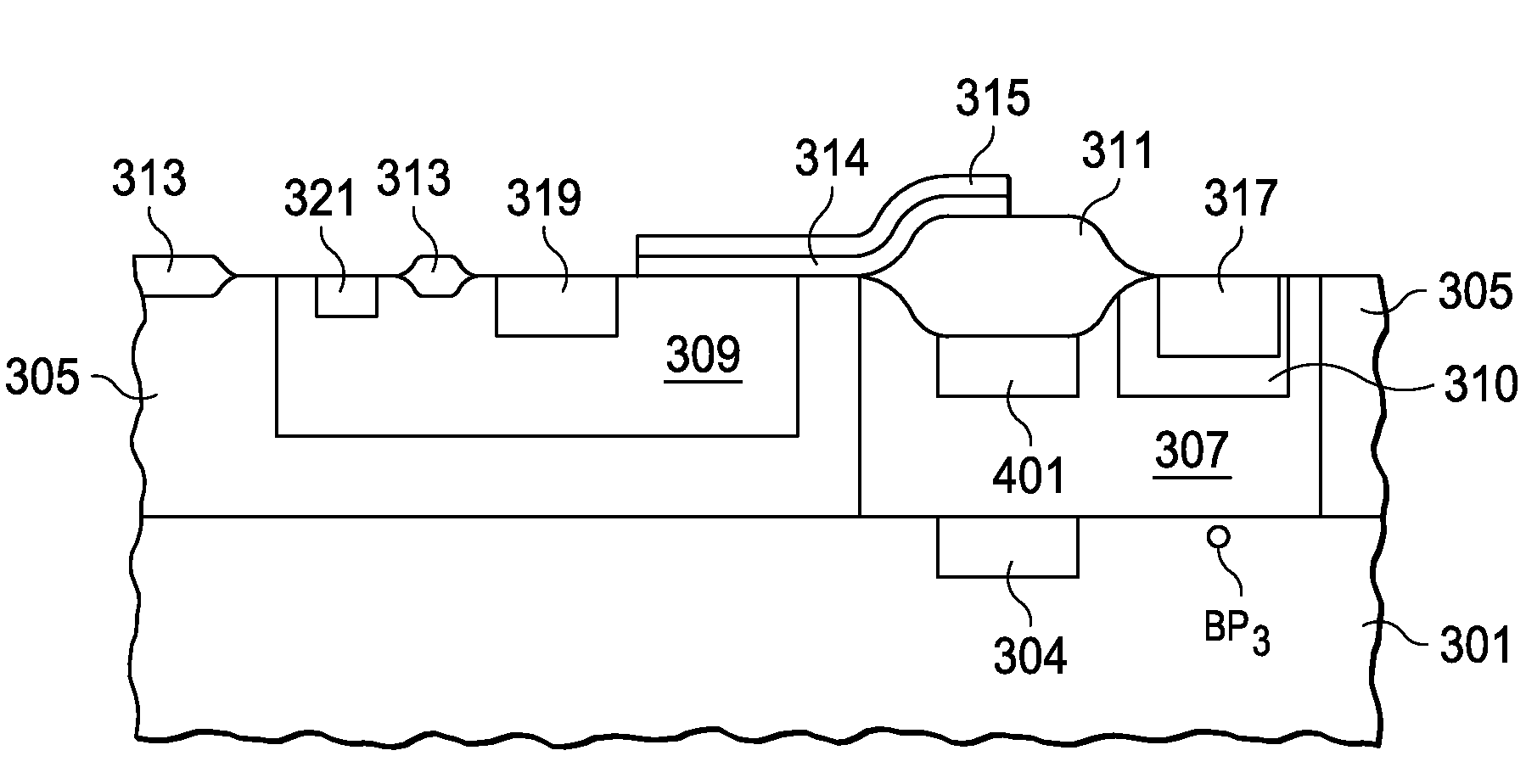

ActiveUS20030071317A1Improve breakdown voltageIncrease heightTransistorStatic indicating devicesPhysicsBuried oxide

An N-channel MOS field-effect transistor on an SOI substrate including a source electrode, drain and gate electrodes both disposed via a field oxide film, a gate oxide film, a high concentration P-type layer, a high concentration N-type layer contacting the source electrode and the gate oxide film, a high concentration N-type layer contacting the drain electrode, a p-body layer contacting the high concentration P-type and N-type layers and the gate oxide film. In this transistor, an N-type layer with a concentration higher than that of a drain region contacting the p-body layer constitutes a region covering at most 95% of the source-drain distance. Further, an N-type region having a concentration from 3.times.10.sup.16 / cm.sup.3 to 1.times.10.sup.22 / cm.sup.3 is provided near a buried oxide film under the drain electrode.

Owner:HITACHI LTD

Lateral power MOSFET with high breakdown voltage and low on-resistance

InactiveUS7989890B2Improve performance and efficiencyOn-resistance of the device is reducedSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structurePower MOSFET

A semiconductor structure includes a semiconductor substrate of a first conductivity type; a pre-high-voltage well (pre-HVW) in the semiconductor substrate, wherein the pre-HVW is of a second conductivity type opposite the first conductivity type; a high-voltage well (HVW) over the pre-HVW, wherein the HVW is of the second conductivity type; a field ring in the HVW and occupying a top portion of the HVW, wherein the field ring is of the first conductivity type; an insulation region over and in contact with the field ring and a portion of the HVW; a gate electrode partially over the insulation region; a drain region in the HVW, wherein the drain region is of the second conductivity type; and wherein the HVW horizontally extends further toward the drain region than the pre-HVW; and a source region adjacent to, and on an opposite side of the gate electrode than the drain region.

Owner:TAIWAN SEMICON MFG CO LTD

Lateral power MOSFET with high breakdown voltage and low on-resistance

ActiveUS7476591B2Improve performance and efficiencyOn-resistance of the device is reducedSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricGate dielectric

Owner:TAIWAN SEMICON MFG CO LTD

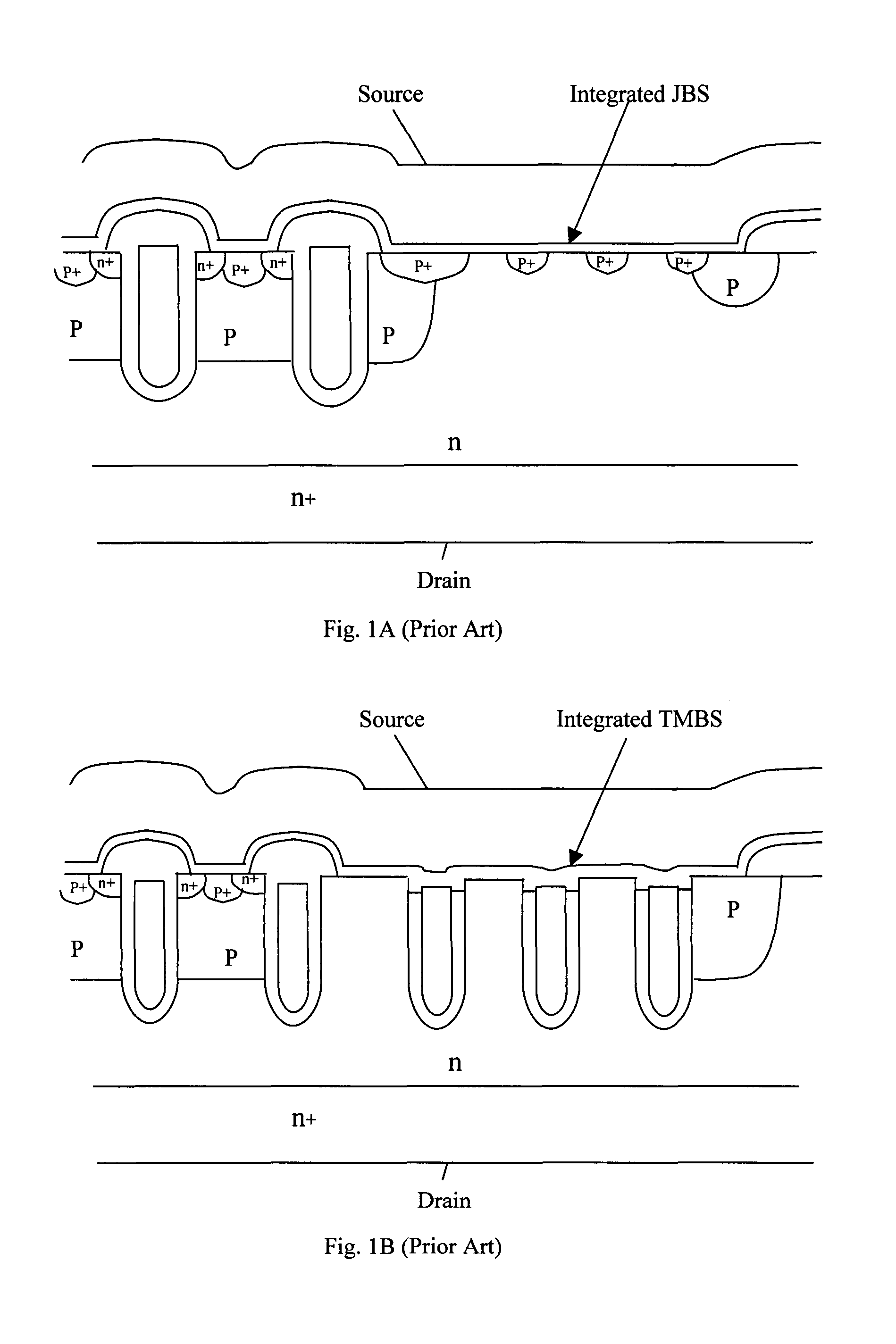

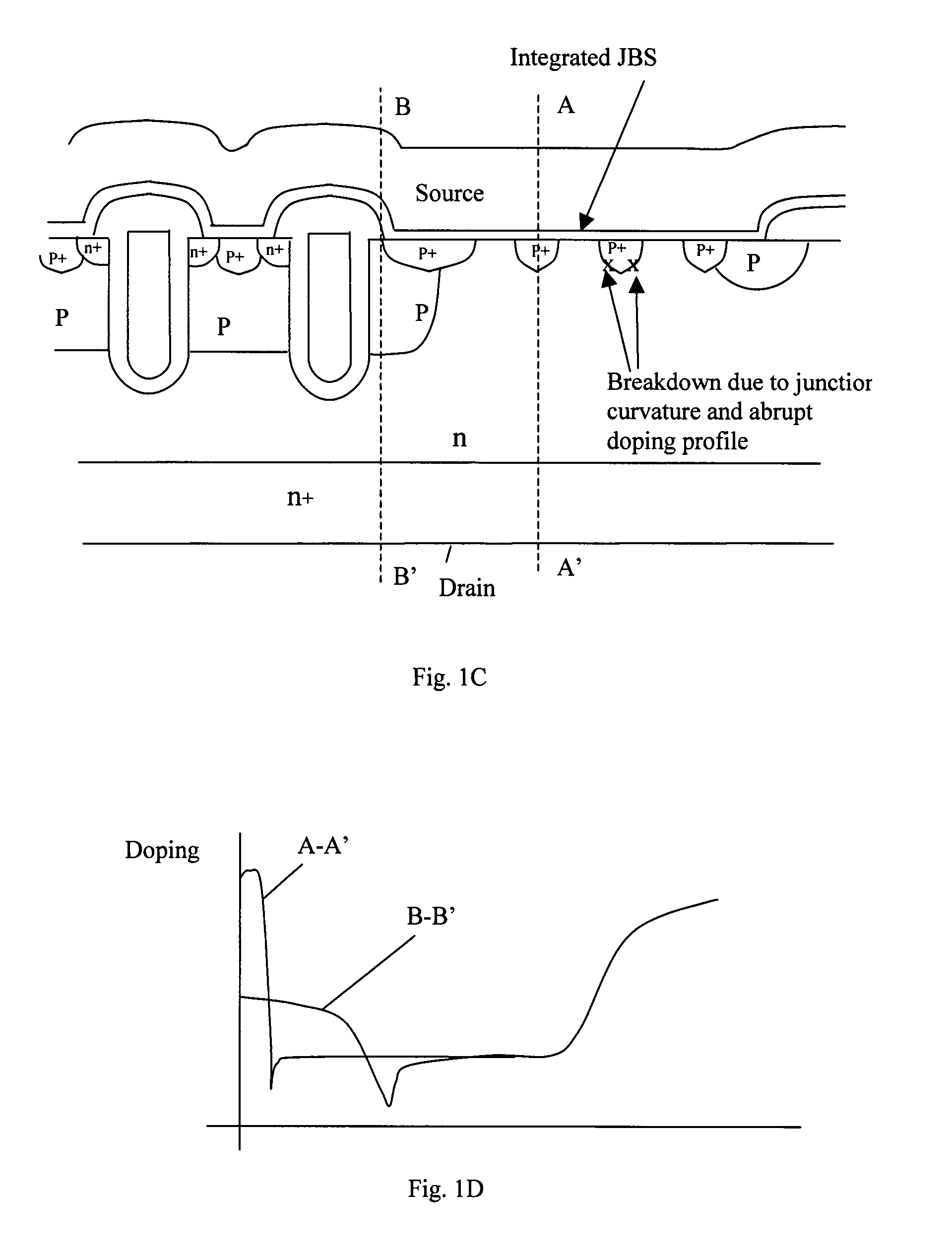

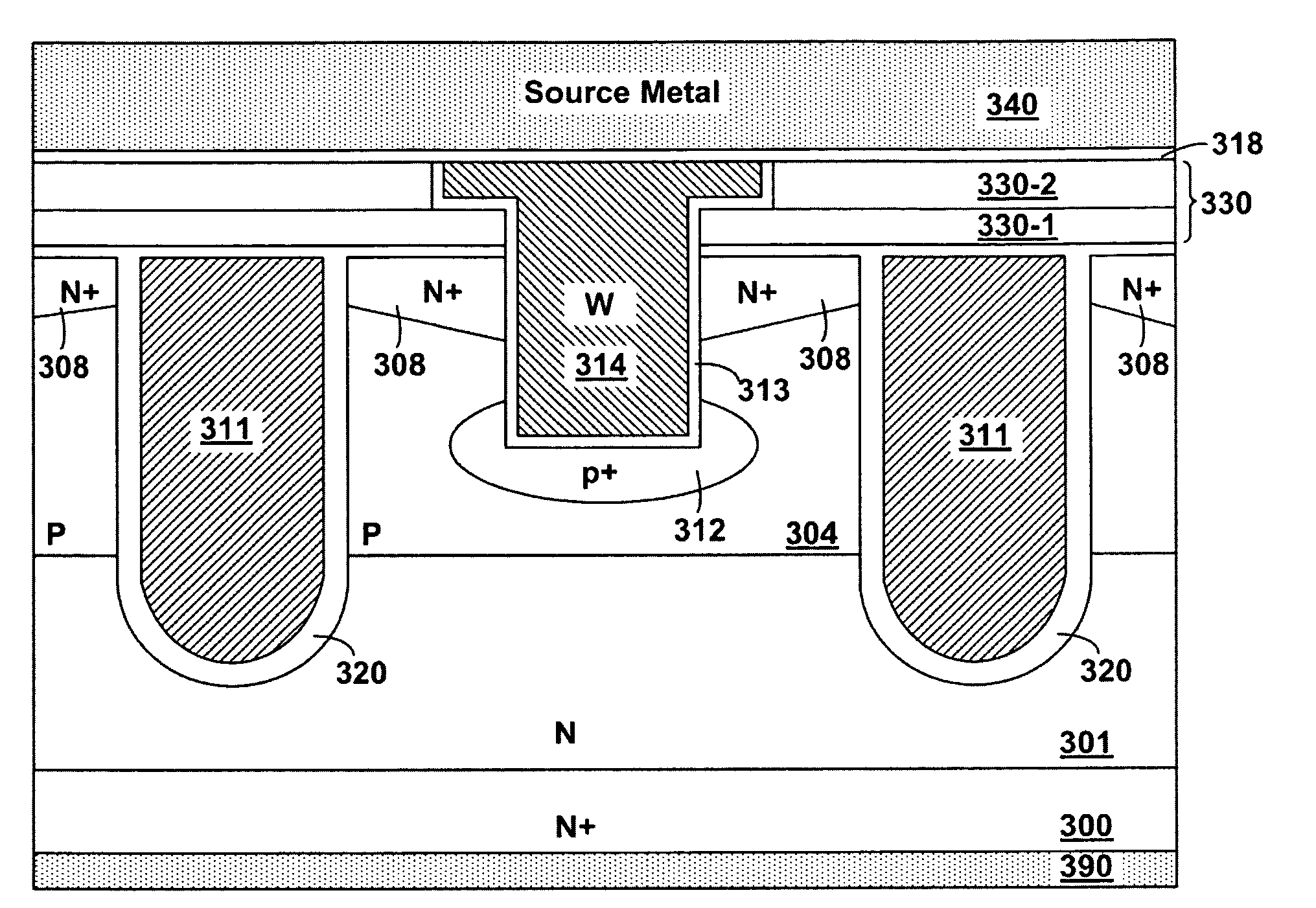

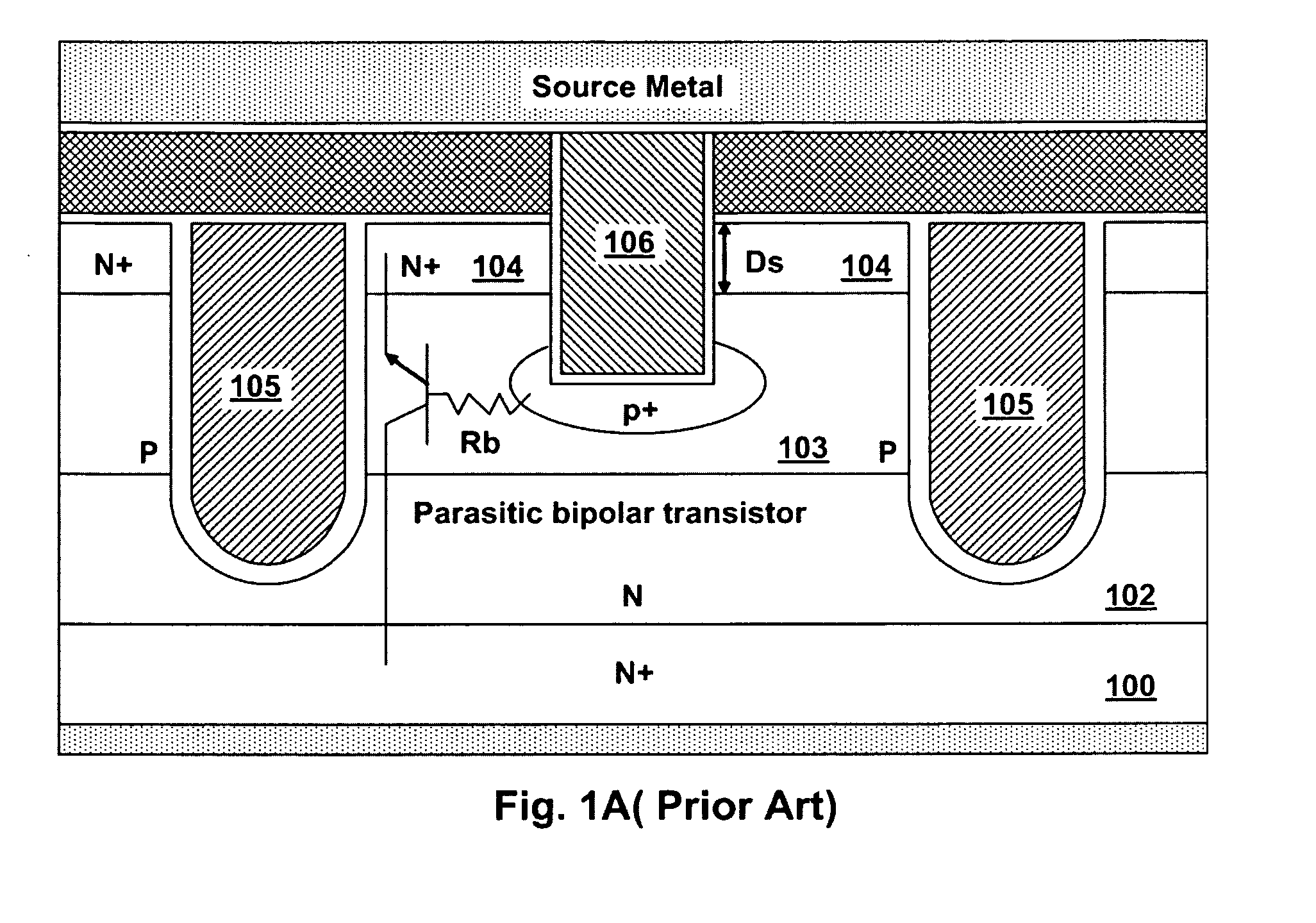

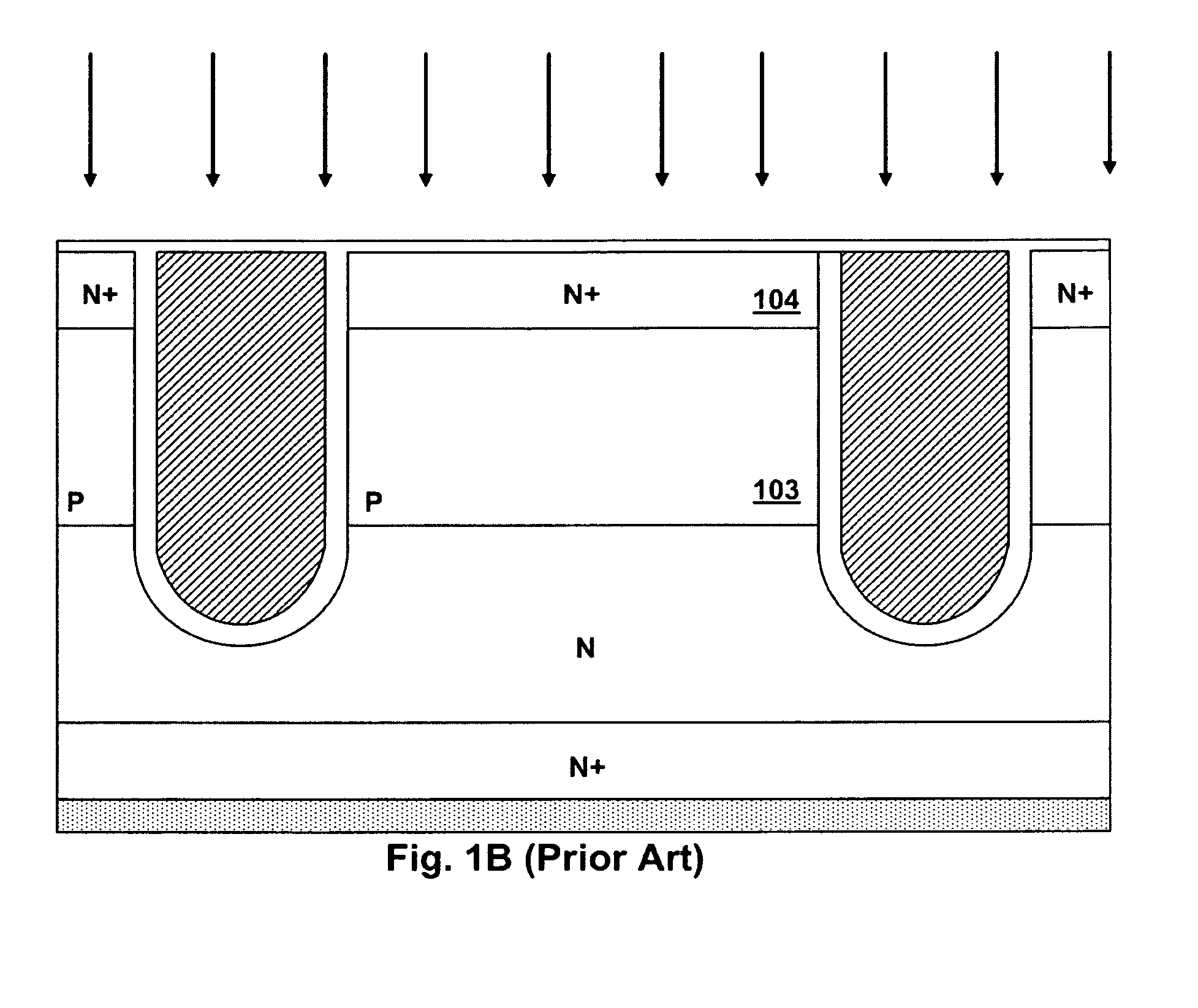

Method of making a trench MOSFET having improved avalanche capability using three masks process

ActiveUS8222108B2Reduce doping concentrationReduces Emitter injection efficiencyTransistorSemiconductor/solid-state device manufacturingTrench mosfetBody contact

Owner:FORCE MOS TECH CO LTD

Semiconductor device having SOI substrate

InactiveUS8604513B2Breakdown voltage of deviceImprove breakdown voltageSolid-state devicesSemiconductor/solid-state device manufacturingSoi substrateActive layer

A semiconductor device includes: a SOI substrate; a semiconductor element having first and second impurity layers disposed in an active layer of the SOI substrate, the second impurity layer surrounding the first impurity layer; and multiple first and second conductive type regions disposed in a part of the active layer adjacent to an embedded insulation film of the SOI substrate. The first and second conductive type regions are alternately arranged. The first and second conductive type regions have a layout, which corresponds to the semiconductor element.

Owner:DENSO CORP

High-voltage Nitride Device and Manufacturing Method Thereof

ActiveUS20150340485A1Improve breakdown voltageIncrease the electric field strengthSemiconductor/solid-state device manufacturingSemiconductor devicesNitrideSilicon

A high-voltage nitride device which can avoid vertical breakdown and has a high breakdown voltage includes: a silicon substrate; a nitride epitaxial layer, prepared on the silicon substrate; a source electrode and a drain electrode, both of which are contacted with the nitride epitaxial layer; a gate electrode, prepared between the source electrode and the drain electrode; and, at least one spatial isolation area, formed in a region between the silicon substrate and the nitride epitaxial layer vertically and between the source electrode and the drain electrode horizontally.

Owner:ENKRIS SEMICON

Planar SRFET using no additional masks and layout method

ActiveUS8836015B2Improved body diode recovery behaviorLess voltage oscillationSemiconductor/solid-state device manufacturingDiodeDopantControl layer

A semiconductor power device is supported on a semiconductor substrate with a bottom layer functioning as a bottom electrode and an epitaxial layer overlying the bottom layer as the bottom layer. The semiconductor power device includes a plurality of FET cells and each cell further includes a body region extending from a top surface into the epitaxial layer. The body region encompasses a heavy body dopant region. An insulated gate is disposed on the top surface of the epitaxial layer, overlapping a first portion of the body region. A barrier control layer is disposed on the top surface of the epitaxial layer next to the body region away from the insulated gate. A conductive layer overlies the top surface of the epitaxial layer covering a second portion of the body region and the heavy body dopant region extending over the barrier control layer forming a Schottky junction diode.

Owner:ALPHA & OMEGA SEMICON INC

High voltage semiconductor device and method of manufacturing same

PendingUS20220367711A1Reduce and prevent deteriorationBreakdown voltage of deviceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialMaterials science

Disclosed is a high voltage semiconductor device and a method of manufacturing the same and, more particularly, to a high voltage semiconductor device and a method of manufacturing the same that enables an improvement in the breakdown voltage relative to the on-resistance by forming a top region in or at the surface of the substrate when the device includes a field plate adjacent to a gate electrode.

Owner:DONGBU HITEK CO LTD

Semiconductor device having p-n column portion

InactiveUS7838995B2Breakdown voltage of deviceImprove breakdown voltageSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor

A semiconductor device includes: a first semiconductor layer; a p-n column portion over the first semiconductor layer and including second and third semiconductor layers, which are alternately arranged; and a peripheral portion adjacently to the p-n column portion and including a fourth semiconductor layer. An end second semiconductor layer has an impurity amount equal to or larger than a half of other second semiconductor layers. The third semiconductor layers include a large impurity amount portion adjacent to the end second semiconductor layer. The large impurity amount portion includes at least one third semiconductor layer having an impurity amount larger than an impurity amount of other third semiconductor layers.

Owner:DENSO CORP

Planar srfet using no additional masks and layout method

ActiveUS20160049392A1High cell densityImprove performanceTransistorSolid-state devicesBody regionEngineering

A semiconductor power device is supported on a semiconductor substrate of a first conductivity type with a bottom layer functioning as a bottom electrode and an epitaxial layer overlying the bottom layer with a same conductivity type as the bottom layer. The semiconductor power device includes a plurality of FET cells and each cell further includes a body region of a second conductivity type extending from a top surface into the epitaxial layer. The body region encompasses a heavy body dopant region of second conductivity type. An insulated gate is disposed on the top surface of the epitaxial layer, overlapping a first portion of the body region. A barrier control layer is disposed on the top surface of the epitaxial layer next to the body region away from the insulated gate. A conductive layer overlies the top surface of the epitaxial layer covering a second portion of the body region and the heavy body dopant region extending over the barrier control layer forming a Schottky junction diode.

Owner:ALPHA & OMEGA SEMICON INC

SOI semiconductor device

InactiveUS6885067B2High voltageReduce voltageTransistorStatic indicating devicesHigh concentrationEngineering

A power IC for an automobile engine control unit incorporating at least one semiconductor device comprising an N-channel insulated-gate filed-effect transistor formed on an SOI substrate, having an N-type layer having a concentration higher than a concentration of an N-type layer in contact with a p-body layer contacting a gate oxide film of the transistor. The high concentration N-type layer is formed in a region covering at most 95% of the source-drain distance between the p-body layer and a drain electrode of the transistor in the silicon substrate over an interface of a buried oxide film, the silicon substrate being in contact with both the field oxide film and the high concentration N-type layer contacting the drain electrode.

Owner:HITACHI LTD

Planar srfet using no additional masks and layout method

ActiveUS9455249B2Improved body diode recovery behaviorLess voltage oscillationTransistorSolid-state devicesDopantControl layer

Owner:ALPHA & OMEGA SEMICON INC

Method for manufacturing an edge termination for a silicon carbide power semiconductor device

ActiveUS10115834B2Easy to manufactureEffective preventionDiodePower semiconductor deviceOptoelectronics

A method for manufacturing an edge termination structure for a silicon carbide power semiconductor device having a central region and an edge region is provided. The following manufacturing steps are performed: a) providing an n-doped silicon carbide substrate, b) epitaxially growing a silicon carbide n-doped drift layer on the substrate, which has a lower doping concentration than the substrate, c) creating at least one p-doped termination layer by implanting a second ion up to a maximum termination layer depth and annealing on the first main side, d) forming a doping reduction layer having a depth range, which doping reduction layer comprises at least one doping reduction region, wherein a depth of a doping concentration minimum of the doping reduction layer is greater than the maximum termination layer depth, wherein for the creation of each doping reduction region: implanting a first ion with an implantation energy in the drift layer at least in the edge region, wherein the first ion and the at least one implantation energy are chosen such that the doping reduction layer depth range is less than 10 μm, e) annealing the doping reduction layer, wherein step d) and e) are performed such that the doping concentration of the drift layer is reduced in the doping reduction layer.

Owner:HITACHI ENERGY LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com