Methdo for fabricating bipolar type longitudinal plane mode transistors

A vertical plane and manufacturing method technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as high collector saturation voltage drop, large collector circuit series resistance, and affecting circuit integration density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

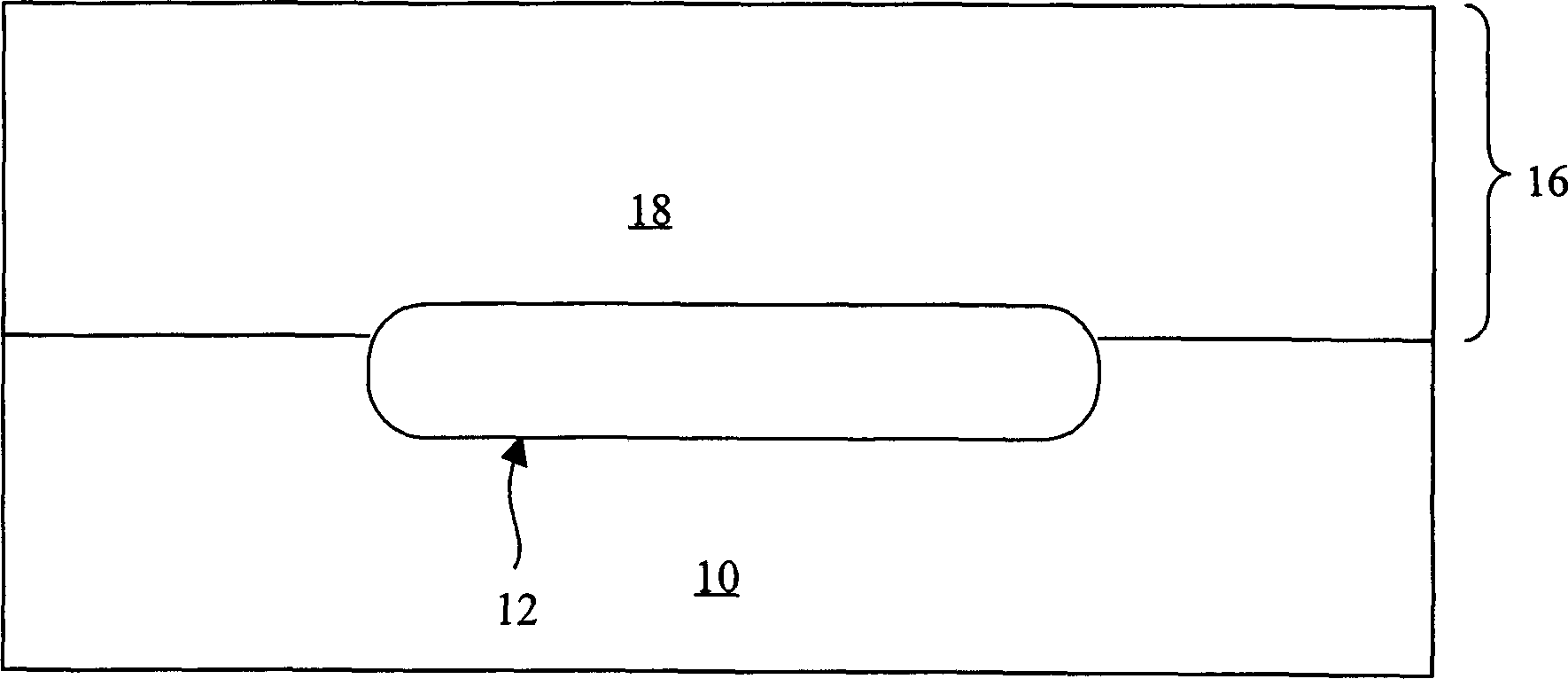

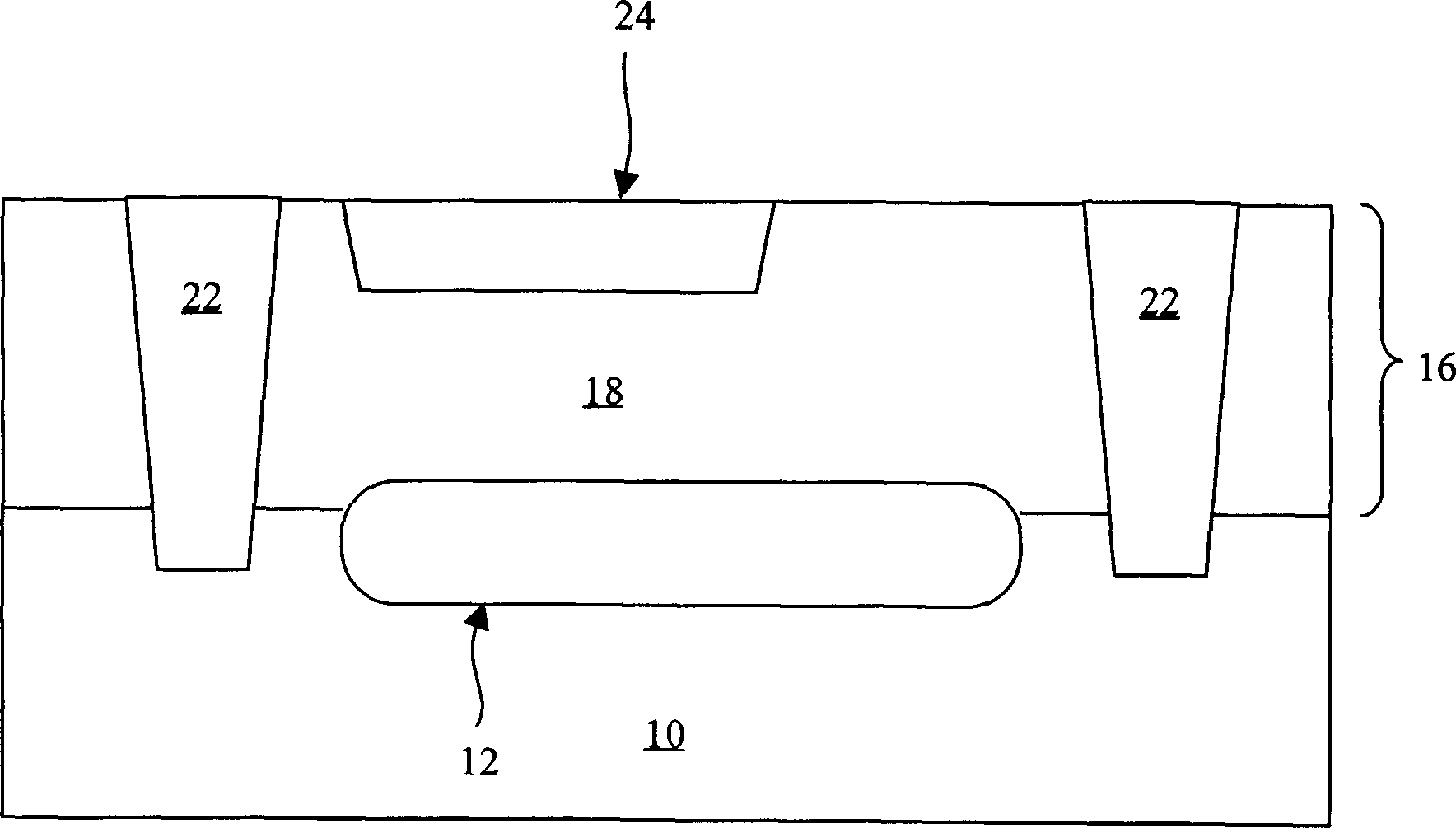

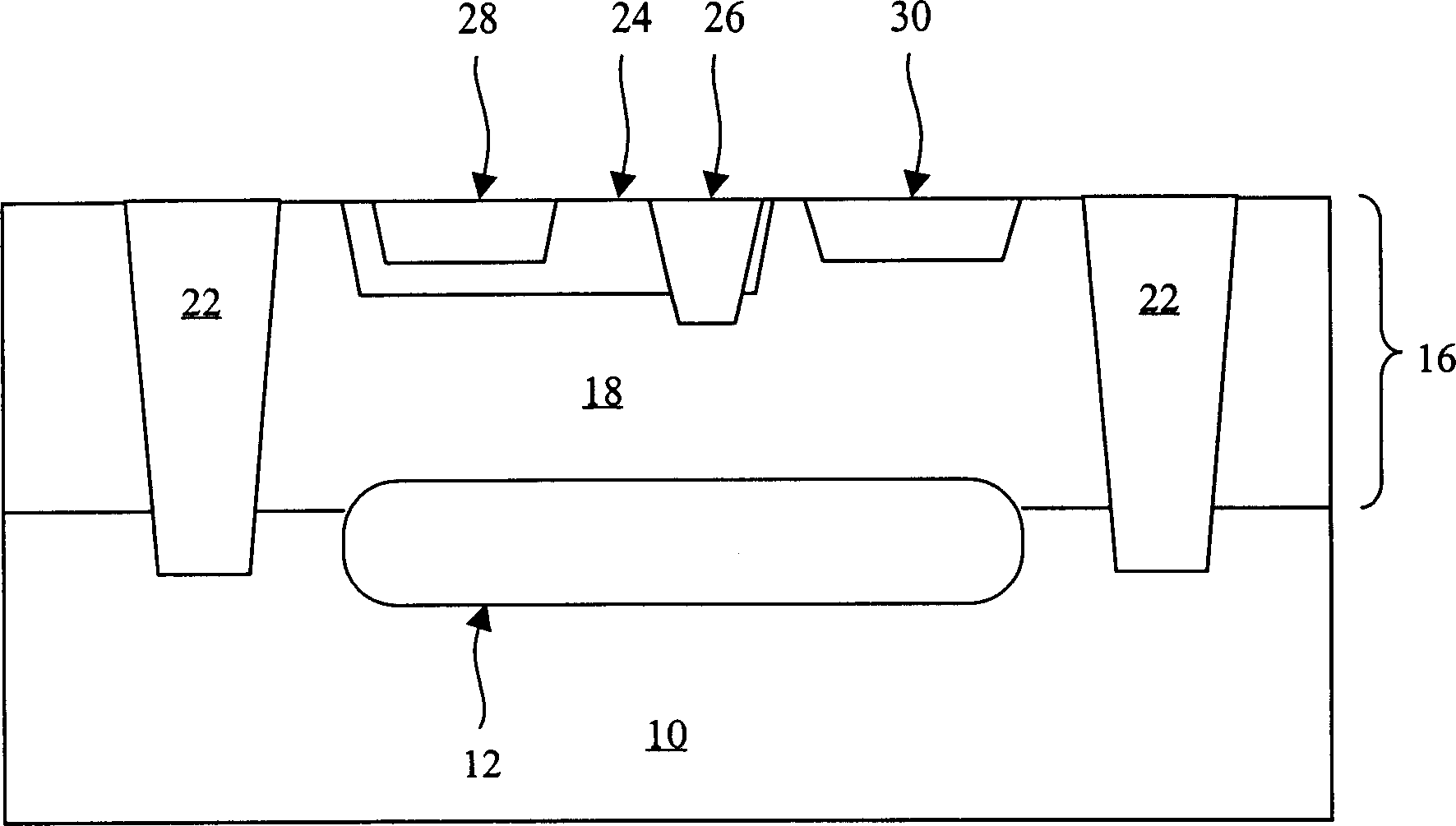

[0026] Figure 5 It is a sectional view of an NPN-type bipolar vertical planar transistor of the present invention. See Figure 5 , forming an N-type extrinsic collector region 52 on the top of the P-type semiconductor substrate 50; doping a P-type impurity element in the semiconductor substrate surrounding the extrinsic collector region 52 as a lower isolation layer 54 of the transistor; A part of the N-type epitaxial layer 56 is used as the intrinsic collector region 58 of the transistor; an N-type impurity element is doped on the top of the epitaxial layer 56 as a plug 60 connecting the extrinsic collector region 52; on the top of the epitaxial layer 56 P-type impurity elements are doped as the upper isolation layer 62 of the isolation transistor, and the upper isolation layer 62 and the lower isolation layer 54 are overlapped, and after a certain high temperature treatment, the upper and lower isolation layers are connected to play an isolation role; The top of layer 56 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More