NPN transistor and fabricating method thereof

A technology of transistors and manufacturing methods, applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as lateral and transient diffusion effects, and achieve the effects of reducing lateral and transient diffusion and reducing series resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

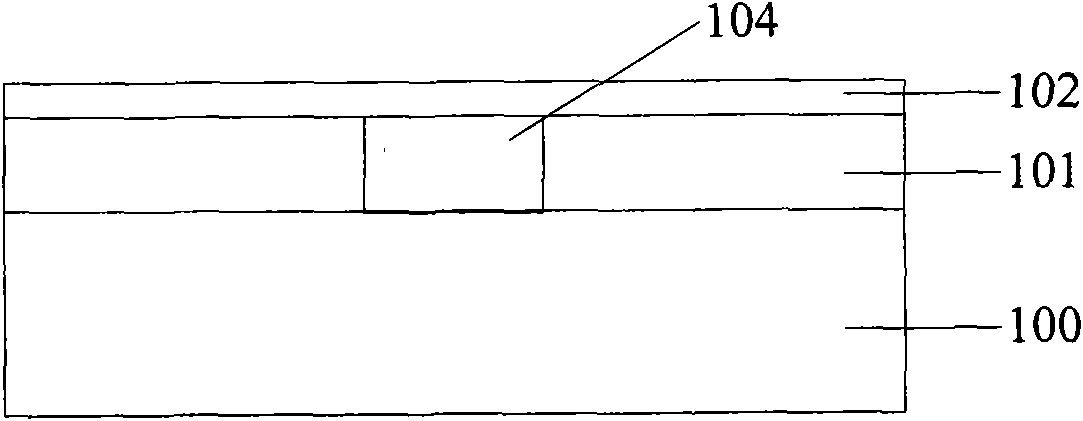

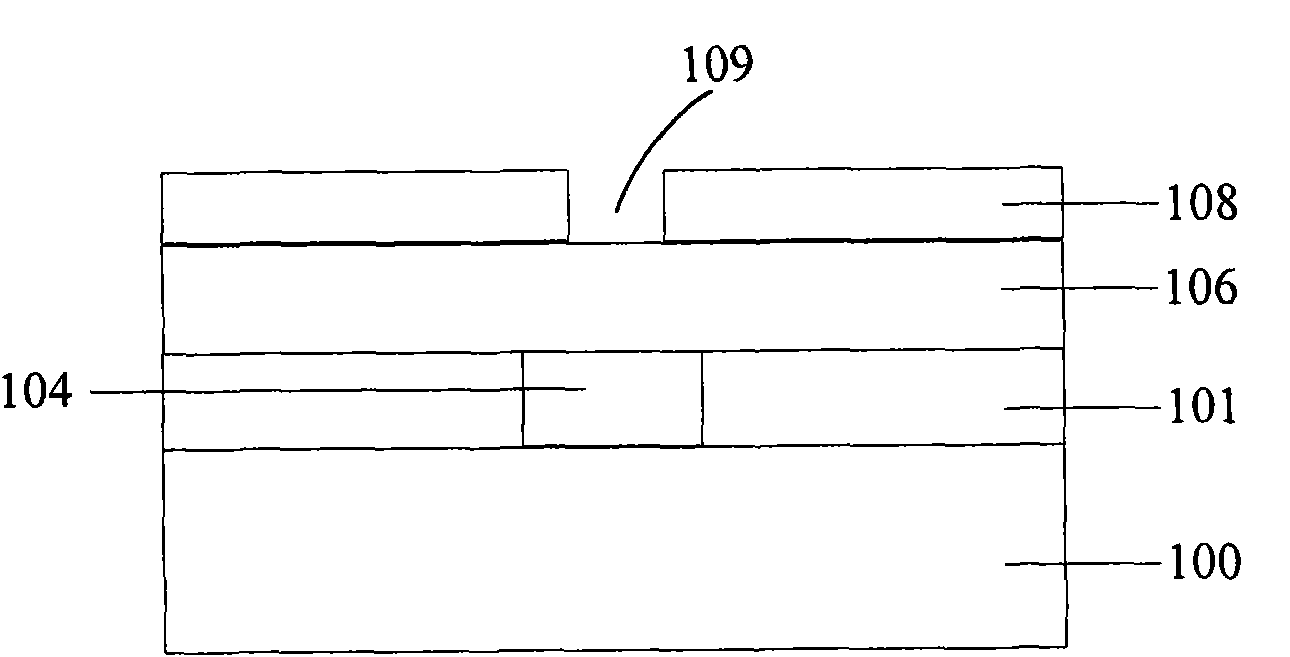

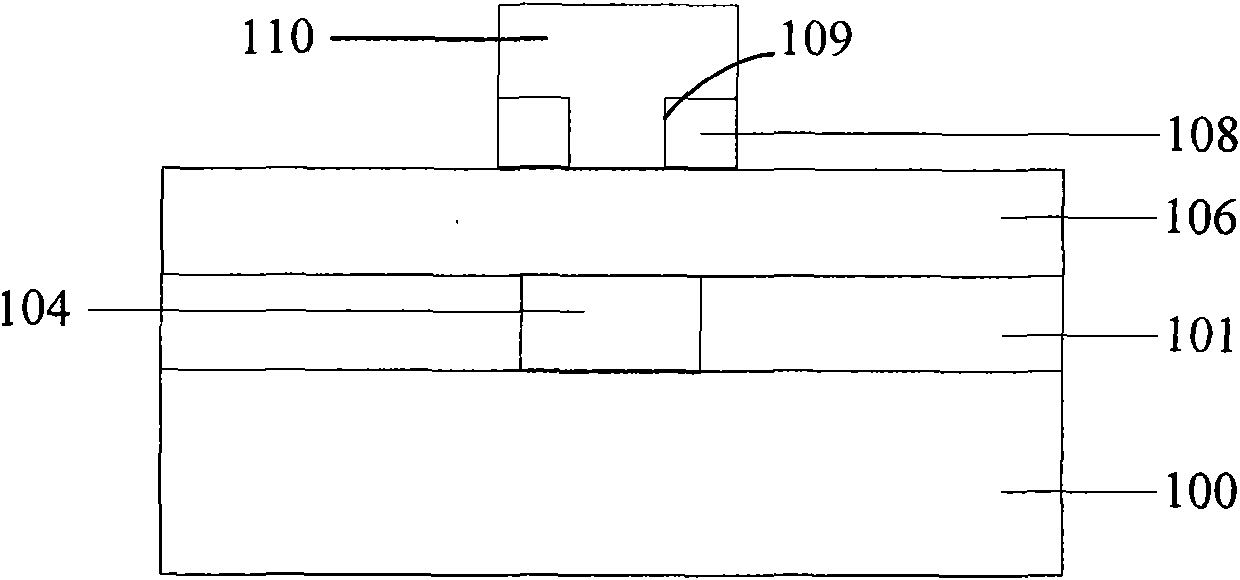

[0016] The specific implementation flow process of forming NPN transistor in the present invention is as follows Figure 5 As shown, step S1 is performed to provide a semiconductor substrate, and an N-type buried layer region is formed in the semiconductor substrate; step S2 is performed to form a first oxide layer on the N-type buried layer region, and the N-type buried layer region Implanting ions to form a collector; performing step S3, after removing the first oxide layer, forming a P-type epitaxial layer on the N-type buried layer region as a base; performing step S4, forming a contact hole on the P-type epitaxial layer After the second oxide layer, a polysilicon layer that fills the contact hole and covers the second oxide layer is formed; step S5 is performed to etch the polysilicon layer and the second oxide layer to expose the P-type epitaxial layer, and the etched polysilicon layer is used as Emitter; perform step S6, form shallowly doped metal contacts in the base o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More