Structure of channel shielded Rom memory unit and producing method thereof

A technology of read-only memory and storage unit, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc. It can solve the problems of lateral diffusion of impurities and uneven distribution of ions, reduction of the width of depletion regions, decline of product qualification rate, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

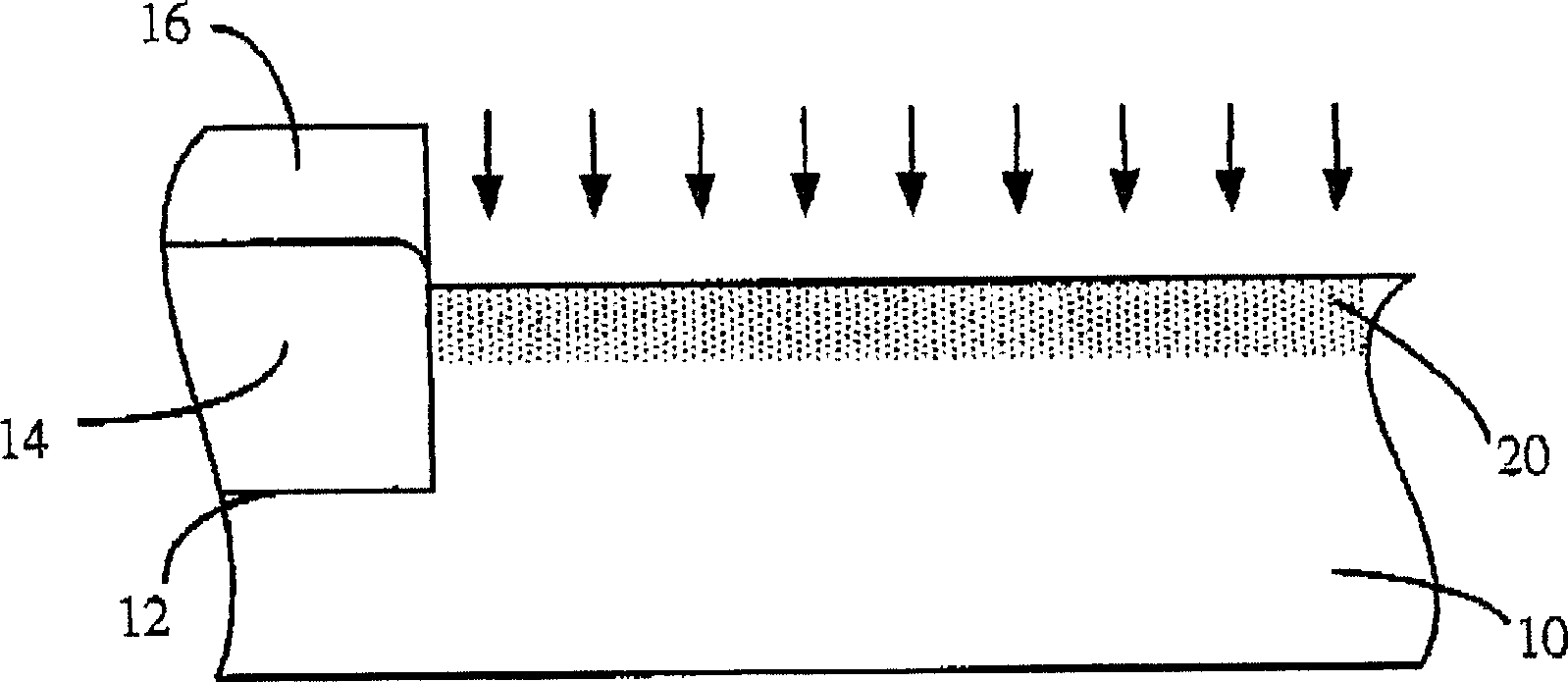

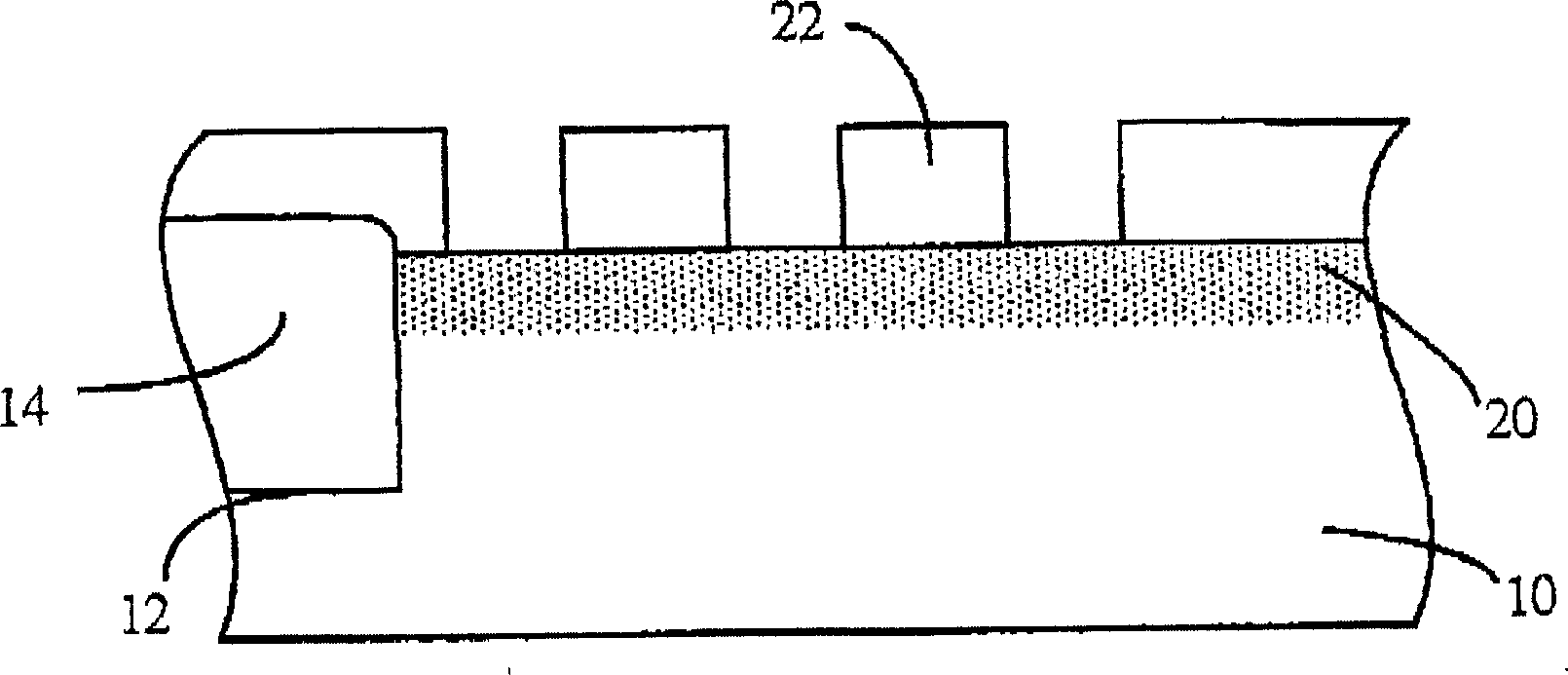

[0011] see Figure 1A Firstly, a silicon substrate 10 is provided, and a shallow trench isolation structure is formed in the silicon substrate 10, and a shallow trench isolation (shallow trench isolation, STI) process is used to form a shallow trench isolation (STI) process on the silicon substrate by using lithography and etching processes. A shallow trench isolation 12 is formed in 10, and then a shallow trench isolation oxide (STI oxide) 14 is formed to fill the shallow trench isolation 12 by chemical vapor deposition (CVD) process.

[0012] see again Figure 1B , forming a patterned photoresist 16 on the silicon substrate 10 by lithography etching to cover the shallow trench isolation oxide layer 14, and performing an ion implantation step, the ion implantation step is to simultaneously perform a buried ion doping impurity and breakdown-resistant ion doping, wherein the buried-type ion doping is to implant buried N-type (buried N+) ions into the silicon substrate 10, and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More