Patents

Literature

55results about How to "Good component properties" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

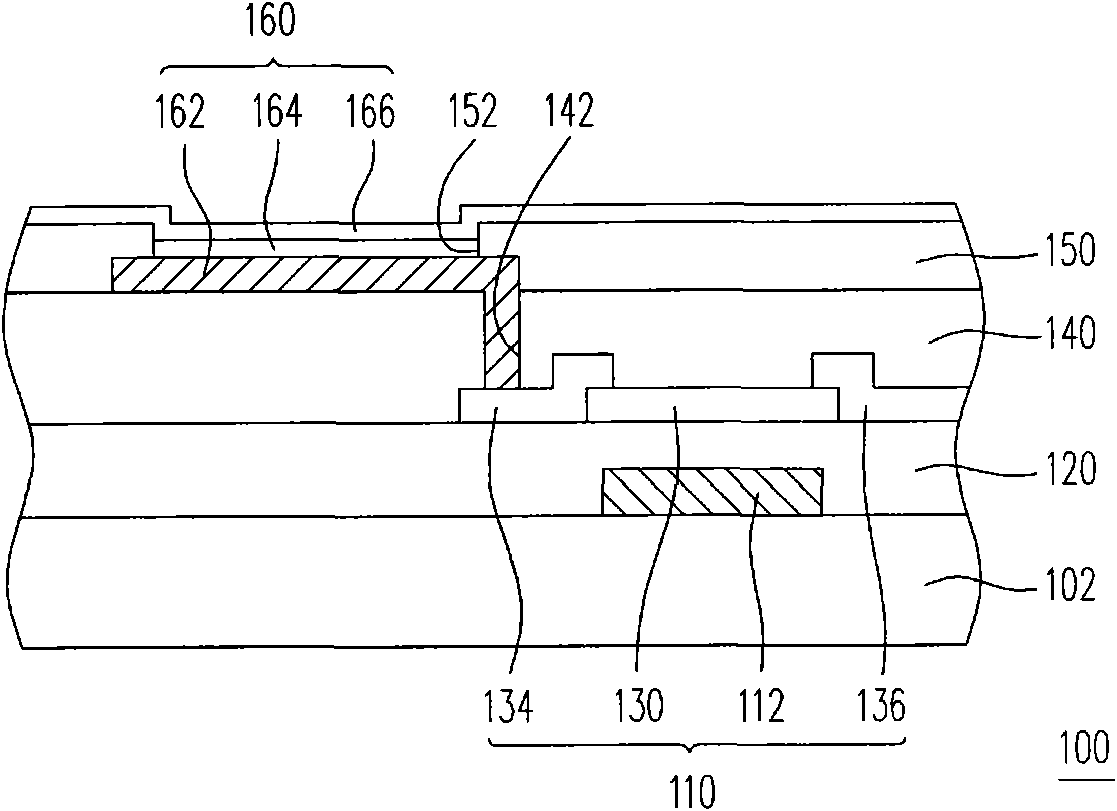

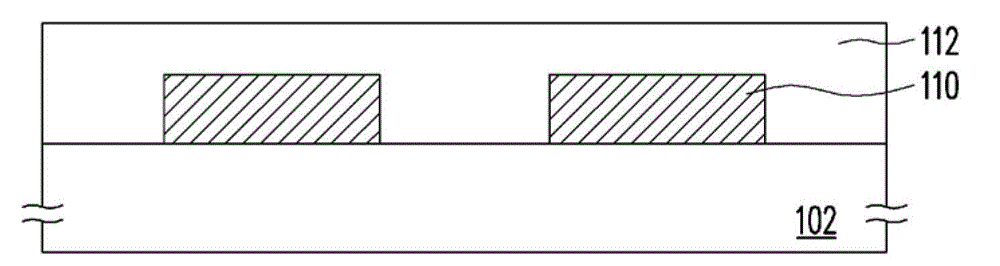

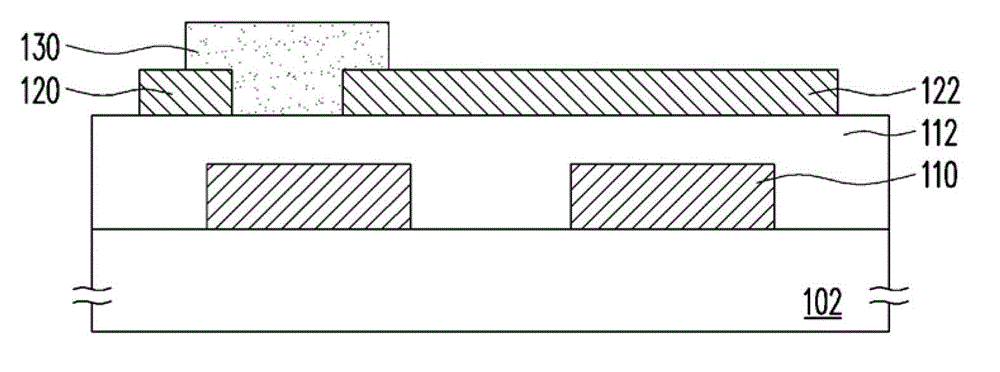

Pixel structure and manufacturing method thereof and manufacturing method of electronic device

ActiveCN101789443ASolve dropGood component propertiesSolid-state devicesSemiconductor/solid-state device manufacturingUltraviolet lightsLight penetration

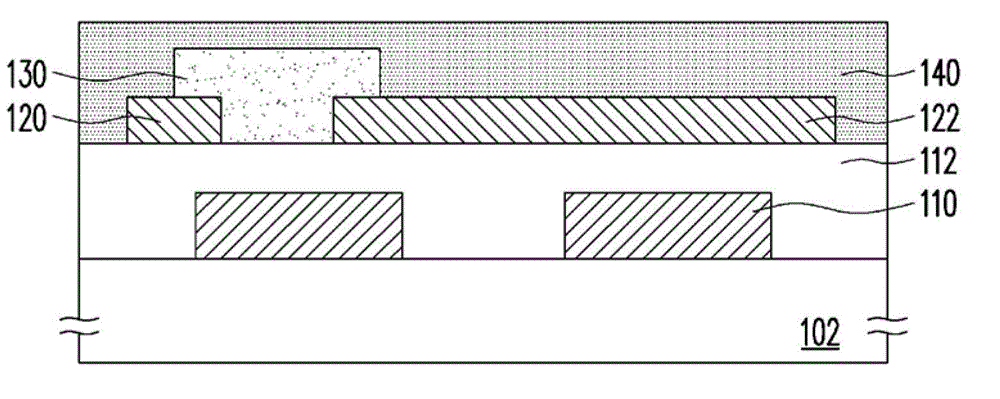

The invention discloses a pixel structure, comprising a substrate, a grid, an insulating layer, a metal oxide semiconductor layer, a source, a drain, at least a film layer and a first electrode layer, wherein the grid is positioned on the substrate; the insulating layer covers the grid; the metal oxide semiconductor layer is positioned on the insulating layer above the grid; the source and the drain are positioned on the metal oxide semiconductor layer; the film layer covers the metal oxide semiconductor layer and comprises a transparent photocatalyst material which blocks the light in the ultraviolet light band from penetrating through the metal oxide semiconductor layer; and the first electrode layer is electrically connected with the source or the drain. The invention simultaneously discloses a manufacturing method of the pixel structure and a manufacturing method of an electronic device.

Owner:AU OPTRONICS CORP

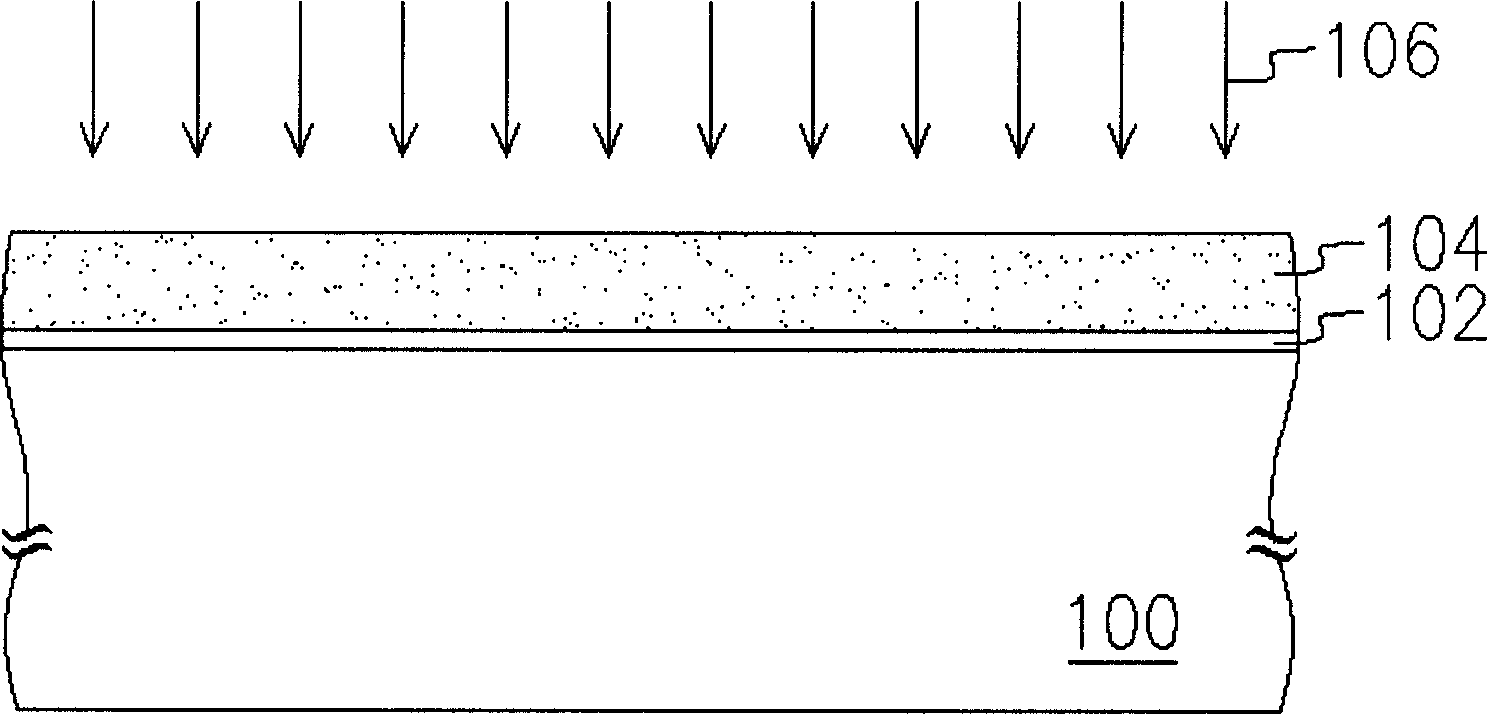

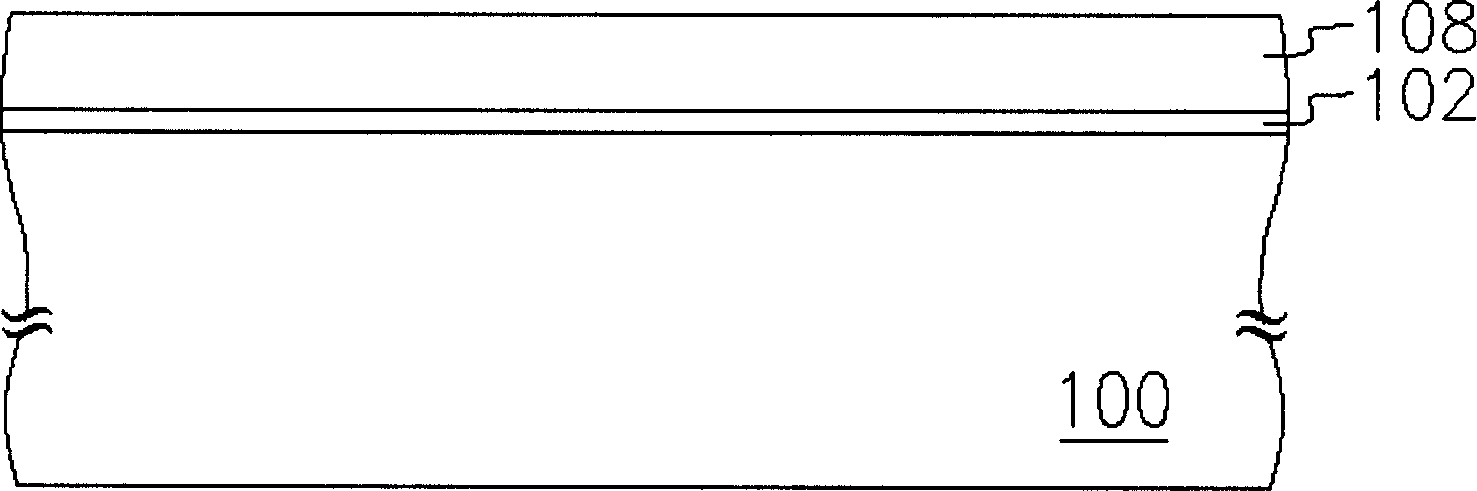

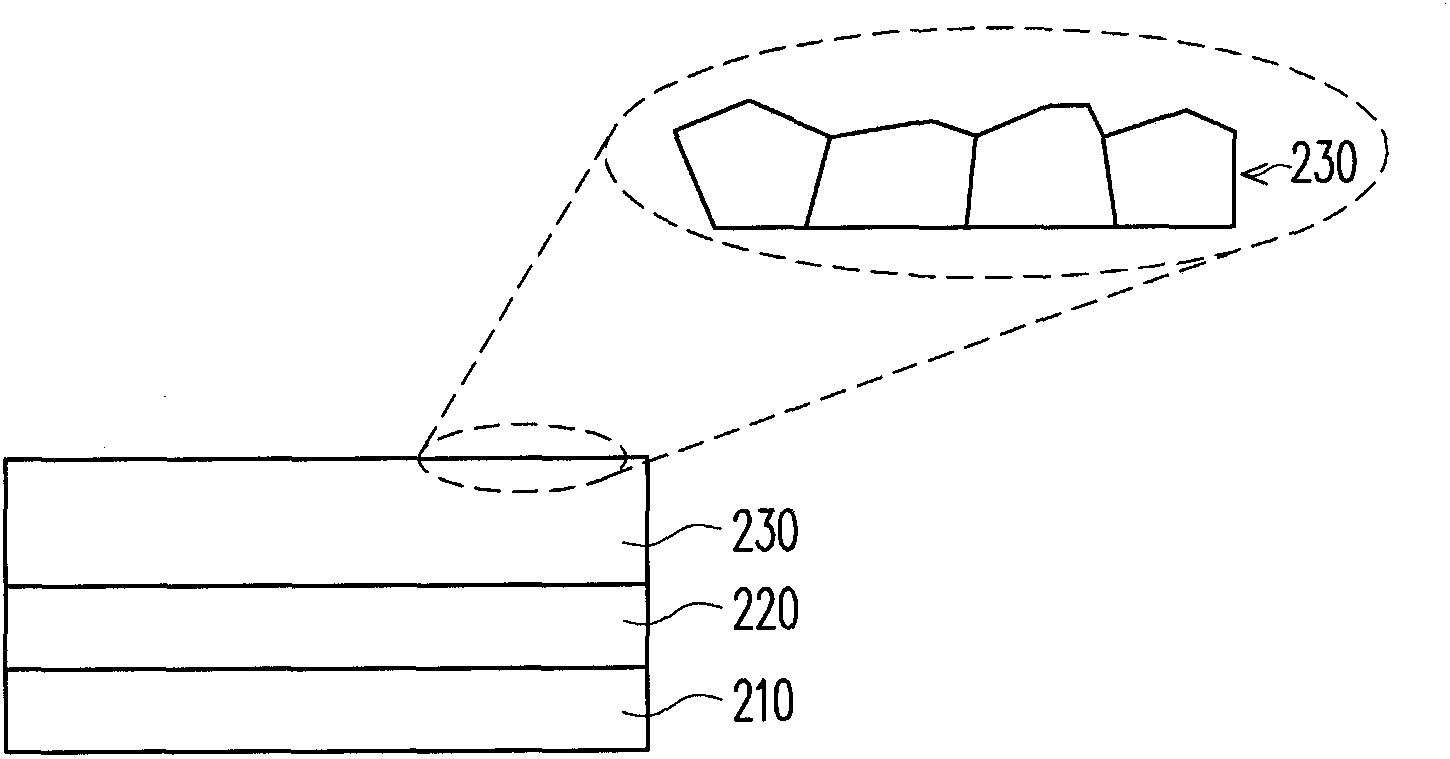

Array substrate and method for manufacturing polycrystalline silicon layer

ActiveCN102664196AInhibit deteriorationGood component propertiesTransistorSemiconductor/solid-state device manufacturingAmorphous siliconOptoelectronics

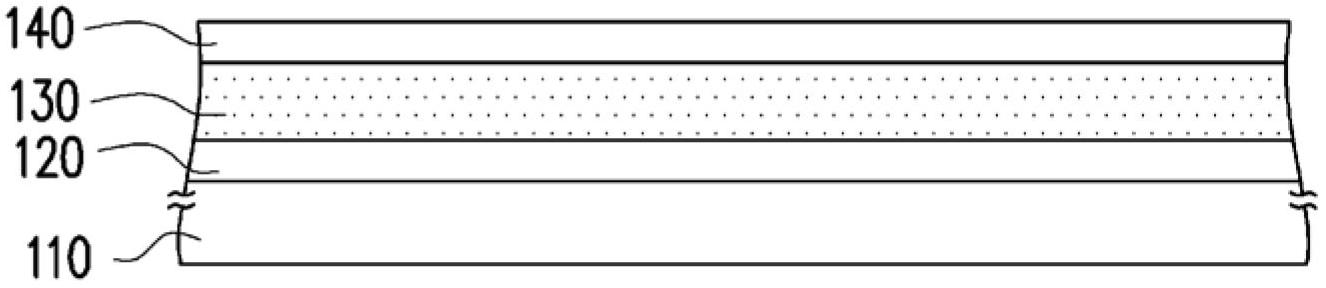

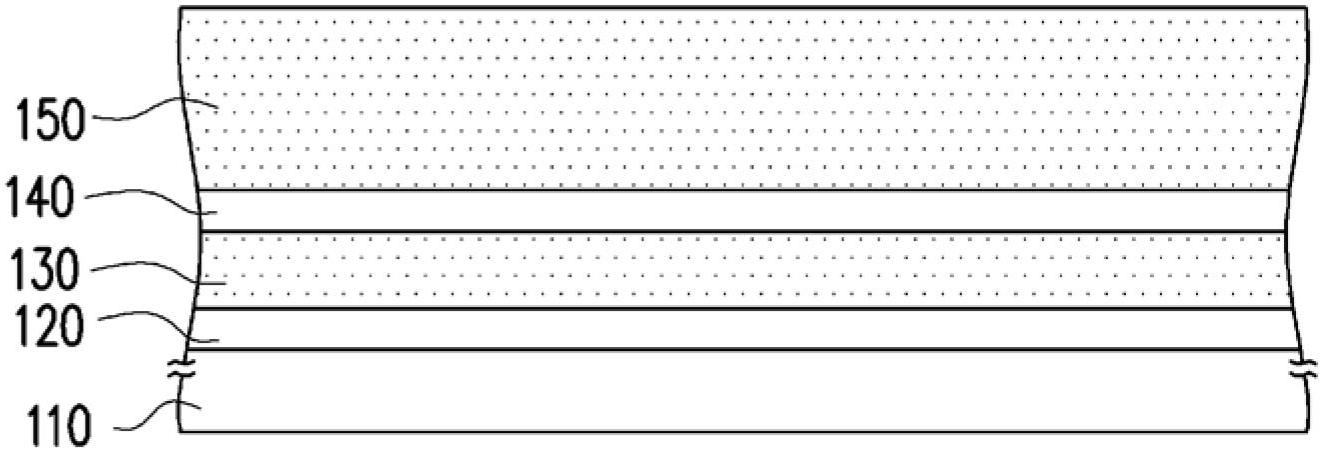

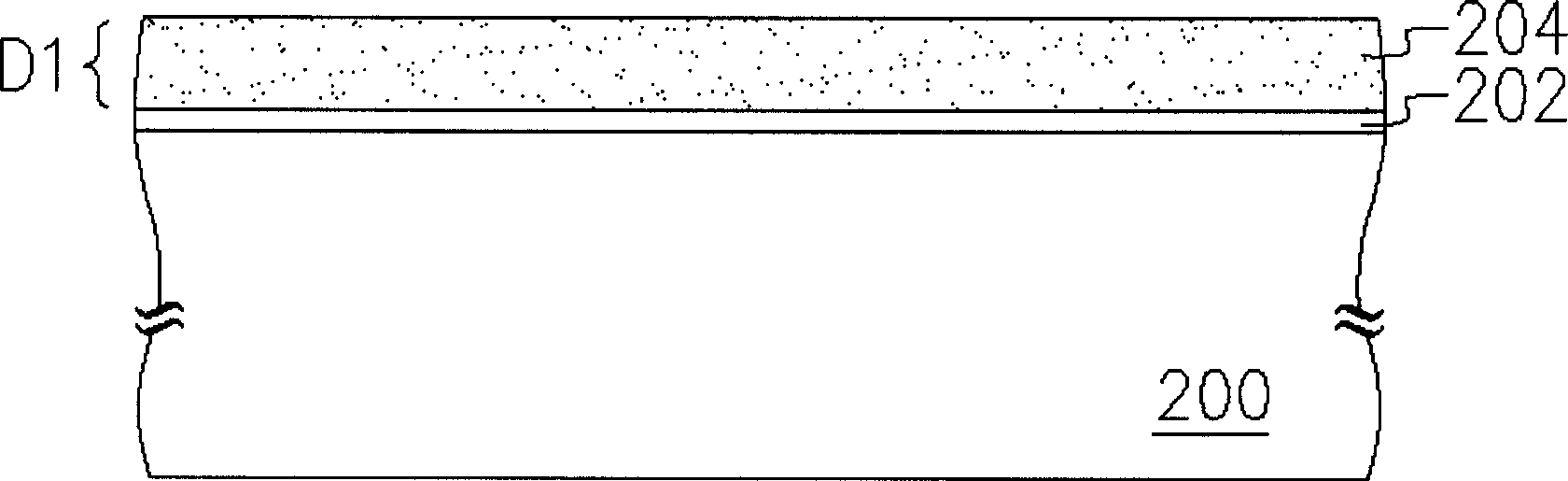

The present invention discloses an array substrate and a method for manufacturing a polycrystalline silicon layer, wherein the method comprises the steps of forming a first buffer layer on a flexible layer, forming a first barrier layer on the first buffer layer, forming a second buffer layer on the first barrier layer, forming a second barrier layer on the second buffer layer, forming an amorphous silicon layer on the second barrier layer, and converting the amorphous silicon layer into the polycrystalline silicon layer through laser.

Owner:AU OPTRONICS CORP

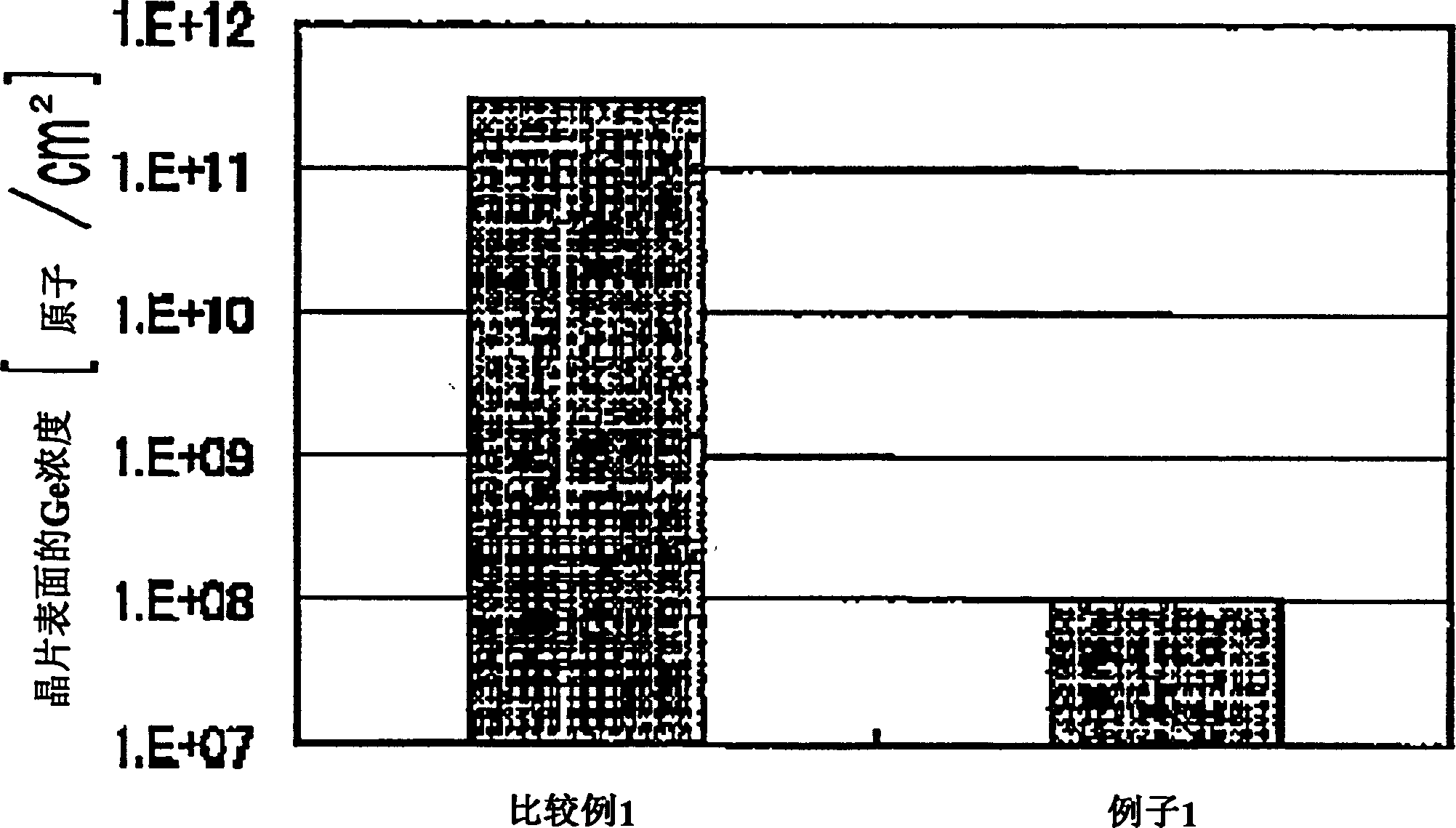

Method for producing semiconductor device and cleaning device for resist stripping

InactiveCN1622281AGood component propertiesImprove featuresSemiconductor/solid-state device manufacturingPhotomechanical coating apparatusResistMetal particle

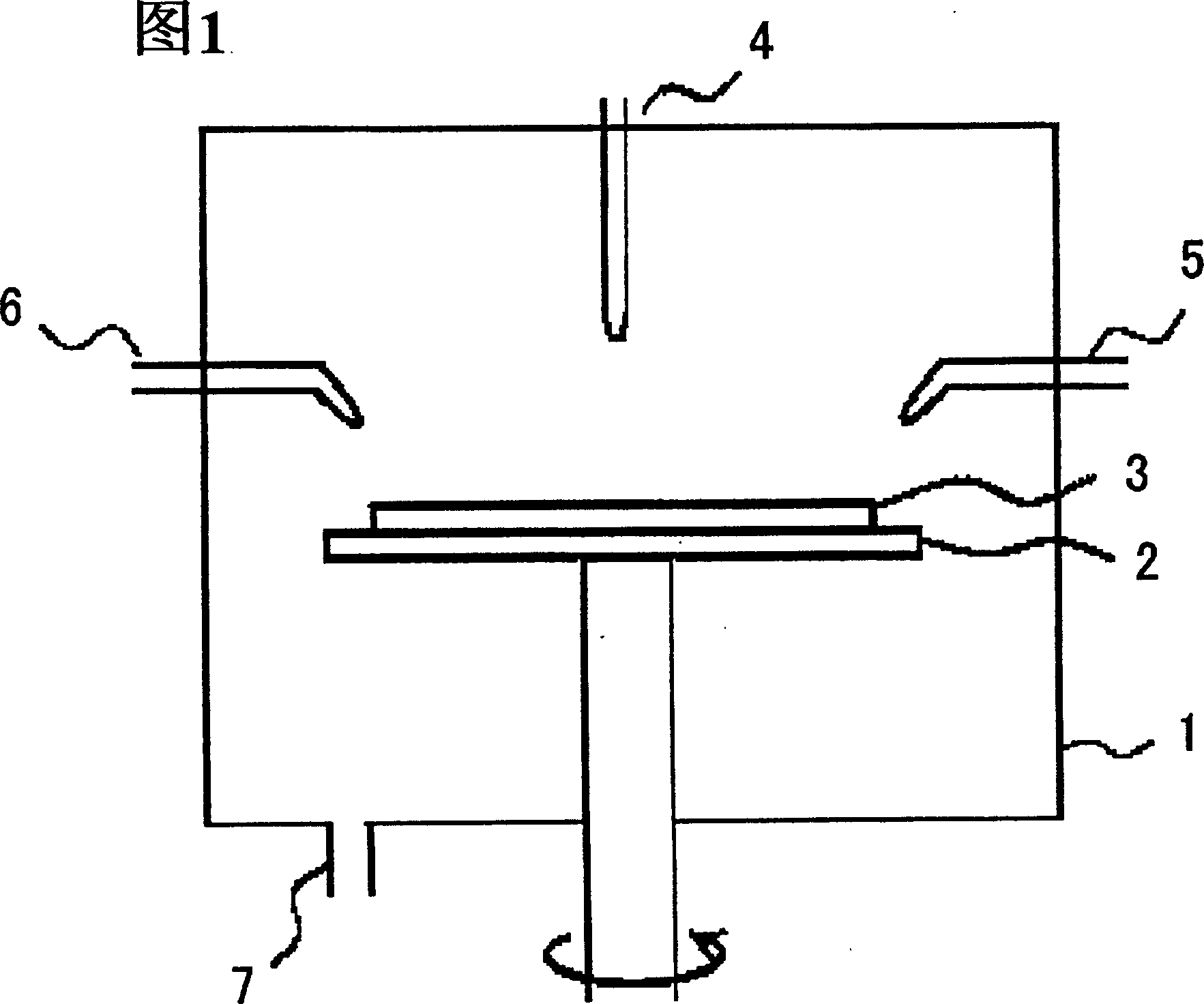

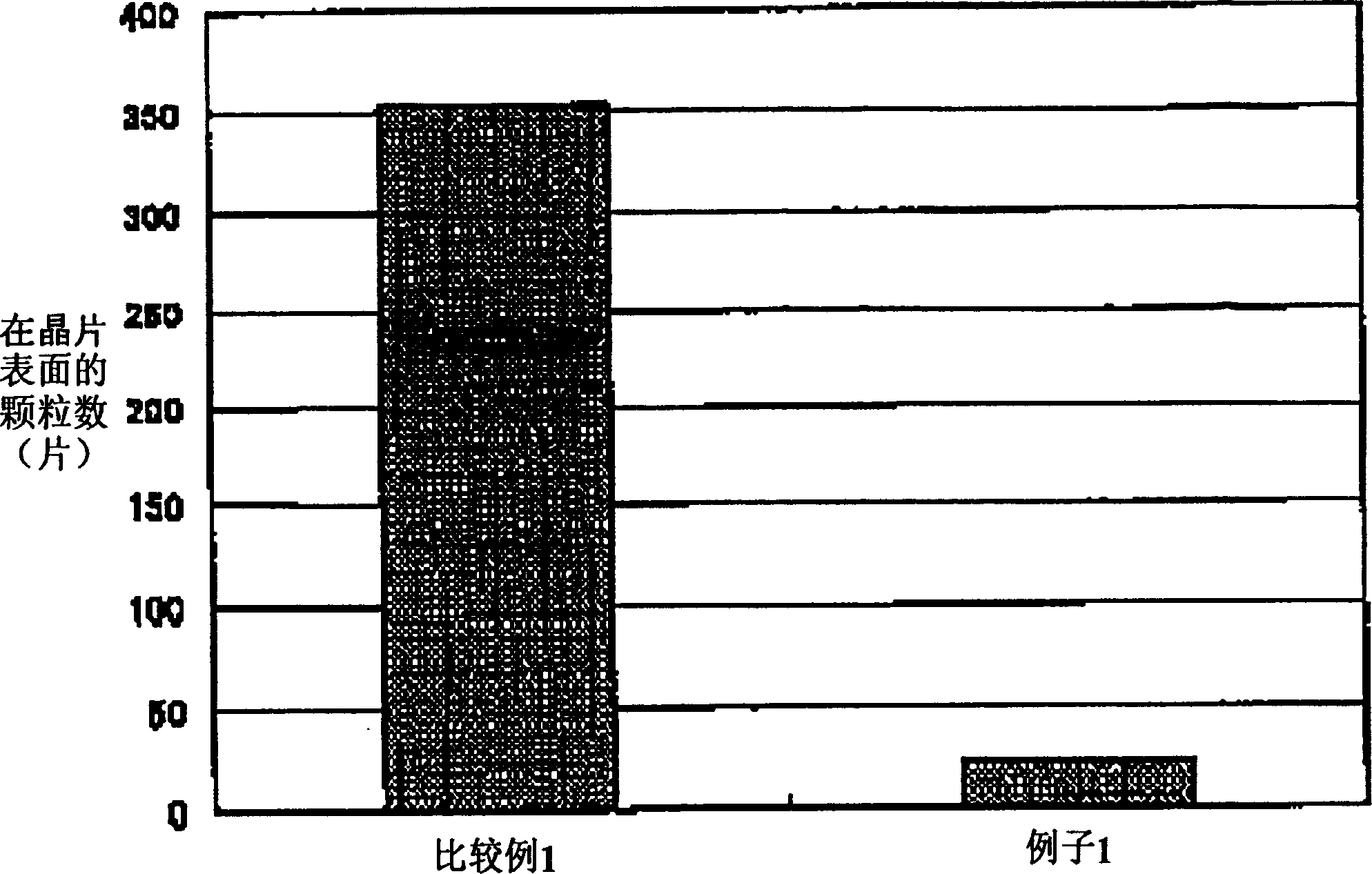

A semiconductor device manufacturing method and a cleaning apparatus for stripping a resist provide a semiconductor device having excellent element characteristics with a sufficient yield in the following manner, after dry etching of a photolithography process, the resist is removed by wet cleaning agent, and sufficiently removes particles or metal impurities without damaging fine patterns. A method for manufacturing a semiconductor device includes forming a resist pattern on a film provided for a semiconductor substrate, forming a fine pattern of a conductive film using the resist pattern as a mask while performing dry etching, supplying a resist stripping solution to The fine pattern formation surface of the semiconductor substrate is processed by a single wafer system to remove the resist pattern, and to perform the rinsing process of the semiconductor substrate.

Owner:RENESAS ELECTRONICS CORP

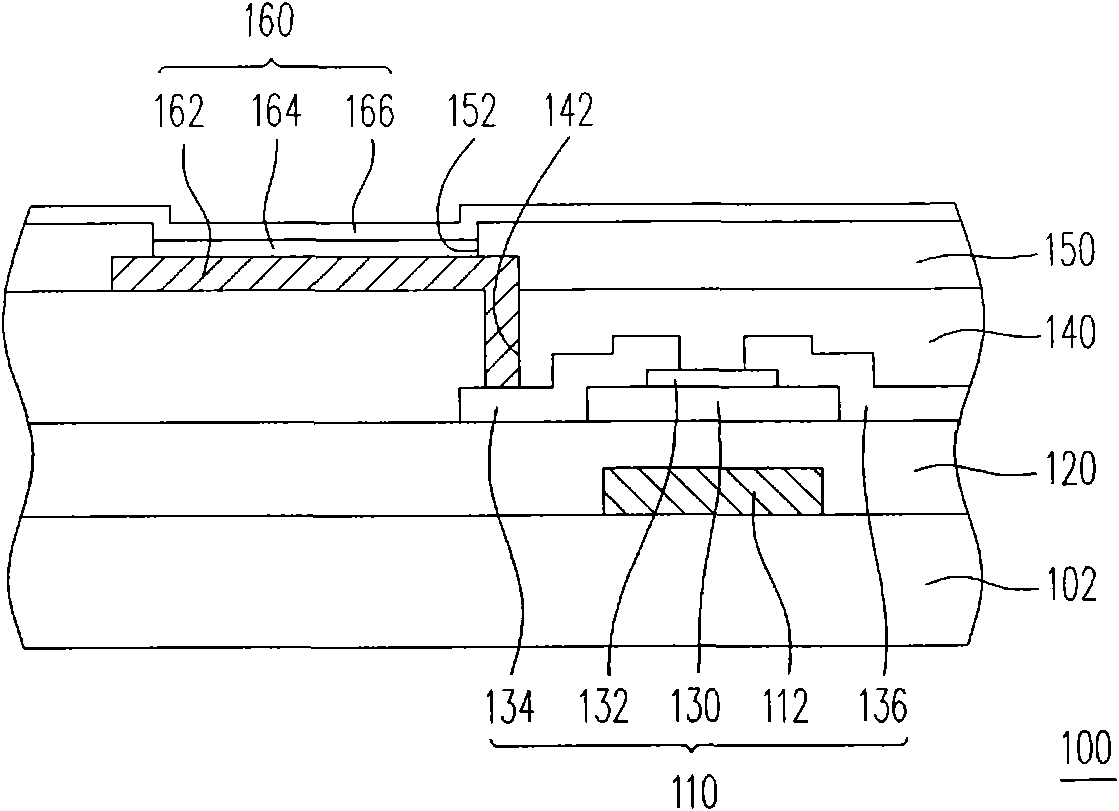

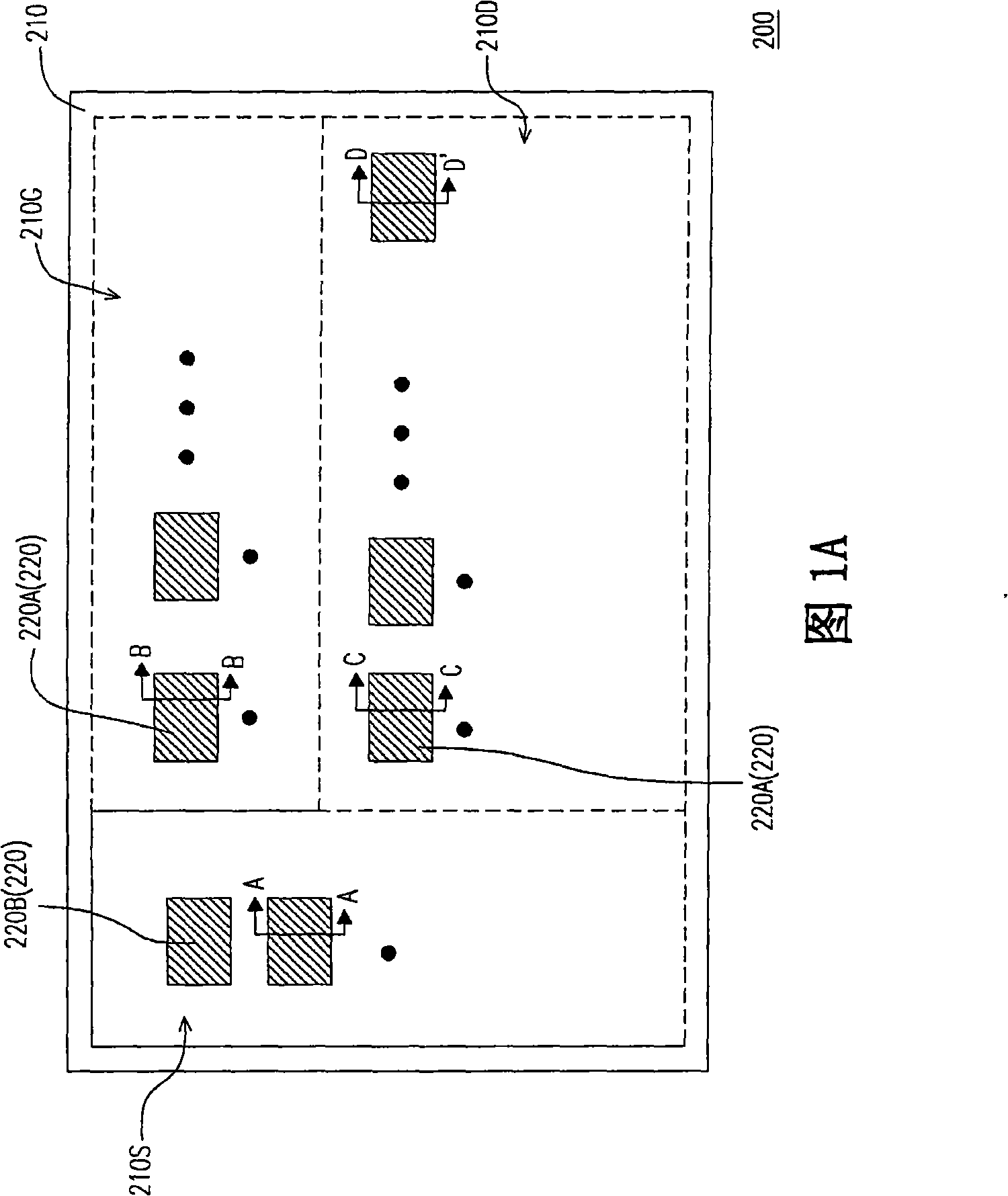

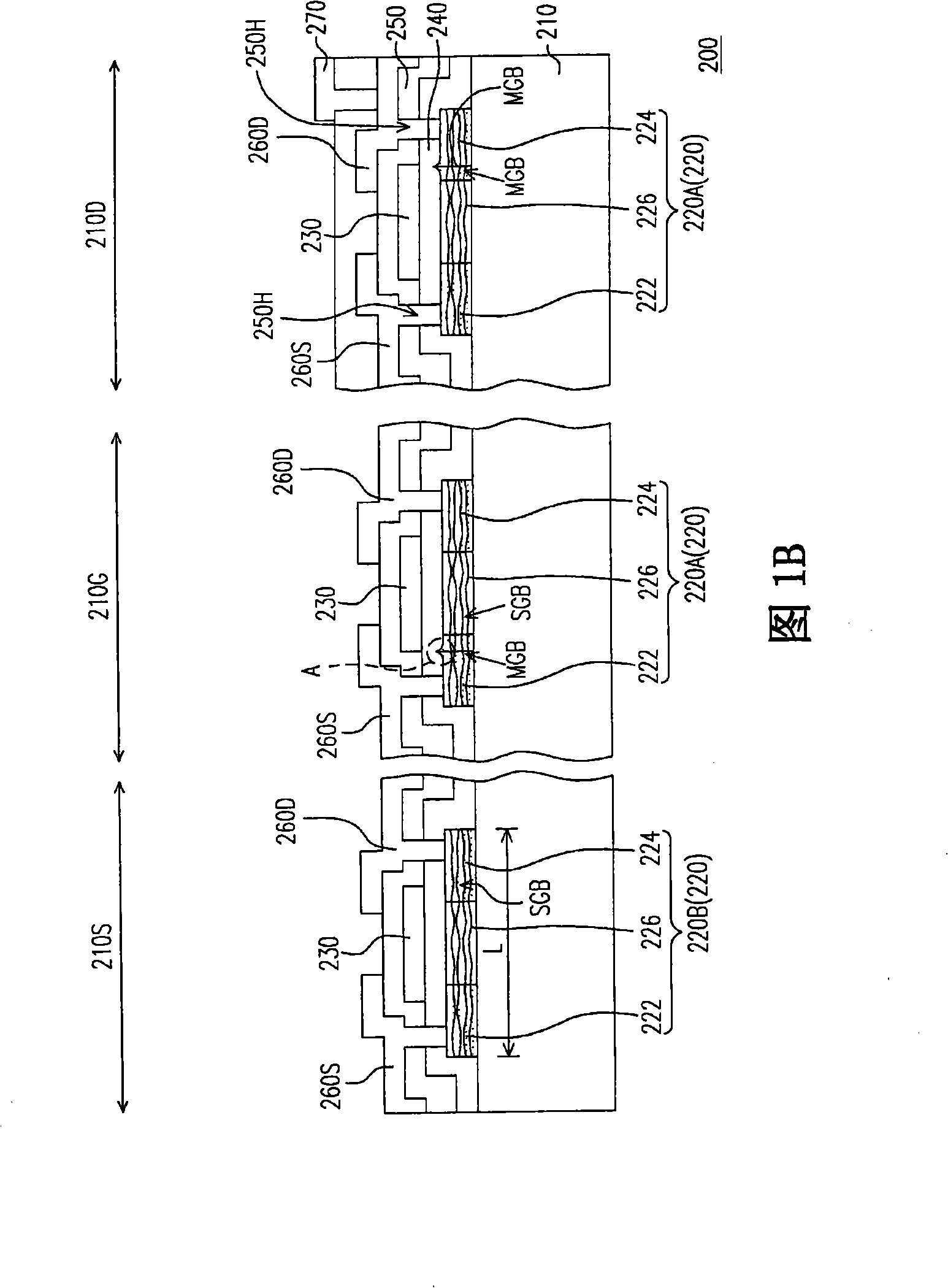

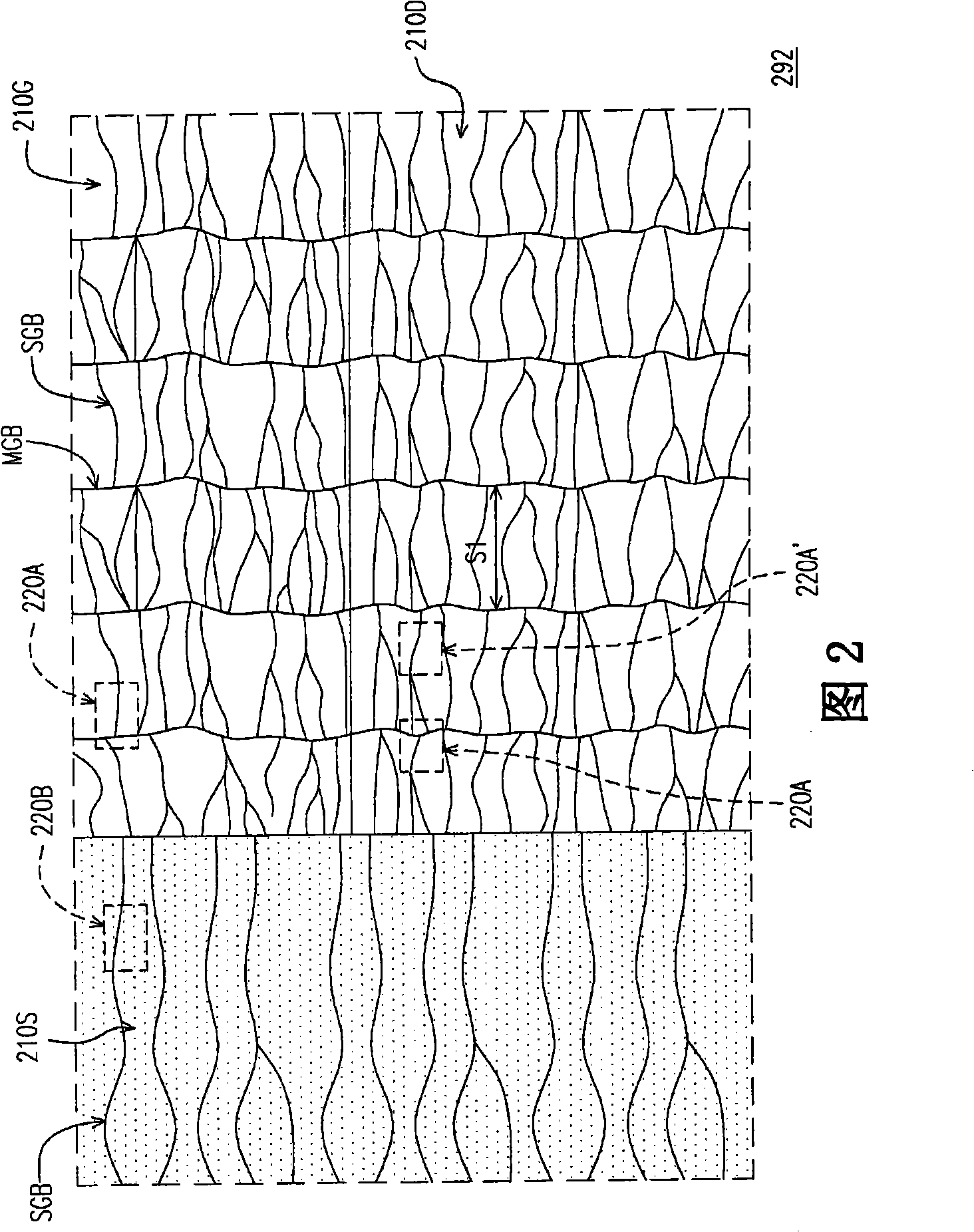

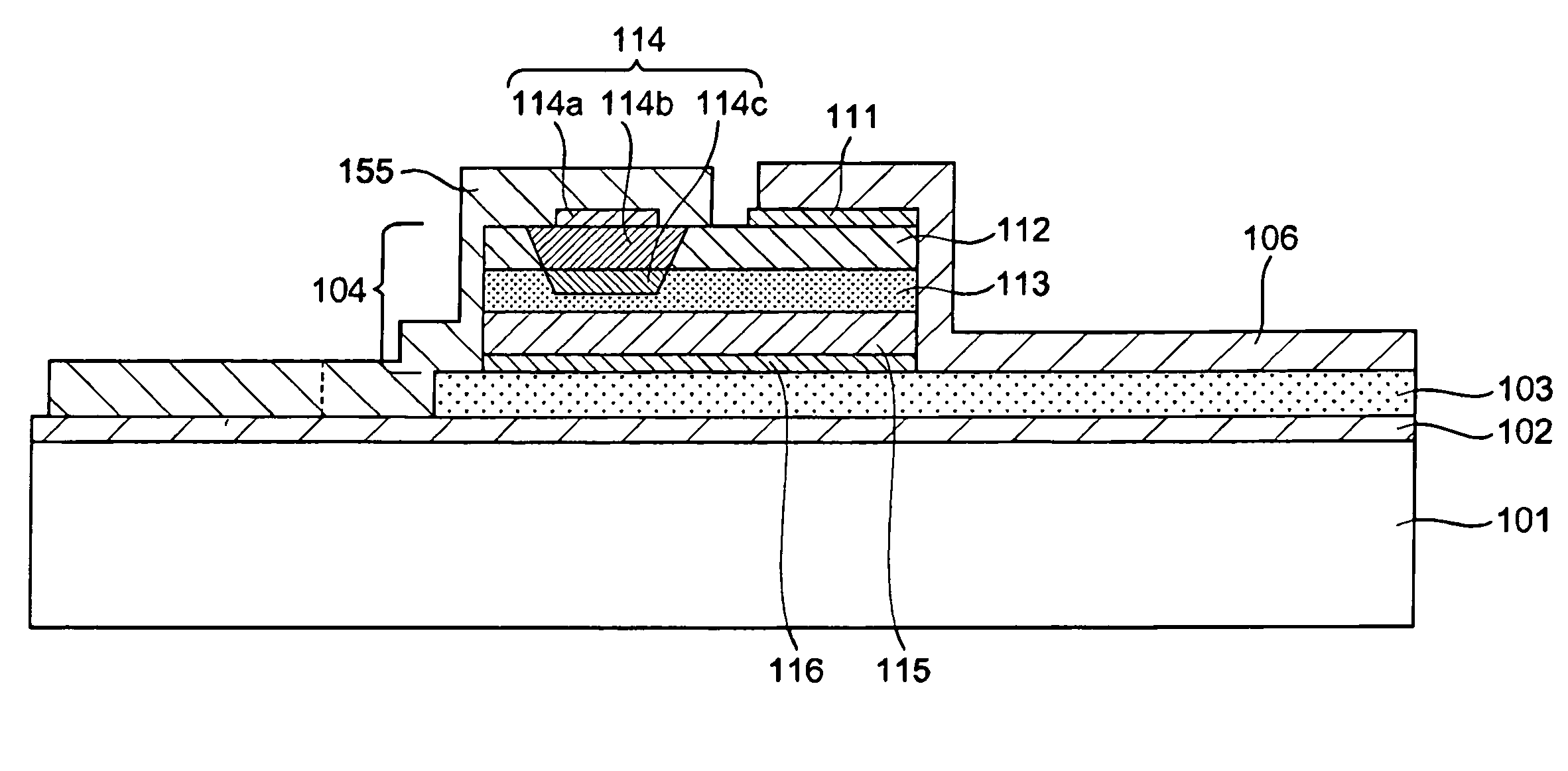

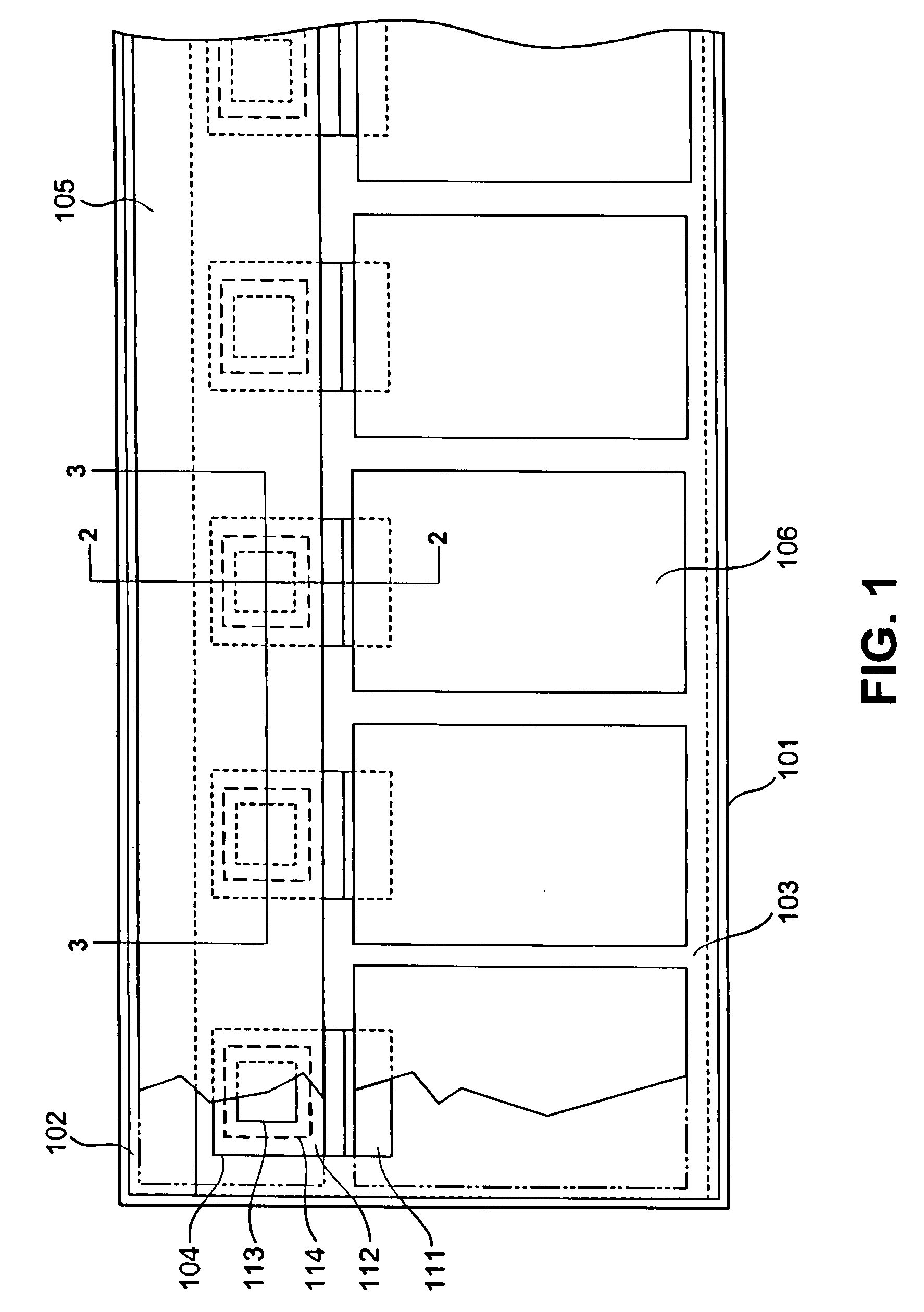

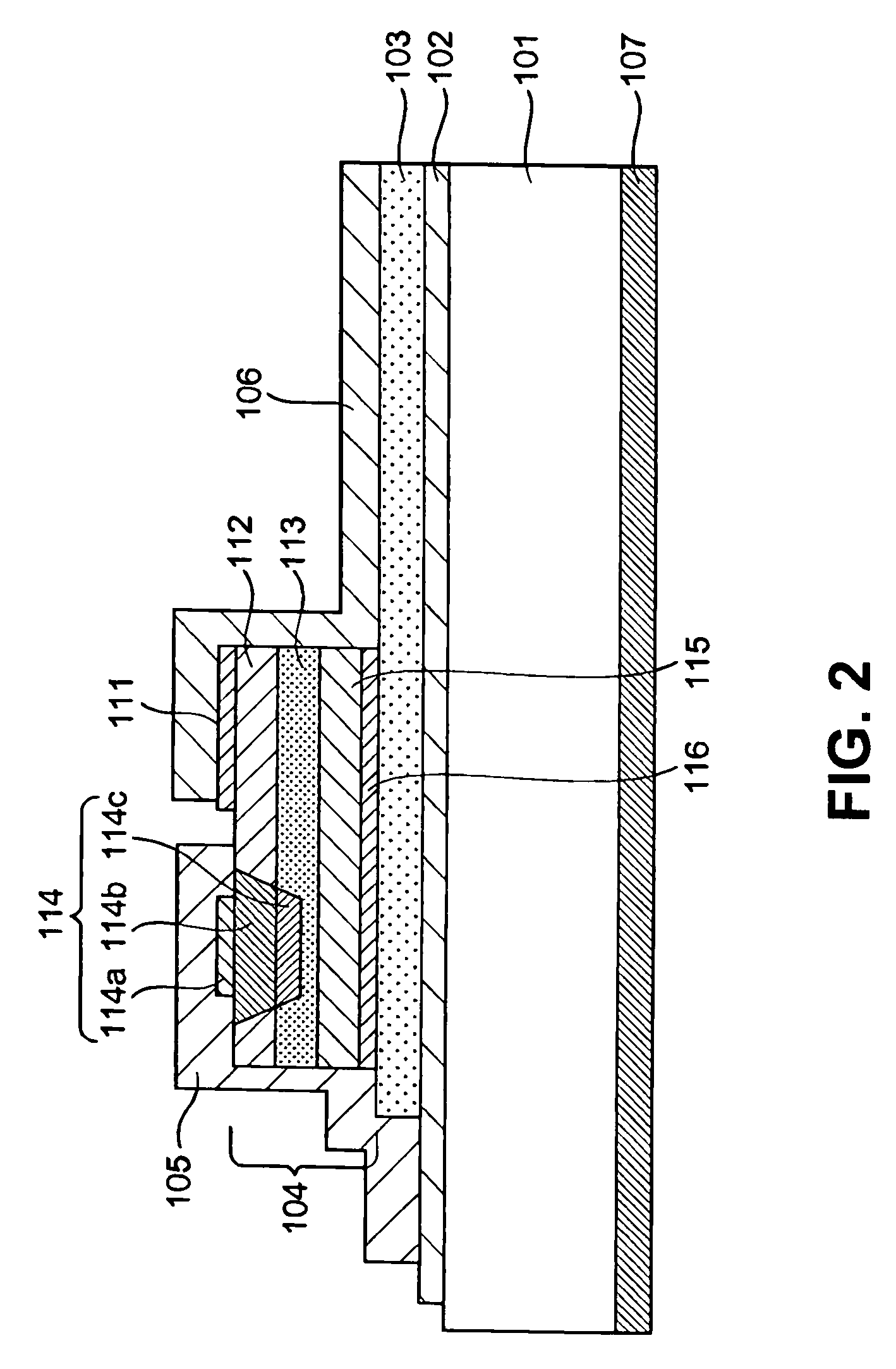

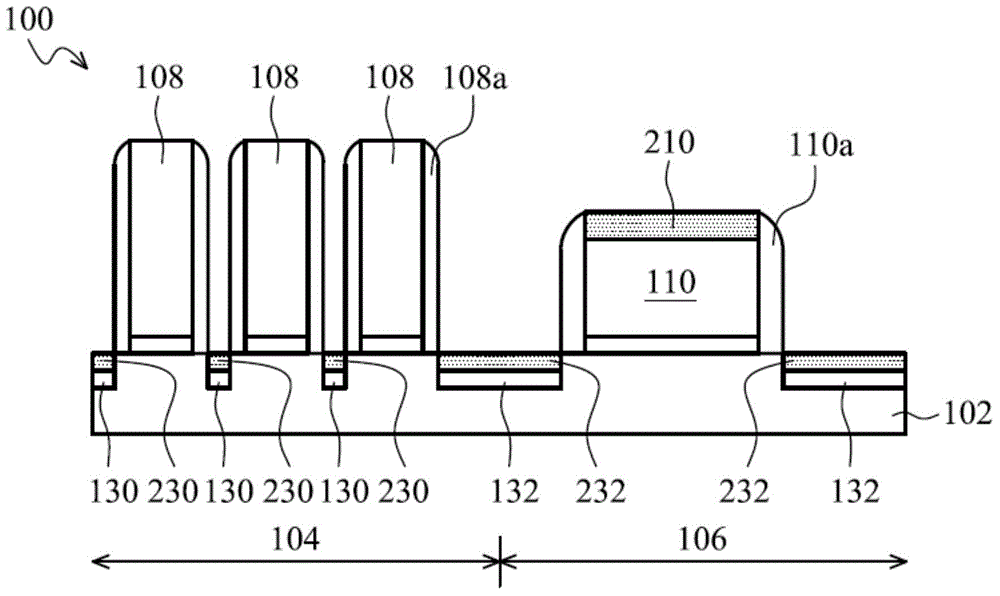

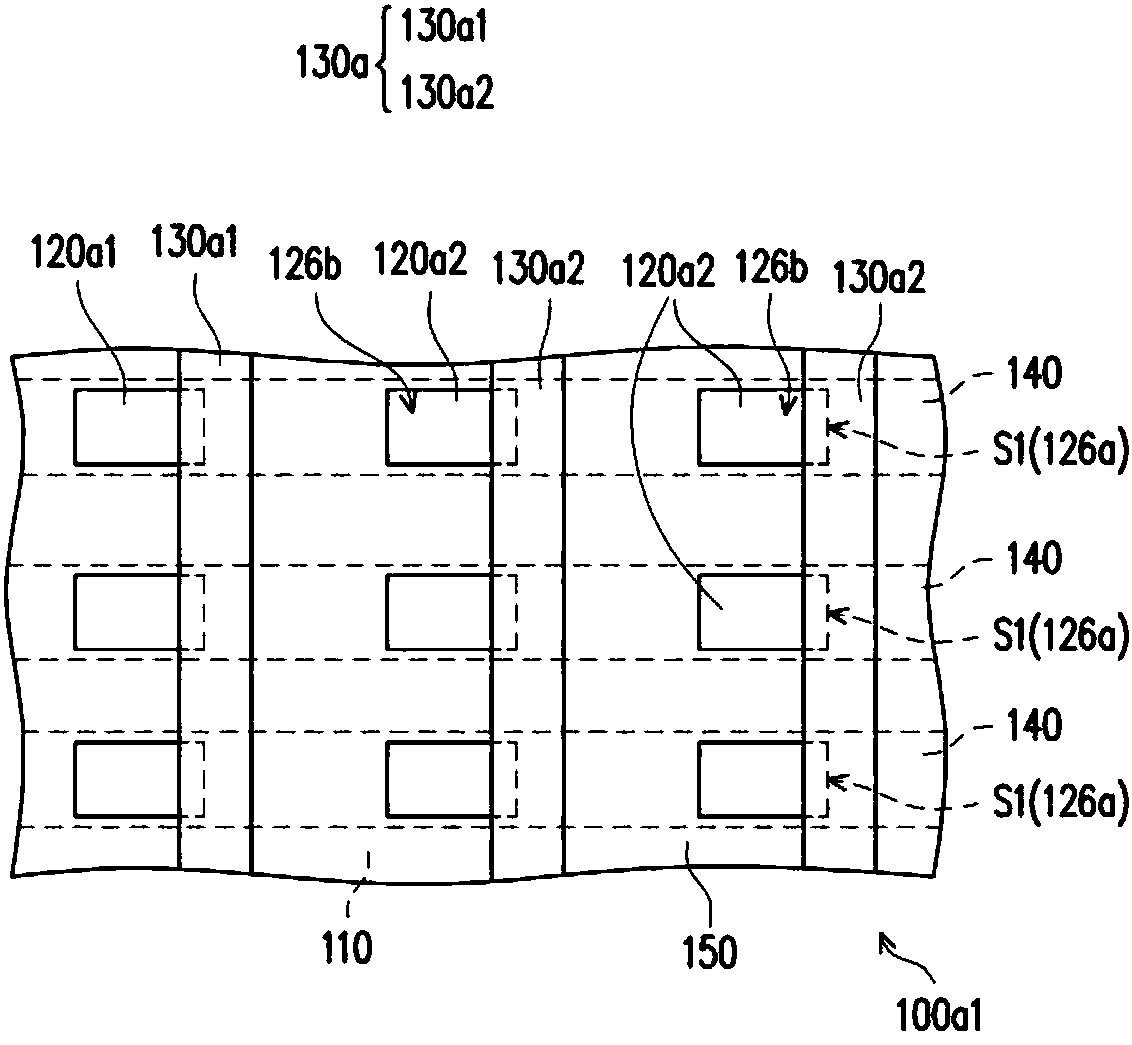

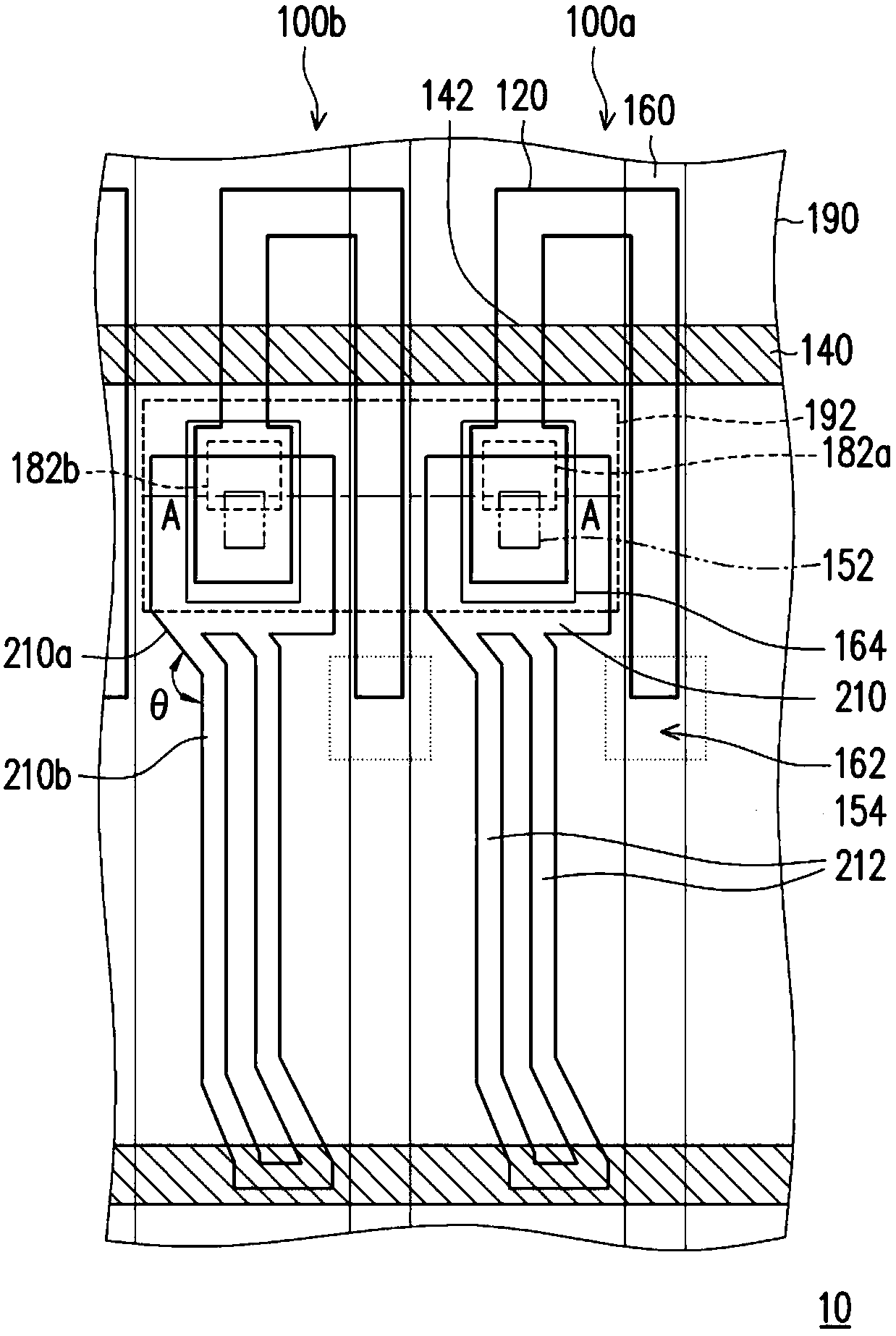

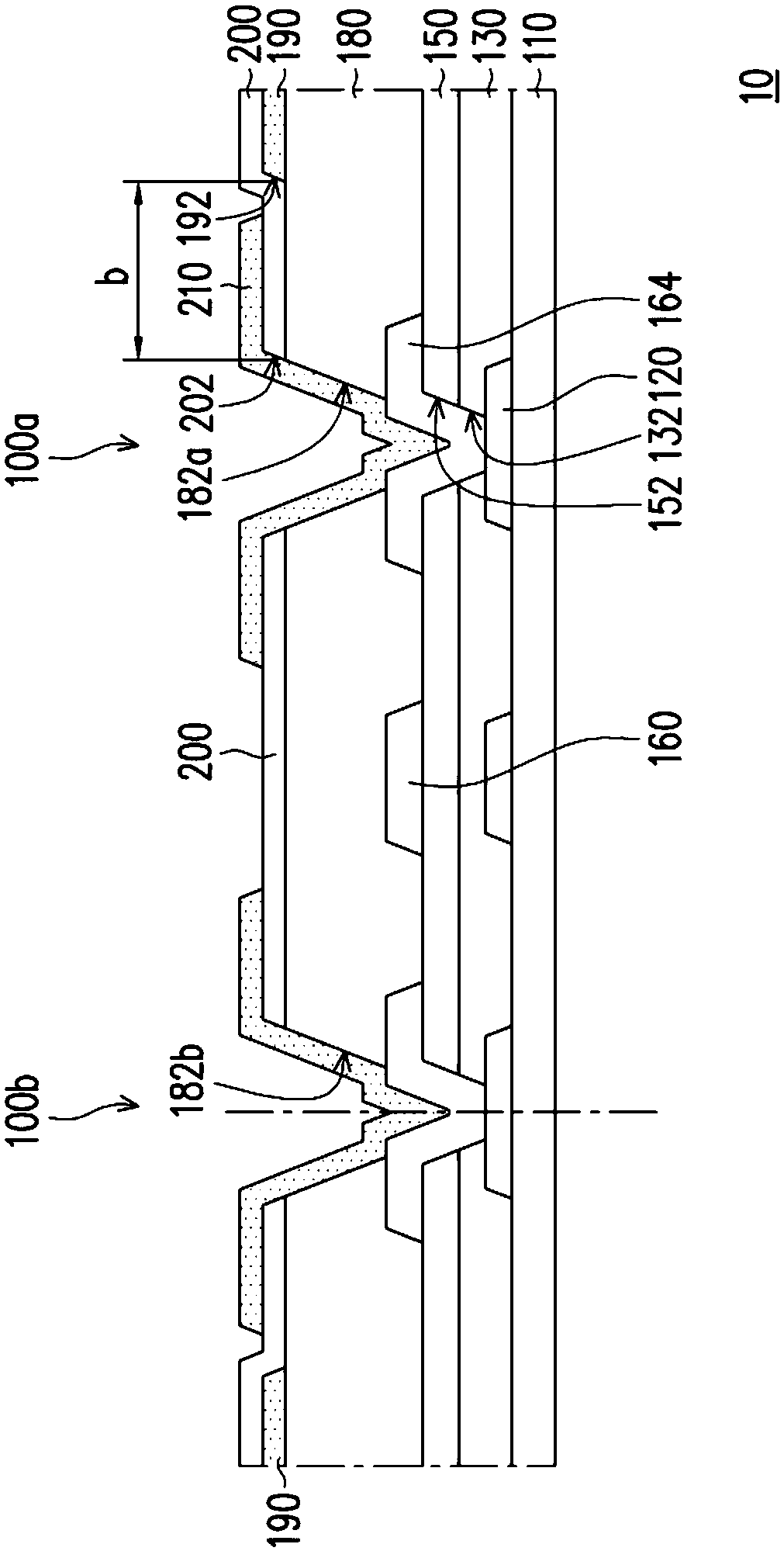

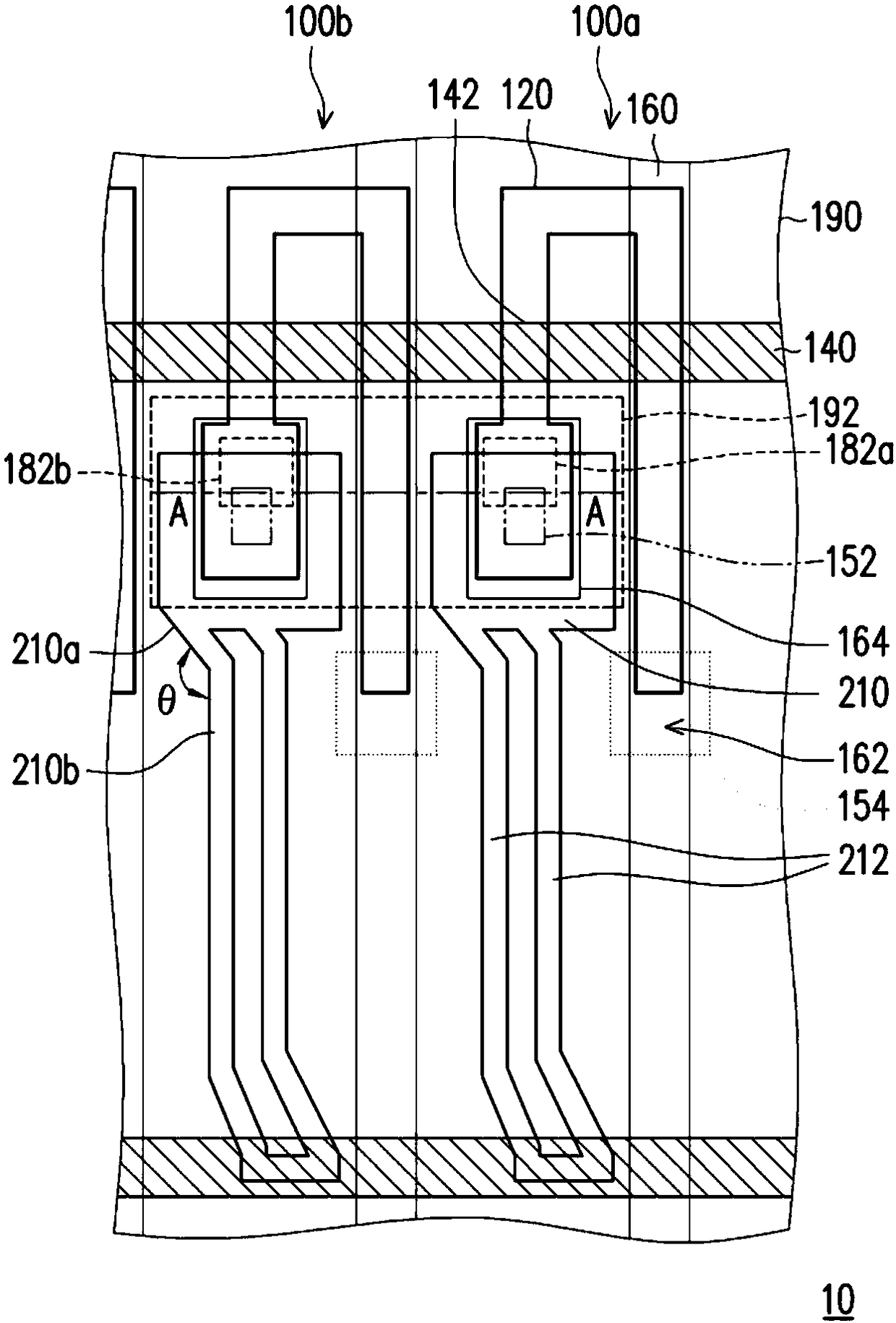

Thin-film transistor array substrate and preparation method thereof

ActiveCN101355090AGood component propertiesHigh carrier mobilitySolid-state devicesSemiconductor/solid-state device manufacturingGrain boundaryTransistor

The invention provides a substrate for a thin film transistor (TFT) array and a method for manufacturing the same. The substrate for the TFT array comprises the substrate, a plurality of multicrystal silicon islands and a plurality of grid electrodes, wherein the substrate has a display zone, a grid electrode drive zone and a source electrode drive zone; the multicrystal silicon islands are arranged on the substrate, and each multicrystal silicon island has a source electrode zone, a drain electrode zone and a channel zone positioned between the source electrode zone and the drain electrode zone; moreover, the multicrystal silicon islands comprise a plurality of first multicrystal silicon islands and second multicrystal silicon islands, wherein the first multicrystal silicon islands are arranged inside the display zone and the grid electrode drive zone, and have major grain boundaries and minor grain boundaries, and the major grain boundaries is only positioned inside the source electrode zone and / or the drain electrode zone; the second multicrystal silicon islands are arranged inside the source electrode drive zone; the size of grain inside the first multicrystal silicon islands is different from that inside the second multicrystal silicon islands; and the grid electrodes are arranged on the substrate and are corresponding to the channel zone.

Owner:AU OPTRONICS CORP

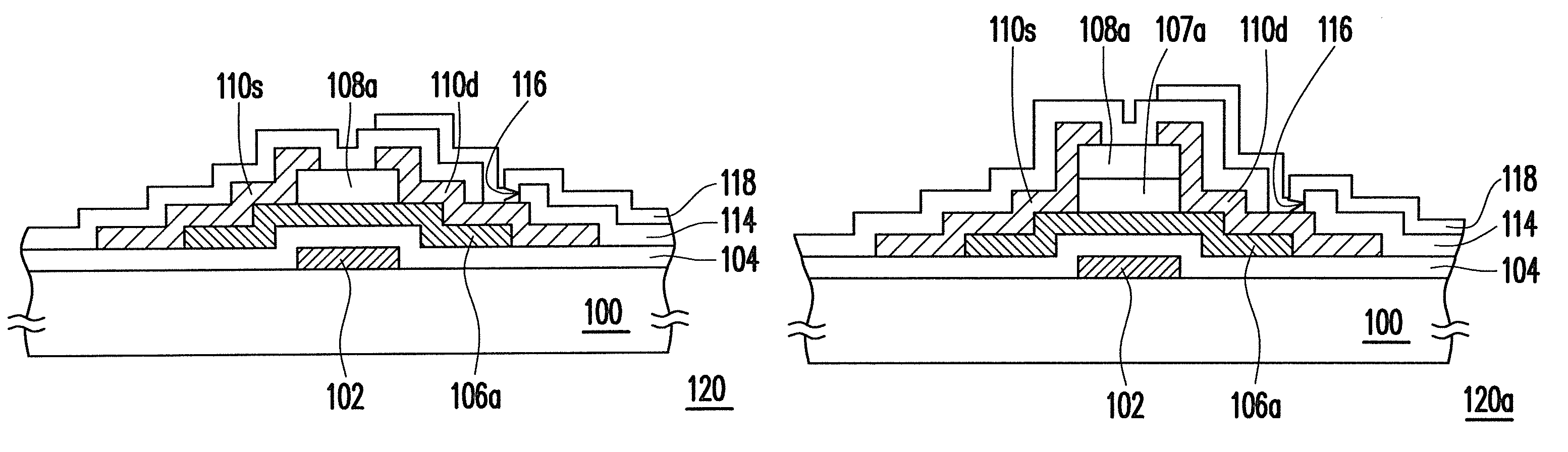

Thin film transistor and manufacturing method thereof

ActiveCN102054874AGood component propertiesTransistorSemiconductor/solid-state device manufacturingElectrical conductorOxide thin-film transistor

The invention discloses a thin film transistor and a manufacturing method thereof. The thin film transistor comprises a substrate, a semiconductor layer, a patterning doped semiconductor layer, a source electrode, a drain electrode, a grid isolating layer and a grid electrode, wherein the semiconductor layer is arranged on the substrate; the patterning doped semiconductor layer is arranged above two opposite sides of the semiconductor layer; the source electrode and the drain electrode are arranged on the patterning doped semiconductor layer and above two opposite sides of the semiconductor layer; a part of the semiconductor layer covered by the source electrode and the drain electrode has a first thickness, a part of the semiconductor layer, which is positioned between the source electrode and the drain electrode and not covered by the source electrode and the drain electrode, has a second thickness, and the second thickness is between 200 angstroms and 800 angstroms; the grid isolating layer is arranged on the source electrode, the drain electrode and a part of semiconductor layer; and the grid is arranged on the grid isolating layer. The thin film transistor provided by the invention has better element characteristics.

Owner:AU OPTRONICS CORP

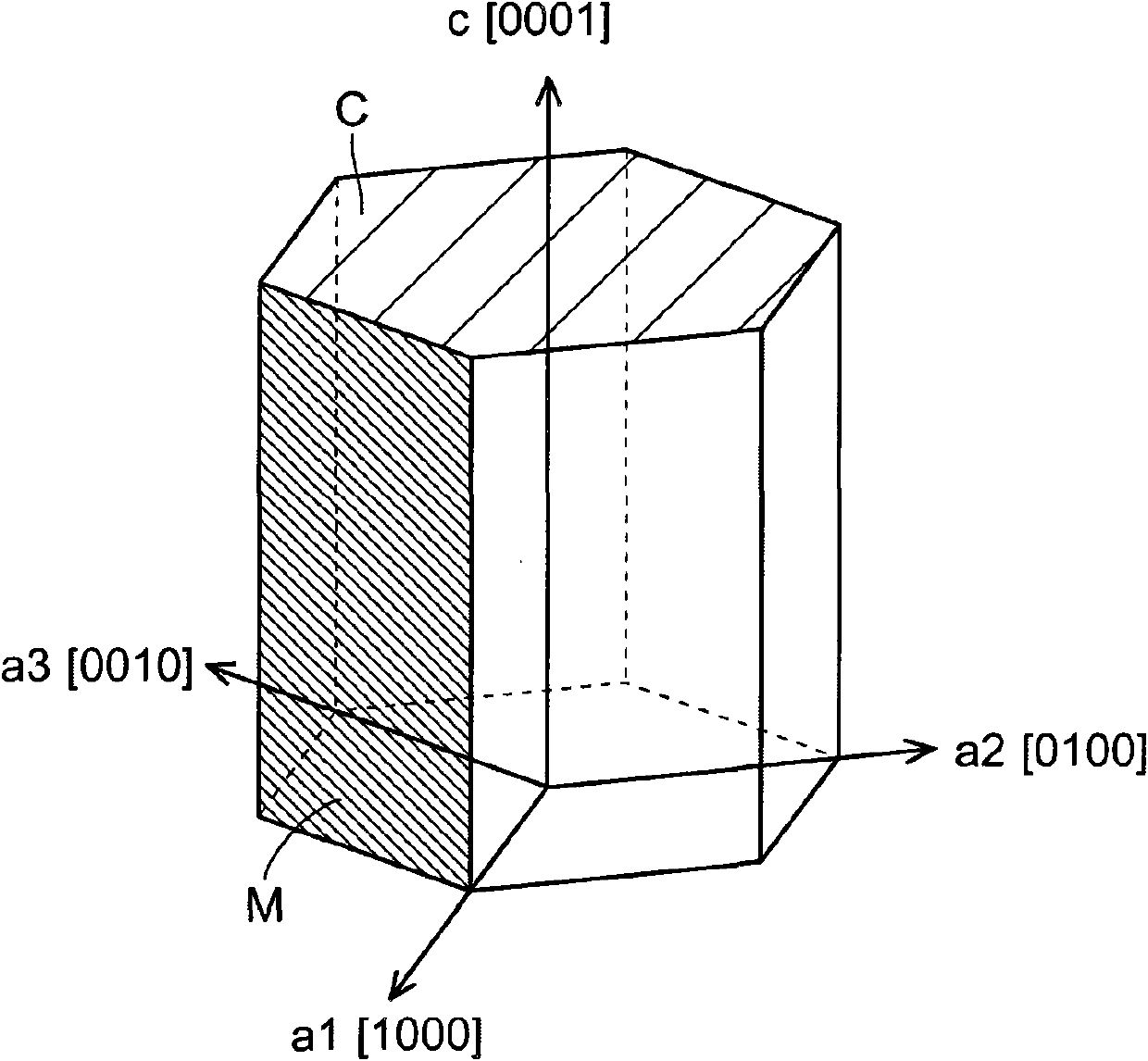

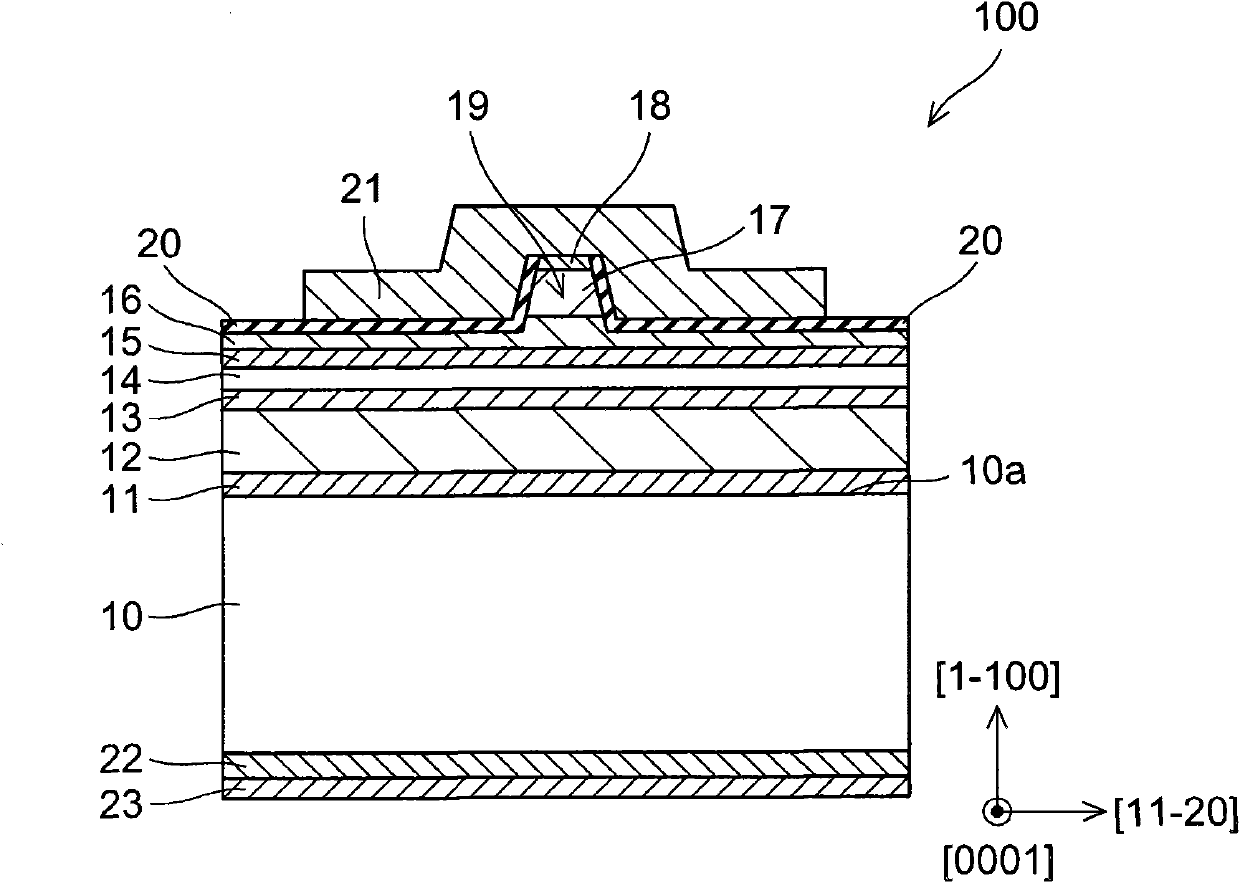

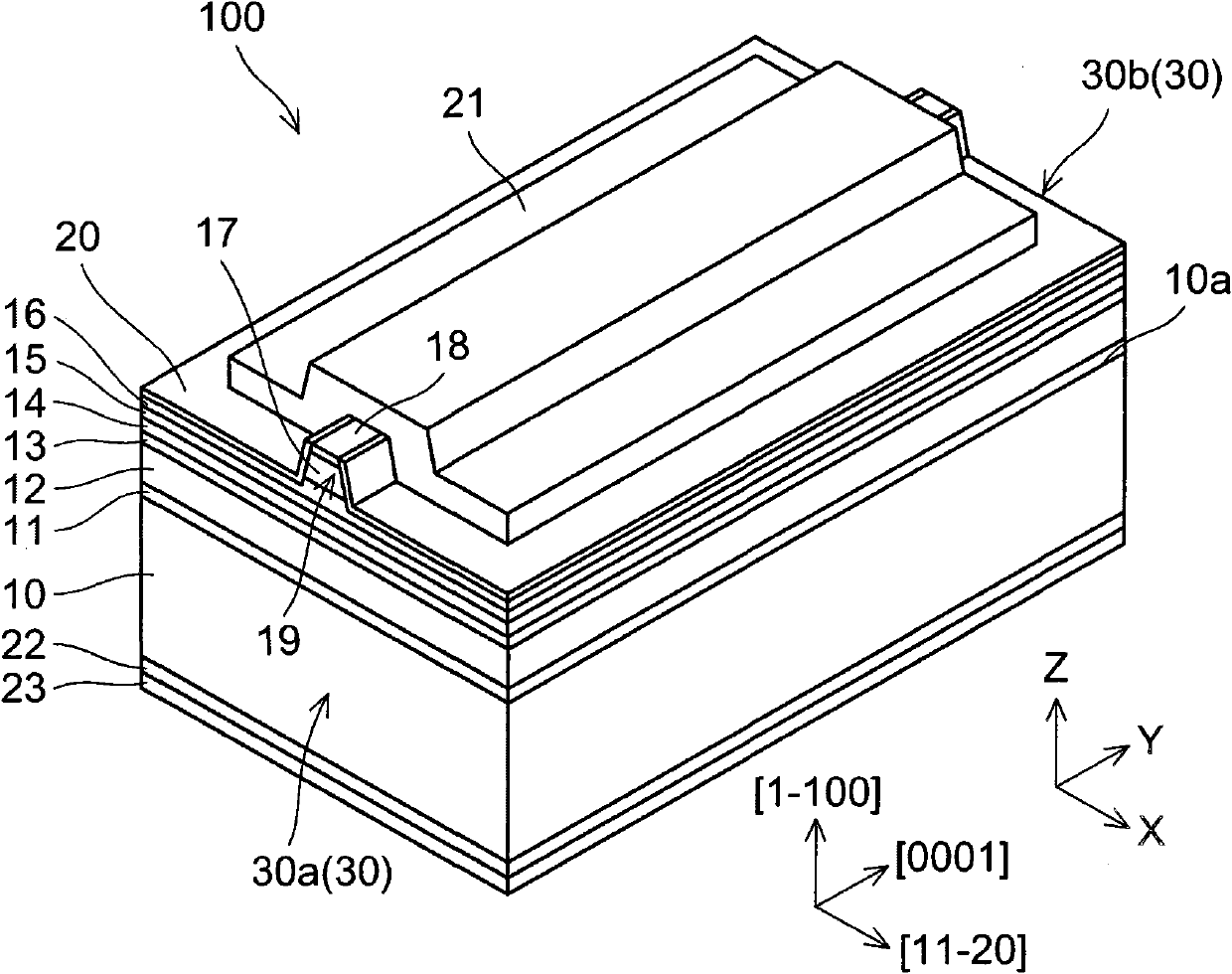

Nitride semiconductor wafer, nitride semiconductor chip, method of manufacture thereof, and semiconductor device

InactiveCN101997268AImprove luminous efficiencyImprove qualified product rateOptical wave guidanceLaser detailsWaferingDevice material

The invention relates to a Nitride semiconductor wafer,a nitride semiconductor chip, a method of manufacture thereof, and semiconductor device. The nitride semiconductor chip allows enhancement of luminous efficacy. The nitride semiconductor laser chip (nitride semiconductor chip) has a GaN substrate, which has a principal growth plane, and an active layer, which is formed on the principal growth plane of the GaN substrate and which has a quantum well structure including a well layer and a barrier layer. The principal growth plane is a plane having an off angle in the a-axis direction relative to the m plane. The barrier layer is formed of AlGaN, which is a nitride semiconductor containing Al.

Owner:SHARP KK

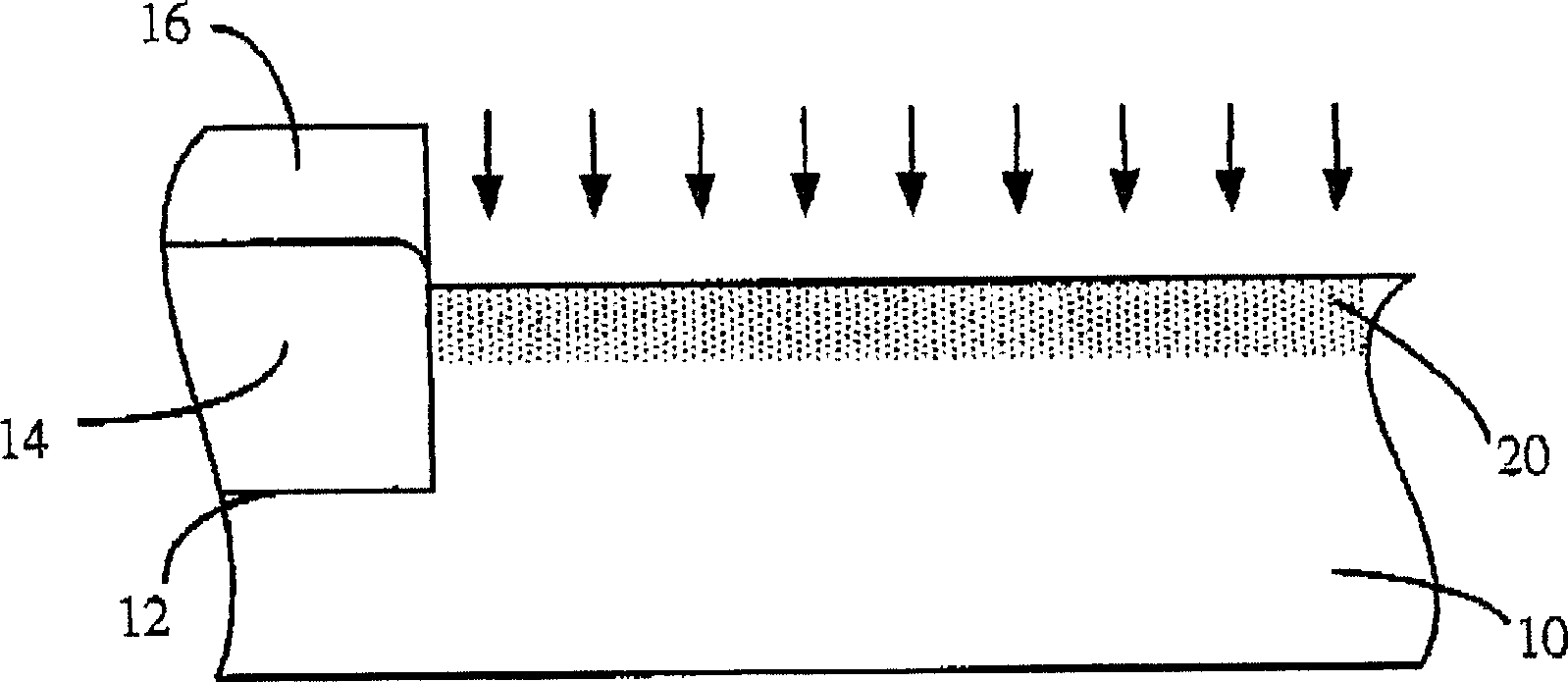

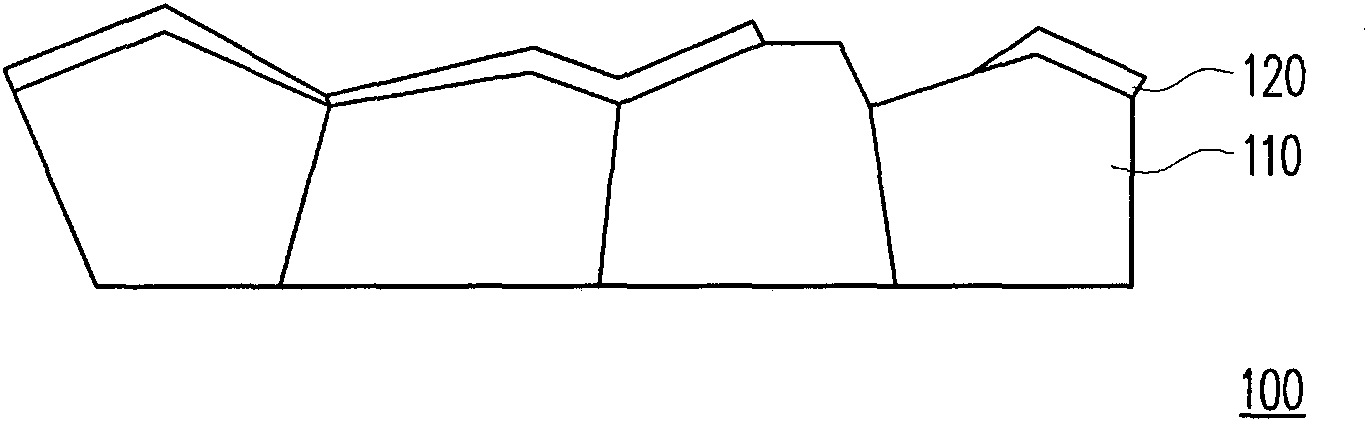

Method for making polysilicon film

InactiveCN1567534ASmall quantityLess denseSemiconductor/solid-state device manufacturingNon-linear opticsMetallurgyLow density

The invention provides a polycrystalline silicon film making method, using the phenomenon that as an ordinary polycrystalline silicon layer is formed, its surface saliences have different heights, and using partiall higher saliences to generate crystal seeds used in the following crystallizing step, therefore able to make the new formed polycrystalline silicon film have uniform and bigger crystal particles and have fewer lower-density saliences, and further have better surface flatness.

Owner:AU OPTRONICS CORP

Semiconductor device and method for producing same

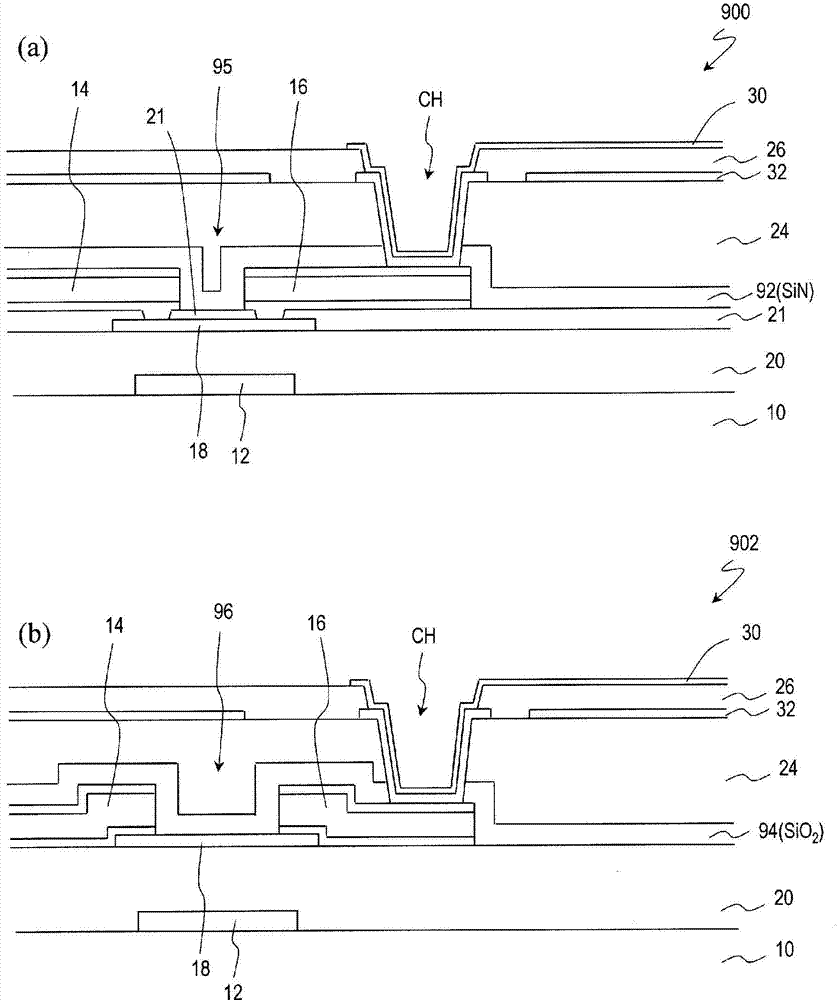

ActiveCN104508808AGood component propertiesImprove yieldTransistorSolid-state devicesSilicon oxideSemiconductor

Owner:SHARP KK

Thin film transistor and producing method

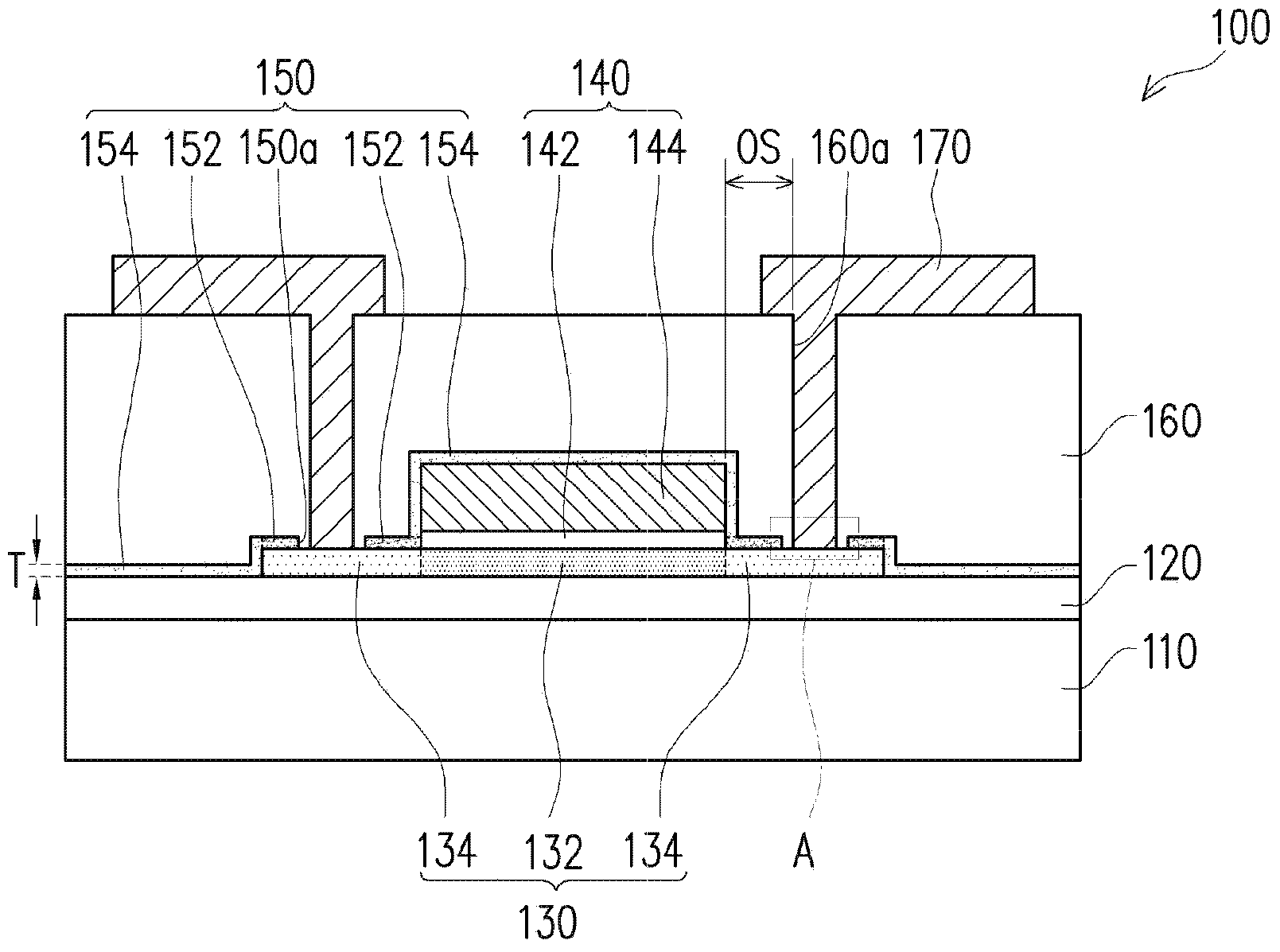

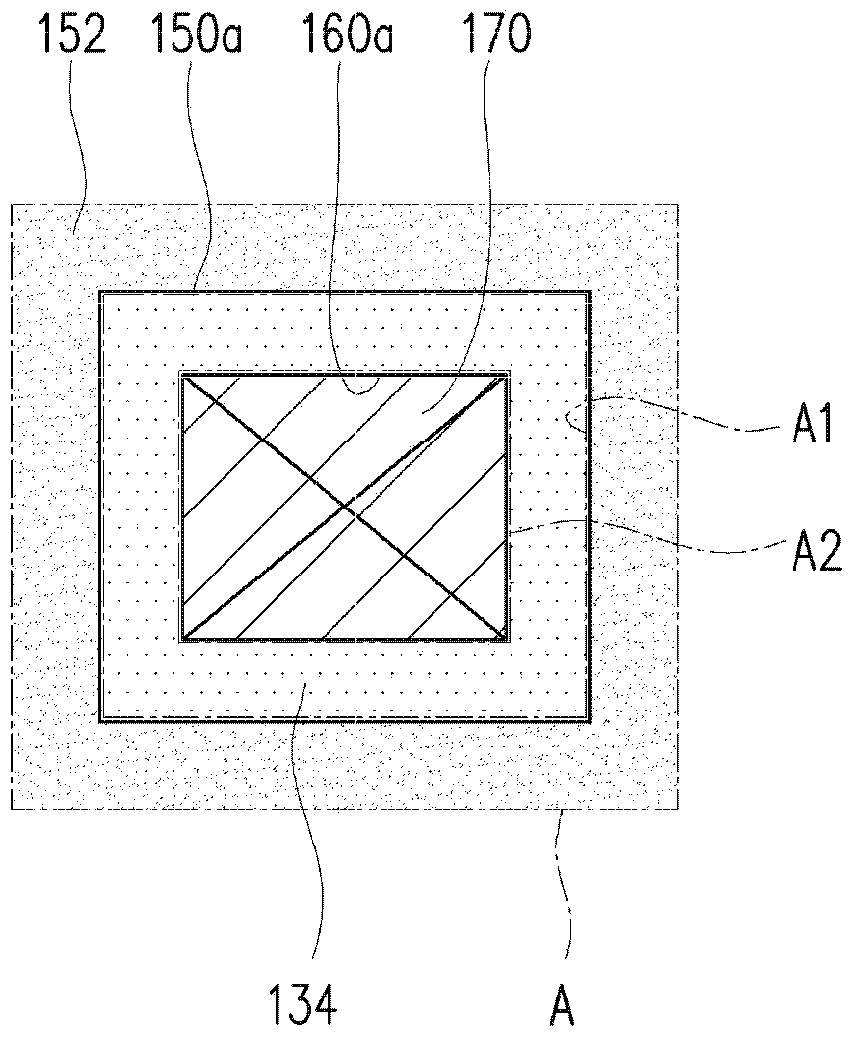

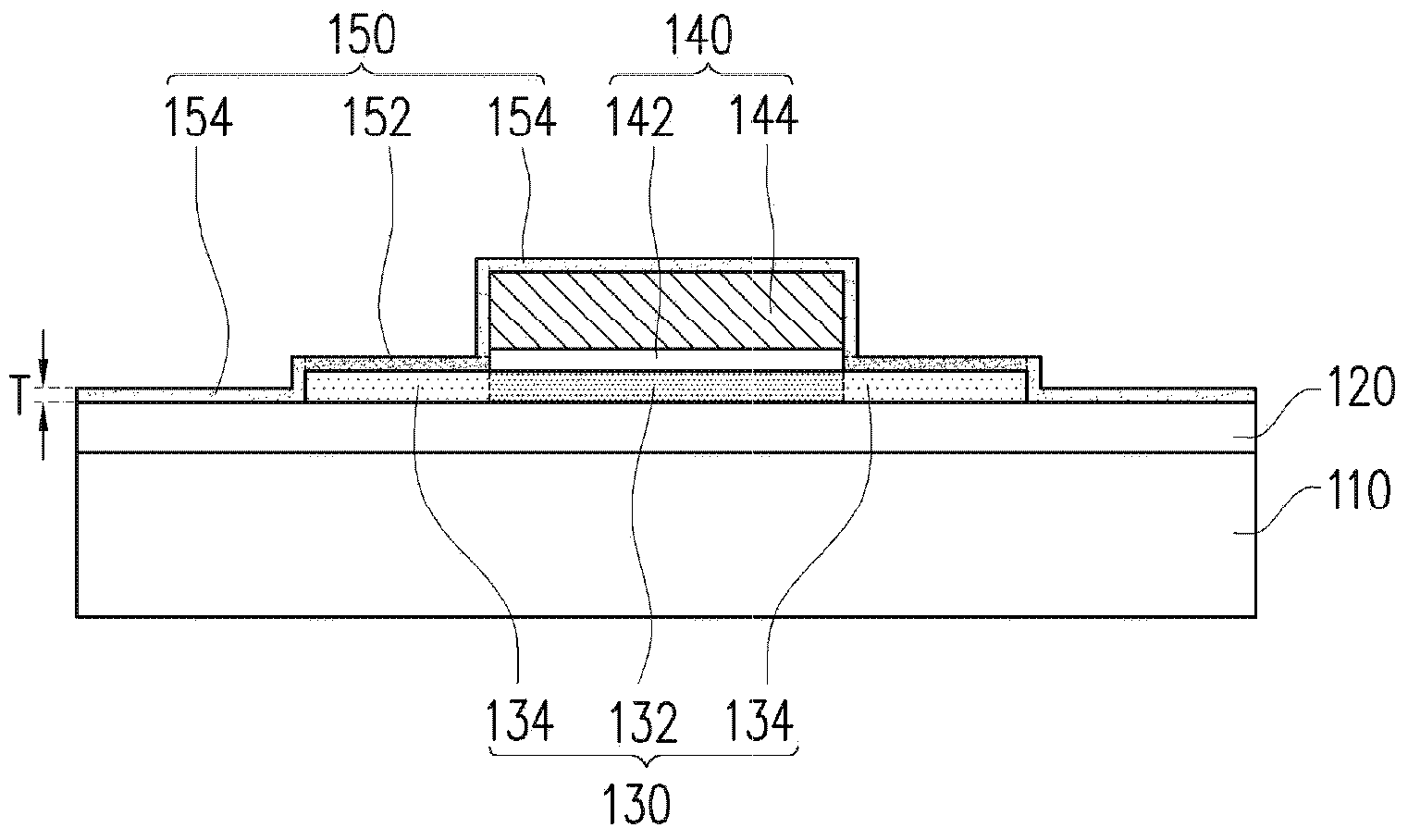

InactiveCN103545380AGood component propertiesAvoid contactTransistorSemiconductor/solid-state device manufacturingLow oxygenSemiconductor

The invention provides a thin film transistor and producing method thereof. The thin film transistor comprises an oxide semiconductor layer, a gate insulating layer, a grid, an oxygen absorption layer, an insulating layer and many conductive electrodes. The oxide semiconductor comprises many low oxygen regions and channel regions between low oxygen regions. The gate indulating layer is located between the oxide semiconductor layer and the grid, and covers the channel region and exposes the low oxygen region. The oxygen absoption layer is located on the low oxygen region with many first openings. The first opening exposes a low oxygen region with a first area. The insulating layer covers the oxygen absorption layer, the oxide semiconductor layer and the gate grid with many second openings. The second opening is located in the first opening for exposing the low oxygen region with a second area. The second area is smaller than the first area. The conductive electrode is located in the second are for contacting the low oxygen region.

Owner:AU OPTRONICS CORP

Structure of channel shielded Rom memory unit and producing method thereof

InactiveCN1472817AReduce lateral spreadImprove featuresSolid-state devicesSemiconductor/solid-state device manufacturingInternal memoryArray data structure

In the method, a shallow ditch is formed on surface of a silicon base material and to implant simultaneously buried ion and anti-punch through dopand in the silicon base material and array region of internal memory storage unit. The buried ion doping region is defined and multiditch is formed at array region of the storage unit. Then, a gate-oxide and a patternized polysilicon grid are formed at the silicon base material and furthermore multitransistor can be formed at peripheral circuit region of the silicon base material.

Owner:GRACE SEMICON MFG CORP

Semiconductor device, light emitting diode head, and image forming apparatus

InactiveUS8035116B2Shorten the lengthImprove energy efficiencySemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceEngineering

Owner:OKI DATA CORP

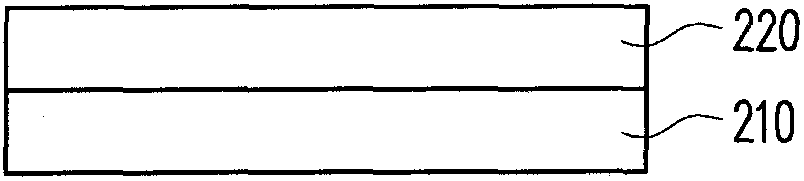

Method for manufacturing solar battery

InactiveCN102254999AIncrease the open circuit voltageHelp mass productionFinal product manufactureSemiconductor devicesOptoelectronicsSolar battery

The invention discloses a method for manufacturing a solar battery, including following steps of: firstly providing a substrate and forming a substrate electrode on the substrate; forming a CIGS crystallizing layer on the substrate electrode; processing a chemo mechanical grinding technology on the surface of the CIGS crystallizing layer so as to flatten the CIGS crystallizing layer; forming a buffer layer on the flattened CIGS crystallizing layer surface; and forming a transparent conductive layer on the buffer layer. Therefore, the method for manufacturing the solar battery facilitates volume production and the manufactured solar battery has the good element performance.

Owner:AU OPTRONICS CORP

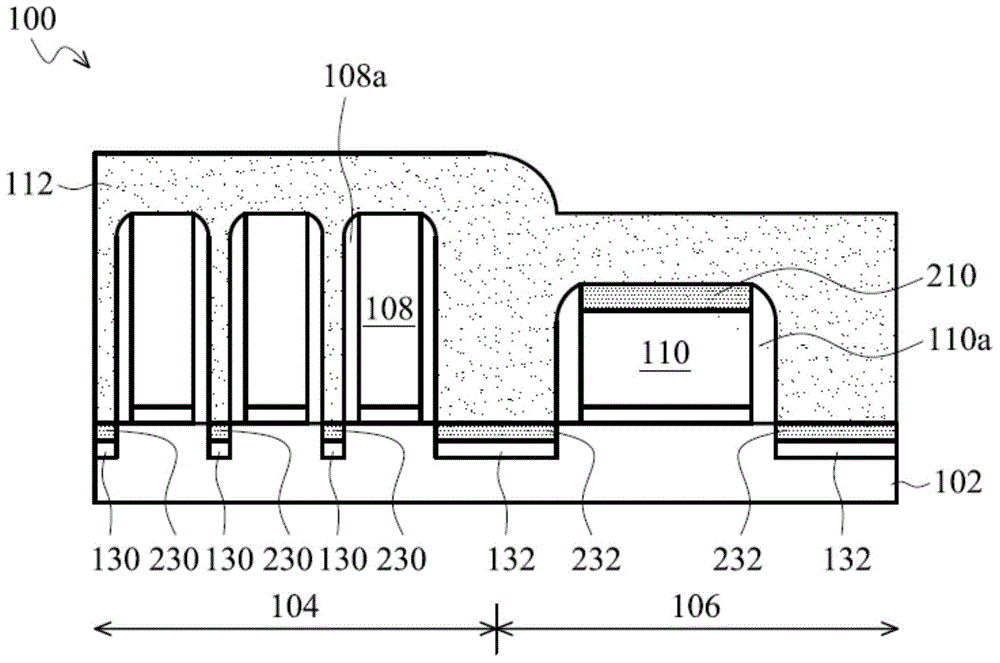

Manufacture method of storage device

ActiveCN104681497AAvoid destructionGood component propertiesSemiconductor/solid-state device manufacturingStorage cellMaterials science

The invention relates to a manufacture method of a storage device. The manufacture method comprises the steps of providing a substrate, wherein the substrate comprises a storage unit area and a peripheral area; forming a plurality of first grid electrodes in the storage unit area and forming at least one second grid electrode in the peripheral area; forming a sacrifice layer on the substrate; forming a first stop layer on the sacrifice layer in the storage unit area; carrying out the etching process by adopting the first stop layer as a mask; sequentially forming a second stop layer on the substrate; depositing a dielectric material on the second stop layer; carrying out the flattening process for the dielectric material by adopting the first stop layer and the second stop layer in the storage unit area as a grinding stop layer; removing the first stop layer and the second stop layer in the storage unit area; removing the sacrifice layer in the storage unit area so as to forming a plurality of first contact openings among the first grid electrodes after the first stop layer and the second stop layer are removed. The stop layers in different thicknesses are formed in the storage unit area and the peripheral area, so that a landing area contacting a plug is not compressed while the size of the storage device is further reduced.

Owner:WINBOND ELECTRONICS CORP

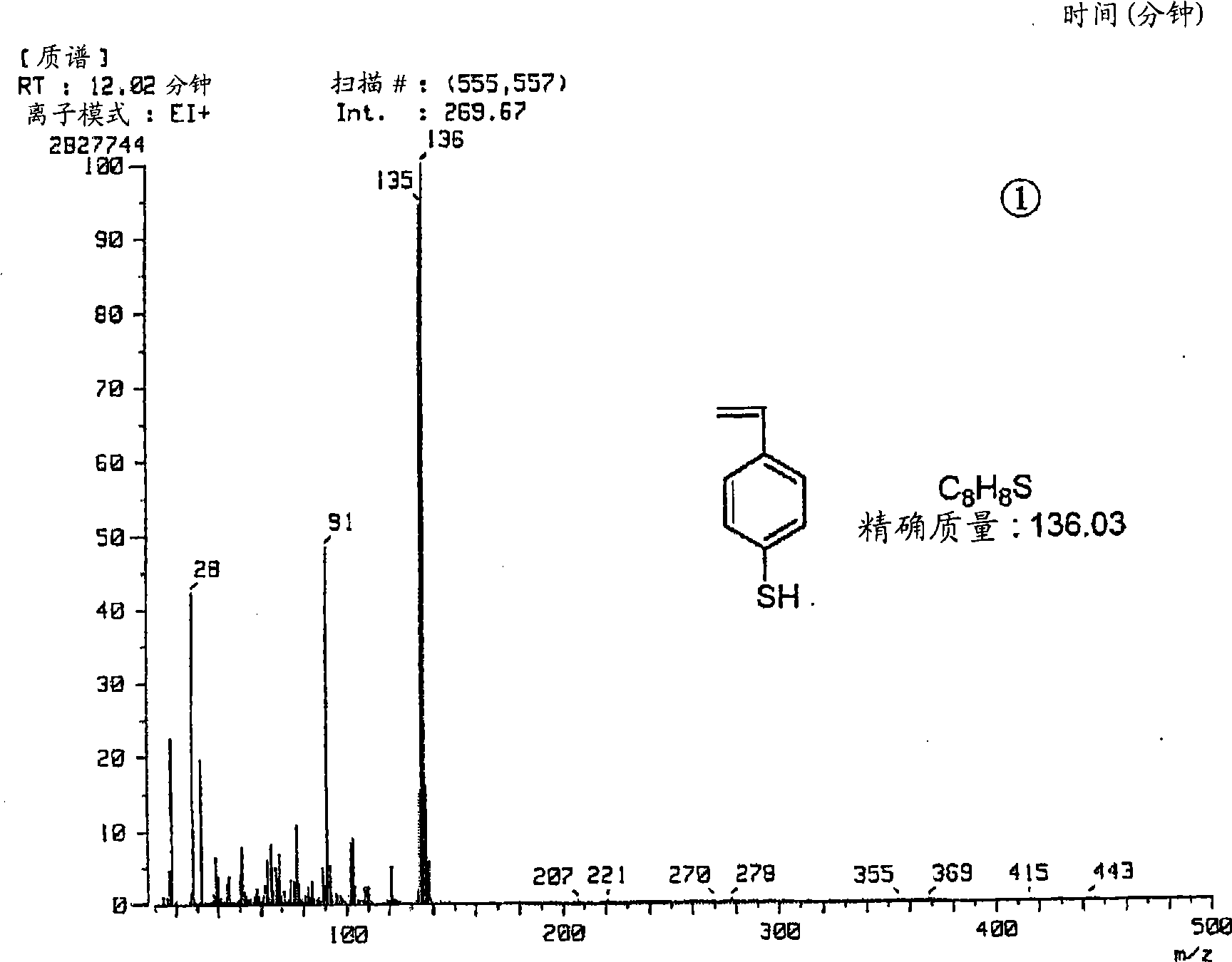

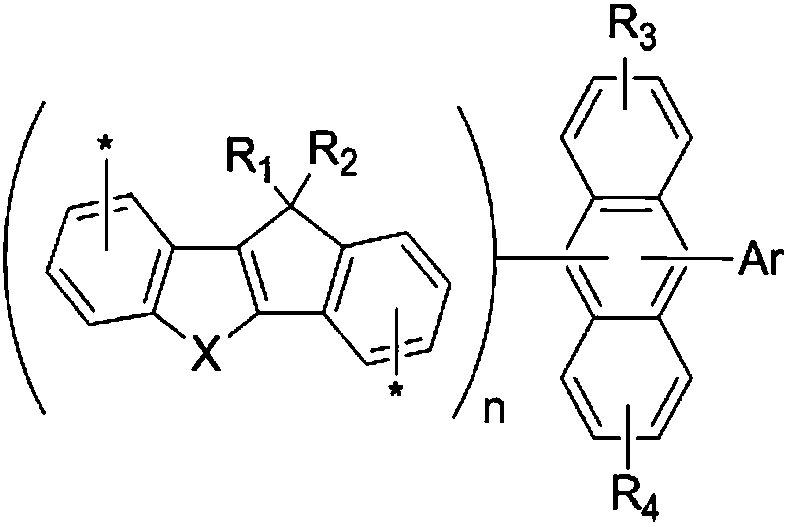

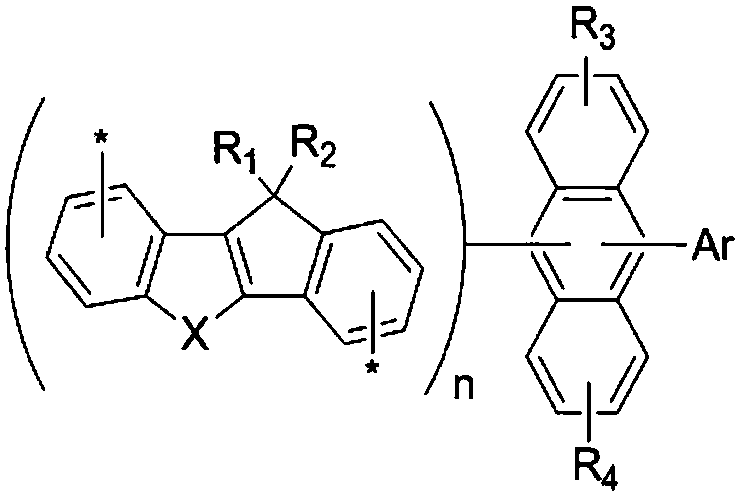

Insulating layer, electronic device, field effect transistor, and polyvinylthiophenol

ActiveCN101501080AGood component propertiesImprove featuresTransistorSolid-state devicesHydrogen atomOrganic group

For the purpose of providing an insulting layer which enables to improve device characteristics when used in an electronic device, a polymer insulator containing a repeating unit represented by the formula below is contained in the insulating layer. In the formula, R represents a direct bond or an arbitrary linking group; Ar represents an optionally substituted divalent aromatic group; and R represents a hydrogen atom, a fluorine atom or a monovalent organic group.

Owner:MITSUBISHI RAYON CO LTD

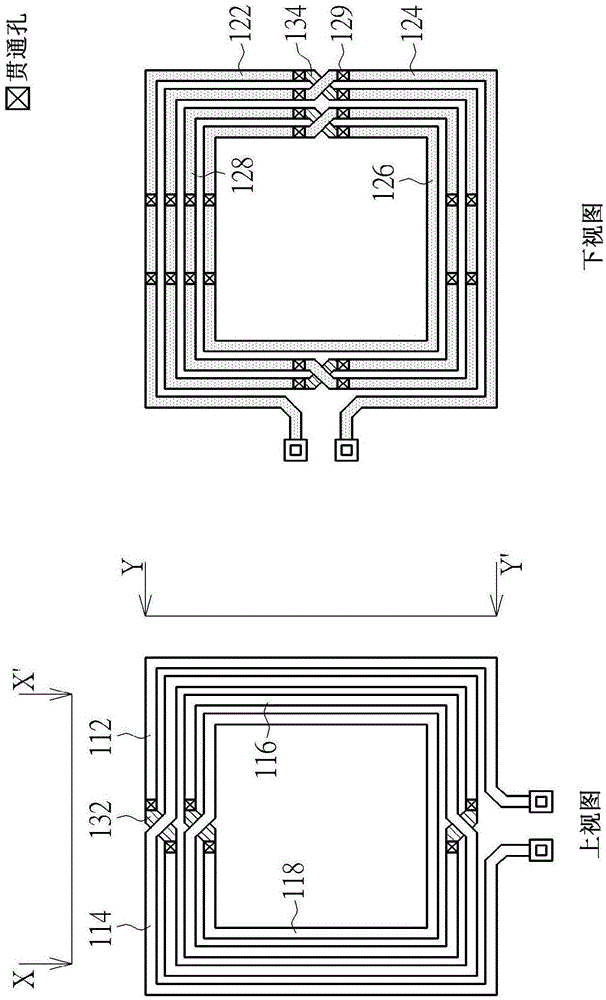

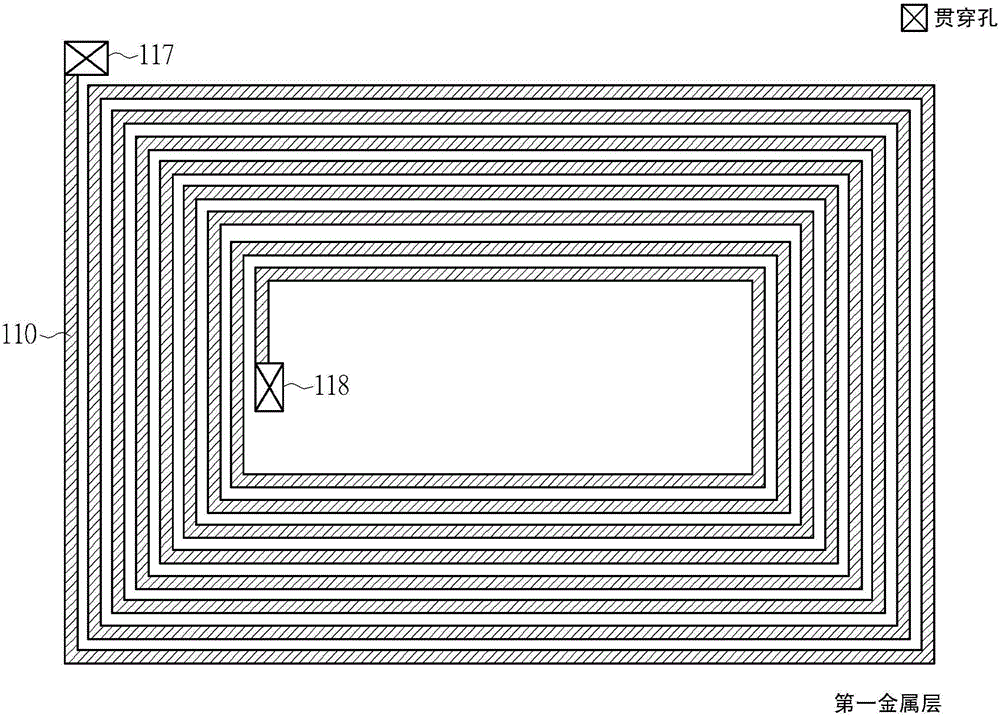

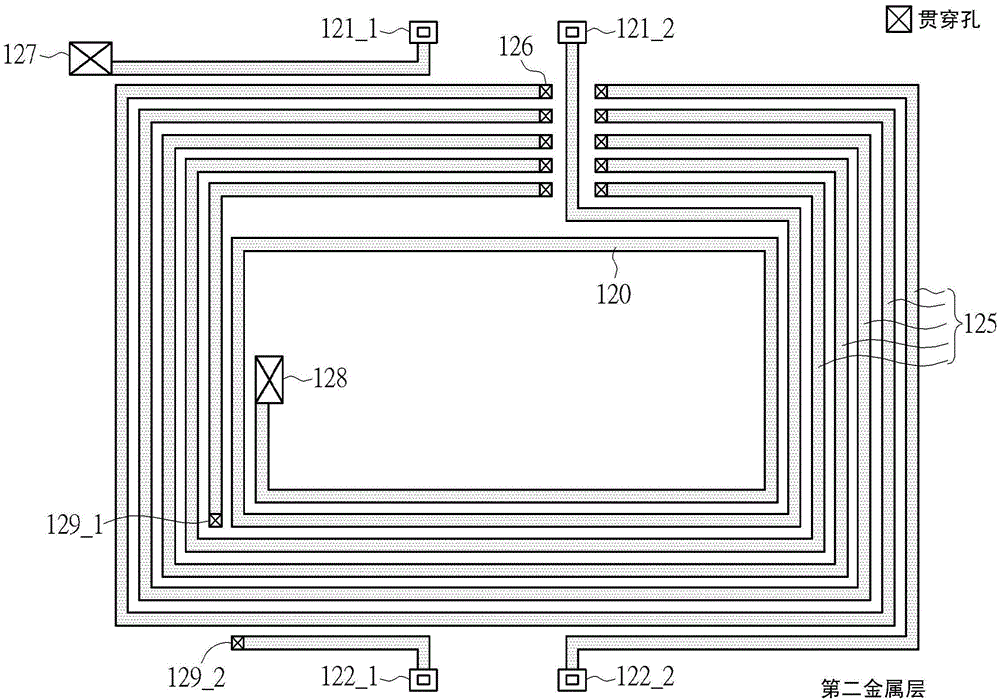

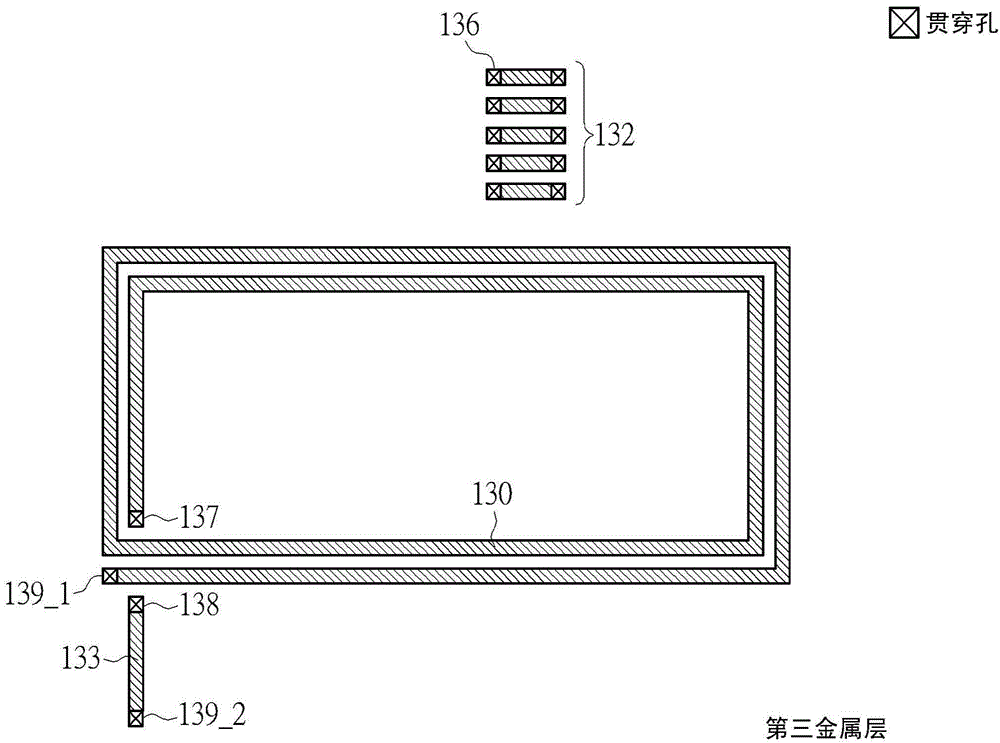

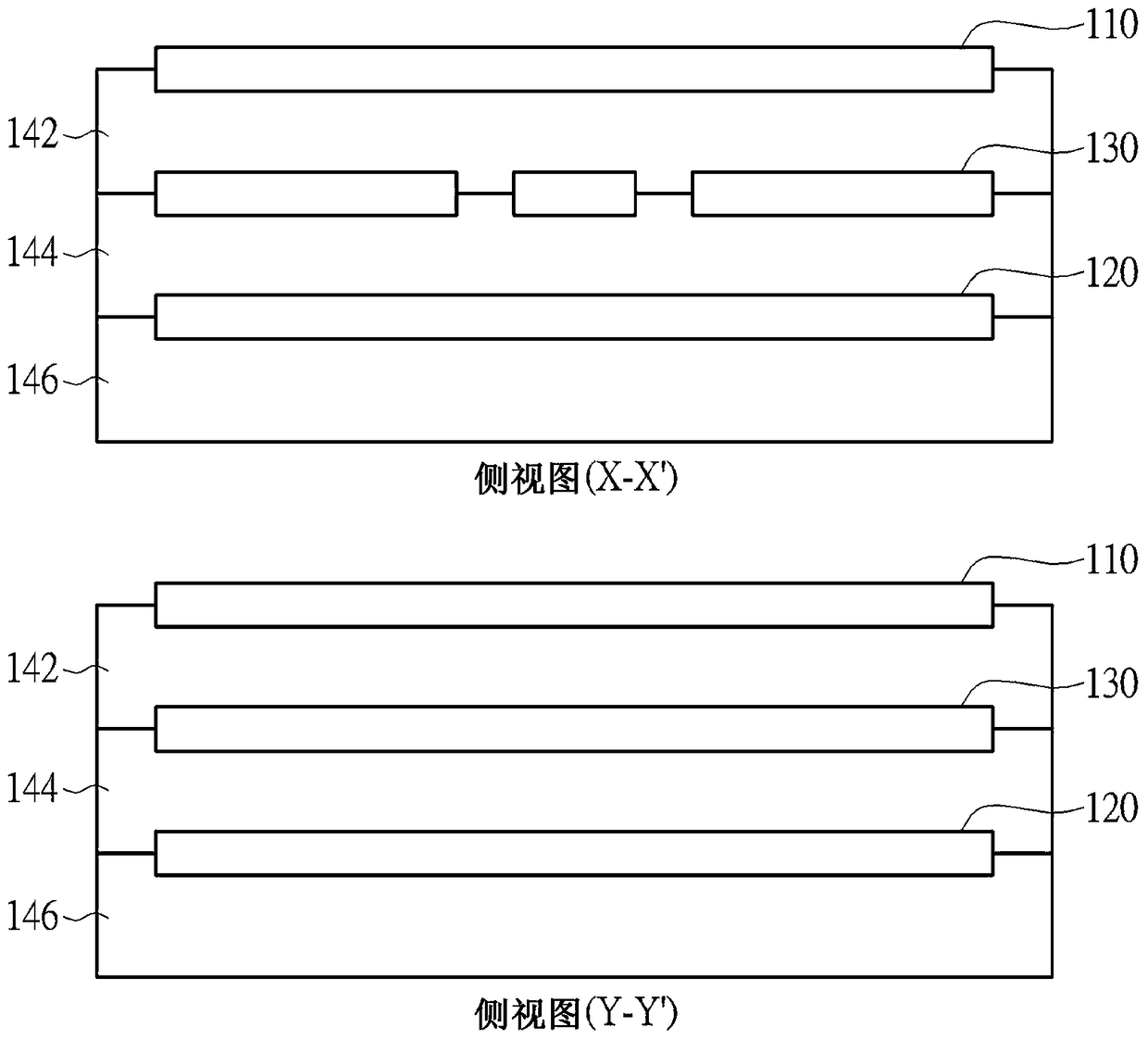

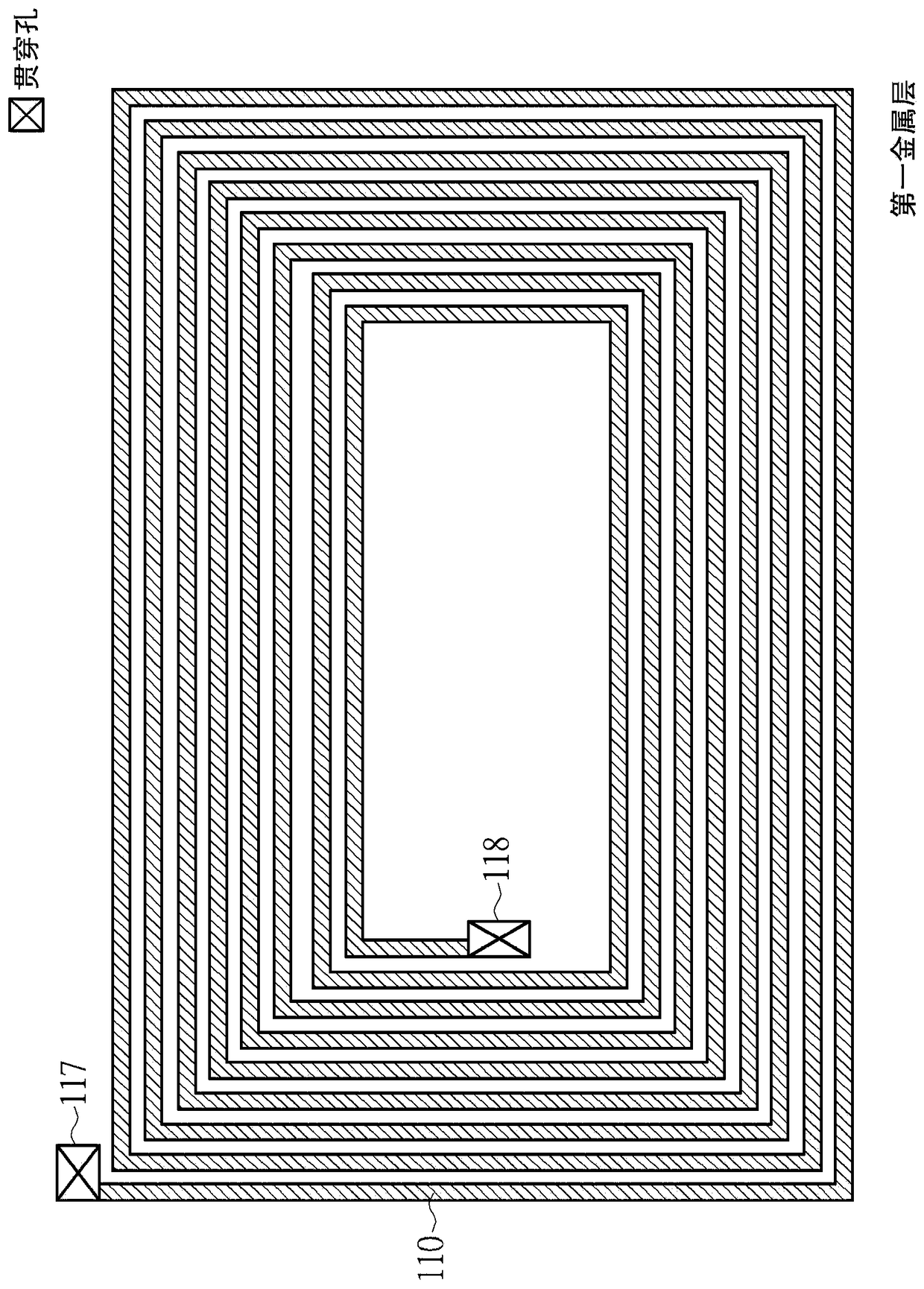

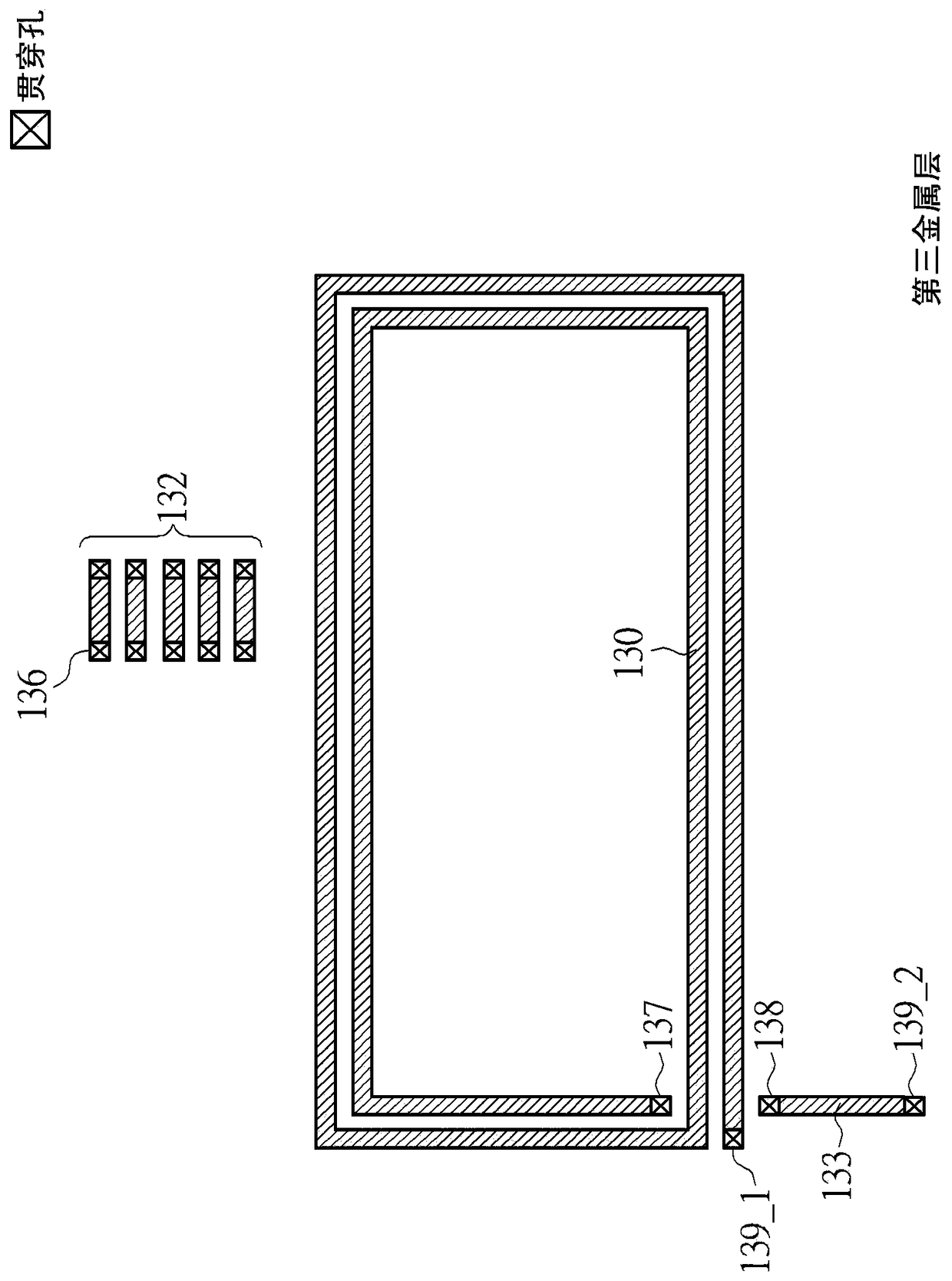

Integrated transformer

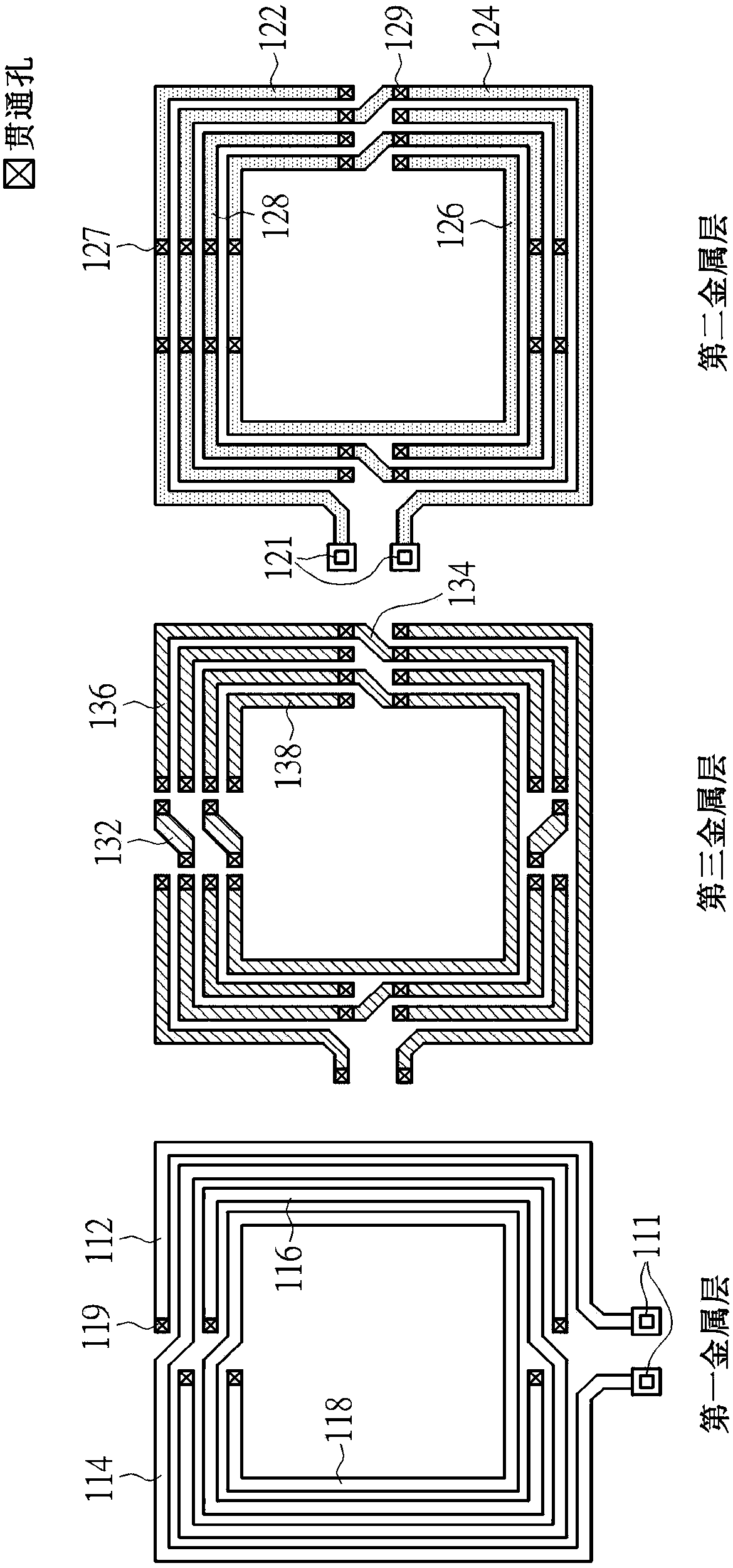

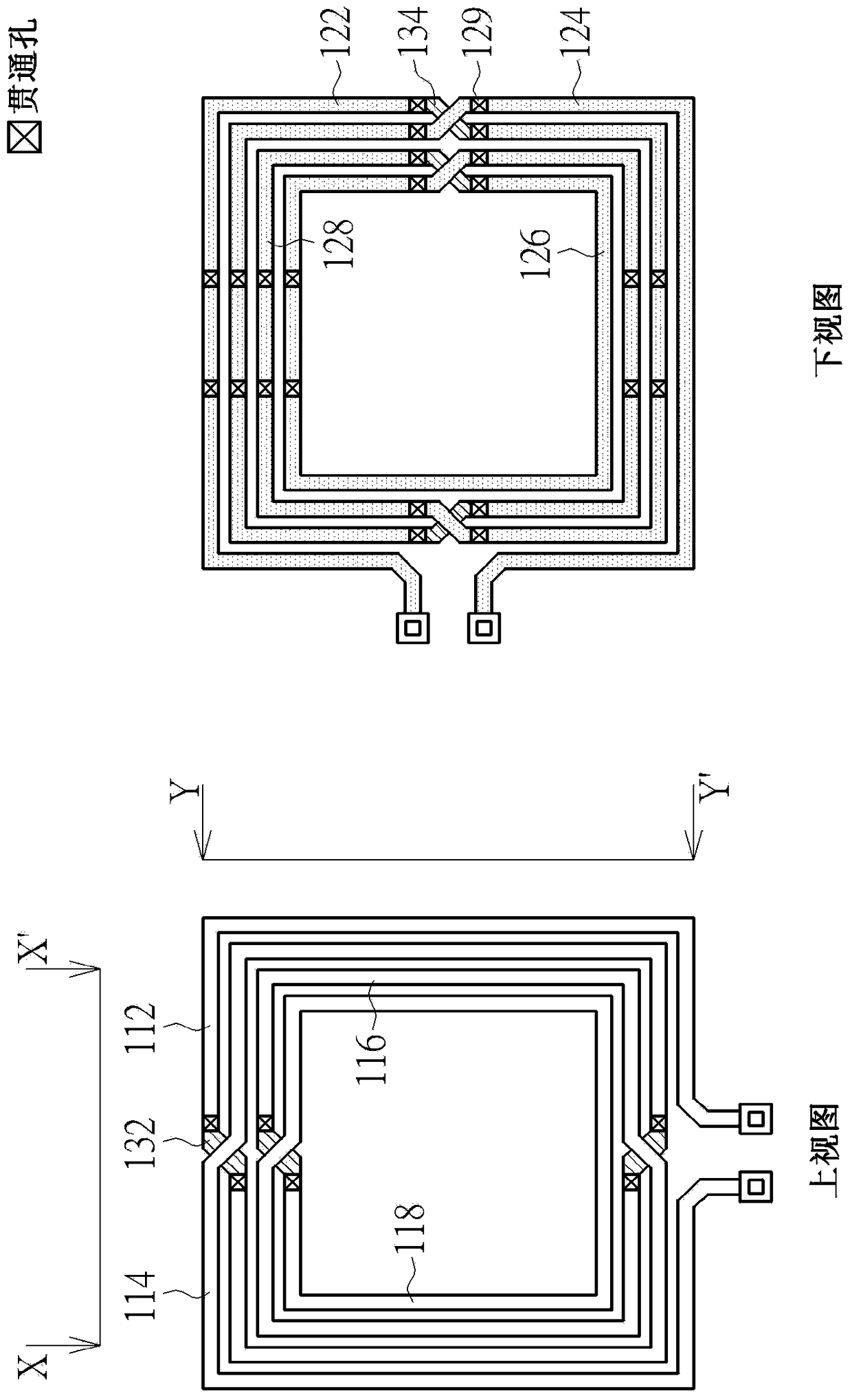

ActiveCN104952834AQuality improvementImprove coupling coefficientSemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsTransformerInductor

The invention discloses an integrated transformer which comprises a first coiling, a second coiling and a plurality of bridging lines, wherein the first coiling is formed by a first metallic layer and has a plurality of disconnected sections, the second coiling is formed by a second metallic layer and has a plurality of disconnected sections, the bridging lines are formed by a third metallic layer. Some of the bridging lines connect the sections of the first coiling, so that the sections of the first coiling form a first inductor. Other bridging lines connect the sections of the second coiling, so that the sections of the second coiling form a second inductor.

Owner:REALTEK SEMICON CORP

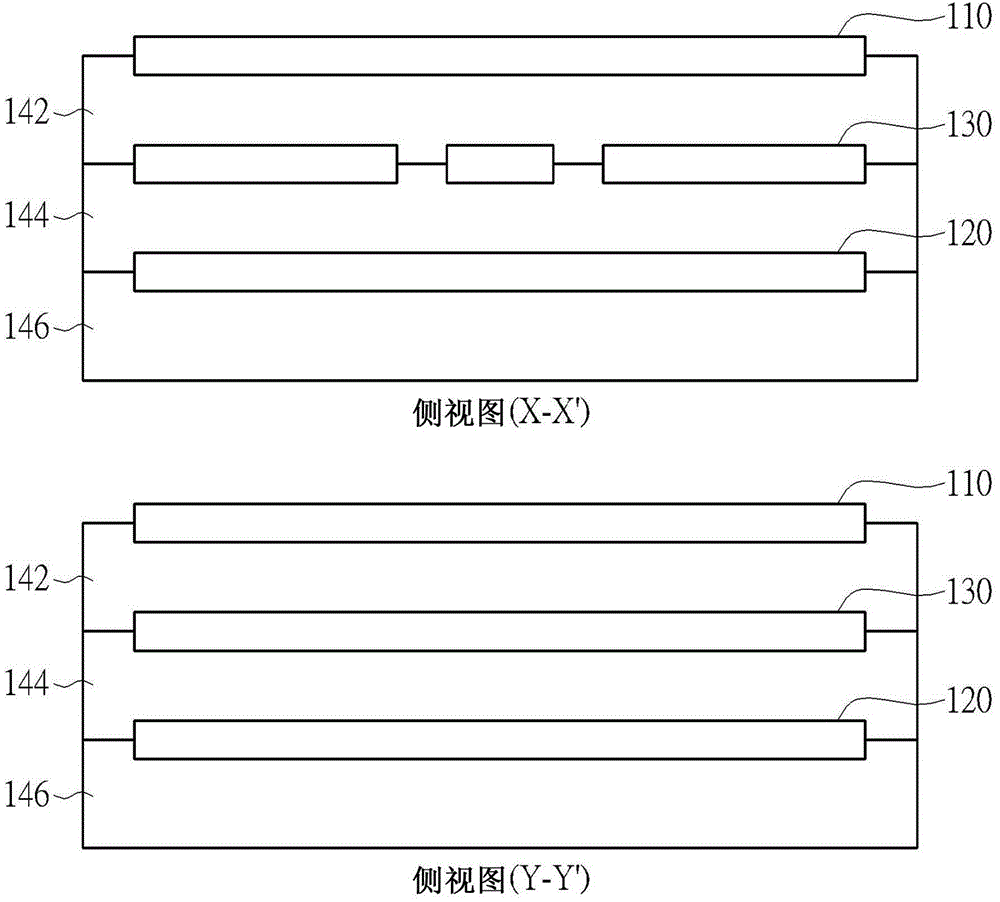

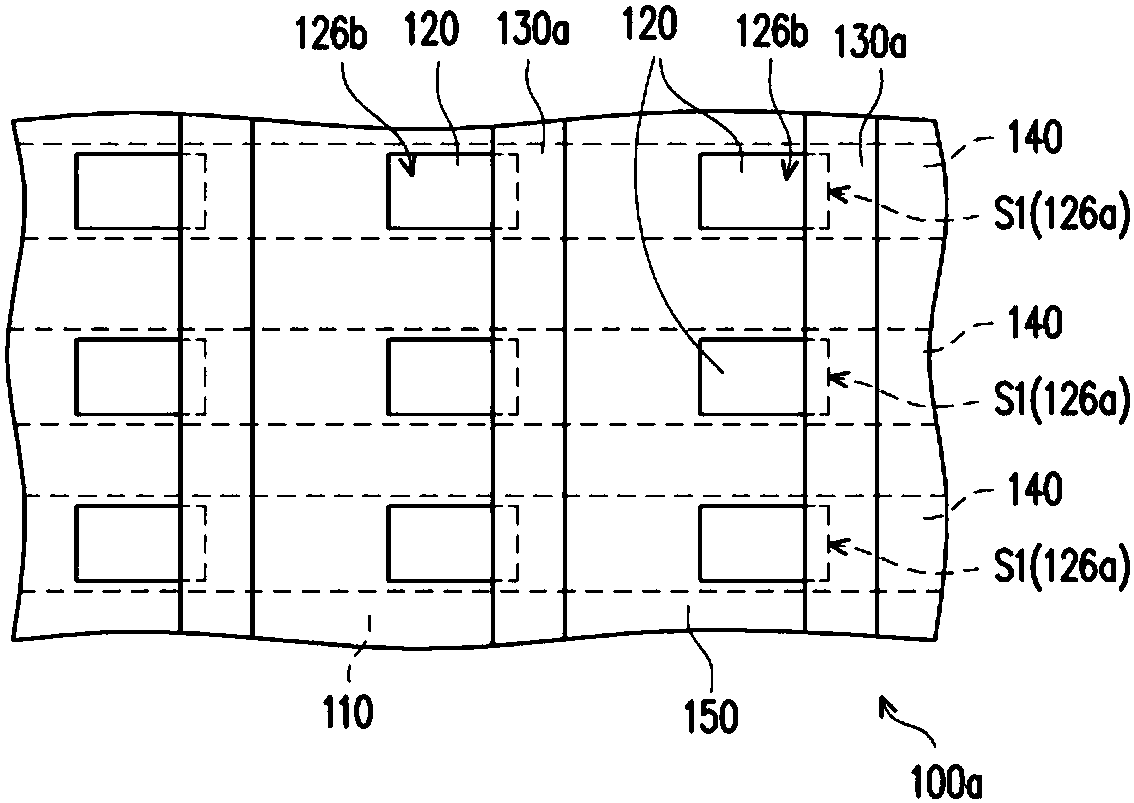

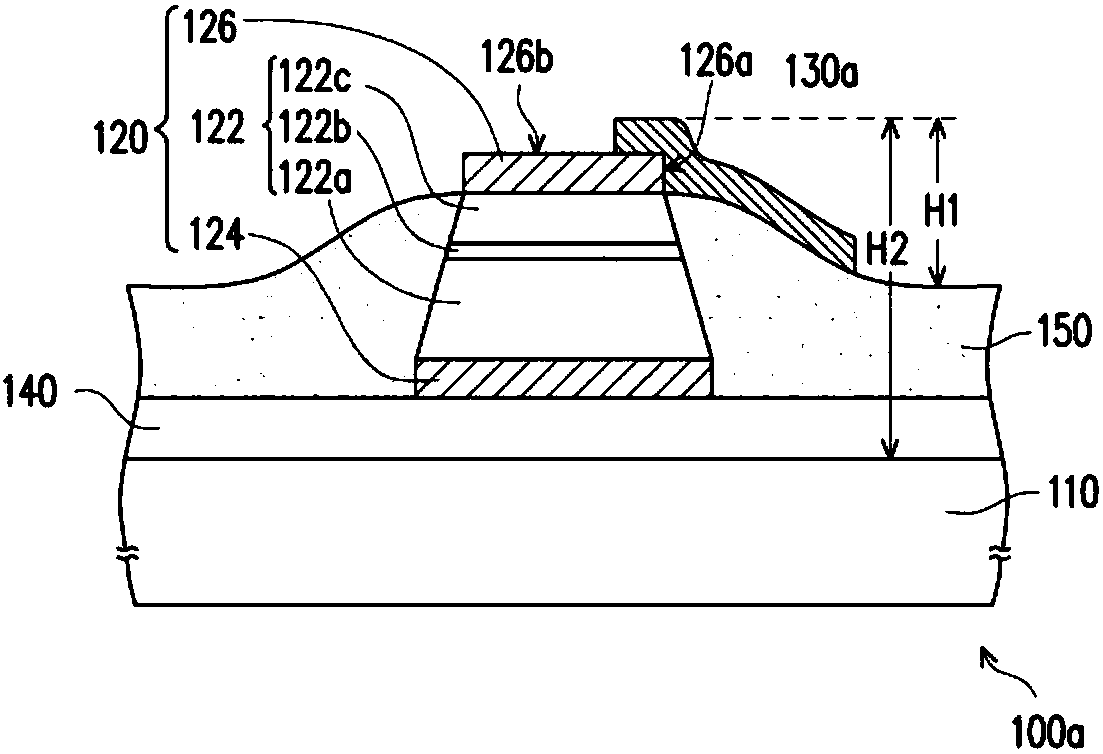

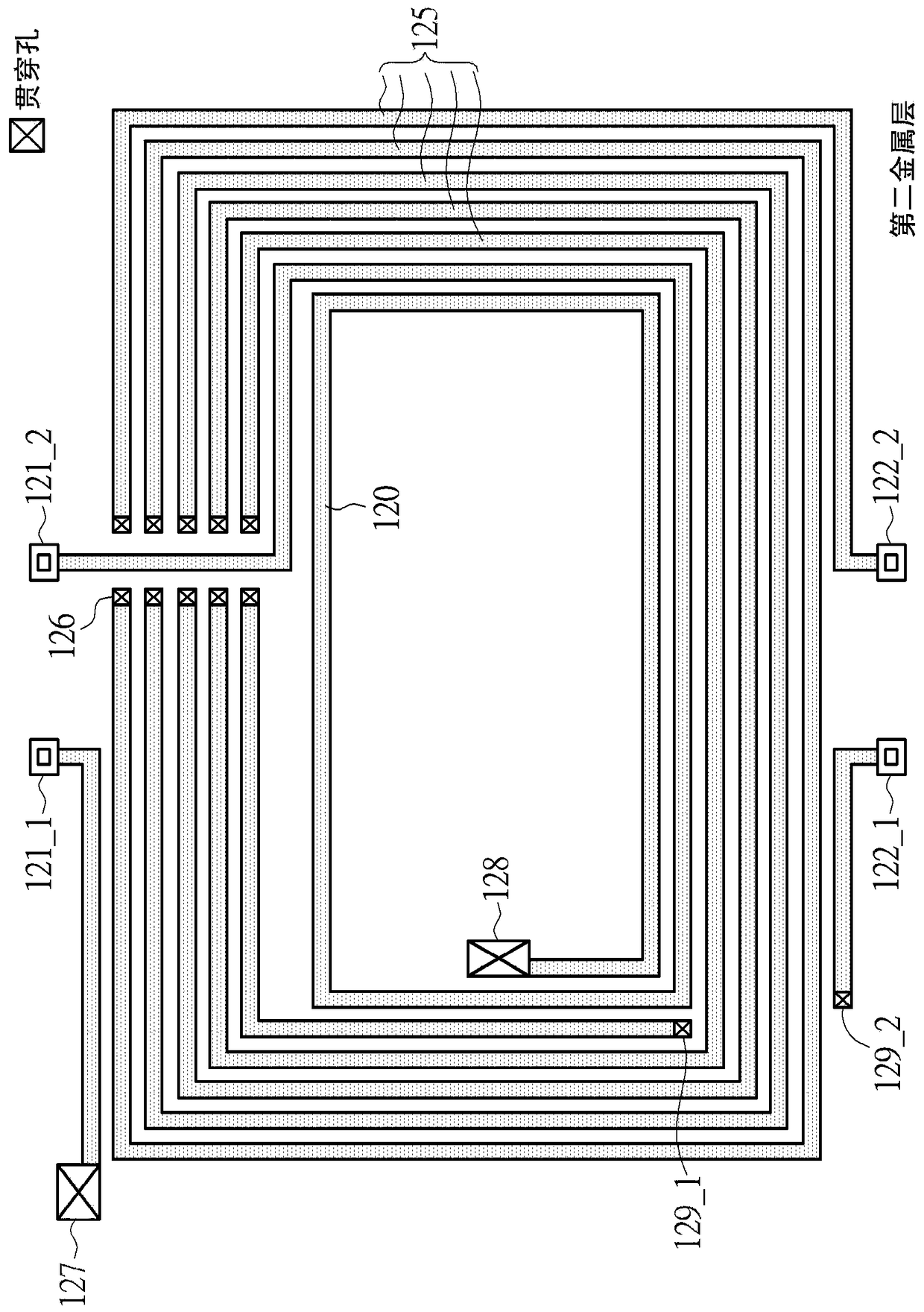

Integrated transformer

ActiveCN105280605AImprove qualityImprove coupling coefficientSemiconductor/solid-state device detailsSolid-state devicesTransformerEngineering

An integrated transformer comprises a first inductor and a second inductor, the first inductor comprises B circles of spiral wirings formed by a first metal layer and A circles of wirings formed by a second metal layer, and the A circles of the wirings formed by the second metal layer is overlapped with the innermost A circles of the wirings of the B circles of the spiral wirings formed by the first metal layer; and the second inductor comprises C circles of wirings formed by at least the second metal layer, the C circles of the wirings, formed by the second metal layer, of the second inductor are substantially overlapped with the partial wirings formed by the first metal layer, A is less than B, and A is less than C.

Owner:REALTEK SEMICON CORP

Display unit

ActiveCN109244100AGood component propertiesImprove production yieldSolid-state devicesSemiconductor devicesOhmic contactDisplay device

A display device includes a driving substrate, a plurality of light emitting elements, and a plurality of metal common electrodes. The light emitting elements are dispersively arranged on the drivingsubstrate, and each light emitting element includes an epitaxial structure layer and a first type electrode and a second type electrode arranged on the epitaxial structure layer. A metal common electrode is dispose dispersedly on that drive substrate and contacts a portion of the second type electrode of each light emit element to form an ohmic contact.

Owner:PLAYNITRIDE

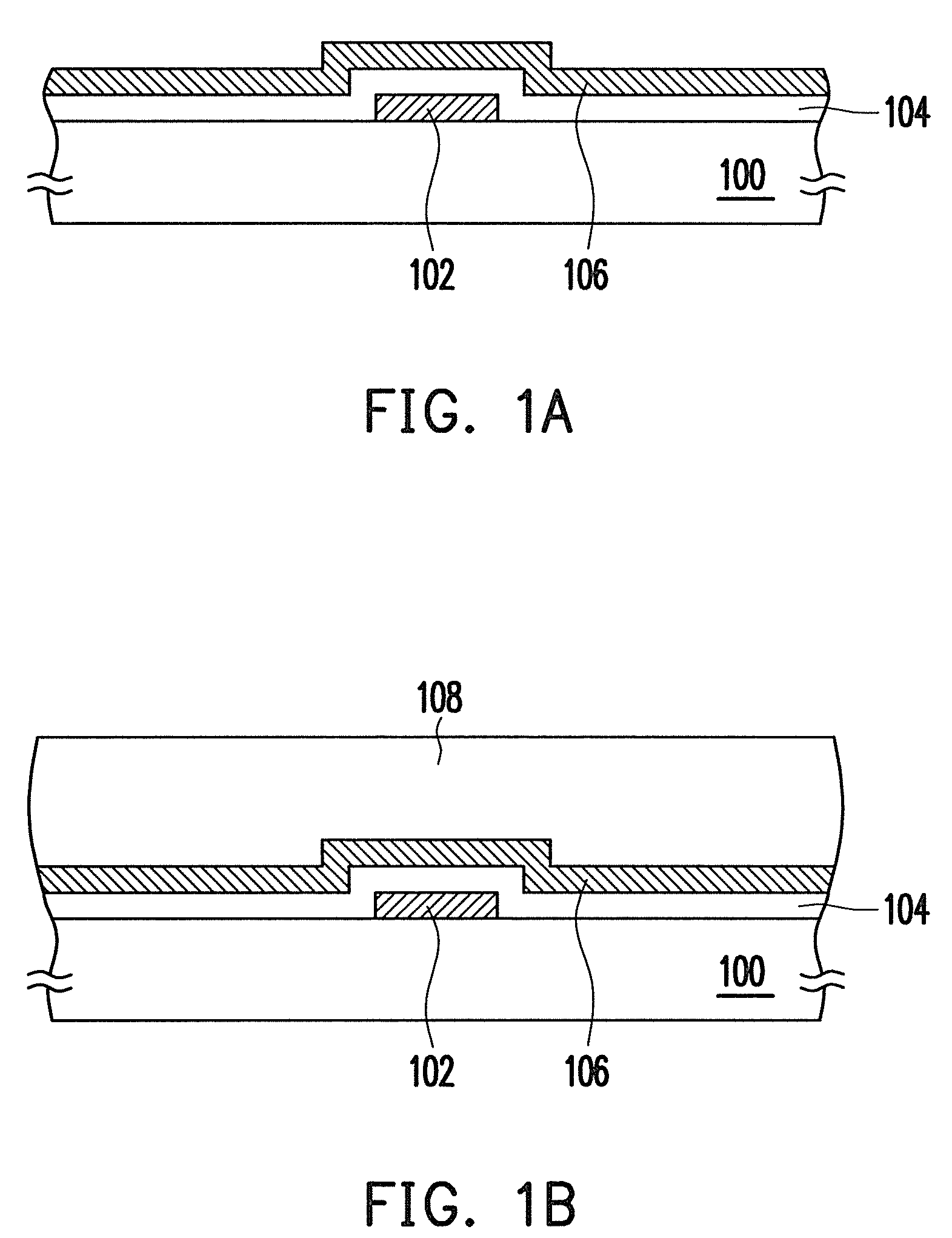

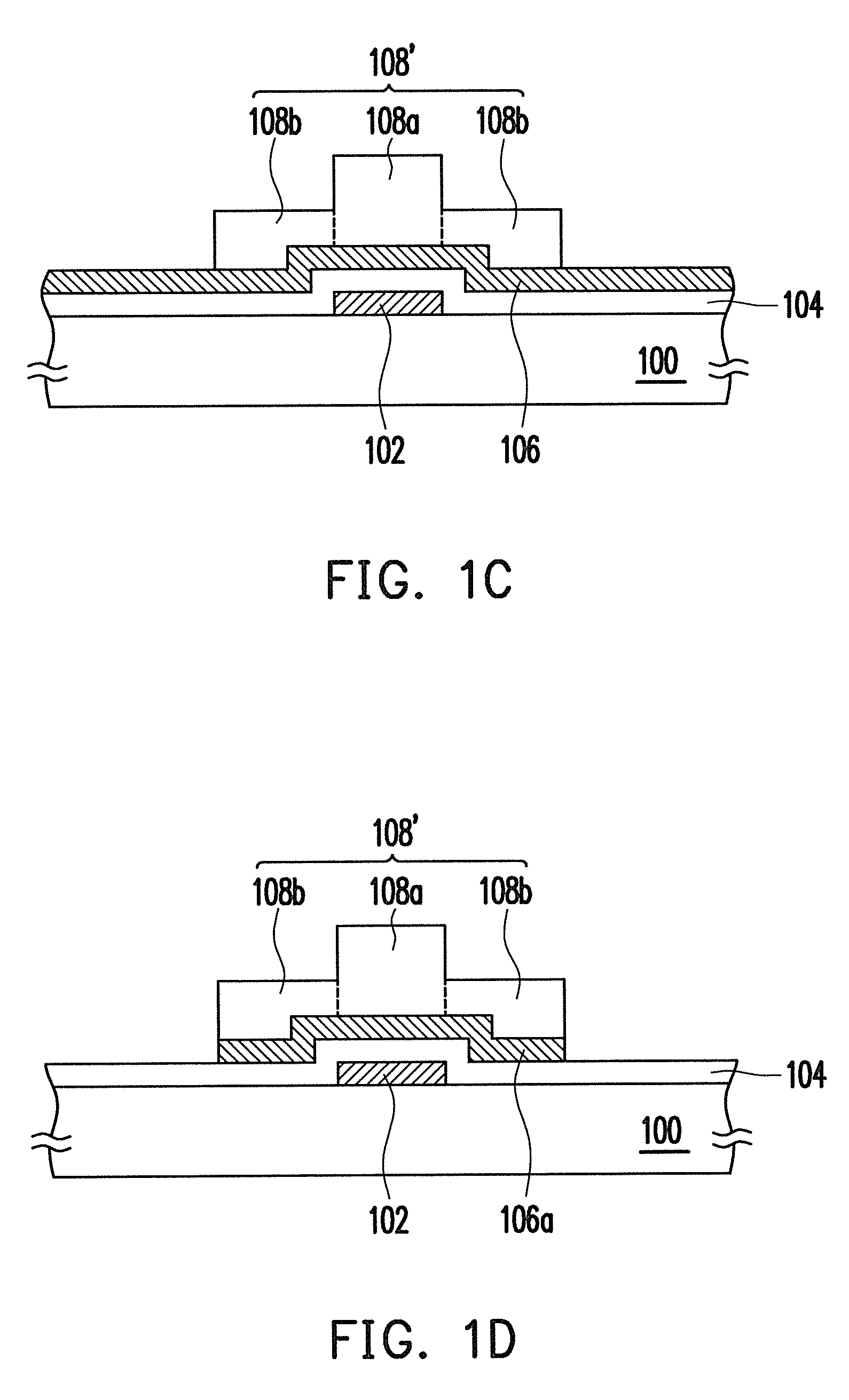

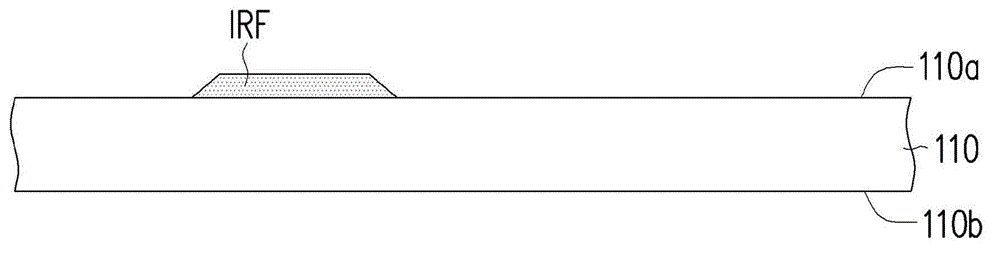

Method for fabricating thin film transistor

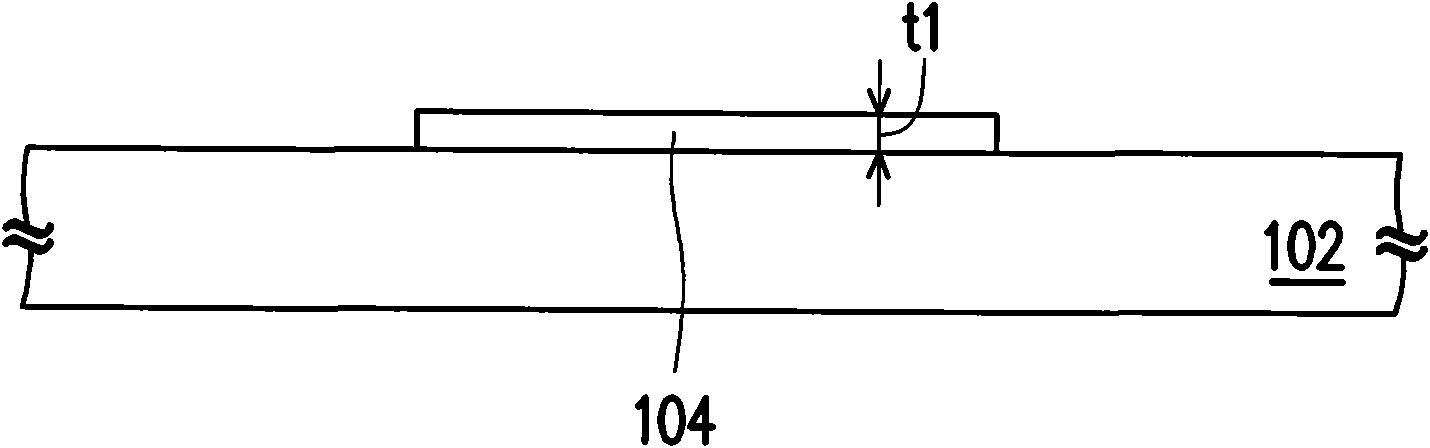

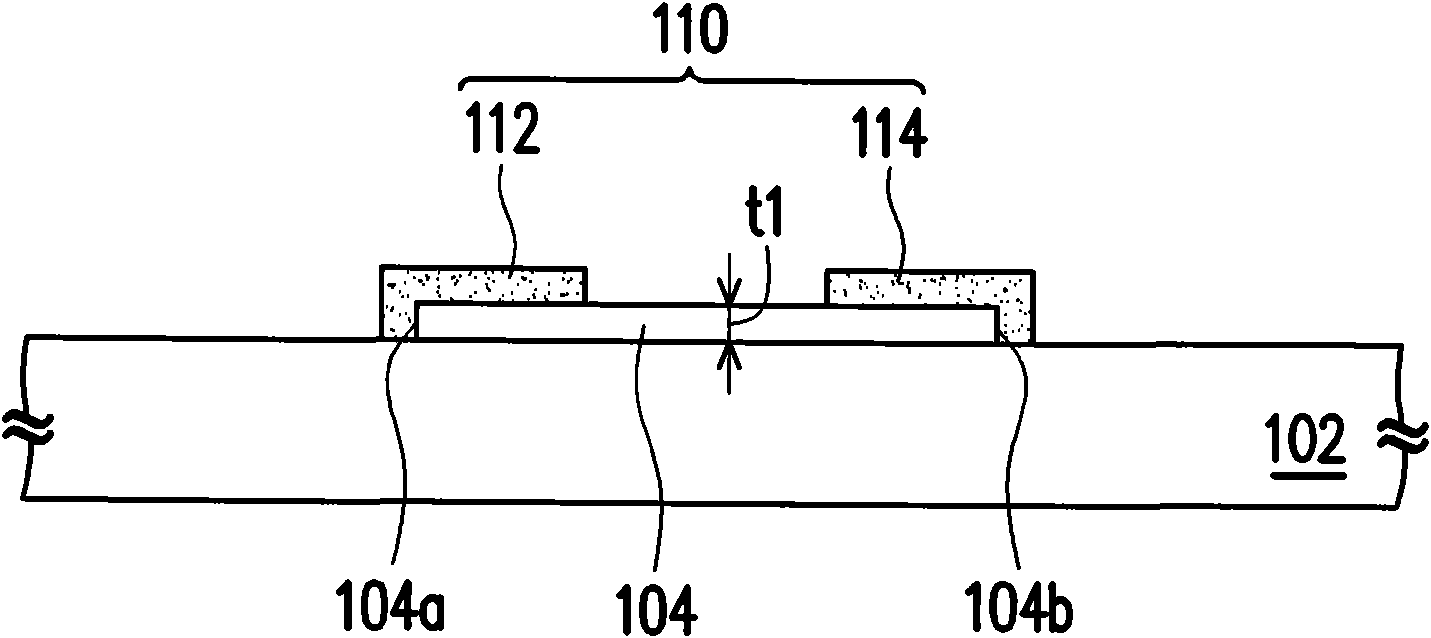

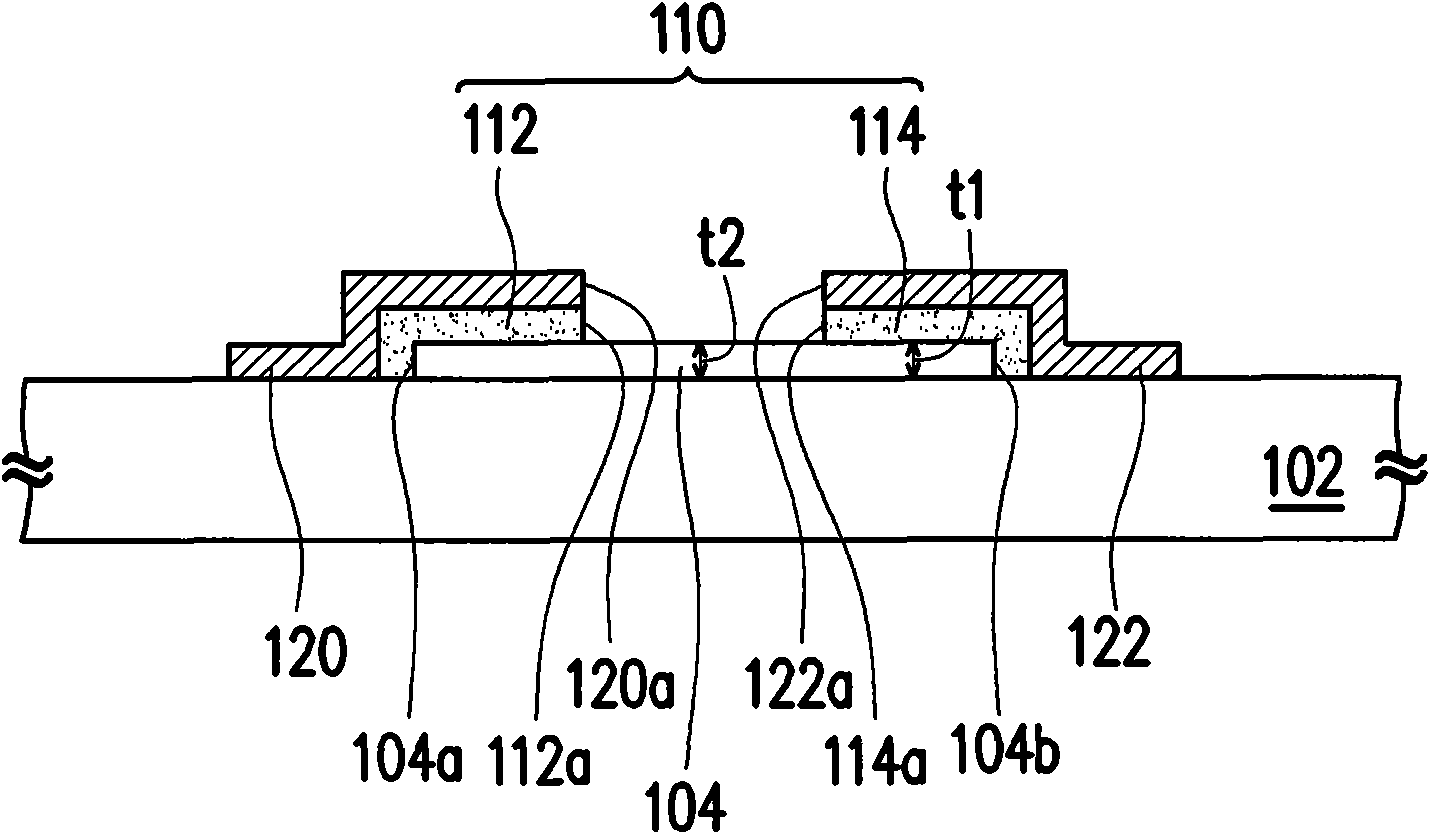

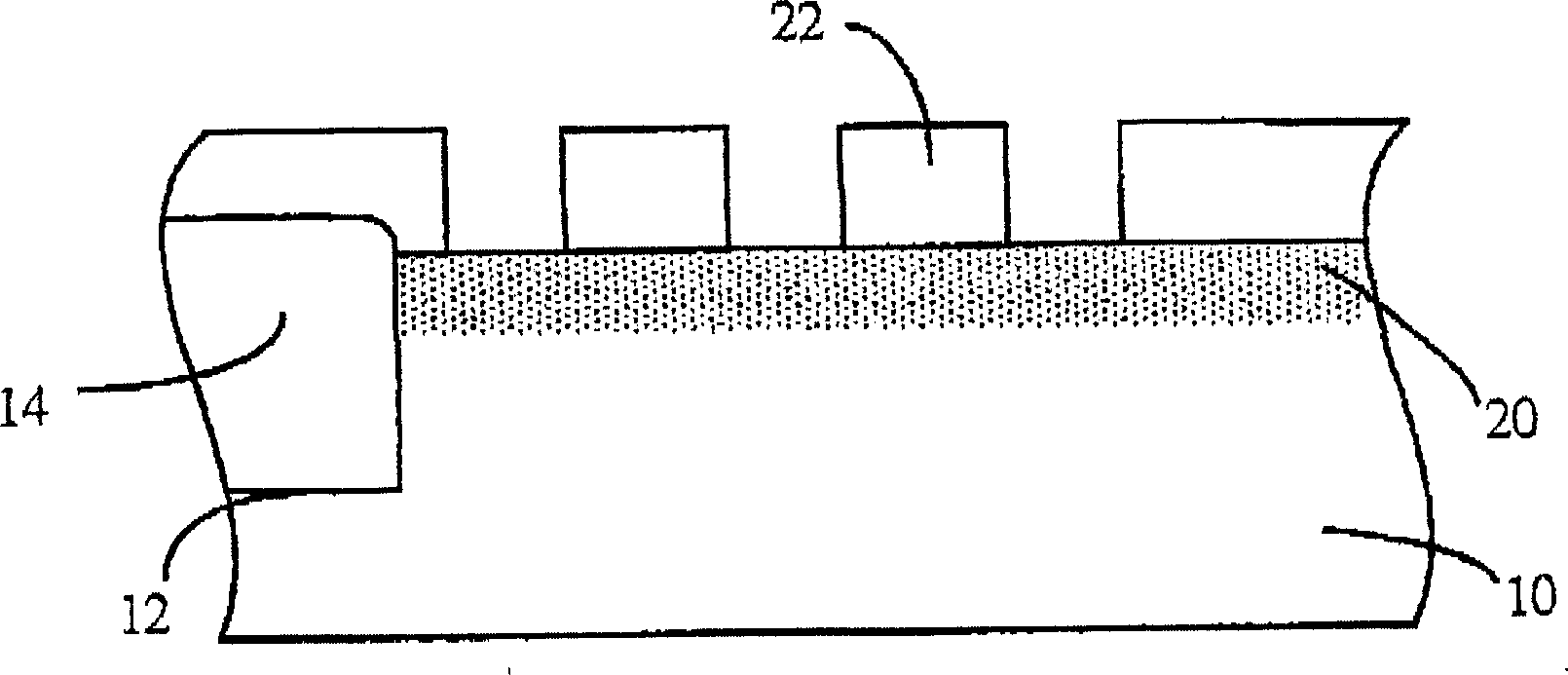

InactiveUS8222095B2Good component propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsActive layer

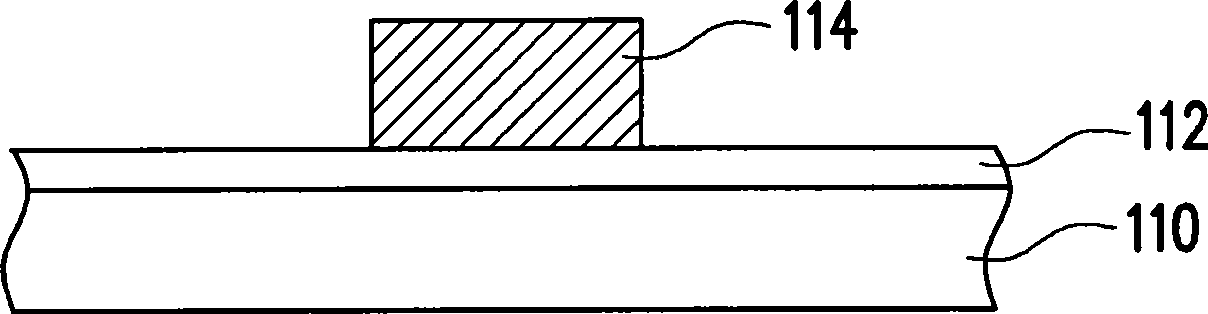

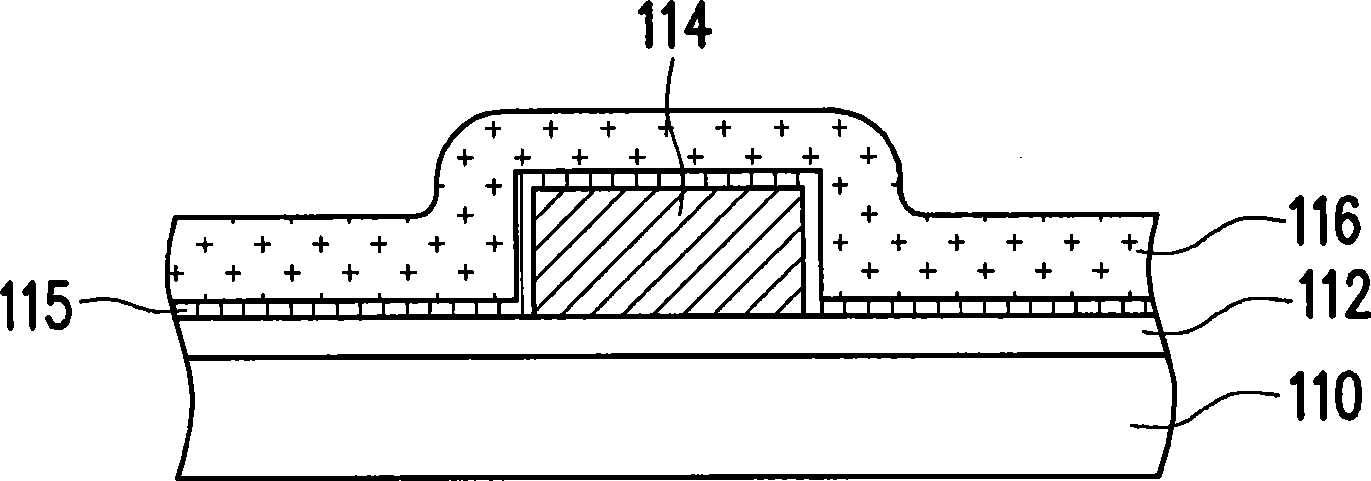

A method for fabricating a thin film transistor is provided. A gate is formed on a substrate. A gate insulating layer is formed on the substrate to cover the gate. A metal oxide material layer is formed on the gate insulating layer. A photoresist layer is formed on the metal oxide material layer, in which a thickness of the photoresist layer above the gate is larger than that of the photoresist layer above two sides adjacent to the gate. A portion of the metal oxide material layer is removed to form a metal oxide active layer by using the photoresist layer as a mask. The photoresist layer above the two sides adjacent to the gate is removed and the remaining photoresist layer covers a portion of the metal oxide active layer. A source and a drain are formed on the metal oxide active layer covered by the photoresist layer.

Owner:TAIWAN TFT LCD ASSOC +5

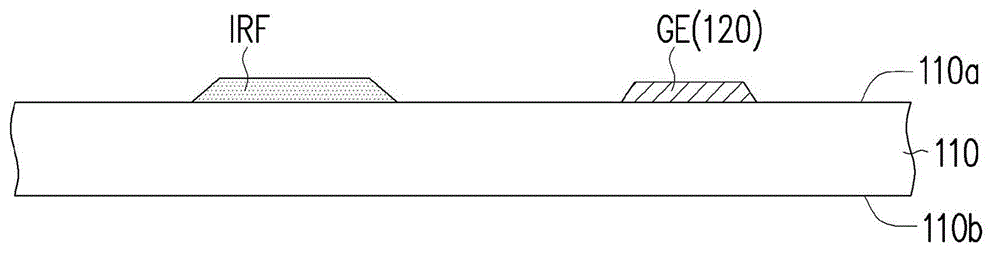

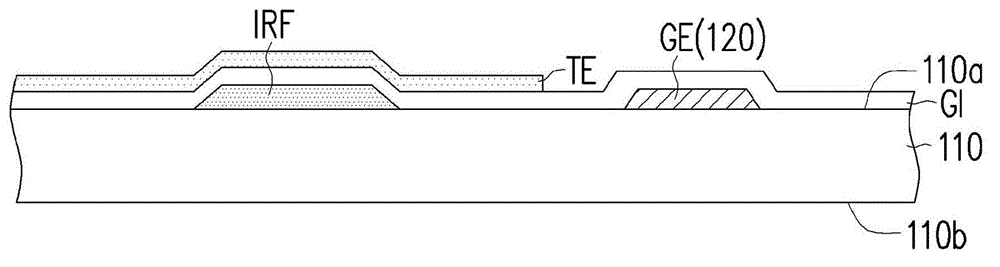

Optical touch panel, manufacturing method thereof, and optical touch display panel

InactiveCN102830859BBest penetration rateGood component propertiesInput/output processes for data processingLight sensingEngineering

The invention provides an optical profile type touch panel, a manufacturing method therefor, and an optical profile type touch display panel. The optical profile type touch panel comprises an infrared light filter layer disposed on an internal surface of a substrate, a first patterning conducting layer comprises grid electrodes and scanning lines which are disposed on the internal surface of the substrate, a first dielectric layer which covers the grid electrodes and the scanning lines, a path layer disposed on the first dielectric layer and located above the grid electrodes, a second patterning conducting layer comprising source electrodes and drain electrodes which are arranged at two sides of the path layer, a transparency electrode disposed on the infrared light filter layer and electrically connected with one of the source electrode and the drain electrode, a second dielectric layer which covers the second patterning conducting layer and part of the transparency electrode, an infrared light sensing layer disposed on the transparency electrode, and a patterning shading conducting layer comprising a sensing electrode disposed on the infrared light sensing layer and a shading electrode disposed on the second dielectric layer and aligned to the path layer. The optical profile type touch panel has an excellent penetration rate and response rate,

Owner:AU OPTRONICS CORP

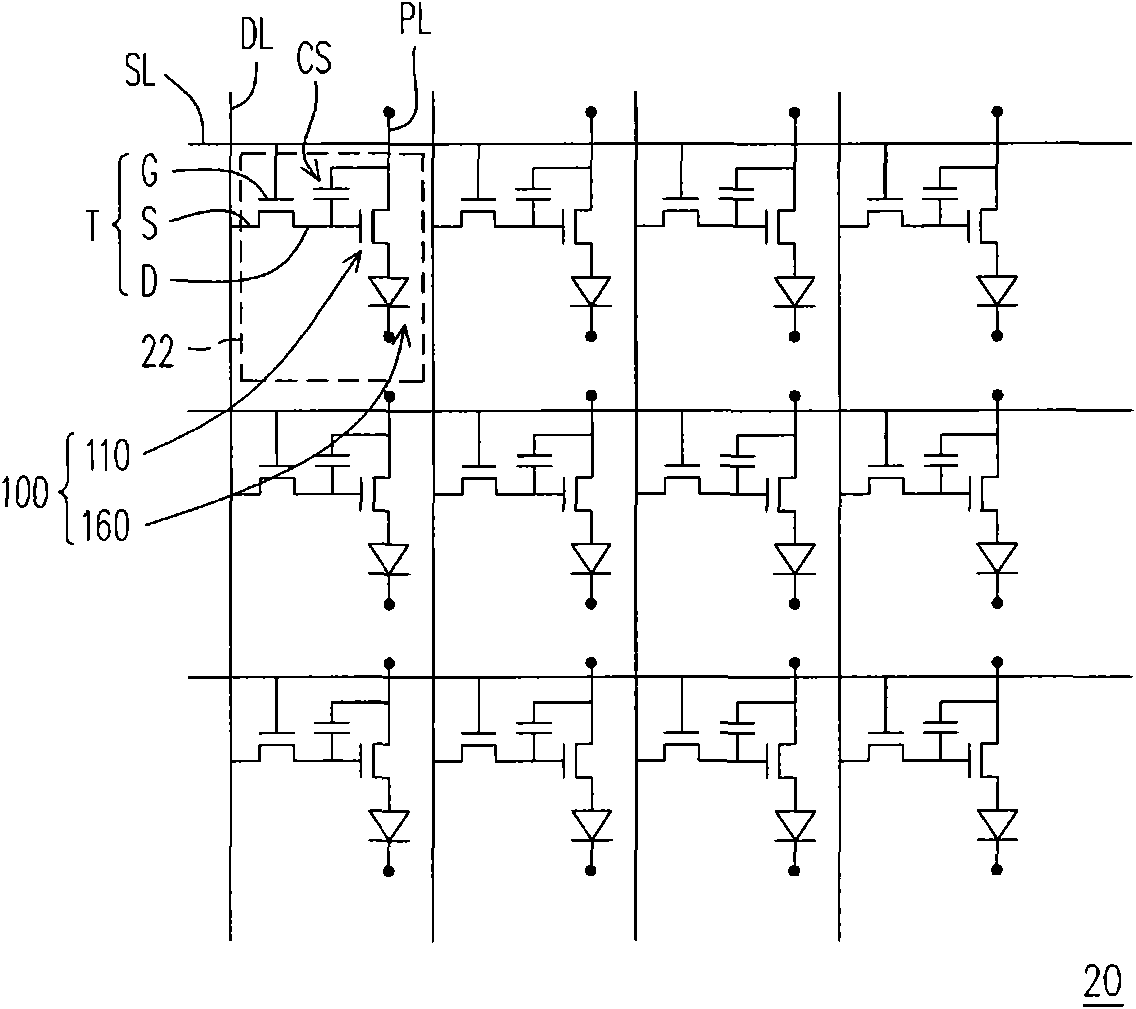

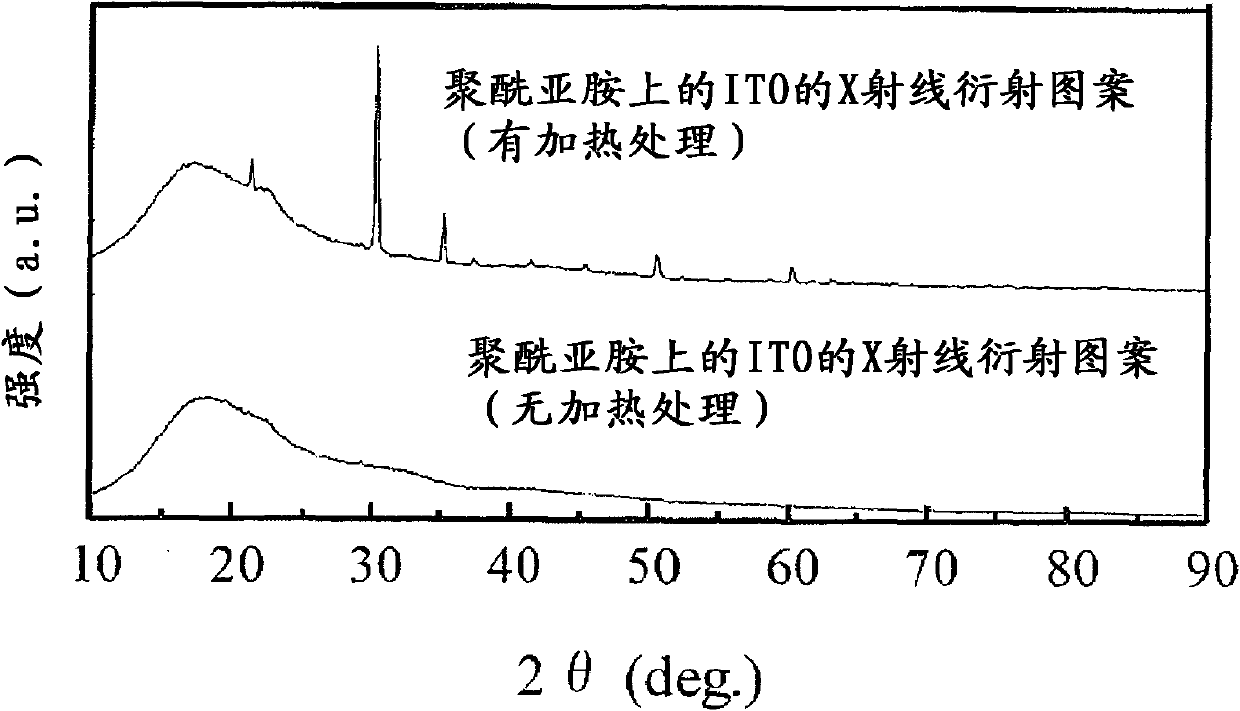

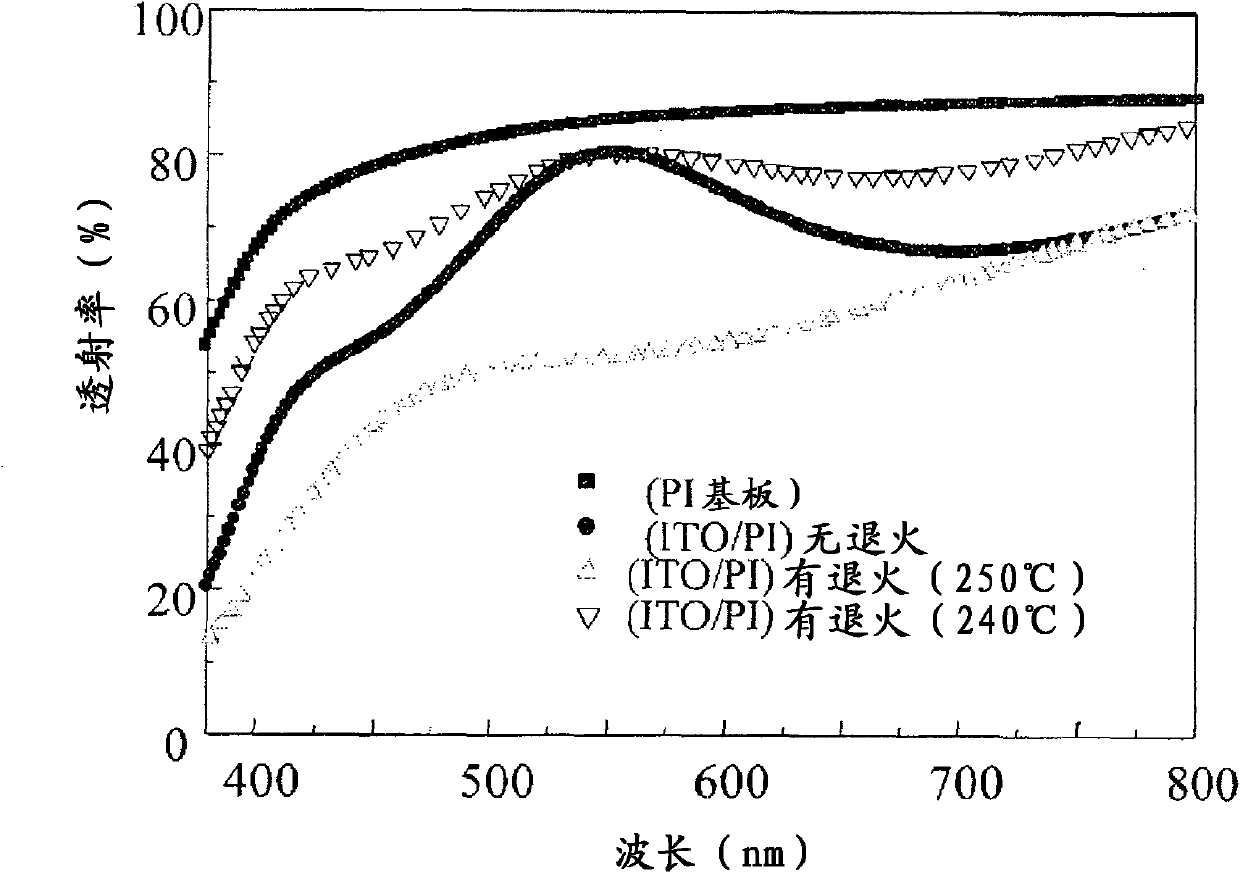

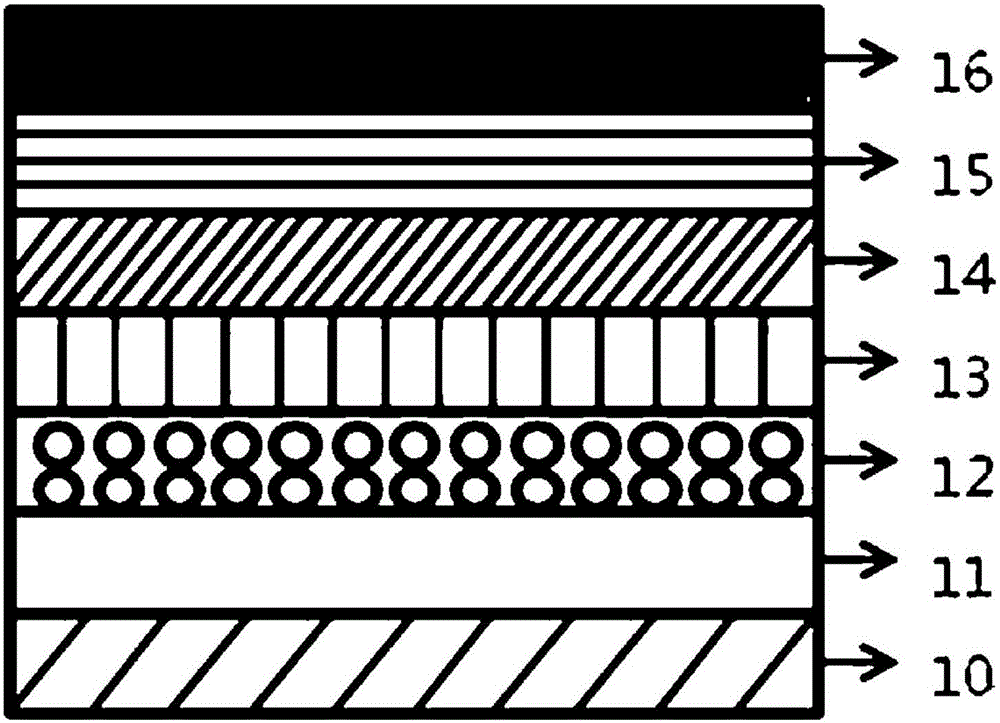

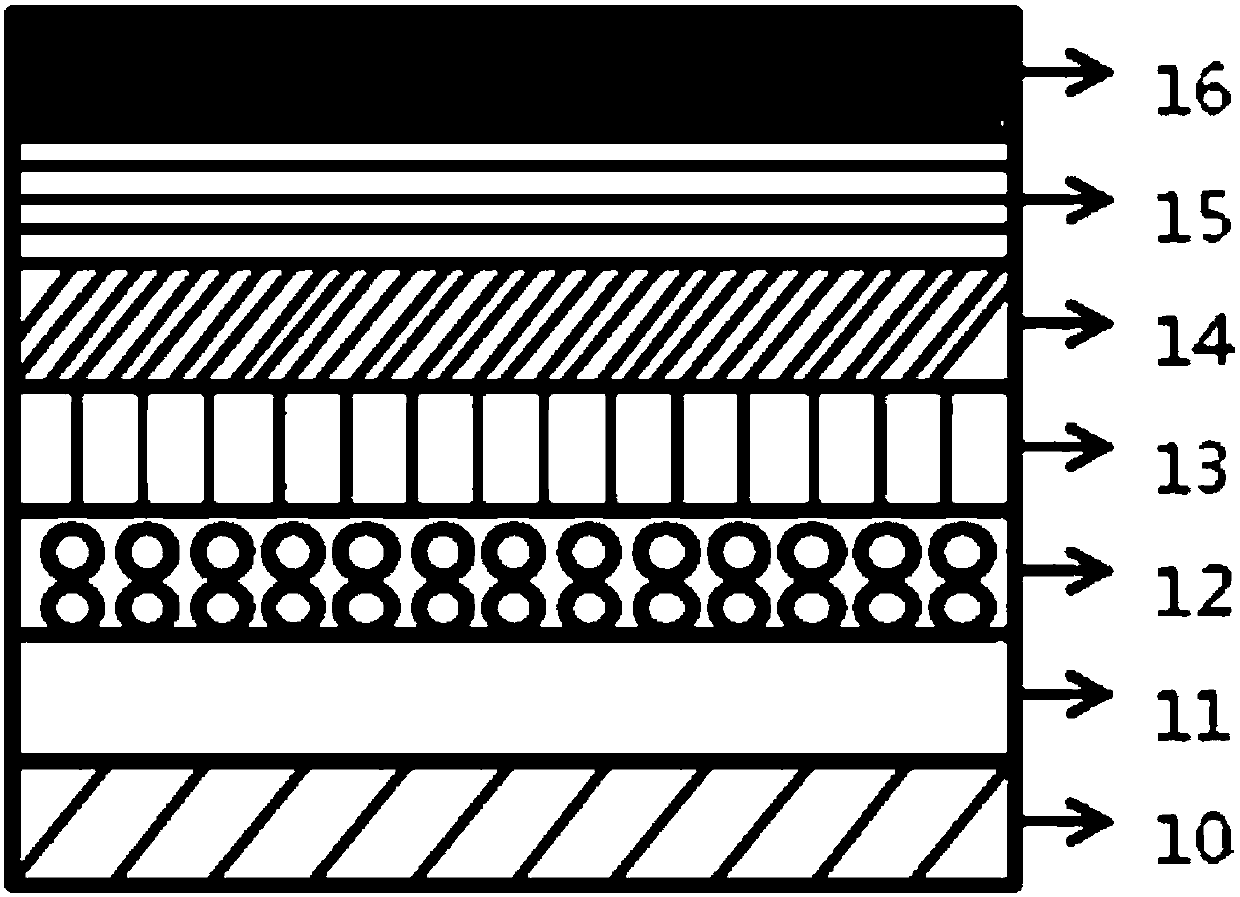

Image display device and organic electroluminescence element

InactiveCN102273318AFlexibleWith luminous brightnessFinal product manufactureElectroluminescent light sourcesCarboxyl radicalDisplay device

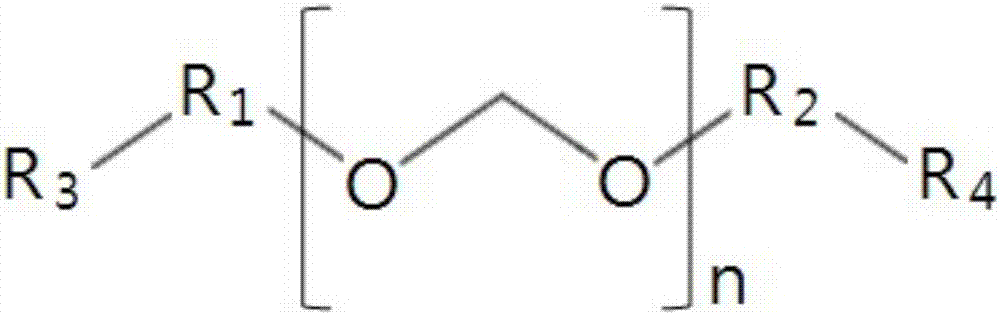

Disclosed are an image display device and an organic EL element, each of which involves at least a polyimide film substrate and an ITO electrode formed on the substrate, wherein the ITO electrode is a polycrystalline ITO electrode and the polyimide film contains a repeating unit represented by formula [1] in an amount of at least 10 mol%. Each of the image display device and the organic EL element involves a flexible polyimide film and has excellent element properties including light emission luminance. (In the formula, R1 and R2 independently represent a hydrogen atom, a halogen atom, or an alkyl group having 1 to 5 carbon atoms; R3, R4 and R5 independently represent a hydrogen atom, a halogen atom, an alkyl group having 1 to 10 carbon atoms, an alkenyl group having 2 to 5 carbon atoms, an alkoxyl group having 1 to 5 carbon atoms, a cycloalkyl group having 3 to 7 carbon atoms, a nitril group, or a carboxyl group; and n represents a integer.)

Owner:TOKYO KOGEI UNIV +1

Semiconductor element and manufacturing method thereof

InactiveCN102751448AGood component propertiesFree from destructionSolid-state devicesSemiconductor/solid-state device manufacturingEtchingEngineering

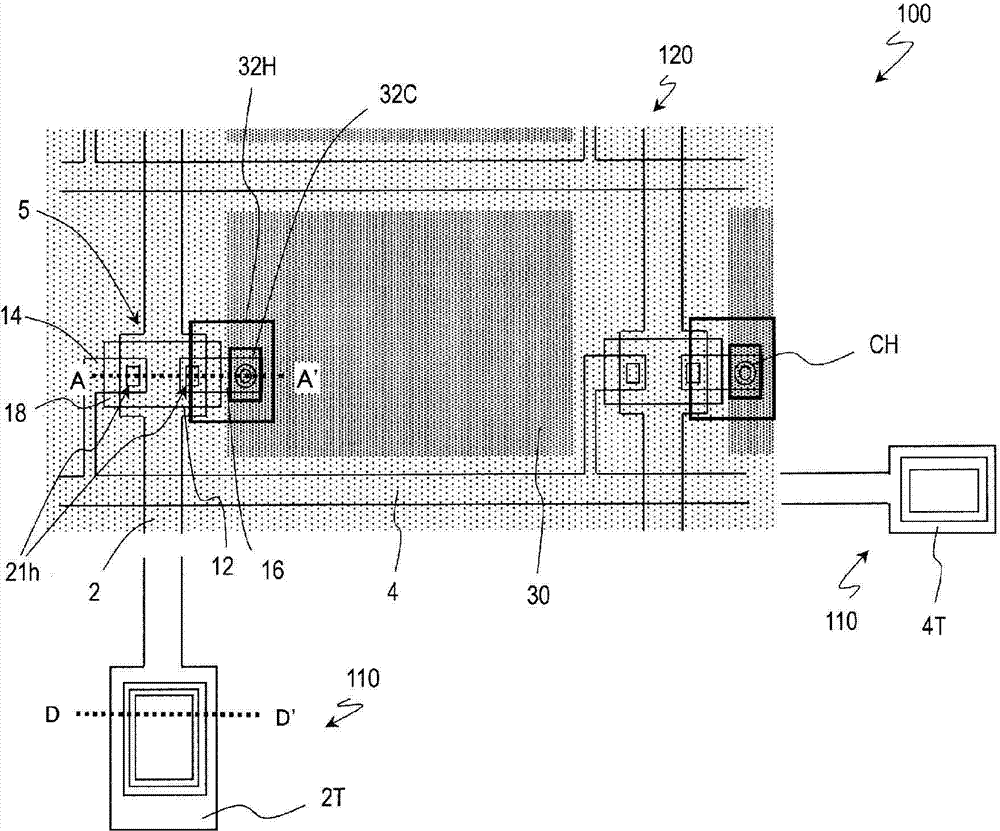

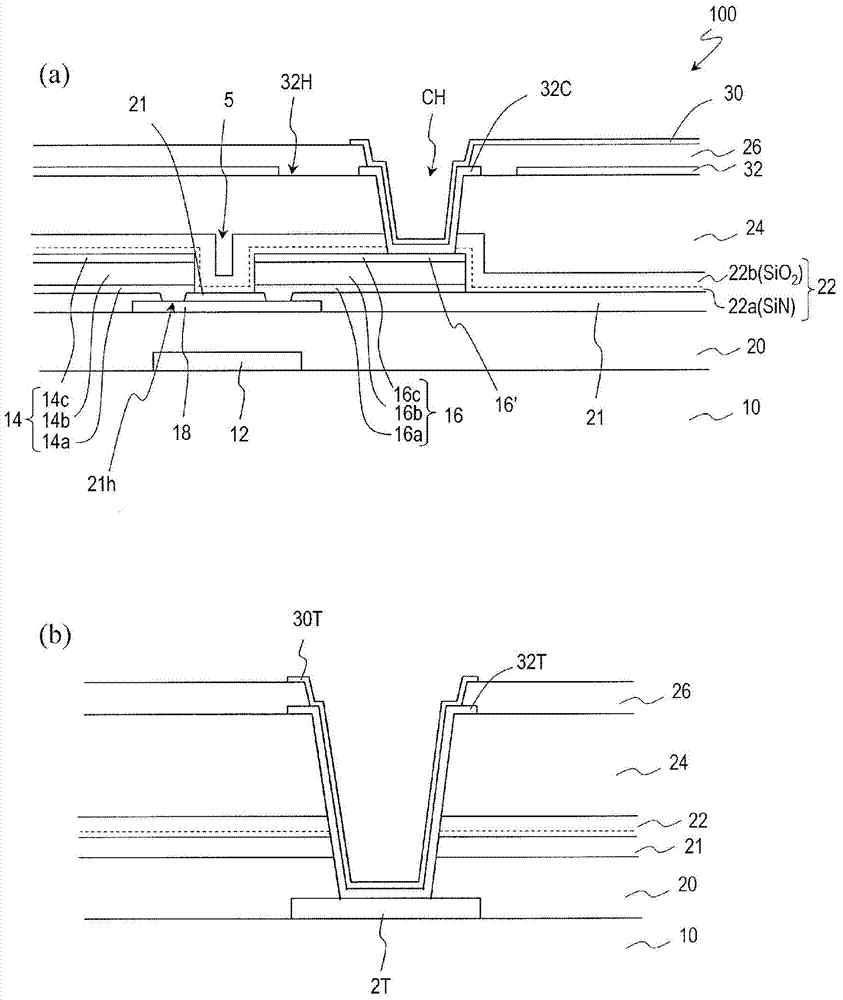

The present invention discloses a semiconductor element and a manufacturing method thereof. The manufacturing method comprises the steps of: forming a grid electrode on a substrate; forming a source electrode and a drain electrode above or below the grid electrode; forming a first insulating layer for covering the source electrode and the drain electrode; forming a semiconductor layer between the source electrode and the drain electrode; patterning the first insulating layer for at least covering the drain electrode; forming a second insulating layer on the patterned first insulating layer; etching the second insulating layer to form a second opening which exposes the patterned first insulating layer and is arranged above the drain electrode, wherein, an etching selection ratio, i.e., the second insulating layer / the patterned first insulating layer, is greater than 1; performing wet etching for the patterned first insulating layer via the second opening, so as to form a first opening which is communicated with the second opening and exposes the drain electrode; and forming a pixel electrode which is electrically connected with the drain electrode via the first opening and the second opening.

Owner:AU OPTRONICS CORP

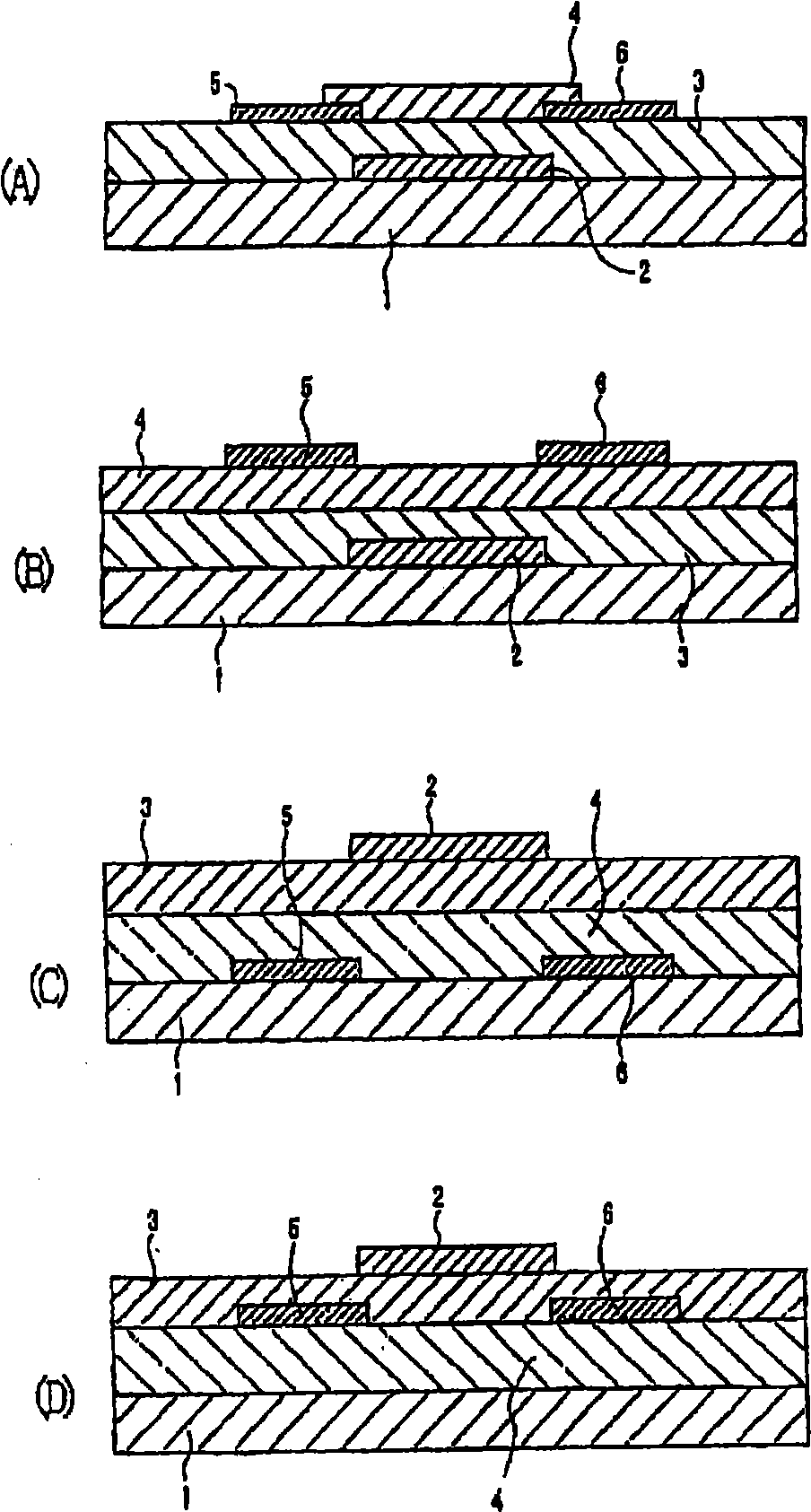

Method of encapsulating organic EL display device having through hole in substrate and/or flat panel

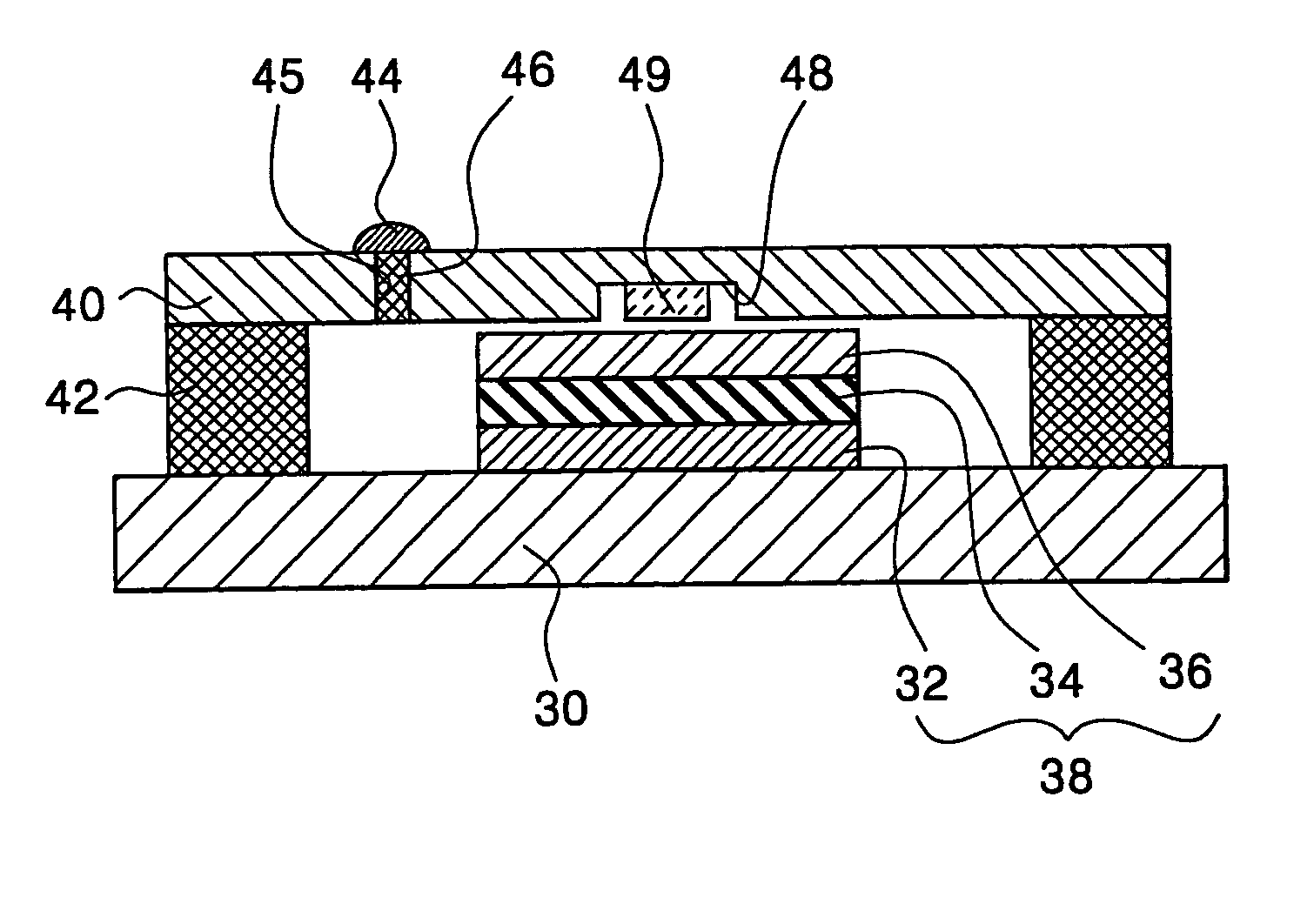

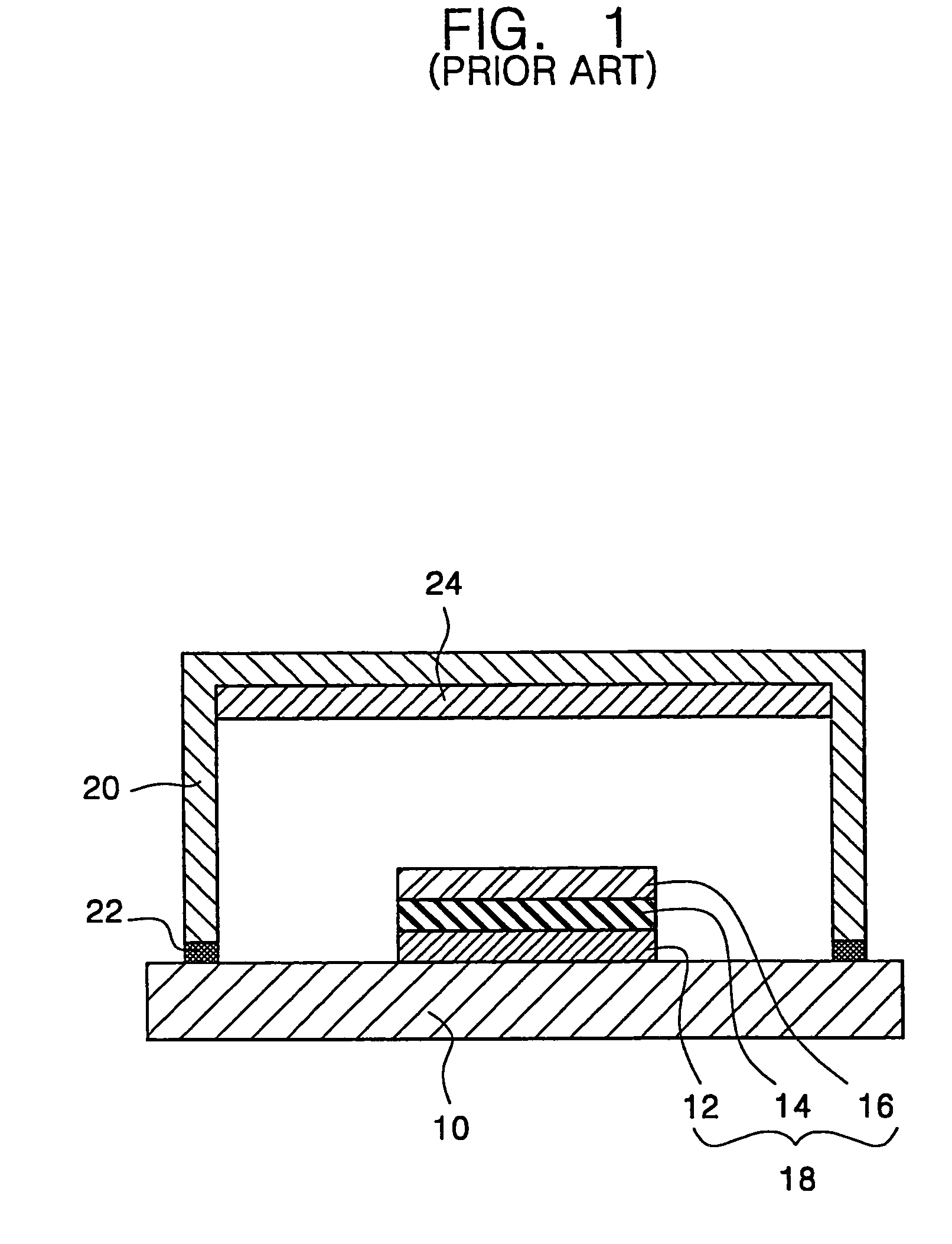

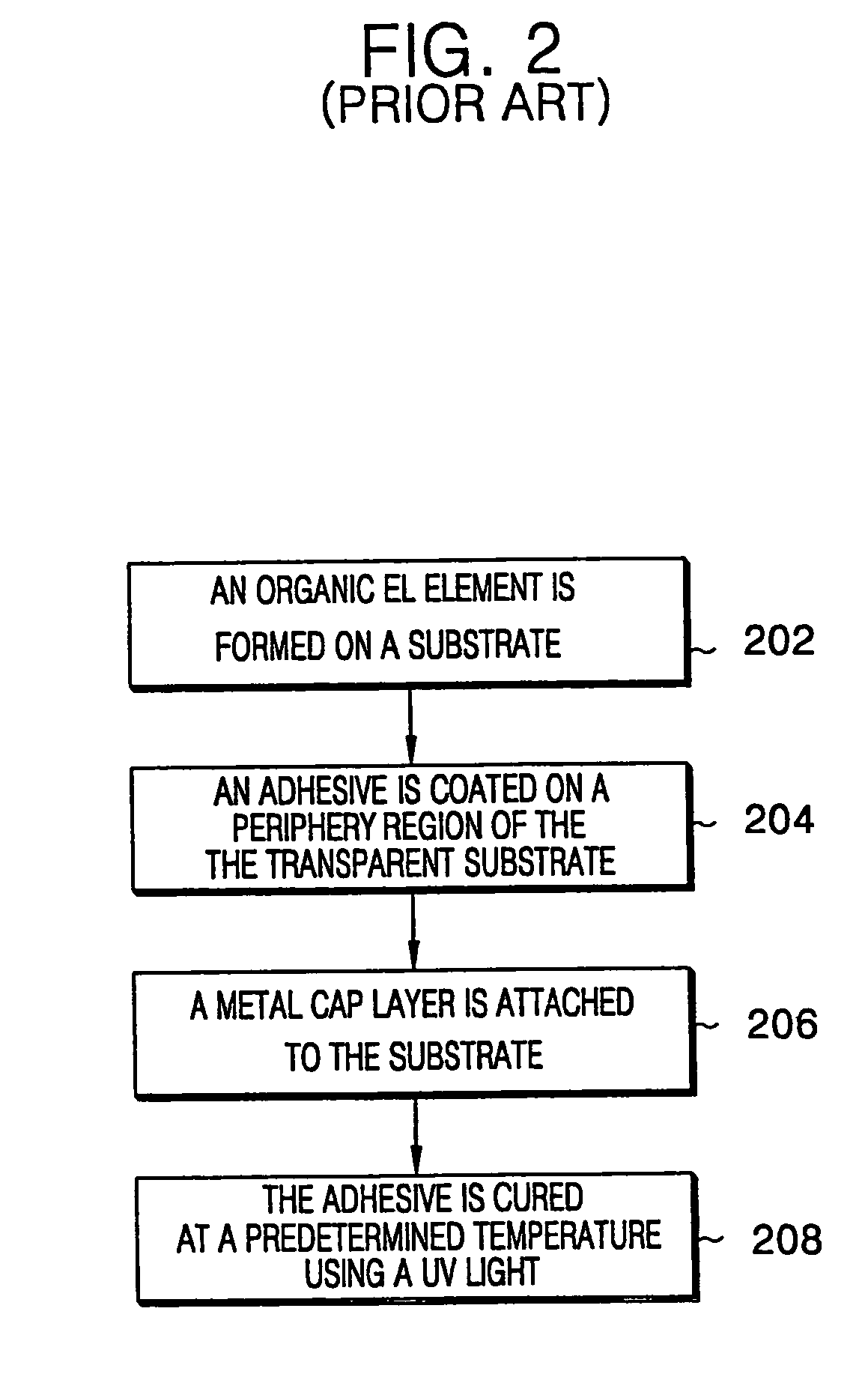

InactiveUS7348725B2Good component propertiesCompact structureDischarge tube luminescnet screensElectroluminescent light sourcesDisplay deviceEngineering

An organic electroluminescent (EL) display device includes an organic EL element formed on a substrate. The organic EL element includes a lower electrode, an organic EL layer and an upper electrode that are sequentially stacked on the substrate. A flat panel is attached to the substrate to encapsulate the organic EL element. At least one through hole is formed in the organic EL display device so as to allow gas inside the organic EL display device to flow out during an encapsulation process. A cap is provided to shut the one or more through holes.

Owner:SAMSUNG DISPLAY CO LTD

Cylindrical sintered body, cylindrical sputtering target, and method for producing the same

ActiveCN107239006AEfficient removalNon-volatileOrganic chemistryPhotosensitive material processingMetallurgyOxygen supply

It is an object of the present invention to provide a cylindrical sintered body, a cylindrical sputtering target, and a method for producing the same in a cylindrical axis direction of 470 mm or more. A method of manufacturing a cylindrical sputtering target according to an embodiment of the present invention is a method of manufacturing a cylindrical sputtering target having a cylindrical sintered body in which a cylinder having a cylinder length of 600 mm or more The shaped body is disposed on a pedestal provided with an oxygen supply port connected to a pipe for oxygen supply and is provided on a pedestal having a length slightly smaller than an inner circumference of the cylinder provided inside the cylinder of the cylindrical molded body Cylinder axis direction of oxygen at the same time sintering. In another embodiment, it is also possible to arrange the pedestal in the chamber, and the piping for oxygen supply is connected from the outside of the chamber to the oxygen supply port.

Owner:DONGWOO FINE CHEM CO LTD

Thin film transistor and production method thereof

InactiveCN101533775AGood component propertiesTransistorSemiconductor/solid-state device manufacturingEngineeringPolycrystalline silicon

The invention discloses a production method of a thin film transistor, which comprises the following steps of: providing a base plate firstly; forming a sacrificial layer on the base plate; forming a multicrystal silicon pattern layer on the base plate to surround the sacrificial layer; and then forming a gate insulation layer large enough to cover the multicrystal silicon pattern layer at least. Additionally, a gate pattern is formed on the gate insulation layer above the multicrystal silicon pattern layer and a source electrode region, a drain electrode region and an active region are formed on the multicrystal silicon pattern layer and the active region is positioned between the source electrode region and the drain electrode region. Furthermore, a protection layer is formed to cover the gate pattern and partial gate insulation layer. And then a source electrode conducting layer and a drain electrode conducting layer are formed on the protection layer and electrically connected with the source electrode region and the drain electrode region of the multicrystal silicon pattern layer respectively.

Owner:CHUNGHWA PICTURE TUBES LTD

Integrated Transformer

ActiveCN104952834BQuality improvementImprove coupling coefficientSemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsTransformerInductor

The invention discloses an integrated transformer which comprises a first coiling, a second coiling and a plurality of bridging lines, wherein the first coiling is formed by a first metallic layer and has a plurality of disconnected sections, the second coiling is formed by a second metallic layer and has a plurality of disconnected sections, the bridging lines are formed by a third metallic layer. Some of the bridging lines connect the sections of the first coiling, so that the sections of the first coiling form a first inductor. Other bridging lines connect the sections of the second coiling, so that the sections of the second coiling form a second inductor.

Owner:REALTEK SEMICON CORP

Integrated Transformer

ActiveCN105280605BImprove qualityImprove coupling coefficientSemiconductor/solid-state device detailsSolid-state devicesTransformerEngineering

An integrated transformer comprises a first inductor and a second inductor, the first inductor comprises B circles of spiral wirings formed by a first metal layer and A circles of wirings formed by a second metal layer, and the A circles of the wirings formed by the second metal layer is overlapped with the innermost A circles of the wirings of the B circles of the spiral wirings formed by the first metal layer; and the second inductor comprises C circles of wirings formed by at least the second metal layer, the C circles of the wirings, formed by the second metal layer, of the second inductor are substantially overlapped with the partial wirings formed by the first metal layer, A is less than B, and A is less than C.

Owner:REALTEK SEMICON CORP

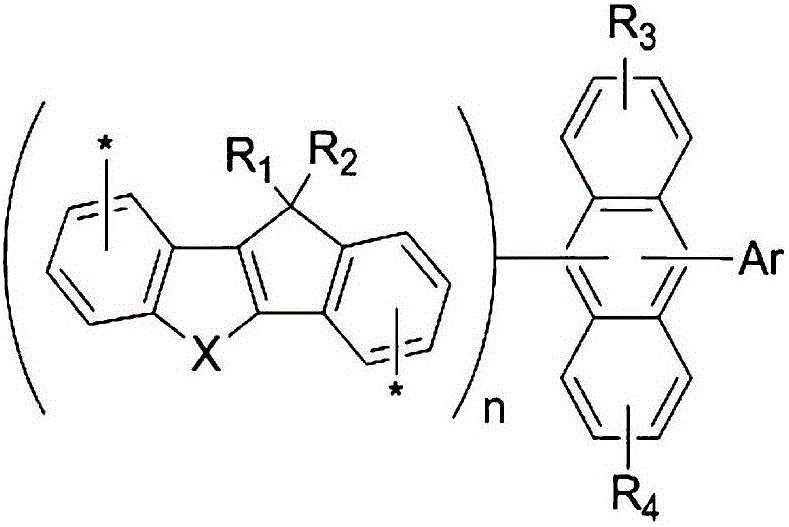

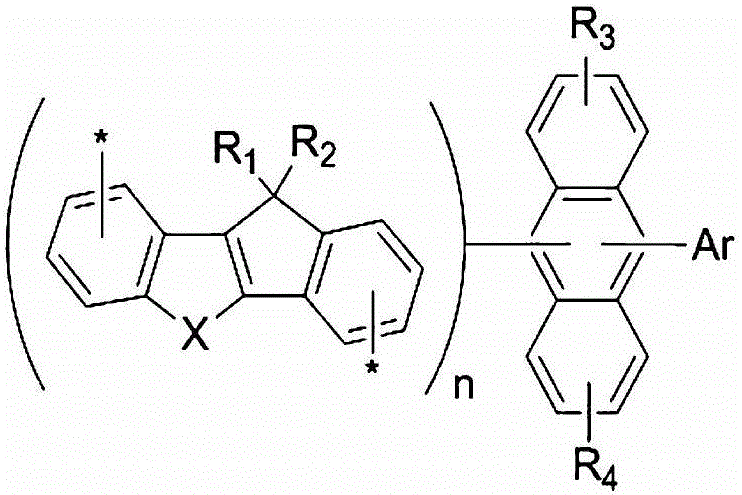

Novel light-emitting compound and organic light-emitting element comprising same

ActiveCN105934497AImprove luminous efficiencyHigh color purityOrganic chemistrySolid-state devicesElectronic transmissionHigh color

An organic light-emitting compound according to the present invention has superb hole and electron transport characteristics, excellent ability to maintain blue light emission, superb light-emitting efficiency, high color purity and efficiency and long lifespan characteristics, and thus can impart superb characteristics to an element when used in an organic light-emitting element.

Owner:DONGJIN SEMICHEM CO LTD

Novel light-emitting compound and organic light-emitting element containing same

ActiveCN105934497BImprove luminous efficiencyHigh color purityOrganic chemistrySolid-state devicesElectron holeHigh color

The organic light-emitting compound of the present invention can exhibit excellent device characteristics when applied to organic light-emitting devices due to its excellent hole and electron transport properties, blue luminescence maintenance and luminous efficiency, high color purity, high efficiency and long life.

Owner:DONGJIN SEMICHEM CO LTD

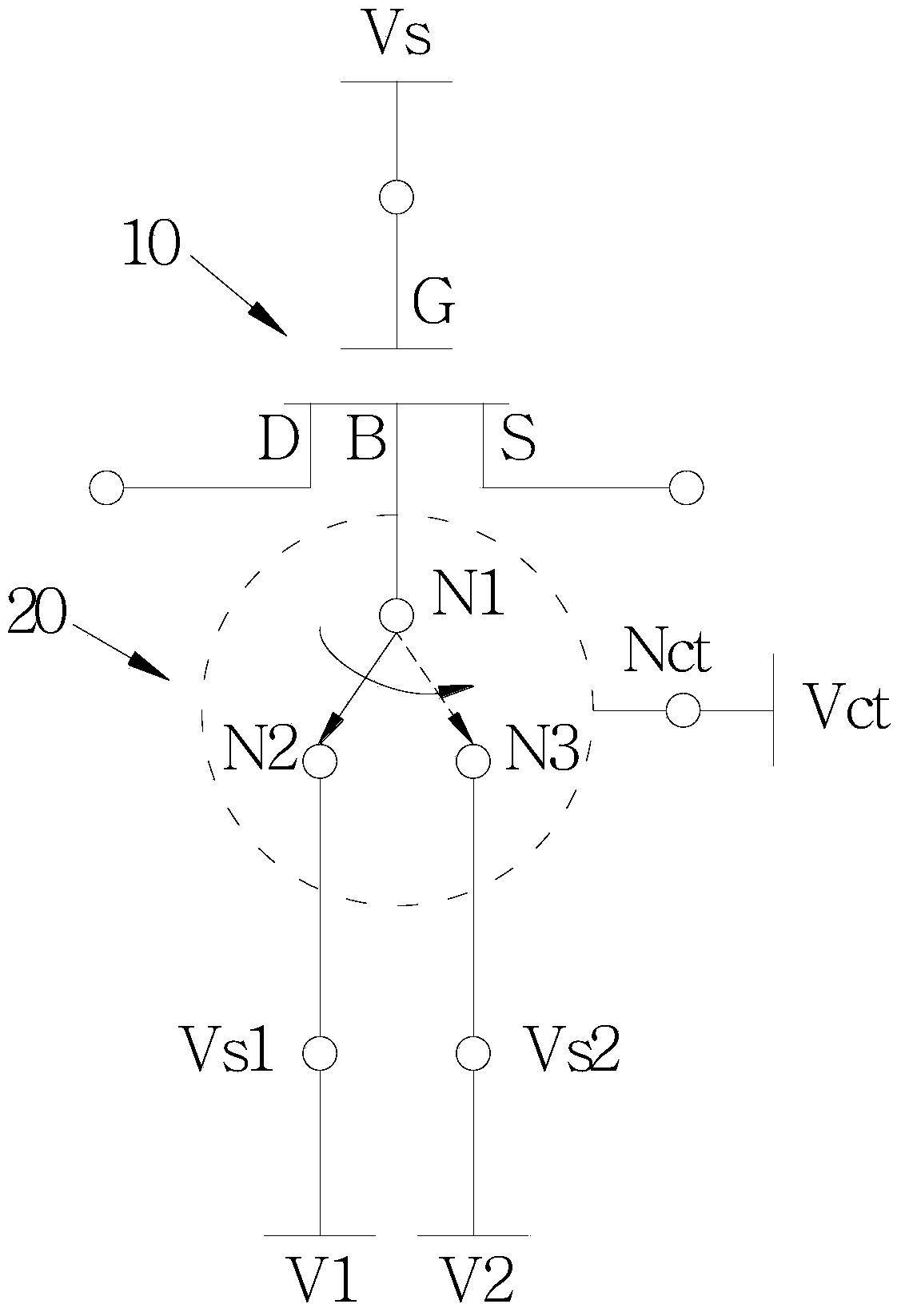

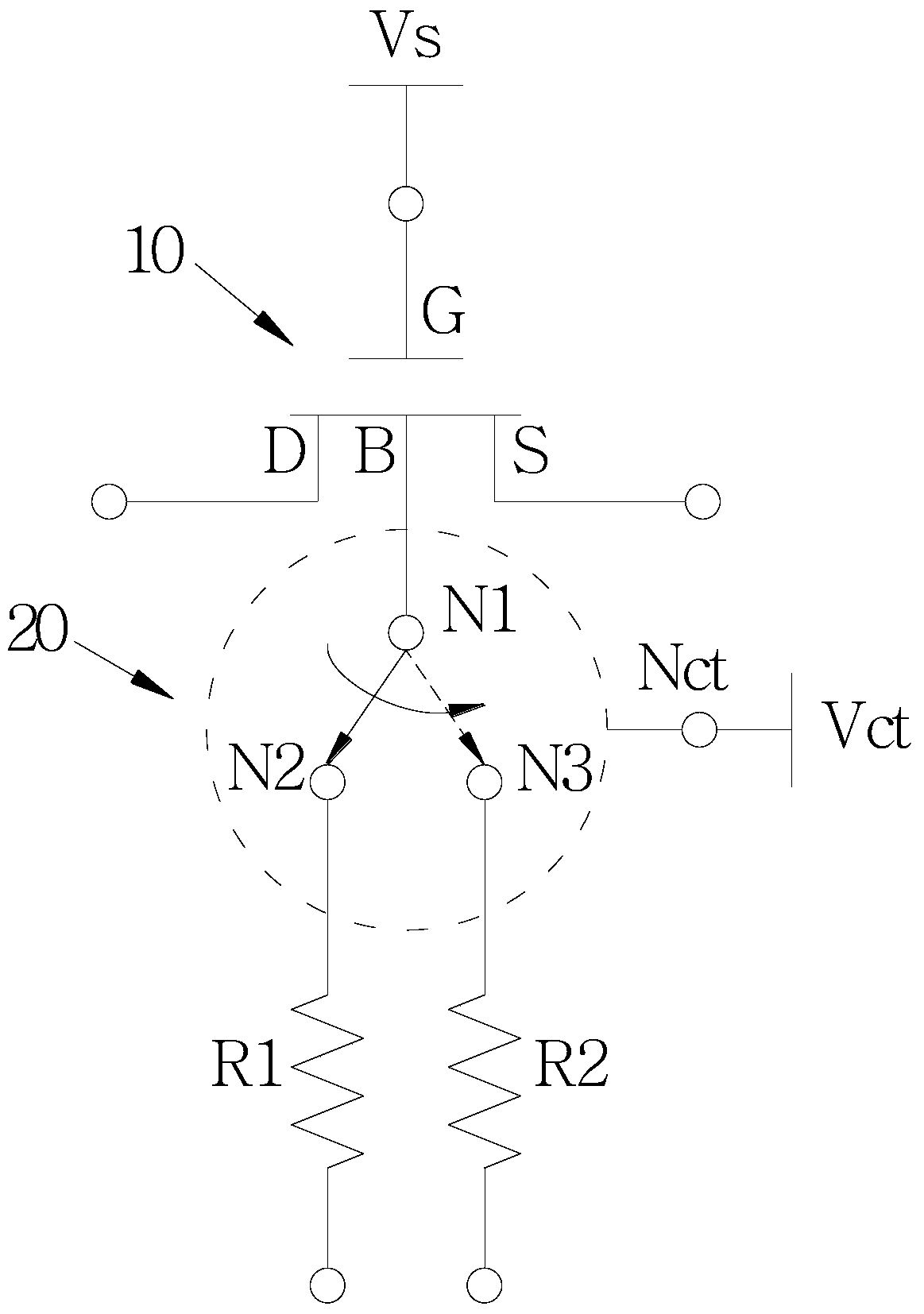

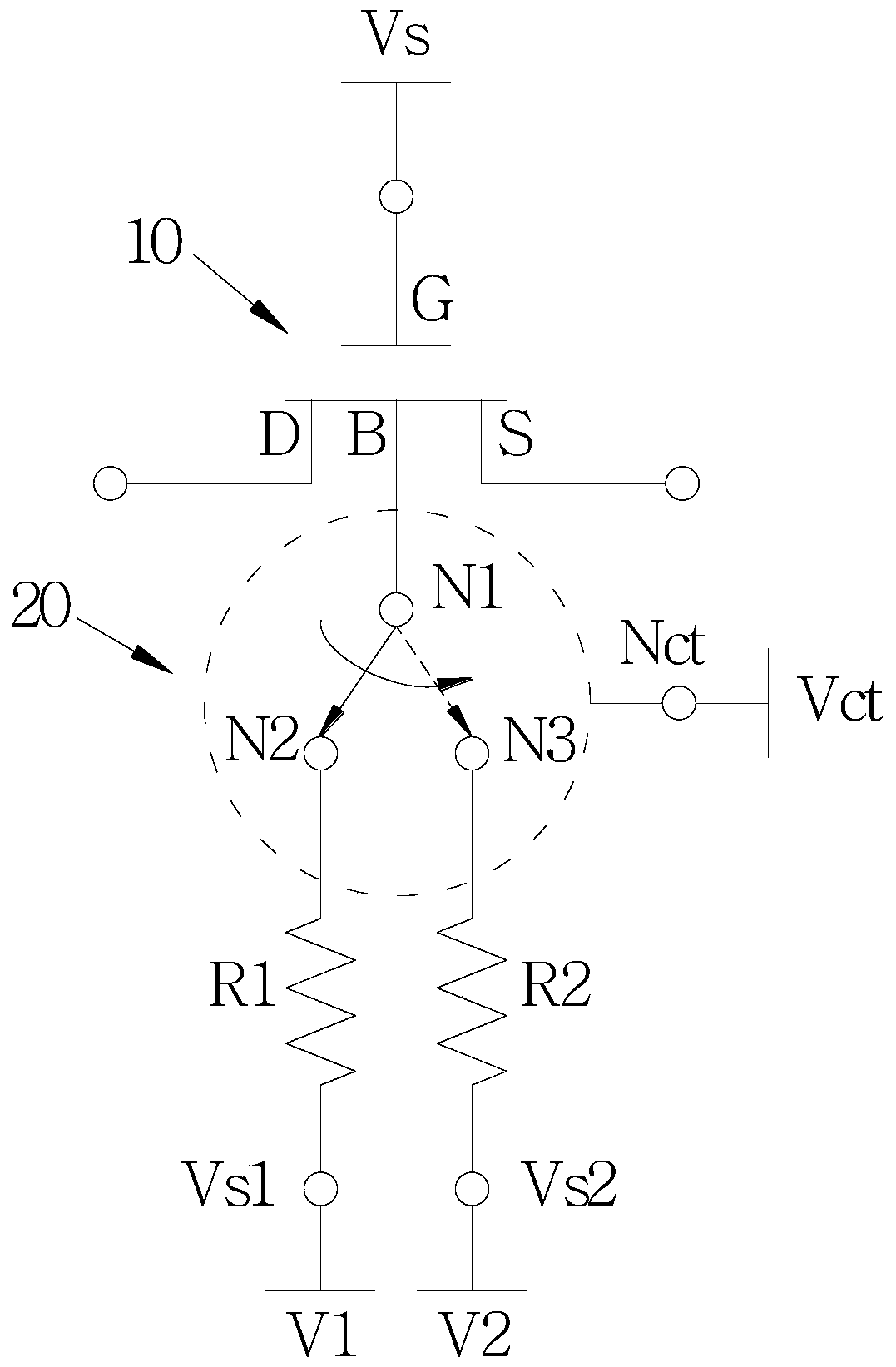

Analog switch circuit

ActiveCN106033961BChange propertiesChange component propertiesElectronic switchingEngineeringVoltage source

Disclosed in the invention is an analog switch circuit for a high-frequency signal. The analog switch circuit comprises a metal-oxide-semiconductor field-effect transistor and a control switch. The metal-oxide-semiconductor field-effect transistor consists of a drain electrode, a source electrode, a gate electrode and a polar electrode. A gate bias voltage is applied to the gate electrode to control conduction or disconnection of the metal-oxide-semiconductor field-effect transistor. The control switch consists of a control terminal, a first terminal, a second terminal and a three terminal; and the first terminal is connected to the polar electrode. A control bias voltage related to the gate bias voltage is applied to the control terminal, so that the first terminal is connected to the second terminal when the metal-oxide-semiconductor field-effect transistor is in a conduction state and the first terminal is connected to the third terminal when the metal-oxide-semiconductor field-effect transistor is turned off. The second terminal is connected to a first voltage source providing a first bias voltage; and the third terminal is connected to a second voltage source providing a second bias voltage different from the first bias voltage.

Owner:REALTEK SEMICON CORP

pixel structure

ActiveCN105762156BSufficient intervalAvoid short circuitSolid-state devicesNon-linear opticsVertical projectionWindow opening

The invention discloses a pixel structure, which includes a first pixel unit, a second pixel unit, a first insulating layer and a common electrode. The first pixel unit is disposed on the substrate and includes a first drain and a first pixel electrode. The second pixel unit is disposed on the substrate and includes a second drain and a second pixel electrode. The first insulating layer covers the first drain and the second drain. The first pixel electrode and the second pixel electrode are disposed on the first insulating layer, and the first insulating layer has a first contact window opening exposing the first drain electrode and a second contact window opening exposing the second drain electrode. The common electrode is arranged on the first insulating layer and is electrically insulated from the first pixel electrode and the second pixel electrode. The common electrode has a common opening. On the vertical projection of the substrate, the opening of the first contact window and the opening of the second contact window both fall within the common opening.

Owner:AU OPTRONICS CORP