Thin-film transistor array substrate and preparation method thereof

A technology of thin film transistors and array substrates, applied in the field of thin film transistor array substrates and its production, can solve the problems of increased process time, unfavorable increase in production capacity, and increased total number of times, and achieve high carrier mobility and good component characteristics. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

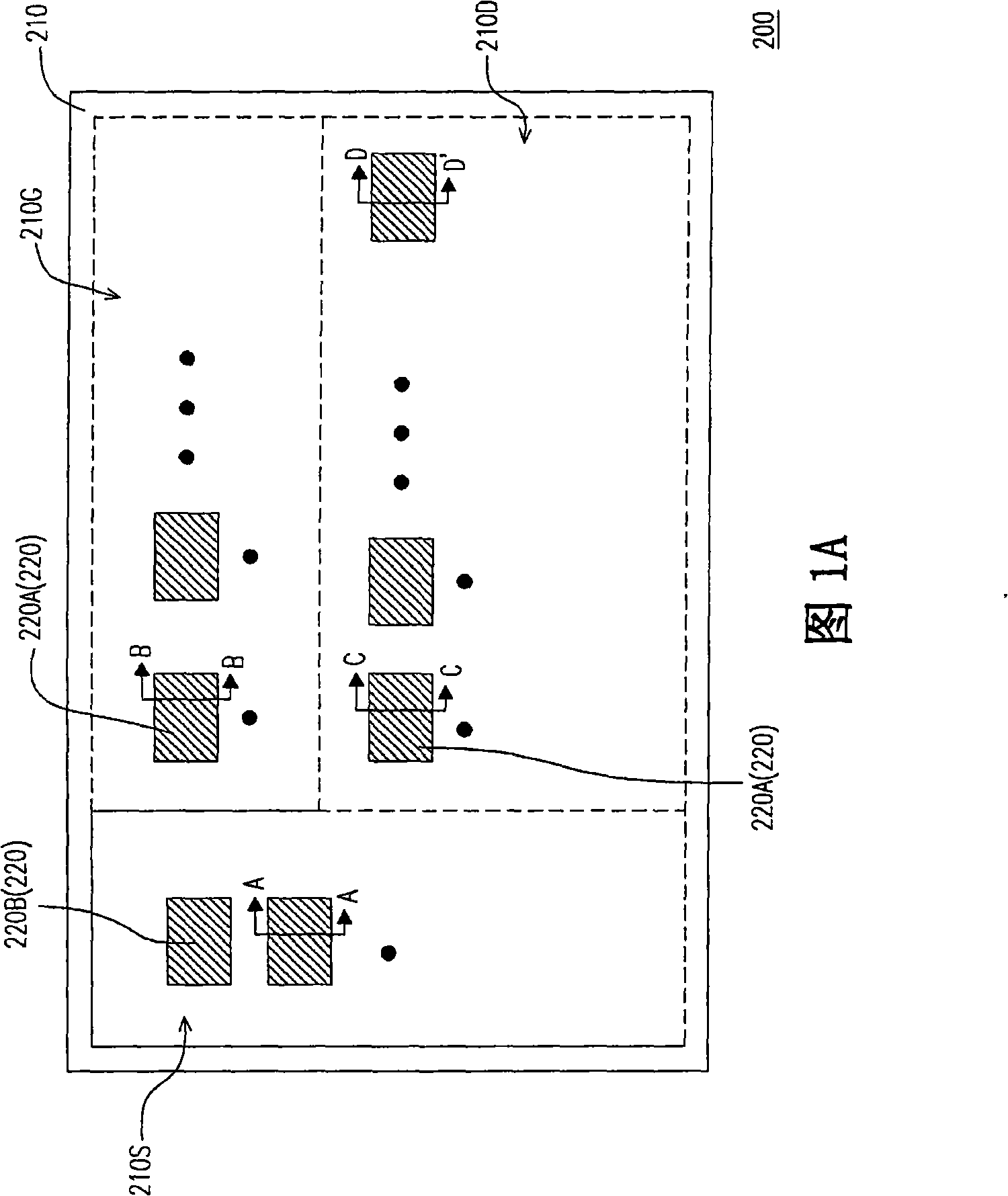

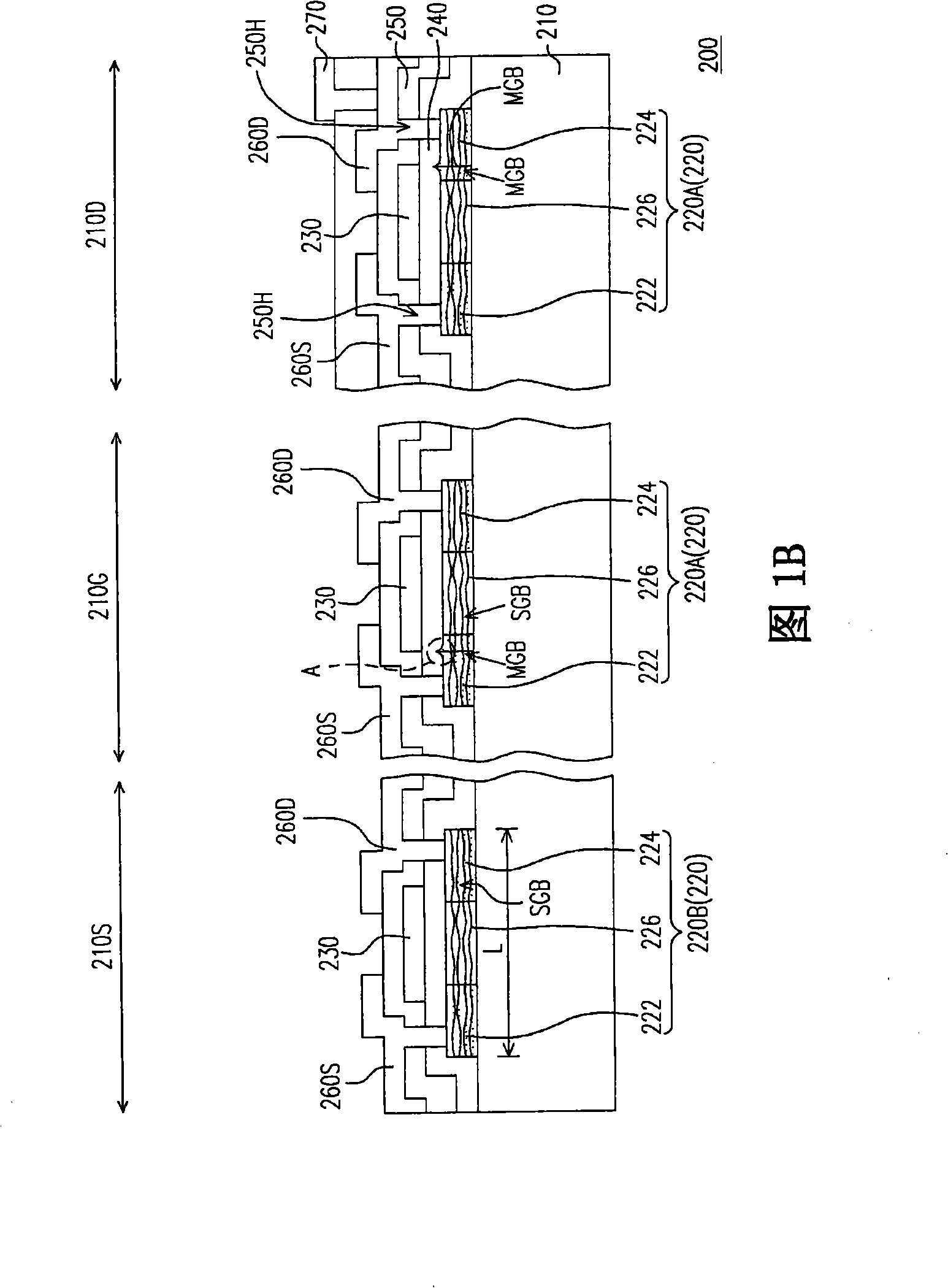

[0060] FIG. 1A is a schematic diagram of a thin film transistor array substrate according to an embodiment of the present invention, and FIG. 1B is a schematic cross-sectional view along line AA, BB and CC in FIG. 1A . Please refer to FIG. 1A and FIG. 1B at the same time. The thin film transistor array substrate 200 includes a substrate 210, a plurality of polysilicon islands 220 disposed on the substrate 210, and a plurality of gates 230. The substrate 210 is mainly divided into a display area 210D, a gate The driving region 210G and the source driving region 210S, and the polysilicon island 220 includes a plurality of first polysilicon islands 220A and a plurality of second polysilicon islands 220B, and the first polysilicon islands 220A are arranged in the display region 210D and the gate in the driving region 210G, and the second polysilicon island 220B is disposed in the source driving region 210S.

[0061] Please continue to refer to FIG. 1B, each polysilicon island 220A...

no. 2 example

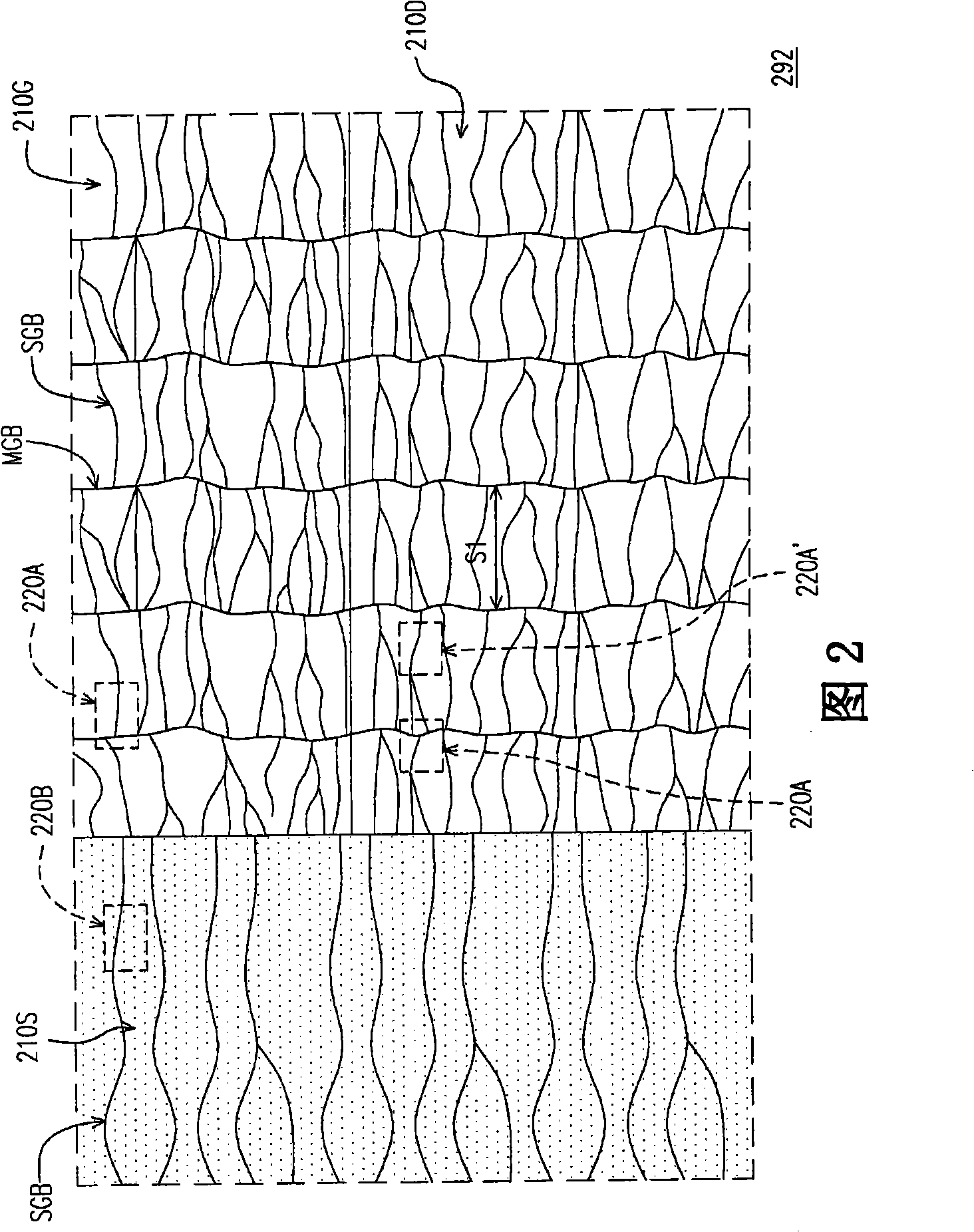

[0081] FIG. 5A is a schematic cross-sectional view of the thin film transistor array substrate according to the second embodiment of the present invention along the lines AA, BB, and CC in FIG. 1A . Please refer to FIG. 5A , for the sake of simplification, the above-mentioned components similar to those mentioned above will not be described again. Compared with the previous embodiments, the second polysilicon island 320B of the thin film transistor array substrate 300 of this embodiment has a main grain boundary MGB and a secondary grain boundary SGB, and the main grain boundary MGB of the second polysilicon island 320B is only located In the source region 222 and / or the drain region 224 , in other words, there is no main grain boundary MGB in the channel region 226 of the second polysilicon island 320B. The formation positions of the main grain boundary MGB and the secondary grain boundary SGB of the second polysilicon island 320B can be controlled, for example, by adjusting ...

no. 3 example

[0085] FIG. 6A is a schematic cross-sectional view of the thin film transistor array substrate according to the third embodiment of the present invention along the lines AA, BB, and CC in FIG. 1A . Please refer to FIG. 6A , for the sake of simplification, the above-mentioned components similar to those described above are not described again. Compared with the second embodiment, the main grain boundary MGB of the second polysilicon island 420B of the thin film transistor array substrate 400 of this embodiment is only located in the source region 222 and / or the drain region 224, in other words, the second most There is no main grain boundary MGB in the channel region 226 of the silicon island 420B. Moreover, in this embodiment, the grain size in the second polysilicon island 420B of the thin film transistor array substrate 400 is substantially smaller than the grain size in the first polysilicon film.

[0086]FIG. 6B is a diagram showing the grain arrangement state of the poly...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More