Thin film transistor and manufacturing method thereof

A technology of thin-film transistors and manufacturing methods, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as the influence of component characteristics, and achieve the effect of optimal component characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

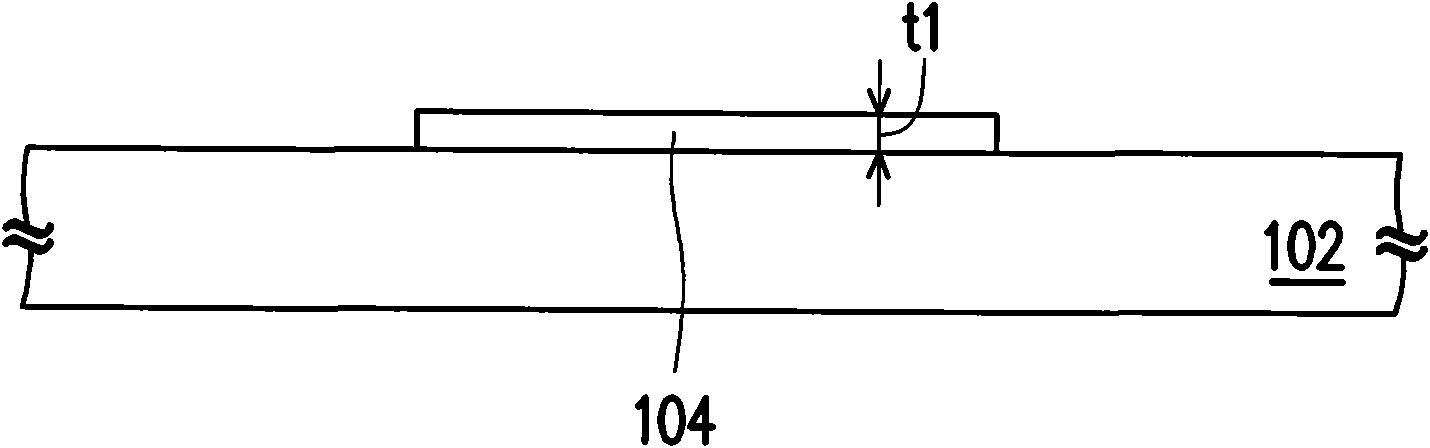

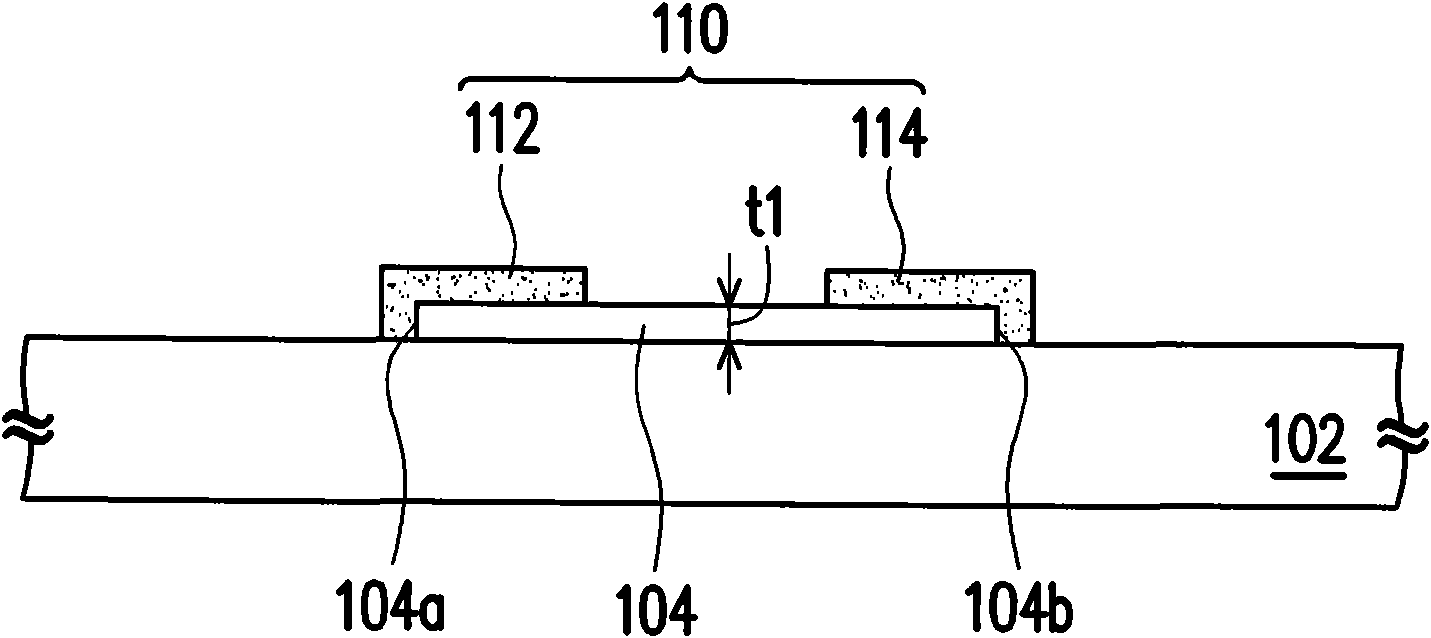

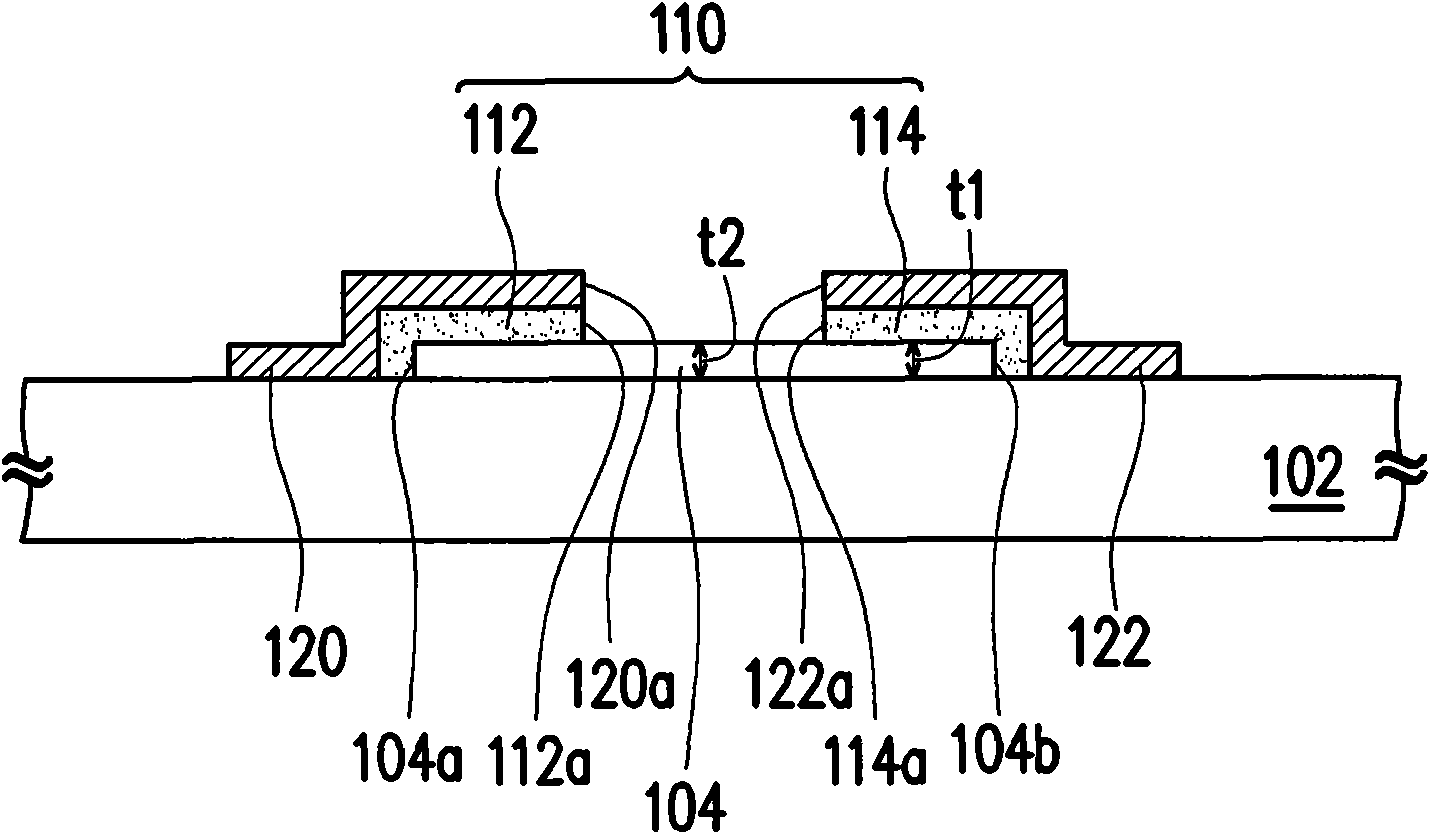

[0049] Figure 1A to Figure 1D It is a schematic cross-sectional flow diagram of a manufacturing method of a thin film transistor according to the first embodiment of the present invention. Please refer to Figure 1A , firstly, a semiconductor layer 104 is formed on a substrate 102, and the semiconductor layer 104 has a first thickness t1. In this embodiment, the substrate 102 may be a glass substrate, a quartz substrate or other material substrates, which is not limited in the present invention. The semiconductor layer 104 is, for example, a polysilicon layer, and its formation method is, for example, a deposition method or a crystallization method. In this embodiment, for example, an amorphous silicon layer (not shown) is formed on the substrate 102 first, and then the amorphous silicon is crystallized by solid phase crystallization (SPC), excimer laser (ELA) layer into a polysilicon layer. Wherein, the first thickness t1 is, for example, between 200 angstroms to 800 angs...

no. 2 example

[0058] Figure 2A to Figure 2D It is a schematic cross-sectional flow diagram of a manufacturing method of a thin film transistor according to the second embodiment of the present invention. Please refer to Figure 2A , firstly, a semiconductor layer 104 is formed on a substrate 102, and the semiconductor layer 104 has a first thickness t1. In this embodiment, the substrate 102 may be a glass substrate, a quartz substrate or other material substrates. The semiconductor layer 104 is, for example, a polysilicon layer, and its formation method is, for example, a deposition method or a crystallization method. In this embodiment, for example, an amorphous silicon layer (not shown) is formed on the substrate 102 first, and then the amorphous silicon is crystallized by solid phase crystallization (SPC), excimer laser (ELA) layer into a polysilicon layer. Wherein, the first thickness t1 is, for example, between 300 angstroms and 2000 angstroms.

[0059] Please refer to Figure 2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More