Semiconductor device and method for producing same

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve the problem of not easily improving the pixel aperture ratio, and achieve the effect of high yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

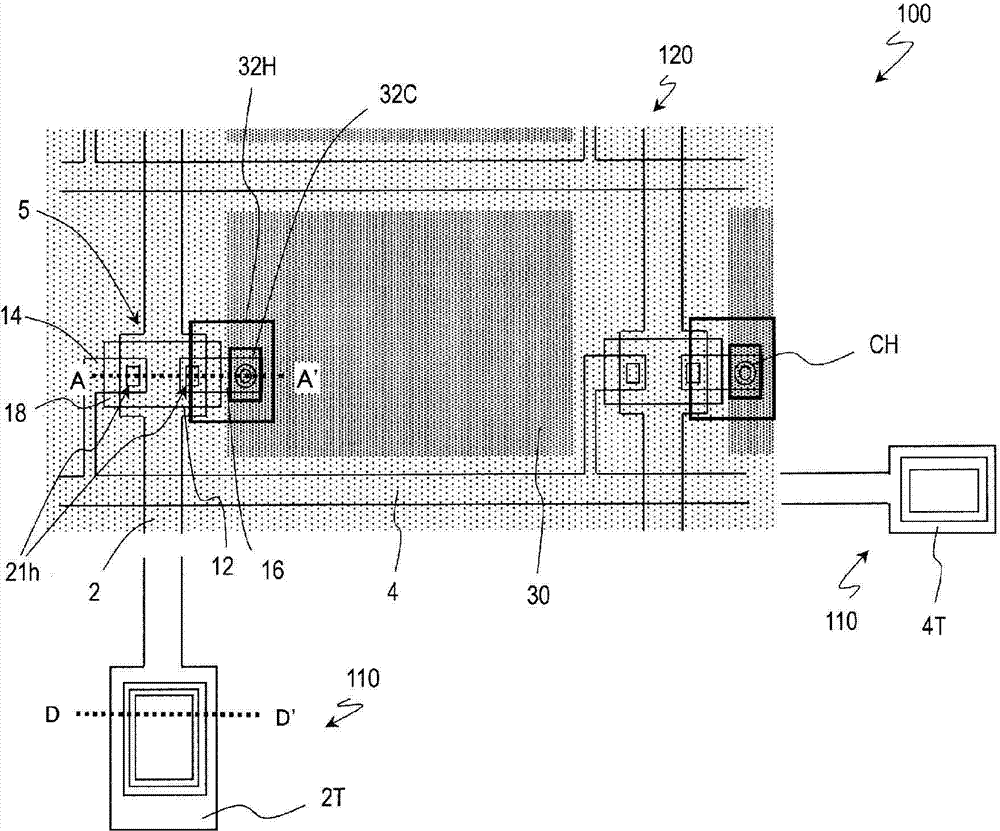

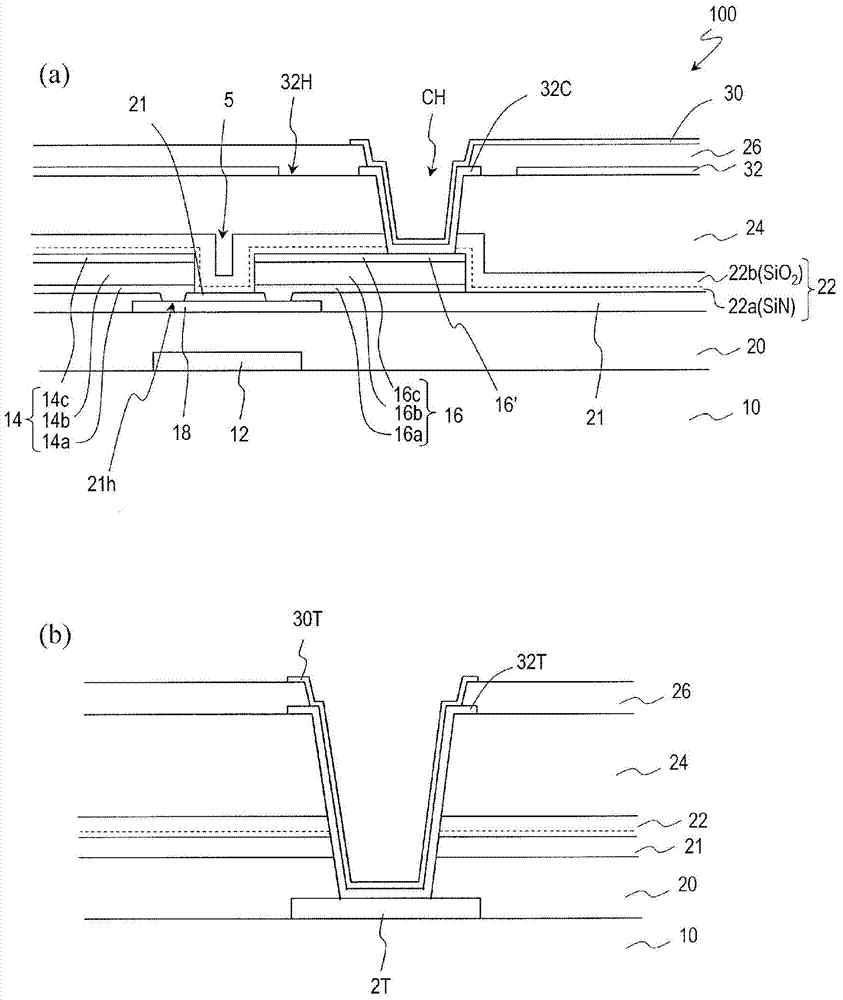

[0055] figure 2 and image 3 (a) and (b) represent the semiconductor device 100 of the first embodiment. Here, the semiconductor device 100 is a TFT substrate (active matrix substrate) 100 used in a liquid crystal display device. figure 2 An example of the planar structure of the TFT substrate 100 is schematically shown, image 3 (a) and (b) represent respectively along figure 2 The section of the line A-A' and along the figure 2 The cross-section of the D-D' line.

[0056] Such as figure 2 As shown, the TFT substrate 100 has: a display region (active region) 120 contributing to display; and a peripheral region (frame region) 110 located outside the display region 120 .

[0057] A plurality of gate wirings 2 and a plurality of source wirings 4 are provided in the display region 120 , and each region surrounded by these wirings becomes a "pixel". A plurality of pixels are arranged in a matrix, and in each pixel, a thin film transistor (TFT) 5 as an active element is...

Embodiment approach 2

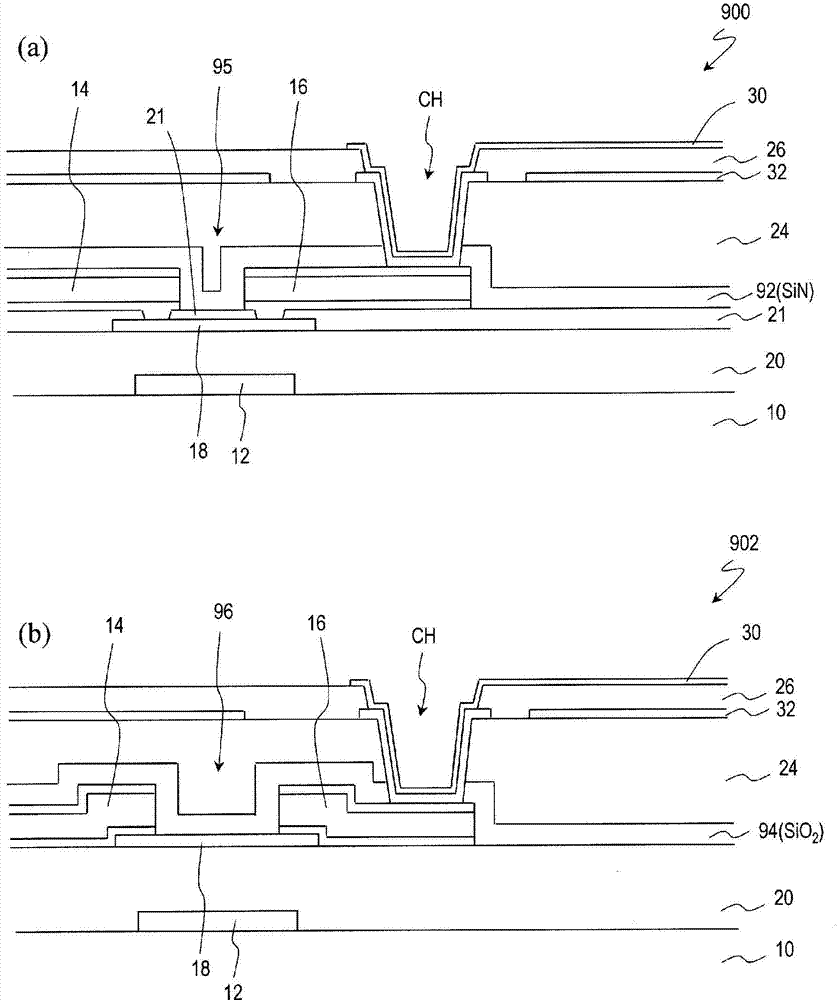

[0108] Figure 7 and Figure 8 (a) and (b) show the TFT substrate 200 of the second embodiment. The TFT substrate 200 of this embodiment differs from the TFT substrate 100 of Embodiment 1 in that the etching stopper layer 24 is not formed on the oxide semiconductor layer 18 . That is, the TFT substrate 200 of the present embodiment includes a channel-etched TFT 6 . In addition, the same reference numerals are assigned to the same components as those in Embodiment 1, and description thereof will be omitted.

[0109] Such as Figure 8 As shown in (a) and (b), in the TFT substrate 200, the passivation layer 23 provided to cover the TFT 6 is provided in contact with the source electrode 14 and the drain electrode 16, and is provided in contact with the oxide semiconductor layer 18. The channel region is also in contact.

[0110] In the present embodiment, the passivation layer 23 includes the lower insulating layer 23 a and the upper insulating layer 23 b provided on the lowe...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More