Thin film transistor and production method thereof

A technology of thin film transistors and manufacturing methods, applied in the direction of transistors, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as limitations, inability to shrink arbitrarily, and inability to effectively improve the control ability of nanoscale channels 118, etc., to achieve good Effect of component properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

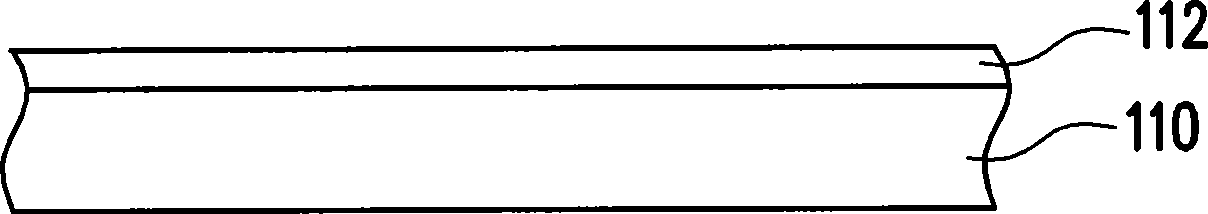

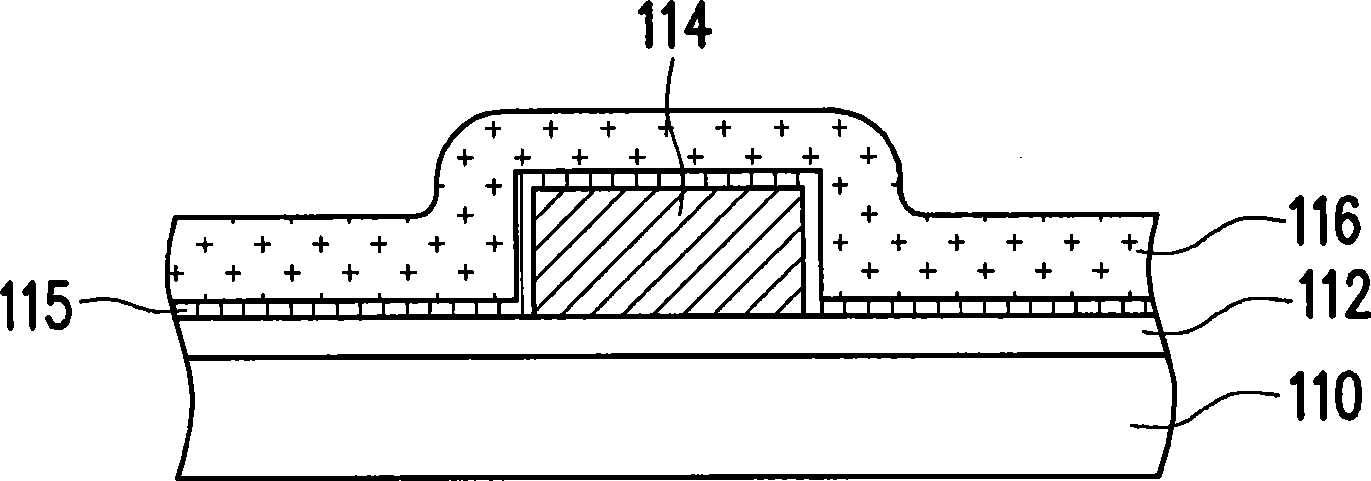

[0052] Figure 2A-2H is a top view of the flow of the manufacturing method of the thin film transistor according to the first embodiment of the present invention, and Figures 3A-3H It is a schematic cross-sectional flow diagram of the manufacturing method of the thin film transistor according to the first embodiment of the present invention. Please refer to Figure 2A and Figure 3A , firstly, a substrate 210 is provided. Generally speaking, a buffer layer 212 can be selectively formed on the substrate 210 to facilitate the fabrication of subsequent film layers. The material of the buffer layer 212 may include silicon oxide, silicon nitride or silicon oxynitride.

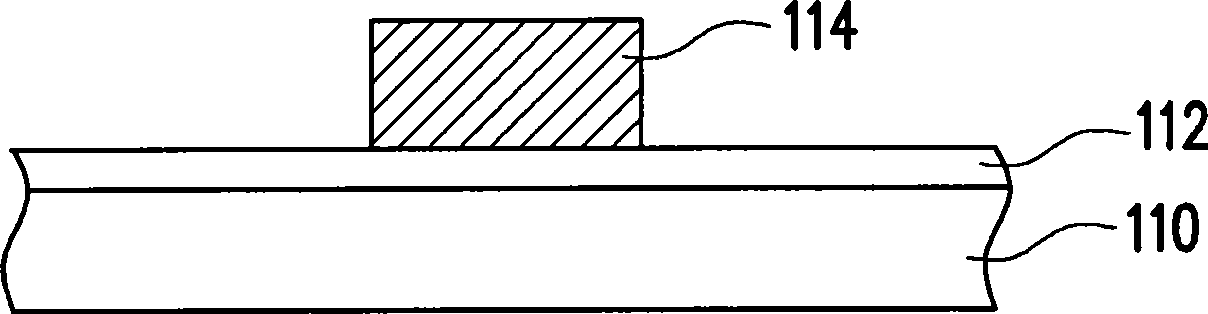

[0053] Then please refer to Figure 2B and Figure 3B , forming a sacrificial layer 220 on the substrate 210 . In detail, the sacrificial layer 220 is formed by, for example, depositing a material layer (not shown) on the buffer layer 212 in an all-round way. The material layer can be made of silicon oxide,...

no. 2 example

[0063] The second embodiment is similar to the first embodiment, and the main difference between the two is that the sacrificial layer is not removed in this embodiment. The initial manufacturing process of the thin film transistor in the second embodiment and Figure 2A ~ Figure 2C as well as Figure 3A ~ Figure 3C The steps shown are the same and will not be repeated here.

[0064] Then please refer to Figure 4A and Figure 5A , forming a gate insulating layer 240 to cover the polysilicon pattern layer 230 and the sacrificial layer 220 . The gate insulating layer 240 can be made of silicon nitride (SiN) or silicon oxide (SiO) formed by using tetraethoxysilane (TEOS) as a reactive gas source.

[0065] Then please refer to Figure 4B and Figure 5B , forming a gate pattern 250 on the gate insulating layer 240 above the polysilicon pattern layer 230 . The gate pattern 250 is, for example, deposited metal material or polysilicon material on the gate insulating layer 240 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More