VCSEL device with high-dielectric-constant limiting hole and preparation method thereof

A high dielectric constant, current limiting technology, applied in electrical components, laser parts, circuits, etc., can solve the problems of inability to concentrate current in the middle of the device, affecting the heat dissipation and performance of the device, and excessive growth process requirements. The effect of strong repeatability, low production cost and reduced process time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

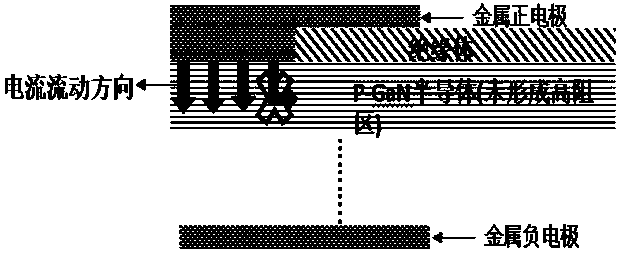

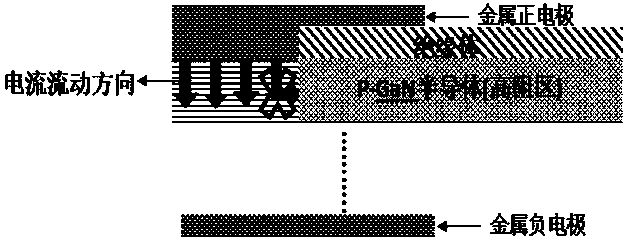

Problems solved by technology

Method used

Image

Examples

Embodiment 1

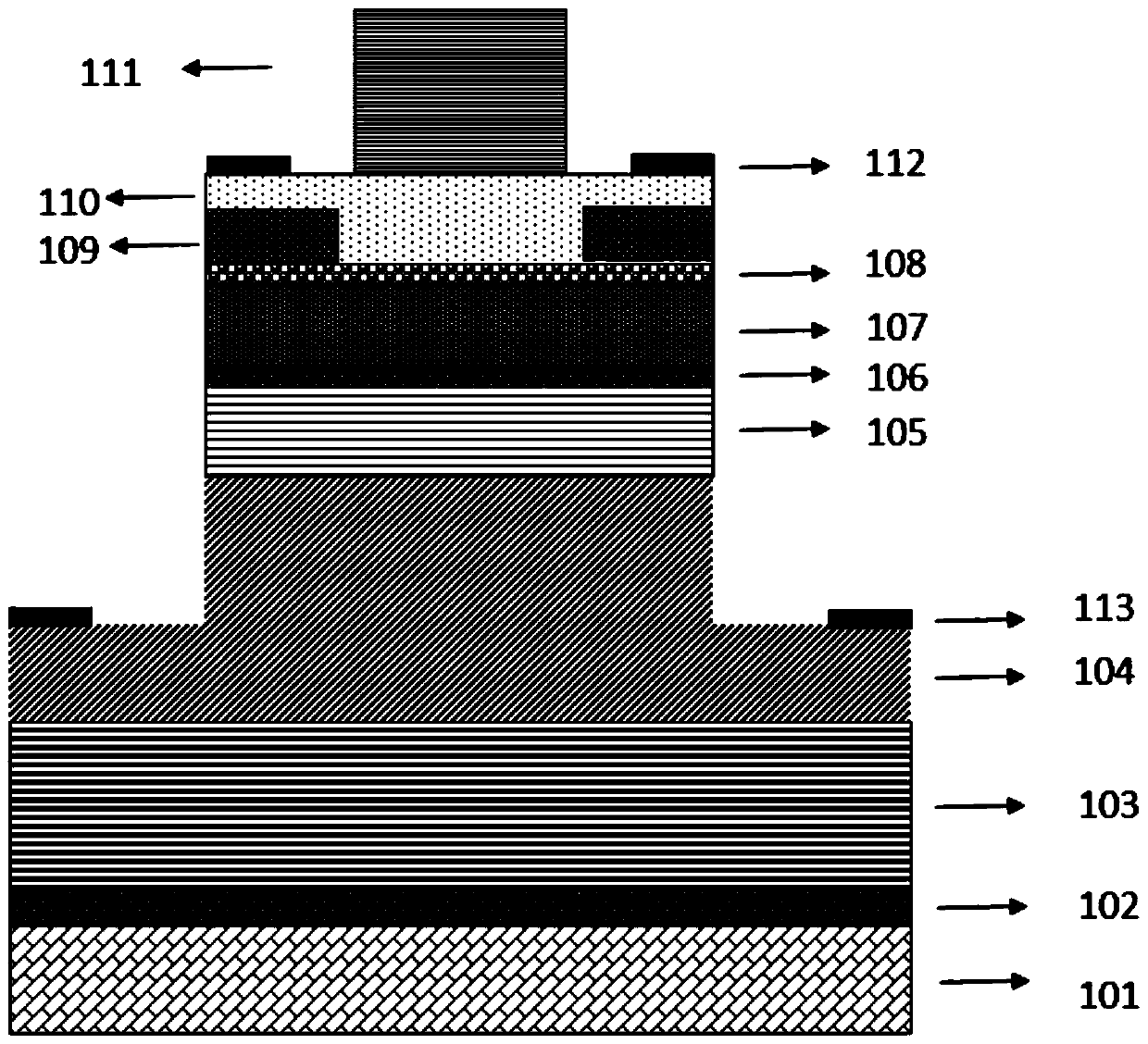

[0059] The epitaxial structure of the VCSEL device with a high dielectric constant current confinement hole in this embodiment sequentially includes a circular substrate 101, a buffer layer 102, a nitride epitaxial DBR103 and an N-type semiconductor transmission layer 104 along the epitaxial growth direction; , the N-type semiconductor transport layer 104 is divided into two parts, the lower layer completely covers the nitride epitaxial DBR103, with a thickness of 2 μm; the projected area of the upper layer is 80% of the area of the lower layer, and is the same as the center of the lower layer, and the thickness is 0.5 μm; The upper layer of the N-type semiconductor transport layer 104 is successively multi-quantum well layer 105, P-type current blocking layer 106, P-type semiconductor transport layer 107; P-type heavily doped semiconductor transport layer 108; P-type heavily doped The outer side of the upper surface of the hetero-semiconductor transport layer 108 is an ann...

Embodiment 2

[0069] The epitaxial structure of the VCSEL device with a high dielectric constant current confinement hole in this embodiment sequentially includes a circular substrate 101, a buffer layer 102, a nitride epitaxial DBR103 and an N-type semiconductor transmission layer 104 along the epitaxial growth direction; , the N-type semiconductor transport layer 104 is divided into two parts, the lower layer completely covers the nitride epitaxial DBR103, with a thickness of 2 μm; the projected area of the upper layer is 80% of the area of the lower layer, and is the same as the center of the lower layer, and the thickness is 0.5 μm; The upper layer of the N-type semiconductor transport layer 104 is successively multi-quantum well layer 105, P-type current blocking layer 106, P-type semiconductor transport layer 107; P-type heavily doped semiconductor transport layer 108; P-type heavily doped The outer side of the upper surface of the hetero-semiconductor transport layer 108 is an ann...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More