CMOS (complementary metal oxide semiconductor) device capable of reducing charge collection generated by radiation and preparation method thereof

A charge collection and device technology, applied in the field of CMOS devices, can solve problems such as aggravating the failure of single-event integrated circuits and output errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

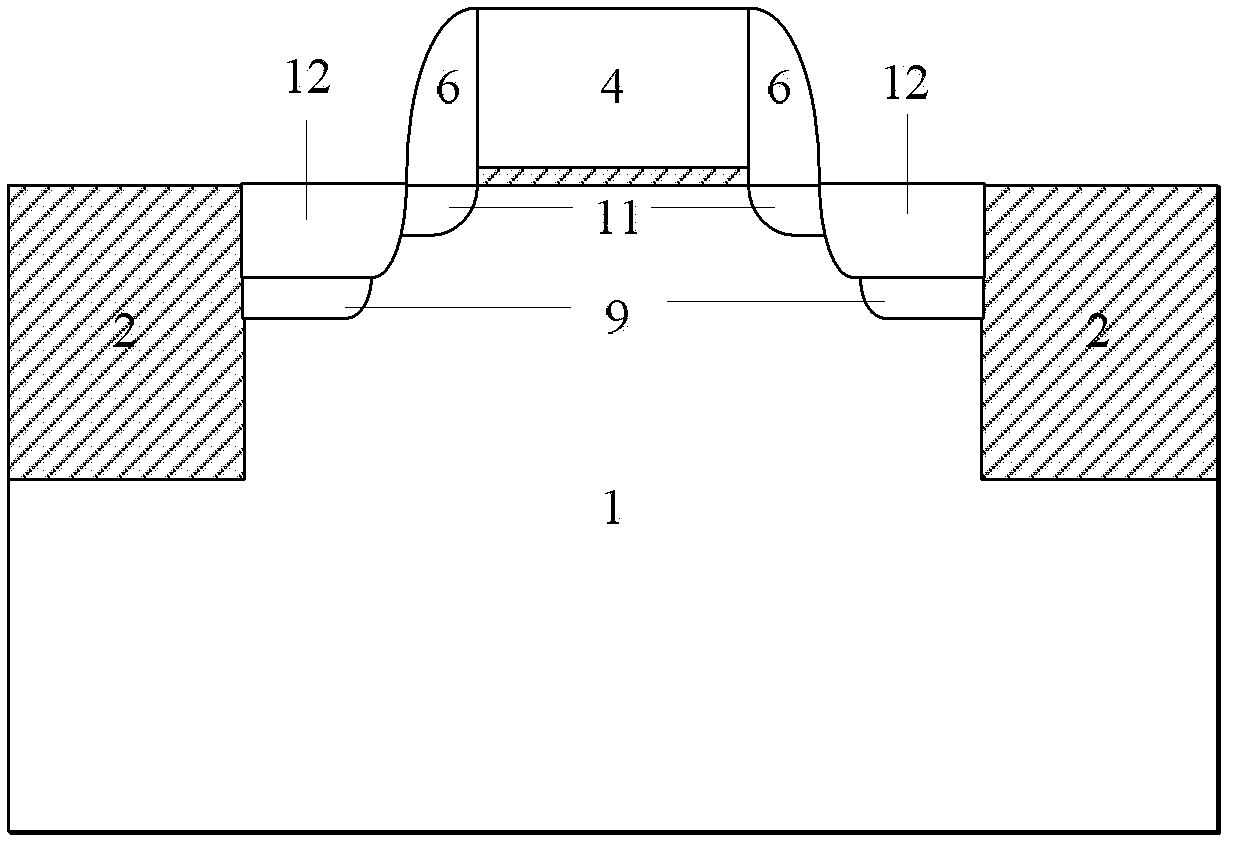

[0030] figure 2 For the cross-sectional view of the CMOS device proposed by the present invention, as shown in the figure, the CMOS device of the present invention includes a substrate 1, a device isolation region 2, a gate region 4, a gate spacer 6, a source region and a drain region 12, and an LDD region 11 , wherein the suppression charge collection region 9 is added directly below the source region and the drain region.

[0031] The specific implementation manner of the present invention will be described below by taking NMOS as an example.

[0032] 1) Substrate preparation: Lightly doped P-type silicon with a crystal orientation of (100) is used as the substrate 1, and the doping concentration is 10 15 ~10 16 cm -3 ;

[0033] 2) Formation of the device isolation region: Thermally grow a layer of silicon dioxide on the substrate 1 as a buffer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More