Patents

Literature

304results about How to "Increase light emitting area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

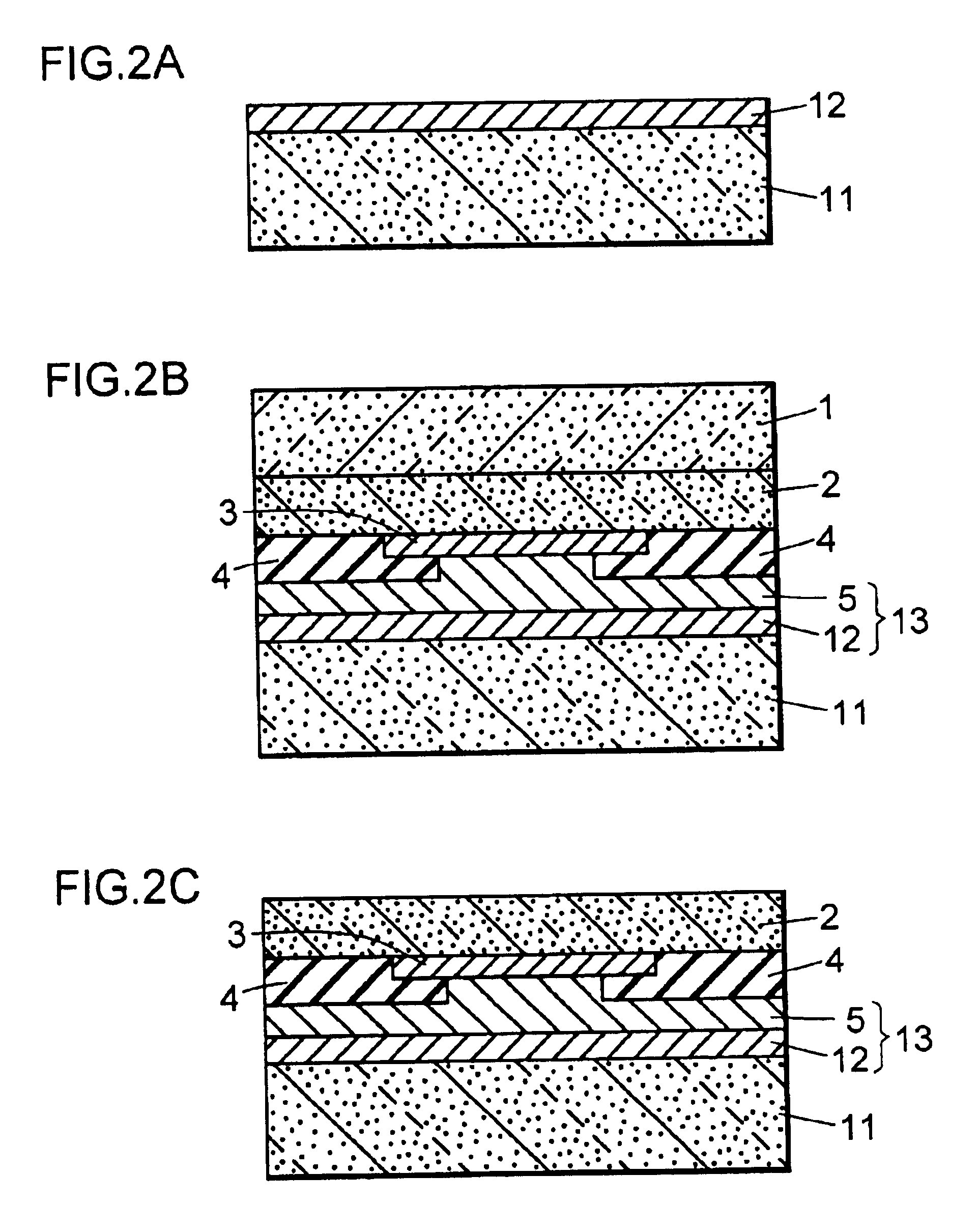

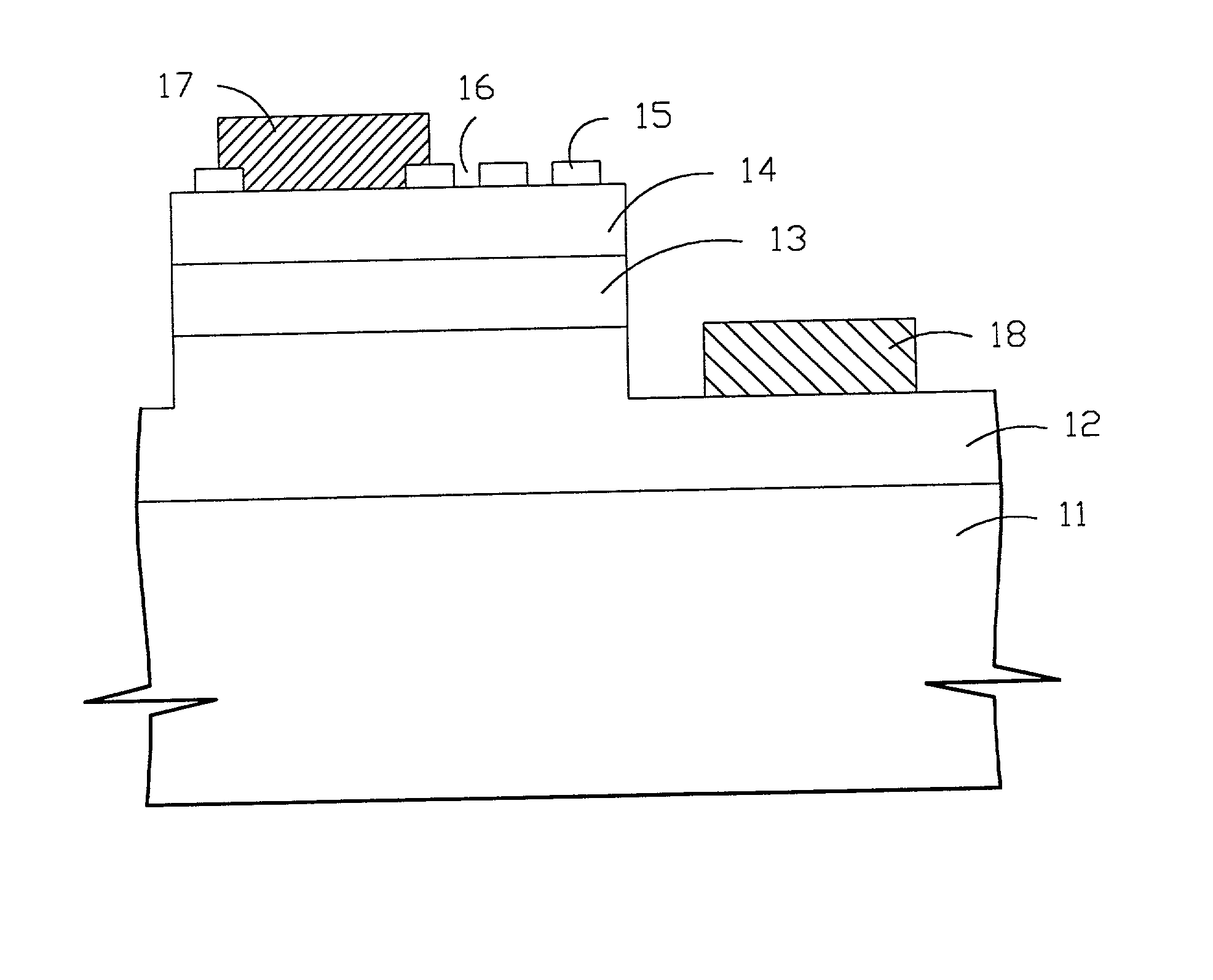

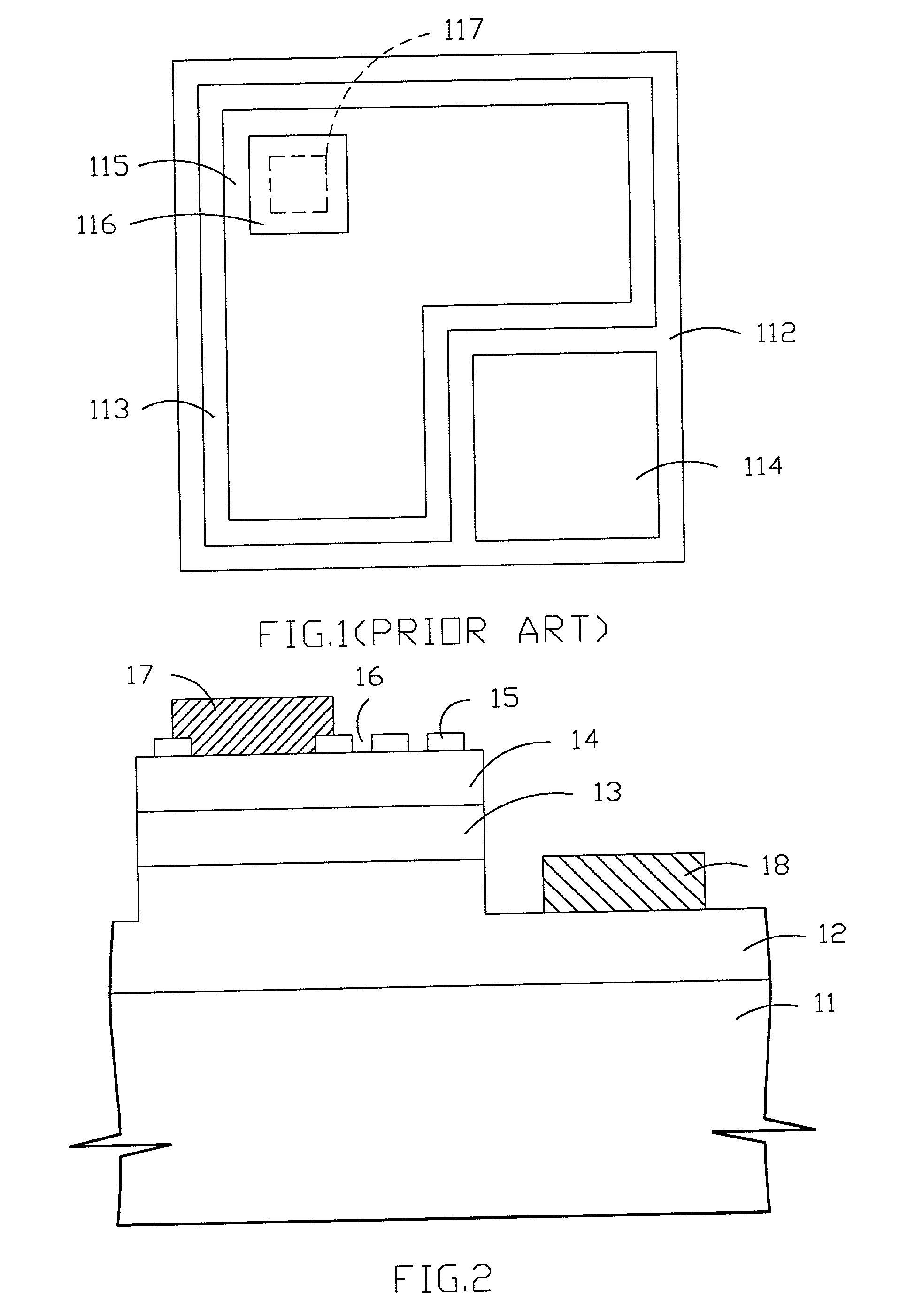

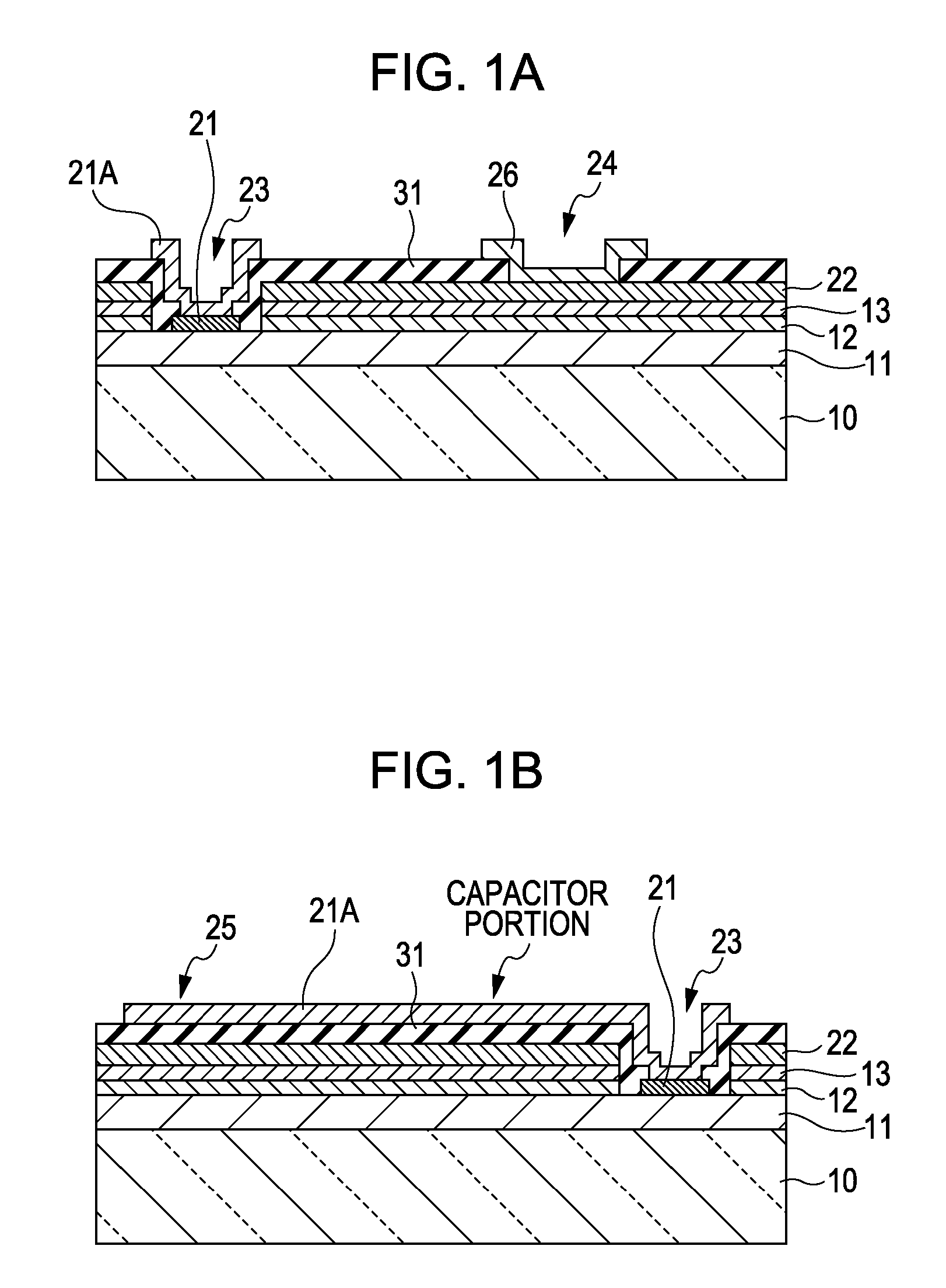

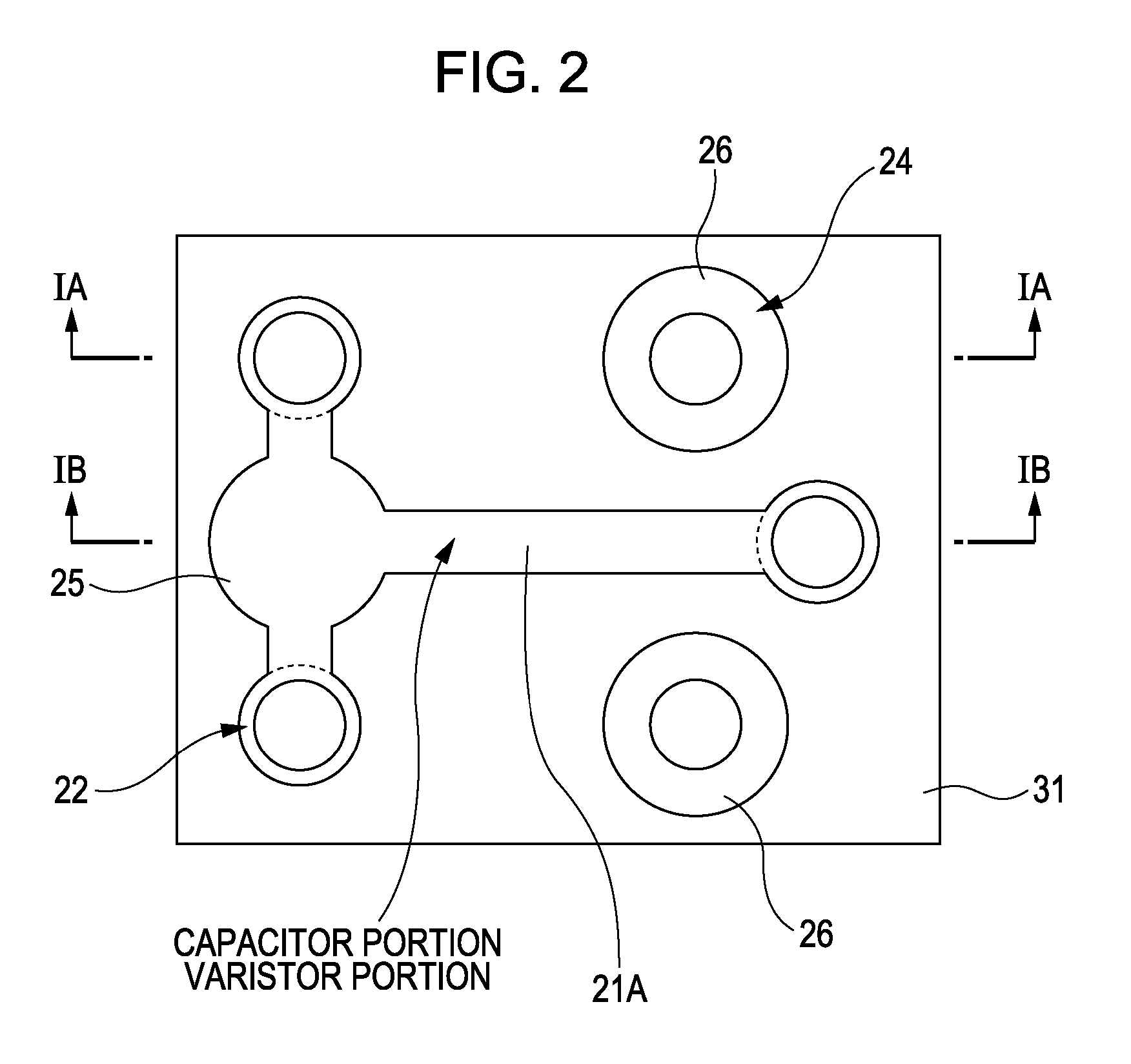

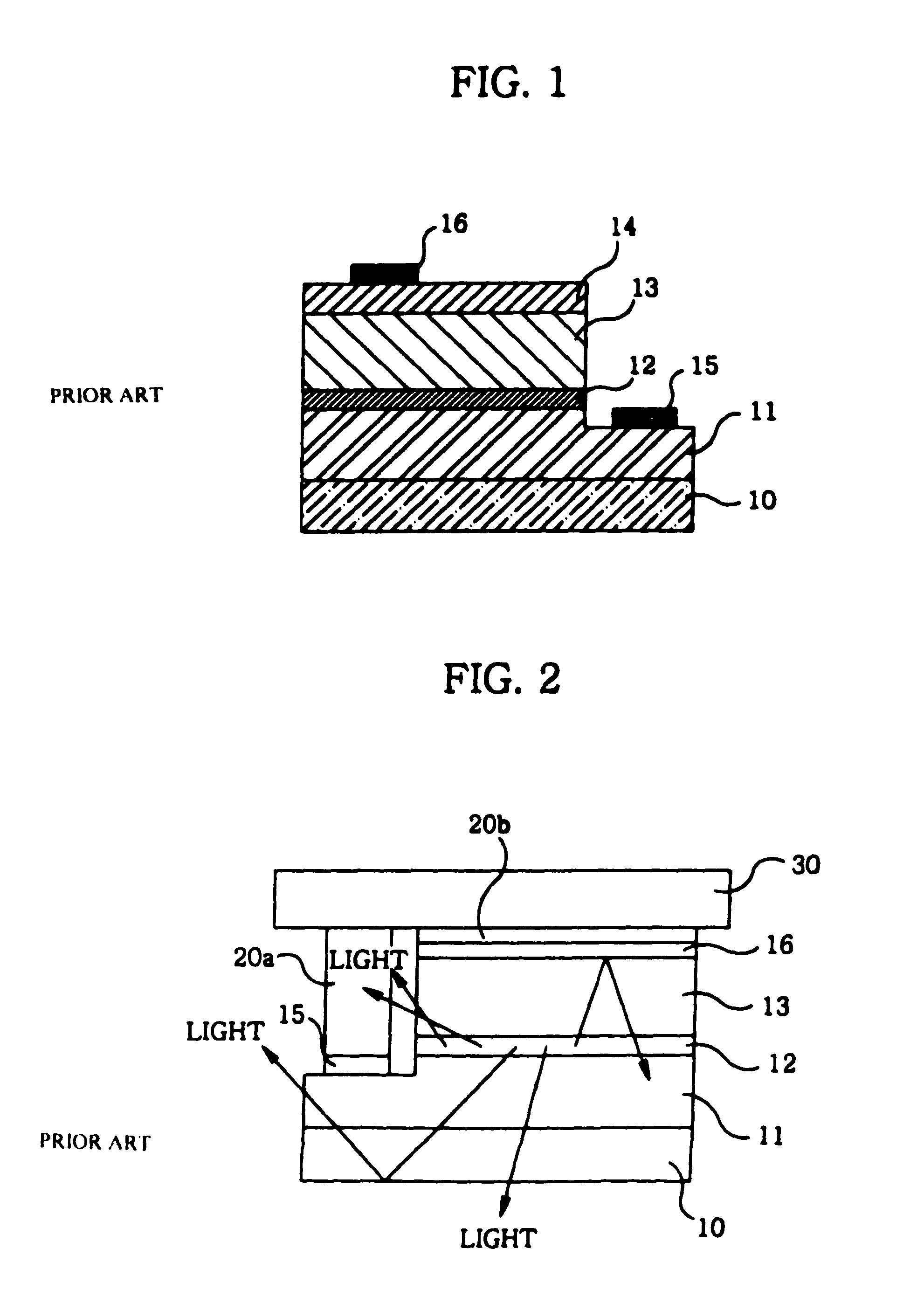

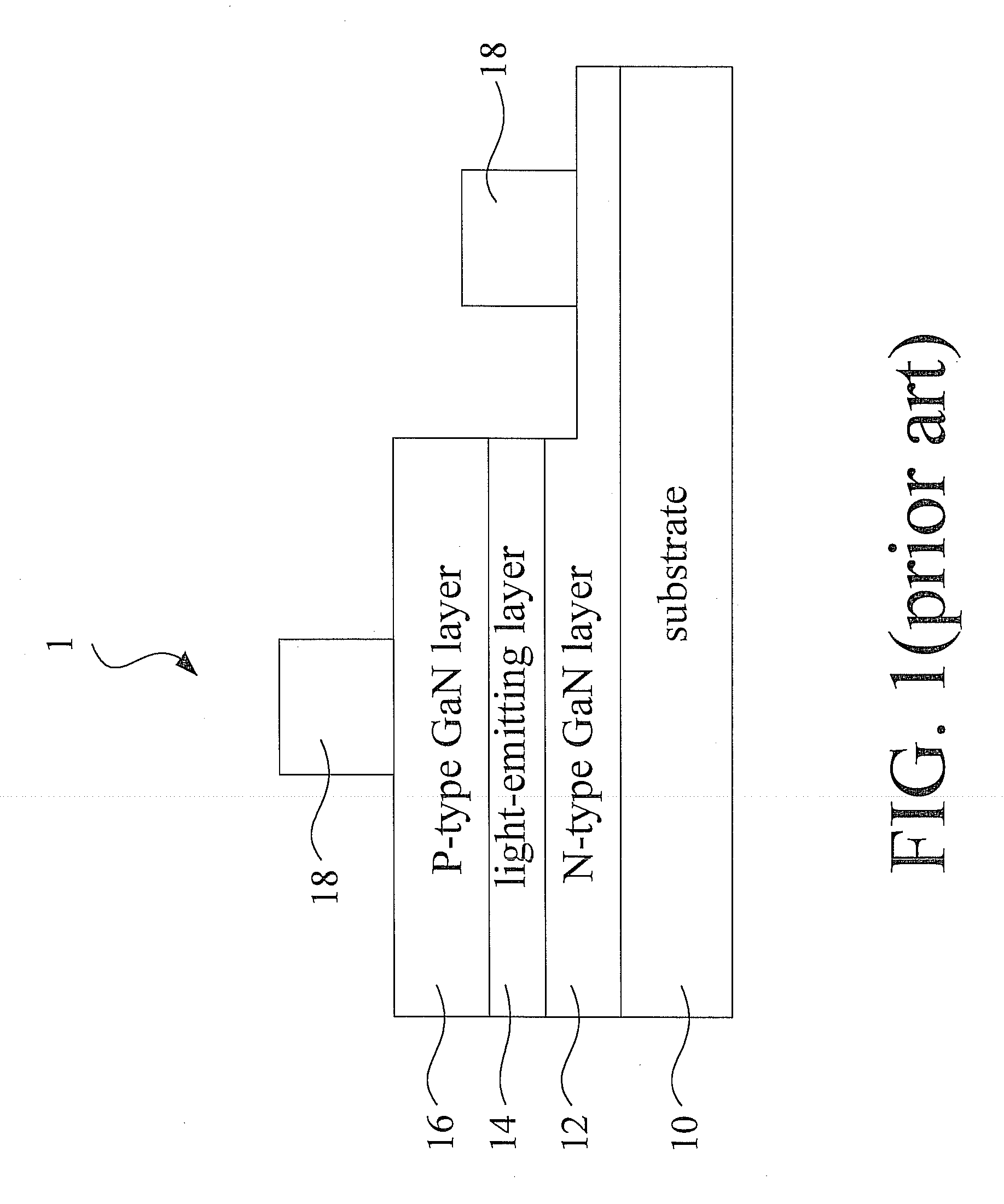

Opposed terminal structure having a nitride semiconductor element

InactiveUS20050035364A1Improve light extraction efficiencyLower resistanceLaser detailsLaser active region structureEngineeringNitride semiconductors

An opposed terminal structure including a supporting substrate, a first terminal, a nitride semiconductor with a light-emitting layer, and a second terminal. The second terminal forms an opposed terminal structure with the first terminal, which can be formed in a variety of patterns.

Owner:NICHIA CORP

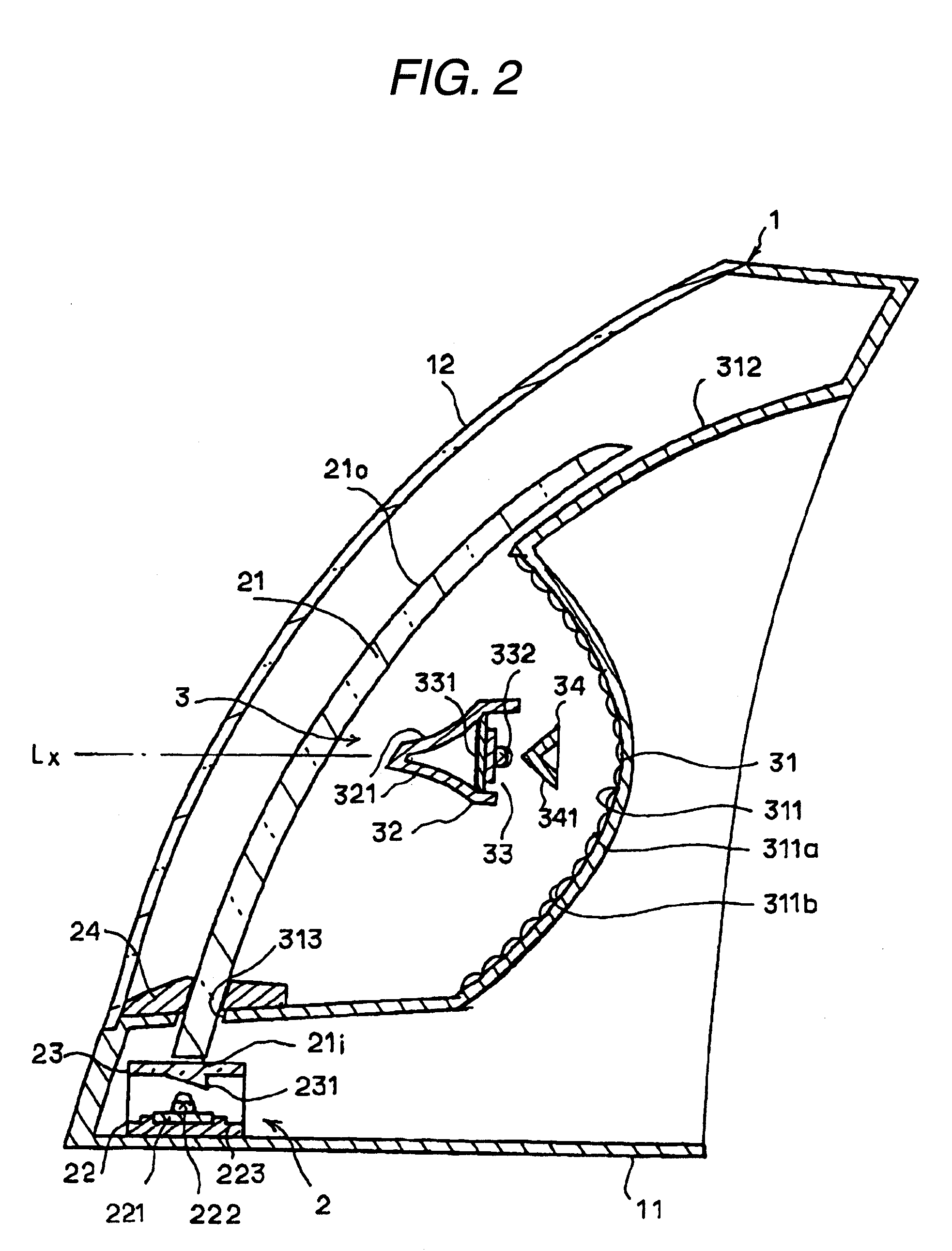

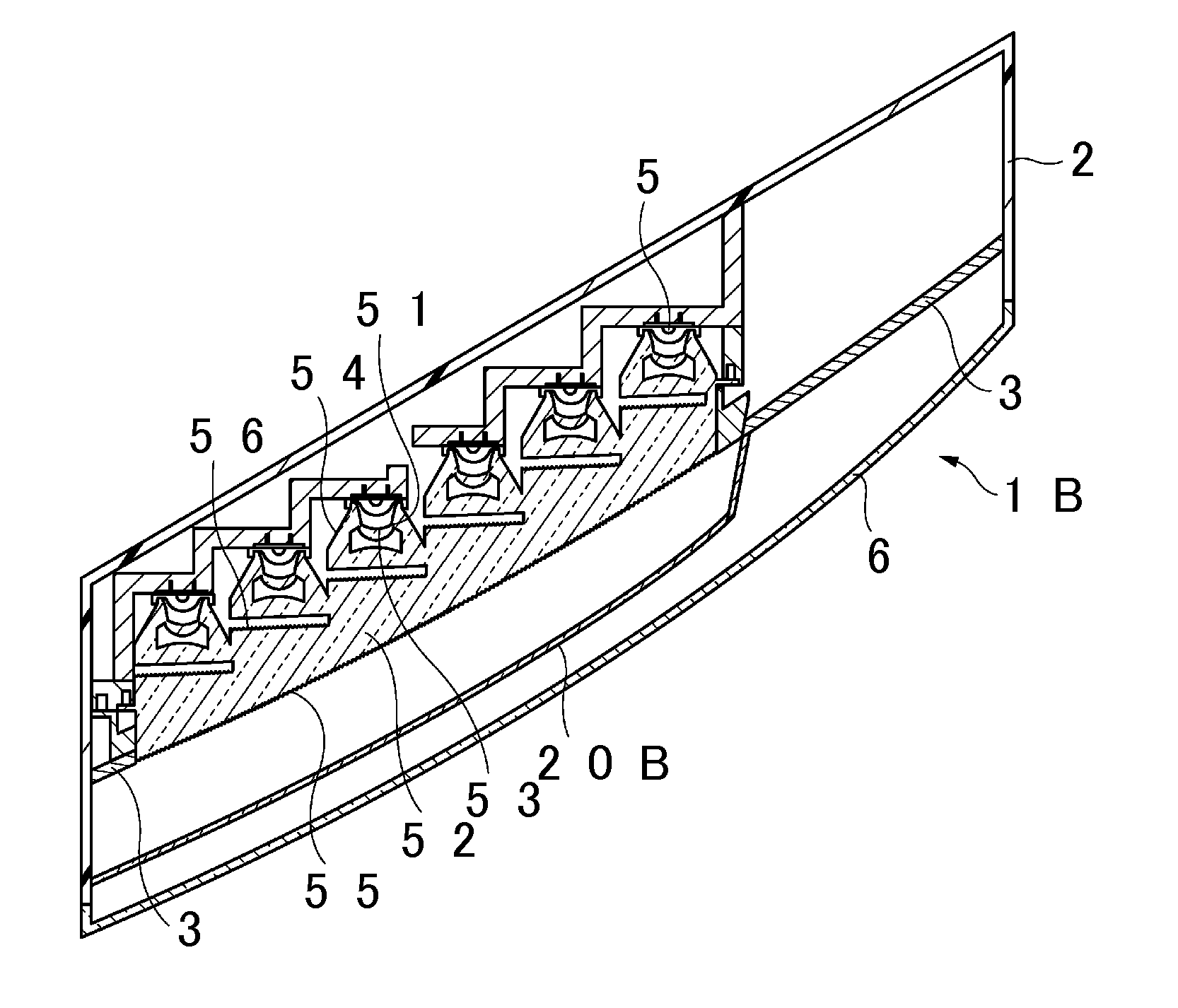

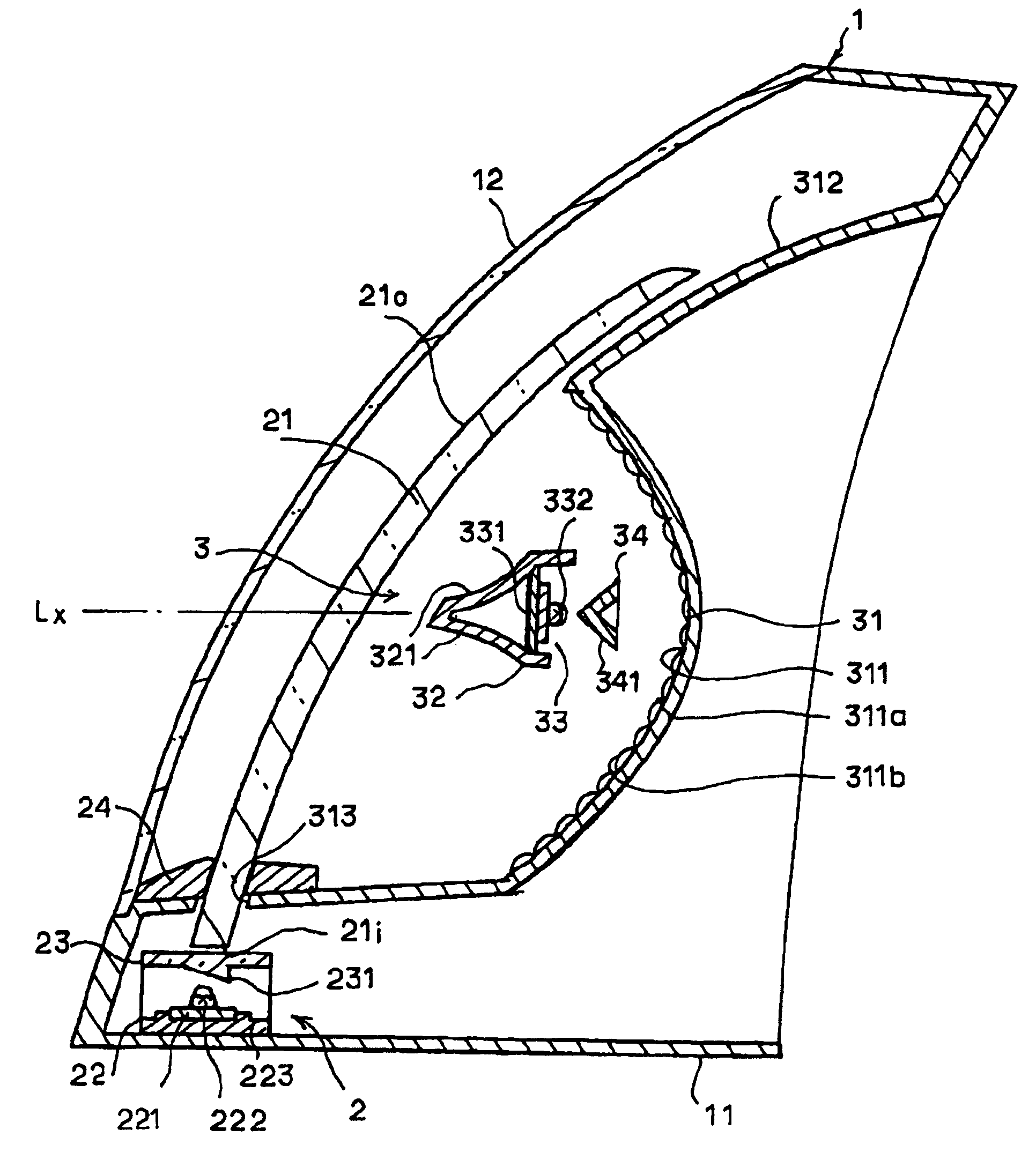

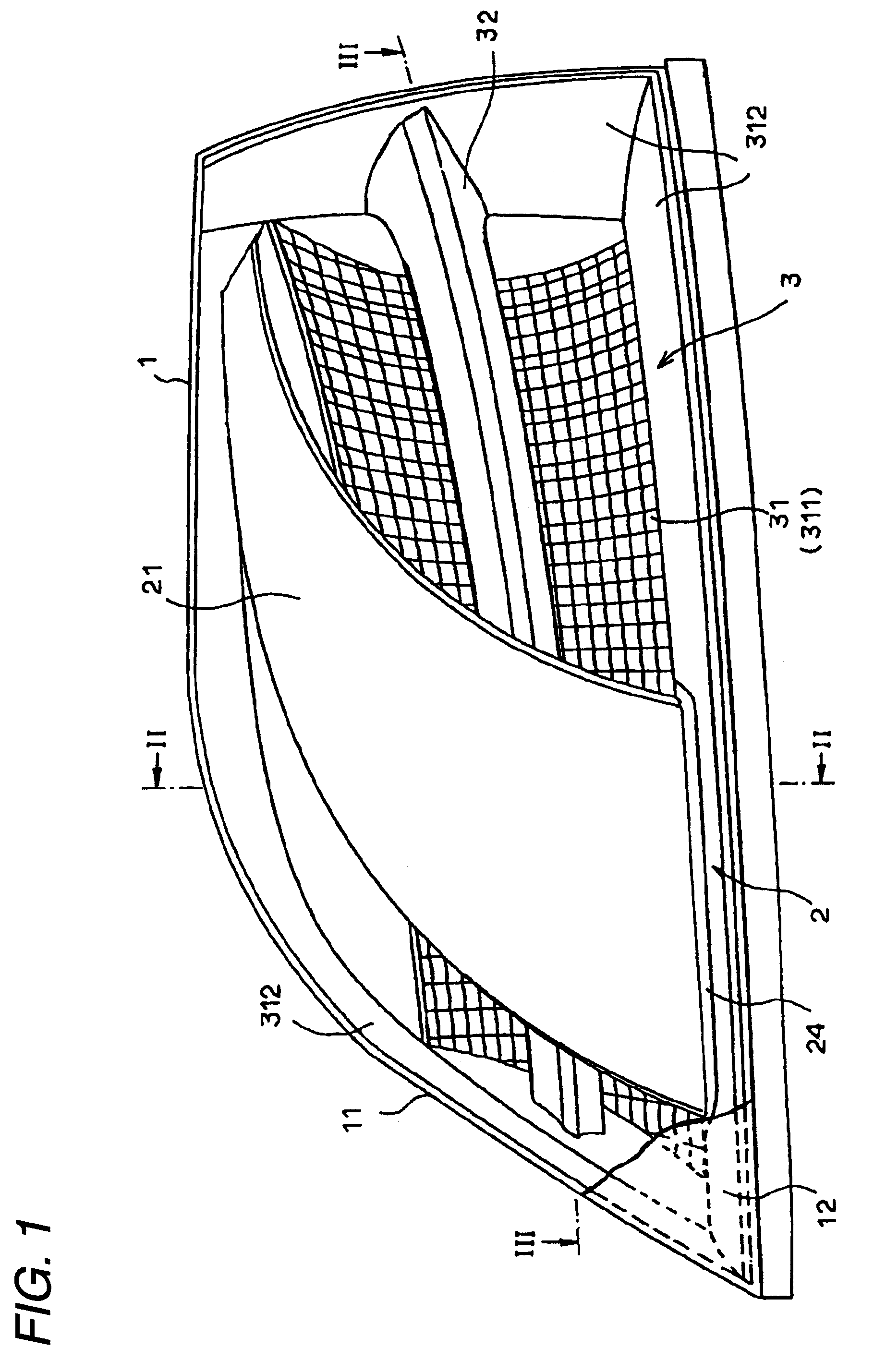

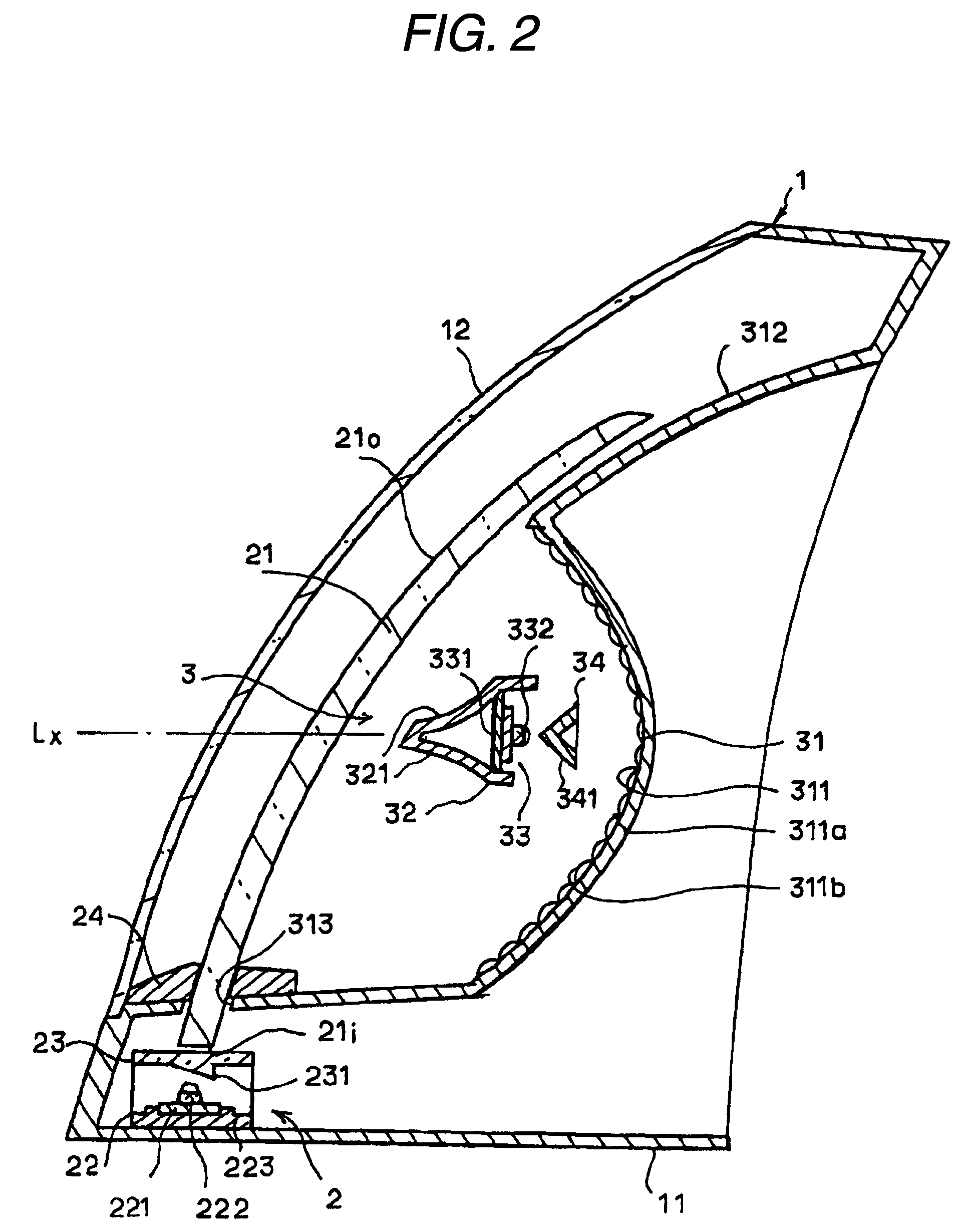

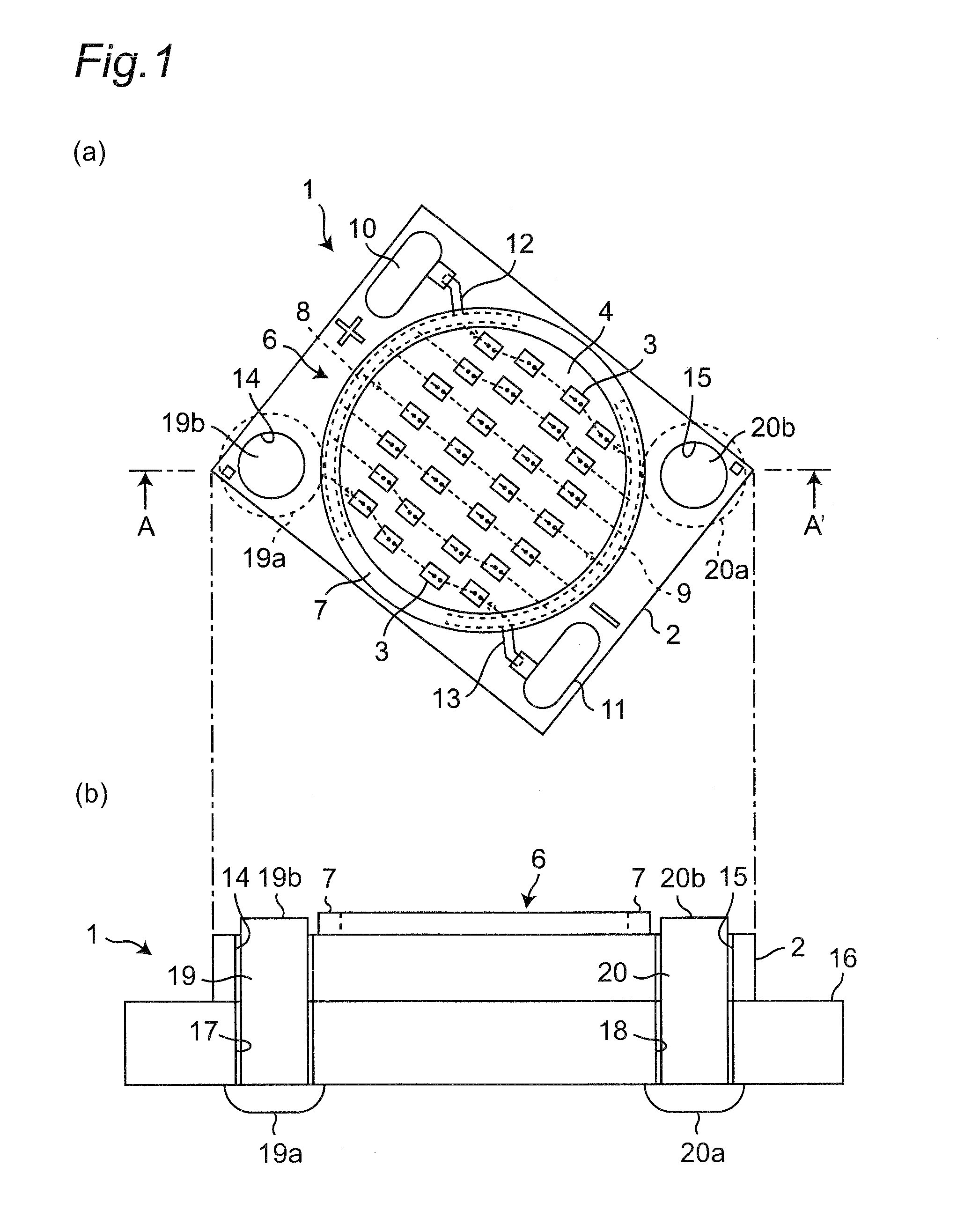

Lamp

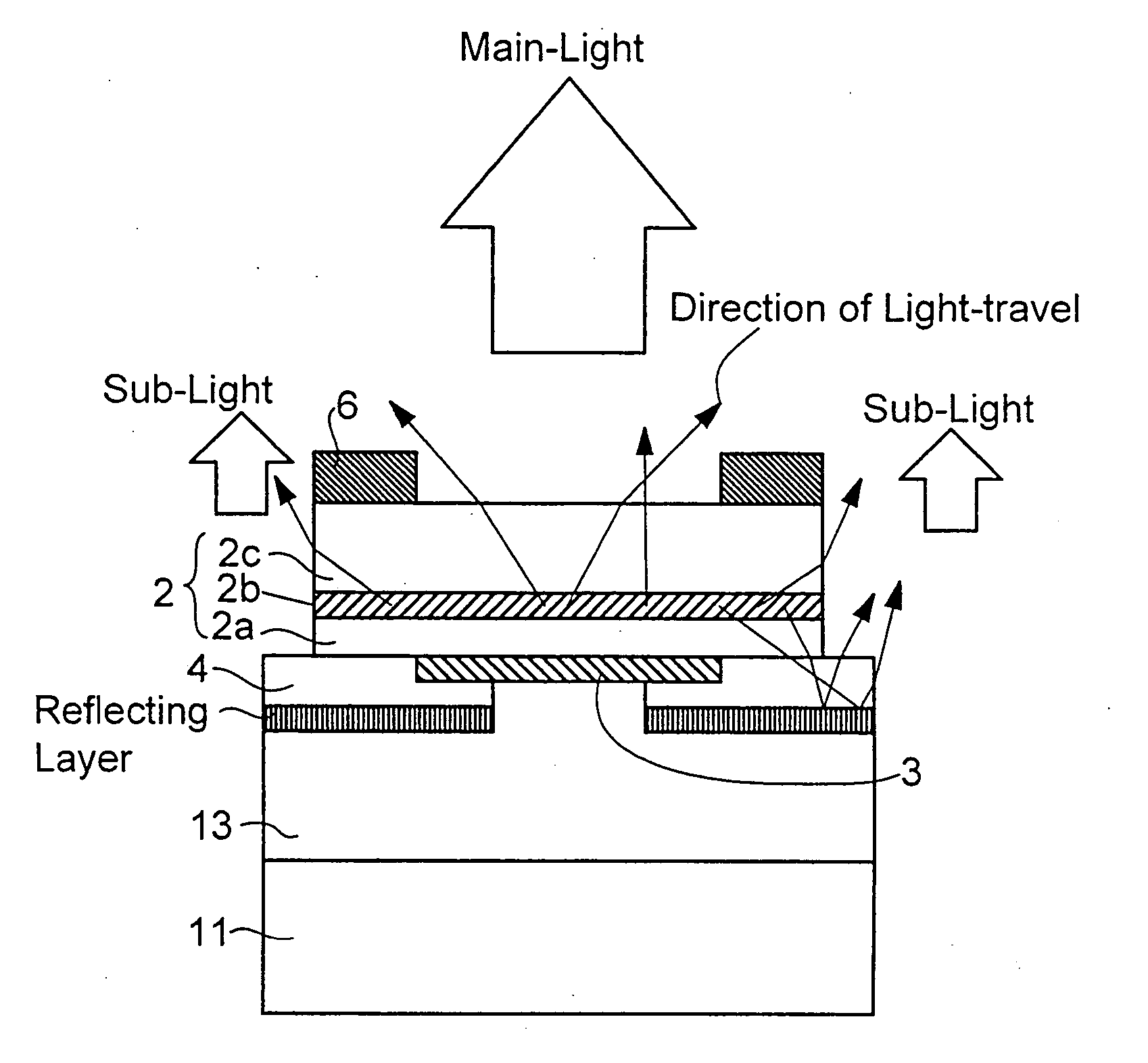

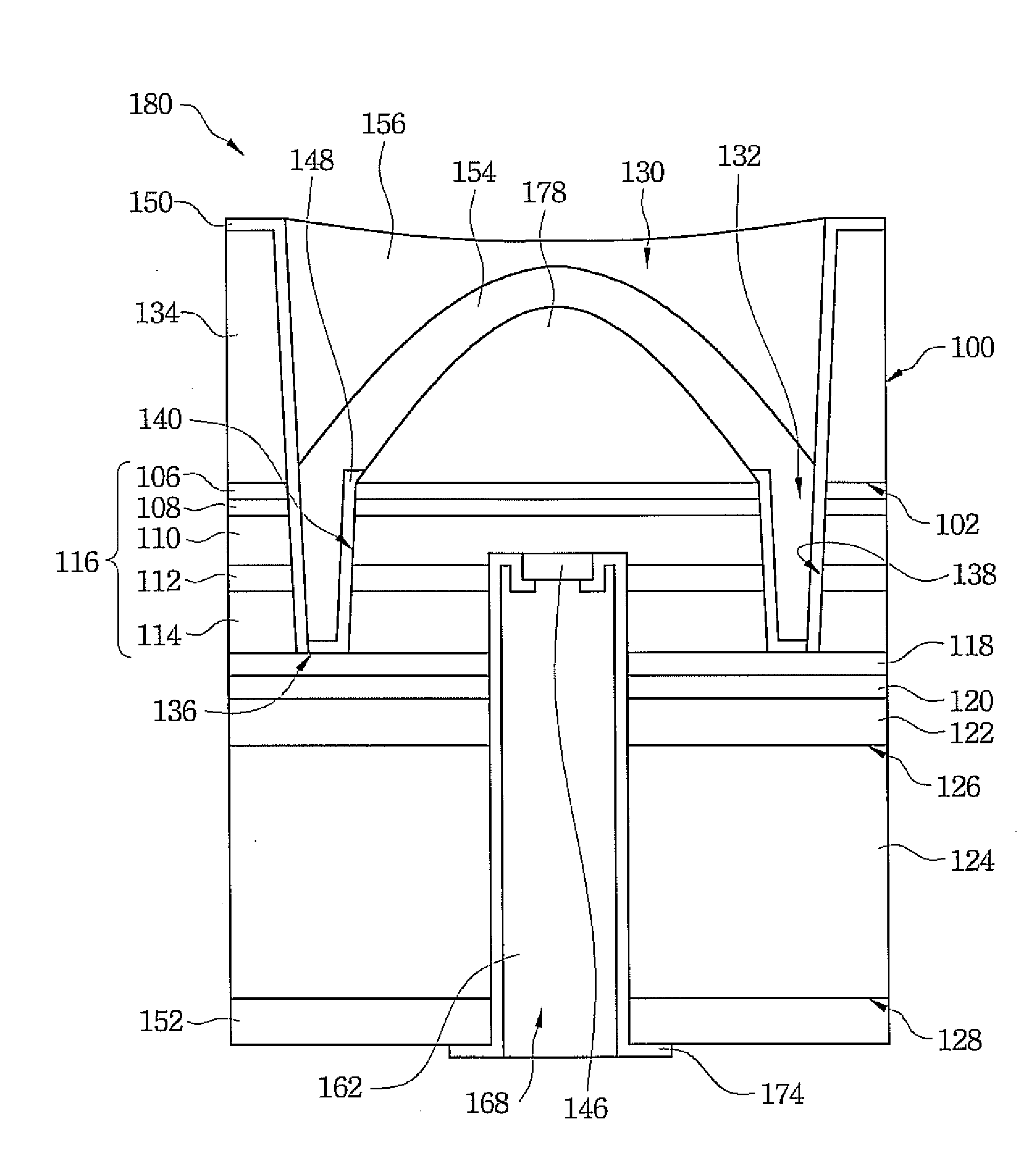

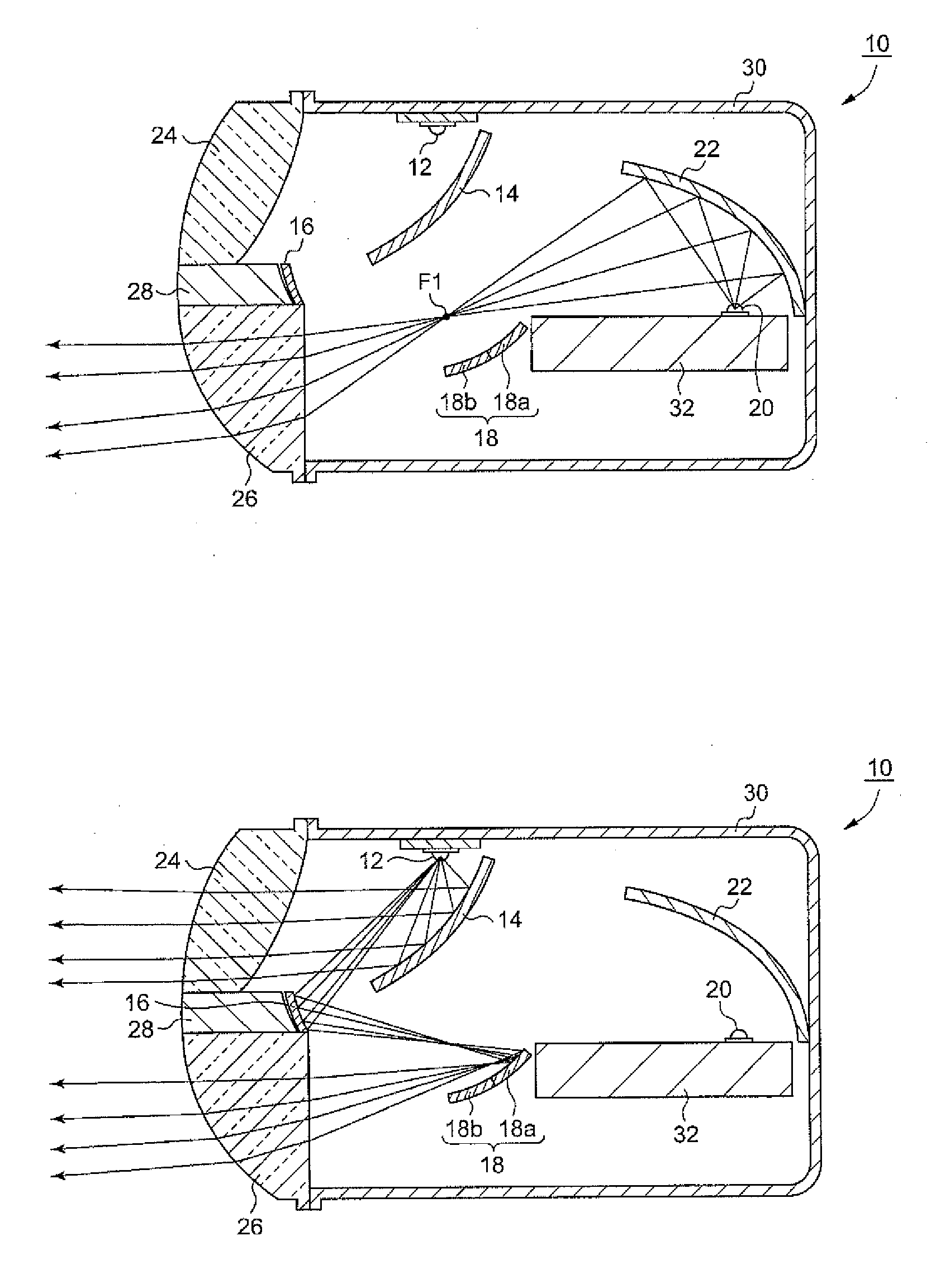

InactiveUS20100008088A1Increase light emitting areaGood lookingLighting support devicesPoint-like light sourceLight-emitting diode

A lamp is provided. The lamp includes a lamp housing; light emitting diodes (LEDs); a main reflector disposed so as to oppose to the LEDs for reflecting light emitted from the LEDs towards a front side of the lamp; a sub-reflector which is interposed between the LEDs and the main reflector, and which reflects and diffuses the light emitted from the LEDs towards the main reflector; an LED element assembly which extends in parallel with the sub-reflector and comprises a plurality of flat portions, each flat portion corresponding to one of the plurality of LEDs and on which the corresponding LED is mounted, adjacent ones of the flat portions being coupled together by at least one step portion; and a center portion which covers the LED element assembly and the LEDs such that the LEDs are not exposed to the front side of the lamp.

Owner:KOITO MFG CO LTD

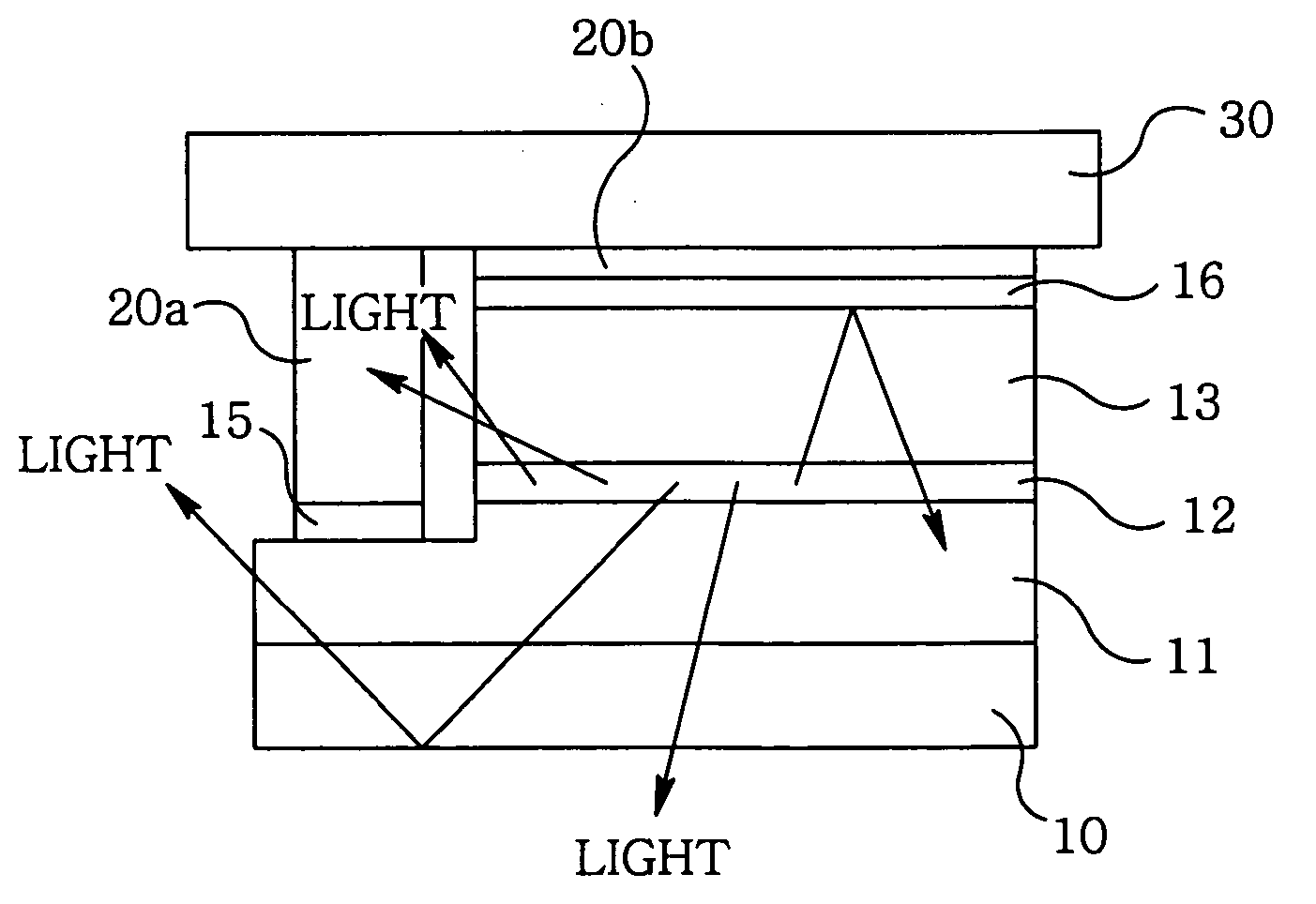

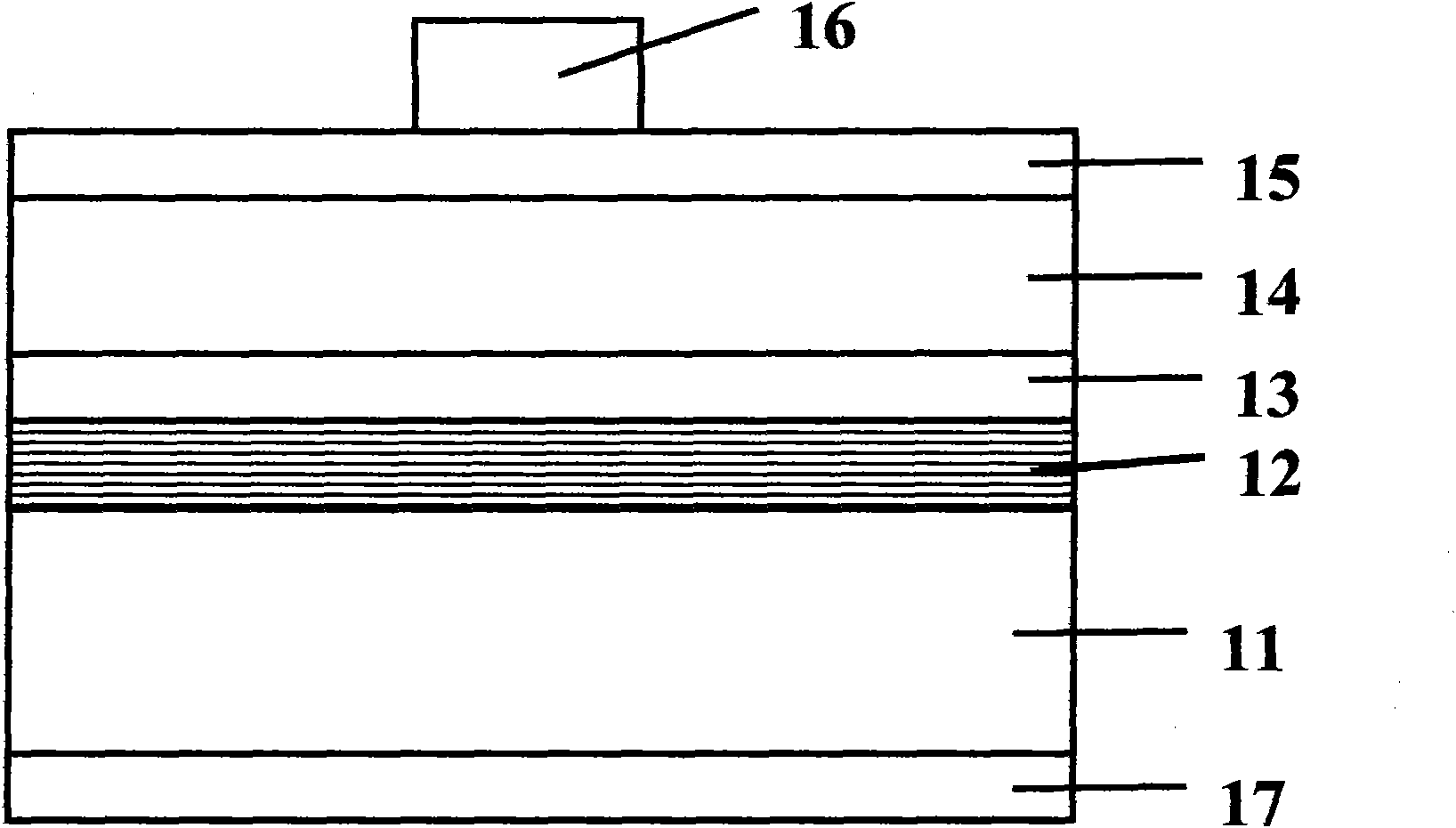

Method for producing a nitride semiconductor element

InactiveUS6916676B2Improve light extraction efficiencyLower resistanceLaser detailsLaser active region structureNitride semiconductorsMaterials science

Owner:NICHIA CORP

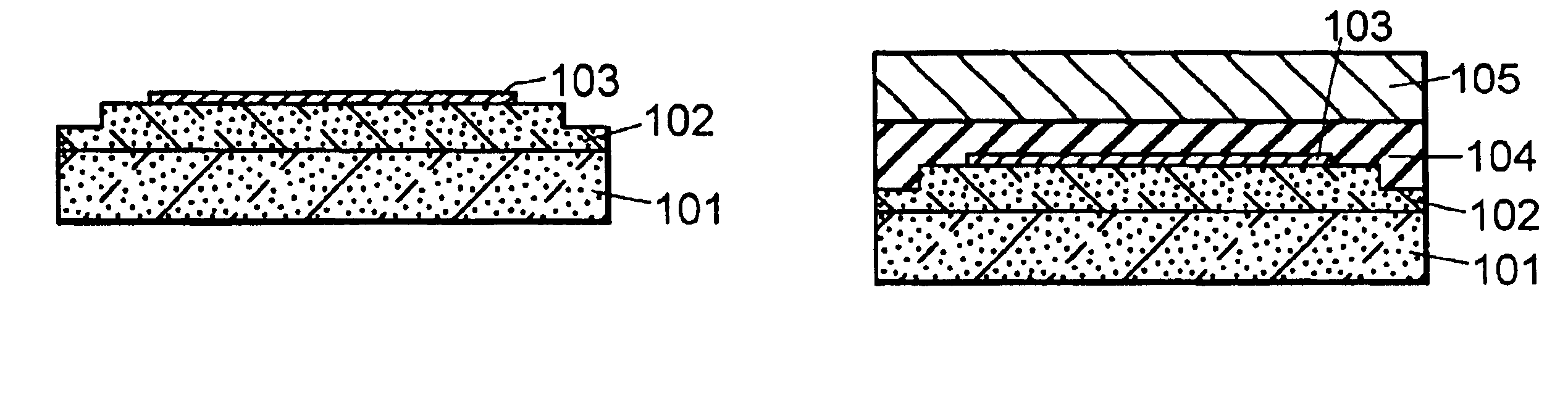

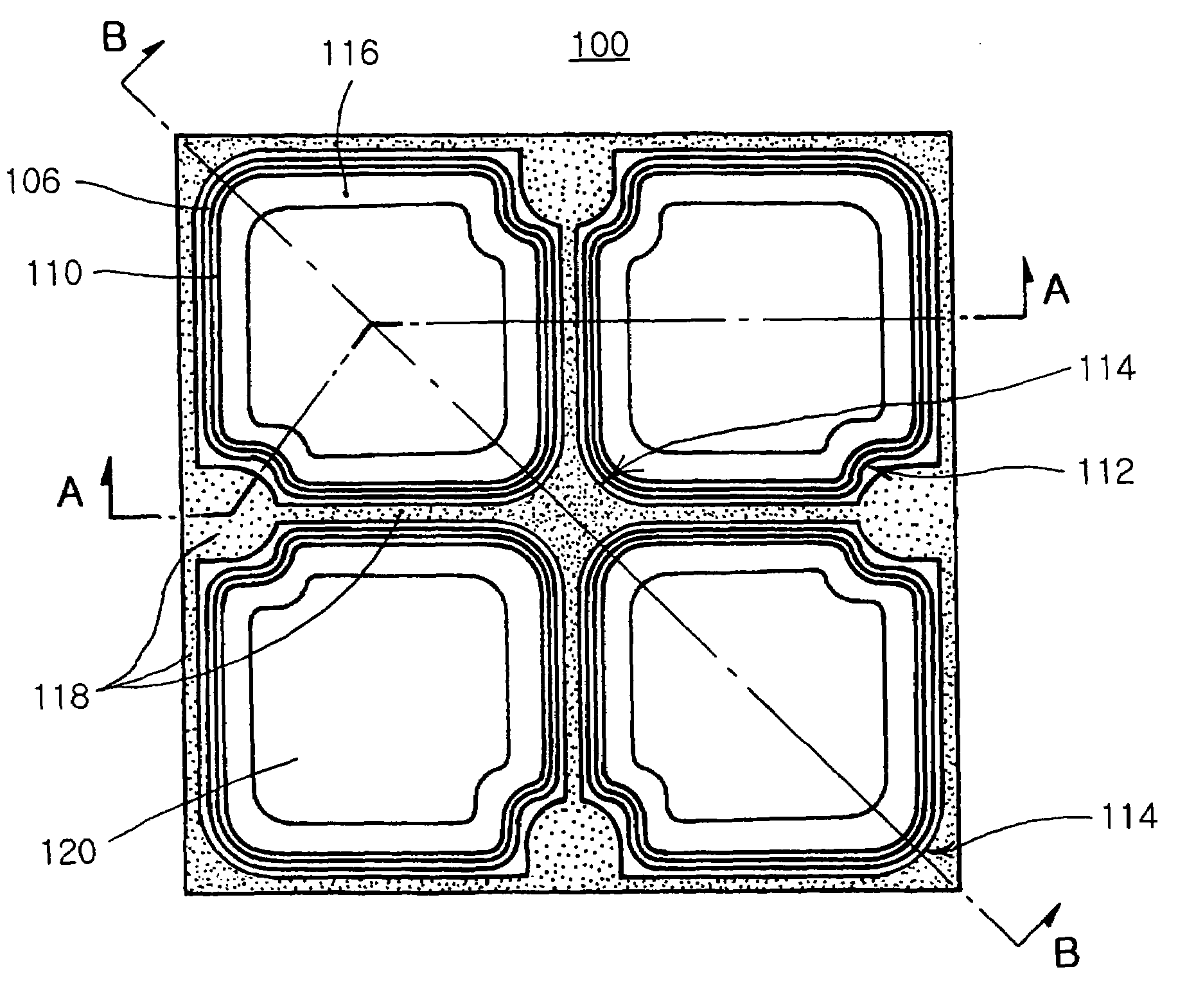

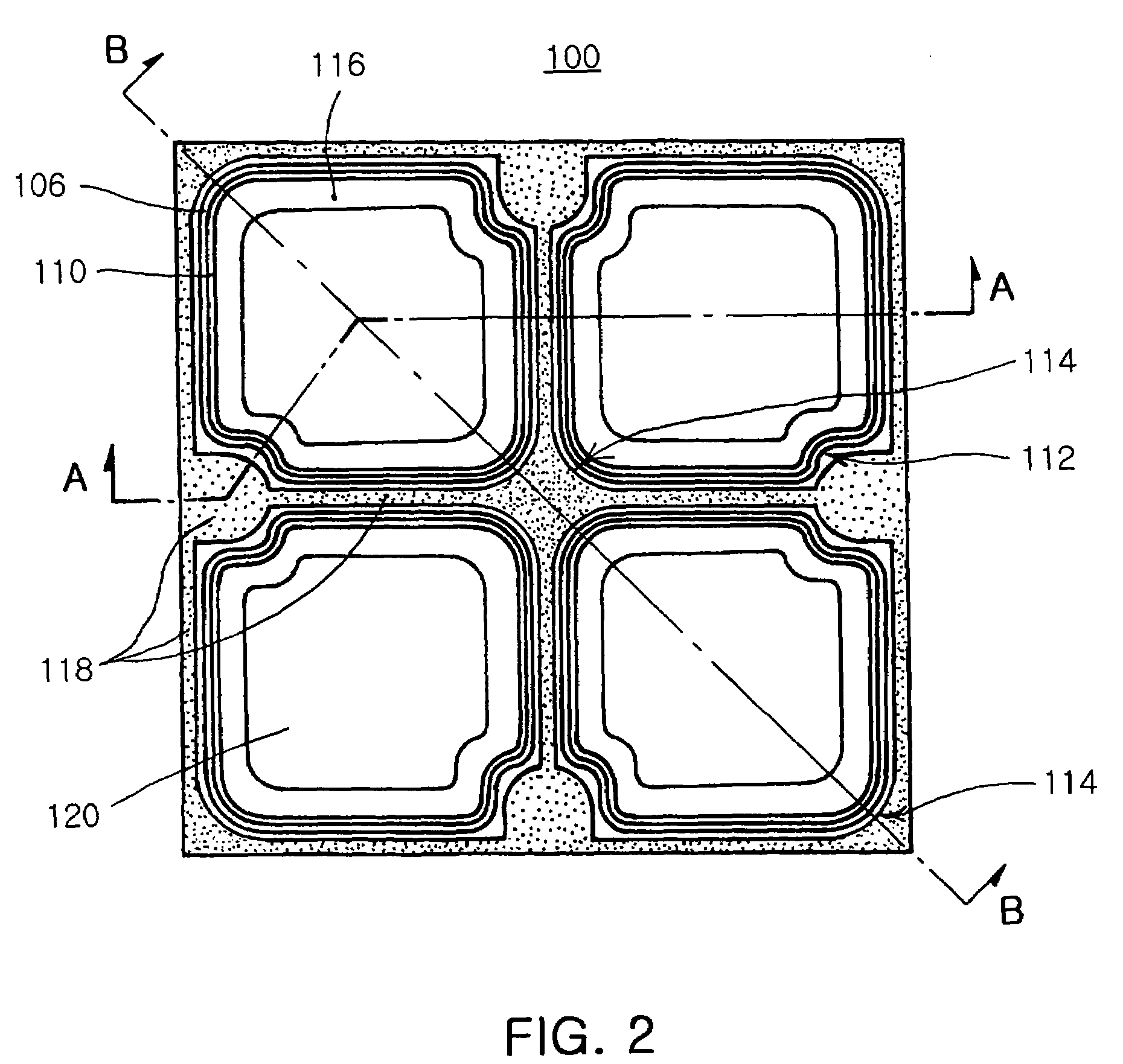

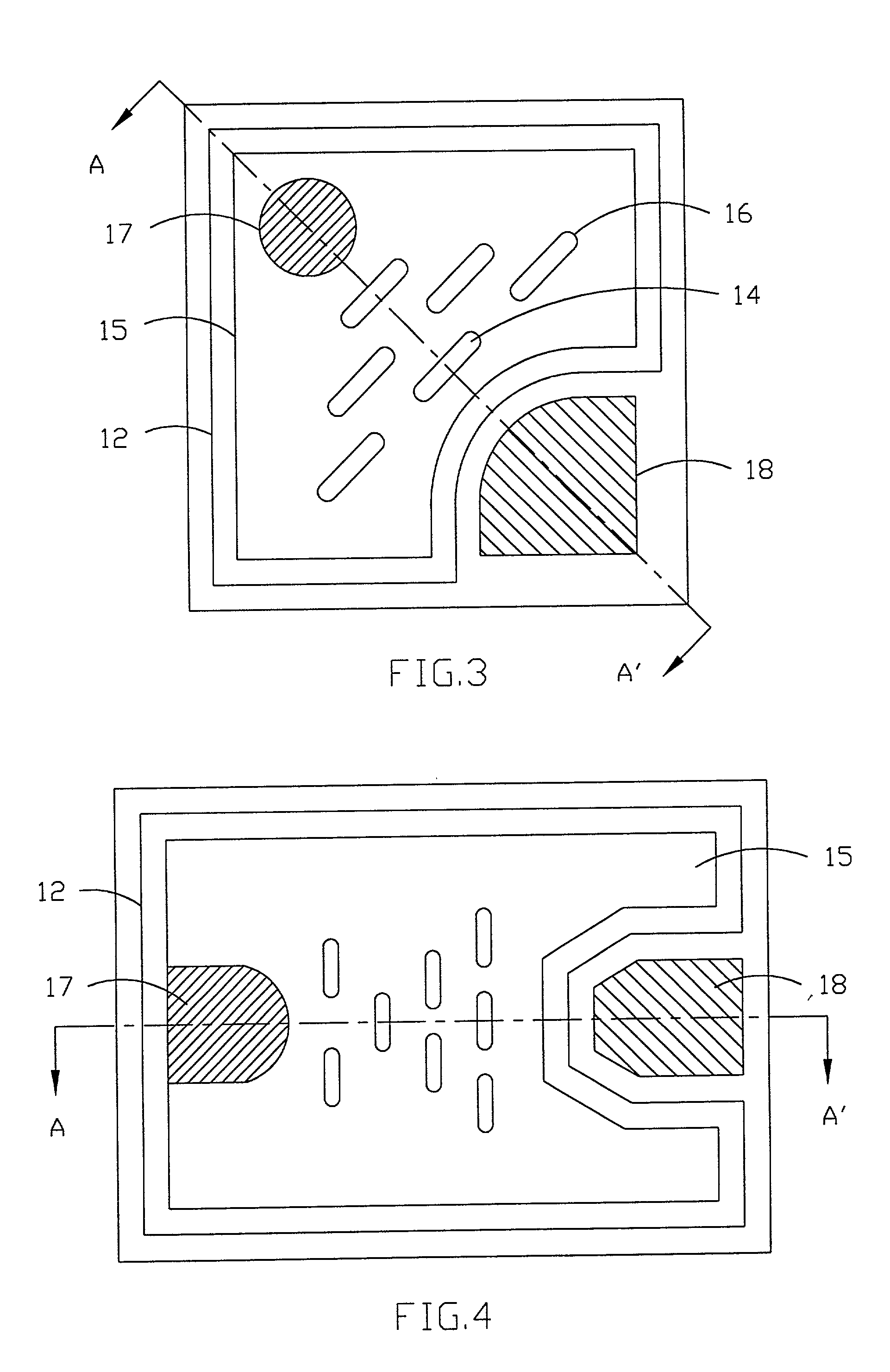

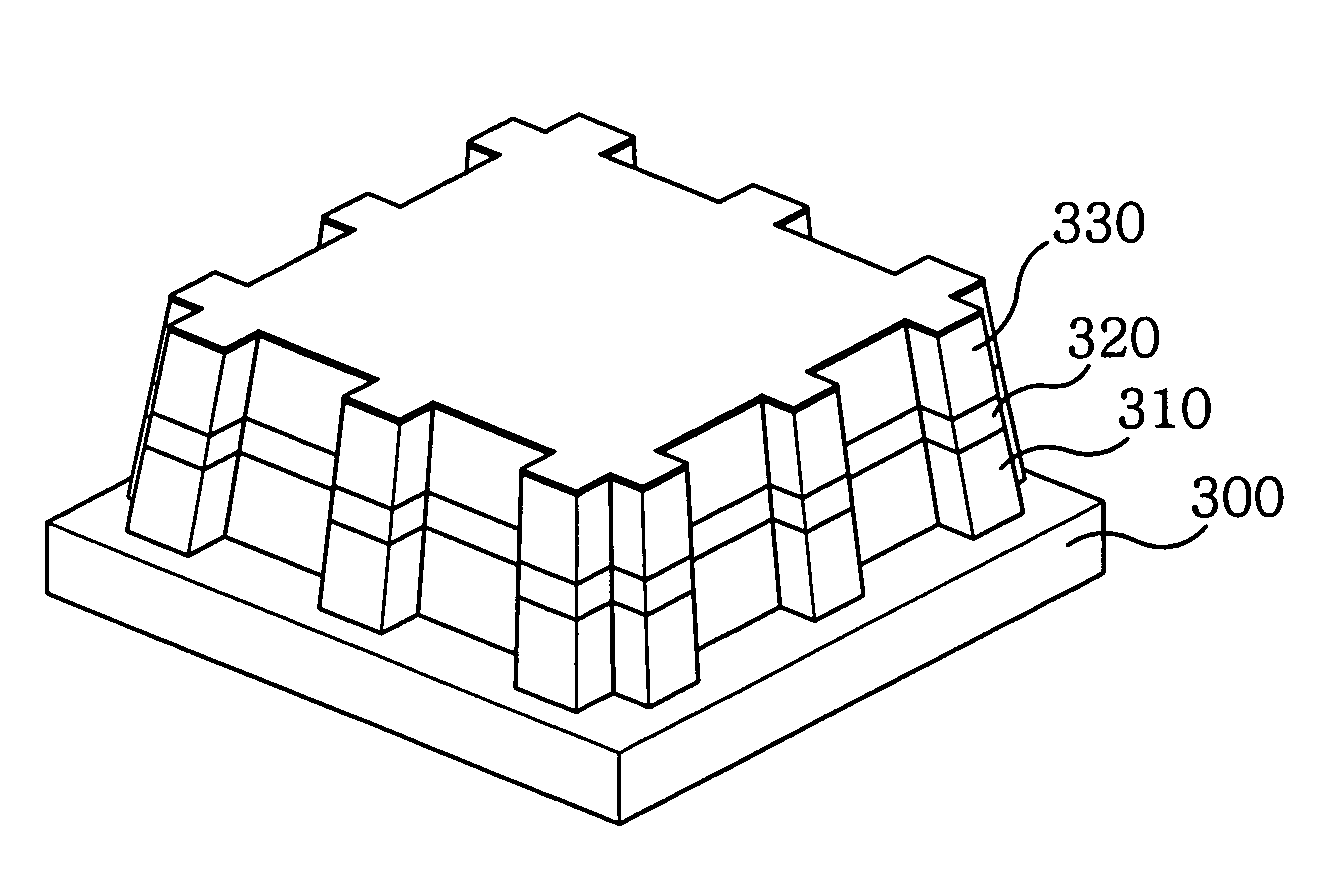

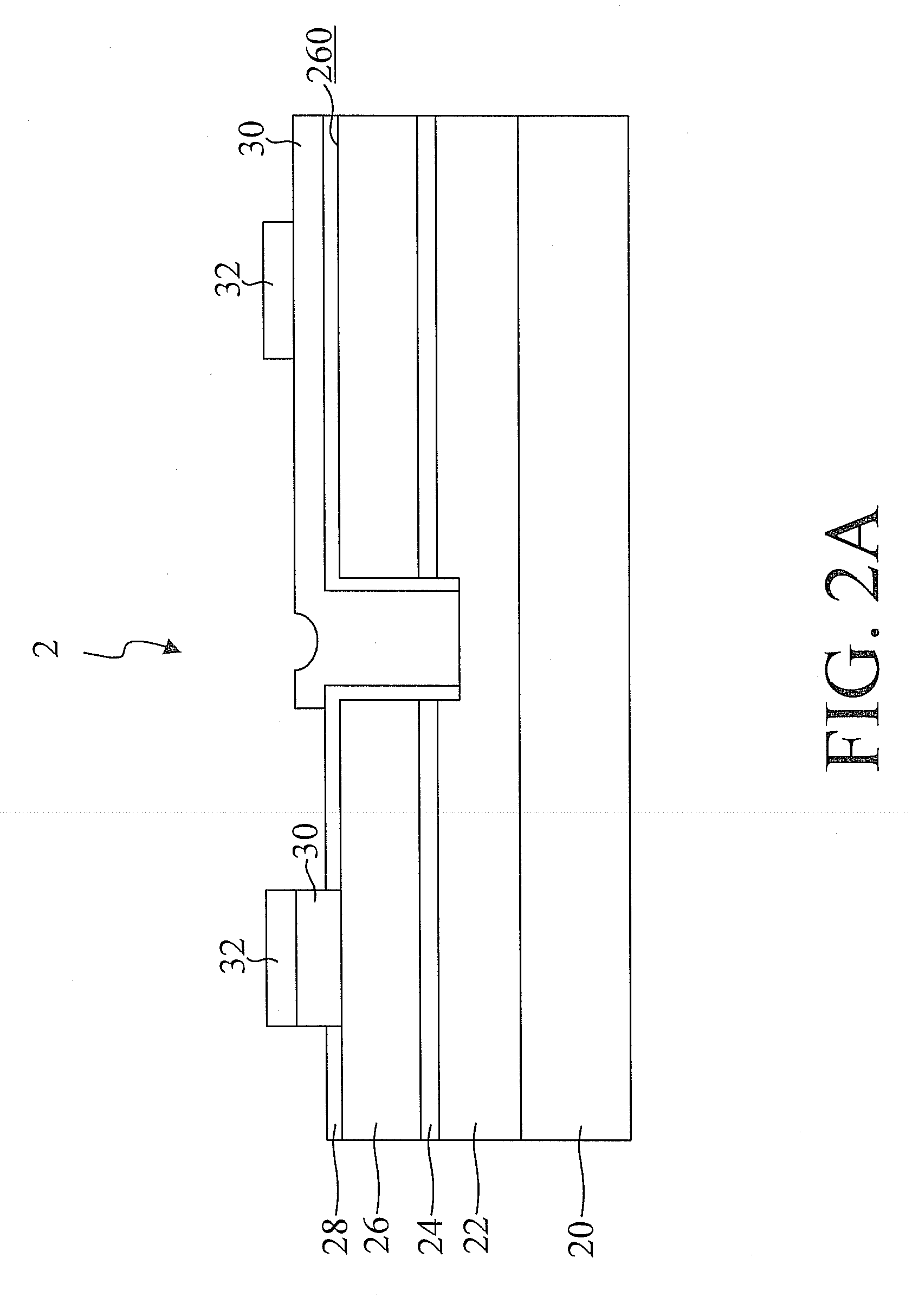

High power flip chip LED

InactiveUS7015512B2Increase powerIncrease light emitting areaSemiconductor/solid-state device detailsSolid-state devicesCurrent channelOhmic contact

A high power flip chip LED has an n-doped semiconductor layer formed on the sapphire substrate, with a plurality of first regions and a second region of intersecting lines for separating the first regions from each other. P-doped semiconductor layers are on the first regions of the n-doped semiconductor layer to form mesa structures. At least one pair of diagonal corners of the respective mesa structures are rounded inward to form first basins between adjacent inward-rounded corners. First metal layers are on the mesa structures in a same configuration. A second metal layer is on the second region of the n-doped semiconductor layer. First ohmic contacts are on the first metal layers. Second ohmic contacts are on the second metal layer in the first basins. The LED can prevent the current channeling to increase the luminous area while equalizing the current density area thereby generating high brightness light.

Owner:SAMSUNG ELECTRONICS CO LTD

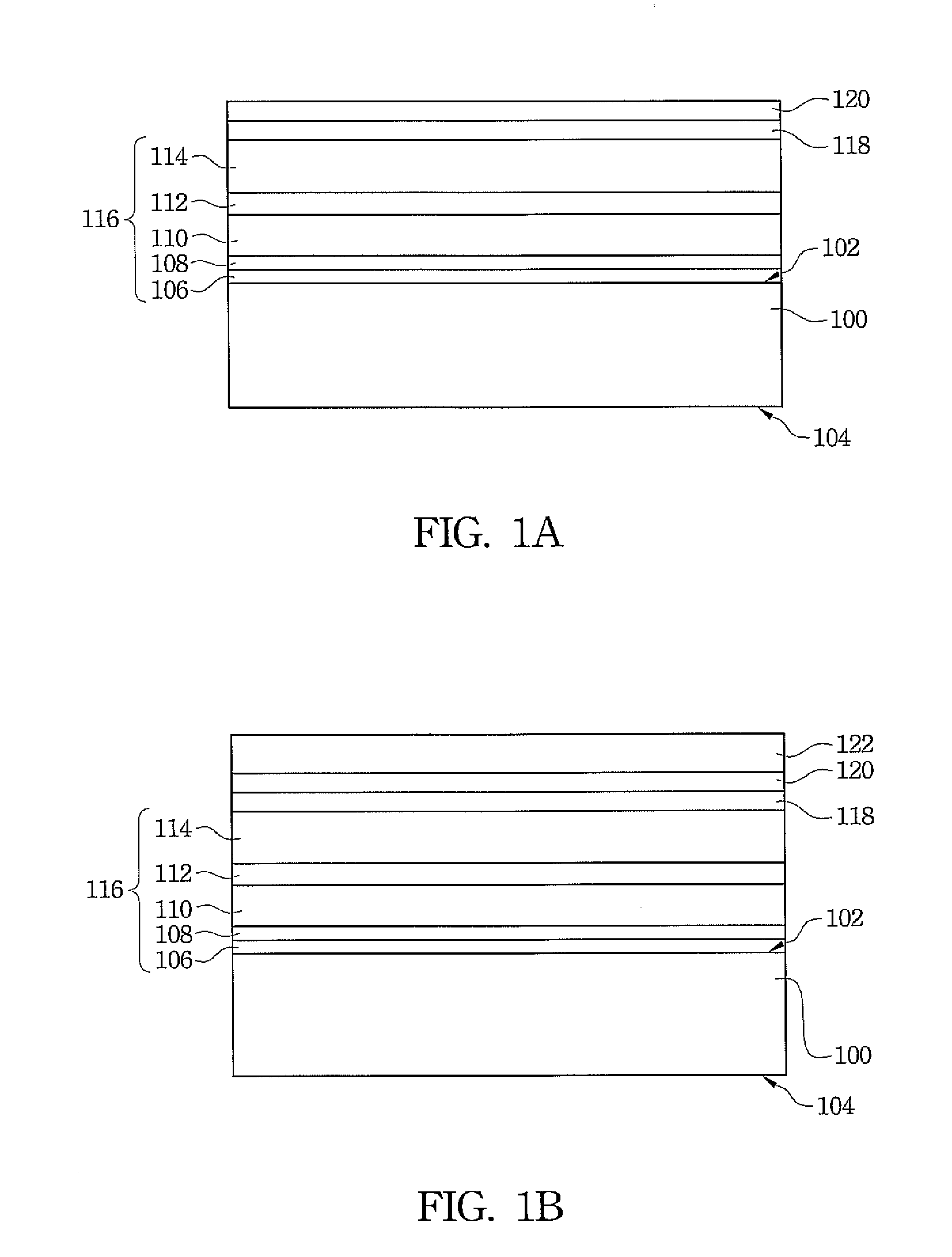

High-efficiency light-emitting element

ActiveUS7355210B2Reduce distanceImprove luminous efficiencySemiconductor laser structural detailsSolid-state devicesNitride semiconductorsPhysics

A high-efficiency light-emitting element includes a substrate, a first nitride semiconductor layer formed on the substrate, a nitride light-emitting layer formed on the first nitride semiconductor layer, and a second nitride semiconductor layer formed on the nitride light-emitting layer including a plurality of hexagonal-pyramid cavities on the surface of the second nitride semiconductor layer opposite to the nitride light-emitting layer.

Owner:EPISTAR CORP

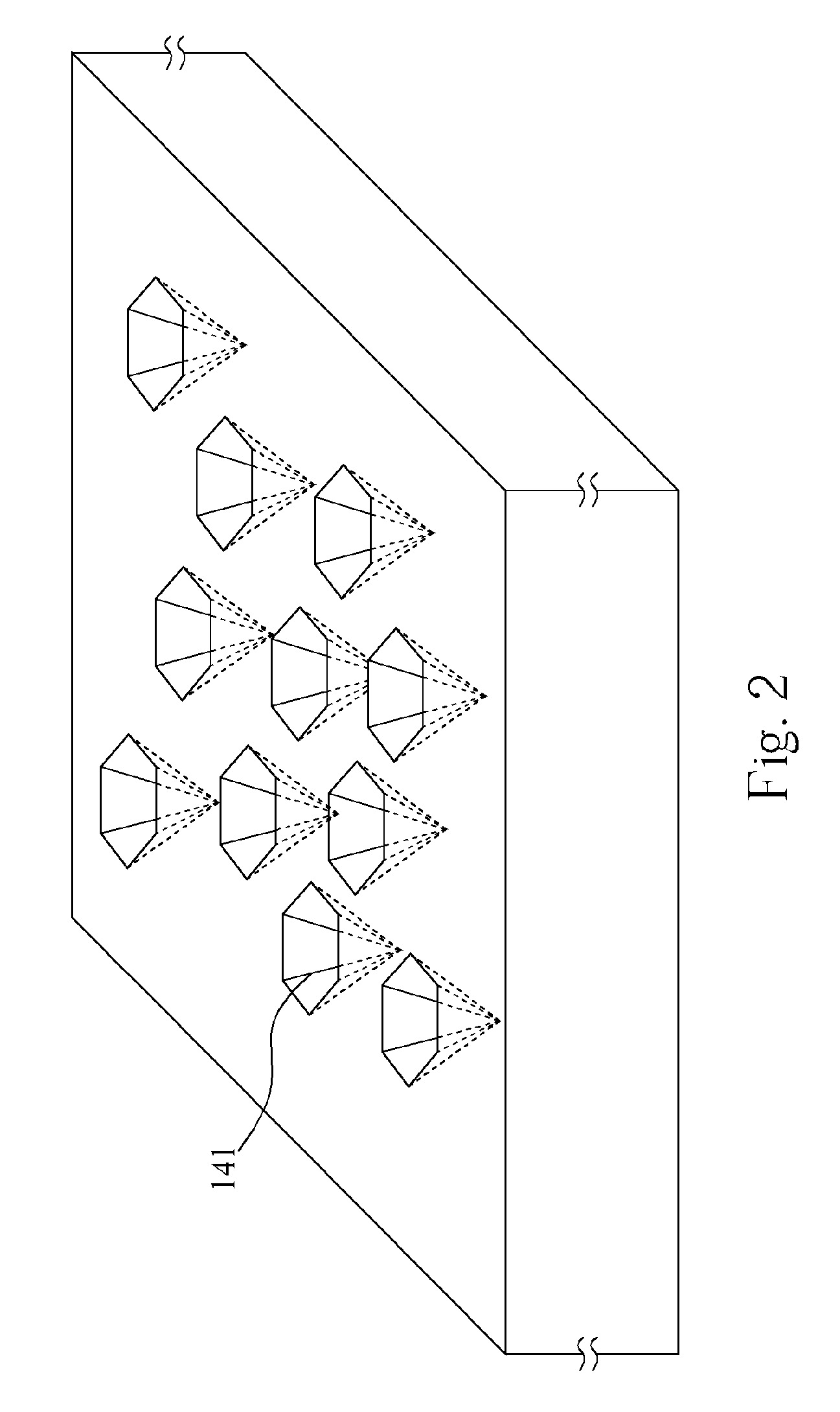

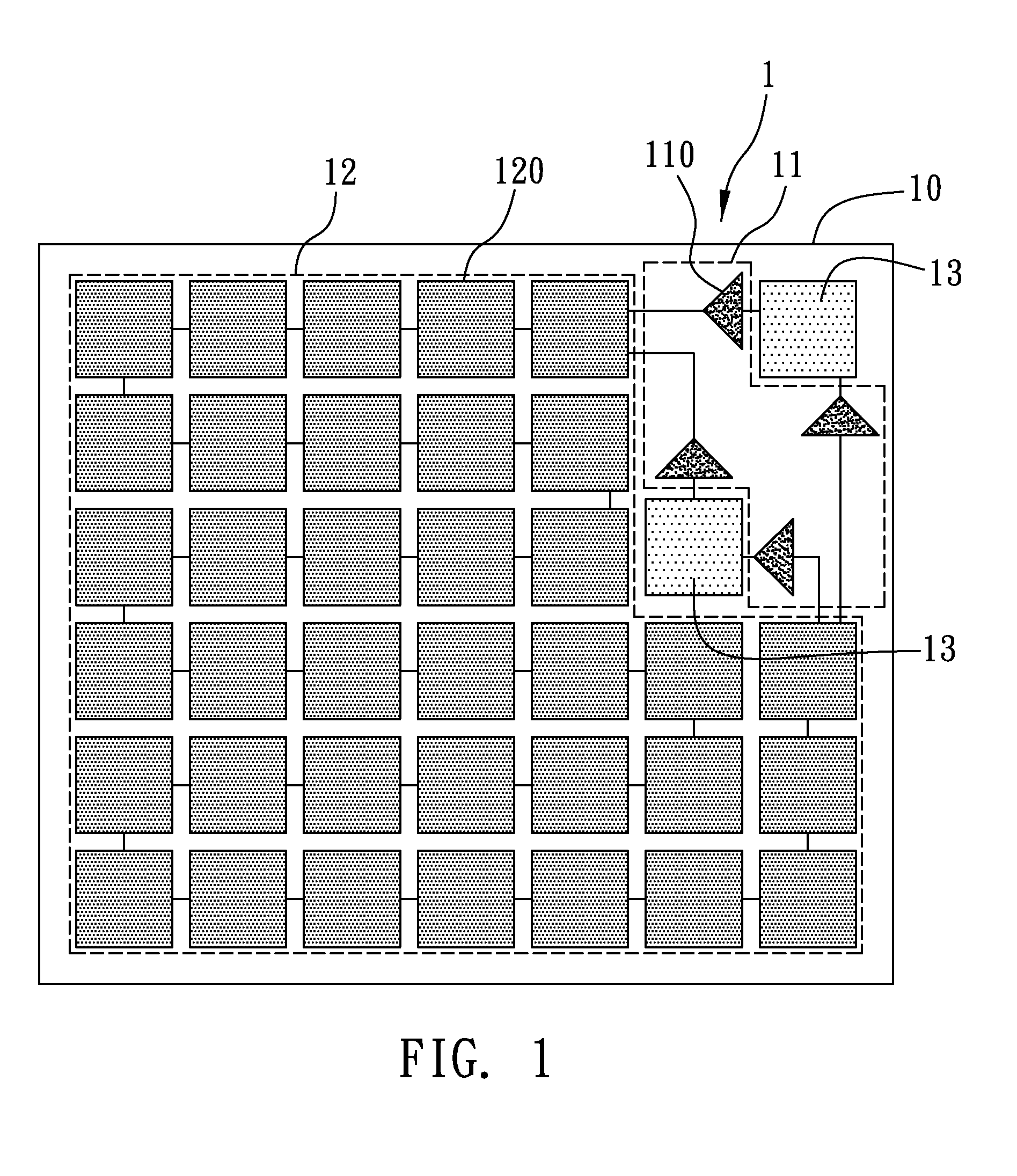

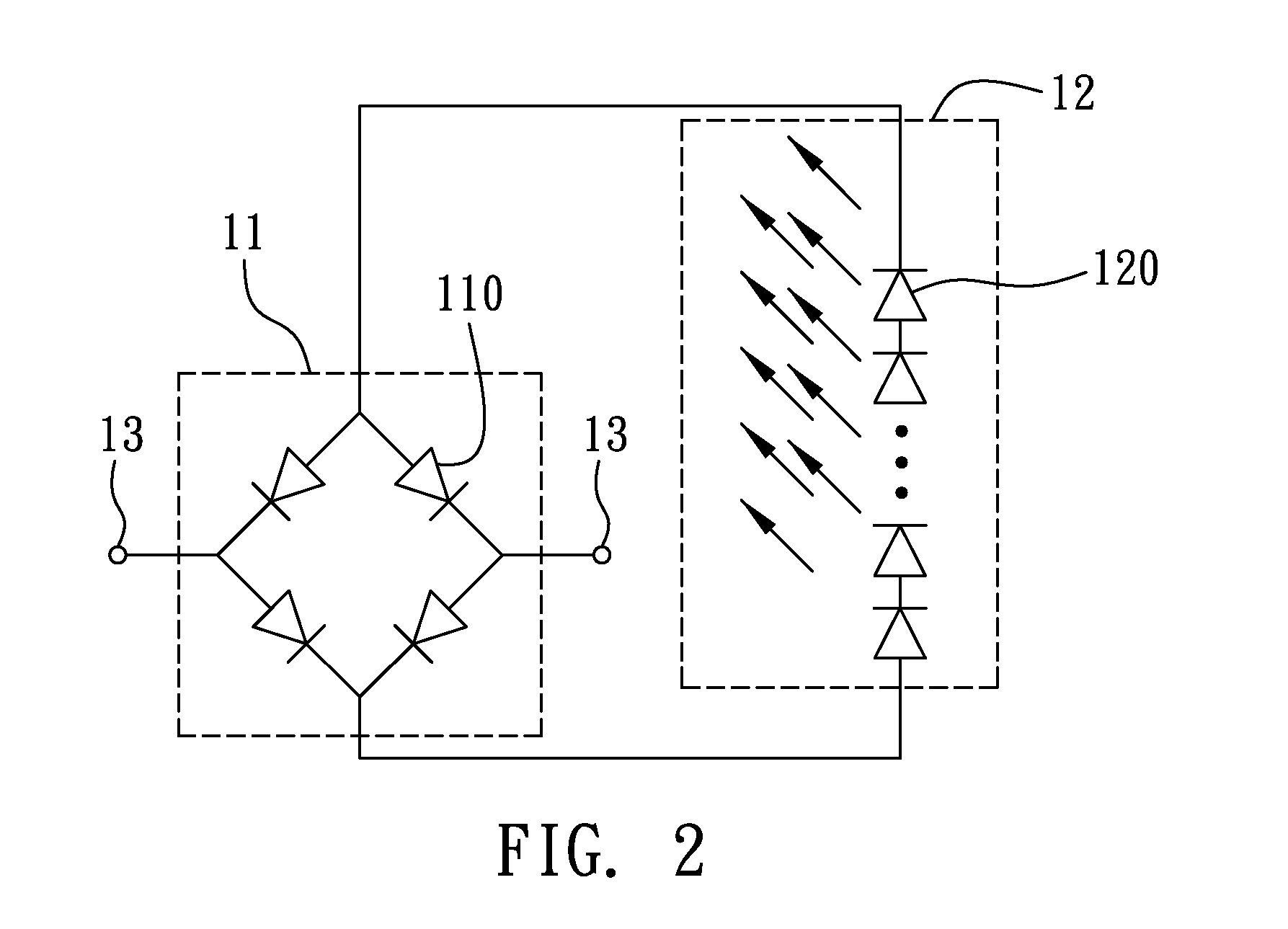

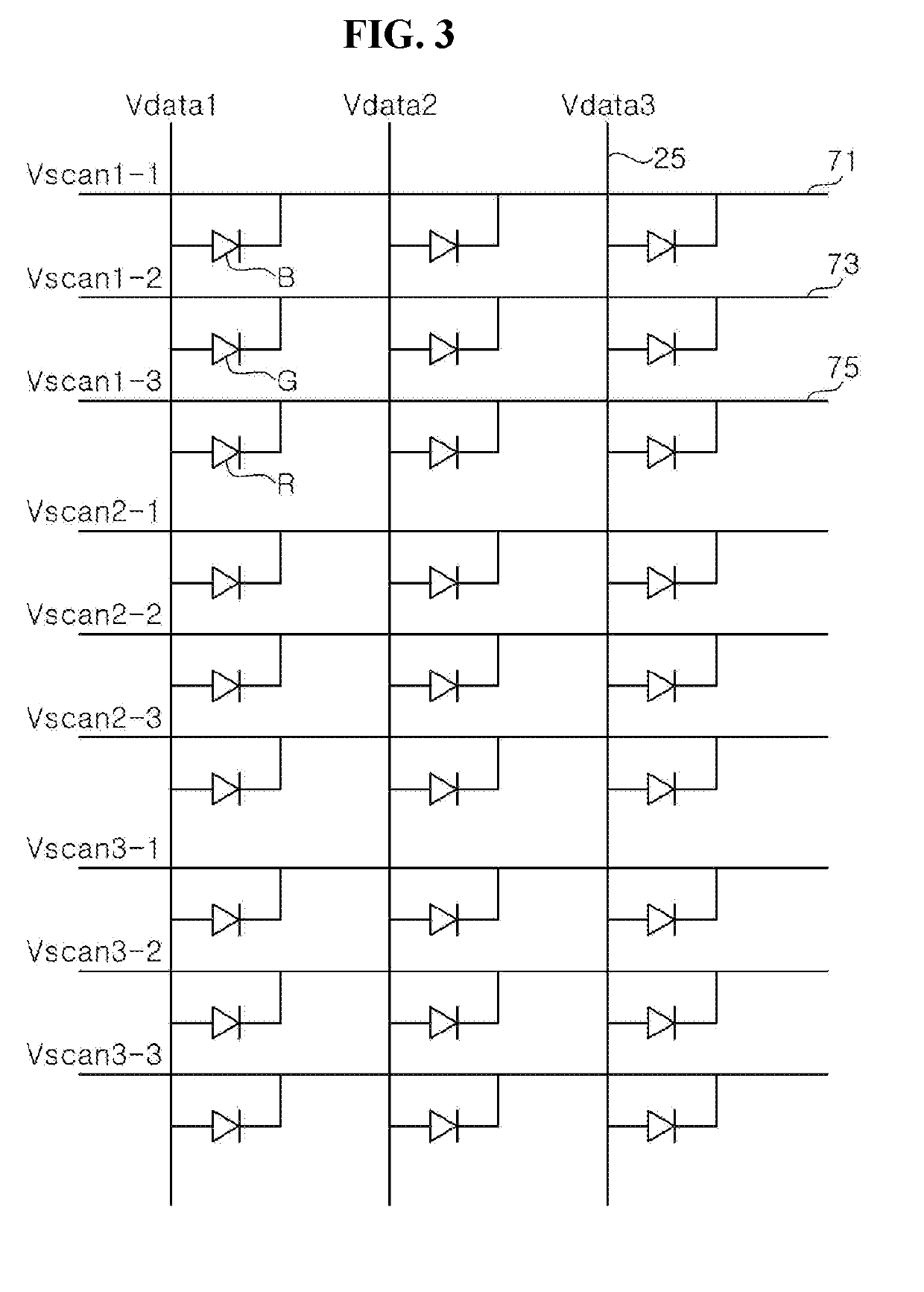

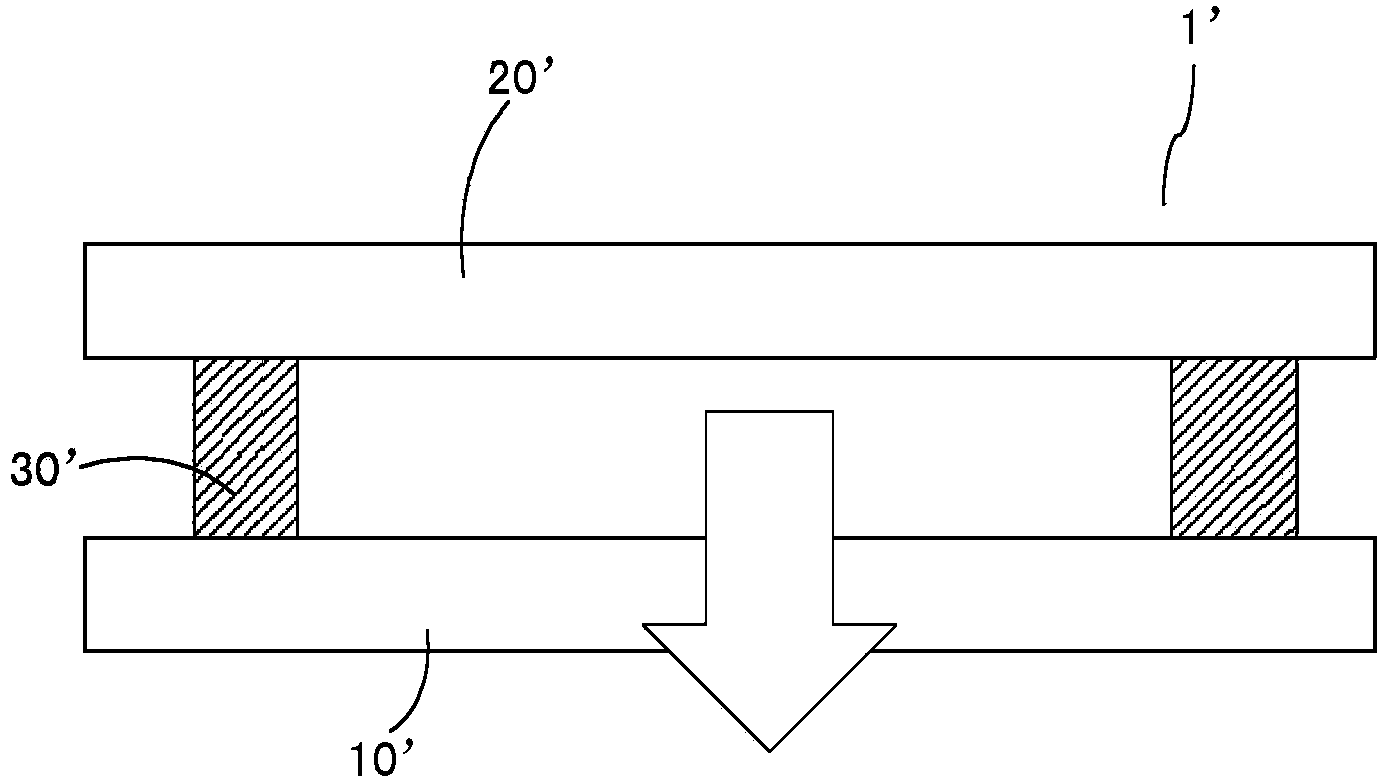

AC Light Emitting Assembly and AC Light Emitting Device

ActiveUS20070131942A1Reduce the numberReduce power consumptionElectroluminescent light sourcesSolid-state devicesEngineeringAlternating current

An alternating current (AC) light emitting assembly and an AC light emitting device are disclosed. The AC light emitting assembly includes a substrate; a rectifier unit comprising a plurality of rectifier components arranged in a Wheatstone Bridge, for rectifying an AC signal into a direct current (DC) signal, each of the rectifier components having a high breakdown voltage and a low forward voltage; a light emitting unit electrically connected to the rectifier unit and comprising a plurality of light emitting components formed on the substrate, for emitting light when receiving the DC signal outputted by the rectifier unit; and two conductive electrodes electrically connected to the rectifier unit for receiving and transmitting the AC signal to the rectifier unit. The AC light emitting device includes two stacked and electrically connected AC light emitting assemblies.

Owner:EPISTAR CORP

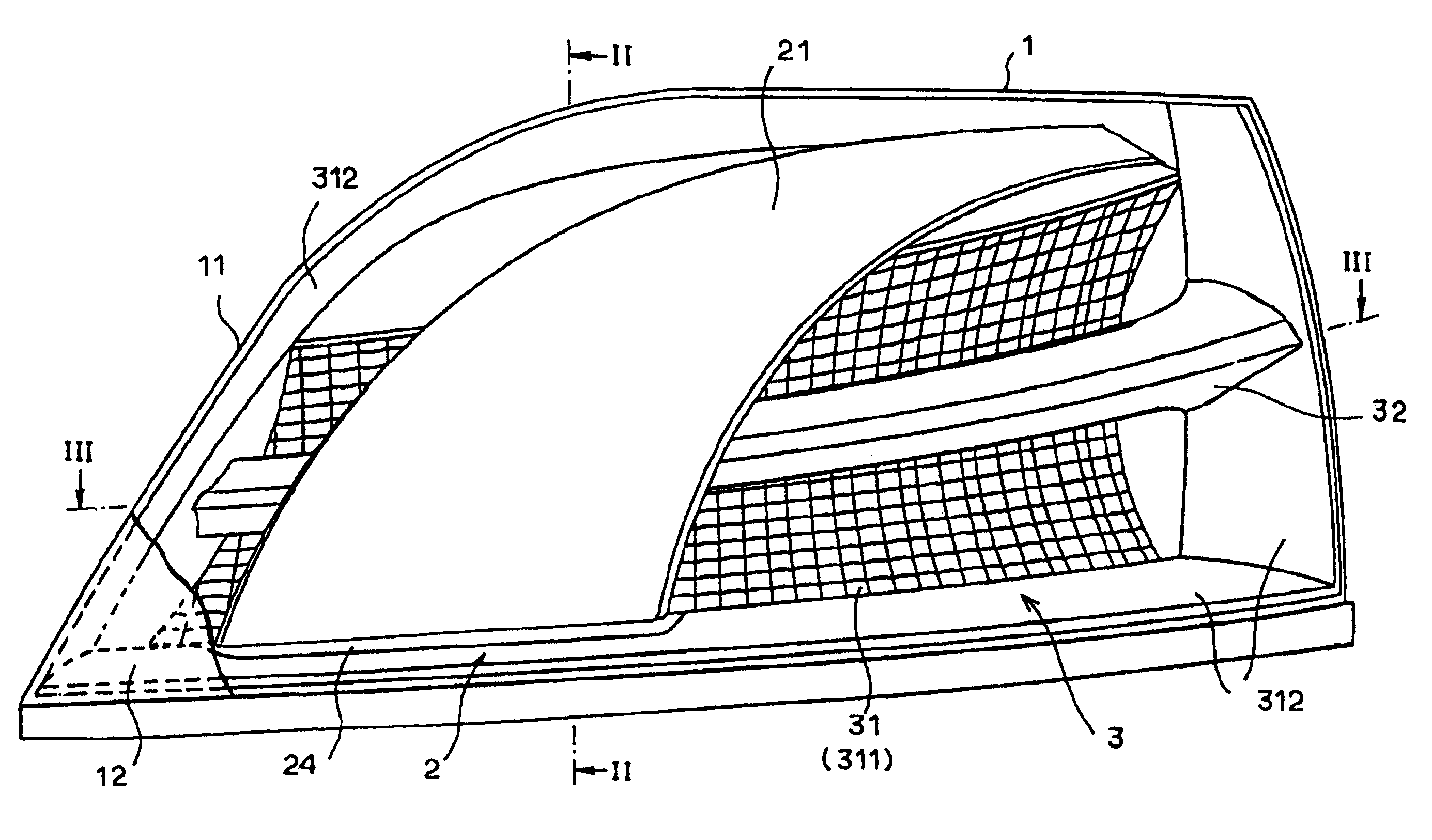

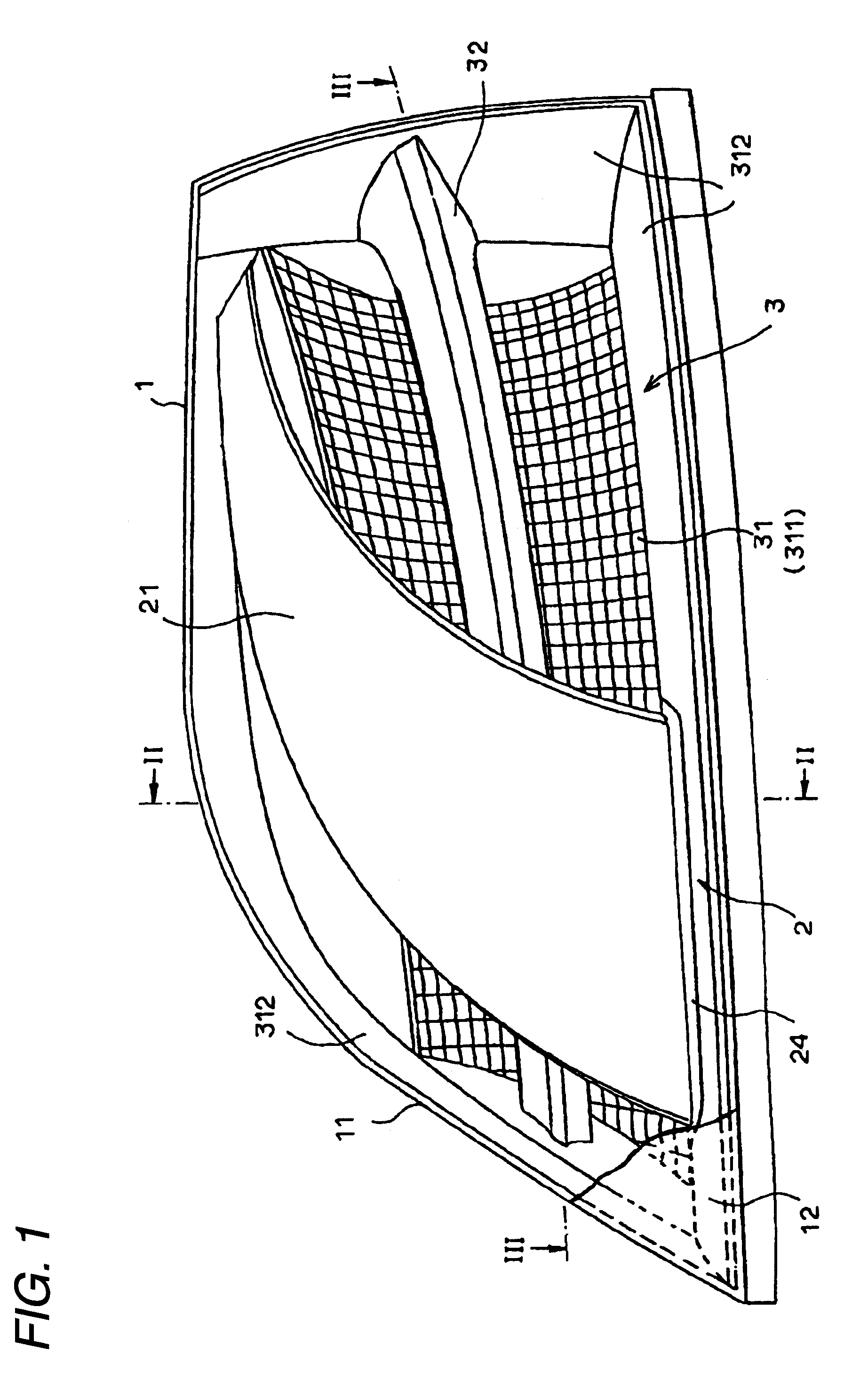

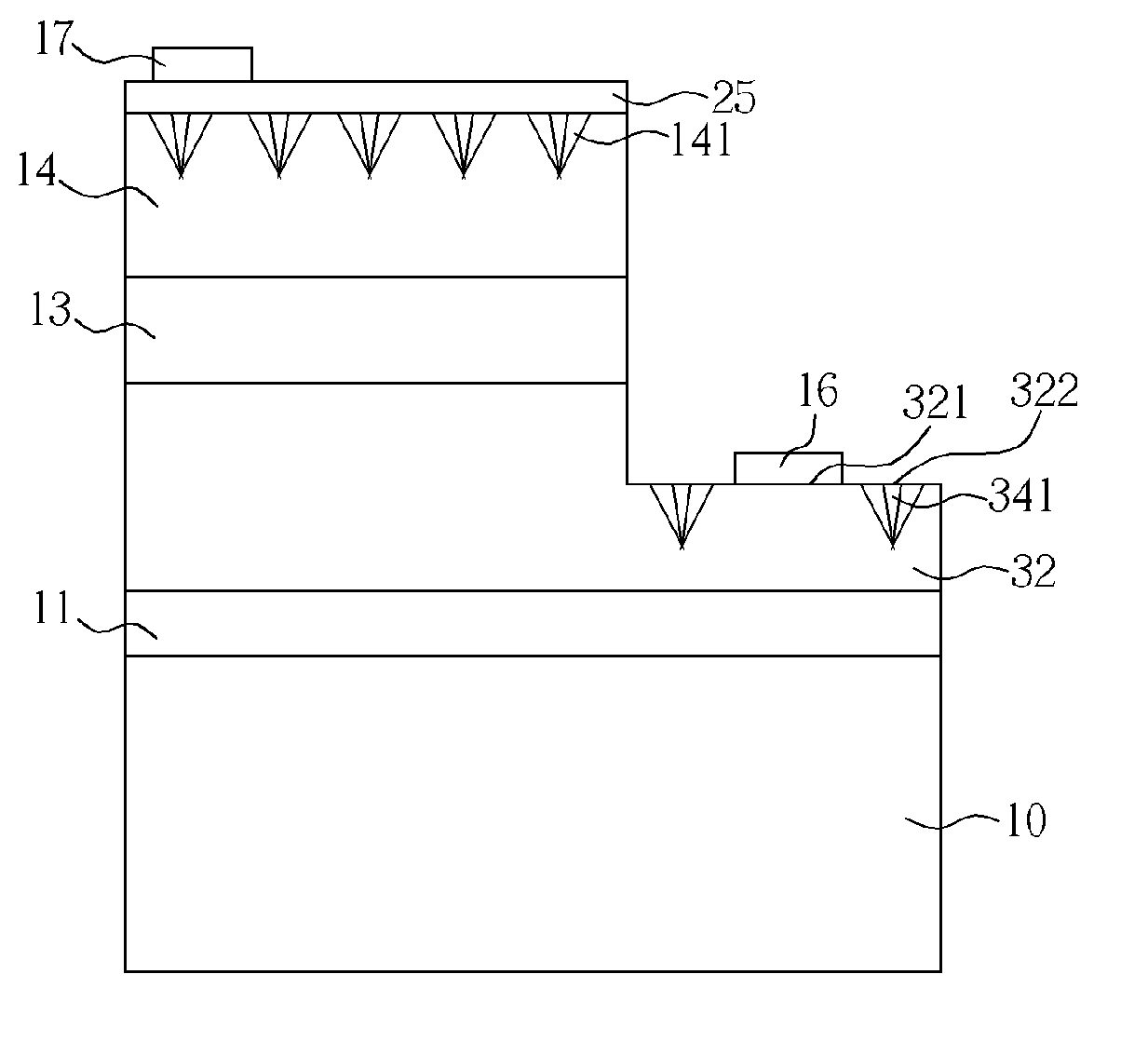

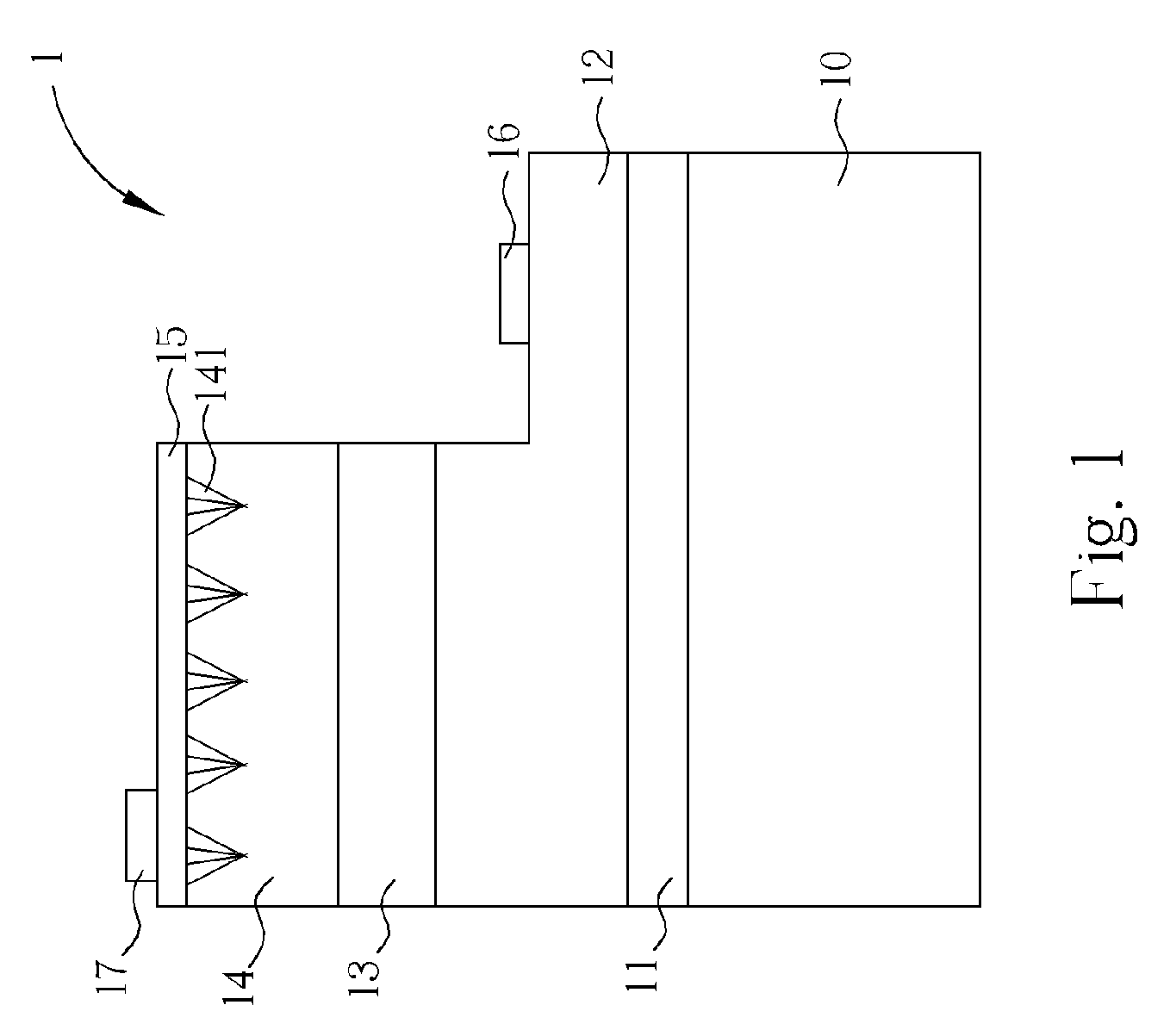

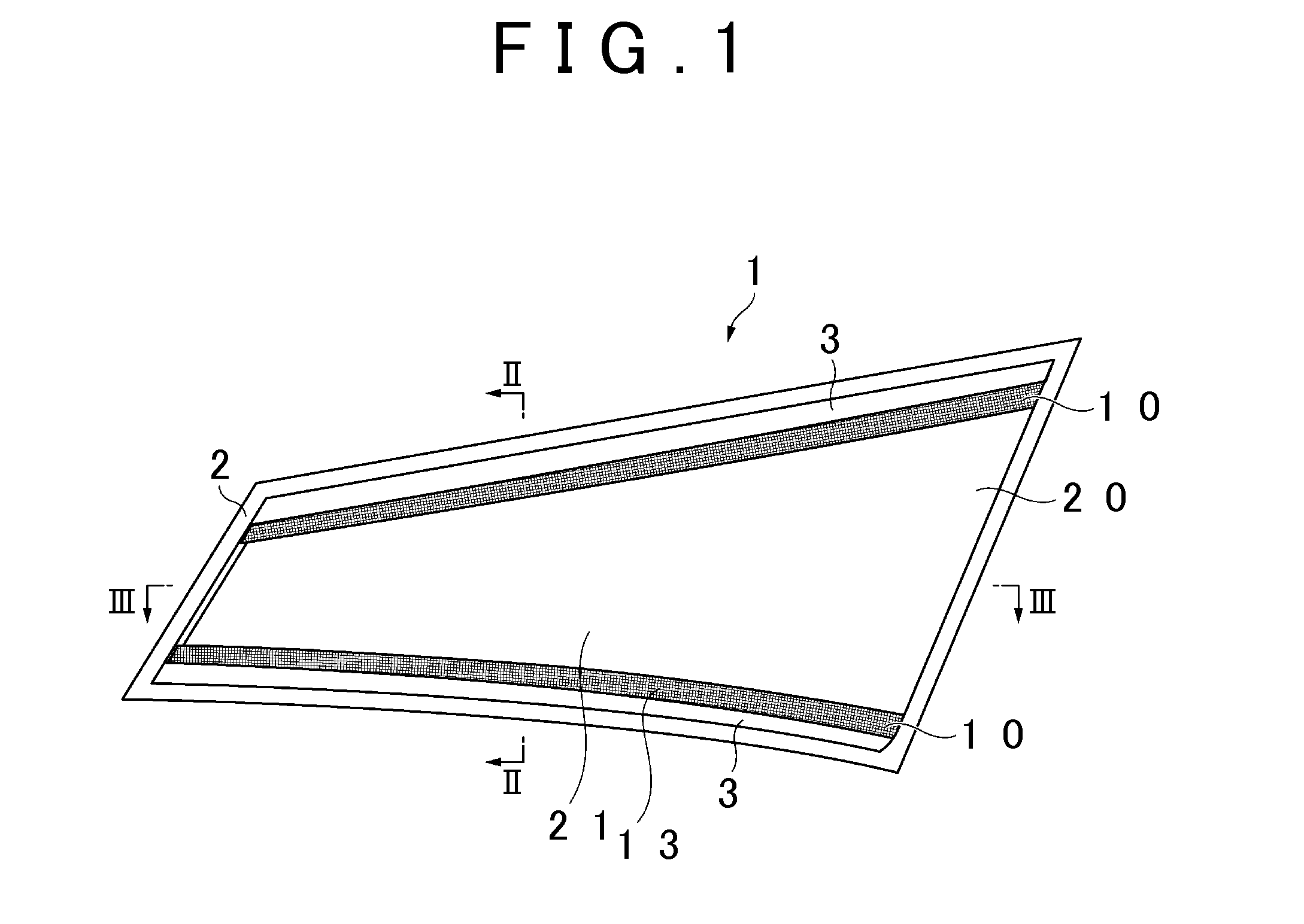

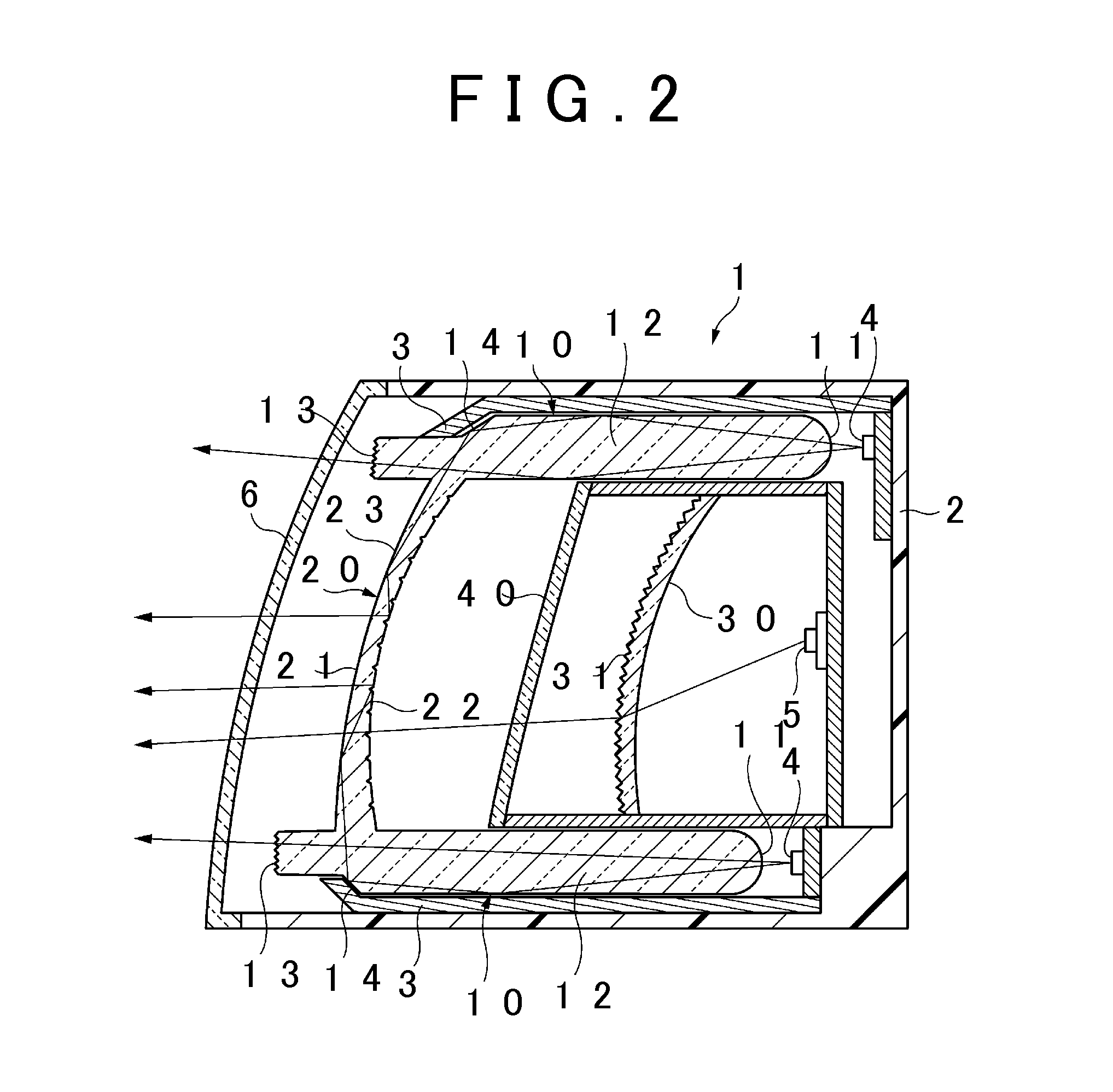

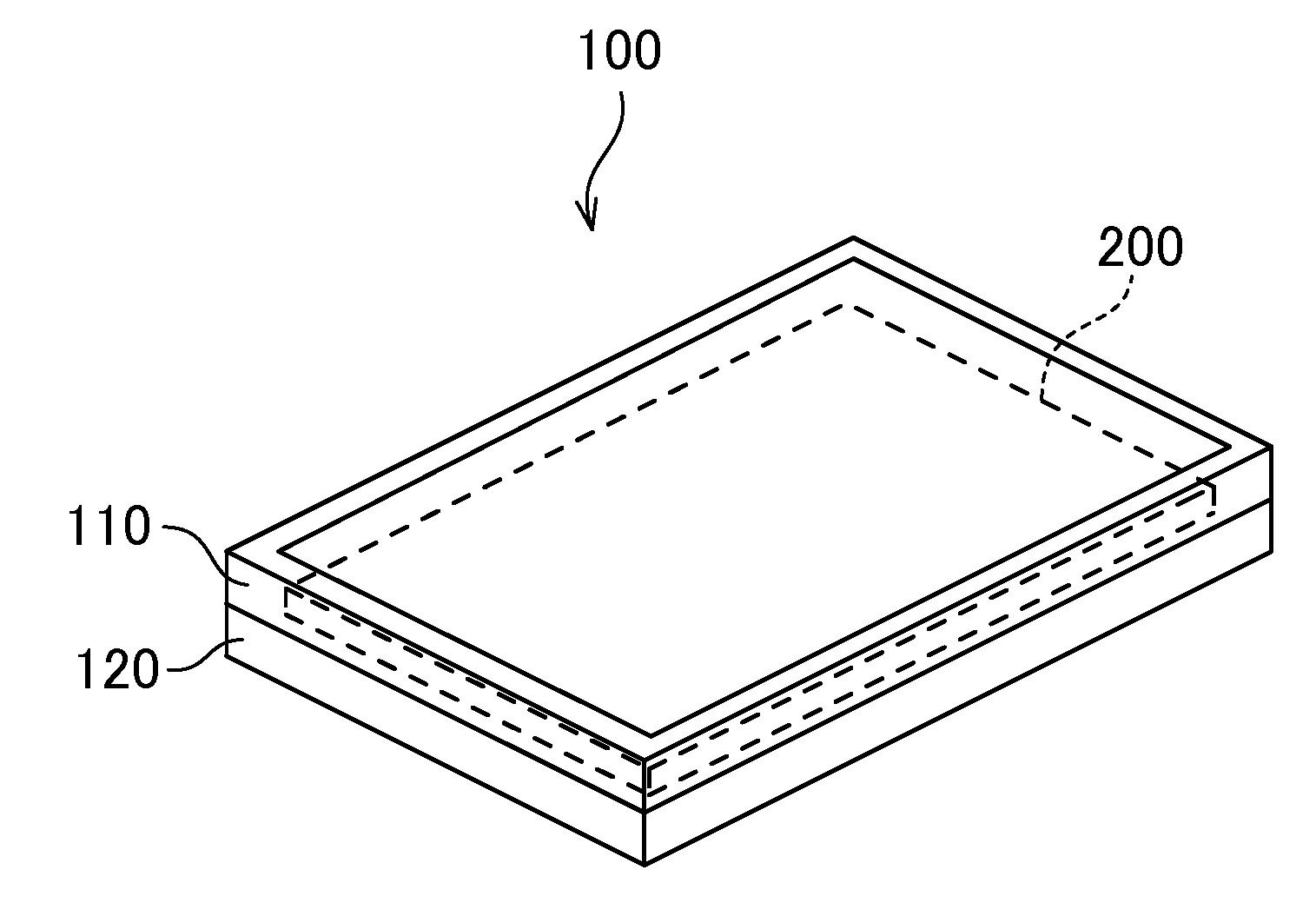

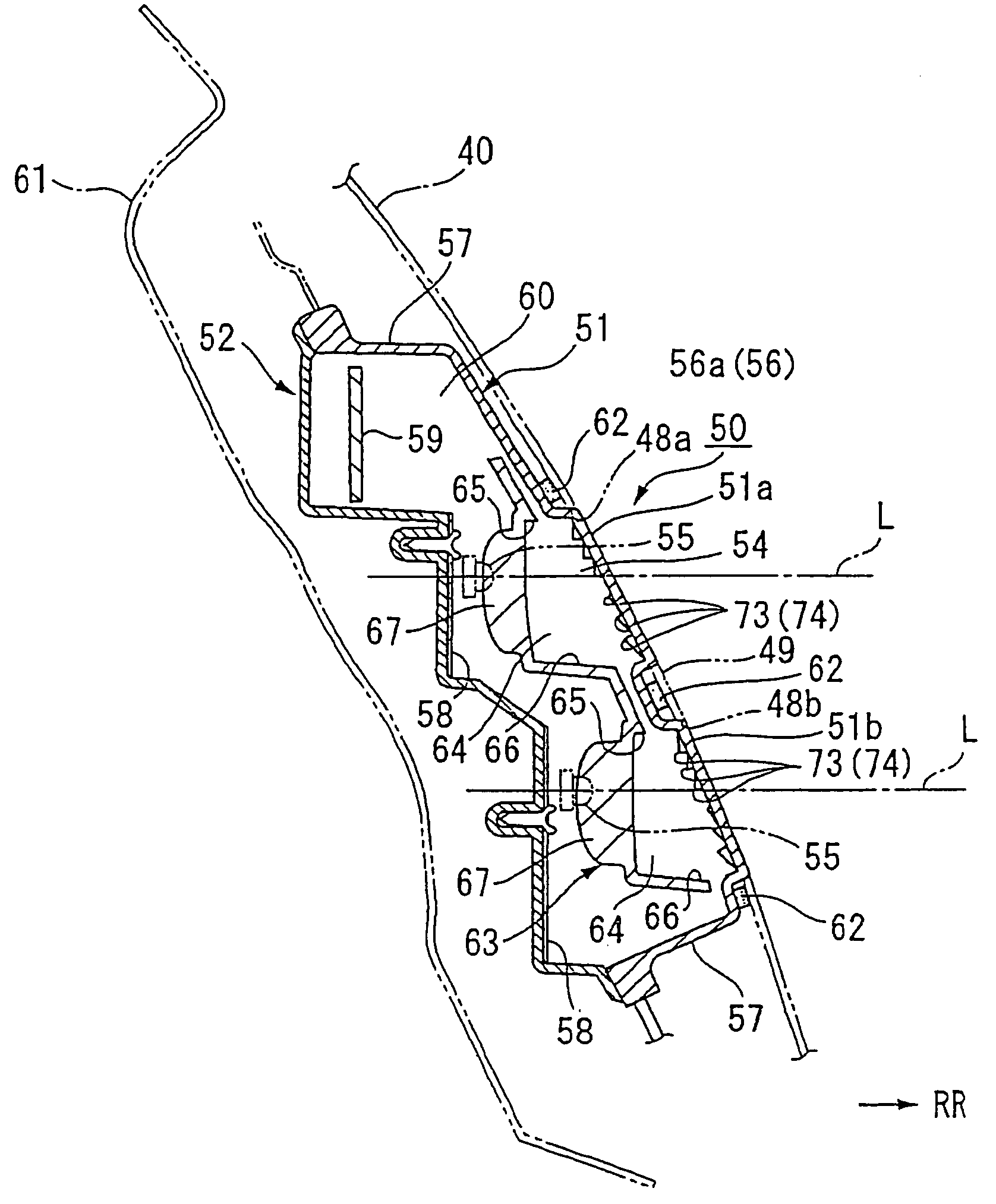

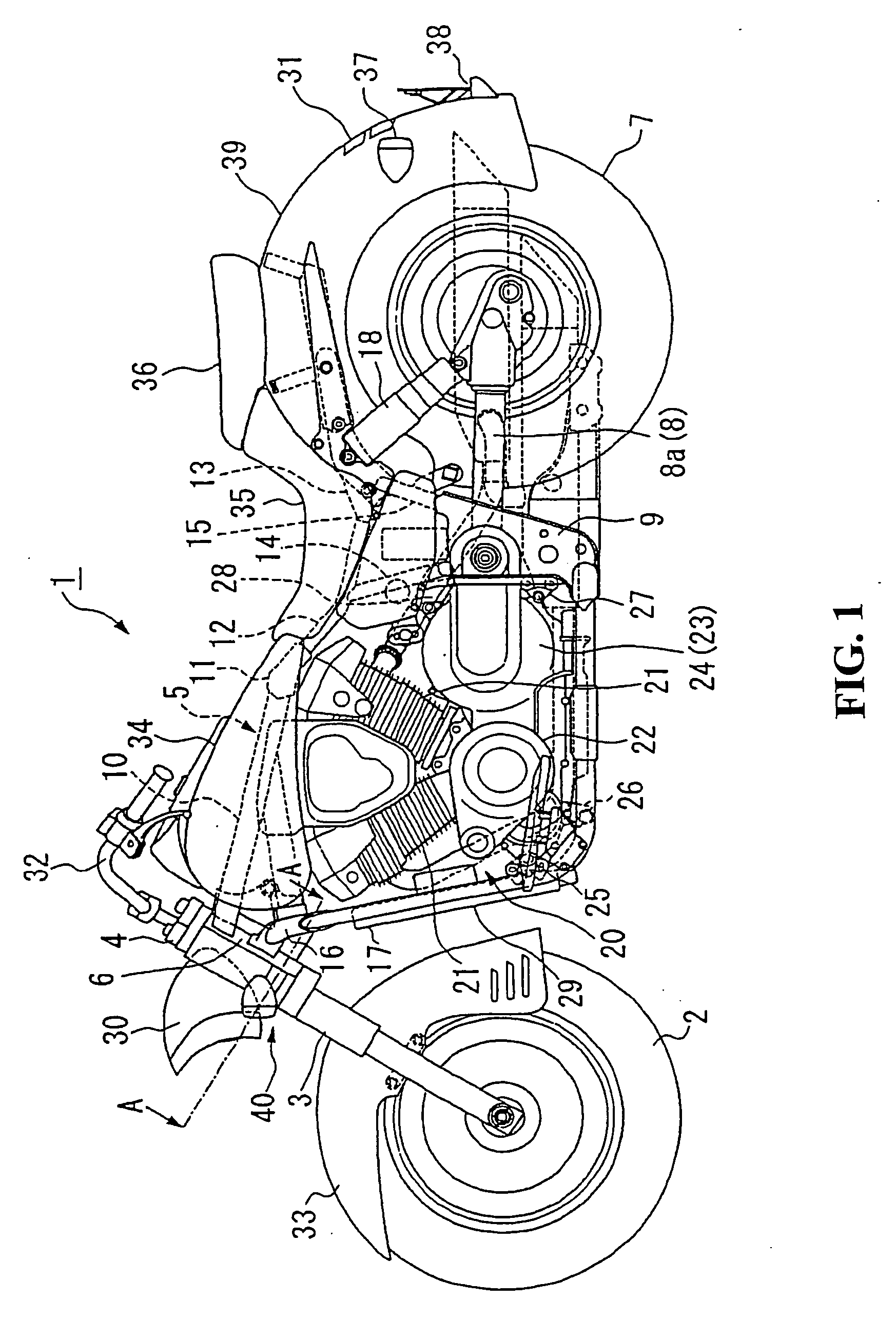

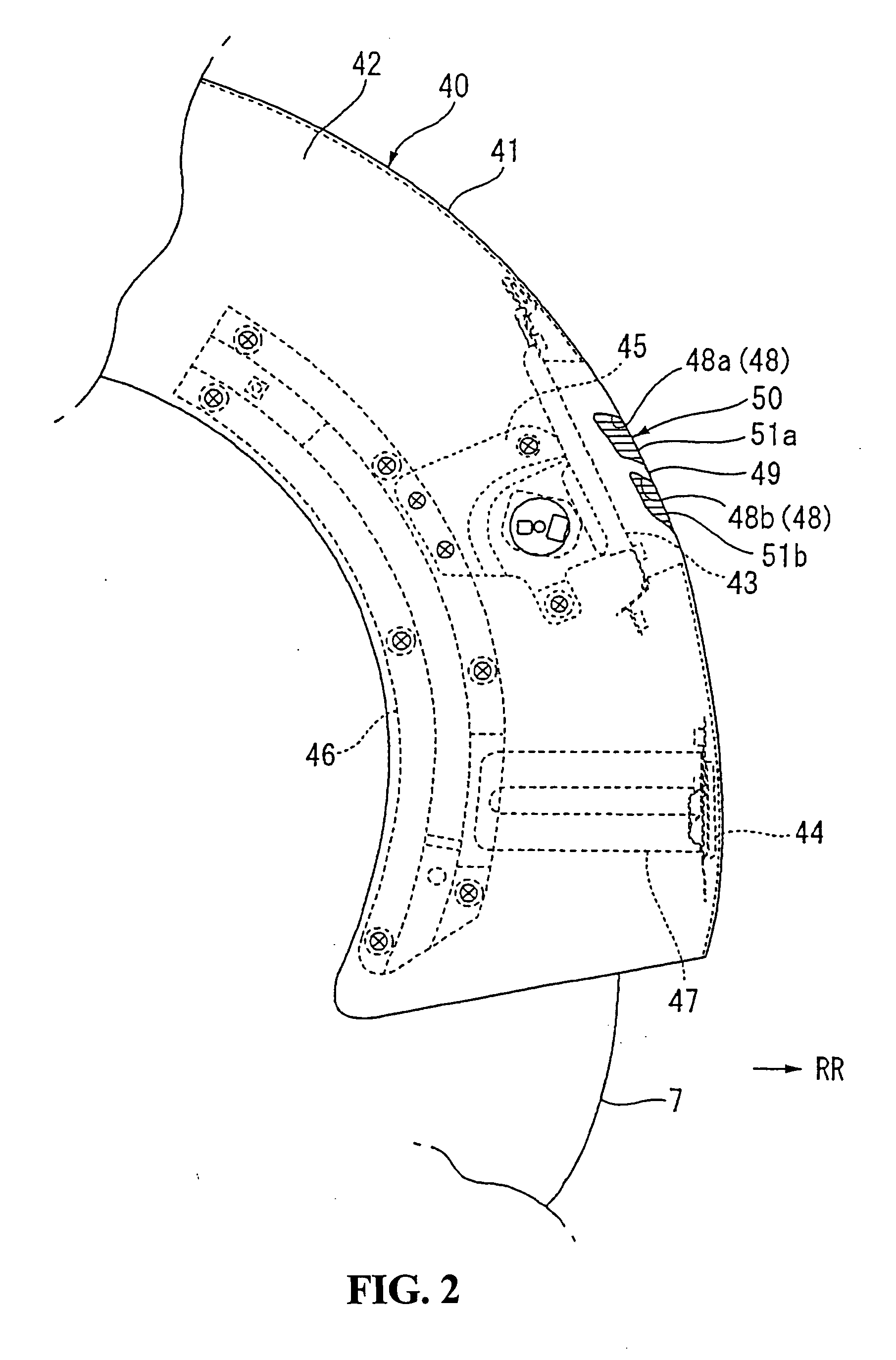

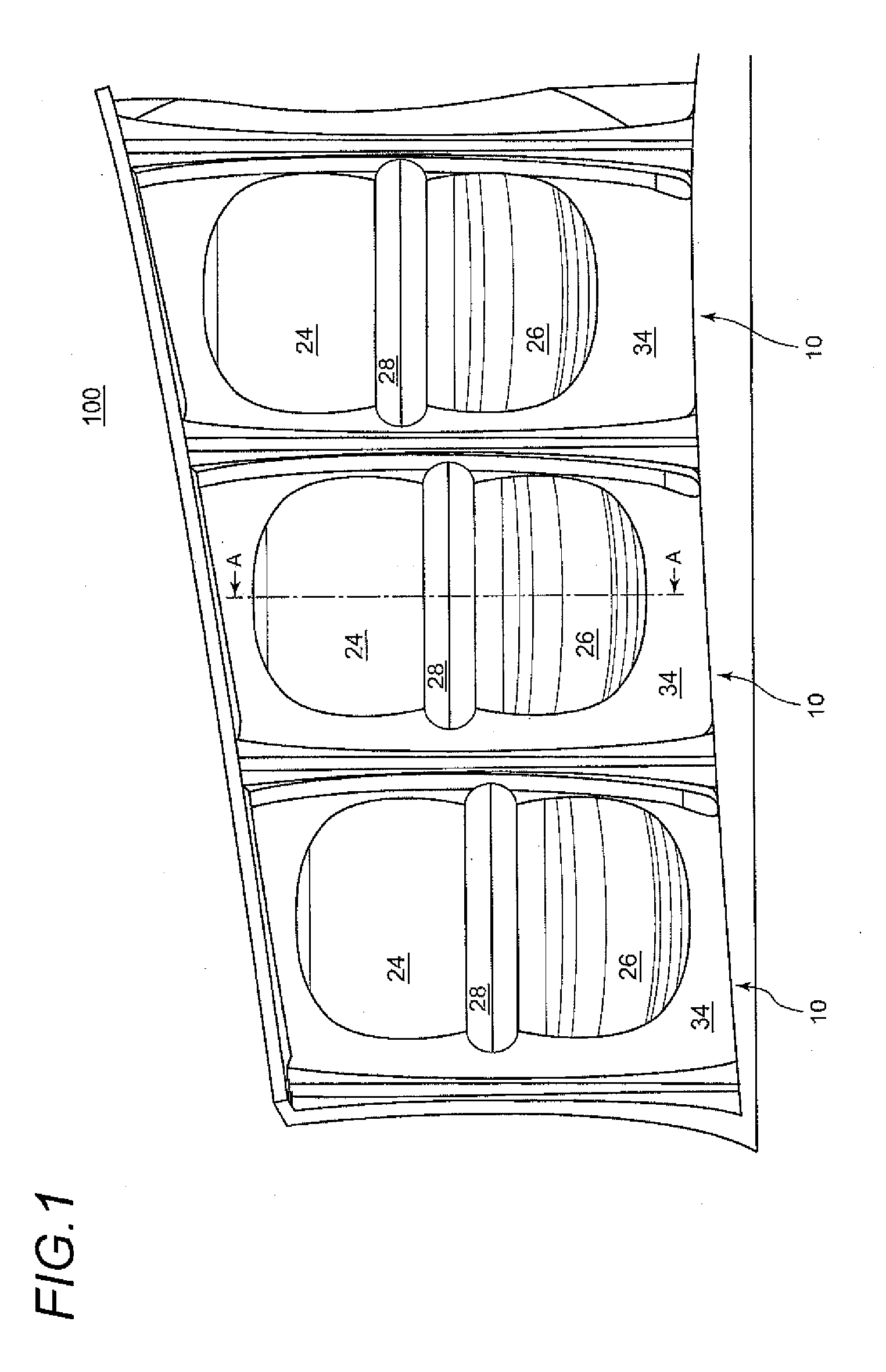

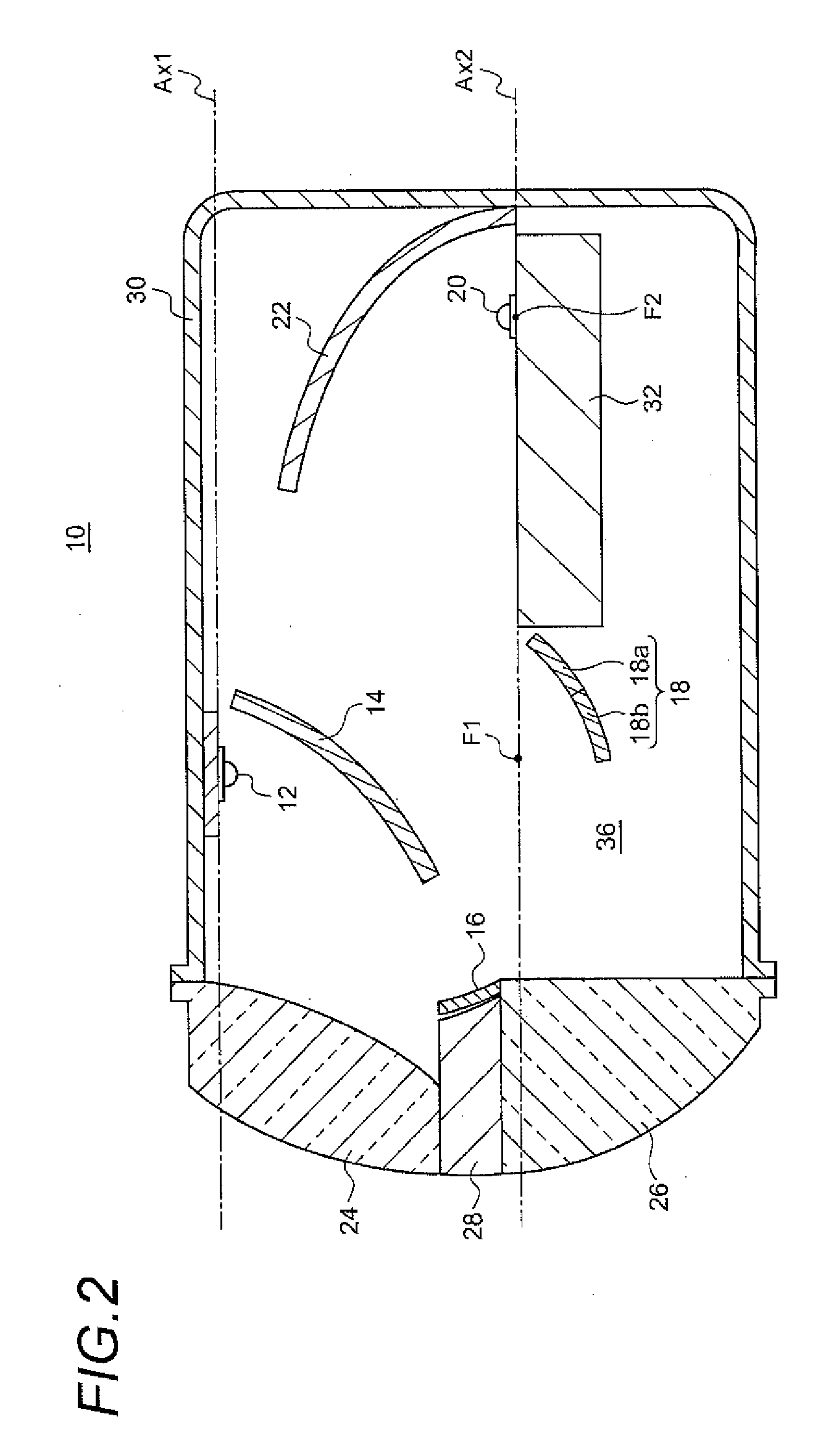

Vehicular lamp

ActiveUS20150277027A1Large surface areaGood visibilityMechanical apparatusVehicle headlampsPhysicsLight guide

A vehicular lamp includes a light emitter, a first light guide, and a second light guide. The first light guide has a first incident surface, a first light guiding portion that guides the entering light, a first light emission surface that emits light guided by the first light guiding portion, and a first reflecting surface that reflects the light guided by the first light guiding portion in a direction toward the second light guide. The second light guide has a second light emission surface that emits light that enters the second light guide after being reflected by the first reflecting surface, and a second reflecting surface that reflects the light that enters the second light guide after being reflected by the first reflecting surface toward the second light emission surface.

Owner:KOITO MFG CO LTD

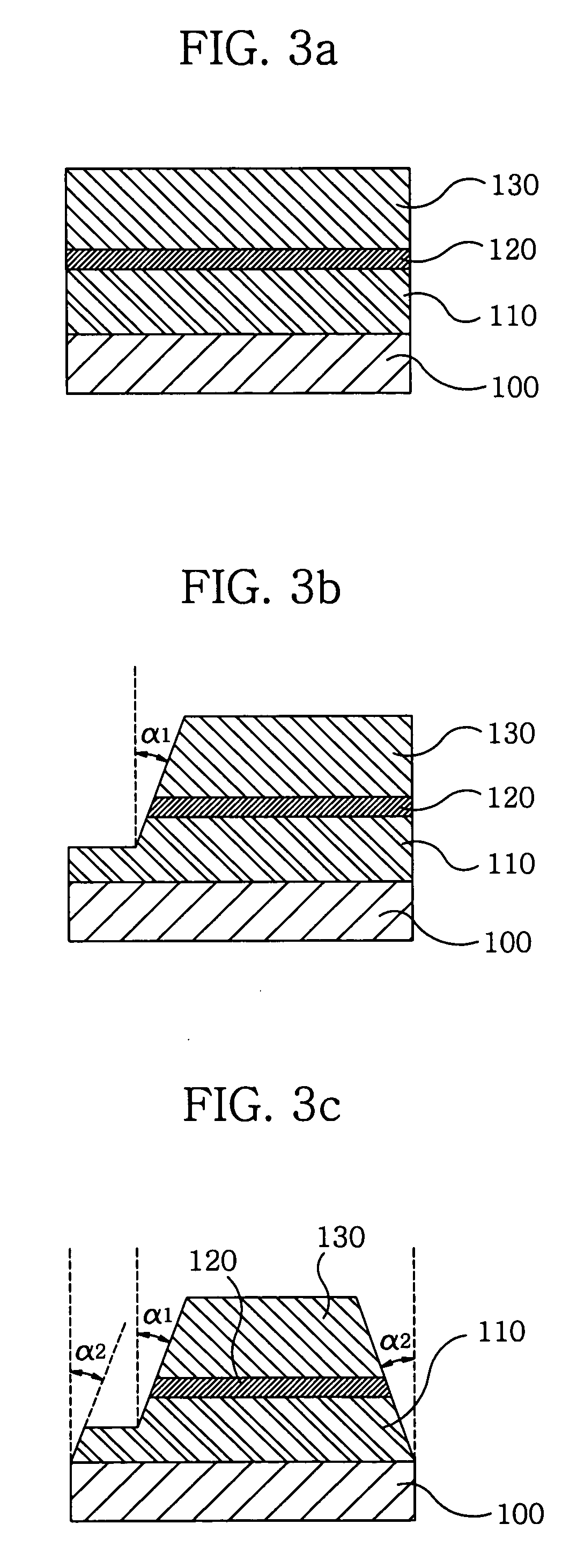

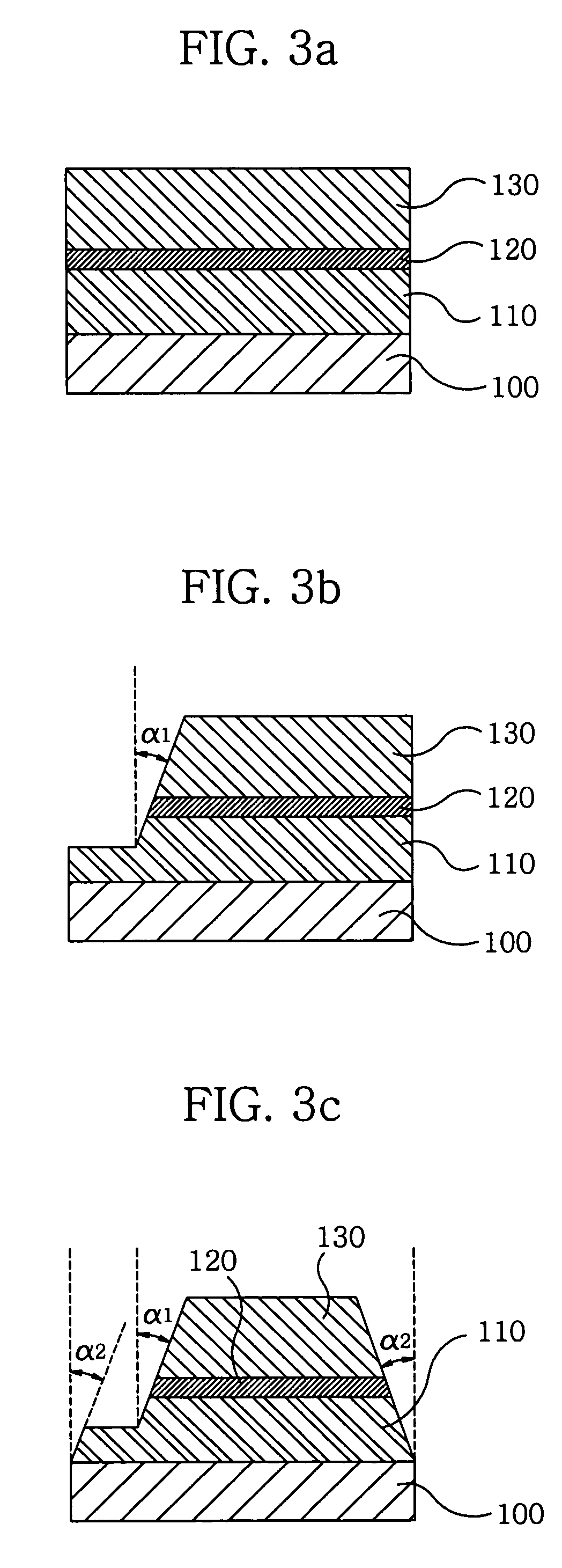

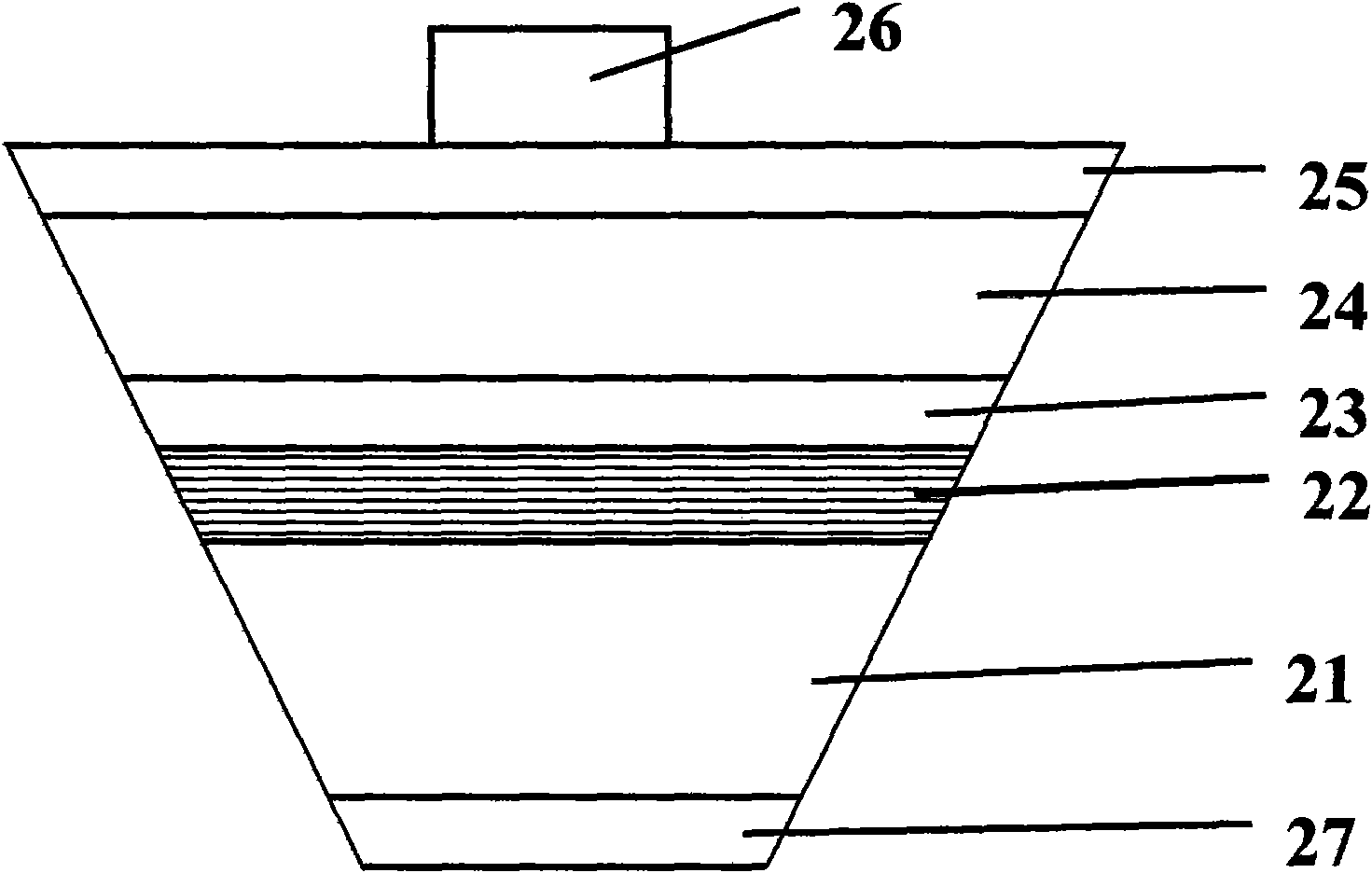

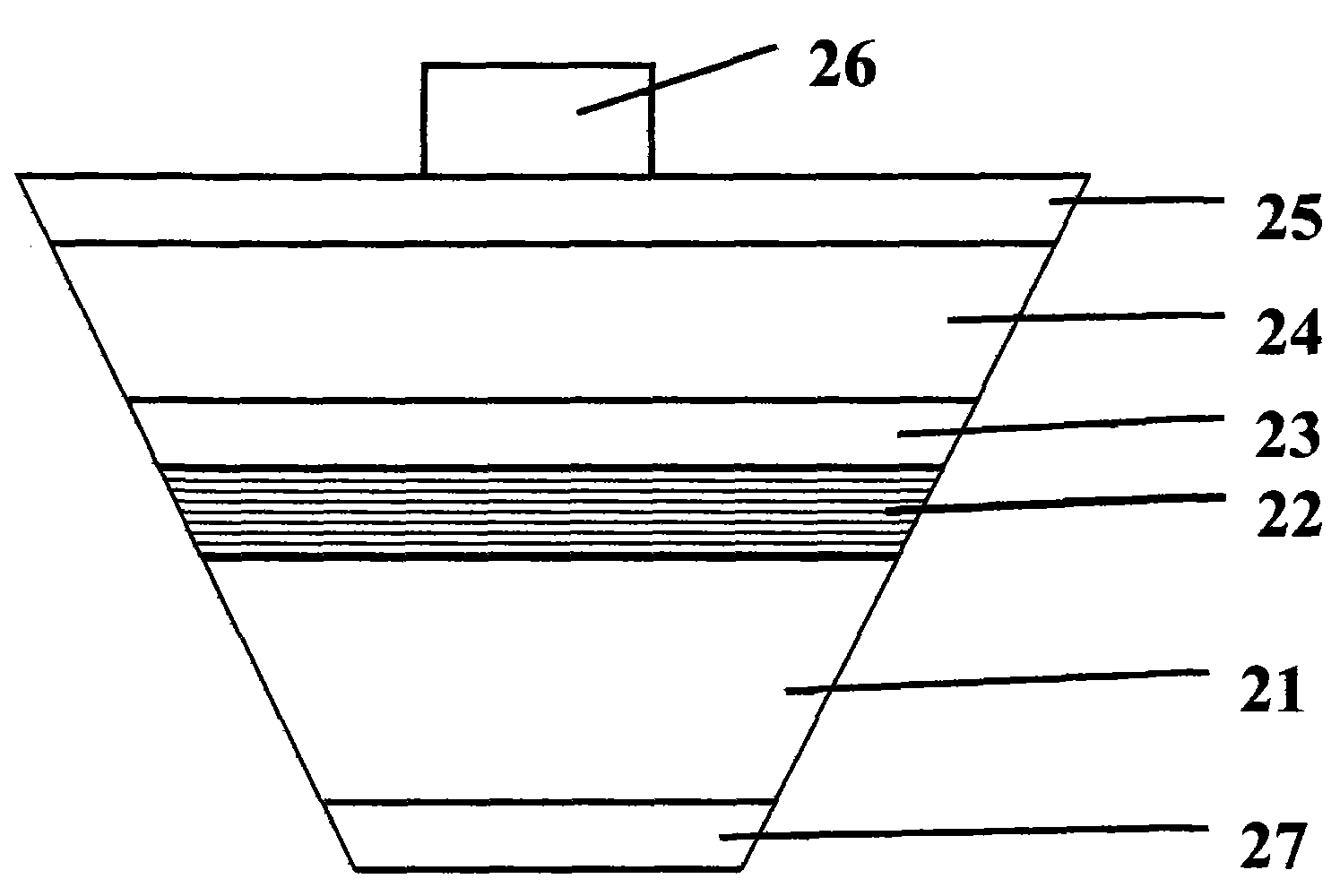

High output light emitting diode and method for fabricating the same

ActiveUS20060145174A1Improve light outputIncrease productionSemiconductor devicesLight-emitting diodeSurface reflection

A high output light emitting diode (LED) and a method for fabricating the LED is disclosed. The LED includes a sidewall or surface that is inclined. A reflective film is formed on the inclined sidewall or surface to allow light to reflect from the reflective film and to emit the light upward or in a favorable direction with respect to the device, thereby being configured and enabled to improve a light output of the LED and dispense with an additional passivation process.

Owner:LG ELECTRONICS INC

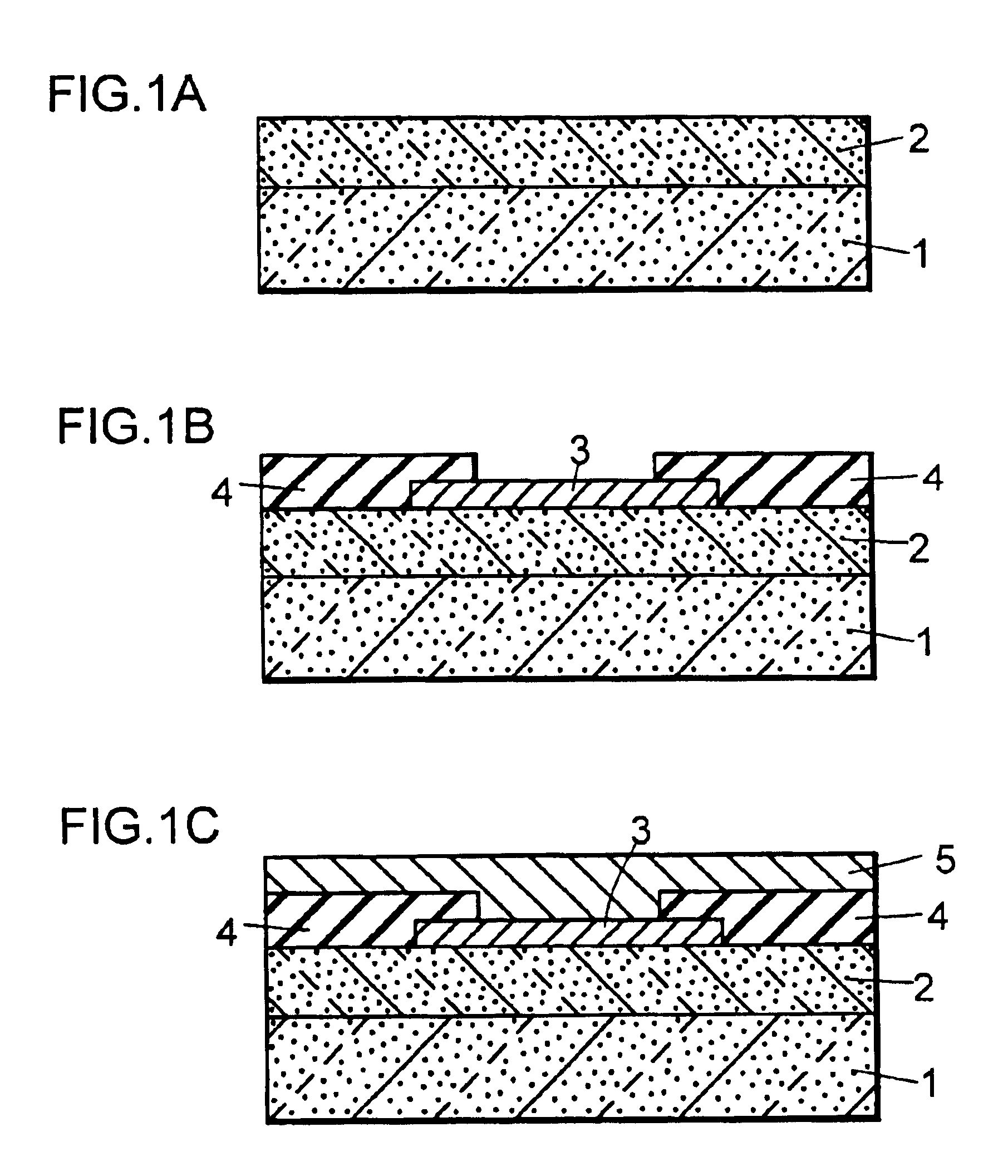

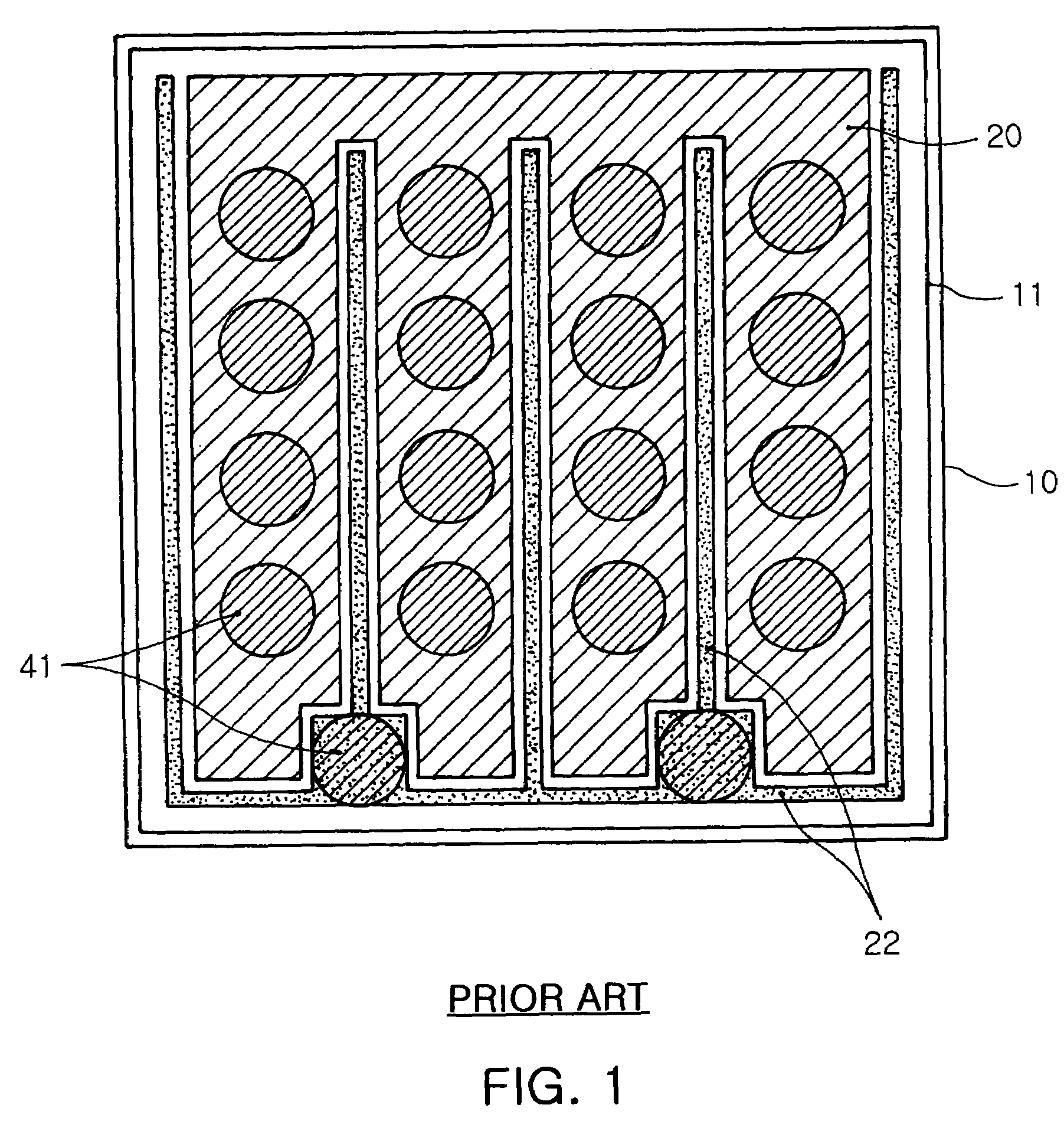

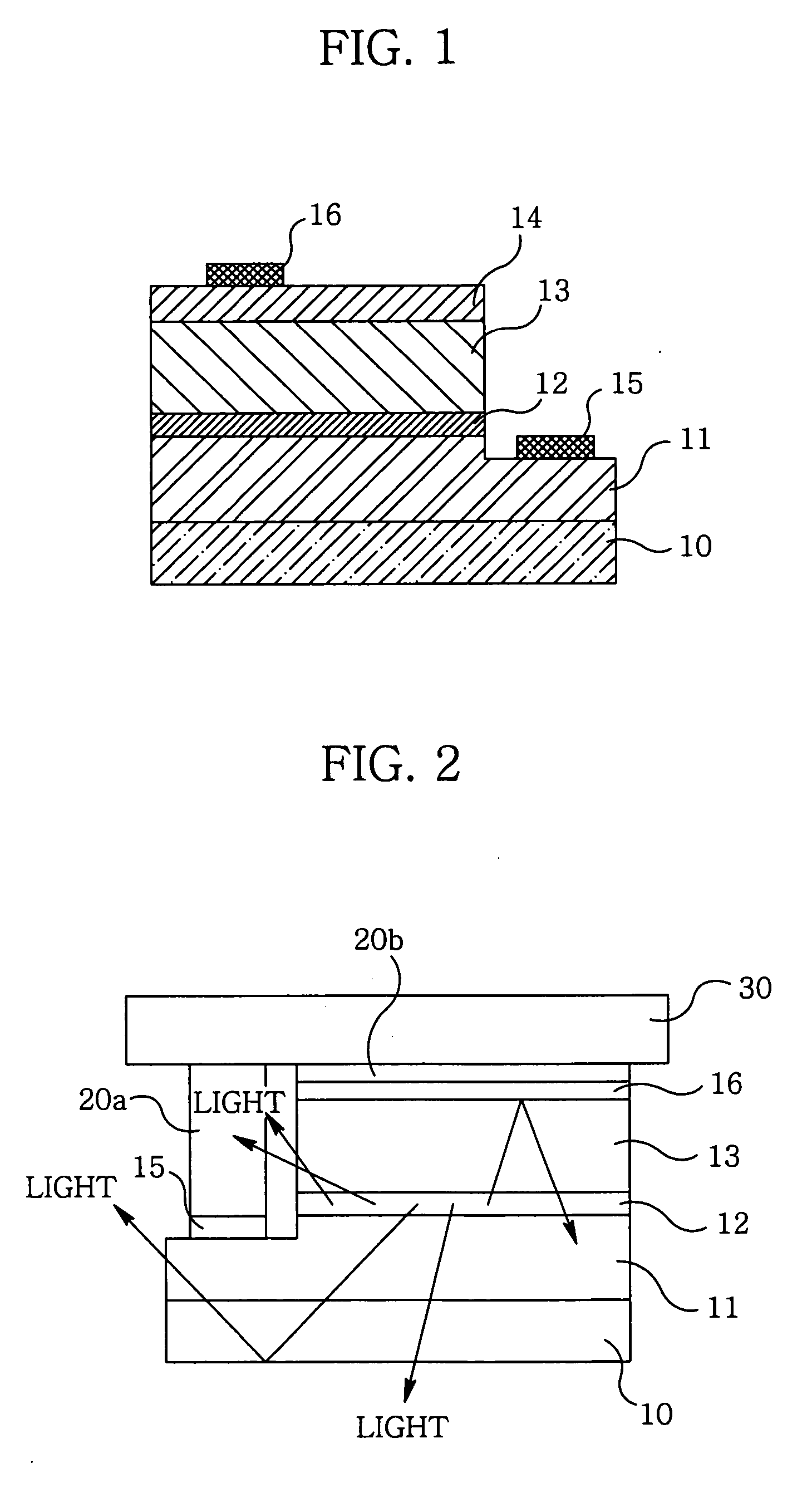

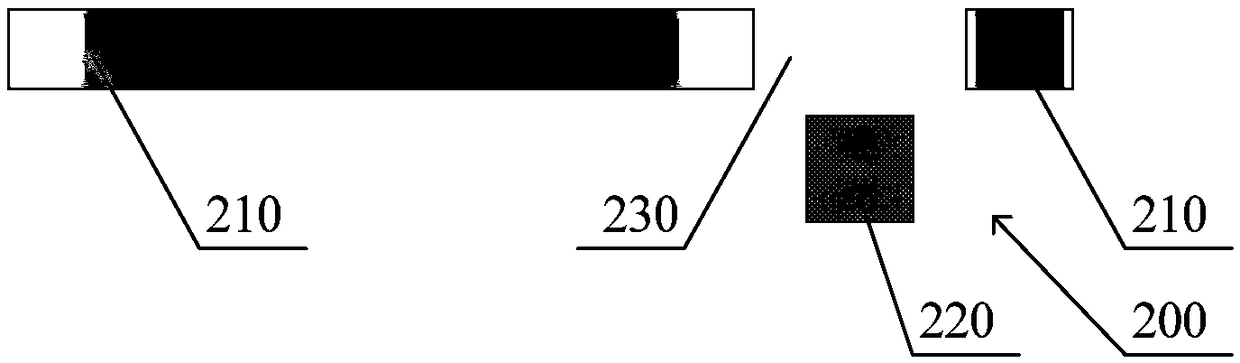

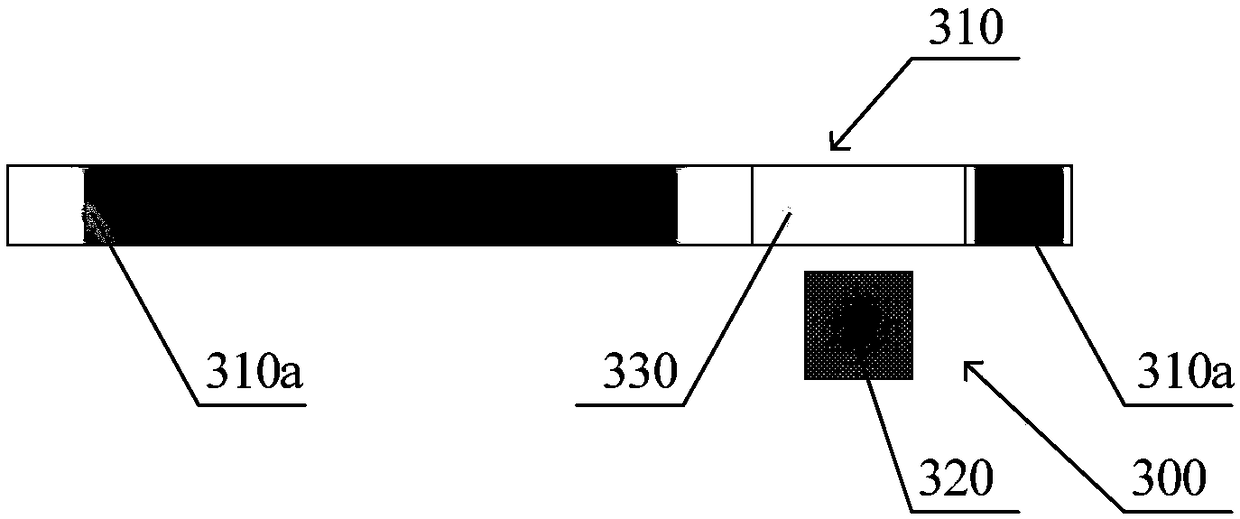

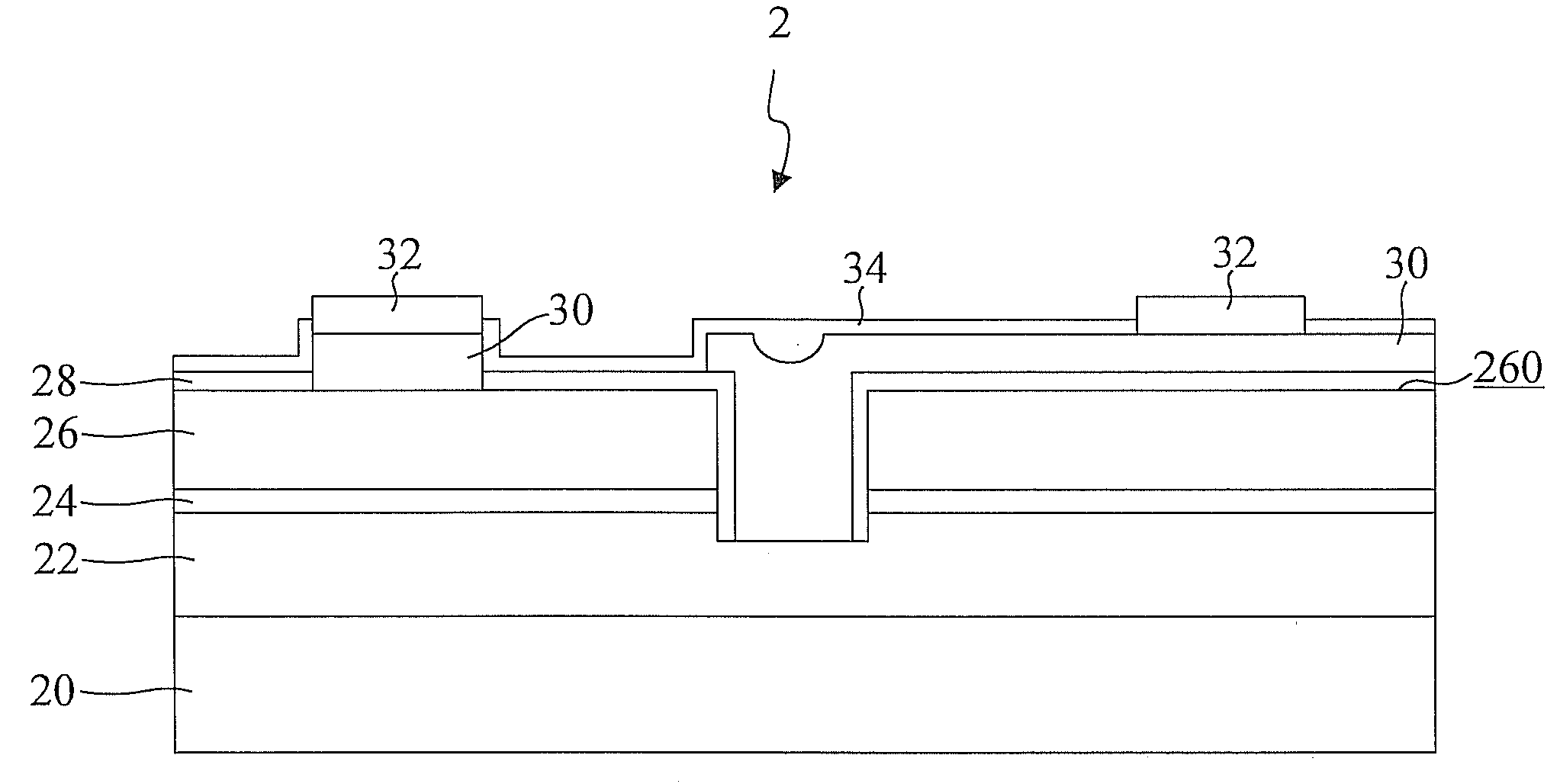

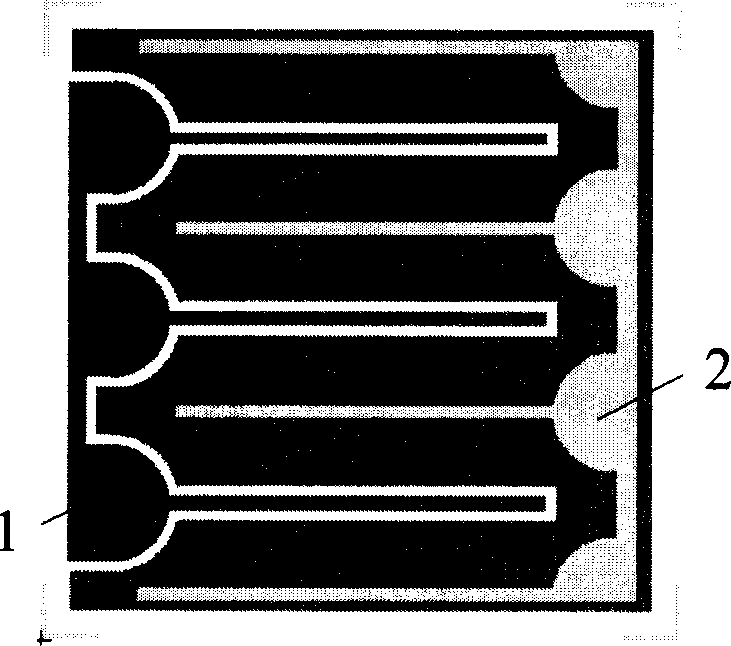

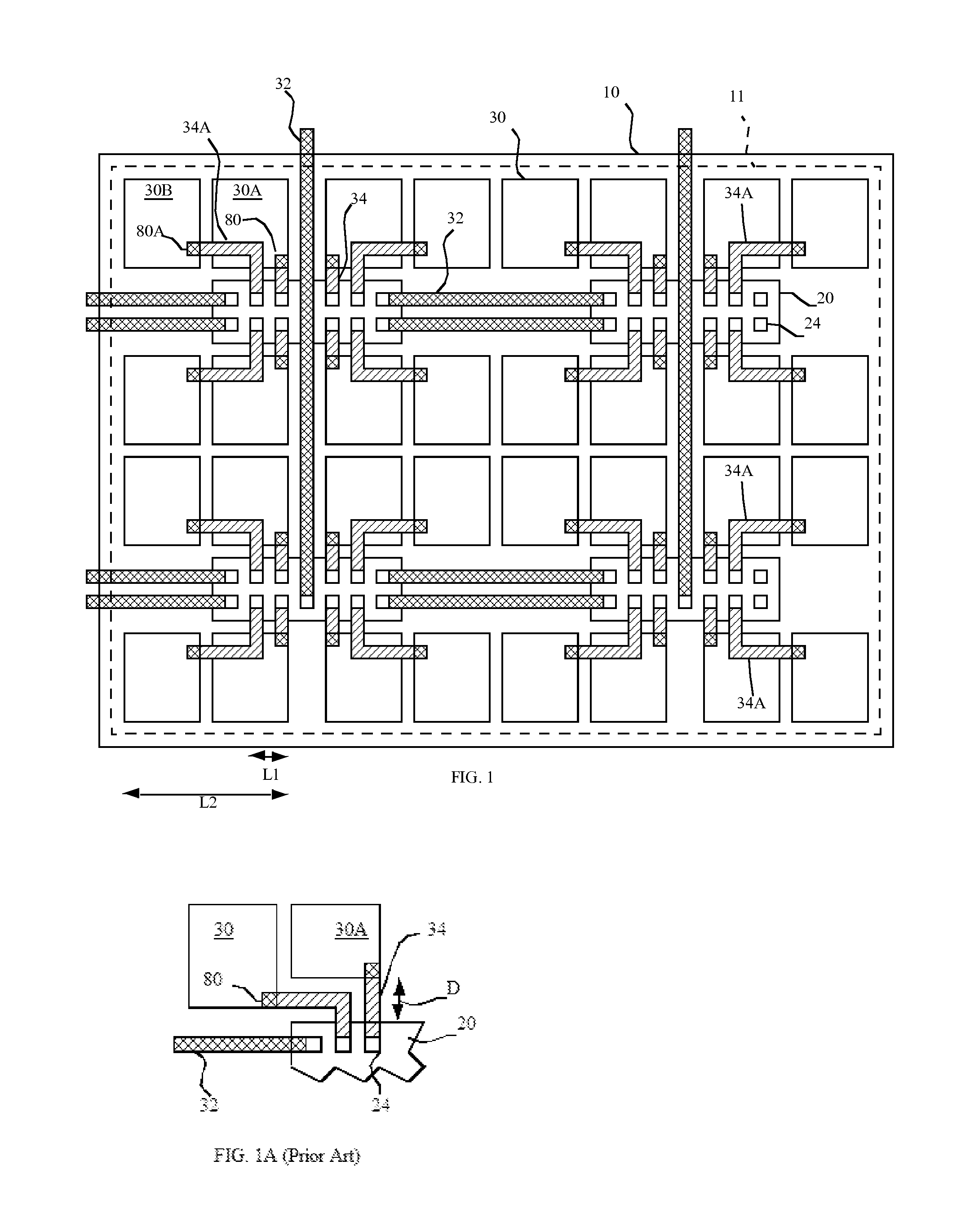

Light emitting diodes with spreading and improving light emitting area

InactiveUS20020130327A1Increase light emitting areaCurrent spreadSolid-state devicesSemiconductor devicesSemiconductor structureLight-emitting diode

The present invention provides a light semiconductor device comprising a substrate and a first semiconductor structure on the substrate. A light emitting structure is on a first portion of the first semiconductor structure. A first contact structure is on a second portion of the first semiconductor structure. The second portion is separated from the first portion of the first semiconductor structure. The first contact structure has a first shape. A second semiconductor structure is on the light emitting structure. A transparent contact is on the second semiconductor structure and has a cut-off portion to expose the portion of second semiconductor structure and a second shape. A second contact structure is on the cut-off portion of the transparent contact. The second contact structure contacting the second semiconductor has a third shape. The second contact structure with the third shape is corresponded to both the transparent contact with the second shape and the first contact structure with the first shape whereby a relationship provides a plurality of current paths with substantially equal distances between the first contact structure and the second contact structure.

Owner:UNI LIGHT TECH INC

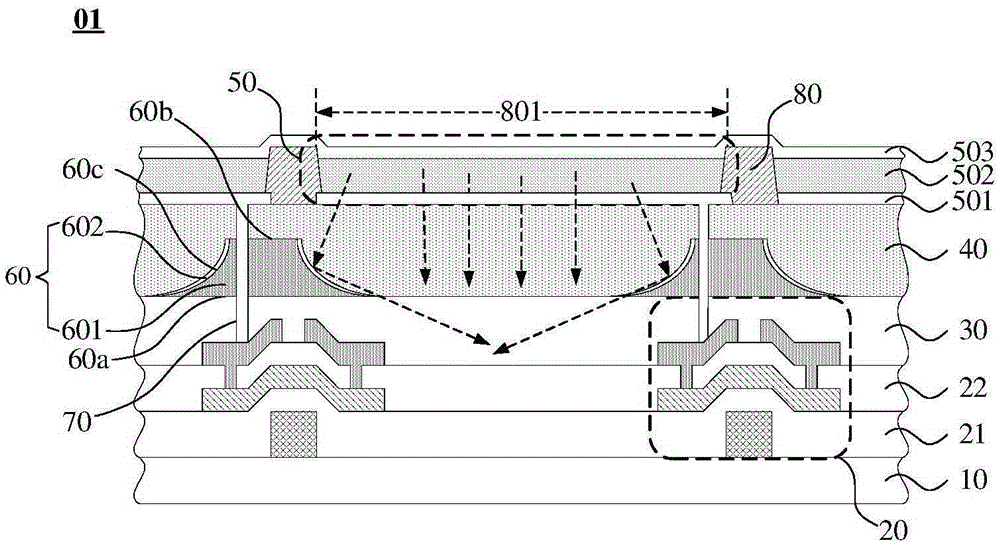

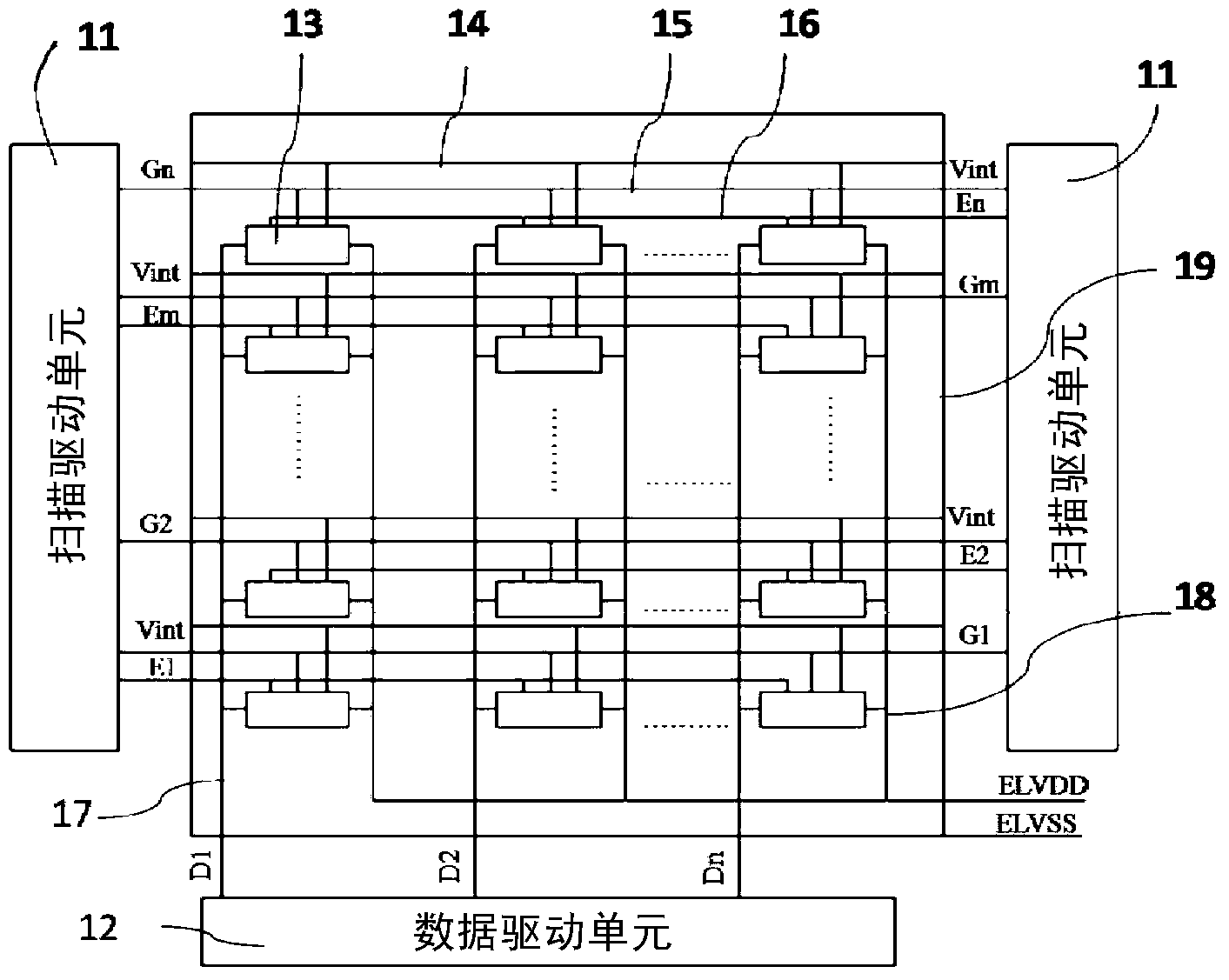

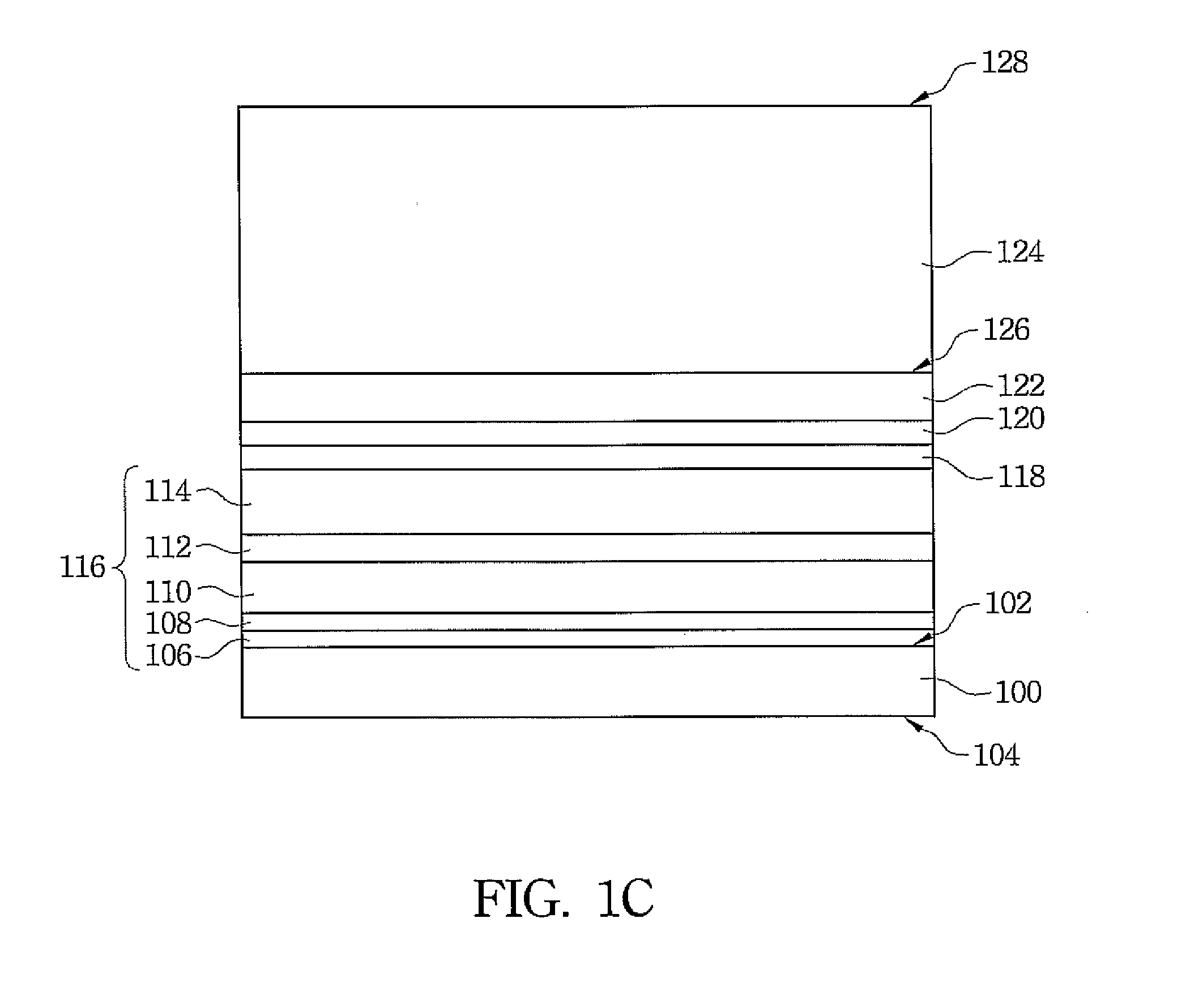

Organic el display device

ActiveUS20150053955A1Convenient lightingAvoid missed connectionsSolid-state devicesSemiconductor/solid-state device manufacturingPhysicsOptoelectronics

An organic EL display device includes: thin film transistors that are arranged in respective pixels within a display area which are arranged in a matrix; a planarization film that is formed over the thin film transistor and made of an organic insulating material; contact electrodes that are connected to drains or sources of the respective thin film transistors through contact holes formed within the planarization film; contact hole planarization films that are arranged over the respective contact electrodes with which the contact holes are embedded, and made of an organic insulating material; a lower electrode that is formed to be electrically connected onto the contact electrodes, and formed over the contact hole planarization film; and an organic layer that is arranged over the lower electrode to cover the overall display area, and formed of a plurality of organic material layers including a light emitting layer.

Owner:JAPAN DISPLAY INC

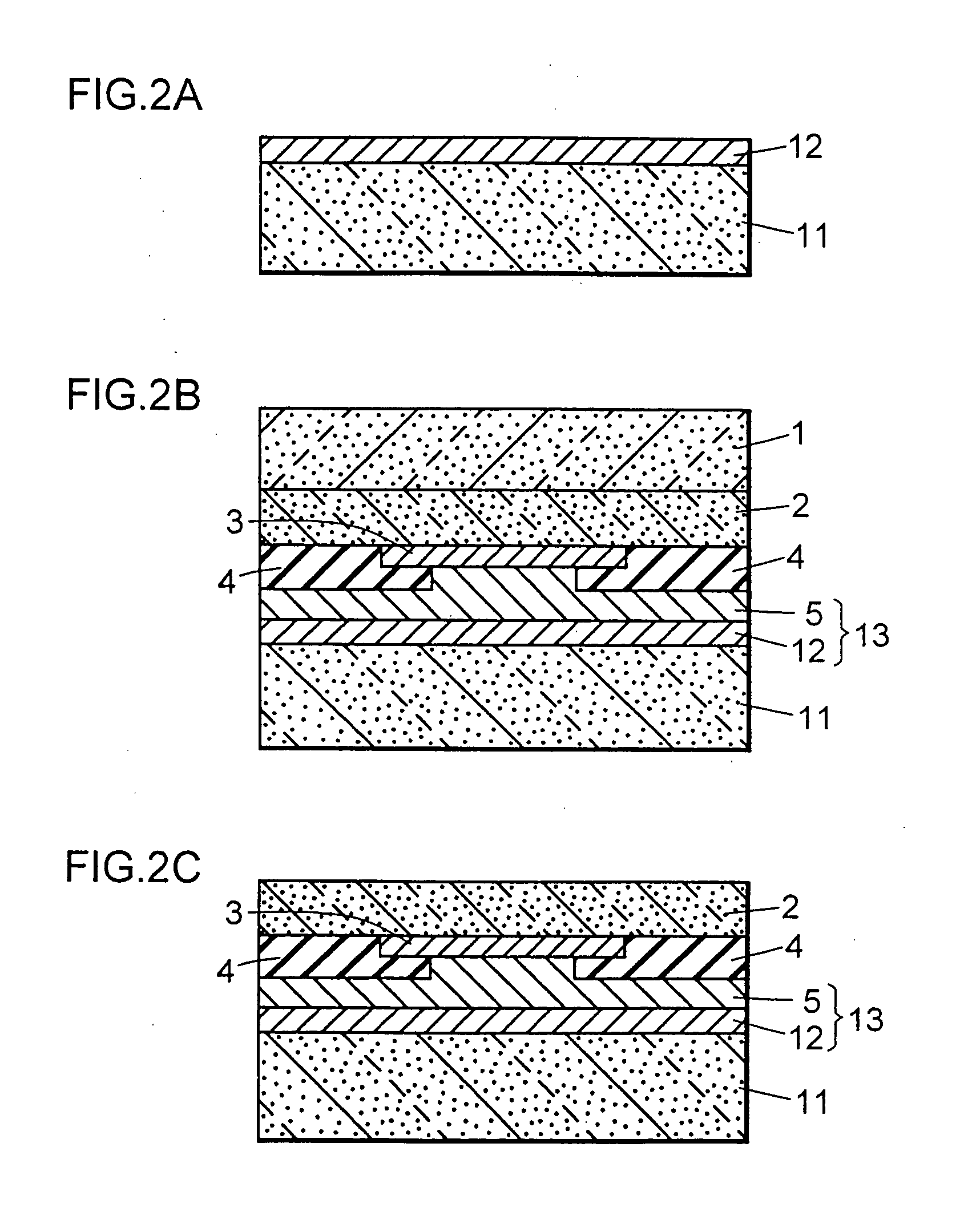

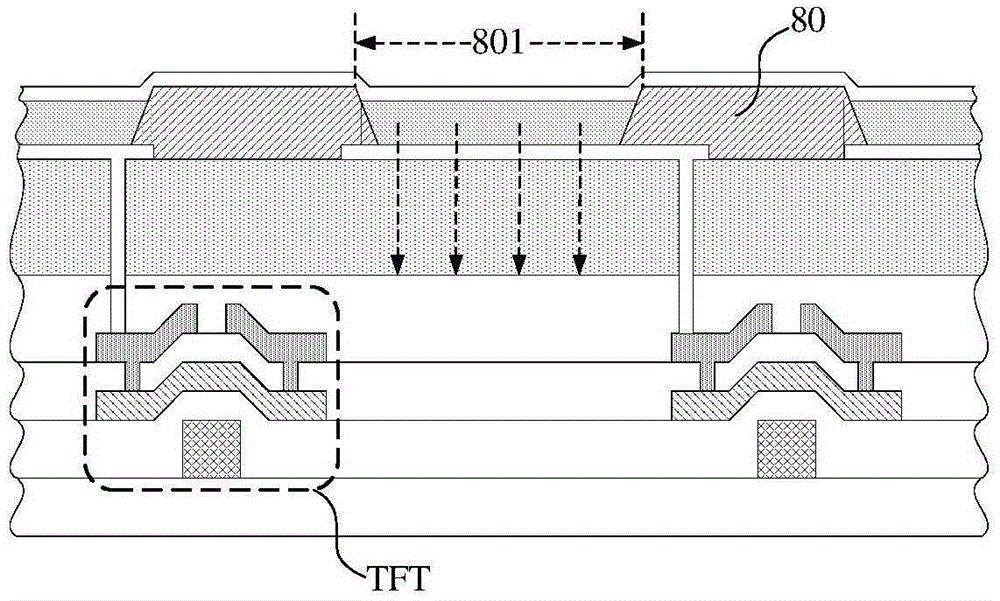

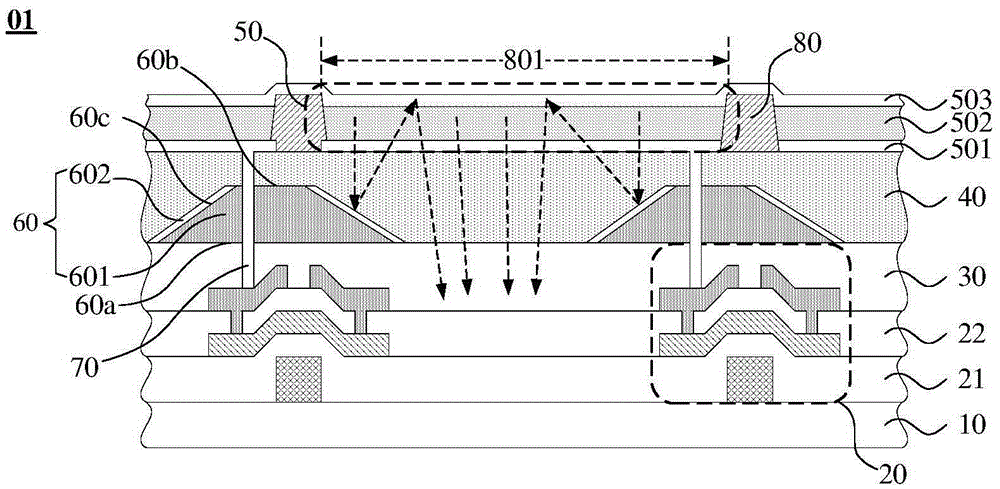

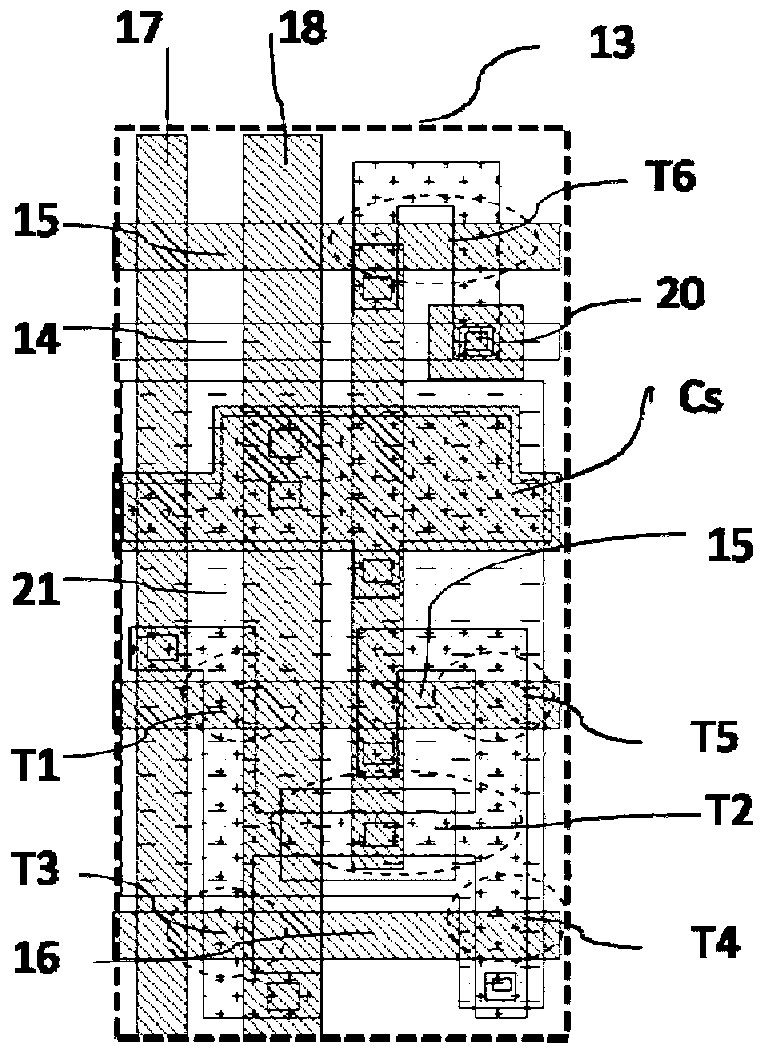

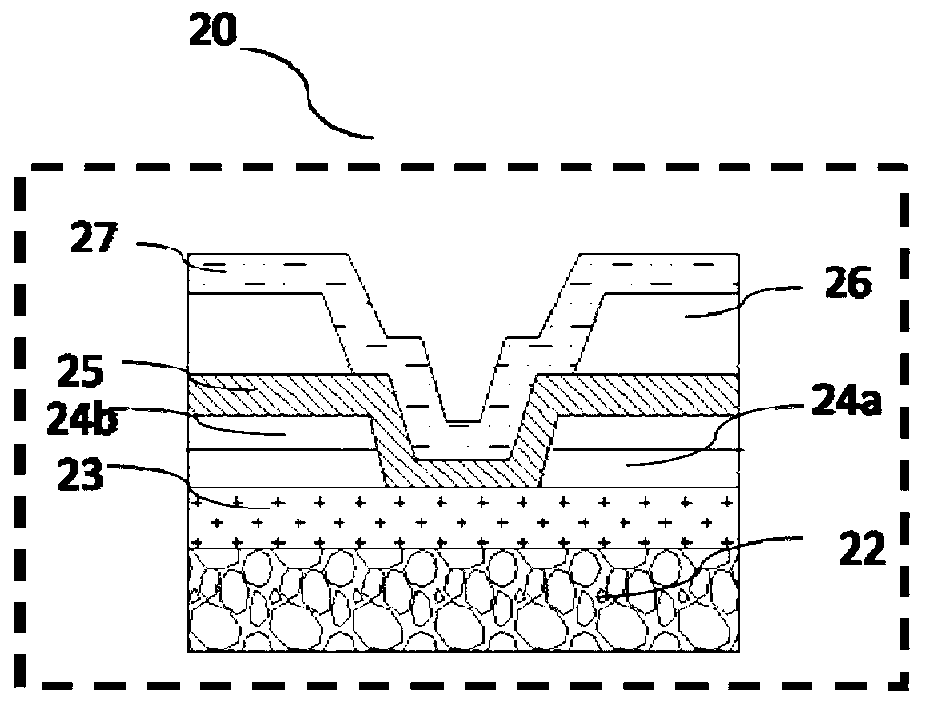

Bottom light emitting type OLED display panel

ActiveCN105304679AImprove light extraction efficiencyIncrease light emitting areaSolid-state devicesSemiconductor/solid-state device manufacturingProtection layerTransistor

The invention provides a bottom light emitting type OLED display panel and belongs to the display technology field. According to the bottom light emitting type OLED display panel, a light emitting area of an OLED device can be improved, light emitting efficiency can be improved, and service life of a light emitting material of the OLED device can be improved. The bottom light emitting type OLED display panel comprises multiple driving transistors arranged on a substrate in an array mode, a protection layer covering the driving transistors, a flat layer arranged above the protection layer and the OLED device arranged above the flat layer and further comprises multiple reflection structures which are arranged between the protection layer and the flat layer and correspond to the driving transistors, the reflection structures are used for reflecting light irradiated on the reflection structures when the OLED device emits light, and a bottom face of one side of the reflection structures close to the protection layer at least covers location areas of the driving transistors. The bottom light emitting type OLED display panel is prepared.

Owner:BOE TECH GRP CO LTD

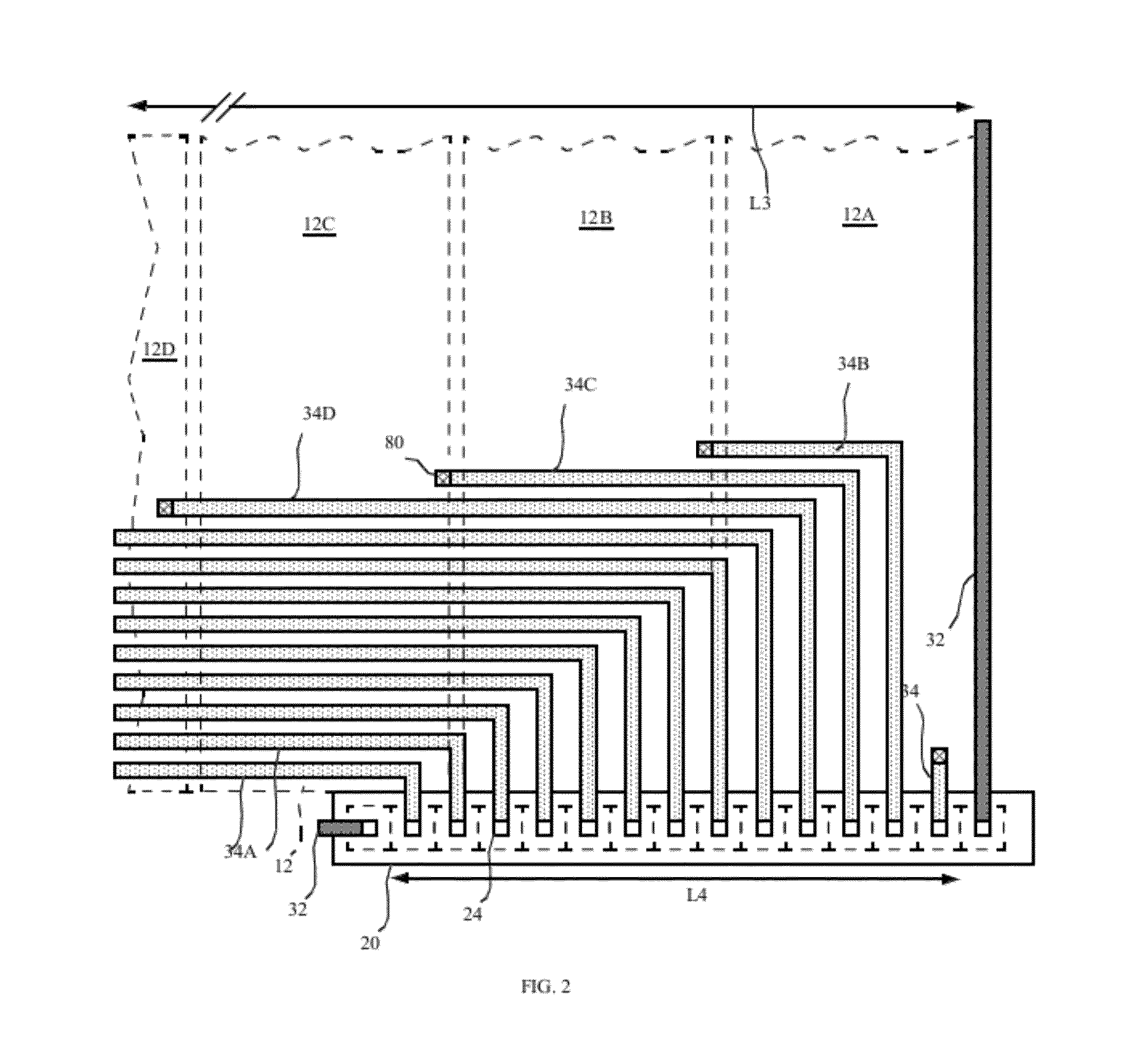

Manufacture method of array type high-voltage LED device

InactiveCN102867837AReduce light absorptionIncrease light emitting areaSolid-state devicesSemiconductor devicesSulfurPhosphoric acid

The invention discloses a manufacture method of an array type high-voltage LED device, which comprises the steps of: manufacturing a mask on a P type gallium nitride layer with an epitaxial structure, selectively etching the epitaxial structure to form an N type step structure; manufacturing a mask on the surface of an N type gallium nitride layer with an epitaxial structure, forming isolated deep trench; carrying out high-temperature sulfur phosphoric acid corrosion; depositing an insulation dielectric layer on the surface of the etched epitaxial structure; corroding the insulation dielectric layer outside the side wall of the deep trench; manufacturing a transparent conductive layer between adjacent N type step structures; partially corroding the transparent conductive layer on the surface of the P type gallium nitride layer on the N type step structure on the outermost side; and manufacturing a P metal electrode and an N metal electrode on the transparent conductive layer. According to the invention, electrode light absorption can be reduced, the light outlet area on the epitaxial side surface and the bottom of the chip is increased, the manufacture method is mutually matched with a post process, and thus the light emitting efficiency of a high-voltage LED chip can be increased.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Light-emitting device

ActiveUS20080105885A1Effective lightingIncrease the areaSolid-state devicesSemiconductor devicesActive layerLight emitting device

A light-emitting device includes a first compound semiconductor layer, an active layer, and a second compound semiconductor layer; a second electrode formed on the second compound semiconductor layer; an insulating layer covering the second electrode; a first opening provided to pass through the insulating layer, the second electrode, the second compound semiconductor layer, and the active layer; a second opening provided to pass through the insulating layer; a first electrode formed on an exposed portion of the first compound semiconductor layer at the bottom of the first opening; a first electrode extension extending from the first electrode to the insulating layer through the first opening and a first pad portion including a portion of the first electrode extension on the insulating layer; and a second pad portion connected to an exposed portion of the second electrode at the bottom of the second opening.

Owner:XIAMEN SANAN OPTOELECTRONICS CO LTD

A display panel and a display device

ActiveCN109192076AIncrease display brightnessIncrease light emitting areaStatic indicating devicesIdentification meansDisplay deviceComputer science

The embodiment of the invention discloses a display panel and a display device. The display panel comprises a display area and a transparent display area; The transparent display area includes a plurality of sub-pixels and a transparent area, and the anode electrodes of at least two sub-pixels of the same color are connected. The embodiment of the invention solves the problem that the brightness difference exists in the display panel because the transparent display area should be compatible with the transparent and display functions in the existing full-screen display panel.

Owner:BOE TECH GRP CO LTD

Rear lamp unit for vehicle

InactiveUS20050068781A1Increase light emitting areaLighting support devicesPoint-like light sourceEngineeringLight-emitting diode

To provide a rear lamp unit for a vehicle which is provided with a desired cut pattern on an outer lens so that the light-emitting area can be increased. A rear lamp unit is provided with upper and lower outer lenses for guiding light emitted from light-emitting diodes to the outside the vehicle. The upper and lower inner lenses are provided between the light-emitting diodes and the upper and lower outer lenses, respectively, and the upper and lower inner lenses are disposed at locations apart from the upper and lower outer lenses, respectively.

Owner:HONDA MOTOR CO LTD

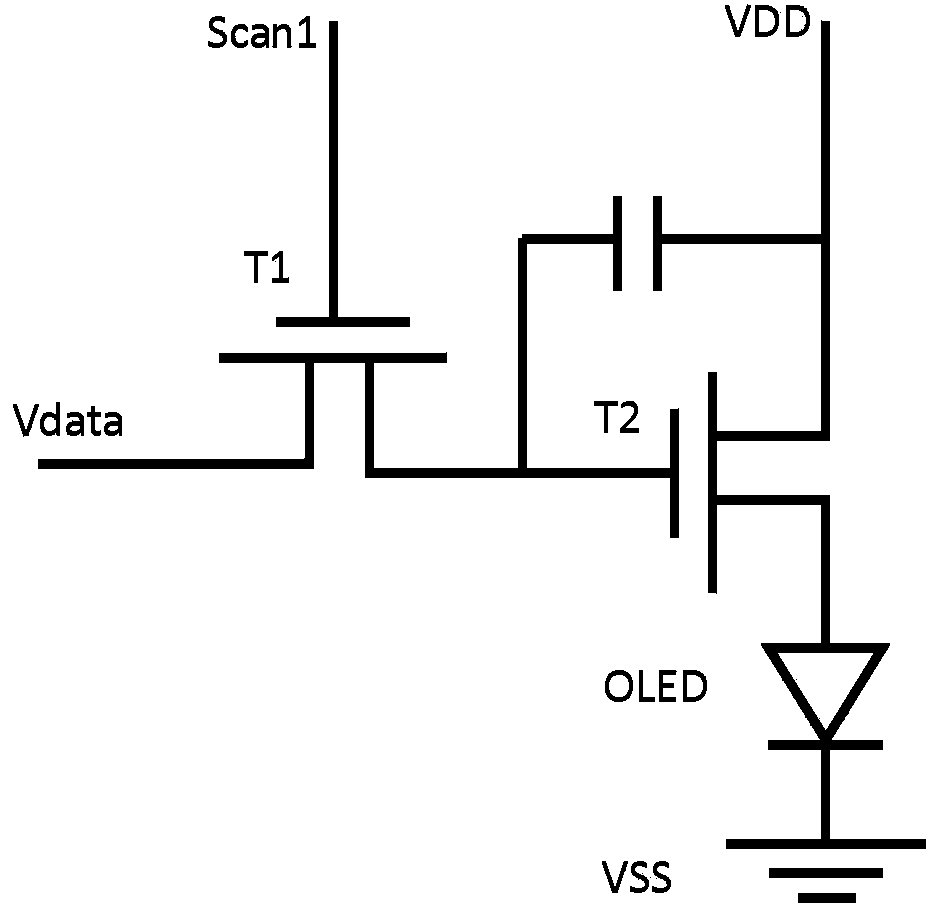

Thin film transistor array substrate and manufacturing method thereof

ActiveCN103199096AIncrease opening ratioIncrease light emitting areaSolid-state devicesSemiconductor/solid-state device manufacturingMetalTransistor

The invention provides a thin film transistor array substrate and a manufacturing method thereof. The thin film transistor array substrate comprises a substrate, an insulating layer, a power line, a data line, an initialized power line, a planarization layer and a pixel electrode, wherein the insulating layer is formed on the substrate; the power line, the data line and the initialized power line are all formed on the insulating layer; the planarization layer is covered on the power line, the data line and the initialized power line; and the pixel electrode is formed on the planarization layer. According to the invention, the initialized power line and the data line are on the same metal layer, while the initialized power line is not on the layer on which the pixel electrode is located, so that the initialized power line does not occupy the lining space of the pixel electrode, the pixel area can be maximized, thus the pixel aperture opening ratio can be improved greatly, the effective light-emitting area can be improved and the product performance can be improved.

Owner:EVERDISPLAY OPTRONICS (SHANGHAI) CO LTD

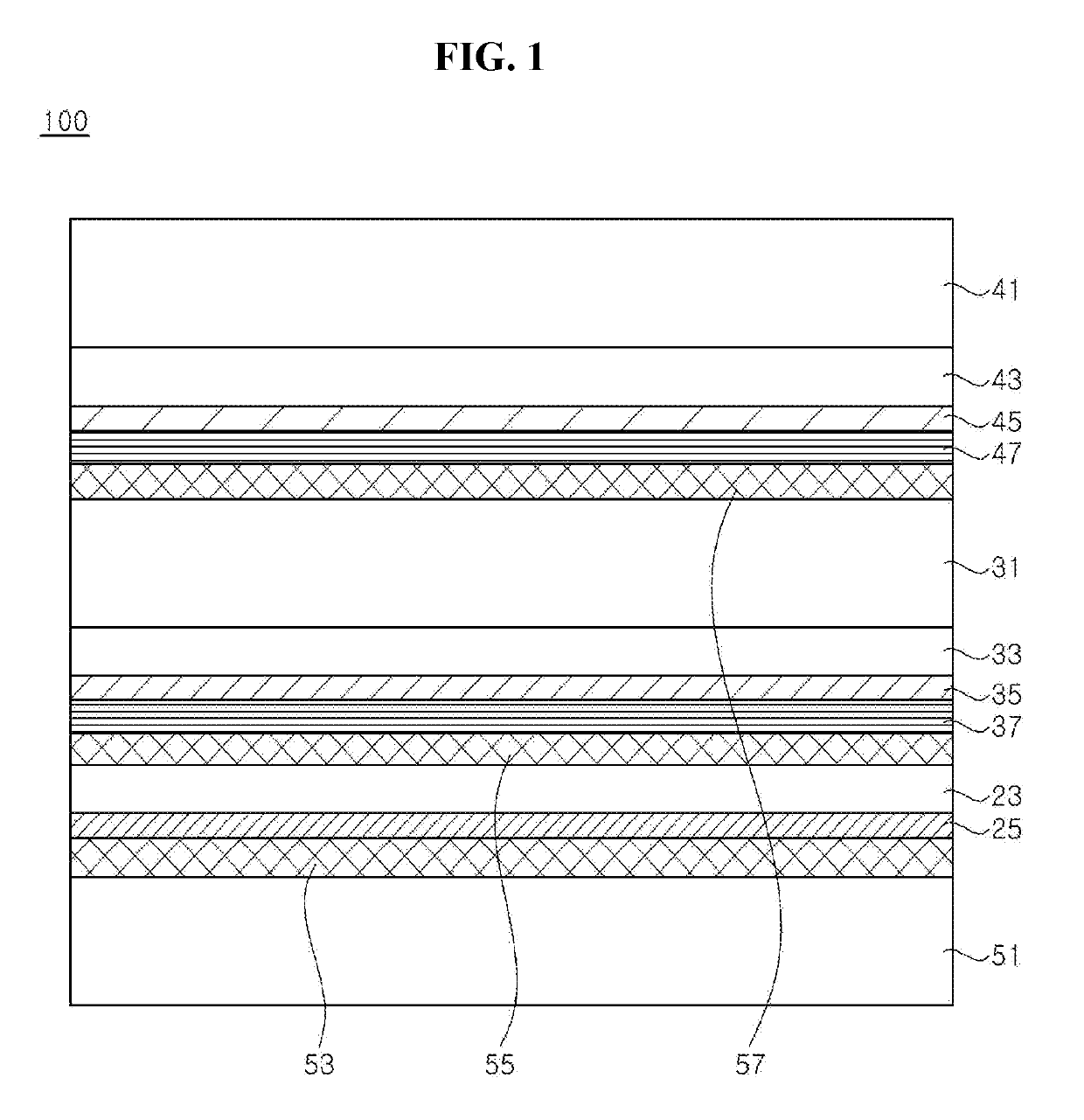

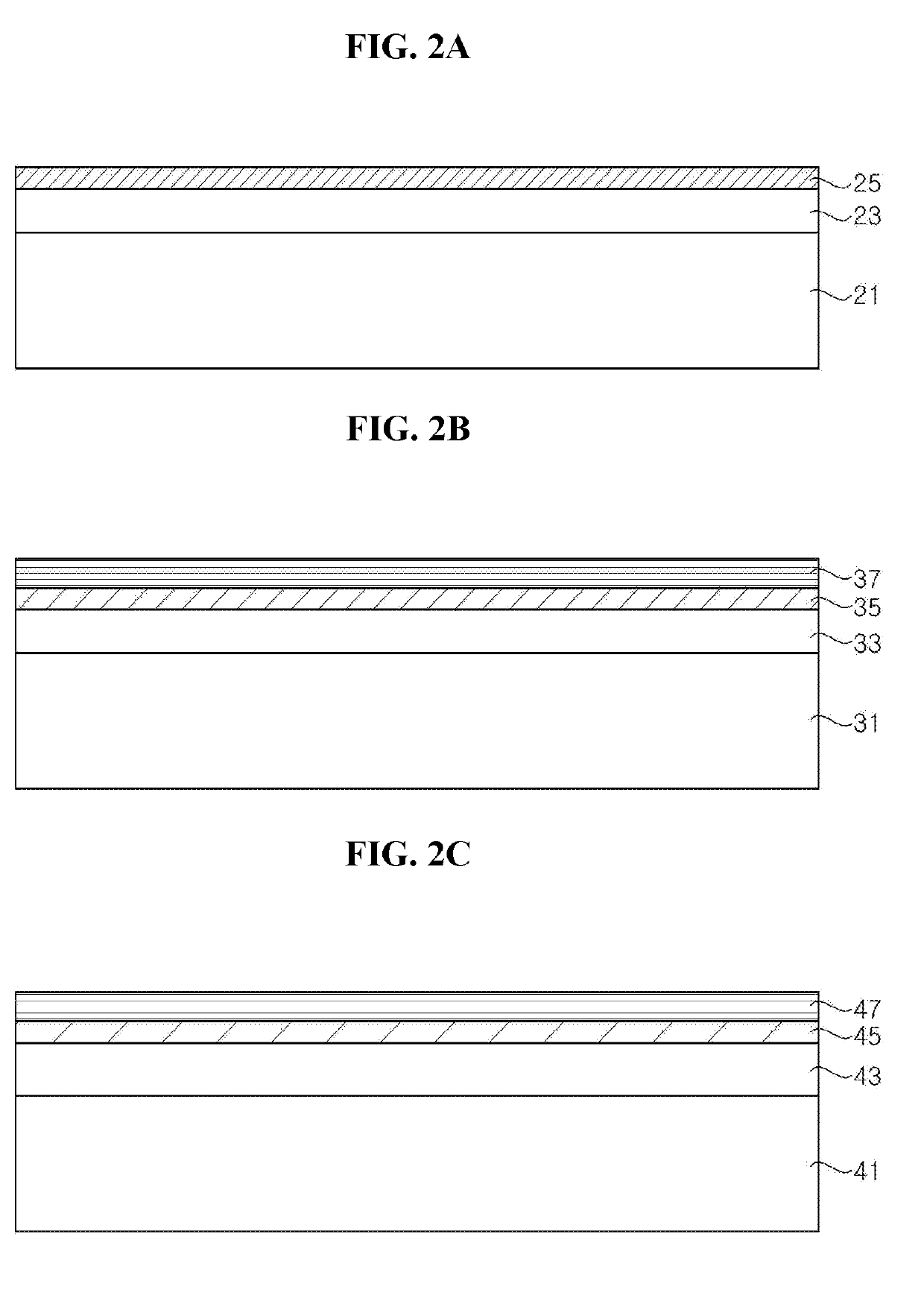

Light emitting diode for display and display apparatus having the same

PendingUS20190164945A1Increase light emitting areaReduce areaSolid-state devicesSemiconductor devicesDisplay deviceLight-emitting diode

A light emitting diode stack for a display includes a support substrate, a first LED stack, a second LED stack, and a third LED stack, a conductive growth substrate coupled to the second LED stack or the third LED stack, a first color filter interposed between the first and second LED stacks and transmitting light generated from the first LED stack while reflecting light generated from the second LED stack, and a second color filter interposed between the second and third LED stacks and transmitting light generated from the first and second LED stacks while reflecting light generated from the third LED stack, in which light generated from the first LED stack is emitted outside through the second LED stack, the third LED stack, and the conductive growth substrate, and light generated from the second LED stack is emitted outside through the third LED stack and the conductive growth substrate.

Owner:SEOUL VIOSYS CO LTD

High output light emitting diode and method for fabricating the same

A high output light emitting diode (LED) and a method for fabricating the LED is disclosed. The LED includes a sidewall or surface that is inclined. A reflective film is formed on the inclined sidewall or surface to allow light to reflect from the reflective film and to emit the light upward or in a favorable direction with respect to the device, thereby being configured and enabled to improve a light output of the LED and dispense with an additional passivation process.

Owner:LG ELECTRONICS INC

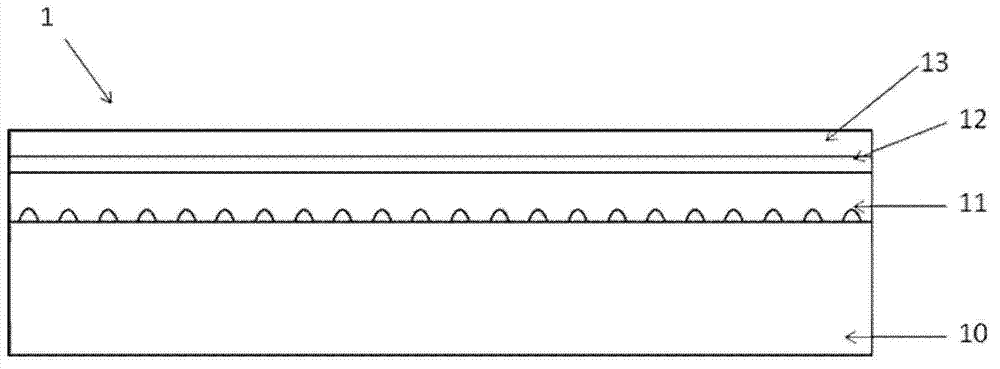

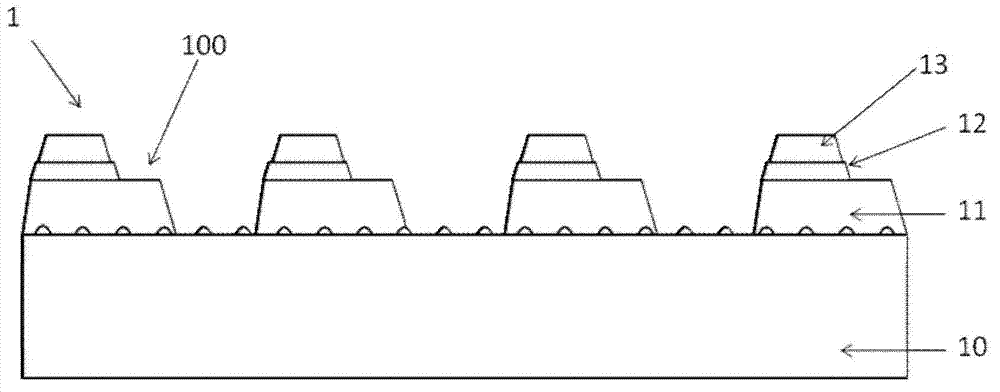

Semiconductor light-emitting device and method of fabricating the same

InactiveUS20090101886A1Increase light emitting areaEasy to makeSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor materials

Owner:EPISTAR CORP

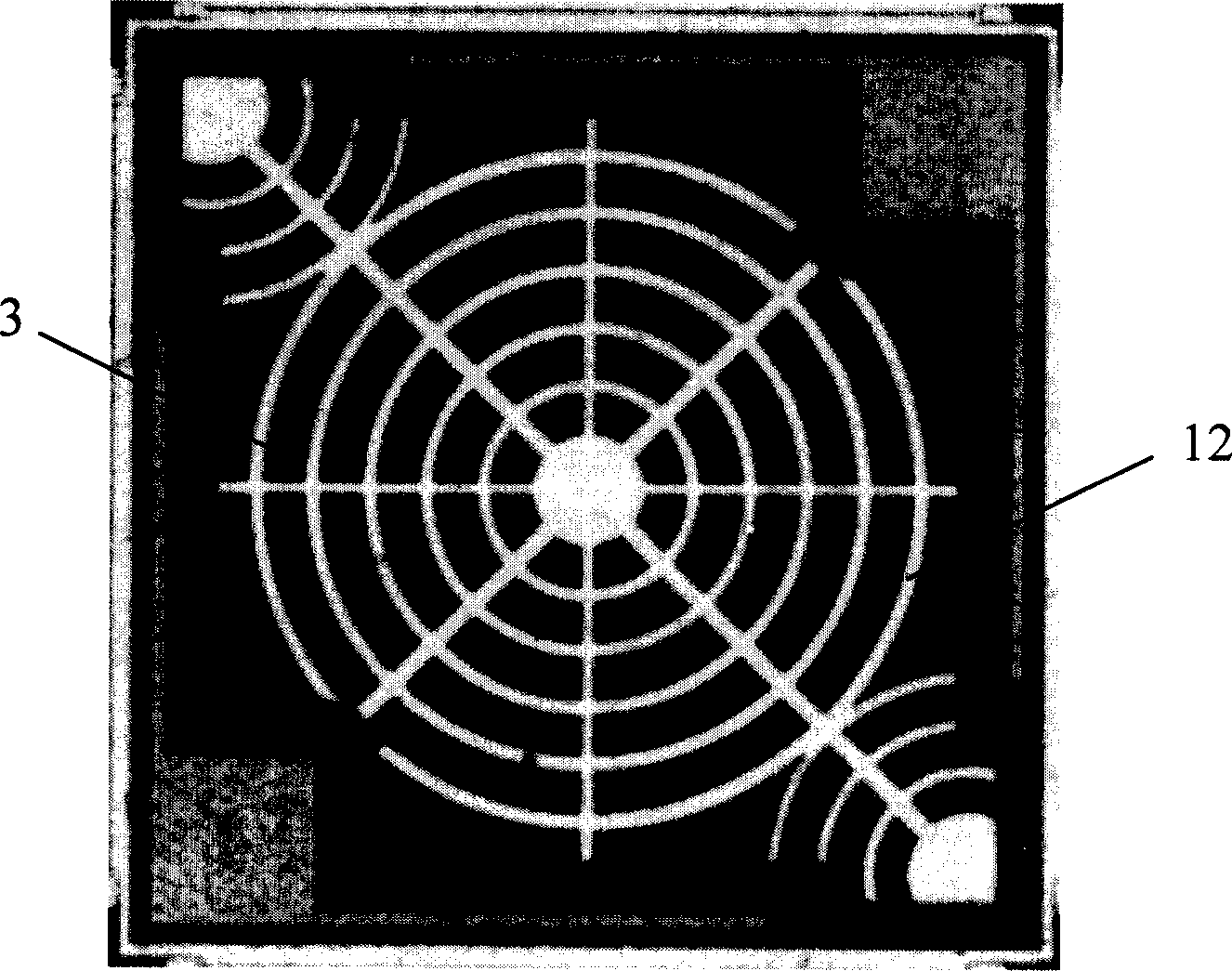

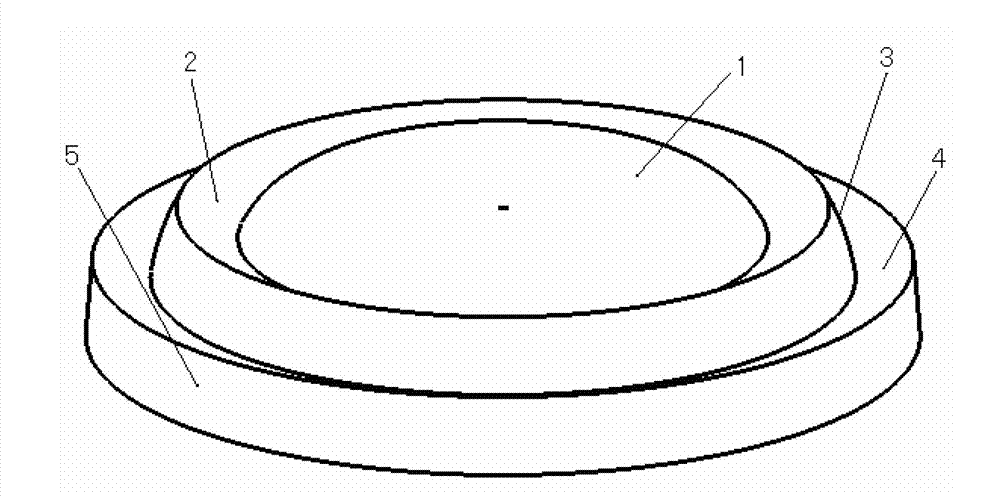

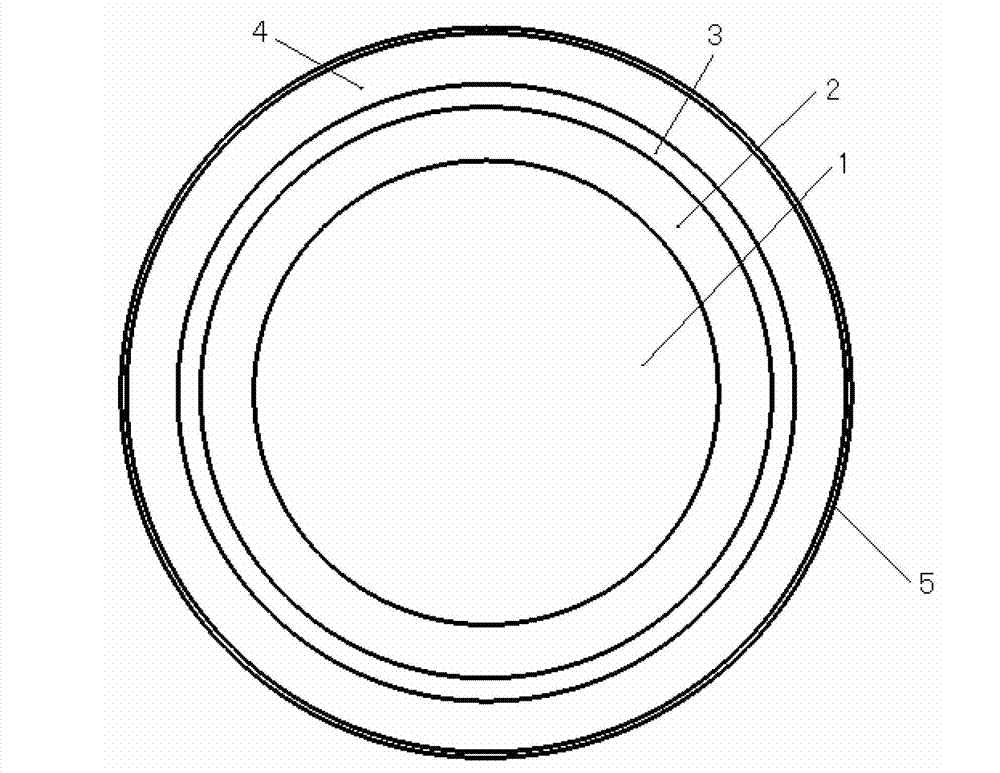

Light-emitting diode and method of preparing the same

ActiveCN1790753AOvercome uniformity issuesOvercoming scalabilitySemiconductor devicesOhmic contactLight energy

The invention discloses a LED, which comprises: a sapphire substrate, a GaN buffer layer, an N / P-type GaN / ohmic contact layer, an InGaN / GaN quantum trap active layer, and a concentric P-type ohmic contact transparent electrode with grooves between near ring electrodes manufactured by dry etching. This invention makes even current injection, increases probability of side-surface light, reduces reflection angle, and thereby decreases greatly light energy loss.

Owner:EPILIGHT TECH +1

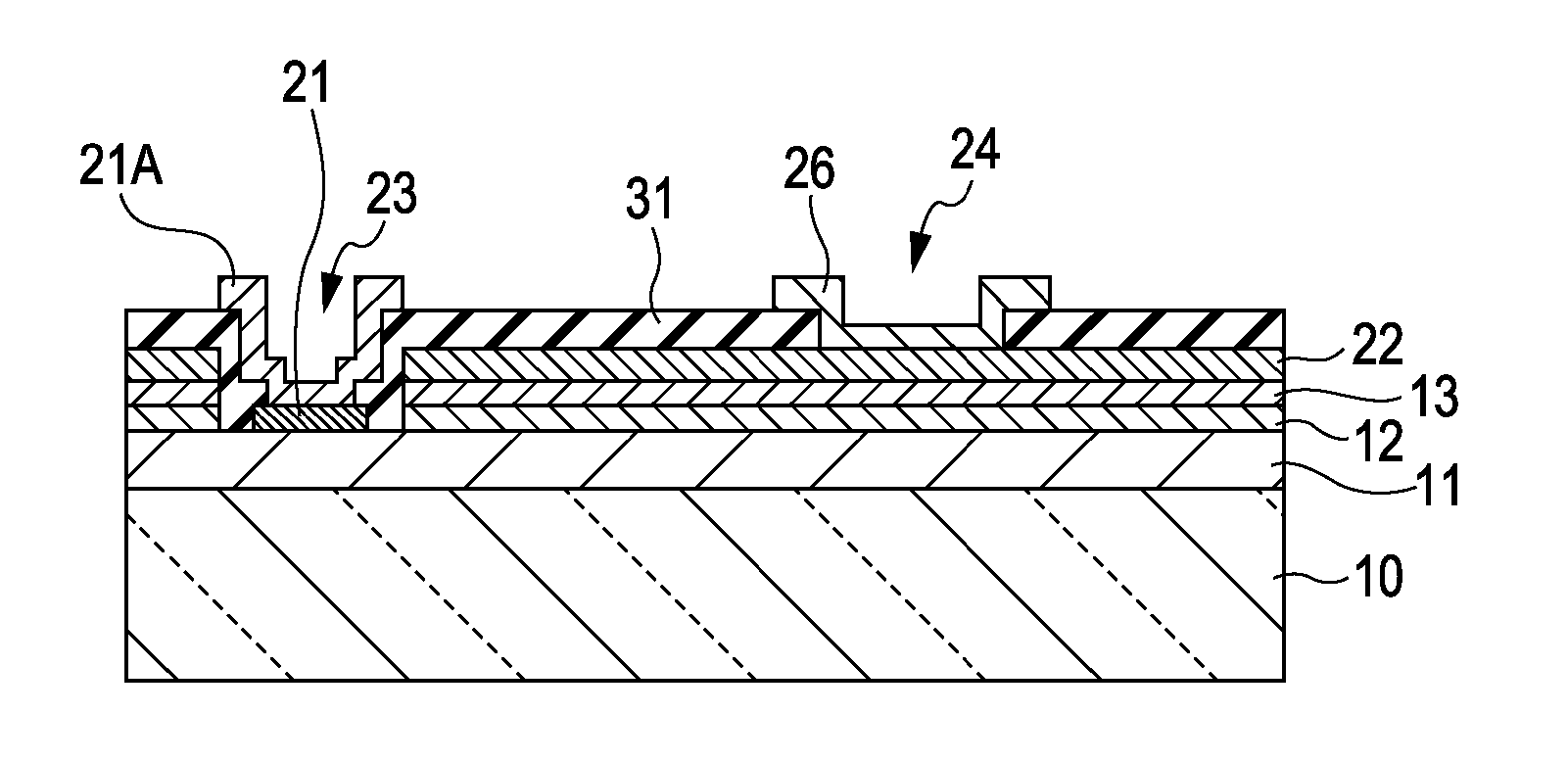

Light-emitting diode and method for manufacturing the same

InactiveUS20110079805A1Reduced packaging volumeReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesActive layerSealant

A light-emitting diode and a method for manufacturing the same are described. The light-emitting diode includes a bonding substrate, a first conductivity type electrode, a bonding layer, an epitaxial structure, a second conductivity type electrode, a growth substrate and an encapsulant layer. The first conductivity type electrode and the bonding layer are respectively disposed on two surfaces of the bonding substrate. The epitaxial structure includes a first conductivity type semiconductor layer, an active layer and a second conductivity type semiconductor layer. A trench is set around the epitaxial structure and extends from the second conductivity type semiconductor layer to the first conductivity type semiconductor layer. The second conductivity type electrode is electrically connected to the second conductivity type semiconductor layer. The growth substrate is disposed on the epitaxial structure and includes a cavity exposing the epitaxial structure and the trench. The encapsulant layer is filled in the cavity.

Owner:CHI MEI LIGHTING TECH

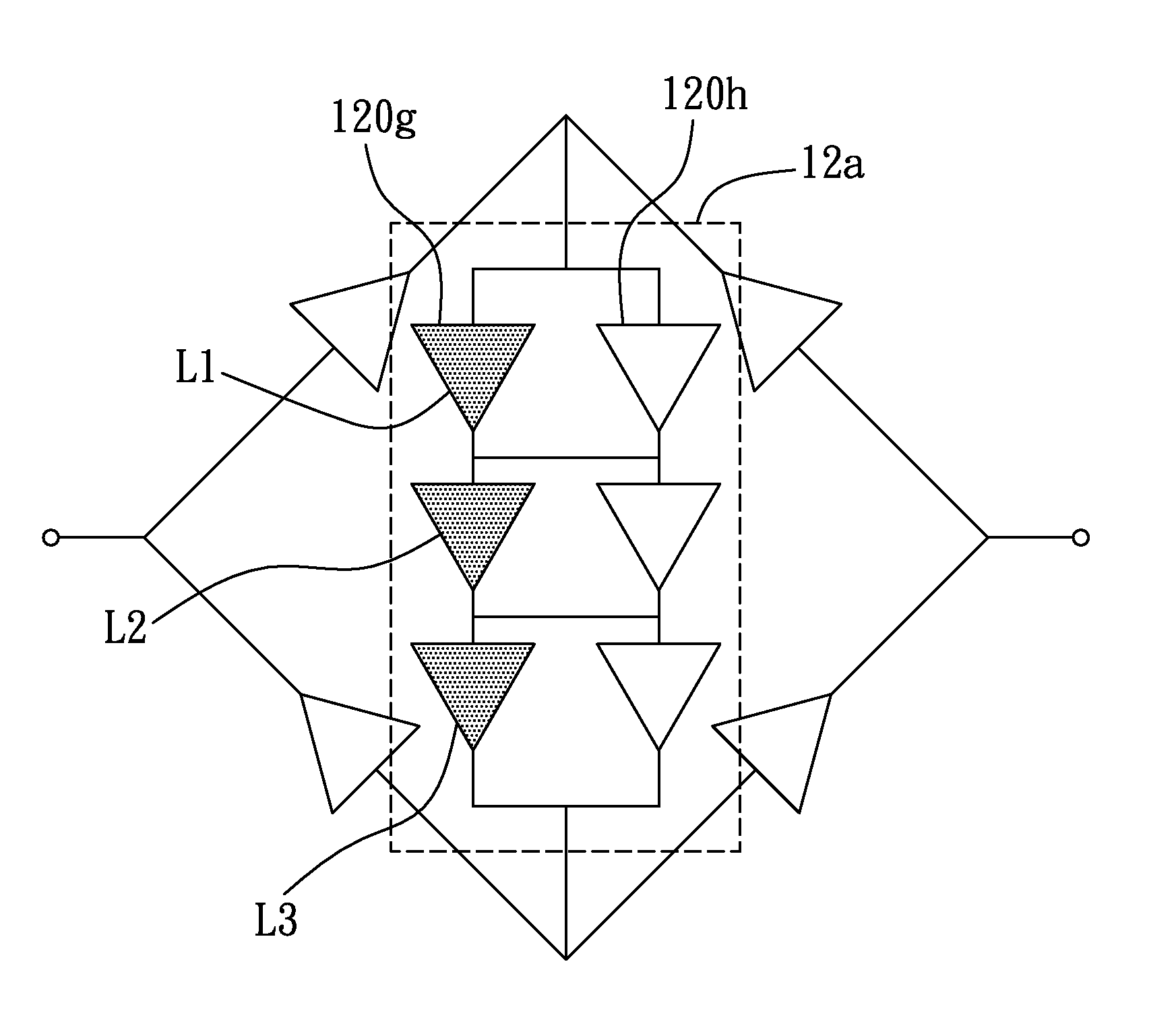

Lamp including main reflector, sub-reflector and LED assembly

InactiveUS8292480B2Increase light emitting areaGood lookingPoint-like light sourceLighting support devicesOptoelectronicsLight-emitting diode

Owner:KOITO MFG CO LTD

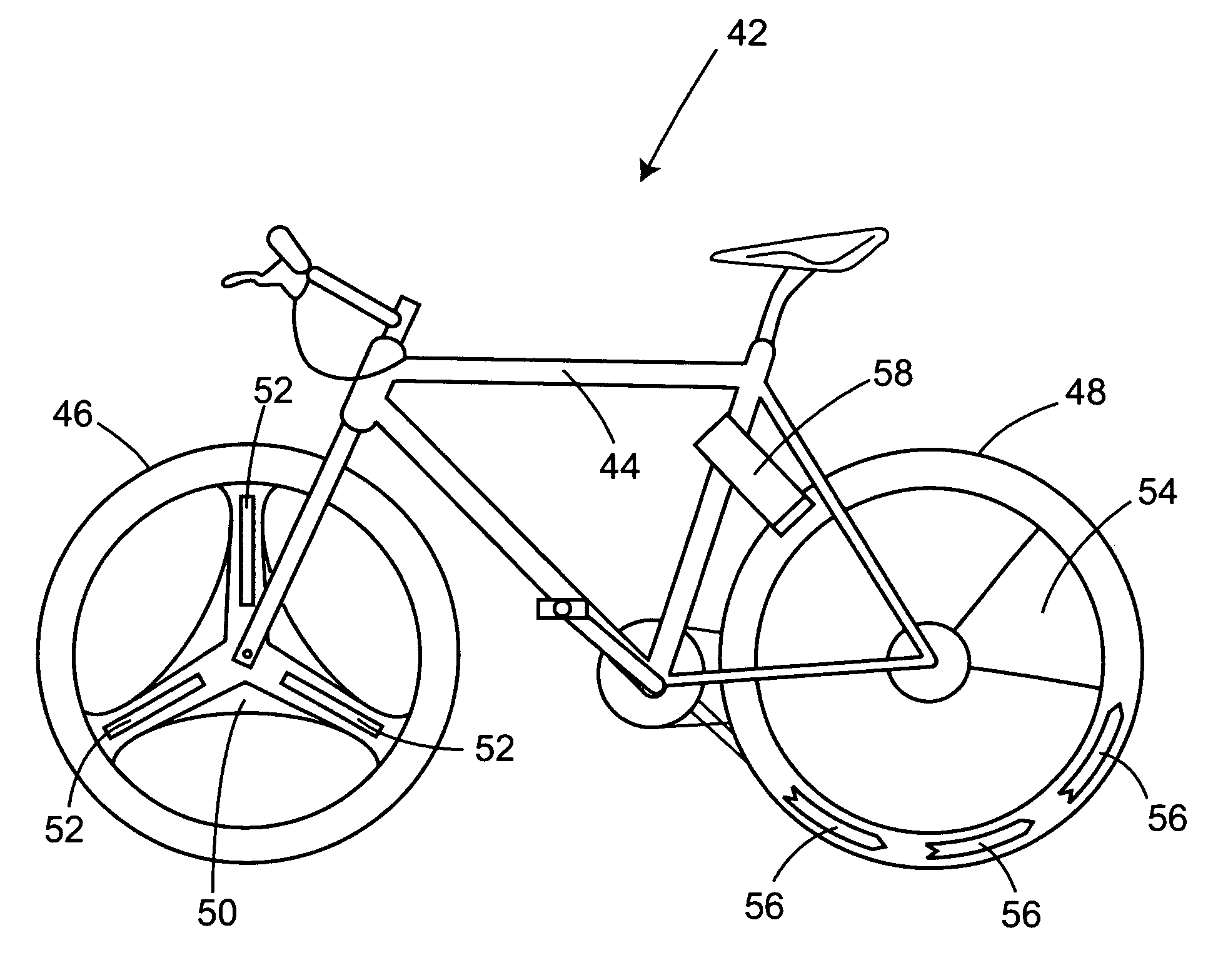

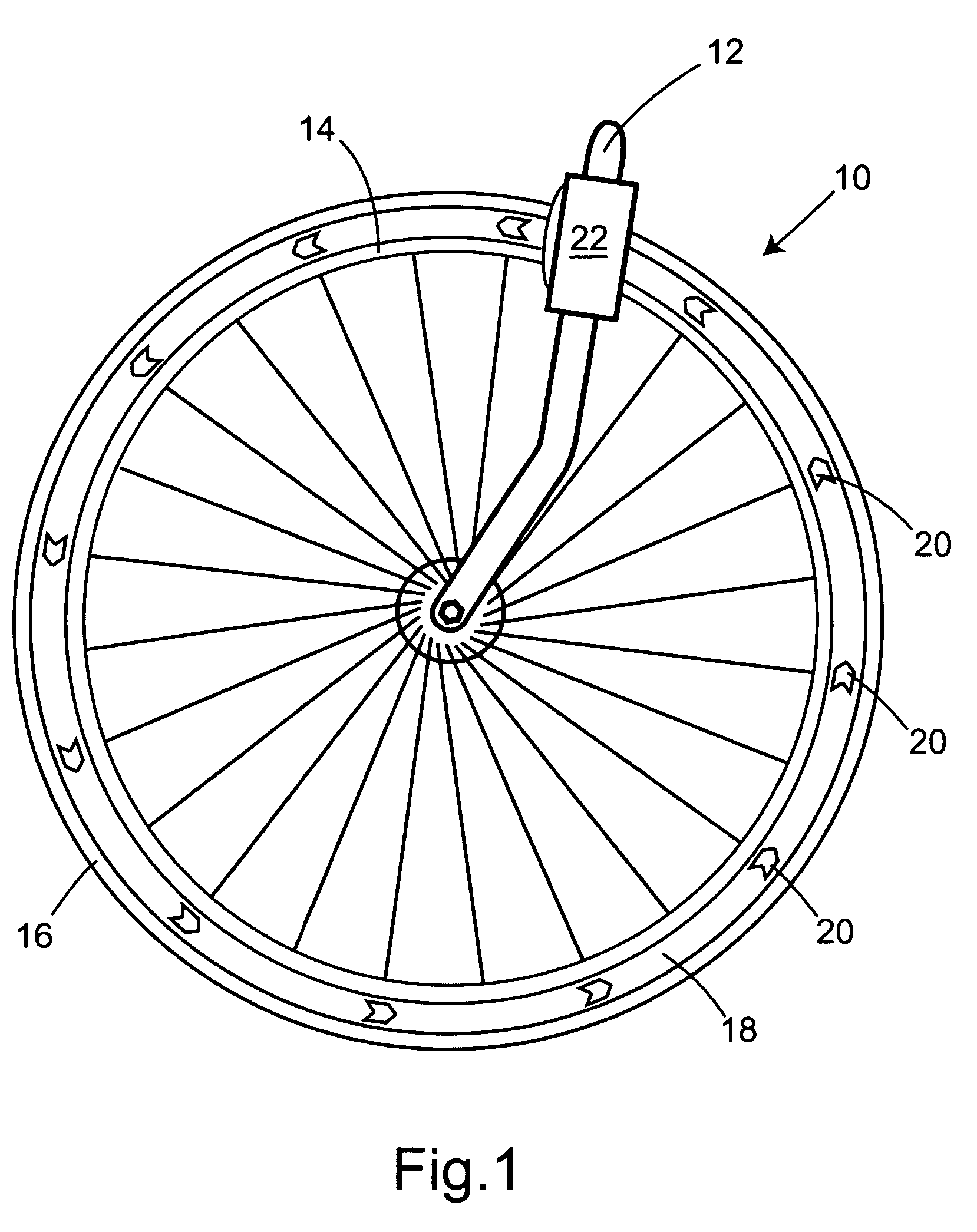

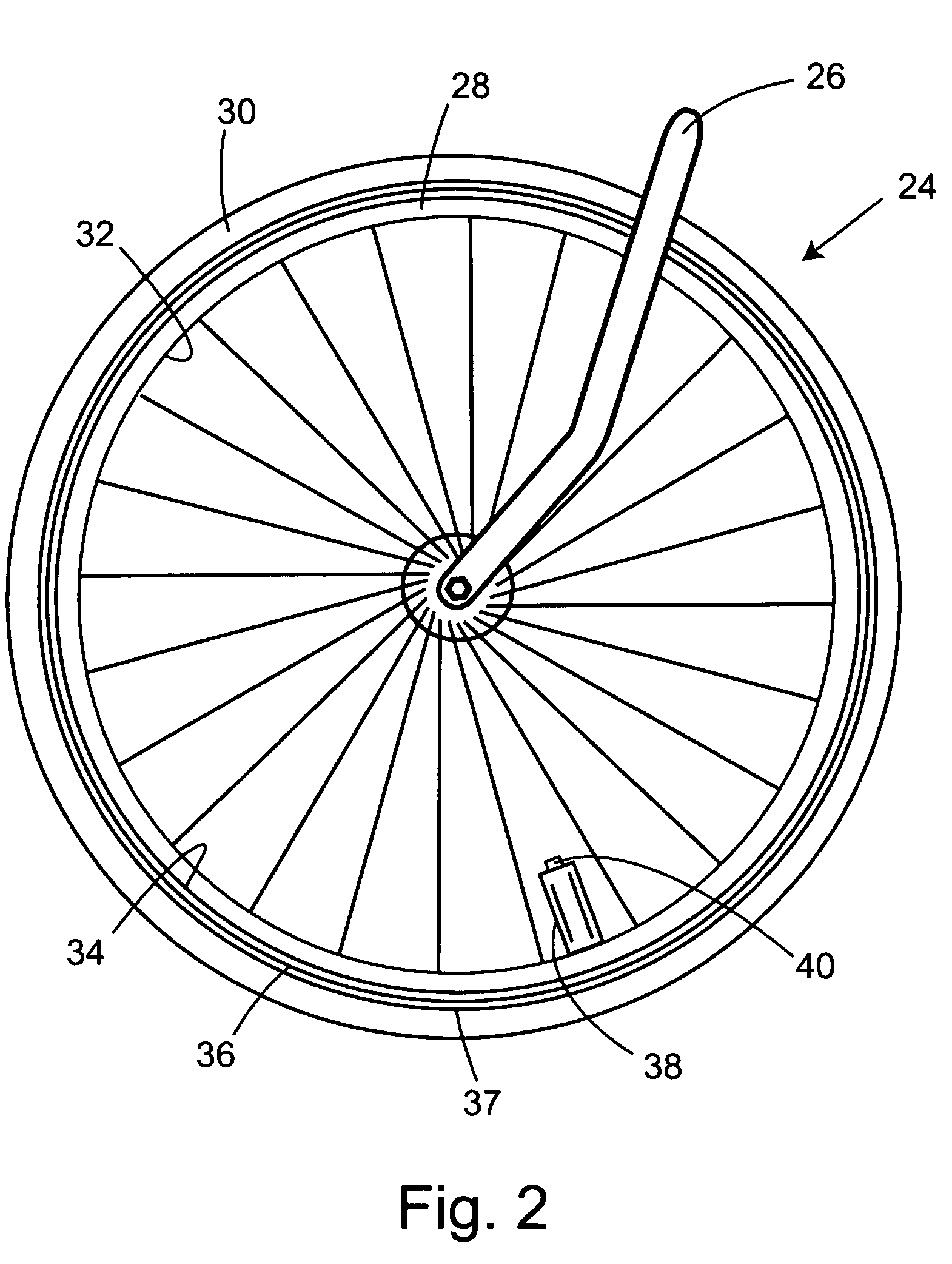

Human powered vehicle safety lighting structures

InactiveUS7001051B2Increase light emitting areaOptical signalLighting elementsVisibilityPhotoluminescence

A plurality of lighting structures is provided for enhancing the visibility of a human powered vehicle at night. The visibility enhanced human powered vehicle has a frame with attached wheels having tires including sidewalls. The safety lighting structures include at least one photo-luminescent section and at least one reflective section being located on at least one of the wheels. A light source is attachable to the human powered vehicle to direct light against the photo-luminescent sections.

Owner:LUNASEE

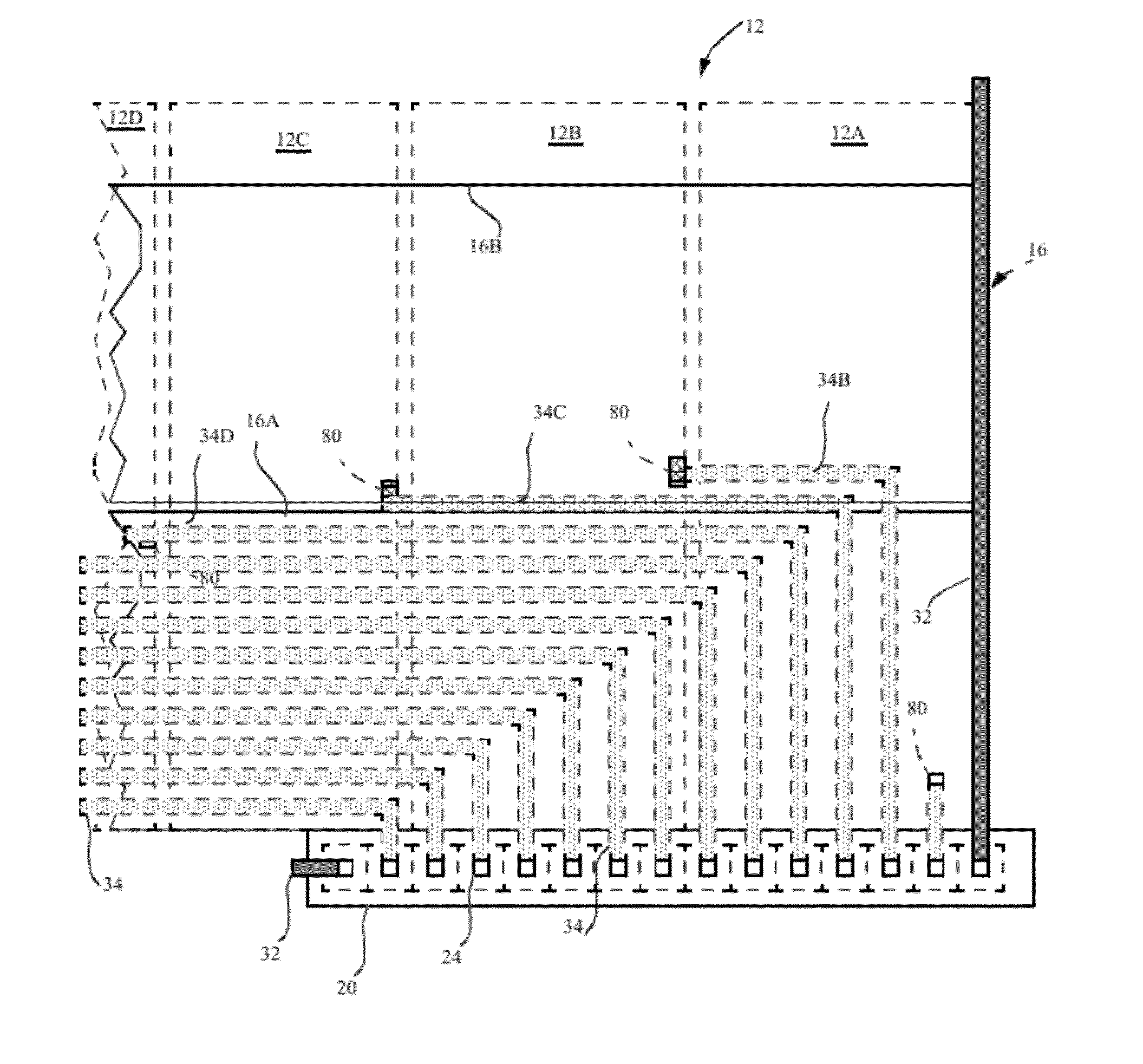

Chiplet display with electrode connectors

ActiveUS8599118B2Improved pixel-driving performanceIncrease light emitting areaDischarge tube luminescnet screensStatic indicating devicesDisplay deviceEngineering

Owner:GLOBAL OLED TECH

Vehicle headlamp

InactiveUS20130010488A1Low costSave spaceVehicle headlampsOptical signallingOptical axisOptoelectronics

A vehicle headlamp has a first light source disposed on a first optical axis that extends in a front-to-rear direction of a vehicle, a first lens that projects light emitted from the first light source to a front of the vehicle, a second lens having a rear focal point on a second optical axis that is parallel to the first optical axis and disposed adjacent to the first lens, a second light source disposed on the second optical axis rearwards of the first light source, a reflector that reflects light emitted from the second light source towards the rear focal point of the second lens, and a sub-reflector disposed such that the sub-reflector does not interfere with an optical path which extends from the reflector to the second lens and that causes part of light emitted from the first light source to be incident on the second lens.

Owner:KOITO MFG CO LTD

Lens, light-emitting diode (LED) backlight module and display device

ActiveCN103090311AIncrease light emitting areaImprove uniformityPoint-like light sourceRefractorsDisplay deviceLight-emitting diode

The invention provides a lens, a light-emitting diode backlight module and a display device, and is applied in the technical field of optics. The lens receives light rays radiated from a light source through a light-in surface, when the light rays radiated from the light source enter into the lens, a part of the light rays directly reflects out from a certain light-out surface, the other part of the light rays reflect to other light-out surfaces or bottom surfaces through a certain light-out surface, then reflect to other light-out surfaces through other light-out surfaces or bottom surfaces, and at last reflect out from the other light-out surface. Accordingly, the light rays radiated from the light source are scattered in the lens and are enabled to reflect out from different light-out surfaces, and thus light-out areas are enlarged and uniformity is good. Therefore, the lens is suitable for various LED backlight module and display devices.

Owner:SHENZHEN COOCAA NETWORK TECH CO LTD

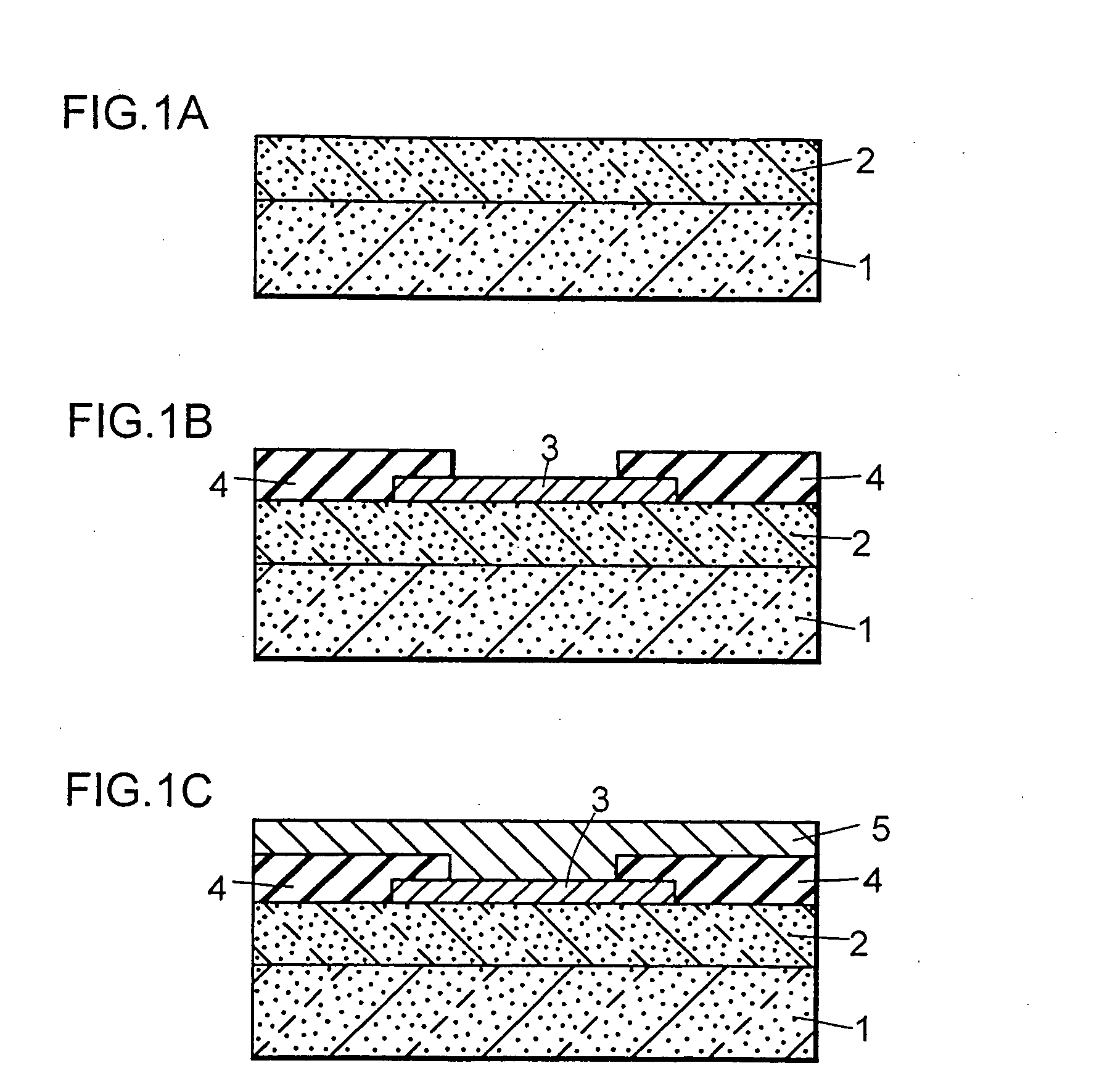

Process for manufacturing AlGaInP light-emitting diode with inclined side face

InactiveCN101807647AIncrease light emitting areaImprove light extraction efficiencySemiconductor devicesReflective layerLight-emitting diode

The invention discloses a process for manufacturing a AlGaInP light-emitting diode with an inclined side face, which comprises the following steps: providing a substrate, forming a distributed Bragg reflecting layer on the top of the substrate, forming a first type epitaxial layer on the distributed Bragg reflecting layer, forming a luminous layer on the first type epitaxial layer, and forming a second type epitaxial layer on the luminous layer; forming a P electrode on the second type epitaxial layer, and forming an N electrode at the bottom surface of the substrate to form an LED chip; cutting the side face of the LED chip at an inclination angle along the direction from the top to the bottom surface of the LED chip by adopting a dry etching method, and cutting the bottom surface of the LED chip by using laser; and finally, cutting through the side face at the bottom of the LED chip by using a diamond knife and forming an inclined plane at the periphery of the LED chip. The AlGaInP light-emitting diode has the advantages of increasing emergent light and decreasing light refracting or reflecting frequency to improve luminous efficiency, and the like.

Owner:XIAMEN SANAN OPTOELECTRONICS TECH CO LTD

Double-face display, control device and manufacturing method of double-face display

ActiveCN103886813AIncrease light emitting areaIncrease display brightnessStatic indicating devicesSolid-state devicesRubber materialElectrophoresis

A double-face display comprises an OLED (organic light emitting diode) substrate, an enclosing substrate on the opposite side of the OLED substrate and rubber materials between the OLED substrate and the enclosing substrate. The enclosing substrate is an electrophoresis film. Displaying of one face of the double-face display can be realized by a part, not covering the OLED substrate, of the electrophoresis film, displaying of the other face of the double-face display is realized by the OLED substrate, the OLED substrate and the electrophoresis film are capable of displaying respectively, or the double faces can be displayed at the same time. The double-face display has the advantages that an OLED lighting area can be increased effectively, an opening rate is increased, displaying brightness of an OLED display device can be effectively increased, and double-side displaying is achieved to adapt to different usage requirements. In addition, OLED displaying and electrophoresis film displaying can supplement each other, an area of luminous pixels is fully utilized, and a better luminous effect can be obtained.

Owner:EVERDISPLAY OPTRONICS (SHANGHAI) CO LTD

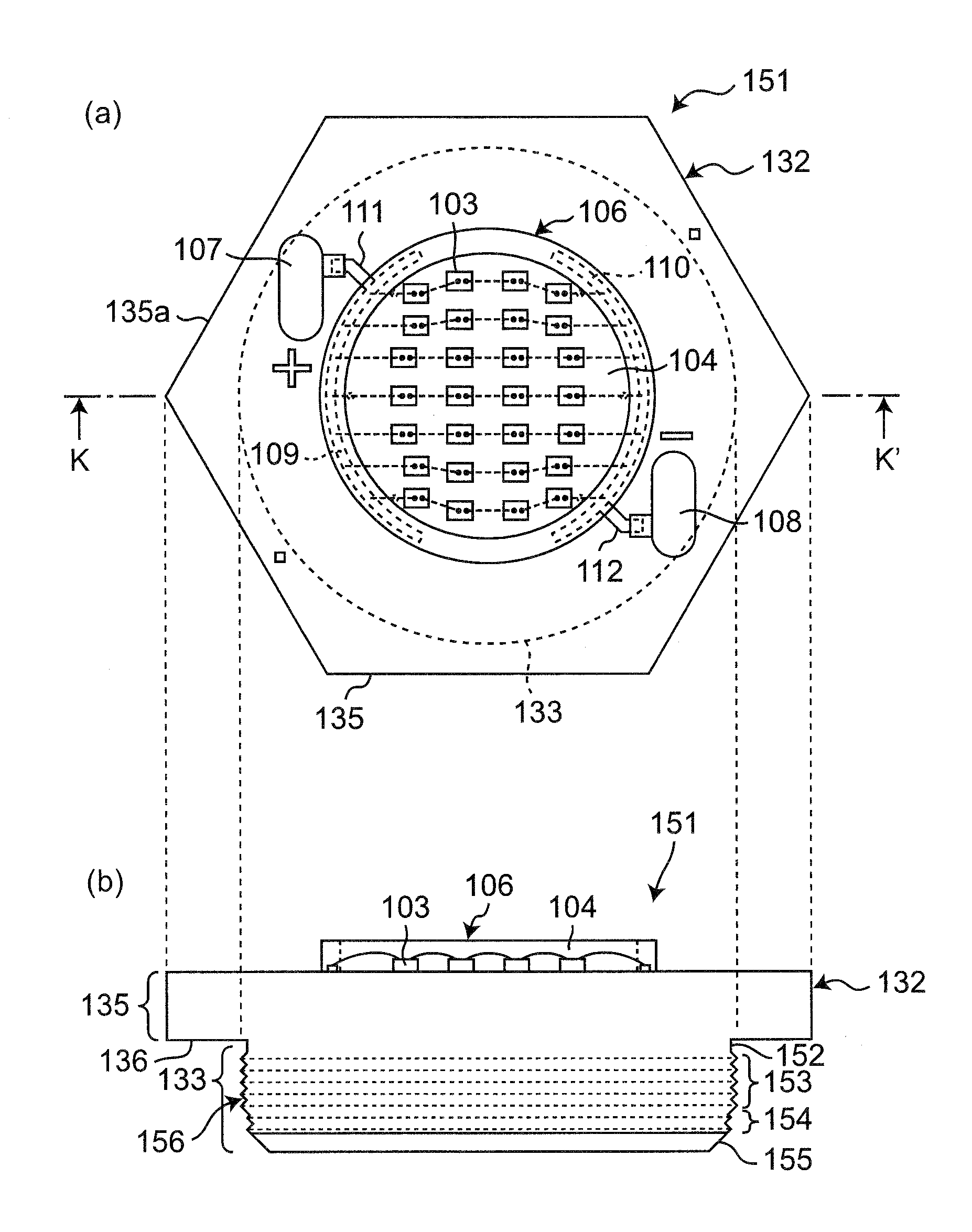

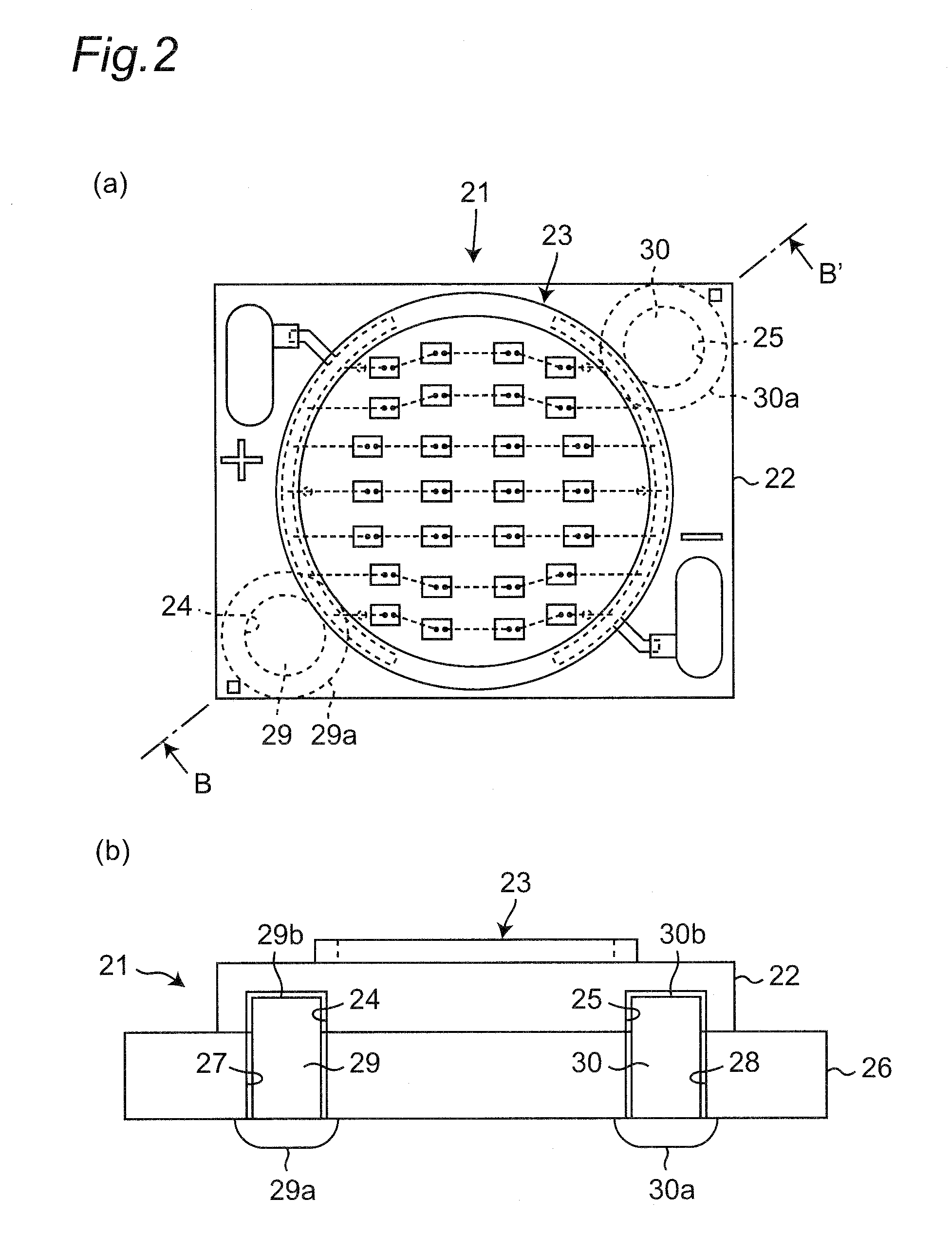

Light-emitting apparatus and structure for attaching light-emitting apparatus to heat sink

InactiveUS20150276198A1Reduce the attachment areaIncrease light emitting areaLighting support devicesPoint-like light sourceHeat sinkLight emitting device

A light-emitting apparatus has a substrate (72) having a generally disc shape, a light-emitting part (76) having a plurality of LED chips (73) mounted on one main surface of the substrate (72), the plurality of LED chips (73) being sealed with a resin (74), and a heat-sink attachment part having a heat-sink attachment male thread (80) formed on a side surface of the substrate (72). When the attachment area of the substrate (72) to the heat sink is kept the same, the light-emitting part (76) may be enlarged, and when the light-emitting unit (76) is kept the same, the attachment area of the substrate (72) may be reduced.

Owner:SHARP KK

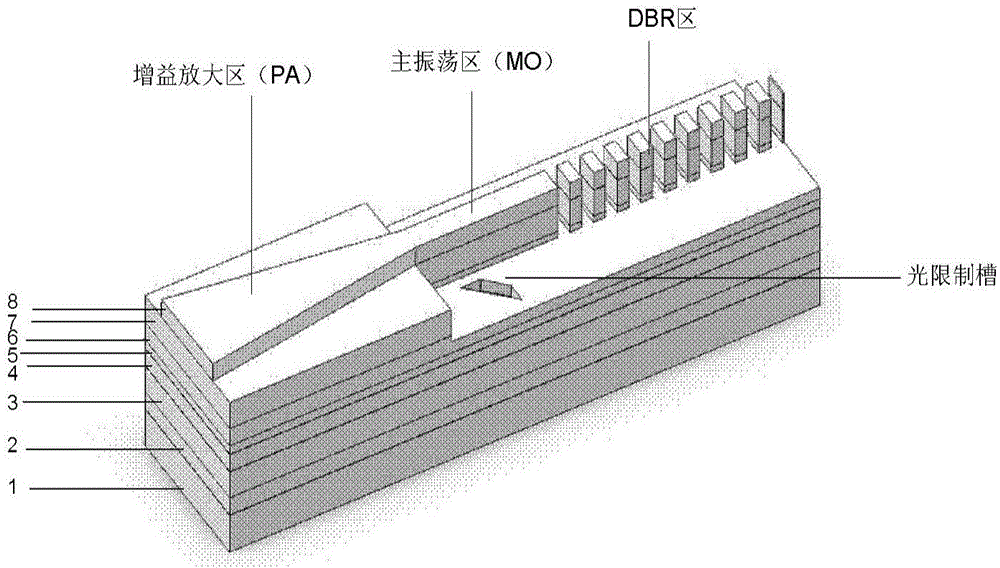

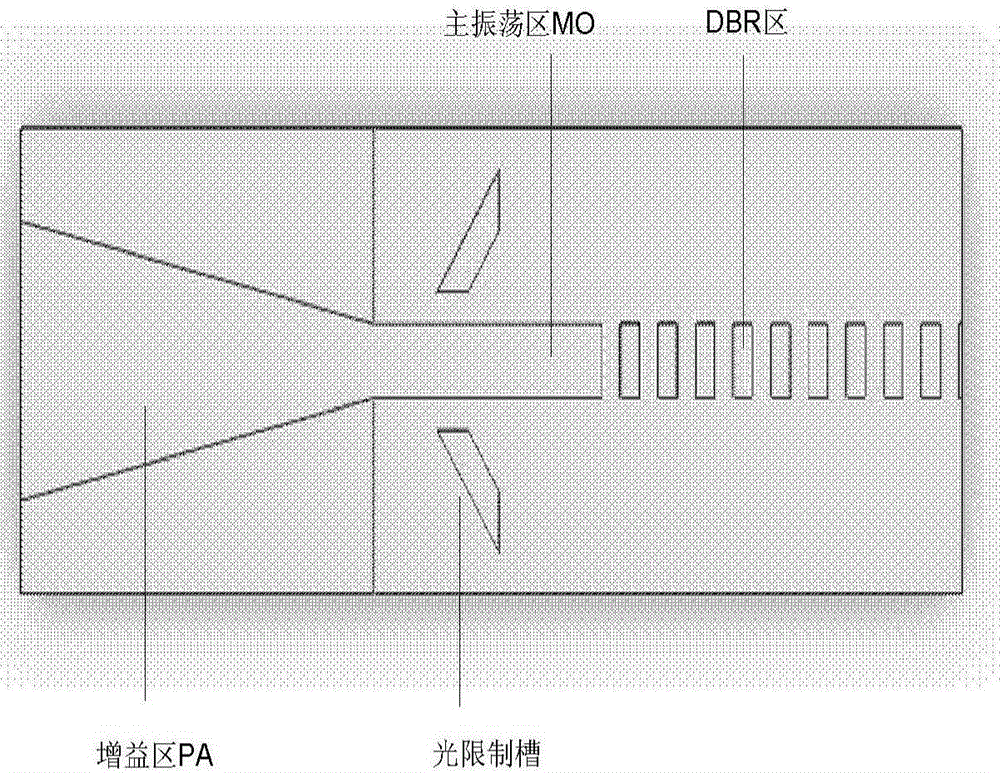

Semiconductor laser and manufacturing method thereof

InactiveCN105161976AGuaranteed to workHigh beam quality of the output light is guaranteed while workingLaser detailsLaser active region structureGratingOptical limiting

The invention discloses a single-mode high-power high-brightness GaSb-based bragg reflection master oscillator power amplifier (MOPA) integrated semiconductor laser and a manufacturing method thereof. The bragg reflection MOPA integrated semiconductor device comprises a substrate, an epitaxy structure, a gain amplification region, a master oscillator region, a bragg reflection region and optical limiting grooves, wherein the epitaxy structure grows on the substrate and comprises an N-type lower contact layer, an N-type lower limiting layer, a lower waveguide layer, an active region, an upper waveguide region, a P-type upper limiting layer and a P-type upper contact layer from bottom to top; the gain amplification region is located on the front part, namely a light outlet part, of the semiconductor laser, and is in a conical structure which is formed by etching the P-type upper contact layer downwards; the master oscillator region is located at the rear part of the gain amplification region and is in a ridge waveguide structure which is formed by etching the P-type upper limiting layer downwards; the bragg reflection region is located at the rear part of the master oscillator region and is in a periodical bragg grating structure which is formed by etching the P-type upper limiting layer downwards; and the optical limiting grooves are symmetrically distributed in two sides of the ridge waveguide and are obliquely arranged together with the ridge waveguide.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI